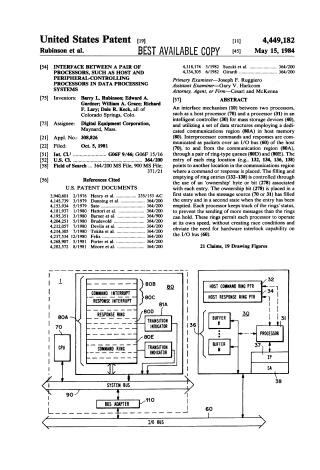

Interface Between a Pair of Processors, Such as Host and Peripheral-Controlling Processors in Data Processing Systems

Order Number: XX-772F5-16

This patent describes an interface mechanism designed for data processing systems, specifically to facilitate communication between a host processor and a peripheral-controlling processor (e.g., in a mass storage controller), especially over an I/O bus that lacks hardware interlock capabilities to prevent race conditions.

The core of the invention involves a dedicated "communications region" established in the host's main memory. This region contains two "ring buffers" (circular queues): one for commands sent from the host to the controller, and another for responses sent from the controller back to the host. Commands and responses are exchanged as packets through these rings.

Key features of this interface include:

- Ownership Bit Protocol (278): Each entry within a ring buffer has an associated "ownership bit." When a processor writes a command or response into a ring entry, it sets this bit to indicate ownership. The receiving processor, upon reading and processing the entry, clears the bit. This strict protocol ensures that an entry is neither read twice nor overwritten before being read, effectively preventing race conditions without requiring hardware interlocks on the bus.

- Asynchronous Operation and Reduced Interrupts: The design allows both the host and controller to operate independently at their own speeds. Interrupts to the host are significantly reduced, typically occurring only when a ring transitions between "full" and "not-full" (for commands) or "empty" and "not-empty" (for responses), rather than for every single message. This buffering of asynchronous message exchanges enhances efficiency.

- Credit-Based Flow Control: A mechanism based on "credits" (288) prevents the host from overwhelming the controller with commands. The controller communicates how many commands it can buffer. The host decrements this credit count when sending commands and increments it upon receiving responses, ensuring it does not send more commands than the controller can handle.

- Robust Initialization: A multi-step initialization process is defined for both the host and controller to establish communication parameters (like ring sizes and interrupt vectors) and verify the integrity and compatibility of the interface.

- Polling: Processors use polling of specific registers (e.g., IP register 37 for the host to prompt controller polling, and host polling the response ring) to detect new messages, complementing the interrupt mechanism for efficiency.

This interface allows for reliable, high-performance interprocessor communication, prevents race conditions, and minimizes host CPU overhead on buses that do not intrinsically support hardware synchronization.

Site structure and layout ©2025 Majenko Technologies