G7002

Order Number: XX-88AE6-31

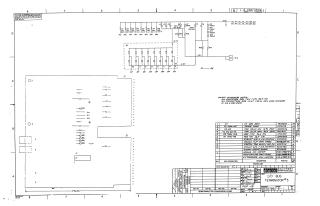

This document is an engineering drawing (DCS G7002-0-1, Revision B) from Digital Equipment Corporation, dated October 30, 1972, for an "I/O BUS TERMINATOR #3" designed for the PDP-10 computer system.

The document includes a schematic diagram illustrating the termination circuit, which features:

- Resistor networks (100 Ohm and 1.5K Ohm) for bus termination.

- Capacitors, including 39µF tantalum capacitors and .01µF disc ceramic capacitors.

- Diodes (D662) and an integrated circuit (DEC 2501).

- Voltage references and power distribution at -0.7V, -2.8V, and -15V relative to ground.

A comprehensive parts list provides quantities, reference designations, descriptions, and part numbers for all electronic components and associated mechanical hardware (like eyelets, a flip-chip handle, and the etched circuit board). General specifications indicate default resistors are 1.5K ±5% 1/4W CC and default capacitors are .01µF ±20% 100V Disc Ceramic. The document also contains proprietary information from Digital Equipment Corporation.

Site structure and layout ©2025 Majenko Technologies