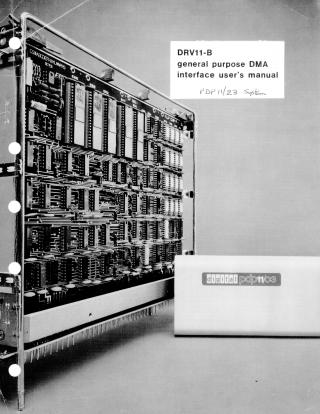

DRV11-B General Purpose DMA Interface User's Manual

Order Number: EK-DRV1B-OP

This document is the user's manual for the DRV11-B, a general-purpose Direct Memory Access (DMA) interface designed for the Digital Equipment Corporation LSI-11 PDP-11/03 system, published in August 1976.

The DRV11-B enables high-speed, direct 16-bit data transfers between the LSI-11's memory and a user's I/O device. It functions as a bus master to facilitate data transfer out (DATO/DATOB) from the I/O device to memory, or data transfer in (DATI/DATIO) from memory to the I/O device. It supports burst modes, byte addressing, and read-modify-write operations, achieving transfer rates of up to 250,000 words per second in single cycle mode and 500,000 words per second in burst mode.

Key components of the DRV11-B include five internal registers: a Word Count Register (WCR), a Bus Address Register (BAR), a Control/Status Register (CSR), and Input/Output Data Buffer Registers (DBRs). These registers are programmable to control the number of transfers, memory addresses, and various interface functions and status. The module features switch-programmable device and interrupt vector addresses and connects to user I/O devices via two 40-pin connectors.

Operation is initialized by programming the WCR, BAR, and CSR. The interface automatically increments the WCR and BAR during transfers. It generates interrupts upon transfer completion (when the word count reaches zero), or in response to specific conditions such as a user-defined attention signal (ATTN) or an attempt to address a nonexistent memory location.

The manual provides comprehensive details on the DRV11-B's specifications (physical, electrical, environmental), installation procedures (including bus loading, power, priority, and cabling), a functional description of its registers and interface lines, detailed data flow and timing diagrams for various transfer modes, and programming instructions for its operation and interrupt handling.

Site structure and layout ©2025 Majenko Technologies