# DIGITAL ETHERNET UNIBUS Network Adapter Technical Manual

# DIGITAL ETHERNET UNIBUS Network Adapter Technical Manual

**PRELIMINARY**

Prepared by Educational Services of Digital Equipment Corporation

# © Digital Equipment Corporation 1982 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

## Printed in U.S.A.

This document was set on DIGITAL's DECset Integrated Publishing System.

The following are trademarks of Digital Equipment Corporation:

| digital™     | DECwriter    | RSX            |  |  |

|--------------|--------------|----------------|--|--|

| Gigital      | DIBOL        | TS05           |  |  |

| DEC          | MASSBUS      | TSV05          |  |  |

| DECmate      | PDP          | UNIBUS         |  |  |

| DECset       | P/OS         | VAX            |  |  |

| DECsystem-10 | Professional | VMS            |  |  |

| DECSYSTEM-20 | Rainbow      | VT             |  |  |

| DECUS        | RSTS         | Work Processor |  |  |

# CONTENTS

|                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER                                                                                                                                                                                                  | 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                     |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1<br>1.4.2<br>1.4.3<br>1.4.4<br>1.4.5<br>1.4.6<br>1.5                                                                                                                    | SCOPE ETHERNET OVERVIEW. DEUNA GENERAL DESCRIPTION. DEUNA SYSTEM OPERATION. ETHERNET Physical Channel Functions. ETHERNET Data Link Functions. Data Encapsulation. Data Decapsulation. Link Management. Diagnostics and Maintenance. DEUNA SPECIFICATIONS. RELATED DOCUMENTS.                                                                                                                                                                                                                                                             | 1-1<br>1-4<br>1-6<br>1-9<br>1-9<br>1-9<br>1-1<br>.1-12                                                                                                              |

| CHAPTER                                                                                                                                                                                                  | 2 PORT MODULE FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                     |

| 2.1<br>2.2<br>2.2.1<br>2.2.1.1<br>2.2.1.2<br>2.2.2<br>2.2.2.1<br>2.2.2.2<br>2.2.2.3<br>2.2.2.4<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.7<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.3 | OVERVIEW.  UNIBUS INTERFFACE.  DMA Control.  RX DMA.  T11 UNIBUS DMA.  Port Control and Status Register Ø.  Port Control and Status Register 1  Port Control and Status Register 2  Port Control and Status Register 3.  MICROPROCESSOR SECTION.  Microprocessor.  Internal Registers.  Default Station Address  Physical Address Registers.  Port Switchpack Register.  Timer.  Internal Buses.  LINK MEMORY CONTROL  Link Memory Arbitration  Link Transmit Address Counter  Link Receive Address Counter  Link Receive Address Counter | 2-3<br>2-4<br>.2-10<br>.2-13<br>.2-13<br>.2-18<br>.2-20<br>.2-21<br>.2-22<br>.2-22<br>.2-25<br>.2-26<br>.2-26<br>.2-28<br>.2-29<br>.2-29<br>.2-30<br>.2-30<br>.2-30 |

| 2.4.4<br>2.4.5<br>2.4.5.1<br>2.4.5.2<br>2.4.5.3<br>2.4.5.4<br>2.4.5.5                                                                                                                                    | Tll Addressing of Link Buffer Memory  Port-to-Link Interface  Link Memory Bus  Link Memory Address Control Signals  Command Register Control  Link Discrete Status  Clock and Reset                                                                                                                                                                                                                                                                                                                                                       | .2-35<br>.2-35<br>.2-36<br>.2-36                                                                                                                                    |

# CONTENTS (Cont)

|         |                                      | Page                |

|---------|--------------------------------------|---------------------|

| CHAPTER | 3 LINK MODULE FUNCTIONAL DESCRIPTION |                     |

| 3.1     | TMERODUCETON                         |                     |

| 3.2     | INTRODUCTION                         | 3-1                 |

| 3.3     | LINK MEMORY BUS                      | 3-1                 |

|         | LINK REGISTERS                       | •••3 <del>-</del> 5 |

| 3.3.1   | Command Register                     | 3-5                 |

| 3.3.2   | Link Mode Register                   | 3-7                 |

| 3.3.3   | Station Address RAM                  | 3-10                |

| 3.4     | PHYSICAL CHANNEL INTERFACE           | 3-12                |

| 3.4.1   | Tranceiver Signals                   |                     |

| 3.4.2   | Receiver                             | 3-12                |

| 3.4.2.1 | Receiver Squelch and Currier Sense   | 3-12                |

| 3.4.2.2 | Manchester Decoder                   | 3-13                |

| 3.4.2.3 | Clock Shaper                         |                     |

| 3.4.2.4 | Collision Squelch                    |                     |

| 3.4.3   | Transmitter                          | 3 – 1 3             |

| 3.4.3.1 | Manchester Encoder                   | 3-13                |

| 3.4.3.2 | Transmit Enable Sync                 | 3 – 1 4             |

| 3.5     | TRANSMIT SECTION                     | 3-14                |

| 3.5.1   | Data Section                         | 3 – 1 4             |

| 3.5.2   | TX Data Latch                        |                     |

| 3.5.3   | TX Message Byte Counter              | 3-16                |

| 3.5.4   | TX Frame and Byte Sync               | 3-16                |

| 3.5.5   | TX Shift MUX                         | 3-16                |

| 3.5.6   | TX Shifter                           | 3-17                |

| 3.5.7   | TX Output MUX                        |                     |

| 3.5.8   | TX Status Information                |                     |

| 3.5.9   | Transmit State Machine               | 2-2 <i>a</i>        |

| 3.6     | RETRY LOGIC                          | J-Zb                |

| 3.6.1   | Collision Jam                        | 2 21                |

| 3.6.2   | Slot Time Counter                    | 3-21                |

| 3.6.3   | 10 MHz Oscillator                    | 3-21                |

| 3.6.4   | Random Number Generator              | 3-21                |

| 3.6.5   | Random Interval Mask/Latch           | 3-21                |

| 3.6.6   | Interval Counter                     | 3 – 2 1             |

| 3.6.7   |                                      |                     |

| 3.6.8   | Retry Counter                        |                     |

| 3.6.9   | Retry State Machine                  | 3-22                |

| 3.7     | Time Domain Reflectometry            | 3-23                |

| 3.7.1   | RECEIVE SECTION                      |                     |

| 3.7.2   | Data Section                         |                     |

|         | Receive MUX                          |                     |

| 3.7.3   | Receive Shifter                      | 3-25                |

| 3.7.4   | RX Data Latch                        | 3-26                |

| 3.7.5   | RX Frame and Byte Sync               | 3-26                |

| 3.7.6   | RX Byte Counter                      | 3-26                |

| 3.7.7   | Receive State Machine                | 3-26                |

| 3.7.8   | Interpacket Delay                    | 3-27                |

| 3.8     | STATION ADDRESS DECODE               | 3-27                |

| 3.8.1   | Physical/Logical Address Detection   | 3-28                |

# CONTENTS (Cont)

|                                                                                                                 | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.8.2<br>3.8.3<br>3.9<br>3.10<br>3.11<br>3.12                                                                   | Promiscuous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 4                                                                                                       | MICROCODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.4.1<br>4.3.4.2<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8 | OVERVIEW.       4-1         STRUCTURE.       4-1         SUPERVISOR.       4-1         Initialization.       4-1         Scheduling.       4-2         Datagram Receive Process.       4-3         Command Execution Process.       4-7         Port Commands.       4-7         Ancilliary Commands.       4-9         Timer Process.       4-10         Loop and Maintenance Process       4-10         Transmit Datagram Process       4-14         Null Process.       4-15 |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                 | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure No                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# FIGURES (Cont)

Title

Tll Address Space......2-24

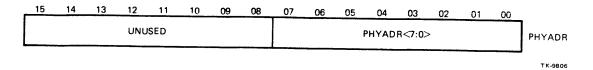

Physical Address Register Bit Configuration.....2-27

Port Switchpack Register Bit Configuration.....2-28

Page

Figure No.

2-13

2-14

2-15

4-1

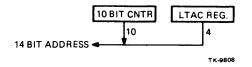

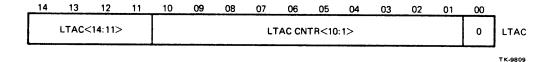

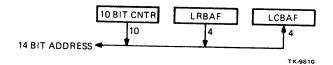

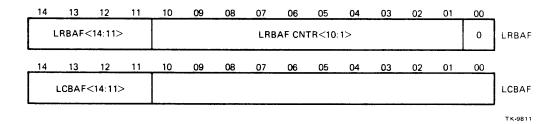

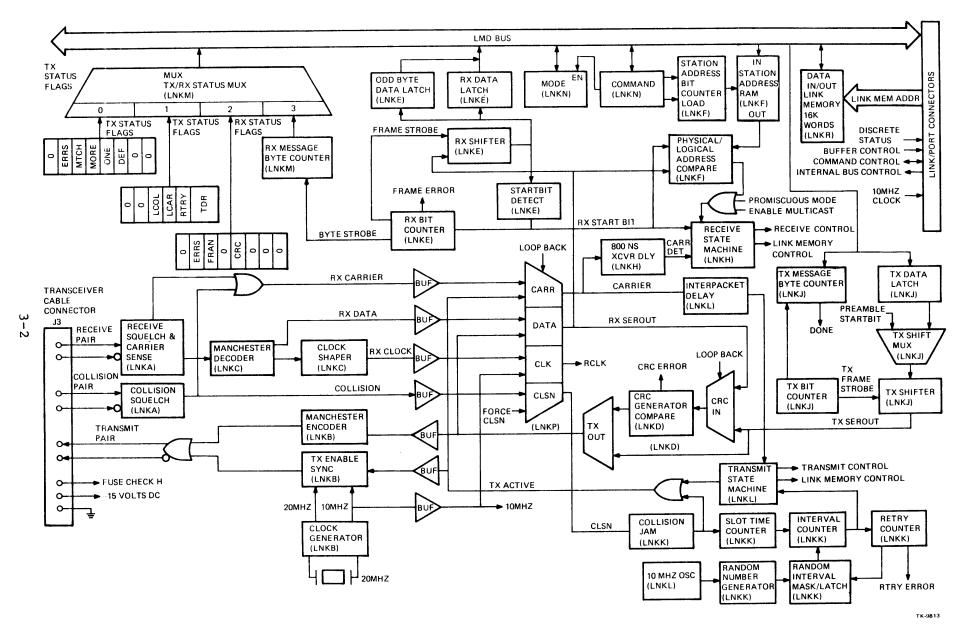

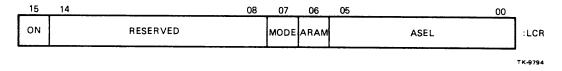

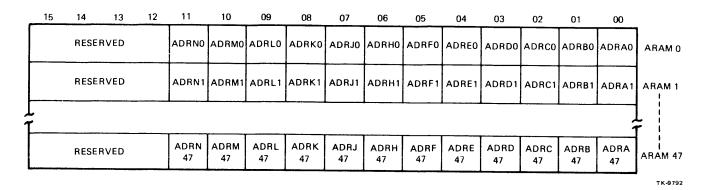

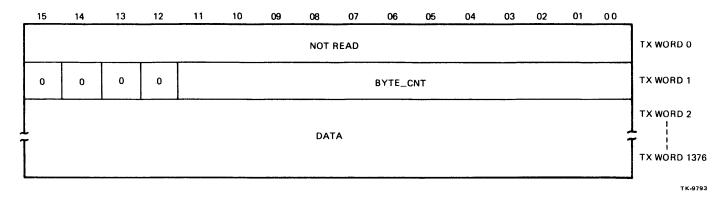

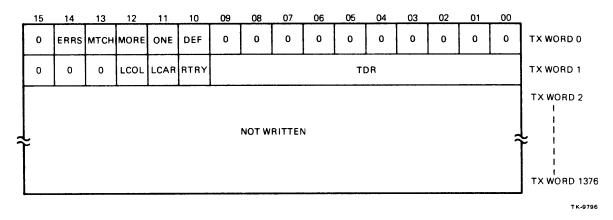

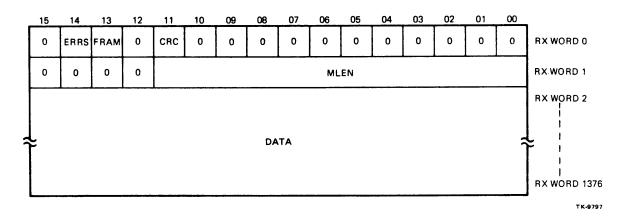

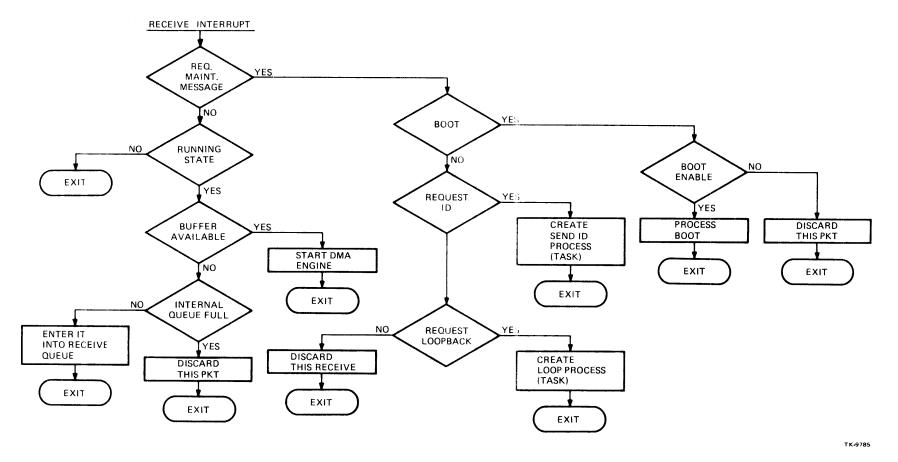

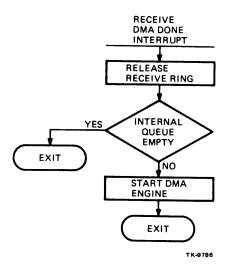

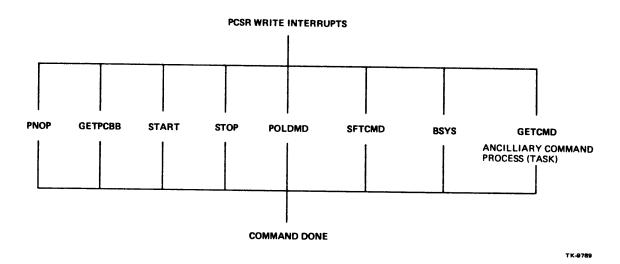

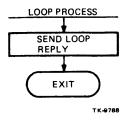

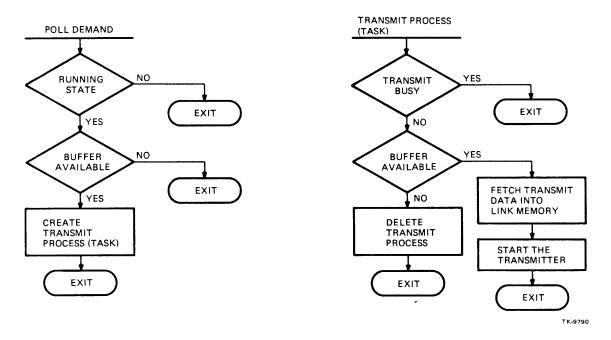

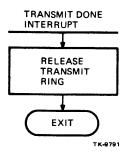

| LTAC Configuration. 2- LTAC Bit Configuration. 2- Receive Address Counter Configuration. 2- LRBAF, LCBAF Bit Configuration. 2- Link Module Functional Block Diagram. 3- Format of Link Command Register . 3 Link Mode Register Format. 3- Station Address RAM Format . 3- Transmit Buffer Format Before Transmission. 3- Transmit Buffer Format. 3- Receive Buffer Format. 3- Receive Flow Diagram. 4- Receive DMA Done Flow Diagram. 4- Port Command Processes. 4- Loop Process Flow Diagram. 4- Station ID Flow Diagram. 4- Transmit Flow Diagram. 4- Transmit Flow Diagram. 4- Transmit Done Flow Diagram. 4- | 31<br>32<br>33<br>34<br>-6<br>-8<br>11<br>15<br>16<br>-8<br>11<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Title Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | дe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DEUNA Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14<br>16<br>14<br>19<br>12<br>12<br>12<br>12<br>13<br>14<br>15<br>16<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LTAC Configuration. 2— LTAC Bit Configuration . 2— Receive Address Counter Configuration . 2— LRBAF, LCBAF Bit Configuration . 2— Link Module Functional Block Diagram . 3 Format of Link Command Register . 3 Link Mode Register Format . 3 Station Address RAM Format . 3— Transmit Buffer Format Before Transmission . 3— Transmit Buffer Format . 3— Receive Buffer Format . 3— Receive Buffer Format . 3— Receive DMA Done Flow Diagram . 4 Port Command Processes . 4 Loop Process Flow Diagram . 4— Station ID Flow Diagram . 4— Transmit Flow Diagram . 4— Transmit Flow Diagram . 4— Transmit Done Flow Diagram . 4— Double Transmit Done Flow Diagram . 4— Transmit Buffer Bit Descriptions . 3— Transmit |

Priority of Processes.....4-3

#### 1.1 SCOPE

This chapter provides an introduction to the DIGITAL ETHERNET UNIBUS Network Adapter (DEUNA). A brief overview of the ETHERNET local area network is included, followed by a description of the DEUNA, its operation, and specifications. Additional documents related to this manual are listed for the reader who wishes more information about the ETHERNET, the DEUNA, or local area networks.

#### 1.2 ETHERNET OVERVIEW

The ETHERNET is a local area network that provides a communications facility for high-speed data exchange among computers and other digital devices located within a moderately sized geographic area. It is intended primarily for use in such areas as office automation, distributed data processing, terminal access, and other situations requiring economical connection to a local communication medium carrying traffic at high-peak data rates.

The primary characteristics of ETHERNET include:

Topology Branching bus.

Medium Shielded coaxial cable, Manchester

encoded digital base-band signaling.

Data Rate 10 million bits per second.

Maximum Separation of Nodes 2.8 kilometers (1.74 miles).

Maximum Number of Nodes 1,024

Network Control Multiaccess -- fairly distributed to

all nodes.

Access Control Carrier Sense, Multiple Access with

Collision Detect (CSMA/CD).

Allocation Packet length from 64 to 1518 bytes

(includes variable data field of

from 46 to 1500 bytes).

The ETHERNET, like other local area networks, falls into a middle ground between long-distance, low-speed networks that carry data for hundreds or thousands of kilometers and specialized, very high-speed interconnections that are generally limited to tens of meters. Using a branching bus topoloy, ETHERNET provides a local area communications network allowing a lØM bits/s data rate over a coaxial cable at a distance of up to 2.8 km (1.74 mi).

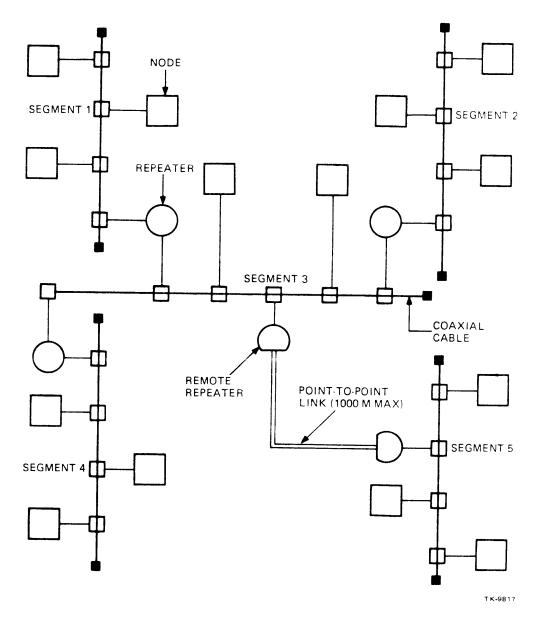

A single ETHERNET can connect up to 1,024 nodes together for a local point-to-point/multipoint network. An example of a typical large-scale ETHERNET configuration is shown in Figure 1-1.

Rules for configuring ETHERNET are derived from certain limits that are imposed on the physical channel to ensure the optimal performance of the network. The maximum configuration for an ETHERNET is as follows:

- A segment of coaxial cable can be a maximum of 500 meters (1640.5 feet) in length. Each segment must be terminated at both ends in its characteristic impedance.

- Up to 100 nodes can be connected to any segment of the cable. Nodes on a cable segment must be spaced at least 2.5 meters (8.2 feet) apart.

- The maximum length of coaxial cable between any two nodes is 1,500 meters (4921.5 feet).

- The maximum length of the transceiver cable between a transceiver and a controller is 50 meters (164.05 feet).

- A maximum of 1,000 meters (3281 feet) of point-to-point link is allowed for extending the network.

- Repeaters can be used to continue signals from one cable segment of the ETHERNET to another. A maximum of two repeaters can be placed in the path between any two nodes.

Figure 1-1 Typical Large-Scale ETHERNET Configuration

# 1.3 DEUNA GENERAL DESCRIPTION

The DEUNA is a data communications controller used to interface VAX-11 and PDP-11 family computers to the ETHERNET local area network. It complies with the ETHERNET specification and allows communication with up to 1024 addressable devices using the ETHERNET shielded coaxial cable.

## Features of the DEUNA include:

- 10M bits/s transmission and reception,

- Transmit and receive data link management,

- Data encapsulation and decapsulation,

- Data encoding and decoding,

- Down-line loading and remote load detect capabilities,

- Internal ROM based microdiagnostics to facilitate diagnosis and maintenance of both the DEUNA and the DIGITAL H4000 transceiver,

- Collision detection and automatic retransmission,

- 32-bit Cyclic Redundancy Check (CRC) error detection, and

- 32 KB (16 KW) buffer for continuous datagram reception, transmission, and maintenance requirements.

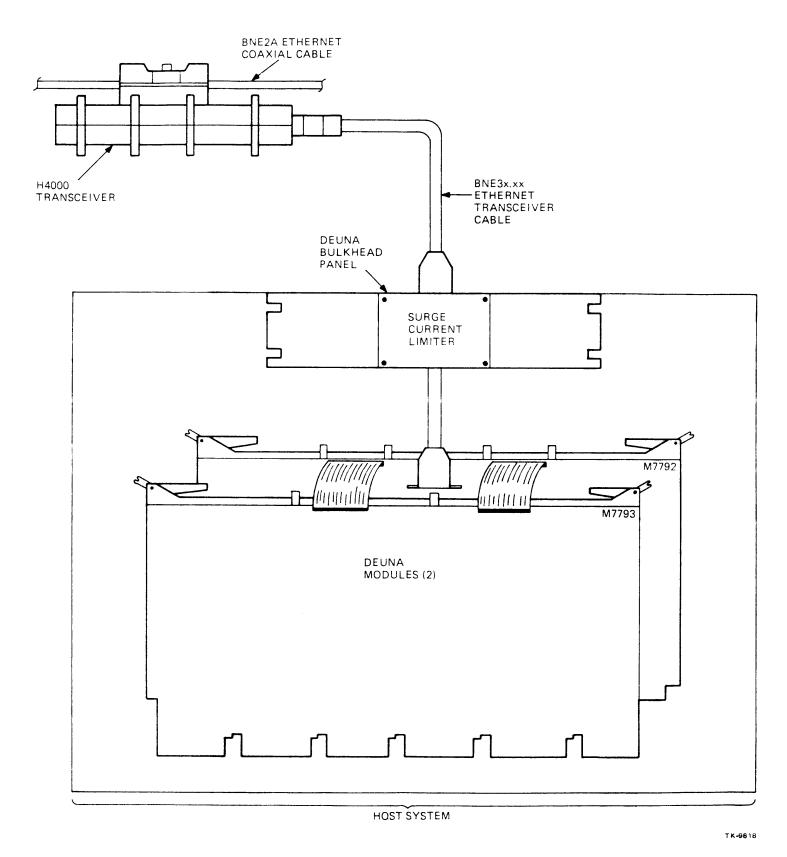

The DEUNA is comprised of two hex-height modules, a bulkhead interconnect panel, and associated cables. It physically and electrically connects to the ETHERNET cable via the DIGITAL H4000 transceiver and the appropriate transceiver cable as shown in Figure 1-2.

Figure 1-2 DEUNA to ETHERNET Connection

#### 1.4 DEUNA SYSTEM OPERATION

The DEUNA controller performs both the ETHERNET data link layer functions and a portion of the physical channel functions. It also provides the following network maintainability features.

- Loopback of data from other stations.

- Individual system identification.

- Loading and remote booting of UNIBUS systems from other stations on the network.

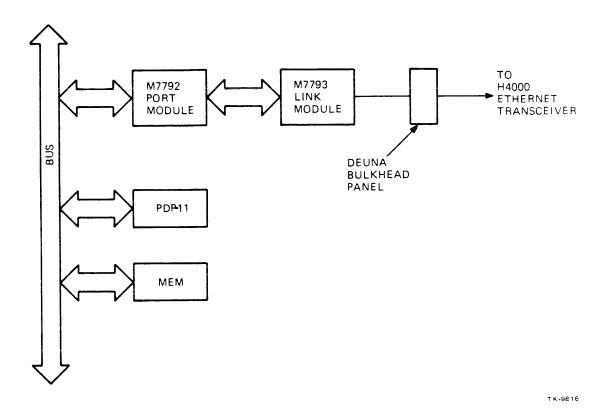

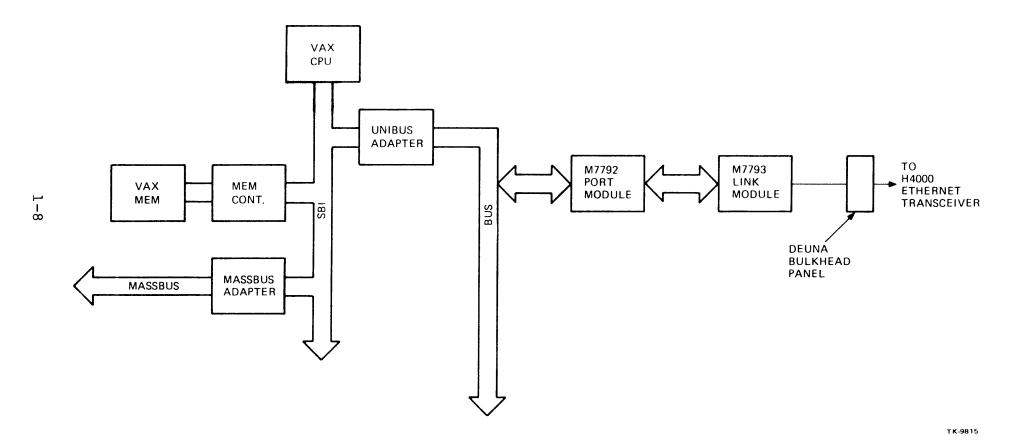

The DEUNA is a microprocessor based device that, when connected to the DIGITAL H4000 ETHERNET transceiver, provides all the logic necessary to connect VAX-11 and UIBUS PDP-11 family minicomputers to an ETHERNET local area network (Figures 1-3 and 1-4). The controller microcode implements data encapsulation and decapsulation, data link management, and all channel access functions to ensure maximum throughput with minimum host processor intervention.

# 1.4.1 ETHERNET Physical Channel Functions

The DEUNA provides the following specific ETHERNET physical channel functions necessary to interface to the DIGITAL H4000 ETHERNET transceiver:

## During Transmission

- Generates the 64-bit preamble for synchronization.

- Generates the Manchester encoding of data.

- Provides parallel-to-serial conversion of the frame.

- Ensures proper channel access by monitoring and sensing the carrier from any stations' transmission.

- Monitors the self-test collision detect signal from the DIGITAL H4000 transceiver.

## During Reception

- Senses carrier from any stations' transmission.

- Provides serial-to-parallel conversion of the frame.

- Performs Manchester decoding of the incoming bit streams.

- Buffers received frames.

- Synchronizes to the preamble and removes it prior to processing.

Figure 1-3 PDP-11 Host System Block Diagram

Figure 1-4  $\,$  VAX-11 Host System Block Diagram

#### 1.4.2 ETHERNET Data Link Functions

The DEUNA provides the following specific ETHERNET data link layer functions.

- Calculates the 32-bit CRC value and places it in the frame sequence field upon transmission

- Attempts automatic retransmission upon collision detection

- Checks incoming frames for proper CRC value

- Performs all address filtration

## 1.4.3 Data Encapsulation

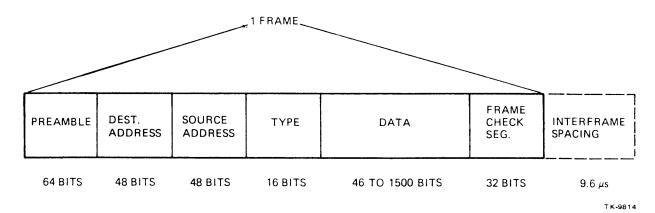

The ETHERNET frame format for the transmission of data packets is shown in Figure 1-5. Each frame begins with a 64-bit preamble, that is used for synchronization by the receiving station, and ends with a 32-bit frame check sequence. Frames are separated by a specified minimum spacing period of 9.6 microseconds.

The destination address field contains the address(es) of the station(s) where the packet is sent. The address may represent: the physical or logical address of a particular station or group of stations; a multicast, or group address, associated with a set of stations; and a broadcast address for broadcast to all stations on the network.

The source address field specifies the physical address of the transmitting station. Each DEUNA has a unique 48-bit address value determined during manufacture. This value is called the default physical address. The system software can override this value and insert a more apropriate logical address into the source address field upon transmission.

The type field is specified for use by high-level network protocols and it indicates how the content of the data field is to be interpreted. The type field indicates the higher level architecture that can further decapsulate the data.

The data field may have between 46 and 1500 bytes of data. The DEUNA can be initialized to automatically insert null characters if the amount of data is less than the minimum 46 byte data size.

The frame check sequence contains a 32-bit Cyclic Redundancy Check (CRC) value that is determined and inserted by the DEUNA during transmission.

## 1.4.4 Data Decapsulation

The DEUNA continuously monitors the signals transmitted by the DIGITAL H4000 transceiver. After sensing a carrier, the preamble sequence of the received frame is used by the controller for synchronization. It then processes the destination address field through a hardware comparator to determine whether or not the incoming frame is intended for its station. The DEUNA accepts only

Figure 1-5 Format of an ETHERNET Data Packet

frames that have a destination address that matches one of the following types of address.

- 1. The physical address of the station

- 2. The broadcast address for all stations

- One of the 10 multicast group addresses that the user may assign to the DEUNA

- 4. Any multicast address

- 5. All addresses, when desired

The DEUNA performs a hardware comparison of the 48-bit destination address to determine if there is a match with the station's physical address or with one of the ten user designated logical multicast addresses. If necessary, all multicast addresses may be passed to higher level software for decoding when more than ten multicast address groups are required by the user.

To assist in network management functions and to aid in fault diagnosis, the DEUNA can operate in a mode that effectively disregards the internal address filter logic. This allows all frames received from the network to be accepted. The DEUNA verifies the integrity to the received data by recalculating the 32-bit CRC value and comparing it with the CRC that is obtained from the received frame.

#### 1.4.5 Link Management

The method utilized by the ETHERNET for channel access is called carrier sense, multiple access with collision detect (CSMA/CD). The DEUNA controls all of the link management functions necessary to successfully place or remove a frame of data on the ETHERNET network. These functions include:

Carrier Deference

The DEUNA monitors the physical channel for traffic and when the channel is busy, refers to the passing frame by delaying any transmission of its own.

Collision Detection

Collisions occur when two of more controllers attempt to transmit data simultaneously on the channel. The DEUNA monitors the collision sense signal generated by the DIGITAL H4000 transceiver. When a collision is detected, the DEUNA continues to transmit to ensure that all network stations detect the collision.

Collision Backoff Retransmission

When a controller has attempted transmission and encountered a collision on the channel, it attempts a retransmission a short time later. The schedule for retransmission is determined by a controlled randomization process. The DEUNA attempts to transmit a total of sixteen times and reports an error if it is not successful.

# 1.4.6 Diagnostics and Maintenance

The DEUNA utilizes both microdiagnostics and extensive system and network diagnostics to greatly minimize the time to isolate and diagnose a network communication fault. On-board self-test microdiagnostics automatically perform a test of the major DEUNA component logic both upon powerup and at the user's discretion. Light emitting diodes on the edge of the port module (M7792) provide an indication of a specific module problem.

The DEUNA does not allow itself to transmit significantly longer than the maximum ETHERNET frame transmit period. It contains an automatic control to prevent monopolizing the ETHERNET channel. The controller can differentiate between normal frame collisions on the physical channel and cable shorts or cable opens. A built-in Time Domain Reflectometry (TDR) circuit is utilized to determine the type of cable fault and its approximate location.

The controller continuously monitors the power applied to the DIGITAL H4000 transceiver to ensure compliance with the transceiver requirements. In addition, the H4000 provides a positive functional verification (heartbeat) after every attempted transmission which indicates its proper operation, including the collision sense circuitry.

Comprehensive system diagnostics provide loopback capability through the DEUNA, transceiver, or the ETHERNET network itself. The DEUNA allows remote stations to loopback through it once the DEUNA has successfully passed the the on-board self-test micro-diagnostic. This provides both a local and remote station diagnostic capability. Network error conditions are detected and statistics tabulated for use by higher level network management applications.

## 1.5 DEUNA SPECIFICATIONS

The DEUNA specifications are outlined in Table 1-1.

Table 1-1 DEUNA Specifications

| Specification                                        | Description                                                 |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| Performance                                          |                                                             |  |  |  |  |  |

| Operating Mode                                       | Half-duplex                                                 |  |  |  |  |  |

| Data Format                                          | ETHERNET specification                                      |  |  |  |  |  |

| Date Rate                                            | lØM bits/s                                                  |  |  |  |  |  |

| Network Specifications                               | 1024 stations maximum                                       |  |  |  |  |  |

| UNIBUS Conductor Loading                             |                                                             |  |  |  |  |  |

| Module Pair                                          | 4 dc loads<br>2 ac loads                                    |  |  |  |  |  |

| DC Power Requirements                                |                                                             |  |  |  |  |  |

| Port Module                                          | +5 V, 7.0 A                                                 |  |  |  |  |  |

| Link Module                                          | +5 V, 9.0 A                                                 |  |  |  |  |  |

|                                                      | -15 V, 2.0 A (for H4000 transceiver)                        |  |  |  |  |  |

| Physical Size                                        |                                                             |  |  |  |  |  |

| Port and Link Modules                                | Height (hex): 21.4 cm (8.4 in)<br>Length: 39.8 cm (15.7 in) |  |  |  |  |  |

| Cable Interface Panel                                | Height: 10.6 cm (4.0 in)<br>Length: 10.6 cm (4.0 in)        |  |  |  |  |  |

| Transceiver Cables available 20 m (65.6 ft) lengths. | in 5 m (16.4 ft), 10 m (32.8 ft), or                        |  |  |  |  |  |

| BNE3A-XX                                             | Low loss PVC jacket/straight connector                      |  |  |  |  |  |

| BNE3B-XX                                             | Low loss PVC jacket/right angle connector                   |  |  |  |  |  |

| BNE3C-XX                                             | Low loss TEFLON* jacket/straight connector                  |  |  |  |  |  |

| BNE3D-XX                                             | Low loss TEFLON* jacket/right angle connector               |  |  |  |  |  |

<sup>\*</sup>TEFLON is a trademark of Dupont de Nemours & Co., Inc.

Table 1-1 DEUNA Specifications (Cont)

| Specification         | Description                      |  |  |  |  |  |

|-----------------------|----------------------------------|--|--|--|--|--|

| Operating Environment |                                  |  |  |  |  |  |

| Temperature           | 5°C to 50°C (41°F to 122°F)      |  |  |  |  |  |

| Relative Humidity     | 10 to 90% (noncondensing)        |  |  |  |  |  |

| Wet Bulb Temperature  | 32°C (90°F) maximum              |  |  |  |  |  |

| Altitude              | Sea level to 2.4 km (8,000 ft)   |  |  |  |  |  |

| Shipping Environment  |                                  |  |  |  |  |  |

| Temperature           | -40°C to 0°C<br>(-40°F to 151°F) |  |  |  |  |  |

| Relative Humidity     | Ø to 90% (noncondensing)         |  |  |  |  |  |

| Altitude              | Sea level to 9 km (30,000 ft)    |  |  |  |  |  |

# 1.6 RELATED DOCUMENTS

Table 1-2 provides a list of documents related to this manual.

Table 1-2 Related Hardware and Software Documents

| Title                                                                                       | Document Numbers |

|---------------------------------------------------------------------------------------------|------------------|

| DEUNA User's Guide                                                                          | EK-DEUNA-UG      |

| H4000 Technical Description                                                                 | (TBS)            |

| The ETHERNET, A Local Area<br>Network, Data Link Layer and<br>Physical Layer Specifications | AA-K759A-TK      |

| ETHERNET Installation                                                                       | (TBS)            |

| Introduction to Local Area Networks                                                         | EB-22714-18      |

| PDP-11 Bus Handbook                                                                         | EB-17525         |

DIGITAL personnel may order hardcopy documents from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA Ø1532

Attn: Publishing and Circulation Services (NRØ3/W3) Order Processing Section

Customers may order hardcopy documents from:

Digital Equipment Corporation Accessories and Supplies Group Cotton Road Nashua, New Hampshire 03060

For information call: 1-800-257-1710

Information concerning microfiche libraries may be obtained from:

Digital Equipment Corporation Micropublishing Group (BUO/E46) 12 Crosby Drive Bedford, MA Ø173Ø

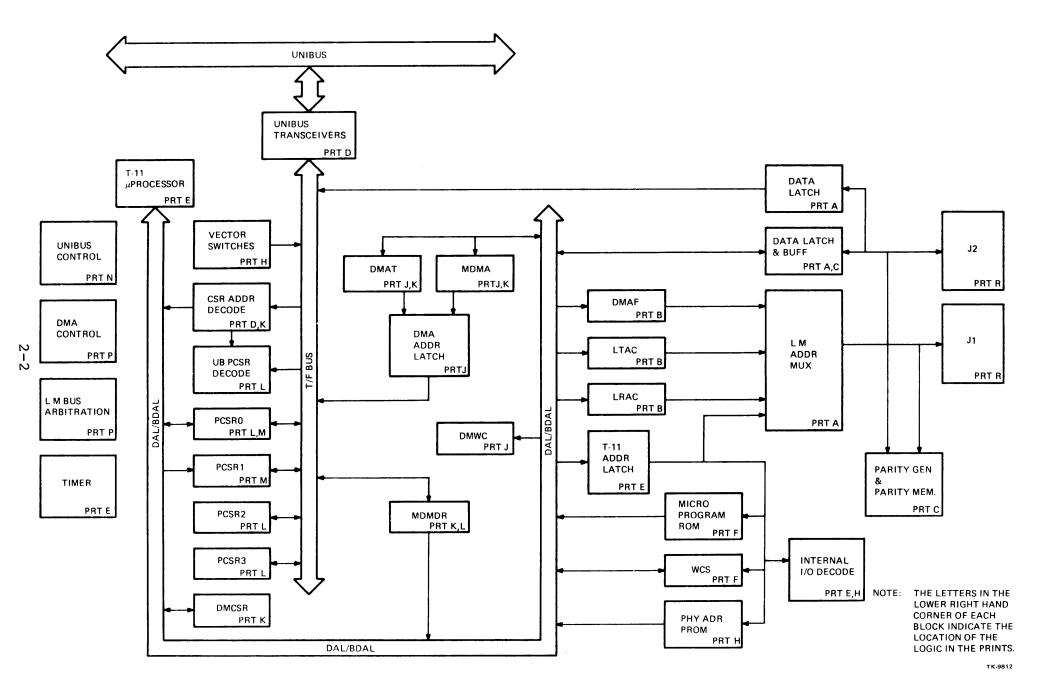

#### 2.1 OVERVIEW

The port module (M7792) is the microprocessor controlled interface between the UNIBUS bus and the link module of the DEUNA. The logic on the port module is divided into three basic functional areas.

- UNIBUS Interface -- This section contains the UNIBUS transceiver, port control and status registers (PCSRs), DMA control, UNIBUS interrupt control logic, and UNIBUS control.

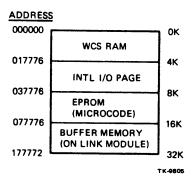

- 2. Microprocessor Section -- This section is made up of the Tll microprocessor, 8K words of ROM for microprogram storage, 4K words of writable control store (WCS), internal register address decode, and timer.

- 3. Link Memory Control -- This section contains the link memory arbitration logic, control for the 16K words of link memory and the port-to-link interconnect.

The port module is a hex-height module that is installed in a small peripheral controller (SPC) slot of a UNIBUS backplane.

A functional block diagram of the port module is shown in Figure 2-1. The letters in the lower right corner of each block of the diagram indicate the page in the engineering drawings where the logic for that block is located.

Figure 2-1 PORT Module Functional Block Diagram

#### 2.2 UNIBUS INTERFACE

The UNIBUS interface logic on the port module is used to control the transfer of data between the host processor and the DEUNA. This logic generates the signals required of a bus master and bus slave on the UNIBUS. The DEUNA functions as bus master when data is to be transferred to or from the host processors memory via direct memory access (DMA). The DEUNA performs DMAs for the transfer of:

- Data received from the ETHERNET and

- Data to be transmitted on the ETHERNET.

The DEUNA functions as a bus slave when the host processor accesses the port control and status registers (PCSRs) for the transfer of control and status information.

#### NOTE

For a detailed explanation of UNIBUS architecture and protocol, refer to the PDP-11 Bus Handbook (EB-17525).

The port also controls the UNIBUS ACLO signal. It does this by setting a bit in the link mode register on the link module (see Section 3.3.2). This is used to get control of the host processor during a down-line load.

#### 2.2.1 DMA Control

The DMA control logic is divided into two sections:

- RX DMA -- Used when a message has been received from the ETHERNET and is ready to be transferred to the host processors memory.

- 2. Tll UNIBUS DMA -- Used when the Tll has to:

- Read the ring structures in host memory,

- Read data buffers in host memory for transmission on the ETHERNET, and

- Write status information into the data buffers in host memory when the transmission is finished.

The control of each of these processes is implemented via programmed array logic (PAL) with the Tll UNIBUS DMA having a higher priority than the RX DMA process. This priority is established because the Tll UNIBUS DMA process transfers its data in smaller segments and therefore does not use the UNIBUS for long periods of time. This results in little effect on the RX DMA process and helps to maximize thoughput.

A description of each of the PALs used in the DMA control is contained in the engineering drawings for the DEUNA.

2.2.1.1 RX DMA -- The DEUNA transfers received messages to host memory via the UNIBUS using DMAs. This is done asynchronous to the process or processes going on in the DEUNA. The port microprocessor (Tll) starts the DMA transfers by loading a group of registers with the necessary address and word count information. Once this information is loaded, the Tll starts the DMA process by setting a bit in the DMA control and status register (DMCSR). This starts the DMA transfers under the control of the RX DMA PAL and the UNIBUS control logic.

The following registers, located on the port module, are used for the RX DMA process:

- DMCSR -- DMA control and status register,

- DMAT -- DMA-to-address register,

- DMAF -- DMA-from-address register, and

- DMWC -- DMA word count register.

The Tll controls the transfer of data from the buffers located on the link module to the host memory in the following manner:

- 1. The Tll loads the DMAT, DMAF, and the DMWC with the proper information.

- 2. The Tll sets the DMA GO bit in the DMCSR.

- The DMA logic takes over and moves the data via NPRs to the host memory.

- 4. When all the data is transferred or when the RX DMA logic receives an error, it interrupts the Tll.

The RX DMA logic only transfers words on the UNIBUS. The host software is responsible for throwing away the extra byte when transferring an odd byte buffer.

A description and layout of each of the registers used is given in the following sections.

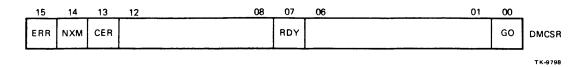

2.2.1.1.1 DMA Control and Status Register (DMCSR) -- The DMCSR is used by the Tll to enable the DMA logic and to report DMA status to the Tll. Figure 2-2 shows the DMCSR bit format and Table 2-1 gives a description of each of the bits.

Figure 2-2 DMCSR Bit Format

Table 2-1 DMCSR Bit Descriptions

| Bit       | Field | Description                                                                                                                                                                    |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMCSR<00> | GO    | Go Bit This bit is set after the address and word count are loaded. On setting the DMA, the engine begins to arbitrate for the UNIBUS and starts data transfer to host memory. |

| DMCSR<07> | RDY   | Ready Bit This bit creates an interrupt to the Tll to indicate that the word count has expired and the current DMA process is complete.                                        |

| DMCSR<13> | CER   | Collision Error When set indicates that the heartbeat from the H4000 or similar transceiver was not detected.                                                                  |

| DMCSR<14> | N XM  | Non-Existent Memory When set causes the DMA logic to interrupt the Tll. Indicates a UNIBUS timeout to the address contained in the DMA-to-address register.                    |

| DMCSR<15> | ERR   | DMA Logic Error Set when UPE or NXM are set.                                                                                                                                   |

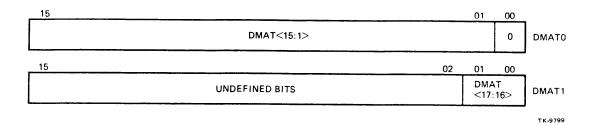

2.2.1.1.2 DMA to Address Registers (DMATØ and DMAT1) -- The DMAT registers are loaded by the Tll with the starting address of the receive buffer in host memory. DMATØ contains the lower 16 bits of the address. DMATI contains the upper 2 bits of the address. These registers are a 17-bit counter that is incremented by two after each NPR cycle.

#### NOTE

Bit Ø of DMATØ is always a Ø. This is because the RX DMA logic only performs word transfers.

Figure 2-3 shows the format of each of the registers.

Figure 2-3 DMAT Bit Format

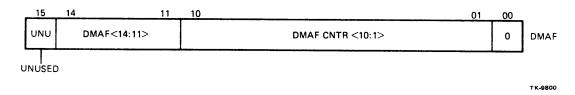

2.2.1.1.3 DMA-from-Address Register (DMAF) -- The DMAF register contains the receive buffer address in the link memory from which data is to be transferred. It is made up of a register for the upper four bits and a counter for the lower ten bits. The Tll loads the upper four bits from the link completed buffer address FIFO (refer to Section 2.4.3 for an explanation of the LCBAF). When the upper four bits are loaded, the lower ten bits are cleared. The counter is incremented by two after each NPR cycle. The address cannot overflow into the next buffer. Figure 2-4 shows the bit format of the DMAF register.

Figure 2-4 DMAF Bit Format and Descriptions

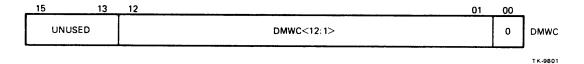

2.2.1.1.4 DMA Word Count Register (DMWC) -- The DMWC is loaded by the Tll with the number of words to be transferred to host memory by the DMA logic. The DMWC is implemented in a counter. After each NPR cycle it is decremented by two. When the register goes to zero, the DMA GO bit in the DMCSR is cleared thereby stopping the DMA logic. The RDY bit in the DMCSR is set causing an interrupt to the Tll. Figure 2-5 shows the bit format of the DMWC register.

Figure 2-5 DMWC Register Bit Format and Bit Descriptions

- 2.2.1.2 Tll UNIBUS DMA -- The Tll UNIBUS DMA is used by the port microprocessor to access the host memory in order to perform the following functions:

- Read ring structure data,

- Read data buffers from host memory for transmission by the link, and

- Write status information to data buffers upon completion of transmission.

A Tll UNIBUS DMA transactions occurs in the following sequence:

- 1. The Tll loads the UNIBUS address registers, MDMAØ and MDMA1.

- The Tll either reads or writes the microprocessor DMA data register. (MDMDRØ incrementing or MDMDR1 decrementing. Refer to Section 2.2.3.1.)

- 3. The reading or writing of the data register causes the microprocessor DMA to acquire the UNIBUS and transfer the data to/from host memory. During the DMA process, the Tll is stalled until the transfer is complete.

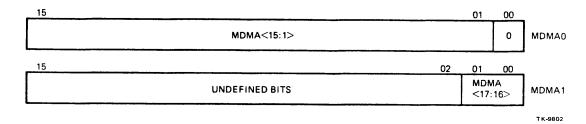

- 2.2.1.2.1 Microprocessor DMA Address Registers (MDMAØ and MDMA1) The micoprocessor DMA address registers are made up of a 17-bit counter that contains the address in host memory to or from which the data is to be transferred. MDMAØ contains the lower 16 bits of the address and MDMAl contains the upper 2 bits of the address.

#### NOTE

Bit Ø of MDMAØ is always a Ø because the DMA logic only performs word transfers.

Figure 2-6 shows the Microprocessor DMA Address Register Bit Format.

Figure 2-6 Microprocessor DMA Address Register Bit Format and Description

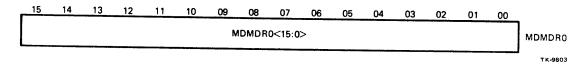

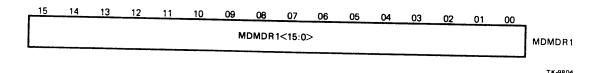

2.2.1.2.2 Microprocessor DMA Data Registers (MDMDRØ and MDMDR1) — The microprocessor DMA data registers are used as data ports for the data that is transferred to/from host memory. If the Tll reads/writes the first register, MDMDRØ, the address contained in MDMAØ and MDMAl is incremented by two. If the Tll reads/writes the second register, MDMDRl, the address contained in MDMAØ and MDMAl is decremented by two. This allows the Tll to do multiple transfers without loading the host memory address for each transfer. The reading or writing of MDMDRØ or MDMDRl by the Tll generates an NPR request to the UNIBUS. Refer to Figures 2-7 and 2-8 for MDMDRØ and MDMDRl bit formats.

Figure 2-7 Data Register MDMDRØ (Incrementing)

Figure 2-8 Microprocessor DMA Data Register MDMDR1

## 2.2.2 Port Control and Status Registers

The port control and status registers (PCSR) are used by the port module to receive commands from the host processor and report the results of the command along with other status information (interrupts, etc.).

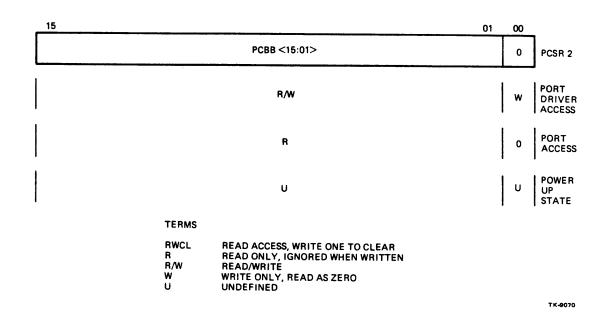

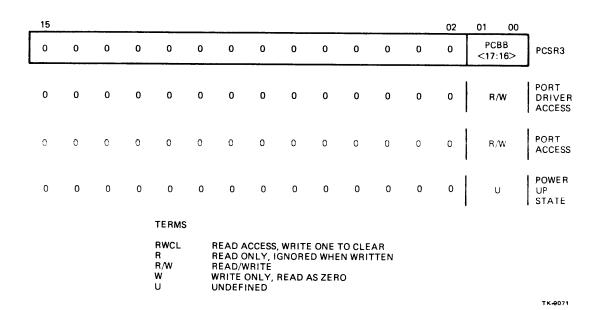

There are four PCSRs, each with a specific function. The following sections show the format of the PCSRs and give a description of their function.

For a more detailed explanation of functions performed by the PCSRs, refer to Chapter 4, "Programming", of the <u>DEUNA User's</u> Guide (EK-DEUNA-UG).

2.2.2.1 Port Control and Status Register  $\emptyset$  (PCSR $\emptyset$ ) -- Figure 2-9 shows the format of PCSR $\emptyset$  and Table 2-2 lists the functions of the bits.

| 15                                                                                                                                                          | 14   | 13   | 12   | 11   | 10   | 09 | 08   | 07   | 06   | 05   | 04 | 03  | (         | 00                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|----|------|------|------|------|----|-----|-----------|--------------------------|

| SERI                                                                                                                                                        | PCEI | RXI  | TXI  | DNI  | RCBI | 0  | USCI | INTR | INTE | RSET | 0  | POR | T_COMMAND | PCSR0                    |

| RWCL                                                                                                                                                        | RWCL | RWCL | RWCL | RWCL | RWCL | 0  | RWCL | R    | R/W  | w    | 0  |     | R/W       | PORT<br>DRIVER<br>ACCESS |

| w                                                                                                                                                           | w    | w    | w    | w    | w    | 0  | w    | w    | R    | R    | 0  |     | R         | PORT<br>ACCESS           |

| 0                                                                                                                                                           | 0    | 0    | 0    | 0    | 0    | 0  | 0    | 0    | 0    | 0    | 0  |     | U         | POWER<br>UP<br>STATE     |

| TERMS  RWCL READ ACCESS, WRITE ONE TO CLEAR R/CL READ ACCESS, CLEAR R READ ONLY, IGNORED WHEN WRITTEN R/W READ/WRITE W WRITE ONLY, READ AS ZERO U UNDEFINED |      |      |      |      |      |    |      |      |      |      |    |     |           |                          |

|                                                                                                                                                             |      |      |      |      |      |    |      |      |      |      |    |     |           | TK-9068                  |

Figure 2-9 PCSRØ Format

Table 2-2 PCSRØ Bit Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                          |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15> | SERI | Status Error Interrupt Indicates the presence of an error condition flagged in status register accessible by the port command function. Set by the DEUNA, cleared by the port-driver through the read and clear status port function.                                                                                                |

| <14> | PCEI | Port Command Error Interrupt Indicates the occurrence of either a function error or a UNIBUS timeout during the execution of a port command. Bit 7 of PCSRl distinguishes between the two error conditions. Set by the DEUNA, cleared by the port-driver.                                                                            |

| <13> | RXI  | Receive Ring Interrupt Attention bit for ring updates. Set the by the DEUNA cleared by the port-driver. Indicates, when set, that the DEUNA has placed a message(s) on the ring.                                                                                                                                                     |

| <12> | TXI  | Transmit Ring Interrupt Attention bit for ring updates. Set by the DEUNA, cleared by the port-driver. Indicates, when set, that transmission has been suspended. All messages it found on the transmit ring have been set, or an error was encountered during a transmission.                                                        |

| <11> | DNI  | Done Interrupt Interrupts when the DEUNA completes a port command. (Note: the port command NO-OP does not cause the DNI bit to set.) Set by the DEUNA, cleared by the port-driver.                                                                                                                                                   |

| <10> | RCBI | Receive Buffer Unavailable Interrupt Interrupts when the DEUNA discards an incoming message due to receive ring buffers being unavailable. Once set by the DEUNA, RCBI is not set again until after the DEUNA has received a PDMD port command and has discarded a subsequent message. Set by the DEUNA, cleared by the port-driver. |

| <09> | zero |                                                                                                                                                                                                                                                                                                                                      |

Table 2-2 PCSRØ Bit Descriptions (Cont)

| Bits | Name | Description                                                                                                                                                                                                                           |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <08> | USCI | Unsolicited State Change Interrupt Interrupts when the DEUNA performs the following actions:                                                                                                                                          |

|      |      | Fatal Error A transition into the NI and UNIBUS halted state from the ready, running, UNIBUS halted, or NI halted states. This state change is caused by the DEUNA detecting an internal fatal error, that is, internal parity error. |

|      |      | Communication Processor Boot A transition into the primary load state caused by the reception of a remote boot request of the communication processor (DEUNA microcode).                                                              |

|      |      | Communication Processor Boot A transition into the ready state from the primary load state following the reception of the memory load with transfer address message, as part of a remote boot request.                                |

|      |      | The three conditions are distinguished by examining the state field of PCSR1. Set by the DEUNA, cleared by the port-driver.                                                                                                           |

| <07> | INTR | Interrupt Summary The logical OR of PCSRØ <15:08>. Set by the DEUNA.                                                                                                                                                                  |

| <06> | INTE | Interrupt Enable Set or cleared by the port-driver, unchanged by the DEUNA.                                                                                                                                                           |

#### NOTE

In order to overcome synchronization problems with the port command field when writing the INTE bit, the DEUNA hardware locks the port command field during write accesses that change the INTE bit from a one to a zero or change the INTE bit from a zero to a one. Issuing the DEUNA, a port command, and changing the state of the INTE bit must occur in two different write accesses.

Table 2-2 PCSRØ Bit Descriptions (Cont)

| Bits    | Name         | Description                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <05>    | RSET         | DEUNA Reset Clears the DEUNA and returns it to the power up state when written with a one byte port-driver. This bit is write-only. After a successful reset, PCSRØ <11> (DNI) = 1 and PCSRØ <07> (INTR) = 1. |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| <04>    | zero         |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| <03:00> | PORT_COMMAND |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|         | 0000         | NO-OP                                                                                                                                                                                                         | No operation                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|         | 0001         | GET PCBB                                                                                                                                                                                                      | Instructs the DEUNA to fetch the address of the port control block from PCSRs 2 and 3. The DEUNA accesses PCSRs over the UNIBUS conductor, and retains a copy of the address internally. If the address of the port control block is changed, this command must be repeated to inform the DEUNA. |  |  |  |  |  |  |

|         | 0010         | GET CMD                                                                                                                                                                                                       | Instructs the DEUNA to fetch and execute a command found in the first word of the port control block. The address of the port control block was obtained through the get PCBB command.                                                                                                           |  |  |  |  |  |  |

|         | 0011         | SELF TEST                                                                                                                                                                                                     | Instructs the DEUNA to enter the reset state and execute self-test.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         | Ø 1 Ø Ø      | START                                                                                                                                                                                                         | Enables transmission and reception of frames from the port-driver. This command is ignored by the DEUNA if it is in the running state. Clears any current buffer status that                                                                                                                     |  |  |  |  |  |  |

Table 2-2 PCSRØ Bit Descriptions (Cont)

| Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Name    | Description |                                                                                                                                                                     |