# **DEC TRNcontroller 100**

# Hardware Description and Debugging

Order Number: EK-DEQRA-TM-001

December 1991

This guide describes the DEC<sup>TM</sup> TRNcontroller 100 Q-Bus-to-Token Ring Adapter (DEQRA), its architecture, and how it works in Digital systems. It also describes the on-line debugging tool, ODT68, for the DEC TRNcontroller 100.

Revision/Update Information: This is a new guide.

Operating System/Version: VMS V5.4

#### December 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated correpanies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

© Digital Equipment Corporation 1991.

All Kights Reserved

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation: DEC, MicroVAX, PATHWORKS, PCSA, VAX, VMS, and the Digital logo.

The following are third-party trademarks: Motorola is a registered trademark of Motorola, Inc. PAL is a trademark of Monolithic Memories Inc. TMS380C16 and BULS (software) are trademarks of Texas Instruments. Z-BUS is a trademark of Zilog Inc.

This guide was produced by Telecommunications and Networks Publications.

# **Contents**

| Pr | eface . |                                      | ix   |

|----|---------|--------------------------------------|------|

| 1  | Produc  | ct Overview                          |      |

|    | 1.1     | Purpose of DEQRA                     | 1-1  |

|    | 1.2     | DEQRA Applications                   | 1-2  |

| 2  | Syster  | n Operations                         |      |

|    | 2.1     | DEQRA Architecture Overview          | 2-1  |

|    | 2.2     | General Operation                    | 2-2  |

|    | 2.2.1   | Start-up                             | 2-3  |

|    | 2.2.2   | Normal Operation                     | 2-3  |

|    | 2.2.3   | Reset                                | 2-3  |

|    | 2.3     | Operation in Application Environment | 2-4  |

|    | 2.3.1   | Host Performance                     | 2-5  |

|    | 2.3.2   | Communications Traffic               | 2–5  |

| 3  | Hardw   | are Description                      |      |

|    | 3.1     | Architecture                         | 3-1  |

|    | 3.1.1   | Dual-Bus Architecture                | 3-3  |

|    | 3.1.2   | Concurrency                          | 3-5  |

|    | 3.1.3   | Host Interface                       | 3–5  |

|    | 3.2     | Memory Map                           | 3-5  |

|    | 3.2.1   | Nonvolatile Memory Space             | 3–7  |

|    | 3.2.2   | Peripheral Space                     | 3–8  |

|    | 3.2.3   | Volatile Memory Space                | 3-8  |

|    | 3.2.4   | Z-BUS Space                          | 38   |

|    | 3.3     | Processor Bus                        | 3-9  |

|    | 3.3.1   | Microprocessor                       | 3–9  |

|    | 3.3.2   | Processor Bus Operation              | 39   |

|    | 3.3.3   | Memory                               | 3-12 |

|    |         | -                                    |      |

| 3.3.4   | EPROM                                 | 3-12         |

|---------|---------------------------------------|--------------|

| 3.3.4.1 | Diagnostics                           | 3–12         |

| 3.3.4.2 | Downloader                            | 3–12         |

| 3.3.4.3 | ODT68 Debugging Tool                  | 3–13         |

| 3.3.5   | Multifunction Peripheral              | 3–13         |

| 3.3.5.1 | Console                               | 3–13         |

| 3.3.5.2 | Timers                                | 3-14         |

| 3.3.5.3 | General Purpose Port                  | 3-15         |

| 3.3.6   | Registers                             | 3-16         |

| 3.3.6.1 | LED Register                          | 3-17         |

| 3.3.6.2 | Board Configuration Register          | 3–17         |

| 3.4     | Communications Bus                    | 3-19         |

| 3.4.1   | Z-BUS Operation                       | 3-19         |

| 3.4.2   | Token Ring Communications Processor   | 3-21         |

| 3.4.3   | Shared Memory                         | 3-21         |

| 3.4.3.1 | Data Organization                     | 3-22         |

| 3.4.3.2 | Arbitration                           | 3-23         |

| 3.4.3.3 | Q-bus Support                         | 3-24         |

| 3.4.3.4 | Refresh                               | 3-24         |

| 3.4.4   | Timers                                | 3-25         |

| 3.5     | Host Interface                        | 3-25         |

| 3.5.1   | Command and Status Register           | 3-27         |

| 3.5.2   | Interface Devices                     | 3-29         |

| 3.5.3   | Support Logic                         | 3-29         |

| 3.6     | Shared Memory Base Address Selection  | 3-29         |

| 3.7     | CSR Address Selection                 | 3-30         |

| 3.8     | Interrupt Vector Address Selection    | 3~30         |

| 3.9     | Shared Memory Jumper (JP1)            | 3–30         |

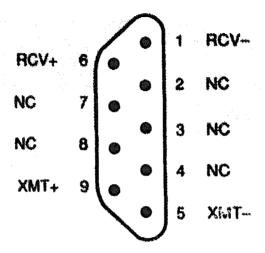

| 3.10    | Token Ring Interface                  | 3–30         |

| 3.10.1  | TMS380C16                             | 3-32         |

| 3.10.2  | TMS380C16 Reset Operation             | 3–32         |

| 3.10.3  | Bus Timing Circuitry                  | 3–33         |

| 3.10.4  | Token Ring Memory                     | 3-33         |

| 3.10.5  | Ring Interface Module                 | 3 <b>–33</b> |

| 3.11    | Host-to-Board-to-Token Ring Transfers | 3-33         |

| 3.12    | Details of Operation                  | 3-34         |

| 3.12.1  | Interrupts                            | 3-34         |

| 3.12.1. | 1 Interrupt Structure                 | 3-34         |

| 3.12.1. | 2 Interrupt Levels                    | 3~35         |

| 3.12.2  | Timing                                | 3-36         |

| 3.12.2  | .1 Clock Generation                   | 3-37         |

| 3.12.2  | .2 Transaction Timing                 | 3-38         |

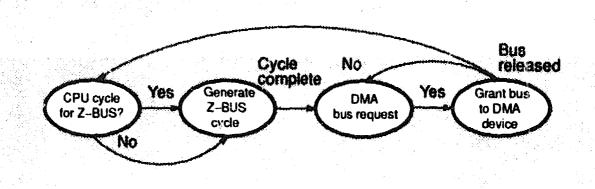

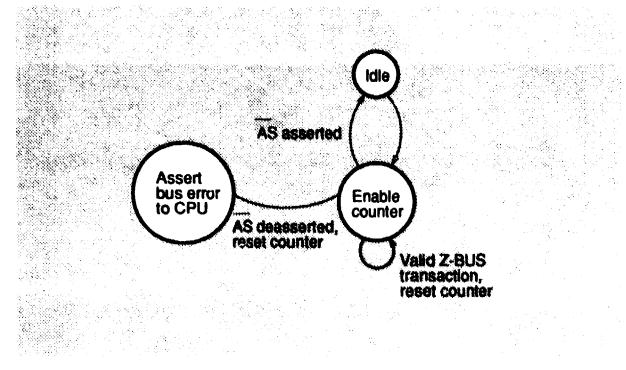

|   | 3.12.3 Z-BUS Arbitration 3.12.3.1 Z-Conversion State Machine 3.12.3.2 Arbitration State Machine 3.12.4 Reset 3.12.5 Bus Error 3.12.5.1 Bus Exception Controller Operation 3.12.5.2 Delayed Z-BUS Transactions 3.12.6 Non-Maskable Interrupt | 3-39<br>3-41<br>3-41<br>3-42<br>3-42<br>3-42<br>3-43<br>3-44                   |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 4 | Electrical Interfaces on the DEQRA                                                                                                                                                                                                          |                                                                                |

|   | 4.1 Token Ring Port                                                                                                                                                                                                                         | 4-1<br>4-2                                                                     |

| 5 | Using the ODT68 Debugging Tool                                                                                                                                                                                                              |                                                                                |

|   | 5.1 Description of the ODT68 5.2 Required Equipment 5.3 Console and Terminal Installation 5.4 Accessing ODT68 5.5 Overview of ODT68 Command Processing  EXIT  HEL?  RECALL                                                                  | 5-1<br>5-2<br>5-2<br>5-3<br>5-6<br>5-7<br>5-8                                  |

| 6 | Using the ODT68 Debug Command Set                                                                                                                                                                                                           |                                                                                |

|   | 6.1 Introduction ASCII AUX BREAKPT DISA DUMP FILL GOTO OFFSET PEEK POKE REGS                                                                                                                                                                | 6-1<br>6-3<br>6-4<br>6-5<br>6-7<br>6-9<br>6-10<br>6-11<br>6-12<br>6-13<br>6-14 |

|   | SEARCH                                                                                                                                                                                                                                      | 6–18                                                                           |

|   | TRACE                                              | 6-19 |

|---|----------------------------------------------------|------|

|   | TTB                                                | 6-20 |

|   | DIAGS                                              | 6–21 |

| 7 | Using the ODT68 Auxiliary Command Subset           |      |

|   | BIA                                                | 7-2  |

|   | ENABLE                                             | 7-3  |

|   | INHIBIT                                            | 7-4  |

|   | SD                                                 | 7-5  |

| 8 | Using the ODT68 Execute Diagnostics Command Subset |      |

|   | CIO                                                | 8-3  |

|   | INT                                                | 8-5  |

|   | LOOP                                               | 8-7  |

|   | MEMTEST                                            | 8-8  |

|   | TMS                                                | 8-10 |

|   | TRM                                                | 8-13 |

|   | XBUSER                                             | ರ−15 |

|   | XEPROM                                             | 8-17 |

|   | XMFP                                               | 8-19 |

|   | XRAM and XZRAM                                     | 8-21 |

| A | PEEK and POKE Command Edit Functions               |      |

| B | Register Names                                     |      |

|   | negister names                                     |      |

- C Sample Power-Up Display

- D LOOP Command Display

# Glossary

# Index

| Fi | Q! | 1 | 6 | S |

|----|----|---|---|---|

|    | _  | _ | _ | _ |

| 1-1  | ISO OS1 Keference Model                           | 1-3  |

|------|---------------------------------------------------|------|

| 2-1  | DEQRA Architecture Overview                       | 2-2  |

| 2-2  | Typical DEQRA Operating Environment               | 2-4  |

| 3–1  | DEQRA PC Board Layout                             | 3-2  |

| 3-2  | DEQRA Architecture Block Diagram                  | 3-4  |

| 3–3  | Detailed Processor Bus Memory Map                 | 3-6  |

| 3–4  | Detailed Z-BUS Memory Map                         | 3-7  |

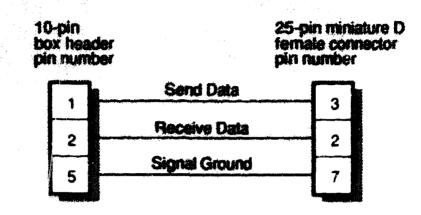

| 3-5  | Console Cable for Use with an EIA-232 Terminal    | 3-14 |

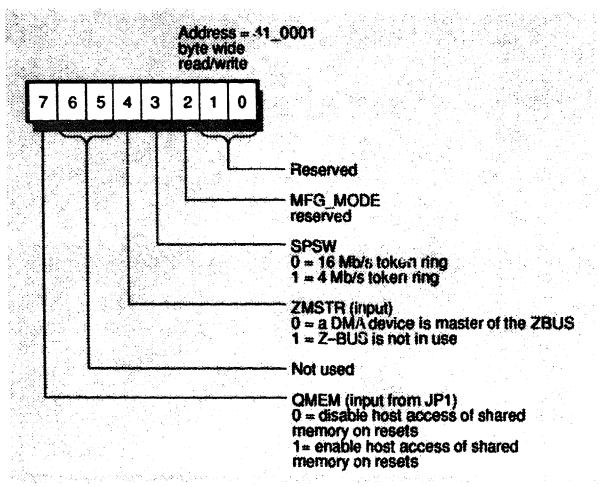

| 3-6  | MFP General Purpose Port                          | 3-16 |

| 3-7  | LED Register                                      | 3-17 |

| 3-8  | Board Configuration Register                      | 3-18 |

| 3–9  | Shared Memory Block Diagram                       | 3-22 |

| 3-10 | Data Organization                                 | 3-23 |

| 3-11 | Host Interface Block Diagram                      | 3-26 |

| 3-12 | Command and Status Register                       | 3-28 |

| 3-13 | Token Ring Circuitry Block Diagram                | 3-31 |

| 3-14 | Interrupt Priority Structure                      | 3–36 |

| 3-15 | DEQRA System Timing                               | 3-38 |

| 3–16 | DEQRA Transaction Timing                          | 3-39 |

| 3-17 | Z-BUS Arbitration Block Diagram                   | 3-40 |

| 3–18 | Z-BUS Arbitration State Diagram                   | 3-41 |

| 3-19 | Bus Exception State Diagram                       | 3-43 |

| 4-1  | Pin Assignments for the Token Ring Port Connector | 4-3  |

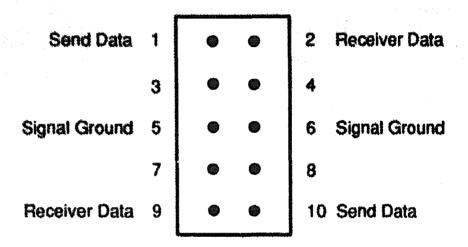

| 4-2  | Pin Assignments for the Console Port Connector    | 4-   |

## Tables

| 1   | Document Conventions                       | Xi   |

|-----|--------------------------------------------|------|

| 1-1 | DEGRA Hardware Features and Benefits       | 1-2  |

| 3-1 | Processor Bus Signal Description           | 3-10 |

| 3-2 | Device Parameters                          | 3-11 |

| 3-3 | Functions of the Prescaler/Counter Timers  | 3-14 |

| 3-4 | Functions of the General Purpose I/O Lines | 3-15 |

| 3-5 | NO_QMEM and INITDIS Bits                   | 3-18 |

| 36  | Z-BUS Signal Description                   | 3-19 |

| 3–7 | TMS380C16 Register Addresses               | 3-32 |

| 4-1 | Console Cable Pin Assignment               | 4-3  |

| 5–1 | Keyboard Functions for ODT68               | 5-3  |

| 6-1 | Summary of Debug Commands                  | 6-2  |

| 7-1 | Auxiliary Command Subset                   | 7~1  |

| 8-1 | Diagnostics Command Subset                 | 8-2  |

| A-1 | PEEK and POKE Command Edit Functions       | A-1  |

| B-1 | DEQRA Registers                            | B1   |

# **Preface**

## Purpose of this Guide

This guide describes the DEC<sup>TM</sup> TRNcontroller 100 Q-Bus-to-Token Ring Adapter (DEQRA) communications controller, its architecture, and how it works in Digital systems. The DEQRA front-end processor belongs to the DEQRA series of products that includes the M7533-AB controller. The information in this guide supplements the basic information that appears in the DEC TRNcontroller 100 Hardware Installation guide.

This guide also describes the DEQRA on-line debugging tool, ODT68.

This guide may aid DEC TRNcontroller 100 programmers in debugging their Digital host-based application software.

## **Intended Audience**

This guide is intended for maintenance technicians, computer system integrators, and software developers who need detailed information about the operating theory and features of the DEQRA hardware.

## **Organization of Document**

If you are not familiar with front-end communications processors read Chapter 1 and 2. If you are familiar with front-end communications processors, you may want to skip these overviews ar 1 go directly to the DEQRA detailed technical descriptions in Chapter 3.

This guide contains the following chapters and appendixes:

Chapter 1

**Product Overview**

Provides a functional overview of the DEQRA.

Chapter 2 System Operations

Describes the DEQRA hardware and its operation in a host system.

Chapter 3 Hardware Description

Describes the DEQRA hardware architecture, memory map, buses,

and design.

Chapter 4 Electrical Interfaces on the DEQRA

Describes the primary (token ring port) and secondary (console port)

electrical interfaces on the DEQRA.

Chapter 5 Using the ODT68 Debugging Tool

Provides basic information needed to run the ODT68 debugging tool.

Also described, is how to attach a terminal to the DEQRA to run

diagnostics routines.

Chapter 6 Using the ODT68 Debug Command Set

Explains how to use the ODT68 debugging command set.

Chapter 7 Using the ODI68 Auxiliary Command Subset

Explains how to use the ODT68 debugging auxiliary command

subset.

Chapter 8 Using the ODT68 Execute Diagnostics Command Subset

Explains how to use the ODT68 diagnostic command set.

Appendix A PEEK and POKE Command Edit Functions

Lists the PEEK and POKE command edit characters and a

description of each.

Appendix B Register Names

Lists the DEQRA registers, the ODT68 recognized abbreviation for

each register, and a description of each register.

Appendix C Sample Power-Up Display

Provides a sample console display, depicting a power-up routine.

Appendix D LOOP Command Display

Provides a sample display depicting the execution of the LOOP

command.

Glossary Provides definitions of the terms used throughout the DEQRA

document set.

### **Reference Documents**

Additional information about the DEC TRNcontroller 100 product can be found in the following documents:

- DEC TRNcontroller 100 Hardware Installation

- DEC Token Ring Network Device Driver for VMS Installation

- DEC Token Ring Network Device Driver for VMS Use and Programming

- Token Ring Access Method, IEEE STD 802.5-1989

## **Document Conventions**

Table 1, Document Conventions, lists the conventions used in this guide.

**Table 1 Document Conventions**

| Convention         | Description                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------|

| DEQRA              | The term DEQRA refers to the M7533-AB controller board.                                              |

| NOTE               | Contains information that may be of special importance to the user.                                  |

| CAUTION            | Contains information to prevent damage to software or hardware.                                      |

| Special Type       | Shows program output displayed on the console screen. Special type in examples indicates user input. |

| Return             | Indicates that you press the key labeled Return, in examples.                                        |

| CtrlZ              | Indicates that in examples you press the key labeled Ctrl and the key labeled Z, simultaneously.     |

| $\overline{AS}$    | Indicates the signal is asserted low true.                                                           |

| Communications Bus | Refers to Z-BUS and ZILOG Z8000 TM bus.                                                              |

| []                 | A brantet is used to indicate optional input.                                                        |

# **Product Overview**

The DEC TRNcontroller 100 Q-Bus-to-Token Ring Adapter (DEQRA) intelligent communications controller allows you to attach suitably configured Q-bus-based Digital Equipment Corporation VAX TM computers directly to an industry-compatible token-ring network.

The DEQRA hardware is a single-board computer that has a central processing unit, random access memory, programmable read-only memory, token-ring interface circuitry, and host-interface circuitry. The software consists of an on-board operating system, diagnostic tests, host interface drivers, and application routines.

## 1.1 Purpose of DEQRA

The main purpose of the DEQRA is to provide an intelligent link to an IEEE 802.5 compatible token ring while improving the overall computing efficiency of the host computer. To do this, low-level communications tasks that are traditionally performed by the host central processor are migrated to the DEQRA.

The DEQRA increases overall system bandwidth by distributing the I/O processing away from the host CPU. In the traditional minicomputer architecture, the host services all I/O requests. This load on the CPU has grown steadily as computer peripherals have become increasingly more powerful. Modern operating systems allow intelligent front-end processors to perform these relatively simple tasks. The result is an overall increase in system throughput.

Table 1-1 list the attributes of the DEQRA.

Table 1-1 DEQRA Hardware Features and Benefits

| Feature                                          | Benefits                                                                                           |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| Dual-bus architecture                            | 32-bit processor bus optimized for program execution.                                              |  |  |

|                                                  | 16-bit communications bus optimized for data<br>transfer and host interface.                       |  |  |

|                                                  | Concurrent operation improves performance.                                                         |  |  |

| 68020 CPU                                        | 4 Gbyte linear address space.                                                                      |  |  |

|                                                  | Allows use of familiar, powerful program development tools (assemblers, C compilers, and editors). |  |  |

|                                                  | Development can often be done on host system; separate system not required.                        |  |  |

| TMS380C16 Token Ring<br>Communications Processor | Interfaces all control signals and data transfers to token ring.                                   |  |  |

|                                                  | Protocol handler performs hardware-based protocol functions conforming to standard IEEE 802.5.     |  |  |

| Large private RAM memory                         | Provides space for applications tasks, real-time executive, and so on.                             |  |  |

|                                                  | Applications are downloaded into RAM for ease of change.                                           |  |  |

| Single-module form factor                        | Mounts easily in a standard backplane.                                                             |  |  |

## 1.2 DEQRA Applications

The DEQRA board links the token ring to Digital's Q-bus-based VAX products. At system start-up, the VAX host downloads microcode containing the communication protocols. The application software may be customer-specific or part of a Digital developed turn-key product.

Communications software systems that use the DEQRA can fit the International Standards Organization (ISO) open system interconnection seven-layer reference model for communications protocols. Figure 1–1 shows this model. The DEQRA performs the tasks described by the first two layers of the model.

Once the software download has been completed, the DEQRA hardware and software combination performs its assigned task until a board-level reset initiates another start-up sequence.

Figure 1-1 ISO OSI Reference Model

|              | Layer<br>Number | Function                                     |

|--------------|-----------------|----------------------------------------------|

| Application  | 7               | Services applications                        |

| Presentation | 6               | Code conversion, data format                 |

| Session      | 5               | Coordinates interaction between applications |

| Transport    | 4               | End-to-end data integrity                    |

| Network      | 3               | Routes information                           |

| Data Link    | 2               | Exchanges data with physical link            |

| Physical     | 1               | Transmits/receives bit stream to medium      |

|              |                 |                                              |

LKG-4878-911

# **System Operations**

This chapter contains a general description of the DEQRA hardware and its operation in host systems.

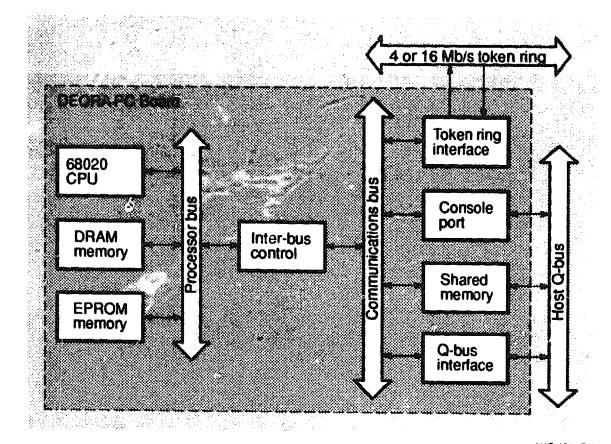

### 2.1 DEQRA Architecture Overview

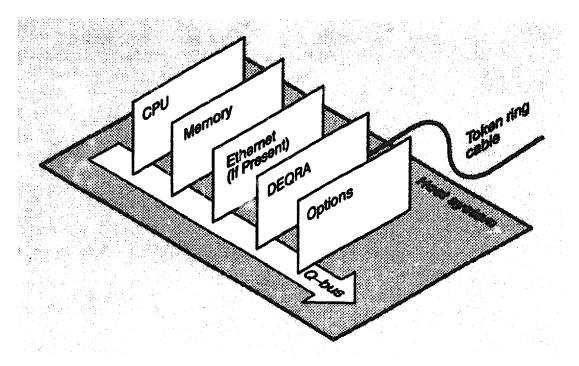

The DEQRA controller uses a dual-bus architecture as shown in Figure 2-1, to provide high-performance, front-end processing in communication environments.

The processor bus consists of a CPU, memory, and support devices. This bus processes the application program and provides computing resources as required by high-level protocols.

The communications bus (the subsidiary bus) consists of a token-ring communication processor, memory, and host-interface circuits. The communications bus moves data between the token ring and the host. The processor and communications buses are two independent buses bridged by circuitry, which isolates them during concurrent operations and translates appropriate signals to control transactions between them during inter-bus operations.

Figure 2-1 DEQRA Architecture Overview

LKG-4941-911

# 2.2 General Operation

The DEQRA operations occur in two phases:

- Start-up

- Normal

When power is initially applied to the DEQRA, its CPU begins execution at a memory address in the PROM devices. This memory address contains instructions that set up the basic working environment for the CPU.

### 2.2.1 Start-up

Start-up begins when the on-board diagnostics test all major sections of the DEQRA circuitry. Upon the successful completion of these tests, the host interface is initialized and the DEQRA loads its operating system and application-program software from the host, through the Q-bus interface circuits into the shared memory. After these have been moved into processor memory, the CPU process the downloaded software.

### 2.2.2 Normal Operation

During normal operation, the DEQRA processes all communications-related work. The software program downloaded during start-up is used to operate the general-purpose DEQRA communications hardware in the mode required by the host system. This program is typically an implementation of some special-purpose communications protocol.

The DEQRA remains in this phase of operation until a board reset command is issued either by the host software, the host-bus hardware, or the reset switch.

### **2.2.3** Reset

A hardware reset causes the DEQRA to stop processing program instructions. No attempt is made to save the current state of the CPU operation. The hardware reset causes the CPU to go back to the start-up phase.

# 2.3 Operation in Application Environment

The DEQRA hardware processes communications-related application software in a typical VAX operating environment. Figure 2-2 shows a typical DEQRA operating environment.

Figure 2-2 Typical DEQRA Operating Environment

LKG-4942-911

### 2.3.1 Host Performance

The DEQRA offloads the host, thus increasing overall VAX system performance. Traditionally, the host's CPU executes the tasks related to the operation of serial communications. These tasks can be extensive, and many require processing in real time. The DEQRA hardware, combined with application software, is capable of processing many of these protocol-dependent, low-level tasks. The application software is downloaded from the host system to the DEQRA during the system start-up phase.

### 2.3.2 Communications Traffic

When the software download is complete, communications traffic is accepted and processed for transfer to or from the host. In most applications, the data format used by the host processor is very different from the format transmitted on the token ring. Many additional structures must be added to the raw data processed by the host system in order to maintain the data's integrit, during transmission. The software programs downloaded into the DEQRA perform this task.

# **Hardware Description**

The DEQRA is an intelligent communications controller that is designed to interface Digital Equipment Corporation Q-bus-based VAX computers to an industry standard token-ring network.

This chapter describes the DEQRA architecture, memory map, buses, and design.

See Chapter 4 for the circuitry and pinout information on the electrical interfaces of the DEQRA.

### 3.1 Architecture

The DEQRA uses a dual-bus architecture to provide a high performance link.

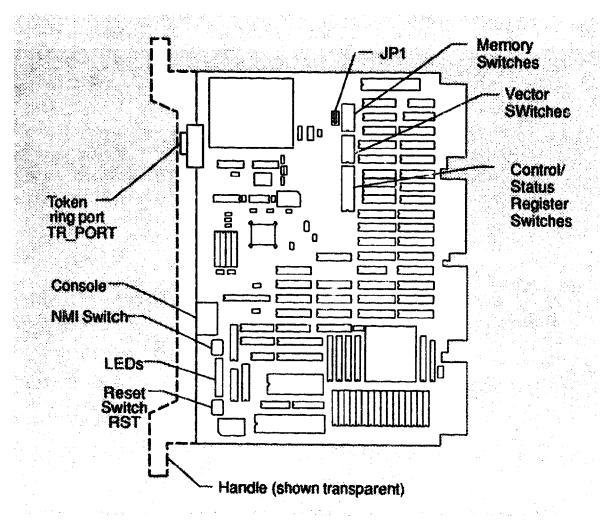

Figure 3-1 shows the physical layout of the hardware components on the DEQRA board.

Figure 3-1 DEQRA PC Board Layout

LKG-4943-91

## The following sections describe:

- Dual-bus architecture

- Concurrent operations

- Host interface

#### 3.1.1 Dual-Bus Architecture

As shown in Figure 3-2, the DEQRA uses a dual-bus architecture to enhance data-transfer rates and allow the CPU more processing time. The processing engine resides on a processor bus while the token ring circuitry resides on an isolated communications bus. Each of these buses is optimized for its primary function. The processor bus has a Motorola 68020<sup>™</sup> 32-bit processor, longwordwide memory, and a non-multiplexed bus architecture that is optimized for program execution. The communications bus is implemented as a Zilog™ multiplexed bus (Z-BUSTM) with a word-wide memory system that is optimized for DMA-controlled data movement and host-interface transfers. The 68020 CPU has access to all of the memory and devices on both buses, whereas the TMS380C16™ on the Z-BUS has access only to the Z-BUS memory.

System console Control 1MB and 68020 dynamic RAM CPU status 68901 registers MFP 512K X 32 32-bit data 32-bit address Pulse ring Ring 128KB Z-BUS conversion interface interface **EPROM** arbitration, and module isolation 64K X16 Multiplexed bus 20-bit address 10-bit data TMS380C16 TMS380C16-totoken ring Z-BUS communications conversion **Multiplexed Z-BUS** processor 2-bit address 16-bit data Multiplexed bus 20-bit address 16-bit data Z8036 **Z-BUS** CIO Memory 512KB memory (Q-bus control dynamic RAM (256K X 16) CSR) 256K X16 Multiplexed Q-bus 22-bit address 16-bit data

Figure 3-2 DEQRA Architecture Block Diagram

## 3.1.2 Concurrency

The dual-bus architecture optimizes the operational characteristics of each bus and enables the processing engine and the TMS380C16 to operate concurrently. This allows the on-board CPU to continue to execute application-level protocol programs and interrupt instruction streams on the processor bus while the TMS380C16 is moving data along the communications bus. Processing is suspended, or DMA transactions delayed, only when both the CPU and a TMS380C16 have transactions waiting for a Z-BUS device at the same time. This reduces the conflicts during normal operation and maximizes the use of each bus.

### 3.1.3 Host Interface

In most cases, the host machine is the ultimate source or destination of the data being transmitted and received. The board requires a mechanism for issuing commands, determining status, and controlling the data exchange with the host system in which it resides. The DEQRA communications bus memory, along with a command and status register, provides the host interface to the Q-bus. The communications bus memory is implemented as a shared memory that the 68020, the token ring communications processor, or a Q-bus master device on the host system can access. This optimizes data exchange between the board, the token ring, and the host. The control/status register (CSR) passes messages between the DEQRA and the host to coordinate data exchange. It is implemented as an eight-bit register in each direction. Writing to the CSR from either side can generate an interrupt on the other side. See Section 3.5 for details.

## 3.2 Memory Map

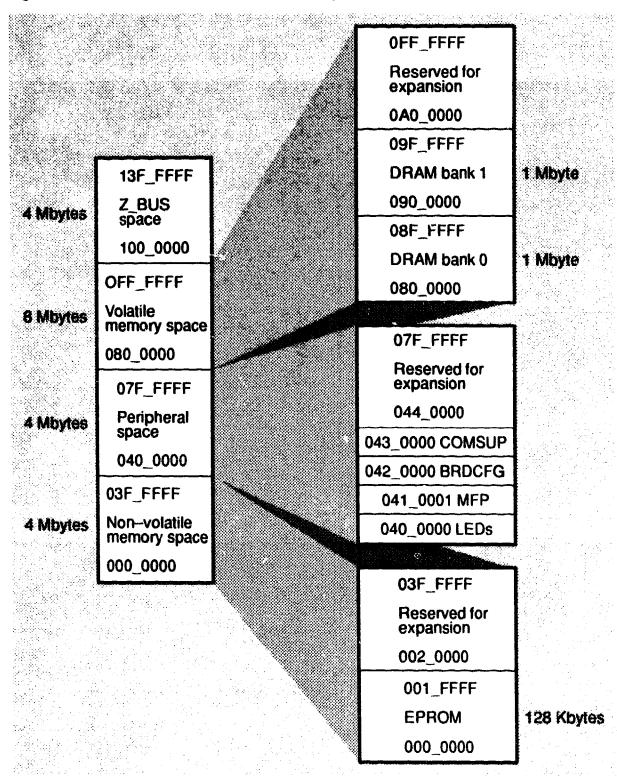

The DEQRA memory map is divided into four main memory spaces:

- Nonvolatile memory

- Peripheral

- Volatile memory

- Z-bus

Figure 3-3 shows the detailed addressing for the volatile memory space, peripheral space, and the nonvolatile memory space.

Figure 3-3 Detailed Processor Bus Memory Map

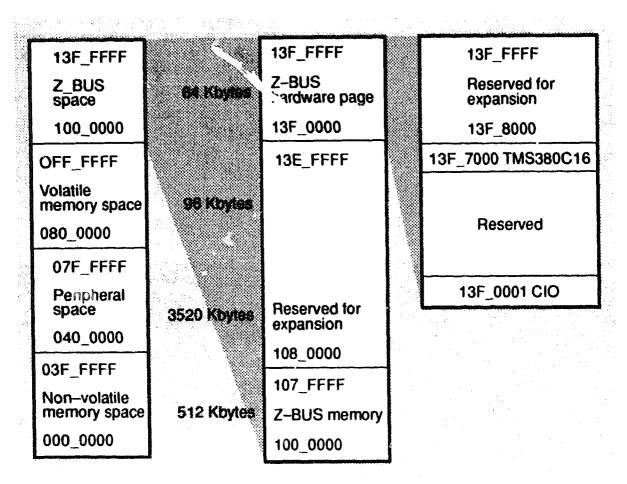

Figure 3-4 shows the detailed addressing for the Z-bus memory space.

Figure 3-4 Detailed Z-BUS Memory Map

LKC 4947-911

## 3.2.1 Nonvolatile Memory Space

The 4 Mbyte space beginning at address 000\_000016 is the nonvolatile memory space. The DEQRA EPROM occupies the lowest 128 Kbytes. The additional space is reserved for future expansion.

### 3.2.2 Peripheral Space

The 4 Mbyte space beginning at address  $040\_0000_{16}$  is the peripheral device space. To simplify the address decoding logic on the board, each peripheral device is assigned a 64 Kbyte window. The DEQRA has three devices assigned: the LED register, the multifunction peripheral device, and the board configuration register. See Section 3.3.5 and Section 3.3.6 for descriptions of these peripheral devices. The additional space is reserved for future expansion.

## 3.2.3 Volatile Memory Space

The 8 Mbyte space beginning at address  $080\_0000_{16}$  is the volatile memory space. One bank of dynamic random access memory occupies the lowest 1 Mbyte of the volatile memory space. The additional space is reserved for future expansion.

## 3.2.4 Z-BUS Space

The 4 Mbytes beginning at address  $100\_0000_{16}$  is the Z-BUS space. This space is further divided into specific address sections:

Z-BUS memory

The 512 Kbytes beginning at 100\_0000<sub>16</sub> is the Z-BUS shared memory. These Kbytes are mapped into the Q-bus memory space beginning at the address chosen by the board-selection switches.

Reserved

The 3.424 Mbytes beginning at  $108\_0000_{16}$  are reserved for future expansion.

Peripheral device

The 64 Kbytes, beginning at  $13F_0000_{16}$ , are used for Z-BUS peripheral devices. To simplify address decoding logic, each device is assigned a 16 Kbyte window. These devices are the Counter/Timer and the TMS380C16 token-ring communications processor. See Section 3.4 for descriptions of these peripheral devices. The additional space is reserved for future expansion.

### 3.3 Processor Bus

The DEQRA processor bus is composed of the CPU, EPROM, RAM, a multifunction peripheral device, control/status registers, diagnostic LEDs. and the support circuitry that is required for timing and control of the bus. Section 3.3.1 through Section 3.3.6 describe the major devices, support circuitry, bus signals, and the operation of the processor bus. For clarity, the processor description precedes the descriptions of the bus operation and other devices that connect to this bus.

## 3.3.1 Microprocessor

The DEQRA processing engine is a Motorola 68020. The 68020 address bus, data bus, and internal registers are all 32-bits wide. The microprocessor has a rich instruction set including versatile addressing modes that support high-level languages. The 68020 has a 256-byte internal instruction cache that may be disabled under program control, but is normally enabled to speed program processing. The internal operations are designed to operate in parallel using a three-stage pipeline. This allows multiple instructions to process concurrently. The processor also supports dynamic bus sizing that enables devices of different data widths to interface directly with the 68020 without data-alignment restrictions.

A partial list of microprocessor features include:

- Sixteen 32-bit general purpose registers

- Two 32-bit supervisor stack pointers, one user stack pointer

- One 32-bit program counter

- Five special control registers

- Eighteen addressing modes

- 4 Gbytes of address space

- One 256-byte instruction cache

## 3.3.2 Processor Bus Operation

The processor bus is an implementation of Motorola's 68020 bus architecture made up of address, data, control, and timing signals as shown in Table 3-1. Although the 68020 is capable of linearly addressing 4 Gbytes of address space, only the lower 25 address lines are decoded by the on-board logic. Detailed information about the memory map is found in Section 3.2.

Table 3-1 Processor Bus Signal Description

| Signal Name                 | Mnemonic         | 1/0 | Description                                                                                |

|-----------------------------|------------------|-----|--------------------------------------------------------------------------------------------|

| Address                     | A0-A31           | 0   | Indicates processor address bus                                                            |

| Address Strobe              | ĀS               | 0   | Indicates that function code, address, size, and R/W signals are valid                     |

| Bus Error                   | BERR             | I   | Indicates that the bus exception controller has timed out                                  |

| Cache Disable               | CDIS             | I   | Disables 256-byte instruction cache (used for production testing only)                     |

| Clock                       | CLK              | I   | Defines the 10 MHz CPU clock used for internal processing and timing                       |

| Data                        | D0-D31           | ľO  | Indicates processor data bus                                                               |

| Data Transfer and<br>Size   | DSACK0-DSACK1    | I   | Acknowledges data transfer<br>and size (used to end cycle and<br>indicate slave data size) |

| External Cycle<br>Start     | ECS              | o   | Indicates cycle is about to begin                                                          |

| Function Codes              | FC0-FC2          | 0   | Indicates processor state and address space identifiers                                    |

| Halt                        | HALT             | 0   | Indicates a double bus fault has occurred                                                  |

| Interrupt Priority<br>Level | IPL0- IPL2       | I   | Indicates the highest level interrupt request is active                                    |

| Read/Write                  | $R/\overline{W}$ | 0   | Determines the direction of data transfer                                                  |

| Reset                       | RESET            | ľO  | Initiates an I/O Reset used to initiate board devices                                      |

| Size                        | SIZ0-SIZ1        | 0   | Indicates size of current transaction (number of bytes to be transferred)                  |

The 68020 dynamic bus-sizing feature allows devices of different widths to reside on the 32-bit data bus; it supports byte, word, three-byte, and longword data transfers on any byte boundary without requiring special data alignment. Bus sizing is accomplished as follows:

- The 68020 asserts the desired transfer size at the beginning of each transaction by encoding the SIZ0 and SIZ1 signals.

- 2. External logic returns  $\overline{DSACK}$  signals to the 68020 indicating what size transfer the addressed device can support.

- 3. The CPU uses internal byte-steering logic and multiple operations to complete the desired transaction.

As an example, when the CPU starts a longword transaction to a byte-wide device, it recognizes the byte-wide  $\overline{DSACK}$ s returned by the external logic and presents, or reads, only one byte of data. The CPU proceeds with three additional byte transactions in order to complete the longword transfer.

The DEQRA uses synchronous design techniques to decode and generate CPU control signals. State machines monitor the address bus, size codes, and function codes to generate  $\overline{DSACK}$  signals matching the size and timing requirements of each device. Table 3-2 shows the DEQRA devices, their widths, and  $\overline{DSACK}$  selection as decoded by programmable array logic. Automatic wait-state selection is generated for slave devices that do not provide  $\overline{DSACK}$  generation.

Table 3-2 Device Parameters

| Device/Memory Space             | Width     | DSACK             |     |

|---------------------------------|-----------|-------------------|-----|

| Processor memory                | longword  | external          | ··· |

| EPROM                           | word      | three wait states |     |

| MFP register                    | byte      | external          |     |

| LED register                    | byte      | one wait state    |     |

| Board Configuration register    | byte      | one wait state    |     |

| Communications Support register | longv ard | one wait state    |     |

| Z-BUS space                     | word      | external          |     |

### **3.3.3 Memory**

The DEQRA processor bus is available with 1 Mbyte of zero-wait-state, longword-wide (32 bits), dynamic random access memory (DRAM). It consists of one bank of 256K by 32-bit DRAM beginning at address 080\_0000<sub>16</sub>. The memory controller state machine is implemented in programmable array logic devices and provides all of the logic required for address multiplexing. read-and-write control, and refresh timing. The memory controller works in conjunction with the 68020's dynamic bus sizing to fully support byte, word, three-byte, and longword access on any byte boundary. A memory refresh cycle is executed every 15.6 µs to maintain dat a integrity.

### **3.3.4 EPROM**

The 128 Kbytes of erasable programmable read only memory, beginning at address 000\_000016, consists of a 64K by 16-bit EPROM device. The EPROM contains self-test diagnostics, a boot-loader program, and a debugging tool that includes a disassembler. For a detailed discussion of these tools, see Chapter 5 through Chapter 8.

### 3.3.4.1 Diagnostics

Self-test diagnostics begin when the board is first powered up. These tests validate the control circuitry, processor and Z-BUS memory, processor and Z-BUS peripheral devices, interrupt operation, bus error logic, EPROM checksum, and concurrent bus execution features of the DEQRA hardware. Test status and error reporting may be monitored either by viewing the LEDs or by connecting a terminal to the console port on the board edge.

Upon completion of these tests, an *inhibit diagnostics* pattern is written into memory. Succeeding hardware resets of the board cause a basic subset of the tests to execute. This prevents downloaded code and device setups from being overwritten or altered by a full reset. It also shortens the time required to download the board since the full diagnostics are not re-run for every reset. You may initiate and monitor menu-driven diagnostics testing from a console.

#### 3.3.4.2 Downloader

The CPU uses the bootloader code and the host driver to download the operating system/impact executive and applications from the host to the board. The bootloader does this by moving the executable images through the shared memory to the processor memory. The CPU begins executing the downloaded code after the download sequence has completed.

### 3.3.4.3 ODT68 Debugging Tool

The ODT68 debugging tool enables you to connect a 9,600 bits/s terminal to the console port to communicate directly with the board during programdevelopment or debugging sessions. It provides access and breakpointing throughout the entire DEQRA address space. It displays the 68020 address, data, and special registers. A disassembler is included and you can specify individual diagnostic tests for execution. See Chapter 5 for more information on the ODT68 debugging tool.

## 3.3.5 Multifunction Peripheral

Motorola's MC68901 multifunction peripheral is a byte-wide 68000 bus device that resides at address 41\_0000<sub>16</sub>. This large scale integration device provides a full-duplex asynchronous serial port, four eight-bit timers, and eight general-purpose, individually programmable, I/O lines with interrupt capabilities.

#### 3.3.5.1 Console

The DEQRA uses the MFP serial port as a console device for direct EIA-232 communications. With a 9,600 bits/s terminal connected to the console port, the results of all the diagnostic self-tests will display.

The console is also used while running the debugging tool during program development. Figure 3-5 shows the pinout for the console cable, BC29E-15.

During normal operation the console port is not used. To prevent RFI emissions the console cable should not be left plugged in.

| NOTE                                                                                             |

|--------------------------------------------------------------------------------------------------|

| To provide ESD protection for the console interface, ensure the console cover plate is in place. |

|                                                                                                  |

Figure 3-5 Console Cable for Use with an EIA-232 Terminal

KG 4879-91

#### 3.3.5.2 Timers

The four eight-bit timers are prescaler/counter timers with a common 2.5MHz clock input. Table 3-3 lists the prescaler/counter timers and their functions

Table 3-3 Functions of the Prescaler/Counter Timers

| Times | Function                                                                                                                                                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A, B  | Implement a 16-bit timer for use by the real-time operating system                                                                                                                                                        |

| C     | Used as the data-rate clock generator for the 9.600 bits/s console port                                                                                                                                                   |

| D     | Available as a general purpose timer for applications that require additional timing functions. It provides a timing resolution of 1.33 $\mu s$ , and may be used in delay, pulse-width-measurement, or event-count mode. |

#### 3.3.5.3 General Purpose Port

The eight general-purpose I/O lines may be individually operated as either inputs or outputs under software control. They may generate an interrupt on either transition direction of an input signal. Four of the eight I/O lines are currently allocated for use by the DEQRA. These I/O lines and their functions are listed in Table 3-4.

Table 3-4 Functions of the General Purpose I/O Lines

| VO Line  | Function                                                                      |

|----------|-------------------------------------------------------------------------------|

| ZMSTR    | Input signifying that the TMS380C16 is actively using the communications bus. |

| QMEM     | Input from JP1, used to set shared memory visibility at power-up.             |

| SPSW     | Input bit that sets the speed of the token ring at 4Mb/s or 16Mb/s.           |

| MFG_MODE | Reserved for manufacturing purposes.                                          |

The other four I/O lines are reserved for future use. Figure 3-6 shows the register for bit assignments.

Figure 3-6 MFP General Purpose Port

LKG-4948-911

### 3.3.6 Registers

The processor bus includes two special-purpose registers. These are the LED and the board-configuration registers. These registers are used to select operational characteristics and maintain board-level configuration parameters. Read-back registers are used to enable the data from the last write (the current value of the register) to be read back by the CPU. This eliminates the need to maintain memory-resident images of the register's contents. The CPU must

read these registers into an internal CPU register to manipulate bits, or bit fields, without affecting other bits.

#### **LED Register** 3.3.6.1

The byte-wide LED register, which resides at address 40\_000016, is a read-back register whose outputs are tied directly to the LEDs on the DEQRA board's edge. These easily viewed LEDs show status and error information during the self-test diagnostics. They may also indicate the operational status of an application program. Clearing or writing a zero to a bit position illuminates the appropriate LED. See Figure 3-7.

Figure 3-7 LED Register

Address=40 0000 Byte wide Read/Write All bits are cleared to 0 at Reset time

Write 00 hexadecimal to turn all LEDs on. Write FF hexadecimal to turn all LEDs off.

LKG-4949-91

#### 3.3.6.2 Board Configuration Register

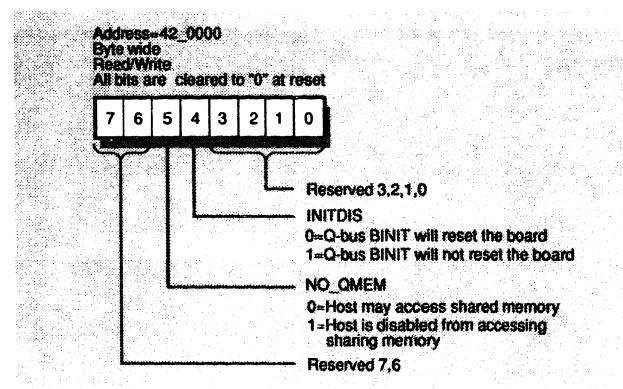

The byte-wide board configuration register residing at address 42\_000016. also a read-back register, is used to control board-level parameters such as reset options and Q-bus shared memory access enable. Figure 3-8 shows the register bit map.

Figure 3-8 Board Configuration Register

LKG-4950-91

Table 3-5 describes the NO\_QMEM and INITDIS bits.

Table 3-5 NO\_QMEM and INITDIS Bits

| Bit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO_QMEM | Some operating systems or hardware configurations have requirements concerning memory visibility at host power-up time. This bit provides a mechanism for disabling the shared memory controller from generating Q-bus memory cycles. The EPROM power-up routine uses the position of jumper JP1 to set or clear the NO_QMEM bit at power-up time. The DEC TRNcontroller 100 Hardware Installation manual describes board configuration. |

| ENITDIS | This bit provides the DEQRA with an option to ignore the Q-bus signal BINIT by disabling the reset controller state machine during BINIT sequences on the Q-bus.                                                                                                                                                                                                                                                                         |

## 3.4 Communications Bus

The DEQRA communications bus exists as a space in the CPU memory map and is composed of a token-ring communications processor, shared memory, and the support circuitry required for timing, data transfer, bus arbitration, and interrupt operations. The following sections describes the major devices, support circuitry, bus signals, and how the communications bus operates. The communications bus is implemented as a Zilog Z8000 bus and is referred to as the Z-BUS throughout these sections.

### 3.4.1 Z-BUS Operation

The Z-BUS is a multiplexed bus made up of 16 address/data lines, 6 extendedaddress lines, and 13 miscellaneous control lines. The possible bus masters on the Z-BUS are the 68020 processor or the token-ring communications processor. Table 3-6 shows the descriptions of the Z-BUS signals.

Table 3–6 Z-BUS Signal Description

| Signal Name     | Z-BUS<br>Mnemonic   | DEQRA<br>Mnemonic | Description                                                                                 |

|-----------------|---------------------|-------------------|---------------------------------------------------------------------------------------------|

| Address Strobe  | ĀS                  | ZAS               | Timing signal indicating that<br>the addresses and certain control<br>signals are valid     |

| Bus Acknowledge | BUSACK, BAI,<br>BAO | BUSACK            | Indicates that the bus arbiter has relinquished control of the bus in response to a request |

| Bus Request     | BUSREQ              | BUSREQ            | Bus requester has, or is trying to obtain, control of the bus                               |

| Byte/Word       | B/W                 | ZB/W              | Indicates whether a byte or word of data is to be transferred on the bus                    |

| Data/Address    | AD00-AD15           | BDAH00-<br>BDAH15 | Multiplexed data and low order address lines                                                |

| Data Strobe     | <del>DS</del>       | $\overline{ZDS}$  | Provides timing of data<br>movement to or from the bus<br>master                            |

<sup>1</sup> IRQCIO, IRQEGL, and IRQEXC are the three possible signals. 2 IACKCIO, IACKEGL, and IACKEXC are the three possible signals.

(continued on next page)

Table 3-6 (Cont.) Z-BUS Signal Description

| Signal Name              | Z-BUS<br>Mnemonic | DEQRA<br>Mnemonic  | Description                                                                     |

|--------------------------|-------------------|--------------------|---------------------------------------------------------------------------------|

| Extended<br>Address      | EA16-EA21         | BDAH16-<br>BDAH21  | High order address lines                                                        |

| Interrupt                | ĪNT               | $\overline{IRQ}^1$ | Shows that an interrupt request is being made                                   |

| Interrupt<br>Acknowledge | INTACK            | TACK <sup>2</sup>  | Shows that an interrupt acknowledge transaction is in progress                  |

| Interrupt<br>Enable In   | IEI               | IEI                | Interrupts daisy chain input from a higher-priority device                      |

| Interrupt<br>Enable Out  | IEO               | IEO                | Interrupts daisy chain output to a lower-priority device                        |

| Peripheral<br>Clock      | none              | PCLK               | Clock timing signal used<br>by peripherals for internal<br>processes and timing |

| Read/Write               | R/W               | $ZR/\overline{W}$  | Determines the direction of the transfer on the bus                             |

| Wait                     | WAIT              | ZW AIT             | Shows that a responding device needs more time to complete a transaction        |

<sup>1</sup> IRQCIO, IRQEGL, and IRQEXC are the three possible signals. 2 IACKCIO, IACKEGL, and IACKEXC are the three possible signals.

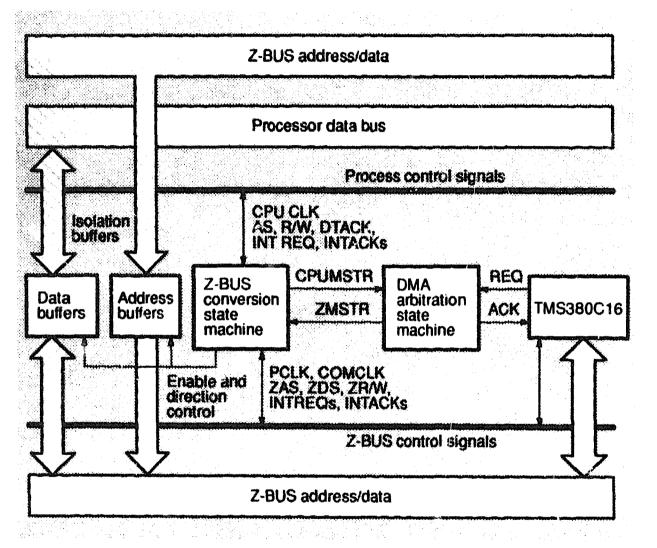

An arbitration controller monitors the individual request lines and grants the bus to a requesting device when possible. CPU read, write, and interrupt transactions in the Z-BUS space require a Z-BUS conversion state machine to control address and data buffers for bus multiplexing, and to generate (using the Motorola signals) control signals that conform to the Z-BUS specification. This state machine also controls bus isolation to enable concurrent operation of the Z-BUS and the processor bus.

After the power-up test diagnostics have executed and the download sequence is completed, the Z-BUS becomes idle and starts to execute the arbitration scheme. Section 3.4.3.2 describes the arbitration.

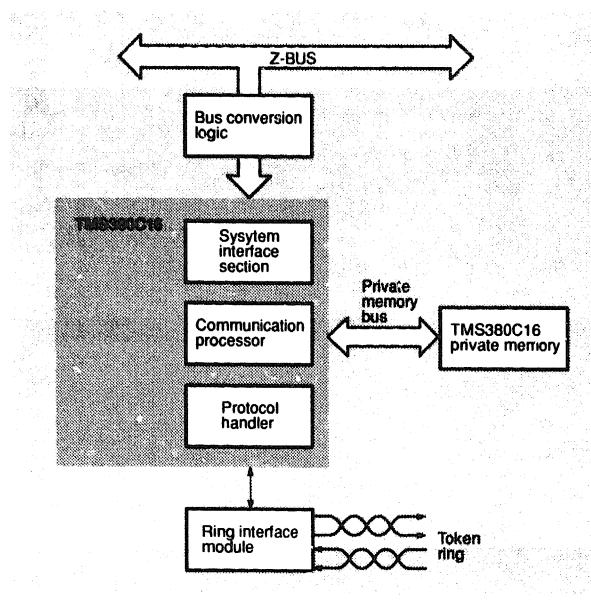

### 3.4.2 Token Ring Communications Processor

The TMS380C16, Texas Instruments' token-ring communications processor. is the interface between the communications bus and the token ring. The TMS380C16 handles all data transfers and control signals between the board and the token ring. Since it was designed to reside on a 68000 bus, the TMS380C16 requires some interface circuitry to make it part of the Z-BUS. For a detailed description of the TMS380C16, see Section 3.16.1.

### 3.4.3 Shared Memory

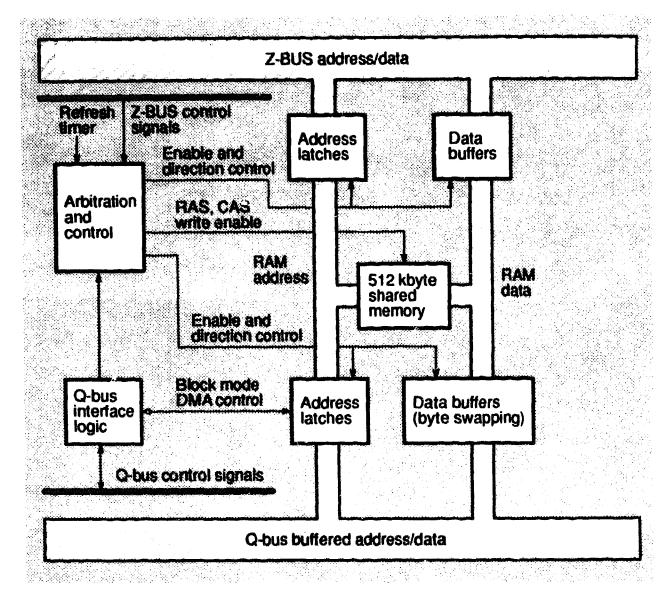

The 512 Kbyte Z-BUS memory is implemented as a 256K by 16-bit DRAM that may be accessed by the CPU, the TMS380C16, or the Q-bus host. The memory controller uses PAL devices to provide all of the control signals required for arbitration, address multiplexing, read-and-write control, and refresh timing. Figure 3-9 is a block diagram of the shared memory.

Figure 3-9 Shared Memory Block Diagram

LKG-4951-911

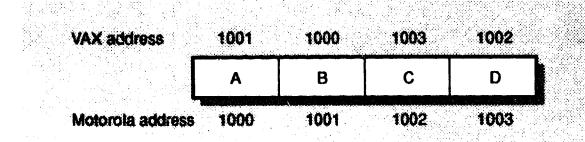

### 3.4.3.1 Data Organization

Motorola and Zilog use a data structure different from the one used by Digital Equipment Corporation. When a word (16-bit) value is stored by a VAX processor, the low-order byte is stored at the lower address in memory, and the high-order byte is stored at the higher address in memory; however, a Motorola processor stores the high-order byte at the lower address and the low-order

byte at the higher address. As shown in Figure 3-10, if the VAX wrote the word "AB" at address 1000, the Motorola 68020 would read the word "AB" from address 1000, but when the VAX writes the byte "B" at address 1000, the 68020 must read address 1001 to access that "B," unless a byte-swapping mechanism is implemented.

Figure 3–10 Data Organization

LKG-4880-

In communications applications, most data is byte-oriented, for example, a string of ASCII characters. Word and longword values are generally the exception, occurring only in headers. A 16-bit data count, or a 32-bit address are examples of header fields. To minimize data manipulation, the DEQRA hardware swaps all bytes as the VAX reads from, and writes to, the shared memory. This enables all byte-oriented data to be interpreted correctly without software intervention. Word values require byte-swapping, and longword values require both byte- and word-swapping. By convention, DEQRA-resident software accepts full responsibility for swapping data fields where required. This makes byte-swapping functions transparent to all host-resident software.

#### 3.4.3.2 Arbitration

A Z-BUS master, the host, and the refresh timer may have simultaneous requests for memory transactions; therefore, arbitration logic must select the active memory-cycle type, execute a memory cycle for that requester, and generate appropriate signals to delay memory transactions from the other requesters. At the end of the current transaction, the arbiter selects the next active cycle, and initiates a new memory cycle to complete the stalled transaction. This arbitration scheme ensures that the Q-bus host and the DEQRA devices alternate cycles when both have continuous requests for memory usage.

#### 3.4.3.3 Q-bus Support

The 512 Kbyte area of shared memory is mapped into the Q-bus address space for use as the shared-memory window by the host. The memory controller supports Q-bus block-mode transfers by providing the  $\overline{BREF}$  control signal required by Q-bus masters, and the address-incrementing function required for contiguous memory access without explicit address overhead for each Q-bus cycle. The DEQRA forces all Q-bus master devices to strictly follow the 16-word boundary, as specified by Digital Equipment Corporation, by not asserting  $\overline{BREF}$  across this boundary.

The memory-controller arbitration unit continues to interleave Z-BUS memory cycles with Q-bus cycles during host block-mode transfers. This ensures that neither the real-time communications data nor the 68020 program execution are locked out during Q-bus block-mode transfers.

#### 3.4.3.4 Refresh

The DRAM requires refresh cycles every 15.6  $\mu$ s to maintain data integrity. Refresh cycles have highest priority and the arbitration unit schedules them for execution while Q-bus, Z-BUS, or both, transactions wait to use the memory. The refresh overhead uses approximately 2 percent of the memory bandwidth.

#### 3.4.4 Timers

The Z-BUS includes a Z8036 counter/timer and parallel I/O device. The CIO contains two general purpose byte-wide parallel I/O ports, one four-bit I/O port, and three 16-bit counter/timers. The parallel I/O ports are used for the host interface and are described in Section 3.5.

The three 16-bit counter/timers are available to applications for general purpose usé.

- Counters 1 and 2 may be linked to form a 32-bit counter under software control.

- The 5 MHz clock input provides for a maximum terminal count rate of 1.25 MHz with a timing resolution of 400 ns.

All timers are tested singly, and in linked mode, during the self-test diagnostics.

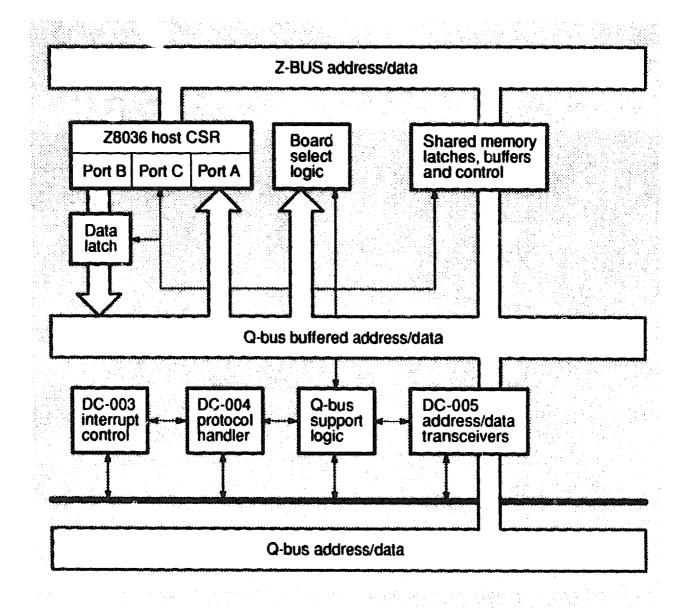

#### 3.5 Host Interface

The DEQRA front-end processor is used with Digital Equipment Corporation's Q-bus-based VAX computers. Figure 3-11 shows the host interface block diagram.

Figure 3-11 Host Interface Block Diagram

LKG-4952-911

The communication medium between the board and the host is provided by the combination of a shared memory and a command and status register. The use of shared memory reduces the complexity of the board interface to the host machine because the shared window is mapped into both the Q-bus and DEQRA memory space. The host driver simply fills a buffer in the shared window and notifies the DEQRA, through the CSR, that the buffer is ready for transmission. The DEQRA manipulates the data, as required, before transferring it to the token ring. Conversely, when a receive buffer has been filled and any data manipulation is completed, the DEQRA sends a message, through the CSR, informing the host of the availability of the completed buffers. Additional interrupts are generated to request and acknowledge download requests or initiate board resets and non-maskable interrupts (NMI) from the host side.

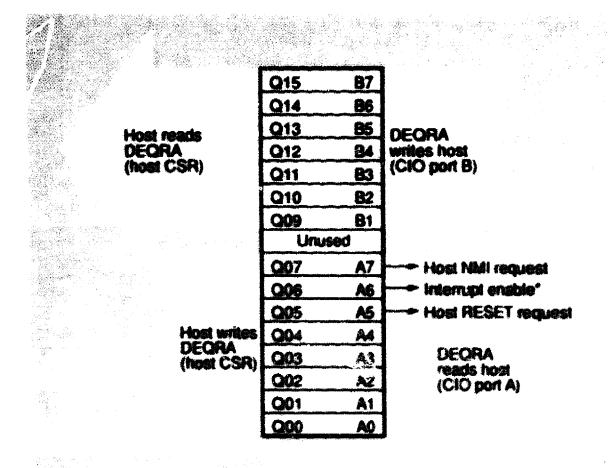

#### 3.5.1 Command and Status Register

The parallel ports of the C!O are configured to be used as the host-interface command and status register. The CSR provides one byte in each direction for me sage transfer between the host and the board. Port A provides the eight-bit input port for host writes to the DEQRA, and port B provides the eight-bit output port for DEQRA writes to the host. The CSR bit definition is shown in Figure 3-12.

Figure 3-12 Command and Status Register

A write to the 68020's CIO port B must occur before the host can see the IE bit previously posted.

CEG AND DE

Port C, the four-bit port, is used to implement the hardware handshake required for proper latching and presentation of data between the DEQRA and the host system. Writes from the board to the host use an interlocked handshake. This means that additional writes by the DEQRA are not executed until the host has serviced the interrupt caused by the initial DEQRA write. Writes from the host to the DEQRA use a strobed handshake. This means that the host may overwrite the data in the CSR whether or not the DEQRA has

serviced the interrupt caused by the initial write. The DEQRA always reads the current data in the CSR; overwritten data is lost.

#### 3.5.2 Interface Devices

The DEQRA uses Digital Equipment Corporation interface integrated circuit (IC) devices for direct connection to the host's Q-bus. These provide optimal bus-loading characteristics by decoupling the board-side logic from the bus. The interface integrated circuits are defined as follows:

- The DC-003 interrupt controller provides the interrupt request, acknowledge, and control functions for the Q-bus. The DEQRA uses level 4 interrupt requests on the Q-bus. Its interrupt priority is dependent on its position in the host system and is determined by the boards between it and the host CPU.

- The DC-004 protocol IC decodes Q-bus control signals and generates buffered control signals indicating read/write, byte/word, and CSR/memory selection that can be used by the DEQRA support logic.

- The DC-005 contains address-recognition logic, interrupt-vector drivers, and address/data bus transceivers in one package.

#### 3.5.3 Support Logic

The Q-bus support logic is implemented in PAL devices. The buffered Q-bus signals from the Digital Equipment Corporation devices and the DEQRA-side control signals are used to assist in shared-memory access. block-mode transfer support, and board selection.

## 3.6 Shared Memory Base Address Selection

The Q-bus base address for the onboard 512k bytes of memory must be set before installation. If more than one DEQRA is installed in a system, or if another Q-bus module using a Q-bus address is installed, you must ensure that the addresses do not overlap. Each module must have a unique base address.

To select the shared memory base address, refer to the DEC TRNcontroller 100 Hardware Installation guide. The default address for the first DEQRA begins at address 12000000 and ends at address 13777777. The second DEQRA, if one exists, begins at address 14000000 and ends at address 15777777.

### 3.7 CSR Address Selection

The CSR switches allow the CSR address to be located anywhere in the Q-bus I/O floating address space. The default address for the first DEQRA is 761344 and 761346 for the second DEQRA.

The CSR base address may be obtained using VMS for both the MicroVAX 3000 series and VAX 4000 Model 300 systems. To select the CSR address, refer to the TRNcontroller 100 Hardware Installation guide.

## 3.8 Interrupt Vector Address Selection

The interrupt vector may be located anywhere in the 300 to 774 vector address space. The default vector address is 300. The correct vector may be obtained using VMS for both the MicroVAX 3000 series and VAX 4000 series systems. To select the interrupt vector address, refer to the DEC TRNcontroller 100 Hardware Installation guide.

## 3.9 Shared Memory Jumper (JP1)

Jumper JP1 determines whether the DEQRA's shared memory is visible to the host at powerup. To make the shared memory visible to the host at powerup refer to the DEC TRNcontroller 100 Hardware Installation guide. Enable is the normal position of JP1.

## 3.10 Token Ring Interface

The token-ring interface is made up of the token-ring communications processor, token-ring private memory, the ring-interface module, and bus timing-conversion circuitry. The token-ring interface handles all data and control signals between the board and the token ring. Figure 3–13 shows a block diagram of the token-ring circuitry.

Figure 3-13 Token Ring Circuitry Block Diagram

LKG-49

#### 3.10.1 TMS380C16

The TMS380C16 is Texas Instruments' token-ring communications processor. It is packaged in a single, 132 plastic quad flatpak. It has three major functions: a DMA transfer controller, a protocol handler, and a communications processor. The DMA transfer controller is the interface between the token circuitry and the rest of the DEQRA. It transfers data between the tokenring private memory and shared memory. It also notifies the CPU of any change in the token-ring status through interrupts. The communications processor runs source code provided by Texas Instruments to control the DMA transfer controller and monitor the token ring. The protocol handler performs hardware-based protocol functions. The protocol conforms to the IEEE 802.5 standard for a 4 or 16 Mbytes/s token-ring local area network. The CPU accesses the TMS380C16 through six registers. Two of these registers (SIFINT and SIFACTL) are used for controlling the TMS380C16, whereas the other four are used to access the TMS380C16's internal registers and private memory. Table 3-7 lists the registers with their addresses.

Table 3-7 TMS380C16 Register Addresses

| TMS380C16 Registers | Address | Description      |  |

|---------------------|---------|------------------|--|

| SIFDAT              | 13F7000 | Data             |  |

| SIFDATI             | 13F7002 | Data             |  |

| SIFADR              | 13F7004 | Address          |  |

| SIFINT              | 13F7006 | Interrupt        |  |

| SIFACTL             | 13F7008 | Control          |  |

| SIFADR2             | 13F700A | Address          |  |

| SIFADRX             | 13F700C | Extended address |  |

### 3.10.2 TMS380C16 Reset Operation

When the TMS380C16 is reset, the device goes into a halted state and waits for its communication processor's halt bit in its adaptor-control register to clear. This prevents the TMS380C16 from trying to execute code from power-up. Since the TMS380C16 fetches instructions from its private DRAM memory, the code needs to be downloaded after any hardware reset before the device can begin to execute instructions. After the code is downloaded and the halt bit is cleared, the TMS380C16 initializes its internal registers from private memory and runs its internal diagnostic tests. If the tests pass, the TMS380C16 begins normal operation.

### 3.10.3 Bus Timing Circuitry

The TMS380C16 is designed for standard 68000 bus architecture; therefore, conversion circuitry is needed to attach it to the Z-BUS. A PAL is used to synchronize and convert the control signals traveling between the Z-BUS and the TMS380C16. This conversion logic minimizes delays while providing deterministic transition cycles between these two asynchronously clocked sub-systems.

### 3.10.4 Token Ring Memory

The token-ring private memory consists of 512 Kbytes of DRAM with 100 ns access time. The DRAM is configured as 256k by 16 bits. The TMS380C16 uses the private memory to store instruction code as well as for packets of data received and transmitted onto the token ring. The TMS380C16 can be programmed for transparent mode allowing the CPU to have access to almost all of its private memory. (Because the TMS380C16 uses a specific area of memory as internal register space, the CPU is restricted from accessing this area.)

### 3.10.5 Ring Interface Module

The TMS380C16 is connected to the token ring by way of a Pulse Engineering analog interface module. This module handles the actual electrical interface to the ring and adheres to the token-ring standard IEEE 802.5. The DEQRA 4 or 16 Mbytes/s token-ring adapter card, uses the token ring optimized line interface (TROLI). The TROLI consists of the Texas Instruments' TMS38053 chip and some passive components. The physical ring is composed of a twisted wire pair for receiving data, and a separate twisted wire pair for transmitting data. The physical connection to the ring is a DSUB9 socket. Figure 4-1 shows the pin assignments for this connector.

## 3.11 Host-to-Board-to-Token Ring Transfers

The DEQRA interfaces to the host through shared memory and the CSR, and to the token ring by means of the TMS380C16. In normal operation, transferring a buffer from the host to the token ring begins by the host filling a buffer in shared memory and notifying the CPU, through the CSR, that a buffer is waiting to be transferred. The CPU performs any data manipulation that is needed before requesting the DMA transfer controller in the TMS380C16 to transfer the buffer. The DMA transfer controller transfers the buffer from shared memory to the TMS380C16's private memory. Once the buffer is in TMS380C16's private memory, the TMS380C16 notifies the CPU that the transfer is complete and sends the buffer out onto the token ring through the ring interface. If a buffer from the ring is destined for the

host, the TMS380C16 reads the buffer through the ring interface and stores it in its private memory. The TMS380C16 then notifies the CPU that a buffer is waiting to be transferred to the host. The CPU requests the TMS380C16 to transfer the buffer to shared memory. The DMA transfer controller on the TMS380C16 transfers the buffer, and the TMS380C16 notifies the CPU when the transfer is complete. The CPU first performs manipulation on the data, if needed, and then notifies the host, by way of the CSR, that a buffer is waiting in shared memory. The host reads the buffer from shared memory and notifies the CPU when the read is complete.

## 3.12 Details of Operation

The remainder of this chapter discusses the DEQRA's:

- Interrupt structure

- Board timing

- **Z-BUS** arbitration

- Resets

- Bus errors

- **NMI** functions

#### 3.12.1 Interrupts

The DEQRA supports the 68020 interrupt level structure.

### 3.12.1.1 Interrupt Structure

The DEQRA uses four of the seven 68020 processor-interrupt levels. The seven-level interrupt structure is implemented by encoding interrupt requests on three interrupt-priority-level signal pins. These input pins are sampled by the processor. If any of them are asserted, and if the encoded priority is greater than the current interrupt mask level, an interrupt request is made. The processor services the pending interrupt at the next instruction boundary. The 68020 supports both device-supplied vector and autovector peripherals, but the devices on the DEQRA are all DSV devices. When the processor is ready to initiate interrupt servicing, it begins an interrupt-acknowledge cycle. This cycle is similar to a normal read cycle. An IACK cycle, at the pending interrupt level, enables the device requesting an interrupt to present a vector byte. The processor uses this byte as an offset to locate the peripheral's interrupt-service entry point.

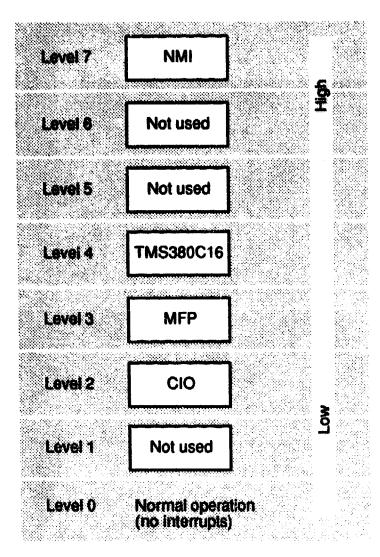

#### 3.12.1.2 Interrupt Levels

There are only three devices on the DEQRA that use interrupts. Therefore, there is only one device for each interrupt level. The following is a description of the interrupt levels shown in Figure 3-14:

- Level 7 is a non-maskable interrupt that causes the 68020 to stop the execution of the current program and break to the debugging tool. NMIs may be issued by pushing the NMI button on the front edge of the board, or by writing a 1 to bit 7 of the host interface CSR from the host side.

- Level 6 is not used.

- Level 5 is not used.

- Level 4 is used by the TMS380C16, the token ring communications processor.

- Level 3 is used by the MFP (operating system and status bits).

- Level 2 is used by the CIO for host CSR interface support.

- Level 1 is not used.

Figure 3-14 Interrupt Priority Structure

LKG-5027-911

### 3.12.2 Timing

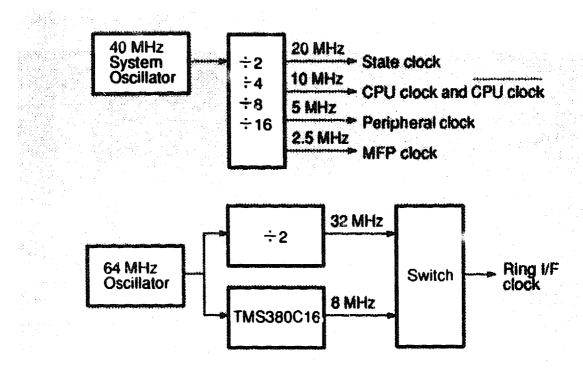

The following sections describe the clock-generation logic of the DEQRA and the transaction timings that result from its implementation. Note that clock generation for token-ring circuitry is isolated from all other timing on the board and is discussed in Section 3.12.2.1.

#### 3.12.2.1 Clock Generation

The DEQRA uses synchronous state machine design techniques throughout the control logic to ensure accurate circuit performance and to increase circuit reliability. All clock signals, except the token-ring clock signals, are derived from a divider circuit that is clocked by the 40 MHz system oscillator as shown in Figure 3–15.

The 20 MHz state clock is used by the processor bus memory controller and DSACK generator state machines. The 10 MHz clock and its complement are used by the 68020, the Z-BUS conversion and arbitration state machines, and the shared memory controller. The 5 MHz clock (PCLK) is used by the CIO and the Z-BUS interrupt state machine. The 2.5 MHz clock is used by the MFP and is further divided for the very low resolution RESET, NMI, and BUS\_ERROR state machines

The token-ring circuitry uses a 64 MHz oscillator. The TMS380C16 divides the 64 MHz internally and provides an 8 MHz clock for the 4 Mbytes/s ring-interface selection. For the 16 Mbytes/s token-ring, the 64 MHz clock is divided by a simple D-flop to 32 MHz. The 32 MHz clock runs the ring-interface module. Switching circuitry is provided to select the 8 MHz clock or 32 MHz clock depending on the respective 4 Mbytes/s or 16 Mbytes/s ring-interface selection.

Figure 3-15 DEQRA System Timing

LKG-5030-911

#### 3.12.2.2 Transaction Timing

The advanced architecture of the 68020 makes exact instruction-timing calculations difficult. The 256-byte instruction cache, the three-stage prefetch pipeline, the execution overlap capabilities, and the effects of operand misalignment complicate these calculations. Timing is also affected by memory system refreshes and Z-BUS arbitration delays. Refresh delays and Q-bus memory usage also affect Z-BUS device memory cycle times. Figure 3-16 shows transaction timing information for CPU and TMS386C16 transfers.

Figure 3-16 DEQRA Transaction Timing

|                             |        |              |        |       | _       |       |       |

|-----------------------------|--------|--------------|--------|-------|---------|-------|-------|

|                             |        | Process      | or bus |       | 4       | Z-BUS |       |

|                             | MEM    | <b>EPROM</b> | MFP    | Regs  | MEM     | CIO   | TMS   |

| 68020 cycle<br>@ 10 MHz     | 333ns* | 500ns        | 750ns  | 333ns | 416ns** | 583ns | 583ns |

| TMS380C16<br>cycle<br>@8MHz | N/A    | NA           | NA     | N/A   | 500ns   | NA    | N/A   |

| Z8016 cycle<br>@5 MHz       | N/A    | NA           | NA     | NA    | 500ns   | N/A   | N/A   |

<sup>\*</sup>For cycles that are not delayed by refresh.

Typical instruction time MOVL (Am)+, (An)+ worst case = 12 clocks @ 83.3 ns = 1.000 μs cache case = 7 clocks @ 83.3 ns = .583 μs

LKG-4957-91

#### 3.12.3 Z-BUS Arbitration

The 68020 or the TMS380C16 may request use of the Z-BUS. The Z-conversion and the arbitration state machines work together to determine which of these will be the next Z-BUS master. See Figure 3-17.

<sup>\*\*</sup>For cycles that are not delayed by refresh or shared mumory cycles already in progress.

Figure 3-17 Z-BUS Arbitration Block Diagram

LKG-5031-911