# DELQA

# **Technical Manua**

Order Number: EK-DELQA-TM-001

# **Technical Manual**

Order Number: EK-DELQA-TM-001

Prepared by Educational Services of Digital Equipment Corporation

# JUNE-1988

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1988 by Digital Equipment Corporation

All Rights Reserved.

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| DEC          | DIBOL     | UNIBUS               |

|--------------|-----------|----------------------|

| DEC/CMS      | EduSystem | VAX                  |

| DEC/MMS      | IAS       | VAXcluster           |

| DECnet       | MASSBUS   | VMS                  |

| DECsystem-10 | PDP       | VT                   |

| DECSYSTEM-20 | PDT       |                      |

| DECUS        | RSTS      | digital <sup>™</sup> |

| DECwriter    | RSX       |                      |

This document was prepared using VAX DOCUMENT, Version 1.0

# CONTENTS

1925

| Preface | <br> | <br>• |  | <br>• | • |  | • | <br>• | • | • | • |  | • | • | • | <br>• | • | • | • |  | • | • | • | <br>• | • | • | <br>• | • | • |  | vii |

|---------|------|-------|--|-------|---|--|---|-------|---|---|---|--|---|---|---|-------|---|---|---|--|---|---|---|-------|---|---|-------|---|---|--|-----|

|         |      |       |  |       |   |  |   |       |   |   |   |  |   |   |   |       |   |   |   |  |   |   |   |       |   |   |       |   |   |  |     |

# **CHAPTER 1** Introduction

| 1.1    | SCOPE                           | 1–1 |

|--------|---------------------------------|-----|

| 1.2    | FUNCTIONAL OVERVIEW             | 1–1 |

| 1.2.1  | Normal Mode and DEQNA-Lock Mode | 1–1 |

| 1.2.2  | Module Interfaces               | 1–2 |

| 1.2.3  | Module Operations               | 1–2 |

| 1.2.4  | Protocol Functions              | 1–3 |

| 1.2.4. | 1 Physical Channel Functions    | 1–4 |

| 1.2.4. | 2 Data Link Functions           | 1–4 |

| 1.2.5  | Q-Bus Interface                 | 1–4 |

| 1.3    | TECHNICAL OVERVIEW              | 1–6 |

| 1.3.1  | Module Components               | 1–6 |

| 1.3.1. | 1 Integrated Circuits           | 1–6 |

| 1.3.1. |                                 | 1–6 |

| 1.3.2  | Module Processing Operations    | 1–7 |

| 1.3.3  | Network Integrity Functions     | 1–8 |

| 1.3.3. | 1 Self-test Diagnostics         | 1–8 |

| 1.3.3. | 2 Sanity Timer                  | 1–8 |

| 1.3.3. | 3 Controller Loopback Modes     | 1–9 |

| 1.3.3. | 4 Remote Console Commands       | 1–9 |

| 1.3.3. |                                 | 1–9 |

|        |                                 |     |

# **CHAPTER 2** Functional Description

| 2.1 SCOPE                          |

|------------------------------------|

| 2.2 MODULE OPERATIONS              |

| 2.2.1 Q-Bus Transfers              |

| 2.2.1.1 Data DMA                   |

| 2.2.1.2 Control DMA 2–2            |

| 2.2.1.3 Non-block-mode DMA 2–2     |

| 2.2.1.4 Data and Status Conversion |

| 2.2.2 Backport Bus Arbitration     |

| 2.2.3 Ethernet Transfers           |

| 2.2.3.1 Transmission               |

| 2.2.3.2 Reception                  |

| 2.2.4 Master Module Control        |

| 2.3 SYSTEM PORT INTERFACE          |

| 2.3.1 Port Registers               |

| 2.3.2 Memory Map                   |

| 2.3.3   | Setup                                                             | 2–6  |

|---------|-------------------------------------------------------------------|------|

| 2.3.3.1 | 1 Setup Information                                               | 2–7  |

| 2.3.4   | Transmit Packet                                                   | 2–7  |

| 2.3.5   | Transmit Programming                                              | 2–9  |

| 2.3.6   | Transmission Errors                                               | 2–10 |

| 2.3.7   | Receive Packet                                                    |      |

| 2.3.8   | Receive Programming                                               | 2–11 |

| 2.4     | NETWORK SUPPORT                                                   | 2–11 |

| 2.4.1   | Remote Trigger Instruction                                        | 2–12 |

| 2.4.2   | Loopback Assistance                                               | 2-12 |

| 2.4.3   | Transmit System ID                                                |      |

| 2.4.4   | Request System ID                                                 | 2–12 |

| 2.4.5   | IEEE 802.3 Network Support: NULL Link-layer Service Access Points | 2–13 |

| 2.4.6   | Datalink Counters                                                 | 2–13 |

# **CHAPTER 3** Technical Description

| 3.1 SCOPE                                                                                                                                                                                                                                                                                                        | 3–1                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 3.2.1       Overview                                                                                                                                                                                                                                                                                             | 3–1<br>3–1<br>3–2<br>3–3<br>3–5                                      |

| 3.3.1       Overview       3.3.1       Overview       3.3.2         Initialization       3.3.3       DMA Functions       3.3.3         3.3.3.1       Data DMA       3.3.3                                                                                                                                        | 3-5<br>3-5<br>3-10<br>3-10<br>3-10<br>3-11                           |

| 3.4.1       Overview       3         3.4.2       Initialization       3         3.4.2.1       Destination Addresses       3         3.4.2.2       LANCE Memory Structures       3         3.4.3       Transmission       3         3.4.4       Reception       3         3.4.5       Collision Detection       3 | 3–11<br>3–11<br>3–12<br>3–14<br>3–14<br>3–14<br>3–14<br>3–15<br>3–15 |

| 3.5.1       Overview       3         3.5.2       Backport Interface Timing       3                                                                                                                                                                                                                               | 8–16<br>8–16<br>8–16<br>8–16                                         |

| 3.6.1 Interrupts                                                                                                                                                                                                                                                                                                 | 8–19<br>8–19<br>8–19                                                 |

# Appendix A IC Descriptions

| A.1                                                       | SCOPE                                                                                                                                                                                                       | A–1                                                          |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

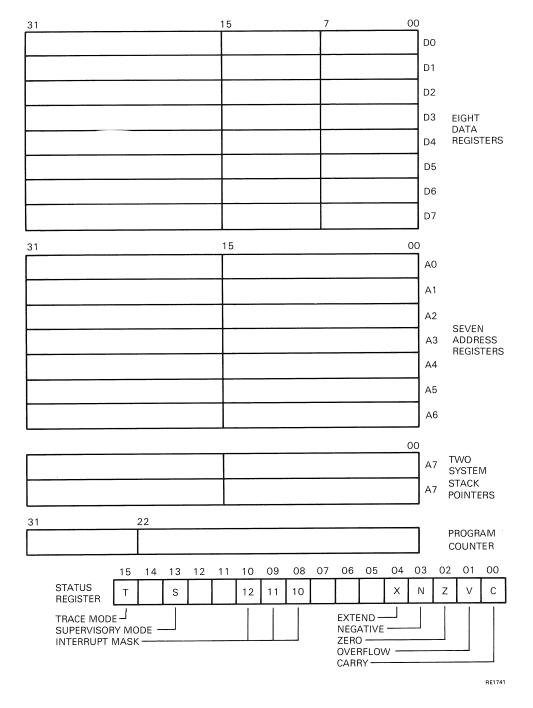

| A.2<br>A.2.1<br>A.2.2<br>A.2.3                            | 68000 MICROPROCESSOR                                                                                                                                                                                        | A-1<br>A-2<br>A-2<br>A-7                                     |

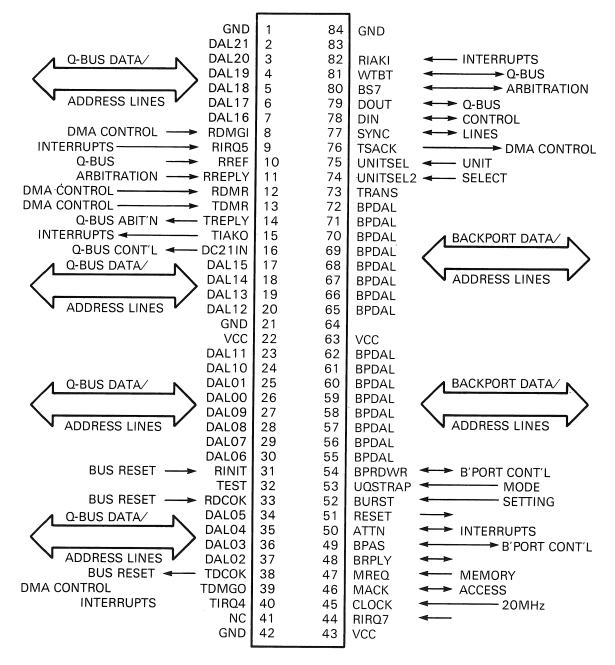

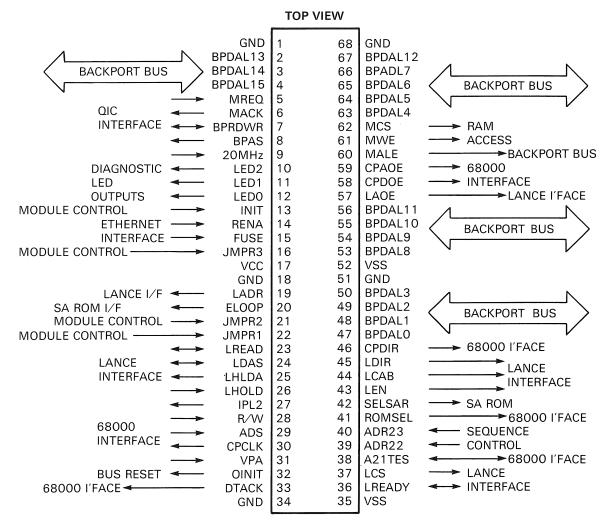

| A.3<br>A.3.1<br>A.3.2<br>A.3.3<br>A.3.4                   | Q-BUS INTERFACE CONTROLLER (QIC)         Overview         Signals and Pinouts         Q-bus Addressing         QIC Registers                                                                                | A-8<br>A-8<br>A-14<br>A-15                                   |

| A.4<br>A.4.1<br>A.4.2<br>A.4.2.1<br>A.4.2.2<br>A.4.2.3    | QNA2 Q-BUS NETWORK ARBITRATOR         OVERVIEW         SIGNALS AND PINOUT         QNA2 Signal Descriptions         Pinout         Addressing                                                                | A–16<br>A–17<br>A–17<br>A–21<br>A–21                         |

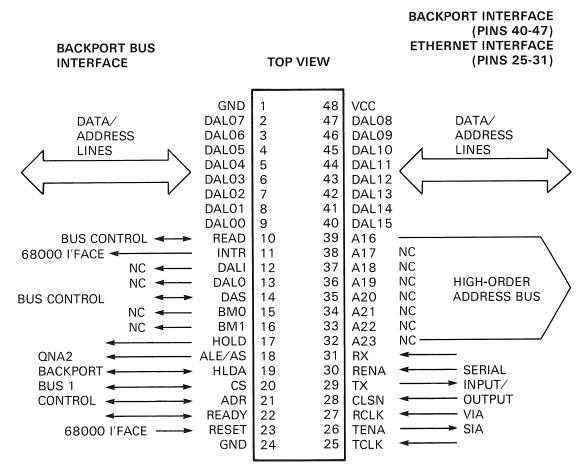

| A.5<br>A.5.1<br>A.5.2<br>A.5.3<br>A.5.4<br>A.5.5<br>A.5.6 | AM7990 LOCAL AREA CONTROLLER FOR ETHERNET         (LANCE)         Overview         Signals and Pinout         LANCE Addressing         LANCE Registers         LANCE Buffers         Logical Address Filter | A-23<br>A-23<br>A-24<br>A-28<br>A-28<br>A-28<br>A-28<br>A-32 |

| A.6<br>A.6.1<br>A.6.2<br>A.6.3                            | AM7991 SERIAL INTERFACE ADAPTER (SIA)                                                                                                                                                                       | A-33<br>A-33<br>A-33<br>A-37                                 |

# Appendix B Network Management

| B.1   | SCOPE                    | B-1 |

|-------|--------------------------|-----|

| B.2   | NETWORK CONTROL          | B-1 |

| B.2.1 | Ethernet Transmission    | B-1 |

| B.2.2 | Ethernet Reception       | B-1 |

| B.2.3 | Ethernet Contention      | B-2 |

| B.2.4 | Ethernet Fault Detection | B-2 |

|       |                          |     |

# INDEX

# **FIGURES**

| 1-1 | DELQA Functional Block Diagram | 1–3 |

|-----|--------------------------------|-----|

| 1–2 | Host I/O Page Map              | 1–5 |

| 1–3 | DELQA Hardware Block Diagram   | 1–7 |

| 2-1 | DELQA Data Path                | 2–4 |

| 2–2 | Backport Control Functions          | 2–5  |

|-----|-------------------------------------|------|

| 2-3 | Transmit Sequence (No Chaining)     | 2–8  |

| 2–4 | Ethernet Packet Format              | 2–9  |

| 3–1 | QNA2 Control Signals                | 3–2  |

| 3–2 | DELQA Clocks and Selection Switches | 3–4  |

| 3–3 | Q-Bus Interface (hardware)          | 3–7  |

| 3–4 | Ethernet Interface (hardware)       | 3–13 |

| 3–5 | DMA Control Signals                 | 3–18 |

| 3–6 | DELQA Interrupt and Reset Signals   | 3–20 |

| A-1 | 68000 Block Diagram                 | A-3  |

| A–2 | 68000 Pinouts                       | A-4  |

| A-3 | QIC Pinouts                         | A9   |

| A-4 | QNA2 Block Diagram                  | A-16 |

| A–5 | QNA2 Pinout                         | A–21 |

| A–6 | AM7990 LANCE Block Diagram          | A–24 |

| A–7 | AM7990 LANCE Pinouts                | A–25 |

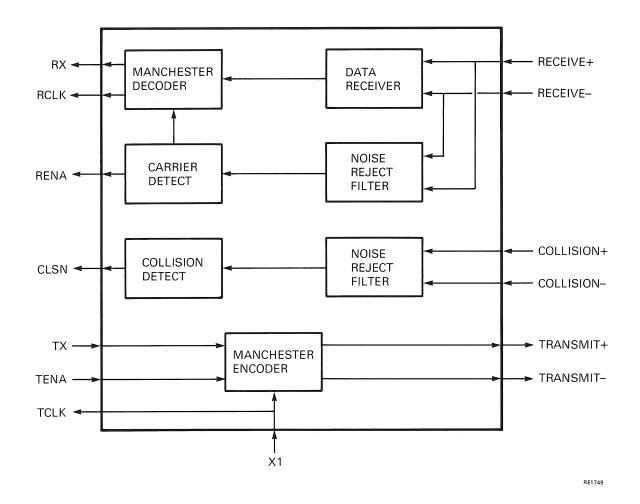

| A–8 | AM7991 SIA Block Diagram            | A-34 |

| A–9 | AM7991 SIA Pinouts                  | A-35 |

|     |                                     |      |

# **TABLES**

| 2-1  | DELQA Unit I/O Base Addresses                | 2–6  |

|------|----------------------------------------------|------|

| 2-2  | Setup Packet: Information Group Combinations | 2–7  |

| 3–1  | DELQA Module: Switch Options                 | 3–3  |

| 3–2  | DELQA and transceiver power requirements     | 3–5  |

| 3–3  | Q-Bus Connector Pins and Signals             | 3–8  |

| 3–4  | Backport Reset                               | 3–10 |

| 3–5  | 68000 Backport Address Map                   | 3–16 |

| A-1  | 68000 Signal Descriptions                    | A–5  |

| A-2  | QIC Signal Descriptions                      | A-10 |

| A-3  | Registers                                    | A-15 |

| A4   | QNA2 Signal Descriptions                     | A–17 |

| A-5  | QNA2 Registers                               | A-21 |

| A-6  | CSR Register Bit Definitions                 | A-22 |

| A–7  | Interrupt Register Bit Definitions           | A-23 |

| A8   | AM7990 LANCE Signal Definitions              | A-26 |

| A-9  | LANCE Registers                              | A-28 |

| A-10 | LANCE Initialisation Block                   | A-29 |

| A-11 | LANCE Descriptor Ring Pointers               | A-29 |

| A-12 | LANCE Four-Word Descriptor Ring Formats      | A-30 |

| A-13 | LANCE Logical Address Filter Mask            | A-32 |

| A-14 | AM7991 SIA Signal Definitions                | A-36 |

|      |                                              |      |

# PREFACE

The DELQA module is a communications option which connects the Q-Bus to an Ethernet (IEEE 802.3 10BASE2) local area network (LAN).

This manual describes how the DELQA communications module functions internally. It provides information on the main hardware components and data paths within the module.

This manual is intended for use by Digital Field Service Support and experienced Customer engineers.

# NOTE Installation, programming and diagnostic information is contained in the Delqa User's Guide. EK-DELQA-UG.

The chapters are as follows:

| CHAPTER 1- | introduces the DELQA module. |

|------------|------------------------------|

|            |                              |

CHAPTER 2 describes the main operations of the DELQA module, and the system port interface to the Q-Bus.

CHAPTER 3 describes how the components of the DELQA module work together on the backport bus.

**APPENDIX** A summarises the details of the principal Integrated Circuits in the DELQA module.

**APPENDIX B** describes the Ethernet Network Management protocol.

Notes and Warnings Notes and warnings are defined as follows:

- A **NOTE** contains general information

- A WARNING is designed to prevent personal injury.

#### Preface

### **Related publications**

Communications Options Mini-Reference Manual: Volume IV (Ethernet) (EK-CMINI-RM)

DECnet Maintenance Operations Protocol (MOP) Functional Specification V3.0.0 (AA-X436A-TK)

DECnet-RSX System Manager's Guide (AA-H224C-TC)

DECnet-VAX System Manager's Guide (AA-H803C-TE)

DELQA Field Maintenance Print Set (MP-02379-01)

Ethernet: A Local Area Network, Data Link Layer, and Physical Layer Specifications (AA-K759B-TK)

Ethernet Installation Guide (EK-ETHER-IN)

H4000 Ethernet Transceiver Technical Manual (EK-H4000-TM)

Introduction to Local Area Networks (EB-22714-18)

### NOTE

When installed in a Micro-PDP11 or a MicroVAX, this equipment has been tested with a Class A computing device and has been found to comply with part 15 of FCC Rules. Operation in a residential area may cause unacceptable interference to radio and TV reception requiring the operator to take whatever steps are necessary to correct the interference.

# CHAPTER 1 INTRODUCTION

### 1.1 SCOPE

This chapter introduces the main functions of the DELQA (Digital Ethernet Local-Area-Network to Q-Bus Adapter), and its main components. The sections are as follows:

# Section 1.2 FUNCTIONAL OVERVIEW Section 1.3 TECHNICAL OVERVIEW

# **1.2 FUNCTIONAL OVERVIEW**

The DELQA module is a DIGITAL Ethernet Local Area Network to Q-Bus Adapter. It fits on the Q-Bus as a communications option for connecting processors from the PDP-11 and MicroVAX families to an Ethernet or IEEE 802.3 local area network (LAN).

## 1.2.1 Normal Mode and DEQNA-Lock Mode

The DELQA module operates in one of two switchable modes: Normal mode or DEQNA-lock mode.

In Normal mode, DELQA supports the following functions:

- Maintenance Operations Protocol (MOP) messages for Remote BOOT, Request ID, Transmit System ID and Loopback.

- IEEE 802.3 Maintenance Messages for XID (Transmit ID) and TEST on NULL LSAP (Link-layer Service Access Point) access points

- Self-test on powerup and via host command.

- Single Ethernet physical address (the first of any specified in a setup packet to replace the default held in Station Address ROM)

- Multiple Ethernet Multi-cast addresses

- All standard DEQNA functions, except multiple Ethernet physical addresses and the automatic enabling of the on-board sanity timer at powerup.

In **DEQNA-lock mode**, DELQA provides functional compatibility with DEQNA modules, but at the expense of losing some Normal mode functions. The functions supported are:

- Multiple Ethernet physical addresses

- Multiple Ethernet Multi-cast addresses

- Sanity timer (Switch enabled on powerup).

The operating mode is selected at powerup by the setting of the mode switch (S3) on-board the DELQA module.

If mode switch S3 is closed, the module operates in Normal mode; subsequently, host software can use the Vector Address Register (VAR15) to set the operating mode to either Normal mode or DEQNA-lock mode. If mode switch S3 is open, the operating mode is fixed as DEQNA-lock, and this cannot be altered by software. Use of DEQNA-lock mode is not recommended.

Host software can determine whether the module is a DELQA or a DEQNA by using bit 0 in the Vector Address Register.

### **1.2.2 Module Interfaces**

The DELQA is a microprocessor-based device which provides all the logic necessary to connect to the Ethernet. It acts as a data communications controller, executing the physical layer protocol and part of the data link layer protocol (as defined by the seven-layer OSI model). The protocol functions include synchronisation, format conversions, encoding and decoding, formatting data packets and data link management.

The DELQA enables programs that execute higher levels of protocol, such as DECnet, to communicate with their peers over the Ethernet link.

The DELQA module performs all the channel access functions necessary to achieve maximum throughput with minimum intervention from the host processor, including:

- Block-mode Direct Memory Access (DMA) to host memory

- Control DMA, which uses Buffer Descriptor Lists (BDLs) in host memory to sequence transfers between data buffers in the host and in the DELQA.

The DELQA implements some of the Maintenance Operation Protocol (MOP) functions on request from a remote station without host intervention. These functions include host reboot, loopback operations, and system identification.

### **1.2.3** Module Operations

The DELQA module transfers data between buffers in host memory and the Ethernet transceiver. The main data flow operations are as follows:

- 1. Transfer of data between host memory buffers and shared RAM in the DELQA.

- 2. Conversion of data and status information between the host format and that used in the DELQA module.

- 3. Transfer of formatted data packets between shared RAM and the Ethernet connector.

The data is formatted in packets of between 60 and 1514 data bytes at a higher level of protocol. The DELQA module calculates and appends a four byte CRC (Cyclic Redundancy Check) to transmit packets, and strips the CRC from receive packets. Therefore, the full length of a packet on the Ethernet is between 64 and 1518 bytes.

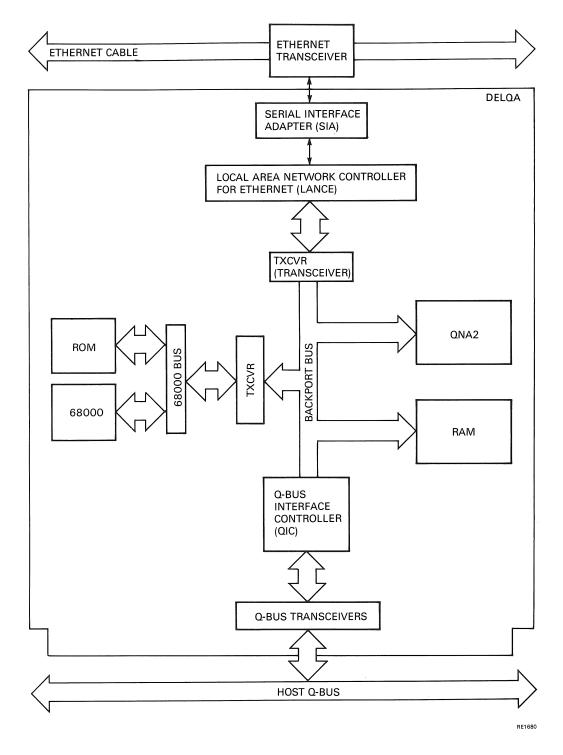

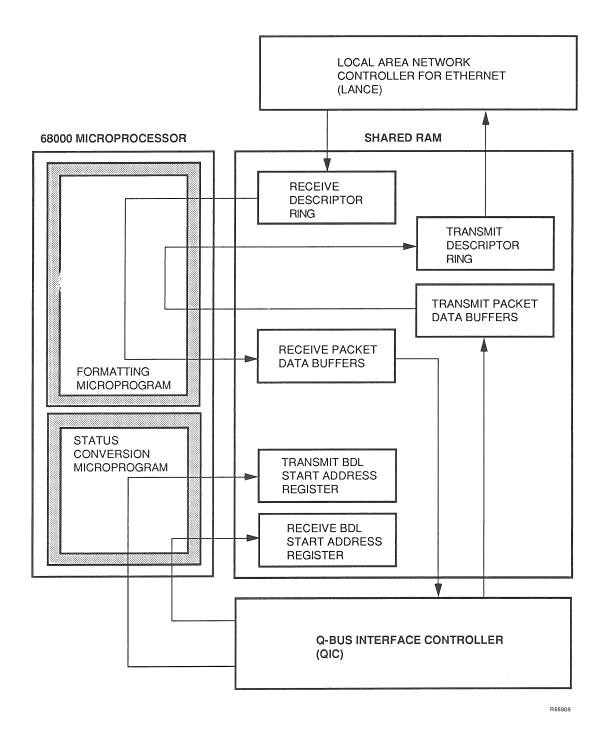

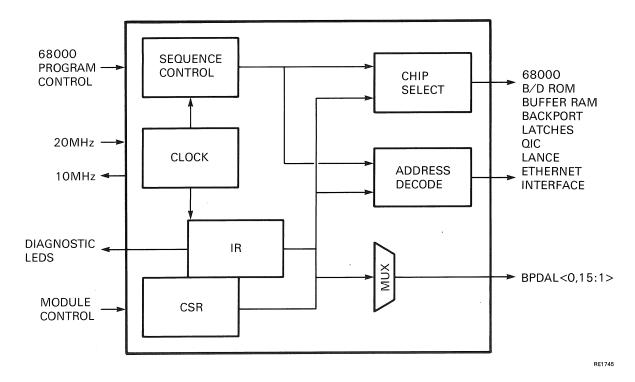

Figure 1–1 shows how transmit and receive data is passed between the main functional components of the DELQA module.

Figure 1–1 DELQA Functional Block Diagram

# **1.2.4 Protocol Functions**

The Physical Channel Functions and the Data Link Functions are described in this section.

# INTRODUCTION

### **1.2.4.1** Physical Channel Functions

The DELQA module transmits and receives at 10 Mbit/s. It provides physical channel functions that are specific to Ethernet and necessary for the interface to the DIGITAL H4xxx Ethernet transceiver. DELQA executes the following functions:

### **During transmission**

- Encodes serial data in Manchester format

- Recognises heartbeat signals from the DIGITAL H4xxx transceiver, verifying that the transceiver is monitoring collision detect signals

- Monitors the self-test collision detect signal from the DIGITAL H4xxx Ethernet transceiver.

### **During reception**

- Senses transmission carrier from any Ethernet station

- Decodes the incoming serial bit-stream from its Manchester format.

### **1.2.4.2 Data Link Functions**

The DELQA module provides the following Ethernet-specific functions at the data link layer:

### **During transmission**

- Generates the 64-bit preamble for synchronisation

- Provides parallel-to-serial conversion of the frame

- Calculates the 32-bit CRC value and places it in the packet sequence field for transmission

- Attempts automatic, multiple re-transmissions upon receiving a collision detect signal.

### **During reception**

- Checks the 32-bit CRC value in each incoming packet

- Performs address filtration, either to match an incoming message to the physical address of the module, or to accept messages broadcast to a group of stations

- Synchronises to the preamble, and removes it prior to processing

- Provides serial-to-parallel conversion of the frame.

The Ethernet provides a datagram service; that is, sending a packet does not guarantee that it will reach its destination. The software for the protocol layers above data link is responsible for checking that a packet has been received, and for recovering from conditions where it has not been received.

### 1.2.5 Q-Bus Interface

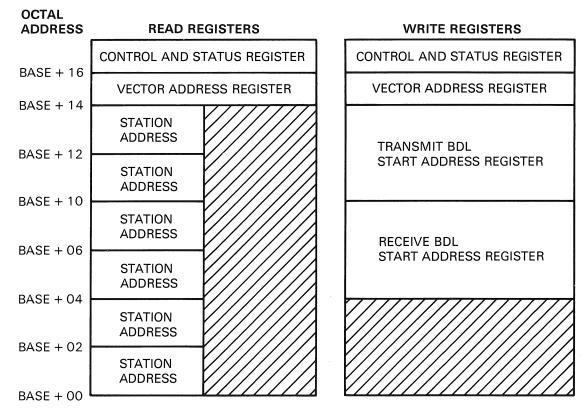

As bus master of the Q-Bus, the host can program the DELQA module by means of eight word-length registers in the I/O page of the Q-Bus memory map. The DELQA acts as bus slave to support access from the Q-Bus to these on-board locations.

Four of the I/O page addresses are write-only registers, used to pass the start addresses of the BDLs for transmit and receive buffers. Two are read/write registers: the Control and Status Register (CSR) and the Vector Address Register (VAR).

The lower bytes of each of the first six addresses are read-only registers, used to access the Station Address (SA) ROM. The SA ROM contains the 48-bit physical address of the DELQA module in the Ethernet LAN.

The DELQA can act as bus master to the Q-Bus, in order to implement DMA transfers (either block mode or non-block mode) between RAM on-board the DELQA and BDLs or data buffers in host memory.

Figure 1–2 shows the Q-Bus memory map for the DELQA module.

RE1686

Figure 1–2 Host I/O Page Map

# **1.3 TECHNICAL OVERVIEW**

The DELQA option comprises one dual-height Q-Bus module, a bulkhead interconnect panel and associated cables. The DELQA module plugs into the Q-Bus backplane and fits into the Q-Bus enclosure. It is physically and electrically connected to the H4xxx transceiver using the bulkhead panel assembly and the appropriate transceiver cable.

## **1.3.1** Module Components

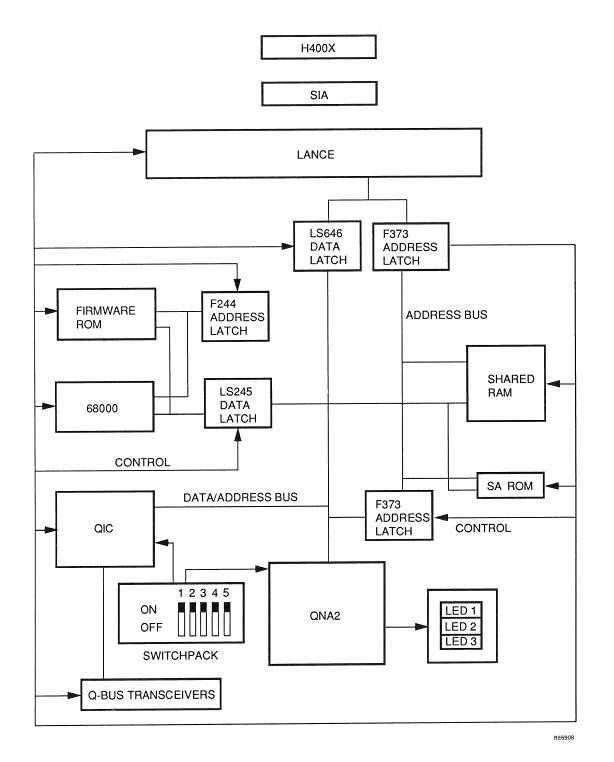

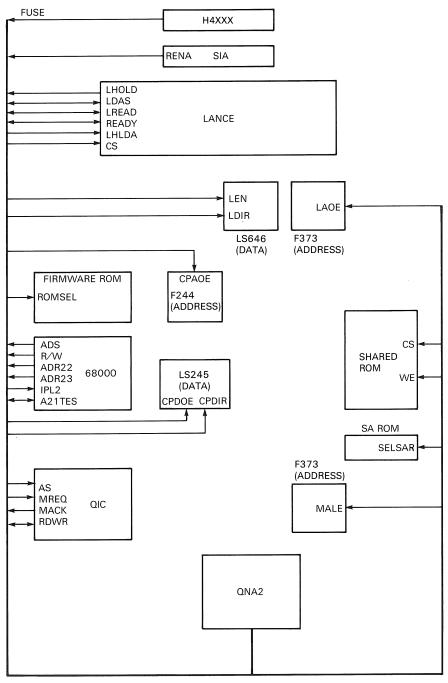

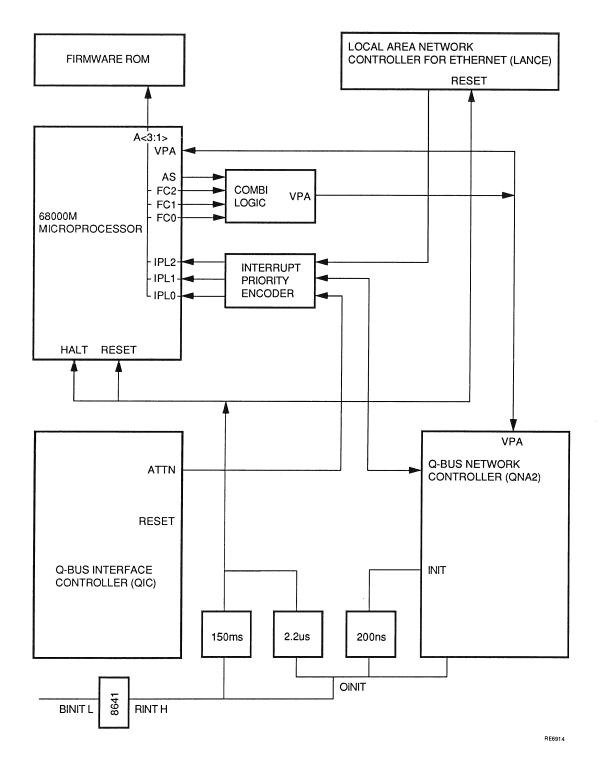

On the DELQA board there are five main integrated circuits to perform the main module operations (refer to Section 1.2.3). These operations are controlled by the on-board microprocessor. Data storage is provided by shared RAM. Figure 1–3 shows the major components of the DELQA module and their interconnections.

# **1.3.1.1 Integrated Circuits**

The principal integrated circuits in the DELQA module are:

## 1. Q-Bus Interface Controller (QIC)

This gate array provides a DMA path between the host system memory and the shared memory on the DELQA board, and between SA ROM and host memory. The QIC also allows the host system access to the internal registers of the DELQA.

## 2. 68000 Microprocessor

This is the 16-bit microprocessor which controls the DELQA and performs the necessary conversions of the frame data between host buffer format and Ethernet packet format.

# 3. Q-Bus Network Arbitrator (QNA2)

This gate array provides access to the backport bus, arbitrating between the QIC, the 68000 microprocessor, and the LANCE.

## 4. Local Area Network Controller for Ethernet (LANCE)

This is a VLSI circuit which performs bidirectional DMA between shared RAM and the Serial Interface Adapter (SIA).

## 5. Serial Interface Adapter (SIA)

This is a VLSI circuit which links the LANCE to the H4xxx Ethernet transceiver. The SIA provides Manchester encoding of data transmitted, and decoding of data received.

## 1.3.1.2 On-board Memory

The DELQA module contains both preprogrammed ROM and static RAM, as follows:

- 1. Firmware ROM contains 12Kwords of Master Control Program for the module (executed by the 68000 microprocessor). In addition the firmware ROM contains 4Kbytes of self-test diagnostic code and 4Kbytes of PDP-11 boot/diagnostic code for a PDP-11 host. (MicroVAX systems provide equivalent boot/diagnostic code for their own host system ROM).

- 2. Station Address (SA) ROM. (32 bytes) contains, in the first six bytes, the default physical address of the DELQA module. The SA ROM also contains a 2 byte checksum which is accessible to host software.

- 3. Shared RAM (16Kwords) provides the memory for data packet buffers, Buffer Descriptor Lists (BDLs) the Vector Address Register, the LANCE initialisation block (which includes the physical address of the module) and firmware data structures.

Figure 1–3 DELQA Hardware Block Diagram

# 1.3.2 Module Processing Operations

The operation of the DELQA can be broken down into processing modules, as follows:

- 1. The QIC transfers data between Q-Bus memory and shared RAM, as follows:

- Block-mode (or non-block-mode) DMA (block size up to 16 words) to transfer data buffers directly to and from shared RAM

- Control DMA (block size up to four words) to transfer control information and Buffer Descriptor List (BDL) entries. Control DMA does not use block-mode.

- 2. The 68000 microprocessor translates data and status information between the format recognised by the host system and that recognised by the LANCE.

- 3. The QNA2 provides access to the backport bus, arbitrating between (in order of priority): the QIC, the 68000 microprocessor, and the LANCE. It also provides all the gating and strobing signals necessary for these devices to access shared memory.

- 4. The LANCE and the SIA operate together to transfer the translated packets between shared RAM and the H4*xxx* Ethernet transceiver.

The SIA uses Manchester coding to encode transmitted data and decode received data. The SIA detects and synchronises with incoming data, and passes it on to the LANCE. The LANCE checks the destination address, and, if it matches any of the module addresses, transfers the data direct by DMA into shared RAM.

5. The 68000 microprocessor controls the operation of the DELQA module, including chip initialisation and module self-test (implemented on powerup or initiated by host software).

### **1.3.3** Network Integrity Functions

The DELQA module provides the following features for network integrity:

- Quick-verify self-test diagnostics for powerup, boot, and via host command.

- Sanity timer to monitor host software

- Controller loopback

- Maintenance Operations Protocol (MOP) messages for Remote Monitor Console (RMC) operations: Remote BOOT, Request ID, Transmit System ID

- Maintenance Operations Protocol (MOP) messages for Ethernet Channel Test (ECT): Loopback

- Maintenance Operations Protocol (MOP): datalink counters, maintained and stored by DELQA

- IEEE 802.3 Maintenance Messages for XID (Transmit ID) and TEST on NULL Link-layer Service Access Points (LSAPs).

To assist in fault diagnosis and network management, the DELQA can also operate in promiscuous addressing mode. Effectively, this disregards the internal address filter logic. This allows the DELQA to accept all packets received from the network, and to verify the integrity of the received data by performing a 32-bit CRC check on each received packet. All transmissions (normal, loopback, and Setup) reset the sanity timer without affecting its status (enabled or disabled).

## 1.3.3.1 Self-test Diagnostics

In Normal mode, the DELQA executes a comprehensive self-test on powerup. This takes approximately five seconds to complete.

The firmware ROM on the DELQA contains 4 KBytes of PDP-11 boot/diagnostic code. If the module is controlled by a PDP host, the host can execute this code in order to increase fault coverage. This enables the DELQA to determine that it is operating correctly, before it attempts to access the Ethernet.

### 1.3.3.2 Sanity Timer

The sanity timer acts as a check that the host software is operating effectively. If the host communications driver fails to reset the timer periodically, the timer initiates a system reboot at the host.

#### **1.3.3.3 Controller Loopback Modes**

In internal loopback, the DELQA loops all messages through the module, and the host can neither send nor receive Ethernet messages.

Internal loopback may be entered either by the host command (set CSR08) or at device powerup. The behaviour of the device differs according to its mode.

- In Normal mode, the characteristics of internal loopback depend upon how loopback was initiated.

- a. From Host command, no Ethernet access is possible.

- b. From device powerup, certain types of MOP messages may be processed by the DELQA (that is; MOP boot if enabled by S4, Ethernet loop channel, and Request System ID).

- In DEQNA-lock mode, no Ethernet access is possible.

### 1.3.3.4 Remote Console Commands

When operating in Normal mode, the DELQA responds to the following MOP remote console commands:

- System Identification Request from another Ethernet station. The DELQA sends the current System ID parameters from shared RAM

- System ID Transmission is sent periodically to a Multi-cast Ethernet address

- Remote Trigger command from another Ethernet station. The DELQA verifies the request, and then causes the host system to reboot by negating BDCOK on the Q-Bus interface in order to simulate a powerup restart.

### **1.3.3.5 Ethernet Channel Loopback**

DELQA recognises Ethernet loopback test messages. The module checks to determine whether to forward or return the incoming message. Messages are received, decoded, and re-transmitted by DELQA independently of host software. Normal messages are passed through as usual.

# CHAPTER 2 FUNCTIONAL DESCRIPTION

## 2.1 SCOPE

This chapter describes the main operations of the DELQA module, and its system port interface with the Q-Bus. The sections are as follows:

# Section 2.2 MODULE OPERATIONS Section 2.3 SYSTEM PORT INTERFACE Section 2.4 NETWORK SUPPORT

# 2.2 MODULE OPERATIONS

The DELQA module transfers data between buffers in host memory and the Ethernet transceiver. The main operations are as follows:

- 1. Transfer of data between host memory buffers and shared RAM in the DELQA.

- 2. Conversion of data and status information between host format and that used in the DELQA module.

- 3. Arbitration of access requests on the backport bus.

- 4. Transfer of encapsulated data packets between shared RAM and the Ethernet connector.

- 5. DELQA module control.

The data is brought together at a higher level of protocol to form packets of between 60 and 1514 data bytes. The DELQA module calculates and appends a four byte CRC to transmit packets, and strips the CRC from receive packets. Therefore, the full length of a packet on the Ethernet is between 64 and 1518 bytes.

# 2.2.1 Q-Bus Transfers

The QIC is a dual-ported device: one set of data and address lines is connected to the Q-Bus; the other interfaces with the backport bus in the DELQA module. In the data DMA path, each port is double buffered, and each port is controlled by sequencer logic in the QIC.

The QIC supports DMA between the Q-Bus and shared RAM:

- 1. Block-mode or (non-block-mode) data DMA.

- 2. Non-block-mode control DMA.

These two types are described in the next sections.

### 2.2.1.1 Data DMA

The QIC can execute up to 16 words of block-mode DMA between Q-Bus system memory and shared RAM each time it acquires control of the Q-Bus. The transfer must consist of either read only instructions, or write only instructions.

When executing DMA transfers to block-mode memory, the QIC relinquishes the backport bus whenever:

- 1. The transfer reaches a 16 word boundary.

- 2. Another device is requesting the Q-Bus when the transfer reaches a 7 word boundary. This causes the QIC to relinquish the bus at the 8 word boundary.

### 2.2.1.2 Control DMA

The QIC can also handle up to four words of control DMA, using mixed read and write instructions to access BDLs. This is known as control DMA; it is used to transfer status information as well as to access descriptors, as follows:

- 1. Buffer Descriptor Fetch. This instruction acquires the Q-Bus, executes one non-block-mode write and three block-mode read instructions, then relinquishes the Q-Bus.

- 2. Chain Descriptor Fetch. As for Buffer Descriptor Fetch.

- 3. Store status. This instruction acquires the Q-Bus, executes two non-block-mode write instructions, then relinquishes the Q-Bus.

### 2.2.1.3 Non-block-mode DMA

When executing transfers to non-block-mode memory, the QIC relinquishes the Q-Bus whenever it reaches a four-word boundary.

### 2.2.1.4 Data and Status Conversion

The 68000 microprocessor handles:

- 1. Formatting of buffers for transmission.

- 2. Reformatting of packets received from the Ethernet.

- 3. Conversion of status information for both transmit and receive messages.

Figure 2-1 shows the data transfers involved in formatting the message data.

### 2.2.2 Backport Bus Arbitration

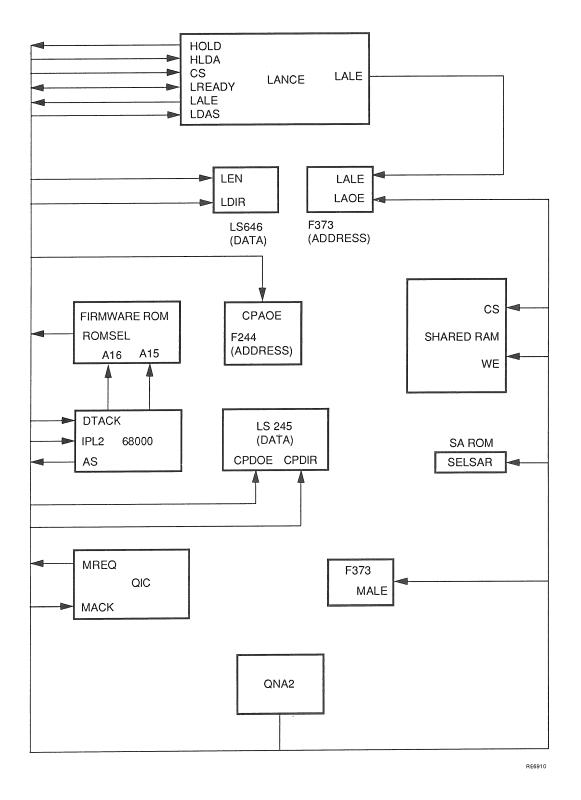

The QNA2 controls access to the backport bus on the DELQA module, arbitrating between access requests from the QIC, the 68000 microprocessor, and the LANCE. The QNA2 provides all the gating and the strobing signals necessary for these devices to access the shared RAM.

Figure 2–2 shows the control and gating signals that the QNA2 generates to control the backport bus.

### 2.2.3 Ethernet Transfers

Ethernet transfers are handled by the LANCE (Local Area Network Controller for Ethernet) in conjunction with the SIA (Serial Interface Adapter).

#### 2.2.3.1 Transmission

When the 68000 has translated a data frame into a packet suitable for transmission, the LANCE transfers it by DMA from the shared RAM to the SIA. The SIA Manchester encodes the data, and sends the packet using the Ethernet connector and bulkhead assembly to the Ethernet.

## 2.2.3.2 Reception

When the SIA detects activity on the Ethernet, it synchronises with the preamble of the incoming message. The SIA then decodes the data and transfers the packet to the LANCE. The LANCE filters the destination address. If the address on the incoming packet matches one of the addresses in module memory, the LANCE transfers the data by DMA to the RAM.

### 2.2.4 Master Module Control

The 68000 microprocessor executes the master control program for the DELQA module. The master control program is held as firmware in the ROM associated with the microprocessor on the 68000 bus, and executes the following functions:

- 1. Conversion of control and status information.

- 2. Initialisation of QIC and LANCE on powerup.

- 3. DELQA self-test on powerup or initiated by host.

- 4. Interrupt control.

The QNA2 contains the CSR (Control and Status Register), and the DELQA IR (Interrupt Register) for the DELQA module.

FUNCTIONAL DESCRIPTION

Figure 2–1 DELQA Data Path

Figure 2–2 Backport Control Functions

# 2.3 SYSTEM PORT INTERFACE

The DELQA is accessed through twelve registers which are mapped into the Input/Output page of Q-Bus address space in the host system. When it receives the valid address of one of the registers from the bus master, the DELQA responds as a bus slave.

### 2.3.1 Port Registers

The address mapping implemented by the QIC enables the host system to access the following internal registers in the DELQA:

### 1. Control and Status Register (CSR).

This is a one-word, read/write register held in the QNA2.

2. Vector Address Register (VAR).

This is a one-word, read/write register held in the shared RAM.

### 3. Receive BDL Start Address Register.

Transmit BDL Start Address Register (BDL SARs).

These are two-word, write-only registers that are maintained by the host in shared RAM.

### 4. Station Address ROM.

This is a set of six read only memory bytes (the lower bytes of the first six words in the DELQA space).

All the registers are word addressable only. The 68000 microprocessor can access these registers directly from the backport bus.

### 2.3.2 Memory Map

The host system can access the DELQA registers as a block of eight word addresses in the Input/Output page.

The base page address is selected by switch settings on the module. There are five switches on the DELQA board: S1 to S5. S1 selects the I/O base page address for the module, as listed in Table 2–1.

| S1     | Base Address | Unit    | Module         |  |

|--------|--------------|---------|----------------|--|

| CLOSED | 17774440     | DELQA 1 | DELQA or DEQNA |  |

| OPEN   | 17774460     | DELQA 2 | DELQA or DEQNA |  |

Table 2–1 DELQA Unit I/O Base Addresses

#### 2.3.3 Setup

The setup packet is the only mechanism, other than the DELQA control registers (CSR and VAR), by which the host software can send commands, status, and control functions to the DELQA module.

The setup packet can be used to initialise the following functions within the DELQA module.

- Multi-cast address or promiscuous filtering for address recognition

- Timeout value for the sanity timer

- Up to 14 sixbyte Ethernet addresses that the DELQA module is to recognise

- MOP configuration and control.

### 2.3.3.1 Setup Information

The setup packet contains three main groups of information which the host software can issue to the DELQA.

- 1. **Target address information** contains the Ethernet physical and Multi-cast addresses for which the DELQA is to receive messages.

- 2. **Control parameters** specify special reception modes (such as promiscuous or all Multi-cast) and sanity timer timeout values.

- 3. **MOP information** is used to read and change MOP parameters.

Setup packets may contain either one or two of these groups of information. A combination of the specified length of the setup packet and the value of the first byte of the setup packet buffer indicates which groups of information are present.

Table 2–2 explains all the possible combinations of information groups.

| Information Groups (Maximum 2)                 | Packet Length in Bytes<br>(Octal) | Value of Byte 1 |

|------------------------------------------------|-----------------------------------|-----------------|

| Target addresses (Group A or B) only           | 177 or less                       |                 |

| Target addresses and control parameters        | 200 to 377                        | Zero            |

| Target addresses and MOP Element Blocks (MEBs) | 400 exactly                       | Non-zero        |

Table 2–2

Setup Packet: Information Group Combinations

More than one setup packet may be issued. Each setup packet overwrites completely the setup area up to the 200 byte offset, but the MOP area between the 200 byte and 256 byte offset is overwritten only if the MOP flag is set at the start of the packet. Therefore, the only useful setup packet lengths are 177, between 200 and 377, or 400 (octal) bytes.

The host should maintain a copy of the current setup data, in order to recreate the correct 14 addresses (which cannot be read back from the DELQA) whenever the setup information is modified. Since the DELQA can only have two types of setup packet information per setup packet, the DELQA will accumulate all setup packet information, unless re-specified in a subsequent setup packet. Although setup packets may be repeatedly issued to the DELQA to modify parameters or to read internal values (that is, counters, system ID parameters), only one setup packet should be outstanding to the DELQA at a time.

## 2.3.4 Transmit Packet

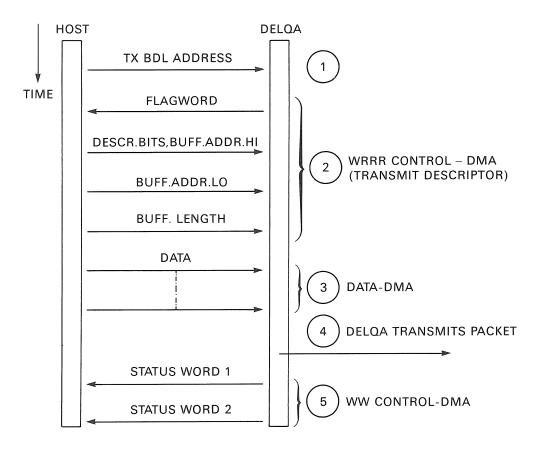

The host initiates transmission by first setting up a Transmit BDL, and then writing its address to the Transmit BDL Start Address register in the DELQA module.

The transmit buffers should be set up before attempting to set up the Transmit BDL. A transmit buffer can be up to 1514 bytes in length; this is the maximum number of bytes allowed in an Ethernet packet, excluding the four CRC bytes.

To complete the transmission, the DELQA executes the following steps:

1. Read the descriptor bits, and act on the buffer descriptor information as follows:

- 1. HOST WRITES TX BDL ADDRESS TO DELQA

- 2. DELQA FETCHES HOST DESCRIPTOR (WRITE-READ-READ-READ CONTROL-DMA)

- 3. DELQA DMAs DATA BUFFER FROM HOST

- 4. DELQA TRANSMITS PACKET

- 5. DELQA WRITES TRANSMIT STATUS TO HOST (WRITE-WRITE CONTROL-DMA)

- 6. THE DELQA WILL CONTINUE TO FETCH AND PROCESS HOST DESCRIPTORS UNTIL IT FINDS A DESCRIPTOR WITH THE VALID BIT CLEAR

RE4622

## Figure 2–3 Transmit Sequence (No Chaining)

- 2. If the Valid bit is set, the DELQA accesses the start address and buffer length fields, reads the relevant buffer, transfers the contents to its on-board shared RAM, updates the status words, and continues to the next descriptor.

- 3. If the Valid bit is clear, the DELQA marks the end of the current BDL. The DELQA ceases to access the BDL and its associated buffers.

- 4. If the chain bit is set, the DELQA links to the BDL, via the start address indicated in the buffer address field, and continues to the next descriptor.

5. If the End-of-Message bit D<13> is set, the DELQA generates the preamble and CRC for the message, and transmits the complete message packet over the Ethernet. Then it updates the status words in the latest buffer descriptor with the outcome of the transmission. (If CSR06 Interrupt Enable is set, the DELQA also generates a transmit interrupt request to indicate that a message has been transmitted.)

To achieve acceptable transmission rates, the DELQA executes control DMA (to set up the next data DMA transfer), data DMA, and data transmissions in parallel. The host software reads the status or contents of buffers only after the DELQA has returned the transmission status to the status word bits.

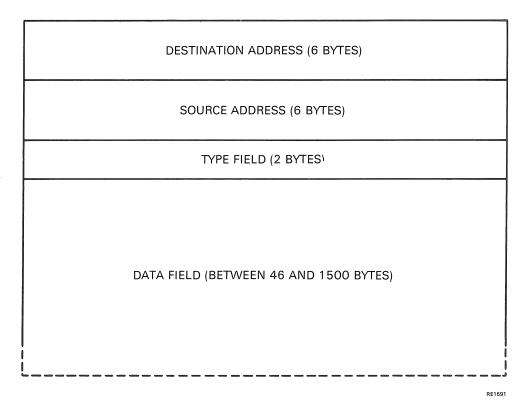

Figure 2–4 Ethernet Packet Format

# 2.3.5 Transmit Programming

The host software for packet transmission is responsible for the following actions.

- 1. Establish the location and contents of the transmit message buffers.

- 2. Initialize the start address and descriptor bits for each buffer descriptor in the Transmit BDL.

- 3. Write all the data fields within the transmit packet, including destination address (6 bytes), source address (6 bytes), type field (2 bytes), and data (between 46 and 1500 bytes).

The DELQA hardware supplies the CRC automatically.

- 4. Clear the Valid bit in the last descriptor of the BDL.

- 5. Set the Valid bit in all the previous descriptors of the BDL.

- 6. Write the start address of the BDL to the BDL Start Address register on-board the DELQA, to initiate transmissions.

### FUNCTIONAL DESCRIPTION

The host software should also provide an interrupt service routine to:

- Check the status and availability of transmit buffers

- Check CSR04 (Transmit List Invalid) to ensure that previous list processing has completed

- Check CSR02 (NXM) in case the interrupt was caused by a memory access error.

- Write 1 to clear CSR07 (Transmit Interrupt Request), if the bit is set.

### 2.3.6 Transmission Errors

In status word 1 of the last BDL entry for the transmitted message, the following status bits in the transmit buffer descriptor record transmission errors.

S1<09> Abort Excess collisions: there have been more than 15 attempts to transmit this packet. Check S1<12> in Transmit Status Word 1 in case the Ethernet circuit is faulty (see below).

S1<12> Loss Loss Loss of carrier during transmission, usually due to a short circuit on the Ethernet. However, Loss does not abort transmission, because it may be set during a normal collision recovery.

### NOTE In the DEQNA bits 11 and 12 of Transmit Status Word 1 have different functions for Carrier Status.

The Time Domain Reflectometry (TDR) counter (S2<09:00>) is a 10 MHz counter which is enabled by the DELQA when a carrier signal is detected, and disabled when the carrier stops or a collision is detected. The contents of the TDR counter are valid only when Abort (S1<09>) is set, and may be used as a relative measure of the distance through the network between the module and the supposed fault or collision.

#### 2.3.7 Receive Packet

The host initiates reception by first setting up a Receive BDL, and then writing its start address to the DELQA module.

To complete the receive process in response to activity on the Ethernet, the DELQA executes the following steps.

- 1. Read the descriptor bits, and act on the buffer status as follows.

- If the Valid bit is cleared, it marks the end of the current BDL. The DELQA ceases to access the BDL and its associated buffers.

- If the Chain bit is set, the DELQA links to the BDL whose start address is indicated in the buffer address field, and continues from step 2.

- If the Valid bit is set, the DELQA accesses the start address and buffer length fields, reads the next part of the incoming message into the indicated buffer from its on-board shared RAM, and continues from step 2.

- 2. If the message ends, the DELQA terminates reception, and updates the status words in the last buffer descriptor used. (If CSR06 is set, the DELQA also generates a receive interrupt request to indicate that a message has been received.)

### 2.3.8 Receive Programming

The host software for packet reception is responsible for the following actions.

1. Establish the location and contents of the receive message buffers.

Sufficient receive buffers should be allocated for at least one packet of the maximum expected length, in order to ensure that a receive interrupt request is generated before the next incoming message arrives.

## NOTE No interrupt is generated if there are not enough valid receive buffers in the Receive BDL to accommodate a complete packet.

- 2. Initialize the start address and descriptor bits for each buffer descriptor in the Receive BDL.

- 3. Initialize Status Word 2 of all the descriptors in the Receive BDL with unequal high and low bytes. (The DELQA makes the high and low bytes both equal to the received byte length, to indicate when the receive data is valid.)

- 4. Clear the Valid bit of the last BD in the BDL. Set the Valid bit in all BDs in the BDL except the last BD.

- 5. Set CSR00 (Receiver Enable) to enable Ethernet packet reception.

- 6. Write the start address of the BDL to the BDL Start Address register on-board the DELQA, to initiate reception.

The host software should provide an interrupt service routine to:

- Check the status and availability of receive buffers

- Check CSR05 (Receive List invalid) to ensure that previous list processing has completed.

- Write 1 to clear CSR15 (Receive Interrupt Request) if this bit is set.

- Check CSR02 (NXM) in case the interrupt was caused by a memory access error

### 2.4 NETWORK SUPPORT

In Normal mode, the DELQA is capable of implementing the following Ethernet MOP functions (a subset of DECnet operations) without host intervention:

- 1. Respond to Trigger Instruction to re-boot local system.

- 2. Loopback assistance.

- 3. Transmit System ID.

- 4. Respond to Request System ID.

In Normal mode, the DELQA processes the following Link-layer Service Access Point (LSAP) messages when used on an IEEE 802.3 local area network:

- 1. NULL TEST (Loopback).

- 2. NULL XID (Transmit ID).

### 2.4.1 Remote Trigger Instruction

The Trigger instruction enables a remote node on the Ethernet to request a system reboot.

When it recognises a Trigger instruction from another node, the DELQA module:

- 1. Decodes the instruction.

- 2. Validates its verification code (if programmed to do so by a setup packet from host software).

- 3. If the instruction requests a reboot of the host system, the QIC negates the signal BDCOK on the Q-Bus in order to force a system reboot.

- 4. Finally, host software must re-initialise the verification code.

The DELQA module checks:

- 1. Whether verification is required.

- 2. COMM BOOT or SYSTEM BOOT requested.

The Remote Boot option is enabled with option switch S4 open and mode switch S3 closed.

### 2.4.2 Loopback Assistance

Loopback messages can be transmitted to the DELQA module over the Ethernet to verify the connection. These are node-to-node connections at the lowest levels of protocol, and do not involve host software at either end. This facility is used by DECnet Network Management software to run diagnostic tools from a remote node on the Ethernet.

### 2.4.3 Transmit System ID

Identification messages enable certain DECnet and Network Interconnect Exerciser (NIE) utilities to map the nodes on an Ethernet network.

On powerup, the DELQA module automatically transmits its system identification over the Ethernet. The identification message contains at least the device type at the node, and its Ethernet address; host software may use a setup packet to add more information to the message. The message is broadcast every 10 minutes +/-2 minutes 11 seconds.

### 2.4.4 Request System ID

On powerup, the DELQA module in Normal mode recognises Request System Identification messages on the Ethernet. In response, the module transmits a copy of its current System Identification message.

# 2.4.5 IEEE 802.3 Network Support: NULL Link-layer Service Access Points

In Normal mode DELQA implements IEEE 802.2 Logical Link control messages when they are received on a NULL Link-layer Service Access Point (LSAP) within an IEEE 802.3 standard local area network.

These messages can be used to interrogate and test many link layer service points per node. Therefore, IEEE 802.2 Logical Link control messages which are received on a non-NULL LSAP are passed on to the host system as normal datagrams.

The messages supported are:

# 1. TEST Message

The IEEE 802.2 TEST message is similar in function to the Loopback Message on Ethernet networks.

# 2. XID (Transmit ID) Message

The IEEE 802.2 XID (Transmit ID) message is similar in function to the MOP Remote Console Request System ID Messages on an Ethernet network.

DELQA does not broadcast IEEE 802.2 XID messages automatically as it does with MOP System IDs since it is not required by the IEEE 802.2 protocols.

For details of this message format and protocol, refer to the ANSI/IEEE Draft International Standard 802.2 Logical Link Control.

# 2.4.6 Datalink Counters

The DELQA maintains in shared RAM a set of datalink counters of bytes and packets transferred successfully and in error. A setup packet provides host software with a mechanism for reading these counters locally.

$e_{\rm D}$

# CHAPTER 3 TECHNICAL DESCRIPTION

### 3.1 SCOPE

This chapter describes how the components of the DELQA module work together on the backport bus. The sections are as follows:

Section 3.2 ARCHITECTURE Section 3.3 Q-BUS INTERFACE Section 3.4 ETHERNET INTERFACE Section 3.5 BACKPORT BUS Section 3.6 MODULE CONTROL

# **3.2 ARCHITECTURE**

### 3.2.1 Overview

The DELQA module is built around a backport bus which passes data between the QIC, shared RAM, and the LANCE. A 68000 microprocessor handles formatting, module control, and initialization. The QIC, the QNA2, and the 68000 microprocessor are surface-mounted devices.

The QIC handles the interface with the Q-Bus protocols, and the LANCE handles the interface with the Ethernet protocols. Shared RAM is used as an intermediate buffer store.

The QNA2 arbitrates between the 68000, the LANCE and the QIC, for access to the backport bus. The QNA2 provides all the control signals for successful data transfer The QNA2 contains the DELQA control and status register (CSR) and the Interrupt Register(IR).

Firmware ROM contains both the master control program for the DELQA module and 4Kbytes of PDP-11 boot/diagnostic code for the Q-Bus system. The firmware ROM can be addressed only by the 68000 microprocessor.

The Station Address (SA) ROM is preprogrammed with the 48-bit default physical address of the DELQA module in the Ethernet LAN.

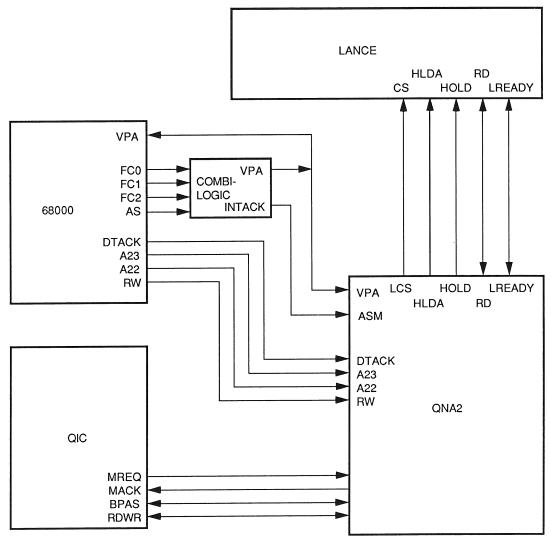

Figure 3–1 shows the principal control signal paths through the DELQA module.

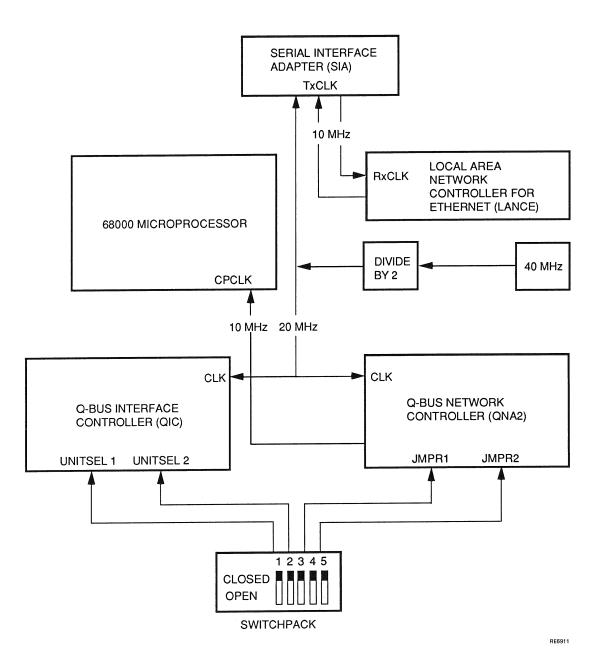

## 3.2.2 Selection Switches

The DELQA has five manual selection switches: S1 to S5. These are part of a switchpack on the DELQA board. Table 3–1 describes how the switches are used. Figure 3–2 shows the selection switch signals.

RE1735

Figure 3–1 QNA2 Control Signals

# Table 3–1 DELQA Module: Switch Options

**S**1

Select Module Address. This switch selects the base address of the module on the Q-Bus.

| S1        | Base Address | Unit    | Module         |

|-----------|--------------|---------|----------------|

| CLOSED    | 17774440     | DELQA 1 | DELQA or DEQNA |

| OPEN      | 17774460     | DELQA 2 | DELQA or DEQNA |

| <u>S2</u> | NOT USED     |         |                |

S3/S4 DELQA Mode and Options. Switch S3 selects whether Normal mode or DEQNA-lock mode is enabled.

When switch S3 is closed, Normal mode is enabled, and host software can switch the module between Normal mode and DEQNA-lock mode. When Normal mode is selected using switch S3, the DELQA supports MOP operations, but the MOP operation for Remote BOOT can be enabled by setting switch S4 to open.

When switch S3 is open, DEQNA-lock mode is enabled. In this mode MOP operations are not supported, and switch S4 determines whether the sanity timer is enabled automatically on powerup.

| Switch |           | Normal   | DEQNA-     | Remote  | Other MOP | Auto Sanity     |         |

|--------|-----------|----------|------------|---------|-----------|-----------------|---------|

| S3     | <b>S4</b> |          | lock       | BOOT    | functions | Timer           |         |

| CLOSED | CLOSED    | enabled  |            |         | enabled   |                 |         |

| CLOSED | OPEN      | enabled  |            | enabled | enabled   |                 |         |

| OPEN   | CLOSED    |          | enabled    |         |           |                 |         |

| OPEN   | OPEN      |          | enabled    |         |           | enabled         |         |

| S5     | NOT US    | ED Reser | veal for P | ESAA-T  | Elored    | anable Turbo ma | od<br>" |

### 3.2.3 Clocks

The clock signals in the DELQA module run from a 40MHz oscillator located at the Ethernet end of the board.

The main clock signal is divided by two to produce two antiphase 20MHz clock signals. One of these is fed into the X1 input of the SIA, where it is used to generate the 10MHz Transmit Clock signal to the LANCE. The other clock is fed to the QIC and the QNA2, so that these two chips can operate synchronously at 20MHz.

The QNA2, as bus controller, generates the 10MHz clock that drives the 68000 microprocessor.

Figure 3–2 shows the main clock signals.

Figure 3–2 DELQA Clocks and Selection Switches

### **3.2.4 POWER LOADING**

| Function            | Typical       | Typical     | Maximum      | Backplane                           |

|---------------------|---------------|-------------|--------------|-------------------------------------|

|                     | Voltage       | Current     | Current      | Pins                                |

| TTL level           | + 5V +/-0.25V | 2.4A +/-10% | 2.7A         | BV1, AA2, BA2                       |

| TTL ground          |               |             |              | AJ1, AM1, AT1 BJ1,<br>BM1, AC2, BC2 |

| ransceiver<br>ower  | +12V +/-0.60V | 0.5A +/-10% | 1.5A (Note ) | BD2                                 |

| ransceiver<br>round |               |             |              | BT1                                 |

Table 3–2 DELQA and transceiver power requirements

NOTE

At powerup, the surge current of the transceiver can cause certain power supplies to current limit or even to fail. These failures can also be caused during powered-up connect. There is no surge protection on the DELQA module. The bulkhead assembly must incorporate a 1.5A/250V slo-blo fuse.

Two fuses provide protection for the DELQA module and associated equipment:

- A 1.5 A/250 V slo-blo <sup>™</sup> 1.25 inch by 0.25 inch glass fuse (order number 90-07213) protects the transceiver and its associated external wiring. The fuse may be replaced with another fuse of the same type, a Littlefuse<sup>™</sup> type 31301.5, a BEL FUSE<sup>™</sup> type 3SB1.5, or an equivalent. The 1.25 inch (3.8 cm) fuse holder (order number 12-22255-03) is located in the bulkhead assembly (not on the DELQA board).

- A 5.0 A/125 V axial lead picofuse (order number 12-05747-00) protects the DELQA module and internal wiring. The picofuse is fitted on the DELQA board near the bulkhead cable connector, it looks like a resistor and is soldered to the board in the same way. It should be replaced only by trained personnel.

## **3.3 Q-BUS INTERFACE**

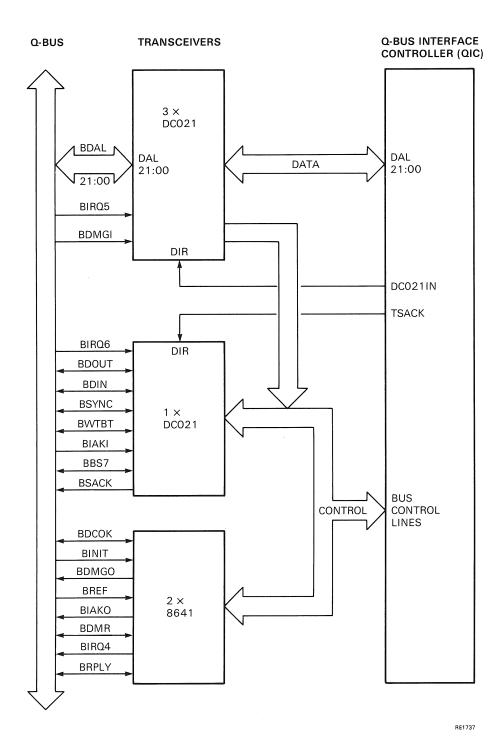

### 3.3.1 Overview

The QIC (Q-Bus Interface Controller) handles the Q-Bus interface protocols. To provide a complete Q-Bus interface, four octal bus transceivers and two sets of quad transceivers are connected between the Q-Bus and the QIC. The QIC shares a 20MHz clock input with the QNA2.

The QIC provides complete Q-Bus slave control logic for host access to the DELQA I/O registers.

### **TECHNICAL DESCRIPTION**

On the Q-Bus side, the QIC supports control DMA and data DMA, using block-mode to achieve the highest possible speeds. The QIC generates two control signals to change the direction of the DC021 transceivers:

- 1. DC012IN controls the direction of transfer of the three DC021 transceivers connected to the Q-Bus data/address lines, BDAL<21:0>.

- 2. TSACK (Transmit DMA Selection Acknowledge) controls the direction of transfer for the fourth DC021 transceiver, which carries the bus control signals that enable the QIC to act as Q-Bus master for DMA.

On the backport side, the QIC supports DMA transfers to and from shared RAM along 16 data/address lines. The QIC is controlled through a series of registers that are accessed by the 68000 microprocessor.

Figure 3–3 shows the Q-Bus interface. Table 3–3 summarizes the signals and pinouts.

Figure 3–3 Q-Bus Interface (hardware)

# **TECHNICAL DESCRIPTION**

| Table 3-3 | Q-bus Connecto | r Pins and Signals |     |           |                    |

|-----------|----------------|--------------------|-----|-----------|--------------------|

| Pin       | Signal         | Description        | Pin | Signal    | Description        |

| AA1       | BIRQ5          | Interrupt          | AA2 | +5V       |                    |

| AB1       | BIRQ6          | lines              | AB2 |           |                    |

| AC1       | BDAL16 L       | Data/Control       | AC2 | GND       |                    |

| AD1       | BDAL17 L       | lines              | AD2 |           |                    |

| AE1       |                |                    | AE2 | BDOUT L   |                    |

| AF1       |                |                    | AF2 | BRPLY L   | Bus                |

| AH1       |                |                    | AH2 | BDIN L    | Control            |

| AJ1       | GND            |                    | AJ2 | BSYNC L   | lines              |

| AK1       |                |                    | AK2 | BWTBT L   |                    |

| AL1       |                |                    | AL2 | BIRQ4 L   |                    |

| AM1       | GND            |                    | AM2 | BIAKI L   | Interrupt<br>lines |

| AN1       | BDMR L         | DMA Control        | AN2 | BIAKO L   |                    |

| AP1       | BHALT L        |                    | AP2 | BBS7 L    | Bus Control        |

| AR1       | BREF L         | Q-Bus control      | AR2 | BDMGI L   | DMA                |

| AS1       |                |                    | AS2 | BDMGO L ) | Control            |

| AT1       | GND            | FUSE H sink        | AT2 | BINIT L   | Bus Control        |

| AU1       |                |                    | AU2 | BDAL0 L   | Data/Address       |

| AV1       |                |                    | AV2 | BDAL1 L   | lines              |

| BA1       | BDCOK H        | DC Power OK        | BA2 | +5V       |                    |

| BB1       | ВРОК           | Power OK           | BB2 |           |                    |

| BC1       | BDAL18 L       | [Data/             | BC2 | GND       |                    |

|           |                |                    |     |           |                    |

Table 3–3

Q-Bus Connector Pins and Signals

| Pin | Signal   | Description        | Pin | Signal         | Description      |

|-----|----------|--------------------|-----|----------------|------------------|

| BD1 | BDAL19 L | [Address           | BD2 | +12V<br>(XCVR) | Transceiver      |

| BE1 | BDAL20 L | [lines             | BE2 | BDAL2 L        |                  |

| BF1 | BDAL21 L |                    | BF2 | BDAL3 L        | Data/<br>Address |

| BH1 |          |                    | BH2 | BDAL4 L        | lines            |

| BJ1 | GND      |                    | BJ2 | BDAL5 L        |                  |

| BK1 |          |                    | BK2 | BDAL6 L        | $\mathbf{i}$     |

| BL1 |          |                    | BL2 | BDAL7 L        |                  |

| BM1 | GND      |                    | BM2 | BDAL8 L        |                  |

| BN1 | BSACK L  | DMA Control        | BN2 | BDAL9 L        |                  |

| BP1 | BIRQ7 L  | Interrupt          | BP2 | BDAL10 L       | Data/<br>Address |

| BR1 |          |                    | BR2 | BDAL11 L       | lines            |

| BS1 |          |                    | BS2 | BDAL12 L       |                  |

| BT1 | GND      | (XCVR) Transceiver | BT2 | BDAL13 L       |                  |

| BU1 |          |                    | BU2 | BDAL14 L       |                  |

| BV1 | +5V      |                    | BV2 | BDAL15 L       | /                |

Table 3–3 (Cont.) Q-Bus Connector Pins and Signals

### Notes:

- 1. (XCVR) indicates isolated power connections through the DELQA to the Ethernet transceiver cable connector.

- 2. **BC2** is tied to the ground plane of the module and serves as a pull-down sink through approximately 14K Ohms for the Ethernet Connector signal FUSE H.

The QIC is reset from the QBUS when BDCOK is regated and BINITL is asserted. The assersion of BINITL also causes a reset sequence to the remainder of the DELQA module. On the falling edge of RINITH a 2000ns pulse resets the QNA2 and a 150ms pulse resets the 68000 and the LANCE.

#### 3.3.2 Initialization

The backport is reset when the Q-Bus RINITH signal transitions from 1 to 0. The backport is also reset when CSR Bit 01 (software reset) is transitioned from 1 to 0.

Initialization code will cause the 68000 to examine the reason for the backport reset. Possible reset causes are:

|                      | DCOK | RINITH | TDCOK |

|----------------------|------|--------|-------|

| Powerup              | 1    | X      | 0     |

| Q-Bus Init           | 0    | 1      | 0     |

| DELQA Initiated boot | Х    | X      | 1     |

| Software Reset       | 0    | 0      | 0     |

Table 3-4Backport Reset

The bits DCOK, RINITH and TDCOK are contained in the QIC registers.

The QIC can initiate a reboot of its Q-BUS host by negating TDCOK. This will occur whenever the TDCOK bit in the QIC Mode Register is toggled to 1.

### **3.3.3 DMA Functions**

The QIC can request, accept, and relinquish ownership of the Q-Bus, for both data DMA and control DMA accesses to the host database.

There are separate addressing and buffering mechanisms for data DMA and control DMA. This allows control DMA requests to take priority over data transfers in progress; when the control DMA is complete, the data transfer is restarted from where it left off.

## 3.3.3.1 Data DMA

During data DMA transfers, the 21-bit Q-Bus address counter is connected to DAL<21:01>, with DAL<00> held at zero. During a transfer, data transferred between the Q-Bus and the backport bus is double-buffered within the QIC. The 16-bit backport address counter is connected to BPDAL<00,15:01> to support transfers of up to 128 Kbytes.

Double buffering inside the QIC allows for the signal setup, hold and access times of Q-Bus and backport bus, and for high speed, pipelined transfers through the chip.

If control DMA is attempted during data DMA, the QIC:

- 1. Relinquishes control of the Q-Bus

- 2. Requests control for a control DMA transfer (non-block-mode).

- 3. Completes the control DMA transfer, and relinquishes control of the bus.

- 4. Requests control of the bus in order to resume data DMA transfers.

The QIC recognizes 16-word boundaries because there is no RREF (Refresh) from the bus slave.

### 3.3.3.2 CONTROL DMA

During Control DMA transfers, the 21-bit Q-BUS address counter is connected to DAL<21:01>, with DAL<00> held at zero. Control information is passed along a latched path through the QIC using single byte or single word transfers.

This is the same path that is used when the host accesses the QIC as bus slave. If the host requests an I/O page access at the same time as the 68000 requests a control DMA transfer, the host request takes priority.

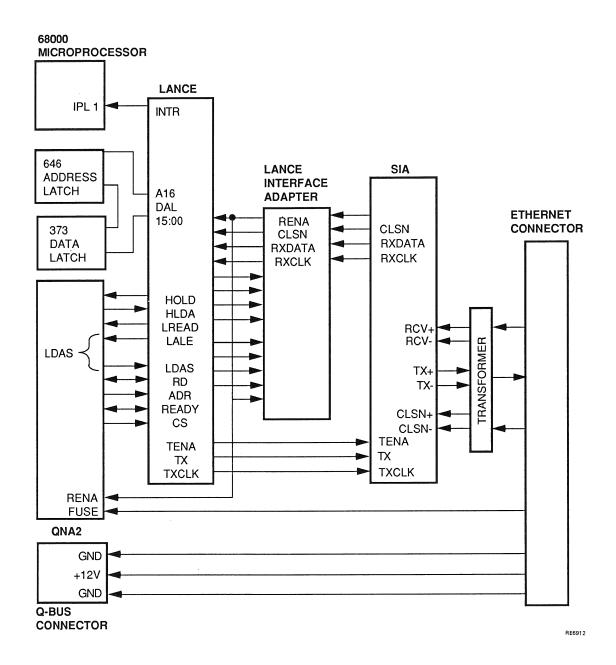

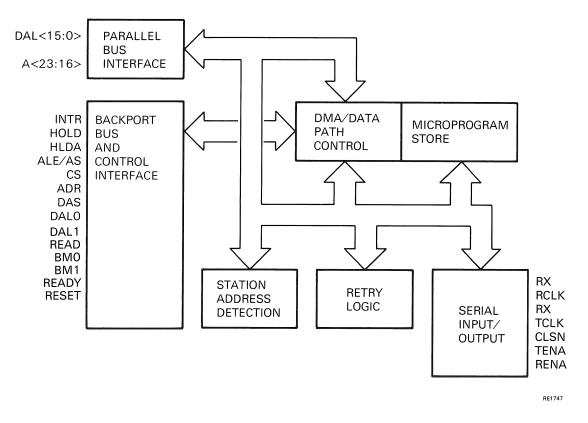

### **3.4 ETHERNET INTERFACE**

### 3.4.1 Overview

The LANCE (Local Area Network Controller for Ethernet) and the SIA (Serial Interface Adapter) operate together to provide a complete interface from the backport bus to the Ethernet. To provide fault isolation required by IEEE 802.3, a transformer is inserted in the path between the 51A and the transceiver cable connector.

On the backport side of the LANCE, two bus transceivers isolate the LANCE from the backport data bus, and two latches isolate the LANCE from the backport address bus (arbitrated by the QNA2). The SIA takes a 20MHz clock input from the DELQA clock, and uses it to generate a 10MHz clock, which it also passes to the LANCE for synchronization.

The SIA provides Manchester encoding of data for transmission, and decodes received data. The LANCE supplies and checks the 32-bit CRC that is appended to all Ethernet packets.

During transmission the LANCE polls the transmit buffer descriptor list for buffer descriptors that it owns. When it finds an entry that it owns it DMAs the data from shared RAM into internal FIFO. It prefixes the 64-bit preamble to the packet and sends the data to the SIA as a serial bit stream. When the packet has been transmitted, or if an error occurs, the LANCE will update the relevant buffer descriptor.

During reception, the SIA detects and synchronizes to the incoming bit stream from the Ethernet. The LANCE checks the destination address contained in the package against its list of addresses. If it finds a match, the LANCE will DMA the data from its internal FIFO in to buffer memory. When the reception is completed, or if an error occurs, the LANCE will update the relevant entry in the receiver buffer descriptor list.

The SIA communicates only with the LANCE and the Ethernet interface. The LANCE acts as backport bus master for all data transfers, and as bus slave for the 68000 microprocessor to program its internal registers. It communicates with the QNA2 in order to access the backport bus and transfer data to and from shared RAM.

Figure 3–4 shows the Ethernet interface.

### 3.4.2 Initialization

The LANCE initializes itself on request from the 68000. The 68000 writes an Initialization block from 68000 ROM to shared RAM, and programs the LANCE CSR to locate the block. The LANCE reads the block to determine mode of operation, address recognition parameters, and buffer descriptor ring pointers.

### **3.4.2.1 Destination Addresses**

The LANCE can be programmed to match three different types of address from an incoming packet, as follows:

## 1. **48-bit destination address**

This is programmed as the unique address of the DELQA. Usually, the initialization block is programmed to include the physical address from the SA (Station Address) PROM, but DECnet software reprograms the address in order to reflect the current DECnet node number. (SA ROM still stores a permanent record of the default physical address.)

## 2. Multicast address filter

This is programmed using a logical address mask in the initialization block.

### 3. **Promiscuous mode**

In this mode the LANCE is programmed to accept all incoming packets. This mode is set using the mode register in the initialization block.

Figure 3–4 Ethernet Interface (hardware)

### 3.4.2.2 LANCE Memory Structures

There are three memory structures accessed by the LANCE:

- 1. **Initialization Block** (12 words) contains the operating parameters for the device: mode of operation; physical address; logical address mask; location of receive and transmit descriptor rings; number of entries in receive and transmit descriptor rings.

- 2. Receive Message Descriptor Rings (rMDR) and Transmit Buffer Descriptor Rings (tMDR). Two ring structures, one each for incoming and outgoing packets. Each entry is four words long, comprising: data buffer address, length, and status.

- 3. Data buffers for packet buffering.

These memory structures are set up in shared RAM by the 68000 microprocessor. The 68000 then writes the Initialization Block Start Address (IADR) to CSR1 and CSR2 in the LANCE, and the LANCE loads itself with the information contained in the Initialization Block.

Refer to Appendix A for details.

### 3.4.3 Transmission

The LANCE polls the transmit Message Descriptor Ring (MDR) automatically every 1.6 milliseconds whenever it is not searching out receive buffers for incoming packets.

The polling consists of searching the status words of the transmit Message Descriptor Ring (MDR) for a buffer descriptor marked as OWNed by the LANCE. Then the LANCE executes two more read operations to collect the transmit buffer address and its buffer byte count.

Where the buffers are chained, the LANCE looks ahead once during the current transfer in order to find the next buffer. If it does not OWN the next MDR entry, it sets the UFLO and BUFF error bits in CSR0. When it empties a buffer, the LANCE clears the OWN status bit for that buffer.

The interpacket gap time on the Ethernet is a minimum of 9.6 microseconds, starting on the falling edge of the SIA signal RENA.

In transmit mode, the host supplies the destination address, source address, and length field. The LANCE appends preamble, sync, and CRC to the frame.

If an error occurs, the current buffer transmission is abandoned, causing an interrupt to the 68000 microprocessor.

### 3.4.4 Reception

The polling consists of searching the status words of the receive Message Descriptor Ring (MDR) for a buffer descriptor marked as OWNed by the LANCE. Then the LANCE executes two more read operations to collect the receive buffer address and its buffer byte count.

If the LANCE OWNs a receive buffer when an incoming packet arrives, it looks ahead once between transfers to find the next OWN buffer. This involves three separate one-word read operations. If the buffers for incoming packet need to be chained, and the LANCE has not found the next buffer, it sets the BUFF and/or the OFLO bits in CSR0.

When an incoming packet arrives, the LANCE checks to see if it owns a receive buffer. If not it will poll the receive ring once for a buffer. If it does not own the buffer it will set the MISS bit in CSR0, and will not poll the receive ring until the packet ends.

The interpacket gap time on the Ethernet is a minimum of 9.6 microseconds, starting on the falling edge of the SIA signal RENA. If a new packet arrives within 4.1 microseconds of this edge, it can only be received correctly if at least eight bits of the preamble are left.

In receive mode, the LANCE strips the preamble and sync bits, and transfers data and CRC to shared RAM. The LANCE discards runt packets of less than 64 bytes (which are usually due to a collision).

The LANCE can handle up to seven dribbling bits when a received packet terminates, so long as the CRC accounts for them. If there are both dribbling bits and a CRC error, then a Framing Error is flagged in the Receive Message Descriptor.

If an error occurs, the current buffer reception is abandoned, causing an interrupt to the 68000 microprocessor.

#### 3.4.5 Collision Detection

The SIA reports a collision on the Ethernet to the LANCE by asserting CLSN. It leaves TENA asserted for between 32 and 40 additional bit times in order to transmit the collision jam signal pattern. The jam pattern is any pattern other than the CRC bytes. The LANCE completes the preamble or the current byte transmission before starting to transmit the jam pattern.

The LANCE makes up to 16 retransmission attempts before reporting a collision.

If CLSN is asserted during reception, the reception is terminated at once, either because of an address mismatch with an internal pointer, or as a runt packet. A late collision (occurring after 64 byte times, or 51.2 milliseconds) is not recognized in receive mode.

### 3.4.6 Buffering

The LANCE operates two types of DMA transfer to shared RAM: single word DMA, and burst mode DMA.

Single word DMA is used to access the Transmit and Receive Message Descriptor Rings (MDRs), and to read the initialization block. Burst mode is used to transfer Transmit or Receive messages in eight consecutive reads or writes.

Bus cycles are a minimum of 600 nanoseconds. Burst mode transfers are separated by a gap of at least 700 nanoseconds.

Separate MDRs describe transmit and receive operations. Up to 128 tasks may be queued upon each MDR.

Each message descriptor entry is four words long. Each descriptor in a ring is marked as OWNed by either the LANCE or the host (the 68000 microprocessor). The status of a descriptor can only be changed while the descriptor is OWNed, and ownership can only be relinquished, never taken.

The location of the descriptor rings is programmed in the initialization block.

### **3.5 BACKPORT BUS**

### 3.5.1 Overview

The QNA2 (Q-Bus Network Arbitrator) arbitrates requests for access to the backport bus. It then implements the control function appropriate to the access request that it has granted. Priority of access is in the order QIC, 68000, LANCE.

The QNA2 input FUSE monitors the power indicator from the H4xxx Ethernet transceiver. The QNA2 also drives the on-board LEDs that indicate: powerup, loopback testing, citizenship (CQ) tests, and normal operation.

Table 3–5 shows how the memory space on the backport bus is used.

| IC         | Word address<br>Octal | Binary                          |

|------------|-----------------------|---------------------------------|

| LANCE RDP  | 70 000 000            | 111 000 000 000 000 000 000 000 |

| LANCE RAP  | 60 000 000            | 110 000 000 000 000 000 000 000 |

| QIC Base   | 40 377 440            | 100 000 011 111 111 100 100 000 |

| QNA2 CSR   | 20 177 416            | 010 000 001 111 111 100 001 110 |

| QNA2 IR    | 20 177 436            | 010 000 001 111 111 100 011 110 |

| SA ROM     | 20 177 400            | 010 000 001 111 111 100 000 000 |

| Shared RAM | 20 000 000            | 010 000 000 000 000 000 000 000 |

| 68000 ROM  | 00 000 000            | 000 000 000 000 000 000 000 000 |

Table 3–5 68000 Backport Address Map

## **3.5.2 Backport Interface Timing**

The 20 MHz CLOCK input to the QNA2 is shared with the QIC. This ensures the synchronous operation between the QNA2 and the QIC. The QNA2 further divides this 20MHz clock to produce a 10MHz clock for the 68000 microprocessor.