# DEC LANcontroller 200 Installation Guide

Order Number: EK-DEBNI-IN-002

The DEC LANcontroller 200 adapter (also known as the DEBNI controller) is an Ethernet/802 controller for systems that have a VAXBI bus. This guide is intended for use by DIGITAL customer service representatives and self-maintenance customers who install the DEC LANcontroller 200.

digital equipment corporation maynard, massachusetts

#### First Printing, May 1969 Rovised, April 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1989, 1990 by Digital Equipment Corporation.

All Rights Received. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEBNA             | PDP    | <b>VAXcluster</b> |

|-------------------|--------|-------------------|

| DEC               | ULTRIX | VAXELN            |

| DEC LANcontroller | UNIBUS | VMS               |

| DECnet            | VAX    | XMI               |

| DECUS             | VAXBI  | da galtall        |

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

| Contents |        |                                                                                                                           |                       |  |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

|          | PREFA  | ACE                                                                                                                       | vii                   |  |

| CHAP     | TER 1  | INTRODUCTION                                                                                                              | <b>5-1</b>            |  |

|          | 1.1    | BASIC FUNCTIONS                                                                                                           | 1–1                   |  |

|          | 1.2    | PHYSICAL DESCRIPTION                                                                                                      | 1–4                   |  |

| СНАР     | TER 2  | INSTALLATION                                                                                                              | 2–1                   |  |

|          | 2.1    | INSTALLATION                                                                                                              | 2–1                   |  |

|          | 2.2    | INSTALLATION VERIFICATION PROCEDURE                                                                                       | 2–4                   |  |

|          | 2.3    | INTERNAL ETHERNET CABLE                                                                                                   | 2-6                   |  |

|          | 2.4    | FIRMWARE CONSOLE-ENABLE JUMPER                                                                                            | 2–8                   |  |

|          | 2.5    | REMOVAL                                                                                                                   | 2-9                   |  |

| CHAF     | PTER 3 | POWER-UP SELF-TEST                                                                                                        | 3–1                   |  |

|          | 3.1    | HOW TO RUN SELF-TEST                                                                                                      | 3–1                   |  |

|          | 3.2    | REPORTING SELF-TEST RESULTS  3.2.1 Self-Test Results in LEDs  3.2.2 Self-Test Results in the Power-Up Diagnostic Register | 3-2<br>_ 3-3<br>_ 3-3 |  |

|          | 3.3    | INTERPRETING TEST RESULTS                                                                                                 | 3_3                   |  |

#### Contents

|       | 3.4    | TESTED COMPONENTS                                                                                                                               | 3-4                               |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|       | 3.5    | UNTESTED COMPONENTS AND FUNCTIONS                                                                                                               | 3–5                               |

| APPE  | NDIX A | ENVIRONMENTAL REQUIREMENTS                                                                                                                      | A-1                               |

| APPEI | NDIX B | REGISTERS  DEVICE REGISTER (DTYPE)  VAXBI CONTROL AND STATUS REGISTER (VAXBICSR)  BUS ERROR REGISTER (BER)  POWER-UP DIAGNOSTIC REGISTER (XPUD) | B-1<br>B-3<br>B-5<br>B-10<br>B-17 |

| APPE  | NDIX C | BOOTSTRAPPING WITH THE DEBNI                                                                                                                    | C-1                               |

|       | C.1    | NETWORK BOOTING                                                                                                                                 | C-1                               |

|       | C.2    | INVOLUNTARY BOOTING                                                                                                                             | C-2                               |

| APPE  | NDIX D | HOW TO READ THE DEBNI ETHERNET ADDRESS                                                                                                          | <b>D</b> –1                       |

|       | D.1    | SYSTEMS WITH DECNET                                                                                                                             | <b>D</b> -1                       |

|       | D.2    | VAX 6XXX SYSTEM                                                                                                                                 | D-1                               |

| D.3   |        | VAX 62XX/83XX SYSTEMS                                                                                                                           | D-2                               |

|       | D.4    | VAX 85XX/87XX/88XX SYSTEMS                                                                                                                      | D<                                |

#### Contents

| APPENDIX E | HOW TO UPGRADE A DEBNA MODULE TO A DEBNI<br>MODULE   | E-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDEX      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FIGURES    |                                                      | and the transfer of the state o |

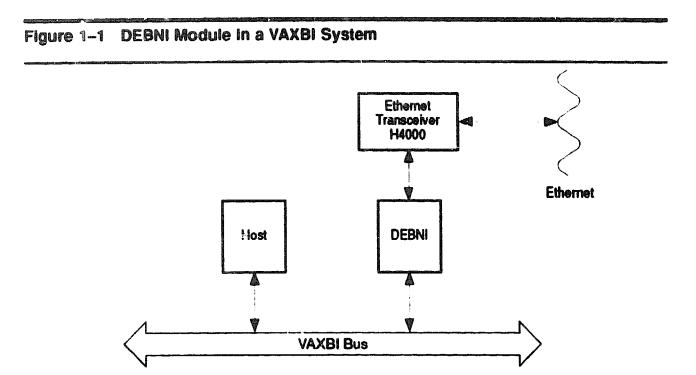

| 1-1        | DEBNI Module in a VAXBI System                       | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

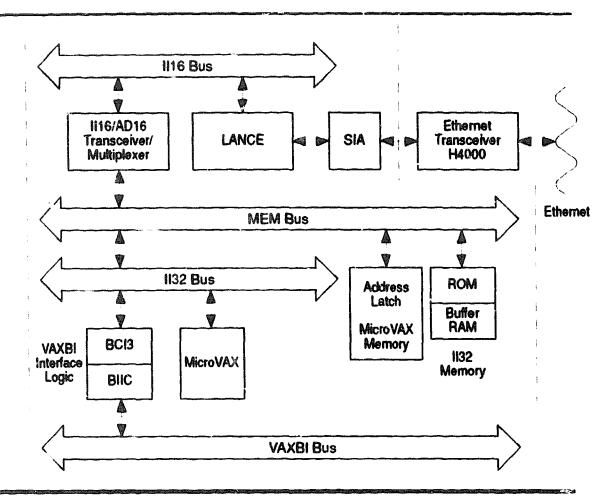

| 1–2        | DEBNI Block Diagram                                  | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

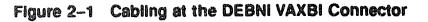

| 2–1        | Cabling at the DEBNI VAXBI Connector                 | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

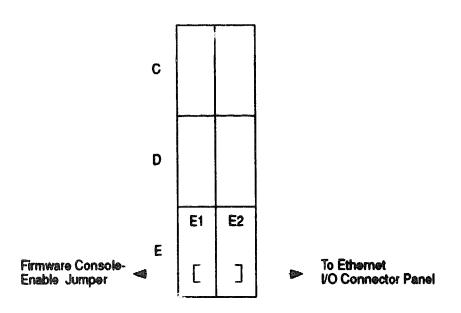

| 2-2        | Firmware Console-Enable Jumper                       | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

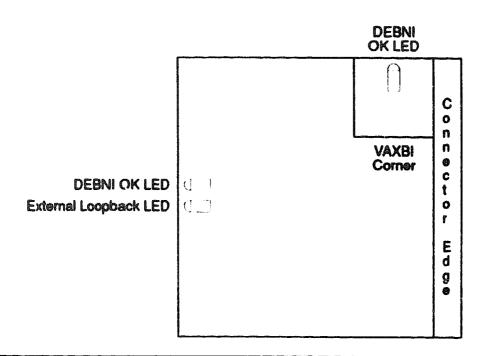

| 3–1        | LED Locations                                        | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

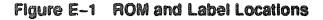

| E-1        | ROM and Label Locations                              | E-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TABLES     |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1–1        | Packing List for DEBNI Option                        | 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1–2        | Cabinet Kits for DESNI Options                       | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2–1        | Power Connection for Internal Ethernet Cable         | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2-2        | Internal Ethernet Cable Pinouts (On VAXBI Backplane) | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2–3        | Transcelver Cable Connector Pinouts                  | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B-1        | Registers Useful During installation—Summary         | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B-2        | Codes for Bit Types                                  | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

PAGE VI INTENTIONALLY LEFT BLANK

#### Preface

#### Purpose of This Manual

This manual describes how to install the DEC LANcontroller 200 adapter. The DEC LANcontroller 200 provides an interface between an Ethernet/IEEE 802 local area network and a system that has a VAXBI bus.

This manual also describes the adapter's self-test and gives advice for troubleshooting.

The DEC LANcontroller 200 is also known as the DEBNI controller. Throughout the rest of this manual, the DEC LANcontroller 200 is referred to as the DEBNI.

#### Intended Audlence

This manual is for DIGITAL and customer personnel who install or replace the DEBNI in the field.

#### **Document Structure**

This manual has three chapters and five appendixes, which are described below:

Chapter 1 briefly describes the DEBNI module: its functions and what you should have received.

Chapter 2 describes installation of the module.

Chapter 3 describes the module's self-test and how to interpret the results.

Appendix A gives environmental requirements for the DEBNI module.

Appendix B gives register information.

Appendix C describes booting with the DEBNI module.

Appendix D explains how to read the DEBNI's hardware Ethernet address.

Appendix E explains how to upgrade a DEBNA module to a DEBNI module.

#### **Associated Documents**

The DEBNI is one of a family of processors, memories, and adapters that use the VAXBI bus. The VAXBI Options Handbook (EB-32255-46) provides a technical summary of all VAXBI modules.

Other related documentation includes:

DEC LANcontroller 200 Technical Manual, EK-DEBNI-TM

DEC LANcontroller 200 Programmer's Guide, EK-DEBNI-PG

Ethernet Installation Guide, EK-ETHER-IN

#### Conventions

- All addresses are in hexadecimal (hex). All bit patterns are in binary notation. All other numbers are decimal unless otherwise indicated.

- Ranges are inclusive. For example, the range 0-4 includes the integers 0, 1, 2, 3, 4.

- Bits are enclosed in angle brackets (for example, <12>).

- Bit ranges are indicated by two bits in descending order separated by a colon; for example, <12:1>. Bit ranges are inclusive.

- K = kilo (1024); M = mega (1024\*\*2); G = giga (1024\*\*3).

- The term "asserted" indicates that a signal line is in the true state.

The term "deasserted" indicates that a signal line is in the false state.

"Assertion" is the transition from the false to the true state.

"Deassertion" is the transition from the true to the false state.

### Introduction

The DEC LANcontroller 200 is an intelligent I/O controller that interfaces an Ethernet local area network to a VAXBI bus. The DEC LANcontroller 200 is compatible with the Ethernet and IEEE 802 specifications <sup>1</sup> and is the standard Ethernet interface for VAX 6xxx and 8xxx systems. The Systems and Options Catalog indicates which systems support the DEC LANcontroller 200 option.

The DEC LANcontroller 200 has a board designation of T1034-YA. It is also possible to upgrade the older DEBNA Ethernet controller, which has a board designation of T1034-00, to a DEC LANcontroller 200 by replacing four ROMs (see Appendix E). The converted version of the DEC LANcontroller 200 has a board designation of T1034-YA but can be distinguished from the nonconverted version of the DEC LANcontroller 200 by the module revision number.

The DEC LANcontroller 200 is also called the DEBNI controller. Throughout the rest of this manual, the DEC LANcontroller 200 is referred to as the DEBNI.

#### 1.1 BASIC FUNCTIONS

The DEBNI supports one Ethernet/IEEE 802 port, which provides the physical link layer and portions of the data link communication layer of the Ethernet and 802 protocols, as defined by the Ethernet and IEEE 802 specifications.

With its own onboard MicroVAX processor, the DEBNI can control operations independently of the host processor. The details of Ethernet transactions, including data transfer over the VAXBI bus, are thus transparent to the host processor (see Figure 1-1).

<sup>&</sup>lt;sup>2</sup> In this manual, 802 refers specifically to the CSMA/CD local area network defined in the IEEE 802.2 and 802.3 specifications (physical and data link layers).

The DEBNI lets the host processor communicate with other nodes in an Ethernet/802 local area network. The DEBNI implements the complete Ethernet protocol and complies with the IEEE 802 specifications.

The DEBNI has extensive on-board diagnostics. On power-up or reset, the DEBNI tests itself and makes its status (pass or fail) available through LEDs on the module and through the DEBNI Power-Up Diagnostic (XPUD) Register. In addition, a field service engineer may invoke other on-board diagnostics from the system console to test the DEBNI's logic and functionality more extensively.

The DEBNI firmware includes a console monitor program that allows a user at any terminal on the network to monitor the DEBNI operation and the network utilization. The console monitor program is accessible only if the DEBNI firmware console-enable jumper is installed (see Section 2.4).

Figure 1-2 is a block diagram of the DEBNI module.

Figure 1-2 DEBNI Block Diagram

The MicroVAX is a 32-bit, single-chip processor that serves as the DEBNI CPU. On the DEBNI module, the MicroVAX is dedicated to running firmware; it cannot be used directly by application programs running on the host processor or by a user at the system console.

The DEBNI Ethernet interface consists of the following chipset:

- A Local Area Network Controller for Ethernet (LANCE chip)

- A Serial Interface Adapter (SIA chip)

The LANCE and SIA chips implement the physical layer and portions of the data link layer of the Ethernet/802 interface.

The DEBNI VAXBI interface is implemented by the BIIC and BCI3 chips. The BIIC has its own power-up self-test.

#### 1.2 PHYSICAL DESCRIPTION

The DEBNI option consists of a single board. The DEBNI has one cable that connects the module with an Ethernet transceiver. This cable is not part of the DEBNI option but is included in the cabinet kits for the DEBNI. (The cabinet kits are described below.)

The Ethernet transceiver cable is a 9-conductor, shielded cable with a male connector. The cable has three main connectors: P1, P2, and P3. The P1 connector connects to the VAXBI backplane. The P2 connector is an industry-standard Ethernet connector that connects to the Ethernet bus. The P3 connector is a +15V direct-current power connection.

Table 1-1 lists the items on the DEBNI packing list. These are the items included with the DEBNI option.

| Table ' | 1-1 | Packing | List | for | DEBNI | Option |

|---------|-----|---------|------|-----|-------|--------|

|---------|-----|---------|------|-----|-------|--------|

| Part Number | Quantity | Description                                                                                                       |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------|

| T1034-YA    | 1        | DEBNI module                                                                                                      |

| EK-DEBNI-IN | 1        | Installation Guide                                                                                                |

| EK-DEBNI-RN | 4        | Release Note                                                                                                      |

| 17-00684-02 | 1        | Power interface cable needed by some VAX 82xx/83xx Configuration 1 systems. See Section 2.1 for more information. |

Table 1-2 lists DEBNI cabinet kits, which must be ordered separately from the DEBNI option. For new systems not included in this table, please see the Systems and Options Catalog.

| System/Enclosure                                                                                                                                                                    | 1.it Number | Contents                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAX 6xxx system cabinets                                                                                                                                                            | CK-DEBNA-LD | Ethernet I/O connector panel (74-26407-41) 3' internal Ethernet cable (17-01496-01) Firmware console-enable jumper (17-01149-01) Ethernet loopback connector (12-22196-02)           |

| VAX 8800, 8810, 8550, and 8530 system cabinets; VAX 8840, 8830, and 8820 system and expansion cabinets; and VAX 6xxx VAXBI expansion cabinets (new VAXBI expansion cabinet (H9657)) | CK-DEBNA-LJ | Ethernet I/O connector panel (74-26407-41) 5' internal Ethernet cable (17-01601-03) Firmware console-enable jumper (17-01149-01) Ethernet loopback connector (12-22196-02)           |

| VAX 8350, 8250                                                                                                                                                                      | CK-DEBNA-LM | Ethernet I/O connector panel (70-18799-00)<br>8' internal Ethernet cable (17-01601-02)<br>Firmware console-enable jumper (17-01149-01)<br>Ethernet loopback connector (12-22196-02)  |

| VAX 8810, 6800, 8700,<br>8550, and 8530 expansion<br>cabinets (old VAXBI<br>expansion cabinet (H9652))                                                                              | CK-DEBNA-LN | Ethernet I/O connector panel (70-18799-00)<br>15' internal Ethernet cable (17-01601-04)<br>Firmware console-enable jumper (17-01149-01)<br>Ethernet loopback connector (12-22196-02) |

The DEBNI module has three status-indicator lights:

- Two DEBNI OK LEDs (yellow)

- One External Loopback LED (green)

Immediately after power-up or reset, all the status-indicator lights are off. If all the tests in the self-test pass (aside from the LANCE external loopback test), the firmware lights the yellow DEBNI OK LEDs. In addition, if the LANCE external loopback test passes (indicating that the DEBNI can transmit and receive a loopback packet over the network), the firmware lights the green External Loopback LED.

## Installation

This chapter explains how to install the DEBNI option into a VAXBI computer system.

For complete instructions for installing an Ethernet transceiver connected to a DEBNI, see the installation guides for the host computer system.

#### WARNINGS

POWER OFF—Shut off system power and disconnect the main system power cord before performing any procedure in this chapter.

STABILIZE THE CHASSIS—For 82xx/83xx Configuration 1 systems: make sure to extend the stabilizer leg(s) before you pull out the processor drawer.

WEAR ESD WRIST STRAP—You must wear an antistatic wrist strap that is connected to the processor cabinet whenever you work inside the cabinet.

USE CONDUCTIVE CONTAINERS—Whenever you remove a circuit board from a VAXBI card cage, place it in a conductive container.

#### 2.1 INSTALLATION

The following steps describe the installation process:

- 1 Power down the host computer system by:

- a. Turning the POWER switch to the OFF position

- b. Setting the system circuit breaker in the rear to OFF

- 2 For 82xx/83xx Configuration 1 systems, extend the cabinet stabilizer leg(s).

- 3 Open the cabinet.

- 4 Make sure you are wearing the ESD wrist strap that is attached to the system chassis.

- 5 For 82xx/83xx Configuration 1 systems, slide out the card cage and rotate it until it locks into the vertical position.

- 6 Remove the card cage cover.

- On some systems, it may be necessary to install a transition header (a cable connector for the backplane) on the VAXBI backplane opposite the slot for the DEBNI. (The VAXBI transition header is part number 12-22246-01.) Use only the torque screwdriver (P/N 29-17381-00). Torque both screws to 6 +0/-1 inch-pounds.

- Make sure there is a node ID plug in place. Note the number on the node ID plug; this number is now the installed module's VAXBI node ID. The node ID number must be unique with respect to the other node numbers on the VAXBI bus.

- 9 Run the internal Ethernet cable from backplane segment E2 to the Ethernet I/O connector panel. See Figure 2–1 and Section 2.3.

- 10 Connect the pigtail connector (P3) from the internal Ethernet cable to a +15V two-prong connector from the power supply.

1 Table 2-1 describes the power connection for various VAX systems.

| Table 2-1 Power Connection for i | Internal Ethernet Cable |

|----------------------------------|-------------------------|

|----------------------------------|-------------------------|

| VAXBI System                                                                                  | Power Connection                                                                           |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| VAX 6xxx                                                                                      | Any H7214 regulator plug (J2) located in the rear of the cabinet                           |

| VAX 82xx, 83xx Configuration 1<br>(12-slot VAXBI card cage) and<br>VAXBI Expansion Box BA32-B | 2-pin Mate-N-Lok pigtail connector located in the bottom of the box                        |

| VAX 82xx, 83xx Configuration 2 (24-slot VAXBI card cage)                                      | 2-pin Mate-N-Lok pigtail connector located in the rear of the cabinet                      |

| VAX 85xx, 87xx, 88xx, and VAXBI Expansion Cabinet H9657                                       | 2-pin Mate-N-Lok pigtail connector labeled P3 or P4 and located in the rear of the cabinet |

#### NOTE

All the pigtail connectors from the power supply may already be used. (Some systems have one or two.) In

<sup>&</sup>lt;sup>1</sup> For VAX 82xx/83xx Configuration 1 systems and for the VAXBI expander box (BA32-B), you may first have to install the +15V connector to the power supply. The connector's part number is 17-00684-02.

this case, the external Ethernet cable from the VO connector panel must not be connected directly to an H4000 transceiver, a DESTA (a thin-wire box), or a DECOM broadband transceiver—none of which have their own power supplies. The cable may, however, be connected to any of the following devices, which do have their own power supplies and which may, in turn, be connected to an H4000:

- A DELNI

- A DEMPR (a thin-wire version of the DELNI)

- A DEBET (a bridge)

- 11 If you wish to have access to the DEBNI's consule monitor program, install the firmware console enable jumper on backplane segment E1. (See Figure 2–2 and Section 2.4.)

- 12 On the module-insertion side of the card cage, locate the card cage slot to which the DEBNI cables and jumper are connected on the connector side of the card cage.

- 13 Lift the locking lever to open the slot.

- 14 Slide the DEBNI module into the slot until it stops: this is a zero insertion force card cage.

- 15 Close the locking lever.

- 16 Replace the card cage cover.

- 17 For 82xx/83xx Configuration 1 systems, rotate the card cage to the horizontal position and retract the stabilizer leg(s).

- 18 Close the cabinet.

- 19 Verify the installation as described in the following section.

#### 2.2 INSTALLATION VERIFICATION PROCEDURE

Follow these steps to verify that the DEBNI is properly installed:

- Turn the system power on and verify that the DEBNI passes both self-test (the two yellow DEBNI OK LEDs light) and the LANCE external loopback test (the green External Loopback LED lights). (See Chapter 3.) If the self-test and/or external loopback test fails, check to see that the module is properly seated in the card cage and that the cables are properly installed. If the module continues to fail self-test, swap in a different DEBNI module if one is available. You can also try installing the module in a different slot.

- 2 After the module passes both self-test and the LANCE external loopback test, boot the operating system.

- 3 Configure the network database and start DECnet.

- 4 If the system is unable to communicate over the Ethernet, verify that the network software is installed and configured properly.

- 5 If the network software is properly installed and configured, shut down the system and check the hardware to isolate the faulty field-replaceable unit (FRU) as follows:

- a. Disconnect the external Ethernet transceiver cable (BNE3) at the transceiver end.

- b. Install a loopback connector (part number 12-22196-02) on the cable.

- c. Run self-test and observe one of the following:

- If the External Loopback LED lights, the transceiver is bad. Replace the transceiver, reconnect the cable to the new transceiver and rerun the self-test to verify proper operation. No further action is required.

- If the External Loopback LED does not light, one of the following is bad: transceiver cable, internal Ethernet cable, backplane, or DEBNI module. Go to the next step.

- d. Disconnect the external transceiver cable at the I/O connector panel and install a loopback connector in its place.

- e. Rerun the self-test and observe one of the following:

- If the External Loopback LED lights, the transceiver cable is bad. Replace the cable and rerun the self-test to verify proper operation. No further action is required.

- If the External Loopback LED does not light, one of the following is bad: internal Ethernet cable, backplane, or DEBNI module. Replace the internal Ethernet cable and install the loopback connector on the new cable. Go to the next step.

- f. Rerun the self-test and observe one of the following:

- If the External Loopback LED lights, the removed cable is bad. Rerun the self-test to verify proper operation. No further action is required.

- If the External Loopback LED does not light, either the DEBNI module or the backplane is bad. If the module passes self-test, it is probably good, but replace it and go to the next step.

- g. Rerun the self-test and observe one of the following:

- If the External Loopback LED lights, the removed DEBNI module is bad. Rerun the self-test to verify proper operation. No further action is required.

- If the External Loopback LED does not light, the backplane is bad. Install the DEBNI module in a different slot. Rerun the self-test to verify proper operation. Consider replacing the card cage.

#### 2.3 INTERNAL ETHERNET CABLE

The internal Ethernet cable connects the VAXBI backplane to the I/O connector panel (see Table 1–2 for part numbers). The external transceiver cable is ordered separately; it runs from the outside of the connector panel to an Ethernet transceiver, such as an H4000 baseband transceiver, DECOM broadband transceiver, or DELNI local network interconnect.

On the backplane, the internal cable plugs into cegment E2 opposite the DEBNI slot. (Viewed with the node ID plugs at the top, E2 is the right side of the segment farthest from the node ID plugs. See Figure 2-1.) The +15V pigtail connector supplies power to the H4000 transceiver; however, you should plug it in (if possible) regardless of the type of transceiver.

Table 2–2 lists pinouts of the internal Ethernet cable connector at the VAXBI card cage. Table 2–3 lists the connector pinouts of the transceiver cable.

Table 2-2 Internal Ethernet Cable Pinouts (On VAXBI Backplane)

| Pin        | Signal                                    | Description                                                  |

|------------|-------------------------------------------|--------------------------------------------------------------|

| E01-E04    | Unconnected                               |                                                              |

| E05-E09    | Logic Ground                              |                                                              |

| E10<br>E11 | Ethernet Collision L Ethernet Collision H | Differential collision detect signals from the Ethernet bus. |

| E12<br>E13 | Ethernet Receive L Ethernet Receive: i    | Differential receive signals from the Ethernet bus.          |

| E14<br>E15 | Ethernet Transmit L Ethernet Transmit H   | Differential transmit signals to the Ethernet bus.           |

| Table 2-2 (Cont.) | Interna: Ethernet | Cable Pinouts | (On | VAXBI | Backplane) |  |

|-------------------|-------------------|---------------|-----|-------|------------|--|

|-------------------|-------------------|---------------|-----|-------|------------|--|

| Pin        | Signal                  | Description                                                                                                                                                                                                                                                      |

|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E16<br>E46 | Firmware Console-Enable | Enables access to the DEBNI console monitor program. The signal is asserted if there is a jumper connection between pins E16 and E46 in the DEBNI section of the VAXBI backplane. The signal is sent to the Status Register, which is a DEBNI-internal register. |

Table 2-3 Transceiver Cable Connector Pinouts

| Pin | Signal                | Description                                   |

|-----|-----------------------|-----------------------------------------------|

| 1   | Shield                |                                               |

| 2   | Collision Presence H  | Differential signals that indicate            |

| 9   | Collision Presence L. | a failure of the collision<br>detection logic |

| 3   | Transmit H            | Differential transmit signals to              |

| 10  | Transmit L            | the Ethernet bus                              |

| 4   | Reserved              |                                               |

| 5   | Receive H             | Differential receive signals from             |

| 12  | Receive L             | the Ethernet bus                              |

| 6   | Power Return          | Power return line                             |

| 7   | Reserved              |                                               |

| 8   | Reserved              |                                               |

| 11  | Reserved              |                                               |

| 13  | Power                 |                                               |

| 14  | Reserved              |                                               |

| 15  | Reserved              |                                               |

#### 2.4 FIRMWARE CONSOLE-ENABLE JUMPER

Install the firmware console-enable jumper if you want to have access to the DEBNI console monitor program. This program provides visibility into the DEBNI operation and the network utilization. The DEBNI console is accessible from any terminal on the network. (See the DEBNI VAXBI Network Adapter Technical Manual, EK-DEBNI-TM, for further information.)

If the firmware console-enable jumper is not installed, you will not be able to access the DEBNI console.

The jumper (P/N 17-01149-01) is a 30-pin connector that is installed on segment E1 of the VAXBI backplane, opposite the DEBNI slot. (Viewed with the node ID plugs at the top, E1 is the left side of the segment farthest from the node ID plugs.) The jumper connects pins E16 and E46, as shown in Figure 2-2.

#### NOTE

On the DEBNA Ethernet controller and the DEBNK Ethernet/tape controller, this jumper was used to enable remote booting. The firmware console-enable jumper for the DEBNI has the same part number and is installed in the same location as the boot-enable jumper for the DEBNA and DEBNK. The only difference is the function controlled by the jumper.

Figure 2-2 Firmware Console-Enable Jumper

E1 Connector

#### 2.5 REMOVAL

To remove a DEBNI module, follow these steps:

- 1 Power down the host computer system by:

- a. Turning the POWER switch to the OFF position

- b. Setting the system circuit breaker to OFF

- 2 For 82xx/83xx Configuration 1 systems, extend the cabinet stabilizer leg(s).

- 3 Open the cabinet.

- 4 Make sure you are wearing an ESD wrist strap that is attached to the system chassis.

- 5 On the module-insertion side of the open cabinet:

- a. For 82xx/83xx Configuration 1 systems, rotate the card cage until it locks in the vertical position.

- b. Remove the card cage cover.

- c. Locate the desired card cage slot.

- d. Lift the locking lever to open the slot.

- e. Slide the circuit board out of the card cage slot.

- f. Put the board into a conductive container.

- g. Close the locking lever.

- n. Replace the plastic card cage cover if another module will not be installed.

- 6 On the cabling side of the open cabinet:

- a. Locate the same card cage slot.

- b. If another module will be installed, leave the cables and jumpers in place; otherwise; remove the cables and jumper.

- 7 If another module will not be installed:

- a. For 82xx/83xx Configuration 1 systems, rotate the card cage to the horizontal position and retract the stabilizer leg(s).

- b. Close the cabinet.

## Power-Up Self-Test

The DEBNI's power-up self-test consists of ROM-resident diagnostic routines that run automatically on power-up or reset. The power-up self-test verifies that the hardware at the node is operational and that the DEBNI can transmit and receive a loopback packet over the network.

Since the routines are contained in ROM, their execution requires no operating system. The self-test routines are thus stand-alone programs independent of any software environment.

#### 3.1 HOW TO RUN SELF-TEST

There are three ways of running self-test for the DEBNI:

- On system power-up—When the user powers up the host system, the DEBNI automatically runs power-up self-test. Front panel controls vary among host systems; see the owner's manual for the specific system.

- On processor reset—When the user presses the reset or restart button on the host system's front panel, the system goes through its reset sequence, which causes each VAXBI node to run its own self-test.

- From the console—A field service engineer can invoke the DEBNI's D0 tests from the system console of a VAX 6xxx, VAX 82xx, or VAX 83xx system. (These are the same tests that run during power-up or reset self-test.)

The following example shows how to use VAX console commands on a VAX 6xxx system to run the self-test on a DEBNI located at VAXBI node 2. (The XMI-to-VAXBI adapter is at XMI node E.) For a description of the Z command used in this example, see the system Owner's Manual.

The following example shows how to use VAX console commands on a VAX 82xx or 83xx system to run the self-test on a DEBNI at node 2. For a description of the Z command used in this example, see the system Owner's Manual.

If you are on a VAX 6xxx console and do not know which VAXBI node the DEBNI is at, use the SHOW CONFIGURATION command at the console prompt to locate the DEBNI.

Another way of locating the DEBNI nodes is to use the EXAMINE command to read the Device (DTYPE) Register at each node until you find the DEBNI, which has a device type of 0118 (hex). A module's DTYPE Register is always at the module's base address. (See Appendix D for a formula for determining the base address of a VAXBI node.)

#### 3.2 REPORTING SELF-TEST RESULTS

Test results (pass or fail) are indicated by LEDs or the module and by the DEBNI Power-Up Diagnostic (XPUD) Register.

#### 3.2.1 Self-Test Results in LEDs

There are three status-indicator lights on the module:

- 2 yellow DEBNI OK LEDs

- 1 green External Loopback LED

The location of the LEDs is shown in Figure 3-1.

The two yellow DEBNI OK LEDs show the status of the module after the node self-test. The green External Loopback LED indicates whether the DEBNI passed the LANCE external loopback test, which tests the DEBNI's ability to transmit and receive a loopback packet over the network.

At power-up or reset, all the LEDs are off. If the DEBNI passes all the executed tests (excluding the LANCE external loopback test), the DEBNI firmware lights the two yellow DEBNI OK LEDs; otherwise, these LEDs remain off. If the LANCE external loopback self-test passes, the firmware lights the green External Loopback LED; otherwise this LED remains off.

### 3.2.2 Self-Test Results in the Power-Up Diagnostic Register

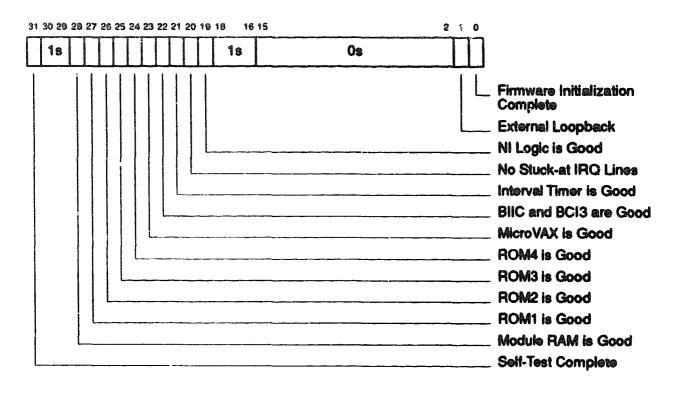

The Power-Up Diagnostic (XPUD) Register indicates which tests in the self-test diagnostic passed. In addition, the Self-Test Complete (STC) bit indicates whether the self-test has completed execution. See Appendix B for a detailed description of the XPUD Register.

#### 3.2 INTERPRETING TEST RESULTS

If the External Loopback LED fails to light, indicating that the LANCE external loopback self-test failed, this does not necessarily indicate that a DEBNI component failed self-test. The problem could be a bad cable, bad Ethernet transceiver connector, improper seating of the transceiver cable, or simply that the DEBNI is disconnected from the transceiver. In any case, such an error condition prevents the DEBNI from transmitting or receiving Ethernet packets.

Figure 3-1 LED Locations

If the XPUD Register indicates that all of the self-test routines failed, the problem is probably the BIIC, MicroVAX, or MicroVAX ROM. If one of these components fails, the self-test routine stops, and the MicroVAX enters a wait state.

Self-test could also fail because of a systemwide fault. For example, a faulty power supply or missing VAXBI bus terminators could be the problem. Make sure that system power is OK and check for other possible systemwide faults.

#### 3.4 TESTED COMPONENTS

Self-test tests the following components and functions on the DEBNI module:

- MicroVAX

- MicroVAX ROM

- MicroVAX RAM

- MicroVAX Interrupt Request (IRQ) lines

#### Power-Up Self-Test

- BIIC and BCI3 chips

- LANCE chip

- Interval timer

#### 3.5 UNTESTED COMPONENTS AND FUNCTIONS

The following components and functions are not tested:

#### MicroVAX:

A complete instruction set

#### Ethernet interface logic functions:

- More (multiple retries of packet transmission)

- One (one retry of a packet transmission)

- Babble error

- Time domain reflectometry

- Late collision

- Loss of carrier

- Memory error

#### In the BCI3/BIIC logic:

- BIIC nodespace locking

- BIIC nodespace Write Sense bits

- BCI3 datamove operations with quadwords and octawords

- BCI3 Nonlocal Memory Reference (NLMR) line

## **Environmental Requirements**

| Operating<br>Environment                     |                                                                                                     |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Temperature                                  | 5°C to 50°C (41°F to 122°F)                                                                         |

| Humidity                                     | 10% to 95% with maximum wet bulb of 32°C (89.6°F) and minimum dew point of 2°C (36°F) noncondensing |

| Altitude To 2.4 km (8,000 ft)                |                                                                                                     |

|                                              |                                                                                                     |

| Storage Environme                            | ent                                                                                                 |

| Storage Environme                            | -40°C to 66°C (-40°F to 151°F)                                                                      |

| Storage Environme<br>Temperature<br>Humidity |                                                                                                     |

## Registers

This appendix describes the DEBNI registers that are useful for troubleshooting problems that may occur during installation. Table B-1 summarizes these registers. Table B-2 explains the access types for these registers, as well as the bit types for the registers. Each register is then described in detail.

| Table B-1 | Ranlefare | lestul | Durina | Installation—Summary |

|-----------|-----------|--------|--------|----------------------|

|           | remisters | USCIUI |        | niamienon—onimieny   |

| Name                        | Mnemonic | VAXBI<br>Address | Type¹ | Description                                                                                                          |

|-----------------------------|----------|------------------|-------|----------------------------------------------------------------------------------------------------------------------|

| Device                      | DTYPE    | bb + 0           | RO    | Indicates the VAXBI node's device type and device firmware revision level.                                           |

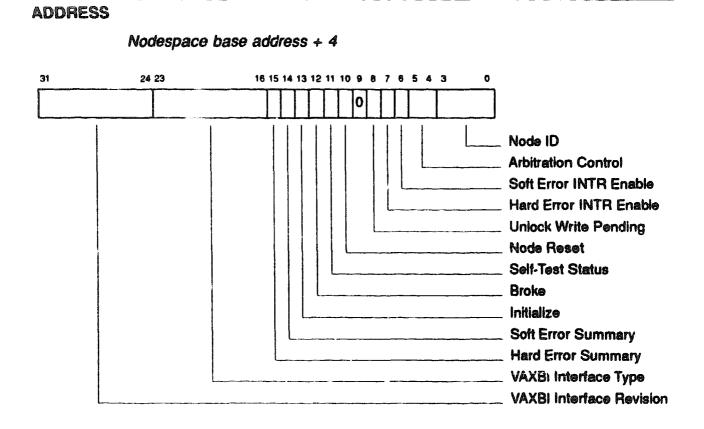

| VAXBI Control and<br>Status | V/KBICSR | bb + 4           | P/W   | Indicates whether the BIIC chip passed its internal self-test and whether the DEBNI as a whole passed its self-test. |

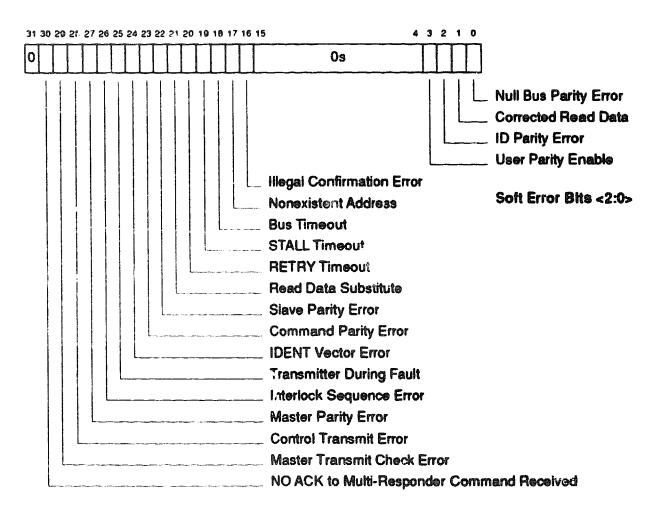

| Bus Error                   | BER      | bb + 8           | P/W   | Records VAXBI bus errors and loopback errors.                                                                        |

| Power-Up Diagnostic         | XPUD     | bb + FC          | Ro    | Indicates whether self-test has completed and which tests in the self-test passed.                                   |

<sup>&</sup>lt;sup>1</sup>With respect to the port driver

Table B-2 Codes for Bit Types

| Code  | Description                                                                                                                                          |