XXXXXXXXXXXXX XXXXXXXXXX XXXXXXXXX XXXXX XXX X

> x XXX XXXXXX XXXXXXXXX XXXXXXXXXXXX XXXXXXXXXXXX

# **CIXCD Interface User Guide**

Order Number EK-CIXCD-UG-003

digital equipment corporation maynard, massachusetts

#### First Edition, May 1990 Second Edition, October 1990

The information in this document is subject to change without nonce and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

The postpaid Reader's Comment Card included in this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| BI        | KDM          | RSTS   | VAX FORTRAN             |

|-----------|--------------|--------|-------------------------|

| CI        | KLESI        | RSX    | VAX MACRO               |

| DEC       | MASSBUS      | RT     | VAXBI                   |

| DECmate   | MicroVAX     | RV20   | VAXcluster              |

| DECUS     | NI           | RV64   | VAXsim                  |

| DECwriter | PDP          | TA     | VAXELN                  |

| DHB32     | P/OS         | ТК     | VMS                     |

| DIBOL     | Professional | ULTRIX | VT                      |

| DRB32     | RA           | UNIBUS | Work Processor          |

| EDT       | Rainbow      | VAX    | $\mathbf{N} \mathbf{M}$ |

| KDB50     | RD           | VAX C  |                         |

|           |              |        | ol 19 i tei l           |

®Plexiglas is a registered trademark of Rahm and Haas Company.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# Contents

4

# **About This Manual**

## User Information

#### **4** Introduction

| 1.1   | General Description           |

|-------|-------------------------------|

| 1.1.1 | Components                    |

| 1.1.2 | Features                      |

| 1.2   | Specifications                |

| 1.3   | Physical Hardware Description |

| 1.3.1 | CIXCD Module                  |

| 1.3.2 | CIXCD Header Card Assembly    |

| 1.3.3 | CI Bulkhead Cable Assembly    |

| 1.3.4 | Jumpers                       |

# 2 Systems Overview

| 2.1   | VAX 6000 Family   | 2–2 |

|-------|-------------------|-----|

| 2.1.1 | VAX 6000 Cabinets | 2-2 |

| 2.2   | VAX 9000 Family   | 2-4 |

| 2.2.1 | VAX 9000 Cabinets | 25  |

# **Installation Procedures**

# 3 Site Preparation and Installation

| 3.1    | Operating Environment                         | 3–1        |

|--------|-----------------------------------------------|------------|

| 3.1.1  | Physical Elements                             | 3–1        |

| 3.1.2  | System Environment and Grounding Elements     | 3–2        |

| 3.2    | System Configurations                         | 3–2        |

| 3.2.1  | VAXcluster Revision Levels                    | 3–2        |

| 3.3    | Unpacking and Inventory                       | 32         |

| 3.3.1  | Unpacking the Shipping Boxes                  | 3–3        |

| 3.3.2  | Inventory                                     | 33         |

| 3.4    | Installation and Configuration                | 33         |

| 3.4.1  | Removal of the CIBCA Option                   | 3-4        |

| 3.4.2  | Installation of the CIXCD Option              | 3 <b>9</b> |

| 3.4.3  | Updating the VAX 6000 Console Microcode       | 3–11       |

| 3.4.3. | 1 Determining the Need for Updated Microcode  | 3–11       |

| 3.4.3. | 2 Performing the Update                       | 3–13       |

| 3.5    | Backplane Jumpers and Configuration Selection | 3-16       |

| 3.5.1  | CI Node Address                               | 3-17       |

| 3.5.2  | Boot Time                                     | 3–19       |

| 3.5.3  | Disable Arbitration                           | 3–20       |

| 3.5.4  | Extend Header                                 | 3-20       |

| 3.5.5  | Alter Delta Time                              | 3–20       |

| 3.5.6  | Cluster Size                                  | 3-21       |

| 3.5.7  | Extend ACK Timeout                            | 3–22       |

## 4 Verification and Acceptance Testing

| 4.1     | Diagnostic Verification                               | 4-2 |

|---------|-------------------------------------------------------|-----|

| 4.1.1   | Diagnostic Programs                                   | 4–2 |

| 4.1.2   | Power-Up Self-Test                                    | 4-3 |

| 4.1.3   | Preliminary Diagnostic Setup                          | 4-4 |

| 4.1.3.1 | Loopback Connectors                                   | 4-4 |

| 4.1.3.2 | 2 Loading the VAX Diagnostic Supervisor (VDS) Program | 4-5 |

| 4.1.4   | Repair-Level Testing                                  | 4-7 |

| 4.1.5   | CI Functional Level Testing                           | 49  |

| 4.1.6 | System Functional Level Test | ing | 4-11 |

|-------|------------------------------|-----|------|

| 4.2   | System Maintenance Tools     |     | 4–13 |

# Service

# 5 Diagnostics

| 5.1     | CIXCD Self-Test/ROM-Based Diagnostics    | 5–2  |

|---------|------------------------------------------|------|

| 5.1.1   | XCDST                                    | 5-2  |

| 5.1.1.1 | XCDST Tests                              | 5-3  |

| 5.1.2   | RBDs                                     | 5-8  |

| 5.1.2.1 | RBD User Interface                       | 59   |

| 5.1.2.2 | 2 RBD Information Printout               | 5-12 |

| 5.1.2.3 | 8 Example of RBD Printout                | 5-14 |

| 5.2     | Macrodiagnostics                         | 5-14 |

| 5.2.1   | Repair-Level Diagnostic — EVGEA          | 5–15 |

| 5.2.1.1 | Running EVGEA                            | 5–15 |

| 5.2.1.2 | 2 Event Flags                            | 5-17 |

| 5.2.1.3 | B EVGEA Tests                            | 5-18 |

| 5.2.1.4 | 1 The MFG Section                        | 5-19 |

| 5.2.1.8 | 5 The EEPROM Update/Verification Utility | 5–19 |

| 5.2.1.6 | 6 EEPROM Memory Map                      | 5–24 |

| 5.2.1.3 | 7 EVGEA Error Messages                   | 5–26 |

| 5.2.2   | CI Functional Diagnostics — EVGAA, EVGAB | 5-26 |

| 5.2.3   | Cluster Functional Diagnostic — EVGAC    | 5–27 |

| 5.2.3.2 | 1 Event Flags                            | 5–27 |

| 5.2.3.2 | 2 Event Tracing                          | 528  |

| 5.2.3.3 | 3 Program Parameters                     | 530  |

| 5.2.3.4 | 4 Support Files                          | 531  |

| 5.2.3.  | 5 Program Tests                          | 5-35 |

# 6 Functional Description

| 6.1        | Overview                            | 6-2        |

|------------|-------------------------------------|------------|

| 6.1.1      | XMI Responder                       | 6-4        |

| 6.1.2      | XMI Commander                       | 65         |

| 6.2        | XMI Corner                          | 6–5        |

| 6.2.1      | XCLOCK                              | 65         |

| 6.2.2      | хцатсн                              | 6-6        |

| 6.3        | XMI Interface Logic and Data Movers | 66         |

| 6.3.1      | XMI Interface Logic                 | 66         |

| 6.3.2      | Data Movers                         | 6-7        |

| 6.4        | Port Microprocessor                 | 6-7        |

| 6.4.1      | Processor Data Path                 | 68         |

| 6.4.2      | Port Microcontrol                   | 68         |

| 6.4.3      | Control Store RAMs/EEPROMs          | <b>6–9</b> |

| 6.4.4      | Local Store                         | 6–9        |

| 6.5        | CI Control Logic and Packet Memory  | 69         |

| 6.5.1      | Packet Buffer Memory Organization   | 6–10       |

| 6.5.2      | Memory Controller                   | 6-11       |

| 6.5.3      | CI Wire Interface                   | 6-11       |

| 6.5.4      | CI Controller                       | 6-11       |

| <b>6.6</b> |                                     | 6-12       |

| 6.6.1      | Receiver Hybrid                     | 6–13       |

| 6.6.2      | CI Receive/Transmit Gate Array      | 6-13       |

# A CIXCD Registers

## **B** EVGEA Sections

# C Cluster Upgrades

| <b>C</b> .1 | CIXCD VAXcluster Minimum Revision Levels | C-1 |

|-------------|------------------------------------------|-----|

| <b>C.2</b>  | Quiet Slot Time Settings                 | C3  |

## Index

# )

| Examples |

|----------|

|----------|

| 3-1         | SHOW CONFIGURATION With Old Microcode | 3-12        |

|-------------|---------------------------------------|-------------|

| 3-2         | SHOW CONFIGURATION With New Microcode | 3–12        |

| 33          | Updating VAX 6000 Console Microcode   | 3–15        |

| 4–1         | VAX 6000 Console Printout             | 4-4         |

| 4-2         | Trace Printout for EVGEA (One Pass)   | 48          |

| 4-3         | Trace Printout for EVGAA (One Pass)   | 4-10        |

| 4-4         | Trace Printout for EVGAB (One Pass)   | 4-11        |

| 4-5         | Trace Printout for EVGAC (One Pass)   | 4-12        |

| 5–1         | Sample Printout of Exam Section       | 5-24        |

| 52          | EVGEA Error Message                   | 5-26        |

| 53          | Sample Parameter File                 | 5-33        |

| 5-4         | Sample Pattern File                   | 5-34        |

| 55          | EVGAC Full Listing                    | 5-36        |

| <b>B</b> –1 | UPDATE Section                        | <b>B</b> 1  |

| B-2         | VERIFY Section, No Errors             | <b>B</b> –2 |

| <b>B3</b>   | VERIFY Section, Errors                | <b>B</b> 3  |

| <b>B-4</b>  | RVERIFY Section, No Errors            | <b>B-4</b>  |

| <b>B5</b>   | RVERIFY Section, Errors               | <b>B5</b>   |

| <b>B6</b>   | REPLACE Section                       | <b>B6</b>   |

| <b>B-7</b>  | RESTORE Section                       | <b>B</b> –7 |

| <b>B</b> 8  | ERRORLOG Section                      | <b>B8</b>   |

| <b>B-9</b>  | EXAMLOG Section                       | <b>B</b> 9  |

## Figures

| 1–1 | Simplified CIXCD Adapter Connection |

|-----|-------------------------------------|

| 12  | CIXCD Header Card Assembly          |

| 13  | CIXCD-AA Bulkhead Cable             |

| 1-4 | CIXCD-AB Bulkhead Cable             |

| 2–1 | VAX 6000 Cabinet                    |

| 2–2 | VAX 9000 Model 210 Cabinet          |

| 2–3 | VAX 9000 Model 400 Cabinets         |

| 3-1 | CIBCA Intermodule Cables            |

| 3-2 | CIBCA Cable Location                |

| 33  | Node ID Plug Location               |

•

| 3-4  | CIBCA Jumpers                                                   | 38          |

|------|-----------------------------------------------------------------|-------------|

| 35   | CIXCD Module Installed in Card Cage                             | 3–10        |

| 3-6  | The Update Position                                             | 3–13        |

| 3–7  | CIXCD Jumper Pinning                                            | 3-17        |

| 4-1  | CIXCD Acceptance Testing Flow Diagram                           | 42          |

| 4-2  | Diagnostic Loopback Cable Connections                           | 4-5         |

| 5-1  | EEPROM Memory Map                                               | <b>5–25</b> |

| 5-2  | Program Parameter Register                                      | 5–28        |

| 6-1  | CIXCD Simplified Block Diagram                                  | 62          |

| 6-2  | CIXCD Block Diagram                                             | 63          |

| 63   | Packet Buffer Format                                            | 6-10        |

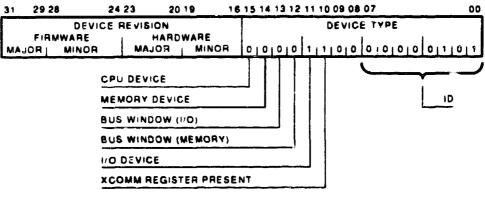

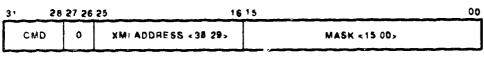

| A1   | XMI Device Register (XDEV) Offset = 00000                       | A-1         |

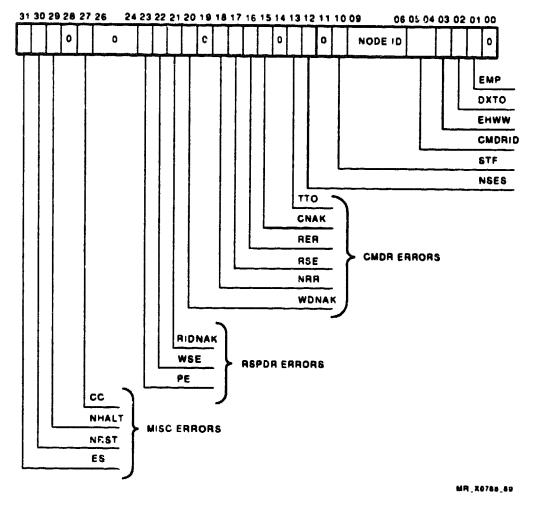

| A2   | XMI Bus Error Register (XBER) Offset = 00004                    | A-2         |

| A3   | XMI Failing Address Register LW0 (XFADR) Offset = 00008.        | A-9         |

| A-4  | XMI Communications Register (XCOMM) Offset = 00010              | A9          |

| A5   | Port Scan Control Register (PSCR) Offset = 00014                | A9          |

| A6   | Port Scan Data Register (PSDR) Offset = 00018                   | A9          |

| A7   | Port Maintenance Control/Status Register (PMCSR) Offset = 0001C | A-10        |

| A8   | Port Diagnostic Control/Status Register (PDCSR) Offset = 00020  | A–18        |

| A-9  | Port Status Register (PSR) Offset = 00024                       | A-18        |

| A–10 | XMI Failing Address Register LW1 (XFAER) Offset = 0002C         | A-18        |

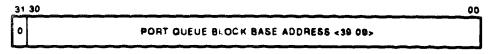

| A-11 | Port Queue Block Base Register (PQBBR) Offset = 01000           | A-19        |

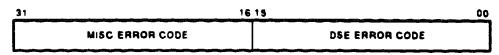

| A-12 | Port Error Status Register (PESR) Offset = 01008                | A–19        |

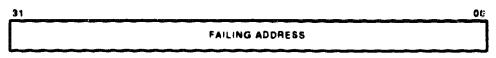

| A-13 | Port Failing Address Register (PFAR) Offset = 0100C             | A-19        |

| A-14 | Port Parameter Register (PPR) Offset = 01010                    | A-19        |

| A-15 | Port Serial Number Register (PSNR) Offset = 01014               | A-19        |

| A-16 | Port Interrupt Destination Register (PIDR) Offset = 01018       | A-20        |

| A-17 | Port Interrupt Vector Register (PIVR) Offset = 01020            | A-20        |

| A-18 | Port Command Queue 0 Control Register (PCQ0CR) Offset = 01028   | A-20        |

| A-19 | Port Command Queue 1 Control Register (PCQ1CR) Offset = 0102C   | A-20        |

| A–20 | Port Command Queue 2 Control Register (PCQ2CR) Offset = 01030   | A-20        |

| A-21 | Port Command Queue 3 Control Register (PCQ3CR) Offset = 01034                        | <b>A-2</b> 1 |

|------|--------------------------------------------------------------------------------------|--------------|

| A-22 | Port Status Release Control Register (PSRCR) Offset = 01038                          | A-21         |

| A-23 | Port Enable Control Register (PECR) Offset = 0103C                                   | A21          |

| A-24 | Port Disable Control Register (PDCR) Offset = 01040                                  | A-21         |

| A-25 | Port Initialize Control Register (PICR) Offset = 01044                               | <b>A-21</b>  |

| A-26 | Port Datagram Free Queue Control Register (PDFQCR)<br>Offset = 01048                 | A-22         |

| A-27 | Port Message Free Queue Control Register (PMFQCR) Offset<br>= 0104C                  | A-22         |

| A-28 | Port Maintenance/Sanity Timer Control Register (PMTCR)<br>Offset = 01050             | A-22         |

| A29  | Port Maintenance/Sanity Timer Expiration Control Register<br>(PMTECR) Offset = 01054 | A-22         |

| A-30 | Port Parameter Extension Register (PPER) Offset=01058                                | A-22         |

## Tables

| 1-1 | CIXCD-AA Hardware Components                        | 16   |

|-----|-----------------------------------------------------|------|

| 12  | CIXCD-AB Hardware Components                        | 1-6  |

| 2-1 | VAX 6000 Family                                     | 2–2  |

| 22  | VAX 9000 Family                                     | 2-4  |

| 3-1 | CI Node Address Table — True/Complement             | 3–18 |

| 3–2 | Boot Time Backplane Jumpers                         | 3-19 |

| 3–3 | Quiet Slot Time Backplane Jumpers                   | 3–20 |

| 3–4 | Cluster Size Backplane Jumpers                      | 3-21 |

| 4-1 | CIXCD Diagnostic Programs                           | 4-3  |

| 4-2 | VAXcluster System Maintenance Tools                 | 4-13 |

| 5–1 | Functional Microcode Test Failure Error Codes       | 53   |

| 5-2 | RBD Commands                                        | 5–10 |

| 53  | START Qualifiers                                    | 5–10 |

| 5-4 | RBD Control Characters                              | 5-11 |

| 55  | EEPROM Update/Verification Utility Program Sections | 5–20 |

| 5–6 | Trace Bit Field Definitions                         | 5-29 |

| 5–7 | EVGAC Program Parameters                            | 5–30 |

| 58  | Parameter File Structure                            | 5-32 |

| C-1 | Minimum Revision Levels                             | C-2  |

$\mathbf{)}$

PAGE x INTENTIONALLY LEFT BLANK

# **About This Manual**

This manual describes the CIXCD interconnect hardware option, which provides the parallel-to-seria! interface between two corporate interconnect bus architecture protocols: the XMI bus and the dual-path CI bus. Included in the manual are the installation procedures, as well as the testing procedures to determine if the option is working correctly.

## **Intended Audience**

This manual is intended for Digital Customer Service personnel, or customers who install and/or maintain this option. Such topics as installation and testing are covered in this manual. Digital personnel includes Customer Service branch-level engineers.

## **Manual Structure**

This manual is divided into three main sections:

User information Installation procedures Service

The User Information section has two chapters: the CIXCD introduction that gives the option's specifications, and an overview of the VAX systems that use this option. The Installation Procedures section has two chapters: one on site preparation and installation and the other on verification and acceptance testing. The Service section has two chapters: a description of the CIXCD diagnostics, and a functional description of the CIXCD option. Also, there is an appendix with a description of all the visible registers.

# **Related Documents**

The following manuals can provide additional information about the CIXCD option and the XMI bus.

| Title                                                   | Order Number |

|---------------------------------------------------------|--------------|

| CIXCD Technical Manual <sup>1</sup>                     | EK-CIXCD-TM  |

| VAX 6000-400 System Technical User's Guide <sup>1</sup> | EK-640EA-TM  |

| VAX 6000-400 Installation Guide                         | EK-640EA-IN  |

| VAX 9000 Model 200 Installation Guide                   | EK-9200I-IN  |

| VAX 9000 Model 200 Hardware User Guide                  | EK-9201U-UG  |

| VAX Diagnostic User's Guide <sup>1</sup>                | EK-VXDSU-UG  |

| VAX Diagnostic User's Guide Update <sup>1</sup>         | EK-VXDSU-U1  |

| VAX Diagnostic System User's Guide <sup>1</sup>         | EK-VX11D-UG  |

| VAX Diagnostic Software Handbook <sup>1</sup>           | AA-F152A-TE  |

| SC008 Star Coupler User's Guide                         | EK-SC008-UG  |

| CISCE-AA Installation Guide                             | EK-CISCE-UG  |

| VAXcluster Service Reference Manual <sup>1</sup>        | EK-VCSRM-PK  |

<sup>1</sup>Available only to Digital Customer Service personnel or licensed self-maintenance customers.

X000000000000000000000000 X00000000000000X XXXXXXXXXXX XXXXXXXXX XXXXXX XXX X

> X XXX X0000X 10000000 3030000000

# **UserInformation**

This section of the manual contains user information regarding the CIXCD. Important information is included regarding the various systems that use the CIXCD.

$\mathcal{X}^{*}$

XXXXXXXXXX XXXXXXXXX XXXXX XXX х

x XXX 20000X 10000000 10000000000 300000000000

# 1 Introduction

This chapter introduces the computer interconnect hardware interface options CIXCD-AA and CIXCD-AB. These options provide the interface between computer systems that use the high-speed XMI bus and the CI bus. Also included in this chapter are the physical description and specifications of the hardware.

The sections include:

- General description

- Specifications

- Physical hardware description

# 1.1 General Description

This section describes the components and the features of the CIXCD.

## 1.1.1 Components

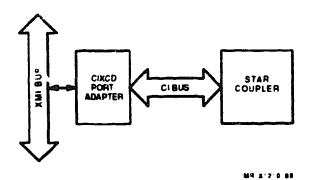

The computer interconnect interface, shown in Figure 1-1, is designated the CIXCD port adapter. It is an intelligent interface, residing on a single module, that connects the XMI bus to the high-speed CI bus.

#### NOTE

All modules that plug into the XMI bus are considered XMI "native adapters." We will refer to the CIXCD as the CIXCD adapter, or as the port adapter.

#### Figure 1–1 Simplified CIXCD Adapter Connection

As a buffered communications port, the CIXCD adapter completes highlevel computer communications, thereby reducing software processing overhead. This is accomplished with hardware that provides all of the necessary data buffering, address translations, and serial data encoding/decoding. The CIXCD uses queue structures provided under the VMS operating system to transfer packet messages and to initiate the transfer of blocks of data between the VAX host memory system and/or other nodes within the VAXcluster configuration.

The CIXCD-AA adapter is made up of a single hardware module, T2080, a single header card assembly, 54-20225-01, and a single cable assembly: either 17-02894-01 for the CIXCD-AA or 17-02894-02 for the CIXCD-AB.

## 1.1.2 Features

- Resequencing dual path

- XMI bus design

- Typical performance of up to 8 Mbyte/s

- Parity on all internal buses and control stores

- Updateable control store

- Diagnostic loopback capability (both internal and external)

- Data integrity through cyclic redundancy checking (CRC)

- Round-robin arbitration at heavy loading, for each path

- Contention arbitration at light loading, for each path

- Packet-oriented data transmission

- Immediate acknowledgment of packet reception

- Operational modes:

- Uninitialized

- Disabled

- Enabled

# 1.2 Specifications

#### **CI General Specifications**

Priority arbitration

Light loading Heavy loading Contention Round-robin

Cyclic redundancy check

Parity

Data format

Manchester-encoded serial packet

### **Environmental Specifications**

| Temperature              |                                                                                                                                                                     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating                | 10°C to 40°C (50°F to 104°F) ambient<br>temperature with a gradient of 10°C (18°F)/hr                                                                               |

| Storage/shipping         | -40°C to 70°C (-40°F to 158°F) ambient<br>temperature with a gradient of 20°C (36°F)/hr                                                                             |

| <b>Relative humidity</b> |                                                                                                                                                                     |

| Operating                | 10% to 90% with a maximum wet bulb temperature of $28^{\circ}$ C ( $82^{\circ}$ F) with a minimum dew point of $2^{\circ}$ C ( $36^{\circ}$ F) with no condensation |

| Storage/shipping         | 5% to 95% with no condensation                                                                                                                                      |

| Altitude                 |                                                                                                                                                                     |

| Operating                | Sea level to 2.4 km (8000 ft)                                                                                                                                       |

|                          | Maximum operating temperatures decrease by a factor of 1°C/1000 ft (1.8°F/1000 ft) for operation above sea level                                                    |

| Shipping/storage         | Up to 9.1 km (30,000 ft) above sea level (actual or effective by means of cabin pressurization)                                                                     |

| Shock                    | 5 Gs peak at 7 to 13 ms duration in three axes mutually perpendicular (maximum)                                                                                     |

|                          |                                                                                                                                                                     |

#### **Electrical Specifications**

| Power consumption:      | Maximum ripple: |

|-------------------------|-----------------|

| +5.0 V at 5.9 A nominal | 300 mV          |

| -5.2 V at 1.8 A nominal | 150 mV          |

| -2.0 V at 0.5 A nominal | 150 mV          |

#### XMI Bus Specifications

**Bus characteristics**

| Туре                         | Synchronous, pended                         |

|------------------------------|---------------------------------------------|

| Width                        | 64 data bits                                |

| Cycle time                   | 64 ns                                       |

| Priority arbitration         | Modified round-robin                        |

| Parity                       | Even                                        |

| Data transfers               | Longword<br>Quadword<br>Octaword<br>Hexword |

| Transmission characteristics |                                             |

| Bandwidth                    | 100 Mbytes/s (for HW transfers)             |

| Length                       | 17 inches                                   |

| Bus loading (maximum)        | 16 nodes                                    |

| CI Bus Specifications        |                                             |

| Bus characteristics          |                                             |

| Width                        | Serial                                      |

| External length<br>(maximum) | 45 m (147.64 ft)                            |

| Data transfer rate           | 140 Mbits/s (maximum)                       |

Bus loading (maximum)

Cable type (BNCIA-XX)

Cable impedance

Double-shielded coaxial 50 ohms

32 nodes

# **1.3 Physical Hardware Description**

Refer to Tables 1-1 and 1-2 for an overview of the CIXCD hardware components. The CIXCD AA is used on VAX 9000 systems, while the CIXCD-AB is used on VAX 6000 systems.

| Table 1-1 | CIXCD-AA | Hardware | Components |

|-----------|----------|----------|------------|

|-----------|----------|----------|------------|

| Component                        | Part Number |  |

|----------------------------------|-------------|--|

| CIXCD port adapter module        | T2080       |  |

| CIXCD header card assembly       | 54-20225-01 |  |

| VAX 9000 bulkhead cable assembly | 17-02894-01 |  |

| Jumpers                          | 12-14314-01 |  |

| CIXCD Interface User Guide       | EK-CIXCD-UG |  |

#### Table 1–2 CIXCD-AB Hardware Components

| Component                        | Part Number |  |

|----------------------------------|-------------|--|

| CIXCD port adapter module        | T2080       |  |

| CIXCD header card assembly       | 54-20225-01 |  |

| VAX 6000 bulkhead cable assembly | 17-02894-02 |  |

| Jumpers                          | 12-14314-01 |  |

| CIXCD Interface User Guide       | EK-CIXCD-UG |  |

## 1.3.1 CIXCD Module

The CIXCD module contains the following:

- XMI interface logic

- Packet buffer (PB) RAMs

- Control store RAMs

- Control store EEPROMs

- Local store RAMs

- Five gate arrays:

- XMOV: data movers, XMI interface control

- MCWI: PB memory control, CI wire interface and control

- MCDP: microprocessor, sequencer

- CIRT (2): Manchester encode/decode logic, byte framer, shift register

#### 1.3.2 CIXCD Header Card Assembly

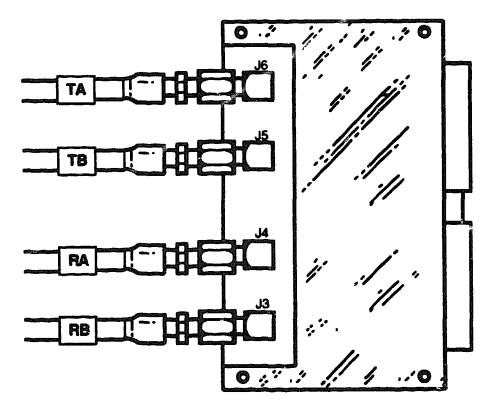

The CIXCD header card assembly is made up of two connected parts: a header card and a plastic cover. The header card is a circuit board that provides active logic to convert the received CI signals to ECL levels. The CI bulkhead cables connect to the header card, which then is plugged into the XMI backplane. The plastic cover provides dual protection: it protects the components from other cables plugged into the XMI backplane and it protects the other cables from the components. It also provides a key, so the assembly can only be plugged into the backplane the correct way. Figure 1-2 shows the CIXCD header card assembly.

MR\_X0712\_90.RAGS

#### Figure 1–2 CIXCD Header Card Assembly

## 1.3.3 CI Bulkhead Cable Assembly

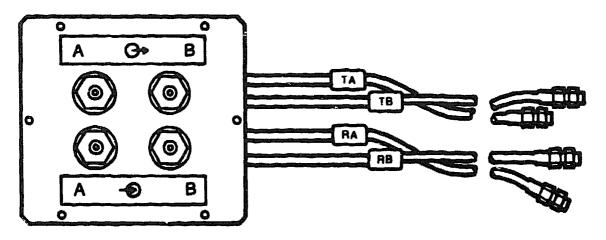

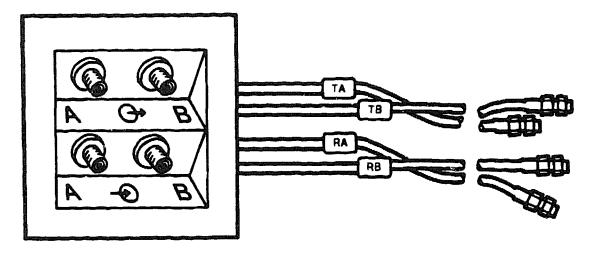

The CIXCD is connected from the XMI backplane, through the header card and the CI bulkhead cable to the CI bulkhead connector panel. The CI bulkhead cable is made up of four coaxial cables, each of which connects to the header card on one end and to the CI bulkhead connector panel on the other end. The CI bulkhead connector panel is mounted on the I/O panels of the cabinet (quad panel size for VAX 6000 systems) and provides an EMI/RFI shield without compromising signal integrity. Figures 1-3 and 1-4 show the CI bulkhead cable.

MR. KOSSS. BE CPG

Figure 1-3 CIXCD-AA Bulkhead Cable

M9,20684,38 CPG

#### Figure 1-4 CIXCD-AB Bulkhead Cable

#### 1.3.4 Jumpers

The jumpers are required to provide specific configuration information to the MCDP microprocessor. They are placed in zones D2 and E2 of the XMI backplane (refer to Section 3.5 for placement information). X0000000000000000 XXXXXXXXXXXXXXXXX XXXXXXXXXXXXXXX XXXXXXXXXXX XXXXXXX XXXXXX

XXXX х

> х XXX XXXXXX XXXXXXXX XXXXXXXXXX XXXXXXXXXXXXX

# **2** Systems Overview

This chapter describes the families of hardware systems that can use the CIXCD interface. All these systems have the XMI bus as either the system bus or as an I/O bus.

They include:

- VAX 6000 family (model 200, model 300, model 400, model 500)

- VAX 9000 family (model 200, model 400)

# 2.1 VAX 6000 Family

All members of the VAX 6000 family can use the CIXCD-AB interface. In this family there are four entries, each of which comes with many models. Table 2-1 shows the members of this family.

| Model                 | Members   | Model                 | Members                |

|-----------------------|-----------|-----------------------|------------------------|

| VAX 6000<br>model 200 | Model 210 | VAX 6000<br>model 400 | Model 410              |

|                       | Model 220 |                       | Model 420              |

|                       | Model 230 |                       | <sup>84</sup> odel 430 |

|                       | Model 240 |                       | Model 440              |

|                       |           |                       | <b>Model 450</b>       |

|                       |           |                       | Model 460              |

| VAX 6000<br>model 300 | Model 310 | VAX 6000<br>model 500 | <b>Model 510</b>       |

|                       | Model 320 |                       | <b>Model 520</b>       |

|                       | Mode! 330 |                       | Model 530              |

|                       | Model 340 |                       | Model 540              |

|                       | Model 350 |                       | Model 550              |

|                       | Model 360 |                       | Model 560              |

Table 2-1 VAX 6000 Family

## 2.1.1 VAX 6000 Cabinets

All VAX 6060 systems use the same standard system cabinet. Figure 2-1 shows the VAX 6000 family cabinet.

Figure 2-1 VAX 6000 Cabinet

# 2.2 VAX 9000 Family

All members of the VAX 9000 family can use the CIXCD-AA interface. In this family there are two entries, one of which comes in many models. Table 2-2 shows the members of this family.

| Model              | Members   |  |  |

|--------------------|-----------|--|--|

| VAX 9000 model 200 | Model 210 |  |  |

| VAX 9000 model 400 | Model 410 |  |  |

|                    | Model 420 |  |  |

|                    | Model 430 |  |  |

|                    | Mode! 440 |  |  |

Table 2-2 VAX 9000 Family

## 2.2.1 VAX 9000 Cabinets

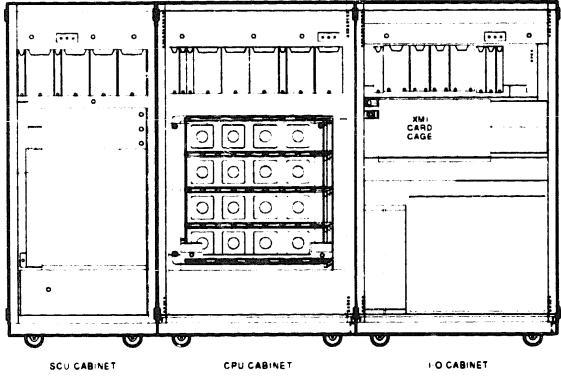

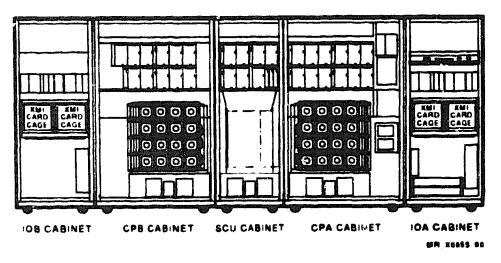

The VAX 9000 family of systems can have many different cabinet configurations, depending on model type. Model 210 has a unique set of cabinets, while model 400 systems all use the same cabinet types, but with different configurations. Figures 2-2 and 2-3 show the different cabinets.

W-4 R0858 80

Figure 2-2 VAX 9000 Model 210 Cabinet

#### 2-6 Systems Overview

Figure 2-3 VAX 9000 Model 400 Cabinets

200000000000000 KKMKKKKKKKKKK XXXXXXXXXX XXXXXXXX XXXXXX xxx X

> X XXXX XXXXXX XXXXXXXXXX 20000000000

> > in si Villaikii

# Installation Procedures

This section of the manual contains the information necessary to install the CIXCD option.

X000000000000000000 X0000000000X XXXXXXXXX XXXXXX XXX X

> X XXXX 100001 20000000 1000000000

# **Site Preparation and Installation**

This chapter describes the site preparations necessary for installation, and steps that must be followed to install the CIXCD option.

The sections include:

- Operating environment

- System configurations

- Unpacking and inventory

- Installation and configuration

- Backplane jumpers and configuration selection

# 3.1 Operating Environment

This section describes the system physical specifications that must be available to install the CIXCD option.

### 3.1.1 Physical Elements

The CIXCD option requires one I/O slot in the XMI backplane.<sup>1</sup>

There must be the equivalent of two available I/O connector panel openings in the appropriate cabinet<sup>2</sup> to hold the CI bulkhead cable connector panel. For VAX 6000 systems, there must be one 102 mm  $\times$ 102 mm (4 in  $\times$  4 in) opening or two adjacent 51 mm  $\times$  102 mm (2 in  $\times$ 4 in) openings. For VAX 9000 systems, there must be one available I/O connector panel opening (4.2 in square).

<sup>&</sup>lt;sup>1</sup> All XMI slots are I/O slots, except slot 7 in VAX 9000 systems, slots 6-9 in VAX 6000 mod. 500 systems, and slots 5-A in all other VAX 6000 systems.

<sup>&</sup>lt;sup>2</sup> CPU cabiant for VAX 6000 systems, I/O cabinet for VAX 9000 systems.

# 3.1.2 System Environment and Grounding Elements

Consult the appropriate system installation manual for information regarding system environment and grounding requirements.

# 3.2 System Configurations

The CIXCD option may be installed in many systems under many different circumstances. For VAX 9000 systems, it might be a new installation with the CIXCD option already installed, or it might be an existing standalone system being upgraded to add a CIXCD. For VAX 6000 systems, you might have an existing unclustered system being added to a cluster, or you might have a clustered system being upgraded from a CIBCA option to the CIXCD option.

For clustered VAX 6000 and VAX 9000 systems performing initial installation, since the module and hardware are already installed, go to Section 3.5.

For nonclustered VAX 9000 systems being upgraded to a clustered system, begin the installation at Section 3.4.2.

For nonclustered VAX 6000 systems being upgraded to a clustered system, go to Section 3.4.2 to start the installation.

For clustered VAX 6000 systems, with the CIBCA option, being upgraded to a CIXCD option, start the installation at Section 3.4.1.

# 3.2.1 VAXcluster Revision Levels

Ensure that the CIXCD hardware and microcode revision levels are consistent with the revision level of the cluster, which must be at least at the N1 level. Consult the VAXcluster Revision Matrix Document (K-RM-CLUSTER-V-0) for the latest information on N1. For the minimum acceptable revision levels, refer to Section C.1.

# 3.3 Unpacking and Inventory

The customer is responsible for the actual movement of the equipment to the installation site. Ensure that all equipment for the CIXCD option is moved to the designated installation site.

# 3.3.1 Unpacking the Shipping Boxes

- 1. Locate and open the box marked "OPEN ME FIRST". It contains the shipping/accessory list.

- 2. Notify the customer of any opened boxes or cartons, and document this fact on the installation report.

- 3. Check all boxes for external damage (dents, holes, or crushed corners).

- 4. Notify the customer of all damage, and list all damage on the installation report.

- 5. Open all remaining boxes.

## 3.3.2 Inventory

- 1. Check the shipment against the shipping/accessory list.

- 2. Inspect the equipment for damage. Note any damage on the installation report.

- 3. If damage is extensive, notify the Customer Service unit manager for instructions on how to proceed.

- 4. Notify the Customer Service unit manager of any missing or incorrect items.

- 5. Request that the customer contact the shipping carrier to locate any missing items.

- 6. Request that the Customer Service unit manager check with the Digital Equipment Corporation Traffic and Shipping Department if the shipping carrier does not have the missing items.

# 3.4 Installation and Configuration

There are three separate procedures involved in the installation of the CIXCD option. Installations require one, two. or all three of the following procedures. Perform them in the order listed.

- 1. Removal of the CIBCA option. This is required only on currently clustered systems that are upgrading to the CIXCD option. Refer to Section 3.4.1.

- 2. Installation of the CIXCD option. This is performed on all installations. Refer to Section 3.4.2.

3. Updating the VAX 6000 console microcode. This is required on any VAX 6000 systems with microcode that does not recognize the CIXCD. Refer to Section 3.4.3.

## 3.4.1 Removal of the CIBCA Option

This section describes the steps involved in removing the CIBCA option from VAX 6000 systems.

## CAUTION

Use an antistatic wrist ground strap when you work on a VAXBI system with its covers removed or when you handle any VAXBI module. Do not remove any module from the card cage until you have antistatic packaging ready for it.

- 1. Power down the system.

- 2. Open the front door of the cabinet and ground yourself with the attached wrist strap.

- 3. Open the Plexiglas doors to gain access to the modules.

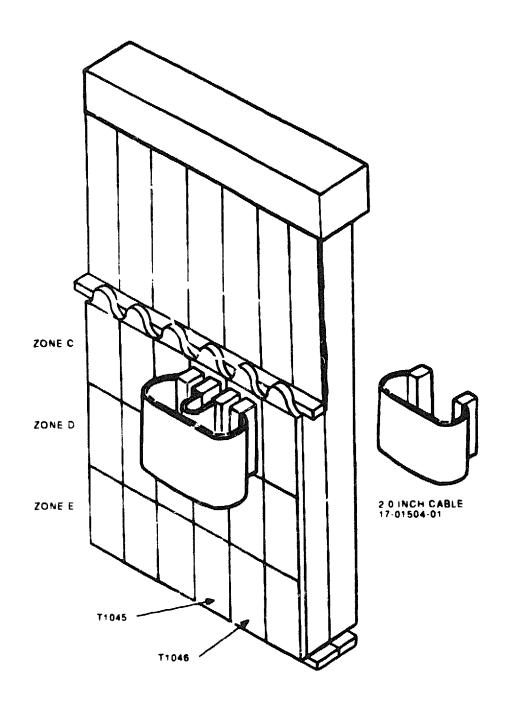

- 4. Remove the T1045 module and the adjacent T1046 module from the card cage, taking care to place each one in an antistatic package. Note the slot numbers.

- 5. Open the rear door of the cabinet and ground yourself with the attached wrist strap.

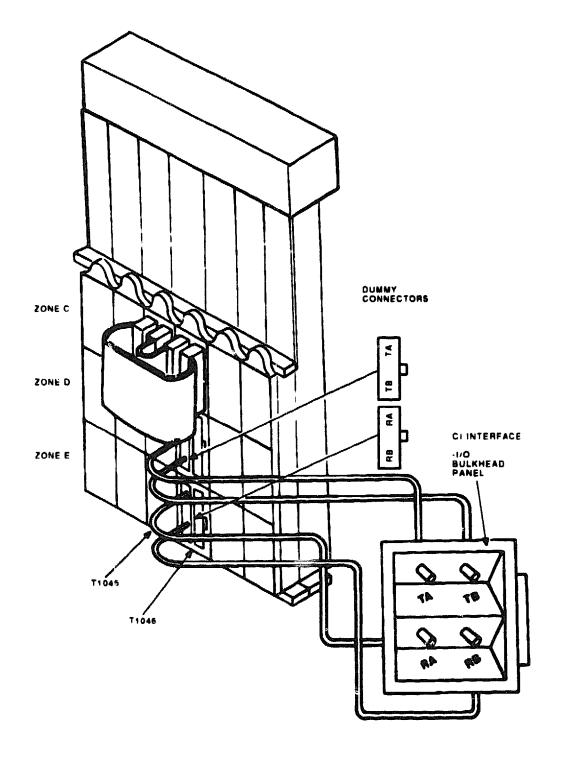

- 6. Checking for the correct slots, carefully remove the 51 mm (2 in) cable (the outermost one, PN 17-01504-01) from section C of the backplane. Then remove the inner cable (PN 17-01504-02). Refer to Figure 3-1.

- 7. Remove the internal CI bulkhead cables and the dummy connectors from sections D and E of the T1046 module slot. Refer to Figure 3-2.

MR. 80858.90 CPG

## Figure 3–1 CIBCA Intermodule Cables

## 3-6 Site Preparation and Installation

## Figure 3–2 CIBCA Cable Location

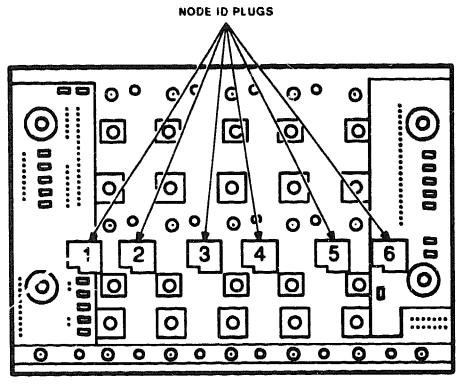

8. Remove the node ID plug from section A of the T1045 module slot. Refer to Figure 3-3.

VAXBI BACKPLANE

MR\_X0665\_90 CPG

#### Figure 3–3 Node ID Plug Location

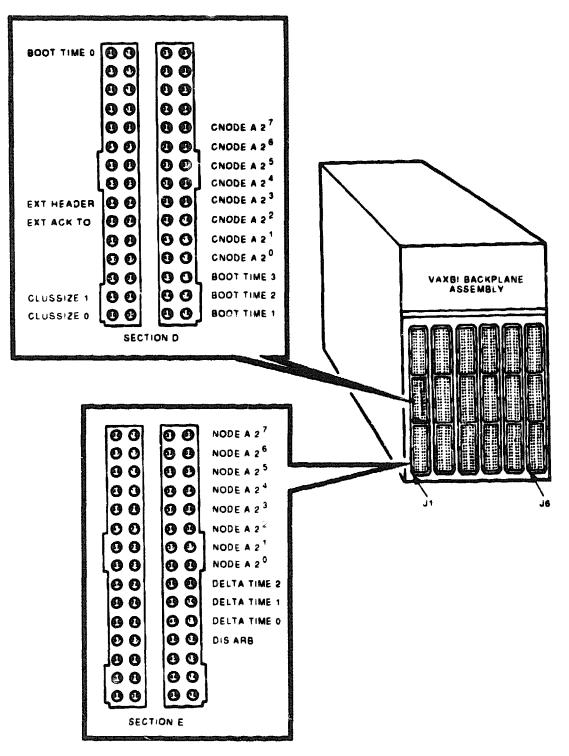

9. Remove all jumpers from sections D and E of the same slot. Refer to Figure 3-4.

Figure 3–4 CIBCA Jumpers

MR. X0660 80 CPG

## 3.4.2 Installation of the CIXCD Option

This section describes the steps required to install and connect the T2080-00 module (CIXCD option) to VAX 9000 systems.

## CAUTICN

You must use an antistatic wrist strap when you work on any VAX system with its covers removed or when you handle any XMI module. Do not remove any module from its antistatic packaging until you are ready to install it.

- 1. Power down the system.

- 2. Open the front door of the cabinet and ground yourself with the attached wrist strap.

- 3. Open the Plexiglas doors to access the XMI card cage.

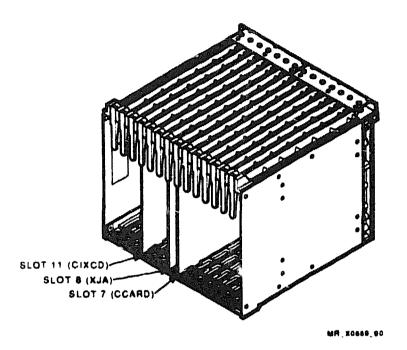

- 4. Remove the T2080-00 module from the antistatic package and carefully insert it into an unoccupied module slot in the XMI card cage (I/O slots only).

On VAX 6000 systems, you cannot configure the CIXCD in the center six slots (5-A) of the XMI card cage (the restriction for model 500 systems is slots 6-9). This area of the card cage is covered by the arbitration daughter card, so the header card and CIXCD configuration jumpers cannot be installed.

On the VAX 9000 systems, this restriction applies only to slot 7. All others are I/O slots.

Figure 3-5 shows the T2C80-00 module installed in the XMI card cage. Notice the proper module orientation in relation to side 1 of the module. Side 1 of the T2080-00 module has the greater number of components on it, and should be facing to the right, when viewing the module from the front of the cabinet.

#### 3-10 Site Preparation and Installation

Figure 3–5 CIXCD Module Installed In Card Cage

- 5. Close the Plexiglas doors and remove the wrist strap. Open the rear door of the cabinet and ground yourself with the attached wrist strap.

- 6. Install the configuration jumpers into the I/O header in zones D2 and E2 of the slot containing the T2080-00 module (refer to Figure 3-7).

- 7. Route the internal CIXCD bulkhead cables and install the I/O bulkhead panel.

- 8. Using a torque wrench (PN 29-27973-01), connect each of the CIXCD bulkhead cables to its corresponding coaxial connector on the header card (refer to Figure 1-2). The torque specification for this connector is 7-10 inch-pounds. The cables and their corresponding connectors are:

- TA J6TB = J5RA = J4RB = J3

9. Carefully insert the header card into the I/O headers in zones D1 and E1 of the slot containing the T2080-00 module. Side 1 of the card (with the cables attached) should be facing to the right as you view the backplane from the rear of the cabinet. The header cover is keyed, so the header card cannot be plugged in incorrectly. This also secures the header card to the backplane.

## NOTES

- 1. Unlike the CIBCA adapter for the VAXBI bus, the CIXCD does not use "dummy" connectors.

- 2. The header cover is keyed in such a way that the header card composity fit in D1/E1.

- 3. The recommended quiet slot time for all nodes in clusters is 10. A quiet slot time of 10 is *required* for all clusters that contain a CIXCD. Refer to Section C.2.

# 3.4.3 Updating the VAX 6000 Console Microcode

Some VAX 6000 systems must have updated console microcode to boot through the CIXCD. This section describes the steps required to determine if the update is needed and to perform the update.

## 3.4.3.1 Determining the Need for Updated Microcode

At the >>> prompt, issue the SHOW CONFIGURATION command. If the system does not recognize the CIXCD, then it needs updated microcode. Refer to Examples 3-1 and 3-2.

## NOTE

The XMI device type code for the CIXCD is 0C05.

1

```

>>> SHOW CONFIG

Type

Rev

1+ KA64A (8001) 8002

2+ MS62A (4001) 0002

4+ ??????? (0C05) 0621

D+ DWMBA/A (2001) 0002

E+ DWMBA/A (2001) 0002

XBI D

1+ DWMBA/B (2107) 0007

5+ DMB32 (0109) 210B

6+ DEBNA (410F) 0248

XBI E

1+ DWMBA/B (2107) 0007

2+ KDB50 (010E) OF1C

6+ TBK50 (410E) 0248

>>>

```

#### Example 3–1 SHOW CONFIGURATION With Old Microcode

```

>>> SHOW CONFIG

Type

Rev

1+ KA64A (8001) 8002

2+ MS62A

(4001) 0002

4+ CIXCD (0C05) 0621

D+ DWMBA/A (2001) 0002

E+ DWMBA/A (2001) 0002

XBI D

1+ DWMBA/B (2107) 0007

5+ DMB32 (0109) 210B

6+ DEBNA (410F) 0248

XBI E

1+ DWMBA/B (2107) 0007

2+

KDB50 (010E) 0F1C

6+ TBK50 (410E) 0248

>>>

```

### Example 3–2 SHOW CONFIGURATION With New Microcode

### 3.4.3.2 Performing the Update

- 1. Locate and insert the update tape cartridge into the TK tape drive following these steps:

- a. Check that the tape drive LOAD/UNLOAD button is out and the power is on.

- b. Open the drive door by pushing the cartridge-release handle to the left.

- c. Hold the tape cartridge with the write-protect switch up, the arrow on the side of the cartridge pointing toward the tape drive.

- d. Insert the cartridge into the TK drive.

- e. Close the door by firmly moving the cartridge-release handle to the right.

- f. Depress the LOAD/UNLOAD button.

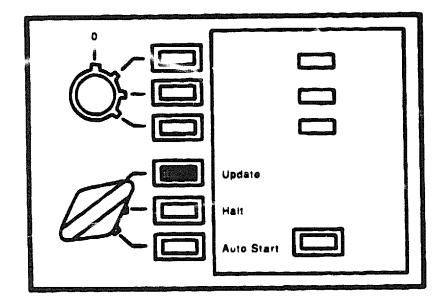

- 2. Turn the lower keyswitch to the Update position. Refer to Figure 3-6.

MR. 10661 90 CPG

#### Figure 3-6 The Update Position

3. At the >>> prompt, type the PATCH EEPROM command, and reply "Y" to the PROCEED? query.

```

>>>

>>> PATCH EE

?6D EEPROM Revision = 2.0/4.4

?6F Tape image Revision = 2.0/4.E

Proceed with EEPROM update? (Y or N) >>> Y

?69 EEPROM changed successfully.

>>>

>>>

```

- 4. If the VAX 6000 system is a multiprocessor system, the new console microcode must be propagated to all other processors. At the >>> prompt, type in the UPDATE ALL command.

- 5. Check that the new microcode has been correctly loaded into the system. At the >>> prompt, type the INITIALIZE command. Check the microcode revision level listed in the last line of the printout.

- 6. The VAX 6000 is now ready to boot through the CIXCD.

5

```

>>>

>>> PATCH FF

26D EEPROM Revision = 2.0/4.4

?6F Tape image Revision = 2.0/4.E

Proceed with EEPROM update? (Y or N) >>> Y

269 EEPROM changed successfully.

>>>

>>> I

F

Ε

2

С

B

A

9

8

7

6

5

4

3

2

1

0

NODE .

P

Ρ

A

A

A

M

P

TYP

.

.

•

.

0

•

+

+

STF

+

+

•

٠

•

•

£

Ε

B

BPD

.

•

•

.

.

.

.

•

•

.

•

ETF

÷

÷

+

.

.

.

.

.

.

.

.

.

.

.

Ξ

Ε

B

BPD

.

•

.

.

٠

.

٠

.

-

.

.

XBIE +

+

.

.

•

•

.

.

٠

+

.

.

.

.

.

A1

ILV

•

•

.

.

•

.

.

.

.

.

•

.

٠

32

32 Mb

.

.

.

.

.

•

.

.

.

.

•

.

ROM = 3.1 EEPROM = 2.0/4.E SN = AG84102189

?2D For Secondary Processor 4

253 EEPROM revision mismatch. Secondary processor has revision 2.0/4.4

22D For Secondary Processor 5

253 EEPROM revision mismatch. Secondary processor has revision 2.0/4.4

>>>

>>>

>>> U ALL

>>>

>>> I

F

D

С

7

0

NODE .

E

8

A

9

8

6

5

4

3

2

1

P

P

TYP

A

A

A

Μ

Ρ

.

.

•

.

•

٠

.

STF

0

+

+

+

+

+

.

•

+

•

•

.

.

.

Ε

BPD

E

в

.

•

•

.

•

٠

•

.

.

•

.

+

+

+

ETF

.

٠

.

.

٠

•

•

٠

٠

.

•

в

Ε

ε

BPD

.

.

.

.

.

.

.

.

XBIE+

+

+

+

.

.

٠

٠

.

٠

•

.

.

•

•

.

•

ILV

A1

.

.

.

.

.

•

.

.

.

.

.

.

•

32 Mb

32

.

.

٠

٠

٠

٠

.

.

ROM = 3.1 EEPROM = 2.0/4.E SN = AG84102189

>>>

>>>

```

#### Example 3-3 Updating VAX 6000 Console Microcode

# 3.5 Backplane Jumpers and Configuration Selection

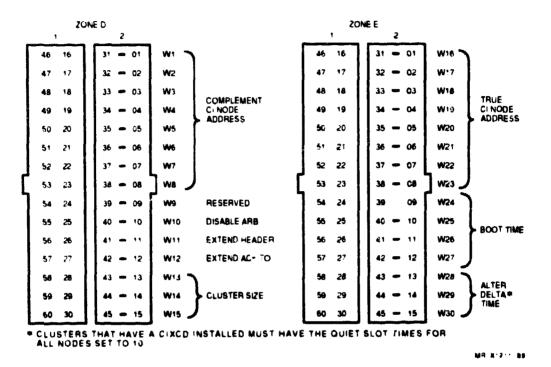

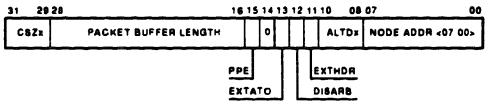

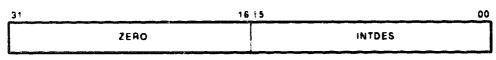

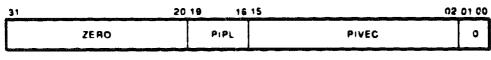

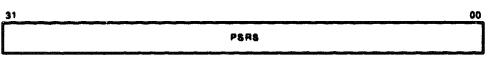

To correctly configure the CIXCD, place the jumpers in the correct place in the backplane. The XMI bus backplane-pin numbering is the same as the VAXBI bus backplane-pin numbering. There are 29 possible pins that may need jumpers on the backplane, in sections D and E of the backplane. The corresponding jumpers are denoted W1 through W30, with W9 being reserved. Refer to Figure 3-7 to determine which jumper corresponds to which backplane pin. Note that the jumpers are only placed in zones D2 and E2.

The functions that can be modified by jumper placement are the following:

- CI node address

- Bcot time

- Disable arbitration

- Extend header

- Alter delta time (quiet slot time)

- Cluster size

- Extend ACK timeout

## Figure 3–7 CIXCD Jumper Pinning

## 3.5.1 Ci Node Address

The CI node address is obtained from the CIXCD port adapter module's backplane slot, with both the CI node address and its complement configured exactly the same. To configure the jumpers for the node's address, refer to Table 3-1 for the true-address and the complement-address configurations.

|                        |              |              |              | True A       | ddrees       |              |              |              |

|------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| CI<br>Node<br>Addr(10) | W16<br>E1/31 | W17<br>E2/32 | W18<br>E3/33 | W19<br>E4/34 | W20<br>E6/35 | W21<br>E6/36 | W22<br>E7/37 | W23<br>E8/38 |

| 0                      | Out          |

| 1                      | Out          | In           |

| 2                      | Out          | Out          | Out          | Out          | Out          | Out          | In           | Out          |

| •                      |              |              |              |              |              |              |              |              |

|                        |              |              |              | •            |              |              |              |              |

|                        |              |              |              |              |              |              |              |              |

| 223                    | In           | In           | Out          | In           | In           | In           | In           | In           |

| <u></u>                | <u></u>      | <u> </u>     | Co           | mpleme       | nt Addre     | :60          |              | <b></b>      |

| CI<br>Node<br>Addr(10) | W1<br>D1/31  | W2<br>D2/32  | W3<br>D9/33  | W4<br>D4/34  | D5<br>D5/35  | D6<br>D6/36  | D7<br>D7/37  | D8<br>D8/38  |

| 0                      | Out          |

| 1                      | Out          | In           |

| 2                      | Out          | Out          | Out          | Out          | Out          | Out          | In           | Out          |

|                        |              |              |              |              |              |              |              |              |

|                        |              |              |              |              |              |              |              |              |

|                        |              |              |              |              |              |              |              |              |

| 223                    | In           | In           | Out          | In           | In           | ĺn           | In           | In           |

## Table 3-1 CI Node Address Table - True/Complement

#### NOTES

CI node addresses 224 through 255 are reserved for Digital Equipment Corporation.

The address in the complement address field must be exactly the same as the address in the true address field.

## 3.5.2 Boot Time

The boot time is the length of time the port will wait after powerup to exit the uninit state. Refer to Table 3-2 for the correct jumper configuration. All jumpers out is the default configuration.

## NOTE

The boot time is the maximum length of time the port will wait after power-up to exit the uninit state. In normal operation, the port will exit this state in conjunction with the virtual machine bootstrap (VMB) long before exhaustion of this timer. To ensure proper operation, all jumpers must be left in the default (out) configuration.

| lime         | W24<br>E9 | 39  | W25<br>E10/40 | <b>W25</b><br>E11/41 | W27<br>E12/42 |  |

|--------------|-----------|-----|---------------|----------------------|---------------|--|

| 500          | Out       | Out | Out           | Out                  | (Default)     |  |

| <b>40</b> 0  | Out       | Out | Out           | In                   |               |  |

| 300          | Out       | Out | In            | Out                  |               |  |

| 200          | Out       | Out | In            | In                   |               |  |

| 100          | Out       | In  | Out           | Out                  |               |  |

| 000          | Out       | In  | Out           | In                   |               |  |

| · <b>900</b> | Out       | In  | In            | Out                  |               |  |

| 1800         | Out       | In  | In            | In                   |               |  |

| 700          | In        | Out | Out           | Out                  |               |  |

| 600          | In        | Out | Out           | In                   |               |  |

| )500         | In        | Out | In            | Out                  |               |  |

| <b>)400</b>  | In        | Out | In            | In                   |               |  |

| 0300         | In        | In  | Out           | Out                  |               |  |

| 0200         | In        | In  | Out           | In                   |               |  |

| 0100         | In        | In  | In            | Out                  |               |  |

| 0000         | In        | In  | In            | In                   |               |  |

## Table 3-2 Boot Time Backplane Jumpers

## 3.5.3 Disable Arbitration

The disable arbitration bit, when set, defeats the normal arbitration sequence and allows the CI controller logic to transmit after waiting only one basic quiet slot (delta) time. The jumper that controls this bit is W10 (D10/40).

| Jumper out = | Allow normal C | I arbitration (default) |

|--------------|----------------|-------------------------|

|--------------|----------------|-------------------------|

Jumper in = Disable normal CI arbitration

## 3.5.4 Extend Header

Jumper W11 (D11/41) controls the extend header bit that, when set, allows the CI controller logic to extend the number of bit sync characters in the header.

| Jumper out | = | Normal header (default) |

|------------|---|-------------------------|

| jumper in  | = | Extended header         |

## 3.5.5 Alter Delta Time

These bits force the CI controller logic to increase the basic quiet slot delta time. Refer to Table 3-3 for the configurations.

| 16Dig 3-3           | Guier Stor Time      | - Decription  | e naulhais    |                              |

|---------------------|----------------------|---------------|---------------|------------------------------|

| Quiet<br>Slot Count | <b>W28</b><br>E13/43 | W29<br>E14/44 | W30<br>E15/45 |                              |

| 7                   | Out                  | Out           | Out           |                              |

| 10                  | Out                  | Out           | In            | (Required setting for CIXCD) |

| Reserved            | Out                  | In            | Out           |                              |

| Reserved            | Out                  | In            | In            |                              |

| Reserved            | In                   | Out           | Out           |                              |

| Reserved            | In                   | Out           | In            |                              |

| Reserved            | In                   | In            | Out           |                              |

| Programmat          | ole In               | In            | In            |                              |

Table 3-3 Quiet Slot Time Backplane Jumpers

### NOTE

For clusters that have a CIXCD installed, all nodes in that cluster must have their quiet slot time set for 10. Refer to Section C.2.

## 3.5.6 Cluster Size

The cluster size bits cause the arbitration logic to arbitrate for more than 16 nodes (which is the default). If any node in the cluster has a node number greater than 15, the appropriate cluster size must be indicated with these jumpers. Refer to Table 3-4 for the configurations.

| Node Count | W13<br>D13/43 | W14<br>D14/44 | W15<br>D15/45 |           |

|------------|---------------|---------------|---------------|-----------|

| .6         | Out           | Out           | Out           | (Default) |

| 2          | Out           | Out           | In            |           |

| 4          | Out           | In            | Out           |           |

| 28         | Out           | In            | In            |           |

| 4          | In            | Out           | Out           |           |

| eserved    | In            | Out           | In            |           |

| eserved    | In            | In            | Out           |           |

| eserved    | In            | In            | In            |           |

## Table 3-4 Cluster Size Backplane Jumpers

## 3.5.7 Extend ACK Timeout

The extend ACK timeout bit forces the CI controller logic to increase the timeout period for an ACK return. The jumper that represents this bit is W12 (D12/42).

| Jumper out | 2 | Short timeout (default) |

|------------|---|-------------------------|

| Jumper in  | Z | Long timeout            |

## NOTE

A system with no jumpers would be configured in the following way:

- CI node address = 0

- Boot time = 1500 s

- Normal CI arbitration

- Normal header

- Quiet slot delta time = 7

- Cluster size = 16

- Short ACK timeout

YYYYYYYYYYYYYYYYYYYYYYYYYYYYYYYYY KNEXKKXXXXXXXX XXXXXXXXXX XXXXXXX XXXXX XXX X

# **Verification and Acceptance Testing**

This chapter describes the procedures to verify that the system is in good working condition. The sections include:

- Diagnostic verification

- System maintenance tools

# 4.1 Diagnostic Verification

After completing the CIXCD installation, verify that the system works as it is supposed to. This section lists the steps required to test out the system.

# 4.1.1 Diagnostic Programs

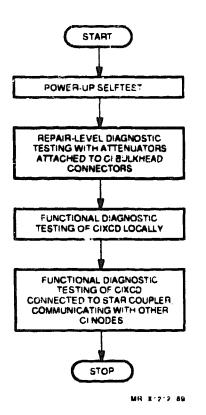

There is a specific set of diagnostic programs used to determine if the CIXCD adapter is working properly. Figure 4-1 describes the testing procedure for the CIXCD, while Table 4-1 lists the diagnostic programs that must be run as part of this procedure.

Figure 4–1 CIXCD Acceptance Testing Flow Diagram

| Program<br>Designation                | Program<br>Level                  | Program<br>Title               |  |  |  |  |

|---------------------------------------|-----------------------------------|--------------------------------|--|--|--|--|

| XCDST 5                               |                                   | CIXCD self-test                |  |  |  |  |

| EVGEA 3 CIXCD repair-level diagnostic |                                   |                                |  |  |  |  |

| EVGEB                                 | 3                                 | CIXCD microcode update utility |  |  |  |  |

| EVGAA                                 | VGAA 3 CI functional diagnostic 1 |                                |  |  |  |  |

| EVGAB                                 | 3                                 | CI functional diagnostic 2     |  |  |  |  |

| EVGAC 3 Cluster functional diagnostic |                                   |                                |  |  |  |  |

| EVXCI                                 | EVXCI 2R CI exerciser diagnostic  |                                |  |  |  |  |

| Table 4-1 | CIXCD | Diagnostic | Programs |

|-----------|-------|------------|----------|

|-----------|-------|------------|----------|

## 4.1.2 Power-Up Self-Test

After a system power-up or reset, the CIXCD runs its self-test (XCDST), which provides logic level testing for the module. It is designed to provide coverage of > 95% of all possible "stuck at" faults.

After successfully completing XCDST, the CIXCD turns on its yellow self-test LED. The pass/fail information is also available to the console terminal. To get the steps necessary to retrieve this information, refer to the VAX 9000 Model 200 Hardware User Guide.

On VAX 6000 systems, there is console printout at power-up that shows the status of the system elements, including the CIXCD. Example 4-1 shows a console printout in which the CIXCD is at node C.

| F | Ē | D | с | B | A | 9          | 8  | 7  | 6          | 5 | 4 | 3 | 2 | 1 | 0 | NODE .  |

|---|---|---|---|---|---|------------|----|----|------------|---|---|---|---|---|---|---------|

|   | A | A | A |   |   | M          | м  | м  | M          |   | P | P | Ρ | Ρ |   | TYP     |

|   | 0 | 0 | • |   |   | •          | •  | •  | •          | • | ٠ | ٠ | + | + |   | STF     |

|   |   |   |   |   |   |            |    |    |            |   | £ | E | D | 8 |   | BPD     |

|   |   |   |   |   |   |            |    |    |            |   | + | + | ٠ | ٠ |   | ETF     |

|   | • | • | • | • | • | •          |    | •  | •          | • | E | E | D | В |   | BPD     |

|   |   | • | • | • |   |            |    |    |            | • | - | ٠ | • | ~ | + | XBI D + |

| • | • |   | • | • | • | •          | •  | •  | •          | + | • | • | + | • | + | XBI E • |

|   | • | • |   |   |   | <b>A</b> 4 | A3 | A2 | <b>A</b> 1 |   | • |   |   | • |   | ILV     |

|   | - | • | • | • | • | 32         | 32 | 32 | 32         | • | • | • | • | • |   | 128MB   |

### Example 4-1 VAX 6000 Console Printout

In this system, the CIXCD is node C and it passed its self-test. This is shown by the plus sign (+) in the third row (labeled on the right side with "STF"). We can tell that nodes D and E are not CIXCDs because they have an "o" in the self-test row, which indicates that they did not run a selftest, and the DWMBA/A is the only option that does not run self-test. The notation for failing self-test is the minus sign (-). For more information about this printout, refer to the VAX 6000-400 System Technical User's Guide (EK-640EB-TM).

## 4.1.3 Preliminary Diagnostic Setup

Prior to running the macrodiagnostics, you must set up the system both hardware- and software-wise. The hardware setup requires the installation of CI bus loopback connectors; the software setup requires the running of the VAX Diagnostic Supervisor ("'DS) program.

### 4.1.3.1 Loopback Connectors

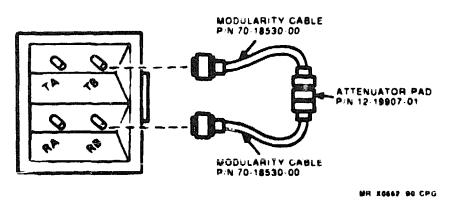

Before running the diagnostics, make the following CI bus loopback connections on the CI bulkhead connector panel located at the back of the panel (refer to Figure 4-2).

- 1. Using one of the attenuator pads (PN 12-19907-01) and two of the modularity cables (PN 70-18530-00), connect the transmit A to receive A.

- 2. Perform the same connection for path B using another attenuator pad and two more modularity cables, connecting transmit B to receive B.

## Figure 4–2 Diagnostic Loopback Cable Connections

## 4.1.3.2 Loading the VAX Disgnostic Supervisor (VDS) Program

The level 3 diagnostics are stand-alone programs that require the support of VDS in order to run. Follow the steps listed below:

- 1. Load VDS into physical memory from the console load device. This procedure can vary, depending on the type of system in which the CIXCD is being installed. (Refer to the applicable system installation manual for the VDS load and run procedures.)

- 2. Identify the CIXCD adapter to VDS, specifying its node configuration parameters. The ATTACH/SELECT sequence of VDS varies according to the system.

### NOTE

Before installing the CIXCD hardware, you should be familiar with the ATTACH and SELECT sequences of VDS for the processor that is used.

If VDS is loaded through a CIXCD, VDS assigns the designation PAA0 to that CIXCD. Other CIXCDs to be tested should be assigned other designations (for example, PAB0 or PAC0). Be careful to avoid the command SELECT ALL under these circumstances, as it will cause PAA0 to be tested. (Not booting through the CIXCD allows you to use both the PAA0 designation and the SELECT ALL command.)

VAX 6000 example:

DS> ATTACH CIXCD HUB PABO C 5

## VAX 9000 example:

DS> ATTACH XJA HUB XJAO O 8 DS> ATTACH CIXCD XJAO PABO 3 7

## 3. Select the CIXCD adapter as the test unit, as follows:

DS> SELECT PABO, XJAO

#### 4. Show the unit selected, as follows:

DS> SHOW SELECT

## 4.1.4 Repair-Level Testing

The repair-level diagnostic for the CIXCD is EVGEA. You must successfully complete five passes of this program to satisfy acceptance testing requirements.

- 1. Ensure that the diagnostics are accessible through the default load path during diagnostic acceptance testing. This might require changing diagnostic media in the current load-path device.

- 2. Load EVGEA, as follows:

DS> LOAD EVGEA

- 3. Set the desired VDS control flags:

- Enable printing of the number and title of each test before it runs.

- Enable halting on a detected error.

DS> SET FLAGS TRACE, HALT

4. Start the diagnostic program.

DS> START/PASS:5

Example 4-2 provides trace printouts for EVGEA.

```

DS> st/pass:1

.. Program: EVGEA CIXCD Functional Level 3 Diag, revision 2 0, 25 tests,

at 13:53:14.27.

Testing: PABO

Test - 1 Scan Data Path Verification

Subtest - 1 Scan Data Register Loopback

Subtest - 2 Port Scan Control Register

Subtest - 3 Port Scan Shift Register

Subtest - 4 PMCS RAM Data Path

Test - 2 PMCS EEPROM region Checksum

Subtest - 1 Backup region Functional Microcode Checksum

Subtest - 2 Primary region Functional Microcode Checksum

Subtest - 3 Backup region Self-test Microcode Checksum

Subtest - 4 Primary region Self-test Microcode Checksum

Test - 3 PMCS RAM Memory

Test - 5 CIXCD Node RESET

Subtest - 1 Run Self-test via XBER NRST - Check XBER status

Subtest - 2 XMOV loads RAM from EEPROM - Check XMOV and RAM data

Test - 6 Scan Visibility Bus CS Address Field

Loading Microcode file EVGEA.BIN

Test - 7 XMI Device (XDEV) and Port Serial Number Register (PSNR)

Test - 8 ROM Based Diagnostic Interface

Subtest - 1 RBD 0 - Power Up Self-test

Subtest - 2 RBD 2 Test 1 - Port Local Store Data Integrity

Subtest - 3 RBD 2 Test 2 - Port Local Store Address Independence

Subtest - 4 RBD 2 Test 3 - Port Local Store Literal Addressing

Subtest - 5 RBD 2 Test 4 - Port Local Store TCB Base Relative Addressing

Subtest - 6 RBD 3 Test 1 - Port Packet Buffer Data Integrity

Subtest - 7 RBD 3 Test 2 - Port Packet Buffer Address Independence

Subtest - 8 RBD 4 - MMI Commander

Subtest - 9 RBD 1 - Verify CI jumpers

Subtest - 10 RBD 1 - External Loopback on Path A

Subtest - 11 RBD 1 - External Loopback on Path B

.. End of run, 0 errors detected, pass count is 1,

time is 30-MAR-1990 13:54:13.34

DS>

```

#### Example 4-2 Trace Printout for EVGEA (One Pass)

# 4.1.5 CI Functional Level Testing

With the CI bus cables and attenuator pads providing signal loopback, load and run the CI functional diagnostics EVGAA and EVGAB. You must successfully complete a minimum of five passes of each diagnostic program to satisfy acceptance testing requirements. Examples 4–3 and 4–4 show trace printouts for EVGAA and EVGAB respectively.

- 1. Ensure that the diagnostics are accessible through the default load path during diagnostic acceptance testing. This might require changing diagnostic media in the current load-path device.

- 2. Load the EVGAA diagnostic program.

DS> LOAD EVGAA

- 3. Set the desired VDS control flags:

- a. Enable printing of the number and title of each test before it runs.

- b. Enable halting on a detected error.

DS> SET FLAGS TRACE, HALT

4. Start the EVGAA diagnostic program.

DS> START/PASS:5

5. After five successful passes of EVGAA, load and run EVGAB.

DS> LOAD EVGAB DS> START/PASS:5

- 6. Disconnect the attenuators from the ends of the CI bus cables in preparation for routing and connecting the cables to the star coupler.

- 7. Route and connect the cables to the star coupler.

#### NOTE

For information on connecting the coaxial CI bus cables, refer to the SC008 Star Coupler User's Guide.

8. Repeat steps 2, 4, and 5 of this procedure.

#### 4-10 Verification and Acceptance Testing

DS> st/pass:1

.. Program: EVGAA - CI Functional Part 1, Level 3, revision 6.0, 17 tests at 11:58:12,80. Testing PABO Event Flag 1 SET = Load CI Microcode Event Flag 2 SET = Print Queue Entries Event Flag 3 SET = REQID Loop Function in Test 1 Testing Device PABO EEPROM Revision = 0020 Functional Revision = 00FC Test 1: Cluster Configuration Cluster Configuration for Path A \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* You CANNOT Differentiate between a CI780, CI750, or a CIBCI remotely. (PS = Pair Select, TP = Transmit Path, RP = Receive Path) Hard Soft Extended Port PIR Node Cevice Path Number Type Status Rev. Rev. Functionality SPP \_\_\_\_\_ \_\_\_\_\_ \_\_\_\_\_ ------------------ - -32 CINCD 0001 0001 OFFF8100 (X) OK AAA 0D HSC50 0001 00000000 (X) OK AAA Cluster Configuration for Path B \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* You CANNOT Differentiate between a CI780, CI750, or a CIBCI remotely. (PS = Path Select, TP = Transmit Path, RP = Receive Path) Node Device Hard Soft Extended Port Path PTR Number Type Rev. Rev. Functionality Status SPP \_\_\_\_\_ ---------------------- - -02 0001 0001 CINCO OFFF8100(X) OK **B B B** CC HSC50 0001 2000000 (X) OK 888 Nodes NOT Listed do not exist on Cluster Test 2: SFICKI with Various Masks and M Values Test 3: SETCKT for Each Valid Port Test 4: SETCKT for Invalid Port Test 5: REQID Basic REQID With 6 Packets on DGFQ Test 6: Test 7: Datagram Discard Test 8: Response Queue Available Interrupt Test 9: Send Datagram Test 10: SNDMSG With No Virtual Circuit Open Test 11: Send Message Crossing Page Boundary Test 12: Message Length Test Test 13: Packet Size Violation Test 14: Send Loopback (SNDLB) SNDIB Full Buffer on Path A Test 15: Test 16: SNDLB Full Buffer on Path B Test 17: SNDLB Automatic Path Selection .. End of run, 0 errors detected, pass count is 1, time is 02-APR-1990 11:58:36.40 25> Example 4-3 Trace Printout for EVGAA (One Pass)

A STATE OF A

```

DS> st/passil

., Program: EVGAB - CI Functional Part II, Level 3, revision 6.0, 12 tests

at 12:05:24.83

Testing PABO

Event Flag 1 SET = Load CI Microcode

Event Flag 2 SET - Print Queue Entries

Event Flag 3 SET = Not Used By This Diagnostic

Testing Device PABO

EEPROM Revision = 0020

Functional Revision = COPC

lest 1: Send Data with Offset Combinations

Test 2: Request Data with Offset Combinations

Test 3: Invalidate Translation Cache

Test 4: SNDMDAT in Enabled/Maintenance State

Port functionality does not support this test

Test 5: SNDMDAT in Enabled State

Port functionality does not support this test

Test 6: REQMDAT in Enabled/Maintenance State

Port functionality does not support this test

lest ": REQMDAT in Enabled State

Port functionality does not support this test

Test 8: SEND RESET in Enabled State

Test 9: Queue Protocol

Test 10: Buffer Read Access

Test 11: Buffer Write Access

Test 12: Write to Global Buffer

.. End of run, 0 errors detected, pass count is 1.

time is 02-APR-1990 12:05:47.34

282

```

#### Example 4-4 Trace Printout for EVGAB (One Pass)

#### 4.1.6 System Functional Level Testing

With the CIXCD still connected to the star coupler, load and run the system functional diagnostic EVGAC. You must successfully complete a minimum of five passes of this diagnostic program to satisfy acceptance testing requirements.

- 1. Ensure that the diagnostics are accessible through the default load path during diagnostic acceptance testing. This might require changing diagnostic media in the current load-path device.

- 2. Load the EVGAC diagnostic program.

DS> LOAD EVGAC

#### 3. Set the desired VDS control flags:

- a. Enable printing of the number and title of each test before it runs.

- b. Enable halting on a detected error.

DS> SET FLAGS TRACE, HALT

4. Start the EVGAC diagnostic program.

DS> START/PASS:5

#### Example 4-5 shows trace printouts for EVGAC.

```

DS> st/pass:1

.. Program: EVGAC - CI Functional Exerciser, revision 1.1, 8 tests

at 11:51:09.89.

Testing _PAB0

Test 1: Local Configuration

Test 2: Local Adapter Test

Test 3: Datagram Test

Test 4: Virtual Circuits Test

Test 5: Message Test

Test 5: Message Test

Test 6: Multiple Message Test

Test 6: Activity Test

.. End of run, 0 errors detected, pass count is 1,

time is 02-APR-1990 11:55:53.84

DS>

```

## Example 4-5 Trace Printout for EVGAC (One Pass)

# 4.2 System Maintenance Tools

In addition to the specified stand-alone diagnostics, there are some additional tools available to verify the CIXCD adapter. Table 4-2 provides a summary of the VAXcluster system maintenance tools.

| Tool         | Function                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EVXCI        | A level 2R multipurpose exerciser that provides local<br>CI interface functional testing, as well as a means to<br>determine the ability of VAXcluster nodes to reliably<br>communicate using the CI bus.                                                                                                         |  |  |  |  |  |  |

| ERF          | The Errorlog Report Formatter. The user may create reports with the system errors catalogued in various ways. <sup>1</sup>                                                                                                                                                                                        |  |  |  |  |  |  |

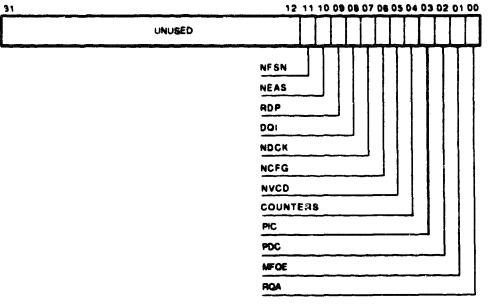

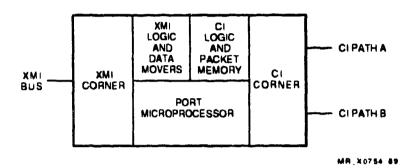

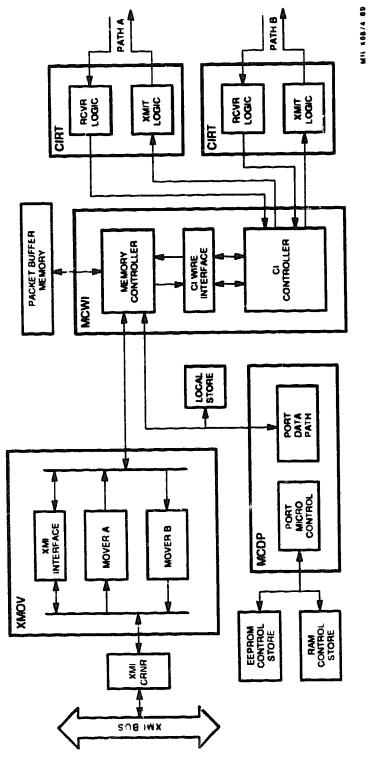

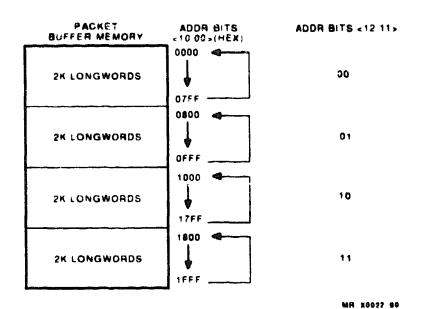

| VAXsim       | A VAX System Integrity Monitor utility program<br>that monitors and filters errors as they are logged<br>by the VMS operating system. The VAXsim program<br>provides the user with a warning mechanism that<br>quickly identifies an option that has either failed or has<br>degraded operationally. <sup>2</sup> |  |  |  |  |  |  |