BA11-L mounting box technical manual

digital

# BA11-L mounting box technical manual

digital equipment corporation • maynard, massachusetts

### Copyright © 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

# CONTENTS

| CHAPTER 1   | CHARACTERISTICS AND SPECIFICATIONS                                 |

|-------------|--------------------------------------------------------------------|

| 1.1         | GENERAL1-1                                                         |

| 1.2         | PHYSICAL CHARACTERISTICS OF THE BA11-L1-2                          |

| 1.3         | H777 POWER SUPPLY1-6                                               |

| 1.4         | H775A BATTERY BACKUP UNIT1-11                                      |

| 1.5         | REMOTE POWER CONTROL                                               |

| CILL DTED A |                                                                    |

| CHAPTER 2   | BACKPLANE CONFIGURATIONS AND INSTALLATION INFORMATION              |

| 2.1         | GENERAL                                                            |

| 2.2         | PHYSICAL DESCRIPTION                                               |

| 2.3         | ELECTRICAL DESCRIPTION                                             |

| 2.3.1       | Non-Processor Grant (NPG) Line2-7                                  |

| 2.3.2       | Bus Grant (BG) Lines2-7                                            |

| 2.4         | POWER HARNESŚ2-8                                                   |

| 2.5         | INSTALLATION                                                       |

| 2.5.1       | Backplane Installation                                             |

| 2.5.2       | Electrical Requirements                                            |

| CHAPTER 3   | H777 POWER SUPPLY                                                  |

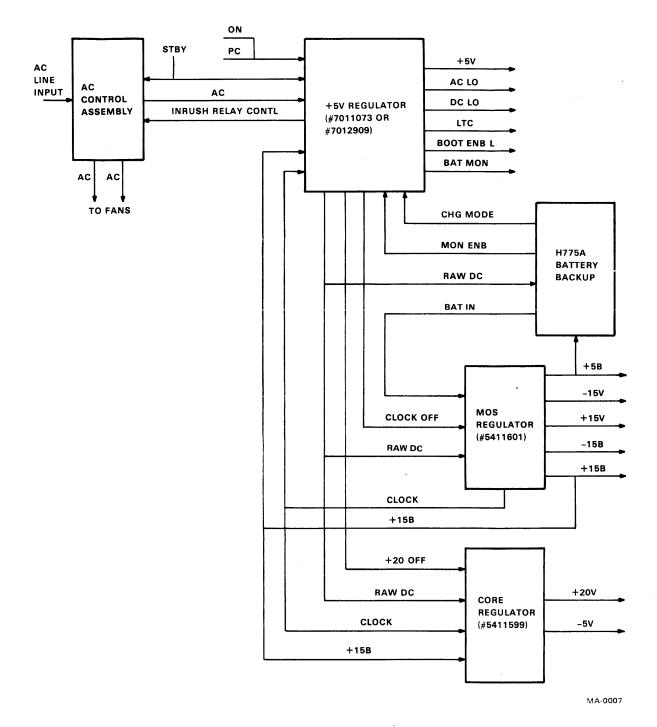

| 3.1         | GENERAL                                                            |

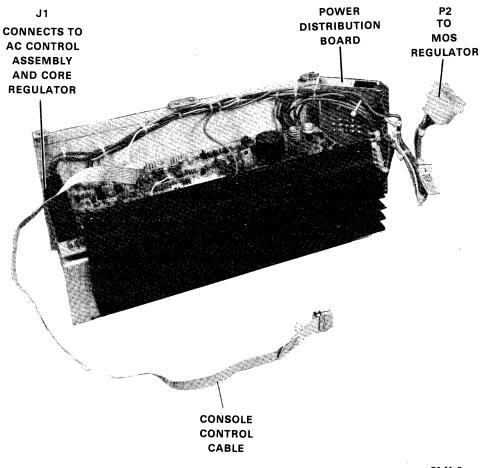

| 3.2         | H777 PHYSICAL DESCRIPTION                                          |

| 3.3         | H777 FUNCTIONAL DESCRIPTION                                        |

| 3.4         | DETAILED DISCUSSION                                                |

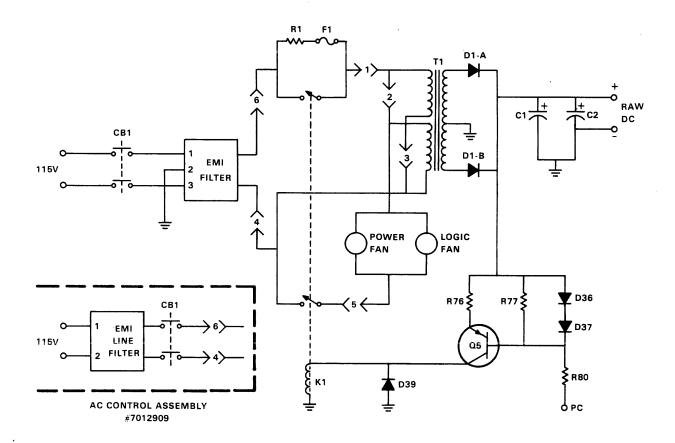

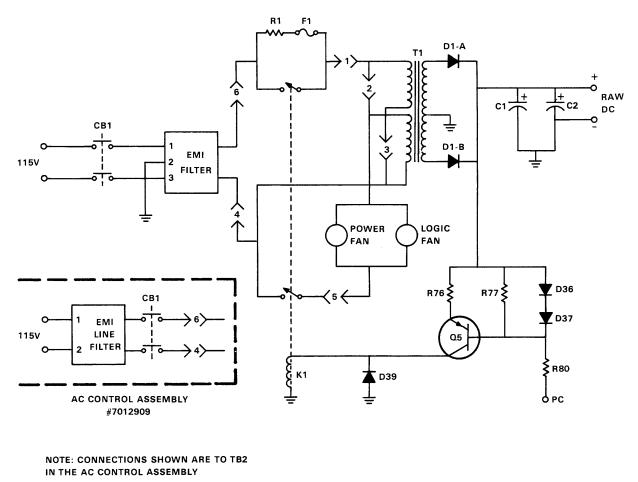

| 3.4.1       | Raw DC Circuit                                                     |

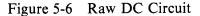

| 3.4.2       | MOS Regulator (Part 5411601)3-5                                    |

| 3.4.2.1     | Functional Description                                             |

| 3.4.2.2     | Master Clock                                                       |

| 3.4.2.3     | ±15B Circuit Detailed Description                                  |

| 3.4.2.4     | +5B Circuit Detailed Description                                   |

| 3.4.3       | Core Regulator (Part 5411599)                                      |

| 3.4.3.1     | Functional Description                                             |

| 3.4.3.2     | +20 V Circuit Detailed Description                                 |

| 3.4.3.3     | -5 V Circuit Detailed Description                                  |

| 3.4.4       | +5 V Regulator (Parts 7011073 and 7012909)3-32                     |

| 3.4.4.1     | Functional Description                                             |

| 3.4.4.2     | +5 V Circuit Detailed Description                                  |

| 3.4.4.3     | Power Sequence Control Circuit Detailed Discussion                 |

| 3.4.4.4     | Battery Monitor Circuit                                            |

| 3.4.4.5     | Boot Enable Circuit                                                |

| 3.4.4.6     | Line Time Clock (LTC) Circuit (Print Set Drawing 35411597-0-1)3-49 |

# **CONTENTS (CONT)**

#### CHAPTER 4 H775A BATTERY BACKUP UNIT

•

| 4.1   | GENERAL                                | 4-1 |

|-------|----------------------------------------|-----|

| 4.2   | PHYSICAL DESCRIPTION                   | 4-1 |

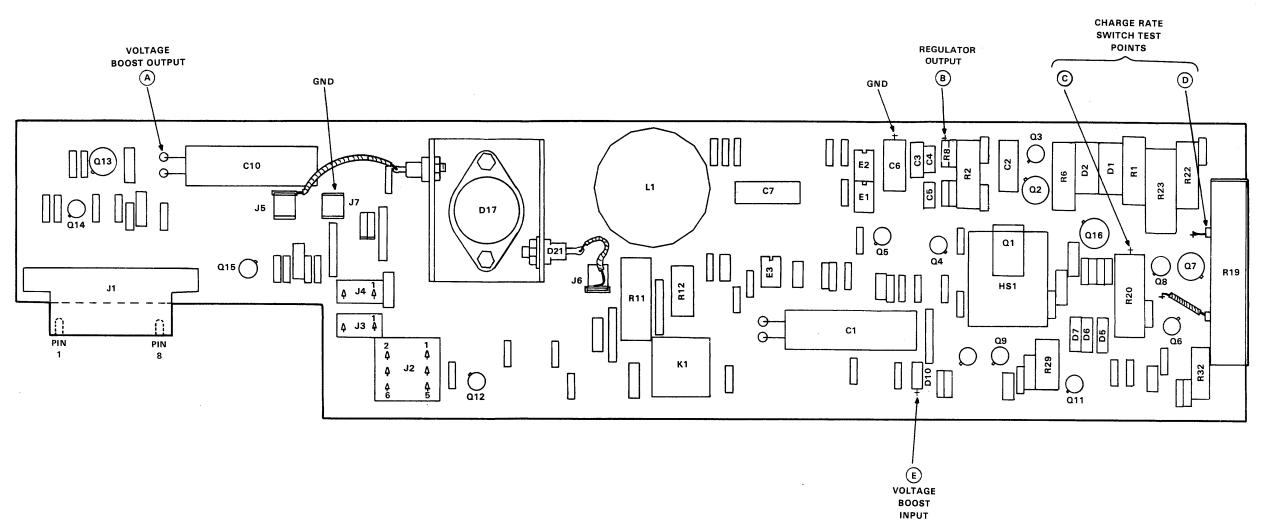

| 4.3   | FUNCTIONAL DESCRIPTION                 | 4-3 |

| 4.4   | DETAILED CIRCUIT DESCRIPTION           | 4-5 |

| 4.4.1 | Voltage Boost Circuit                  | 4-5 |

| 4.4.2 | Regulator Circuit                      | 4-5 |

| 4.4.3 | Battery Charge Rate Status and Control |     |

| 4.4.4 | Battery Discharge Switch and Control   |     |

| 4.4.5 | Battery Discharge Limit Circuit        |     |

# CHAPTER 5 MAINTENANCE

| 5.1     | GENERAL                                            | 5-1  |

|---------|----------------------------------------------------|------|

| 5.2     | PREVENTIVE MAINTENANCE PHYSICAL INSPECTION         | 5-1  |

| 5.3     | CORRECTIVE MAINTENANCE                             | 5-2  |

| 5.3.1   | Introduction                                       | 5-2  |

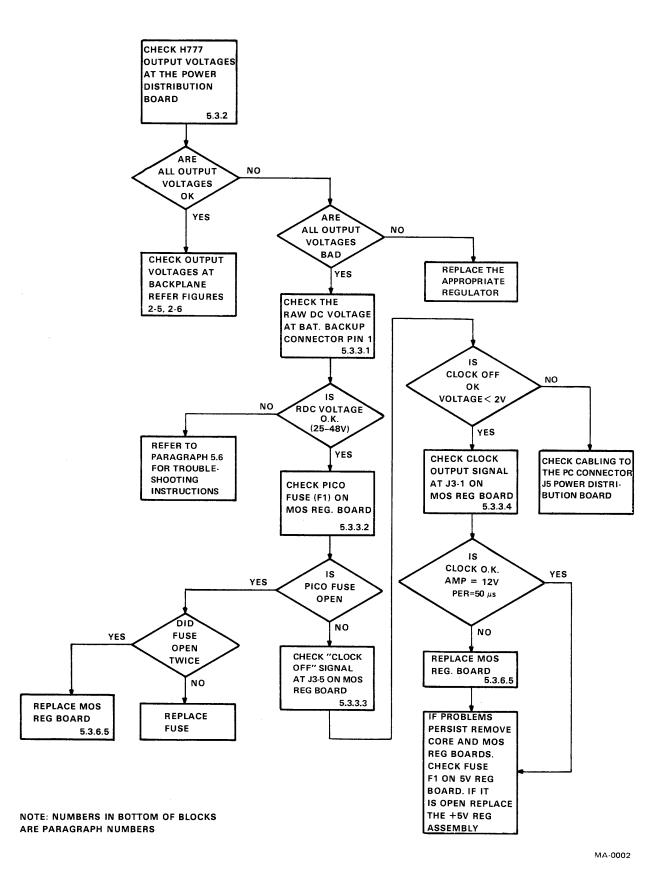

| 5.3.2   | Power Supply (H777) Output Voltage Check           | 5-2  |

| 5.3.3   | Major Power Supply Failure                         |      |

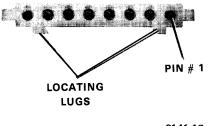

| 5.3.3.1 | Raw DC Voltage Check                               |      |

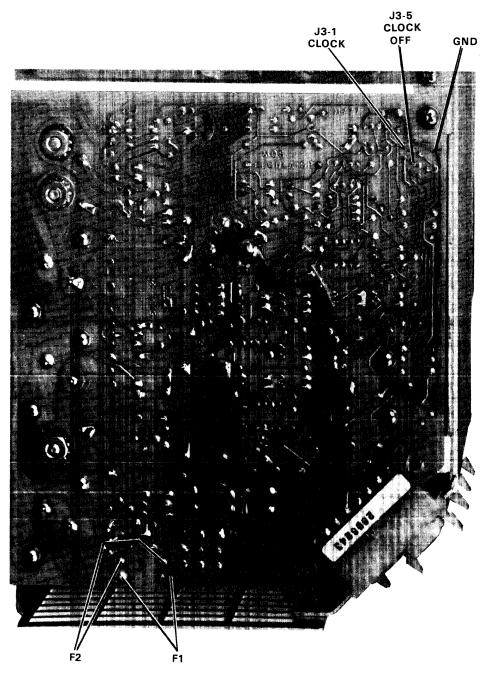

| 5.3.3.2 | MOS Regulator Pico Fuse Check                      |      |

| 5.3.3.3 | CLOCK OFF Signal Test                              | 5-5  |

| 5.3.3.4 | Clock Output Check                                 | 5-5  |

| 5.3.3.5 | +5 V Regulator Fuse Check                          |      |

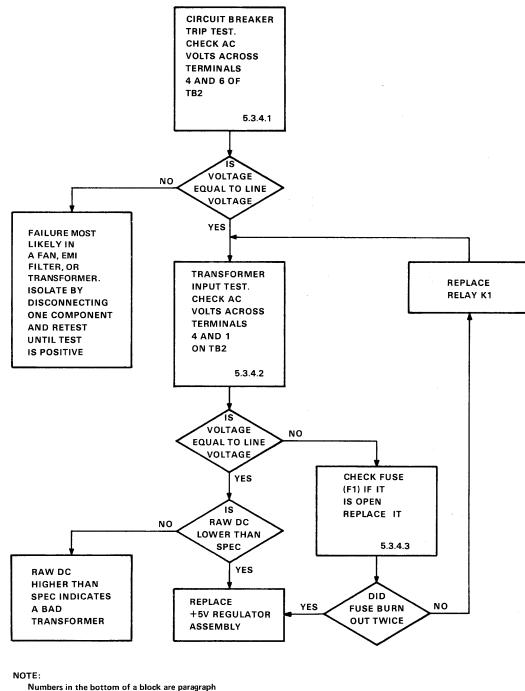

| 5.3.4   | Raw DC Voltage Failure                             |      |

| 5.3.4.1 | EMI Line Filter Test                               |      |

| 5.3.4.2 | Transformer Input Check                            | 5-9  |

| 5.3.4.3 | Fuse Check                                         |      |

| 5.3.5   | AC LO and DC LO Corrective Maintenance             | 5-10 |

| 5.3.6   | Removal of Power Supply and Assemblies             | 5-10 |

| 5.3.6.1 | Power Supply Cover Removal                         | 5-10 |

| 5.3.6.2 | Power Supply Removal                               |      |

| 5.3.6.3 | AC Control Assembly Removal                        |      |

| 5.3.6.4 | Core Regulator Removal                             | 5-12 |

| 5.3.6.5 | MOS Regulator Removal                              |      |

| 5.3.6.6 | Removal of the +5 V Regulator (7011073 or 7012909) | 5-14 |

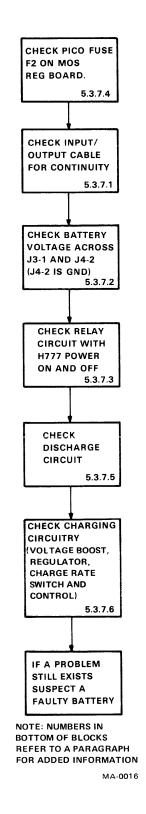

| 5.3.7   | H775A Battery Backup Maintenance                   | 5-15 |

| 5.3.7.1 | Input/Output Check                                 | 5-15 |

| 5.3.7.2 | Battery Check                                      |      |

| 5.3.7.3 | Shut-Off Relay Circuit Check                       | 5-21 |

| 5.3.7.4 | Fuse Check                                         |      |

| 5.3.7.5 | Discharge Circuit Check                            |      |

| 5.3.7.6 | Charging Circuit Check                             | 5-21 |

| 5.3.8   | Battery Backup Component Replacement               | 5-24 |

# APPENDIX A H777 INTERCONNECTION DIAGRAM

Page

# **FIGURES**

# Figure No.

## Title

# Page

| 1-1  | BA11-L Mounting Box                                            | .1-3        |

|------|----------------------------------------------------------------|-------------|

| 1-2  | Consoles                                                       |             |

| 1-3  | H777 Power Supply                                              |             |

| 1-4  | Power Distribution Board                                       |             |

| 1-5  | H775A Battery Backup Option (Front View)                       | <b>I-11</b> |

| 1-6  | Remote Power Control                                           |             |

| 2-1  | Double System Unit Backplane                                   |             |

| 2-2  | Backplane Size                                                 |             |

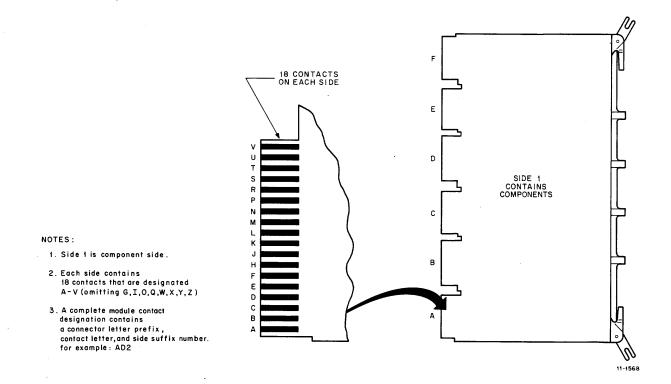

| 2-3  | Module Contact Designations                                    |             |

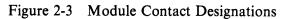

| 2-4  | Backplane Map                                                  |             |

| 2-5  | Standard and Modified Unibus Pin Designations                  |             |

| 2-6  | SPC Pin Designations                                           |             |

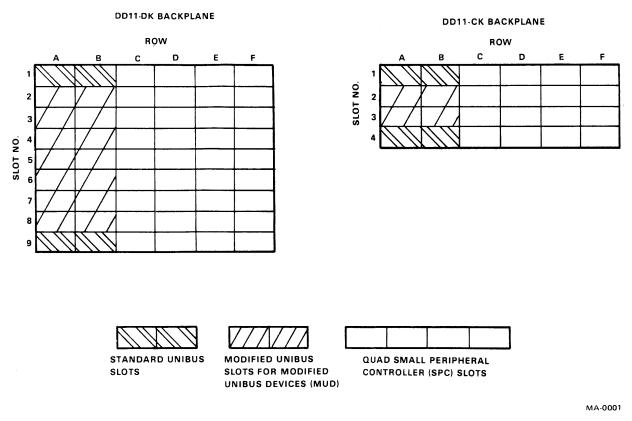

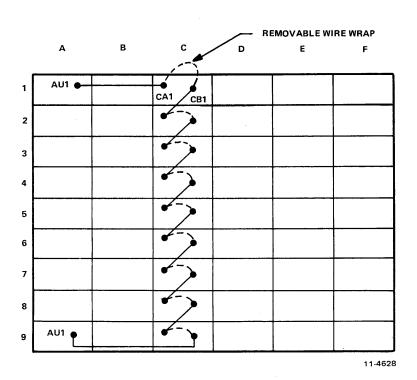

| 2-7  | NPG Signal Path                                                |             |

| 2-8  | BG Signal Path (BG4 Line)                                      |             |

| 2-9  | Backplane Power Harness                                        |             |

| 2-10 | Mate-N-Lok Connector Pin Locations (Viewed from Wire Side)     |             |

| 2-11 | Power Distribution Board                                       |             |

| 2-12 | Connector Specifications for BA11-L                            | 2-13        |

| 2-12 | Connector Specifications for 861-B and 861-C Power Controllers | 2-14        |

| 3-1  | H777 Power Supply                                              | .3-1        |

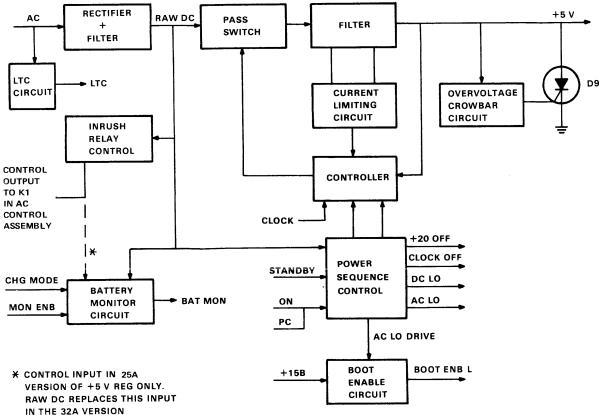

| 3-2  | H777 Block Diagram.                                            |             |

| 3-3  | Raw DC Circuit                                                 |             |

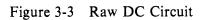

| 3-4  | 115 V and 230 V Transformer Configurations                     |             |

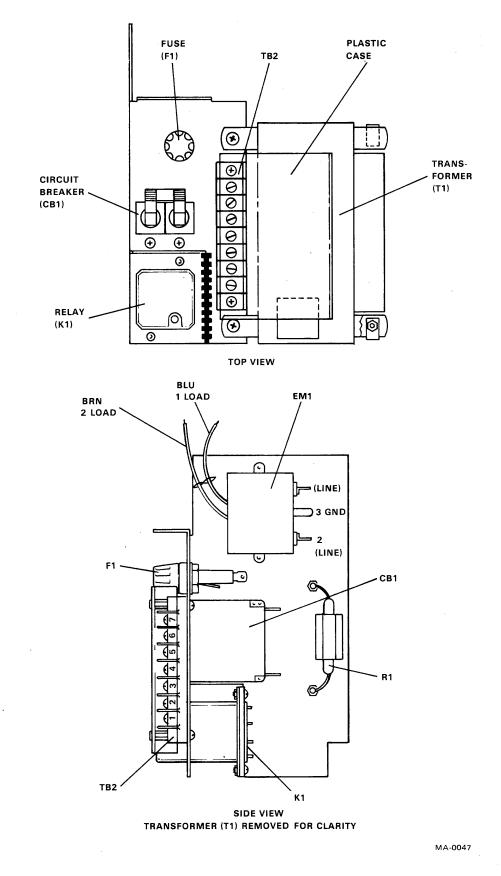

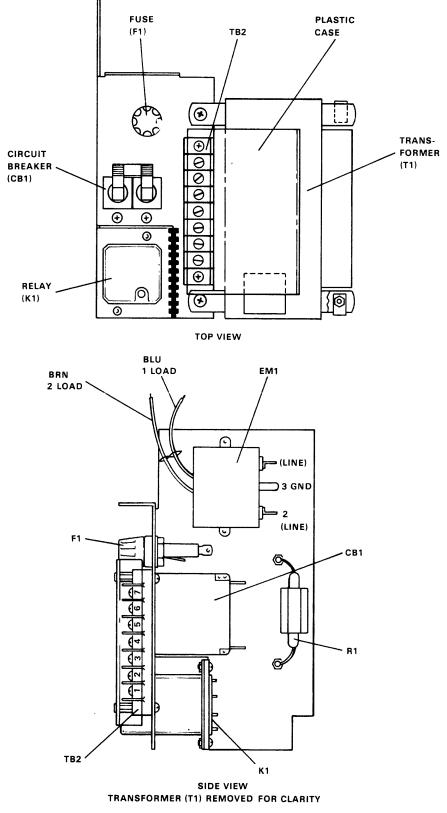

| 3-5  | AC Control Assembly Mechanical Configuration (7011075)         |             |

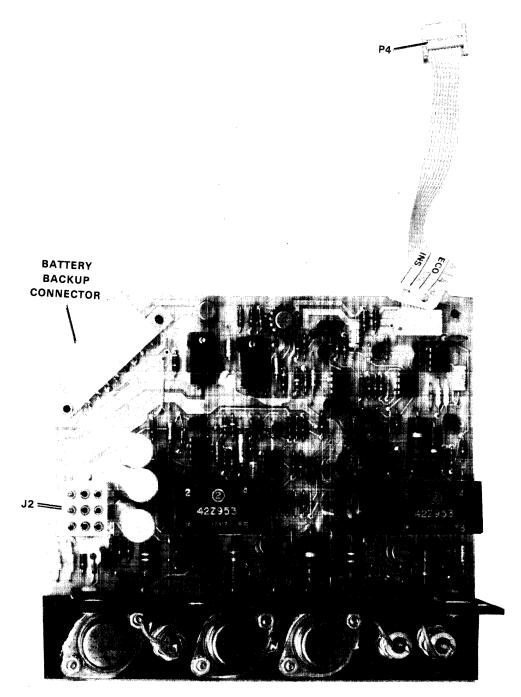

| 3-6  | MOS Regulator Board                                            |             |

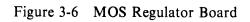

| 3-7  | MOS Regulator Block Diagram                                    |             |

| 3-8  | 555 Timer                                                      |             |

| 3-9  | Master Clock                                                   |             |

| 3-10 | ±15B Circuit                                                   |             |

| 3-11 | ±15B Pass Switch and Filter                                    |             |

| 3-12 | ±15B Controller                                                |             |

| 3-13 | Reset-Trigger Sequence Exaggerated Waveform                    |             |

| 3-14 | Overcurrent Limiting Waveforms                                 |             |

| 3-15 | +5B Circuit                                                    |             |

| 3-16 | Current Foldback                                               |             |

| 3-17 | Core Regulator Board                                           |             |

| 3-18 | Core Regulator Block Diagram                                   |             |

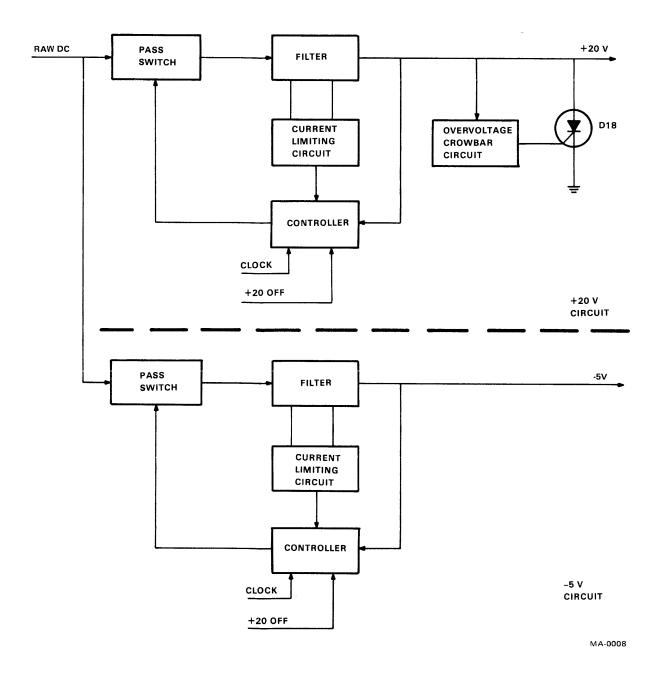

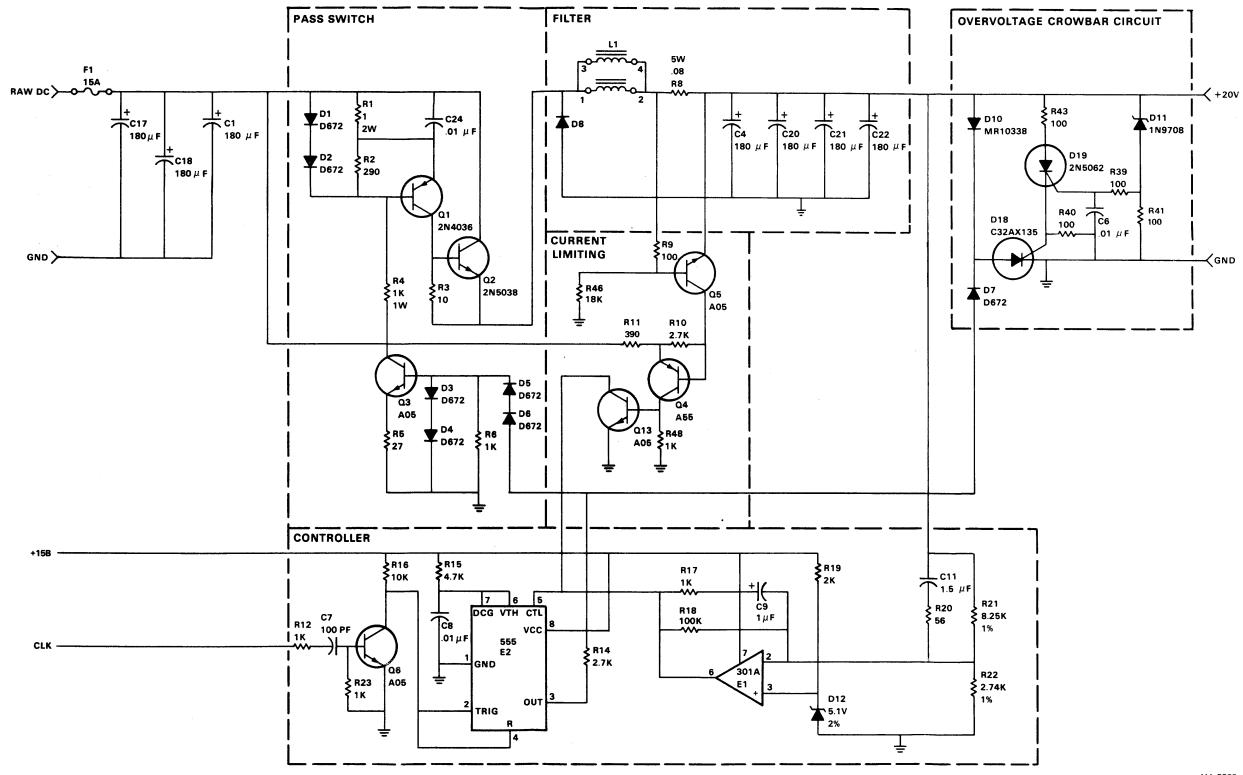

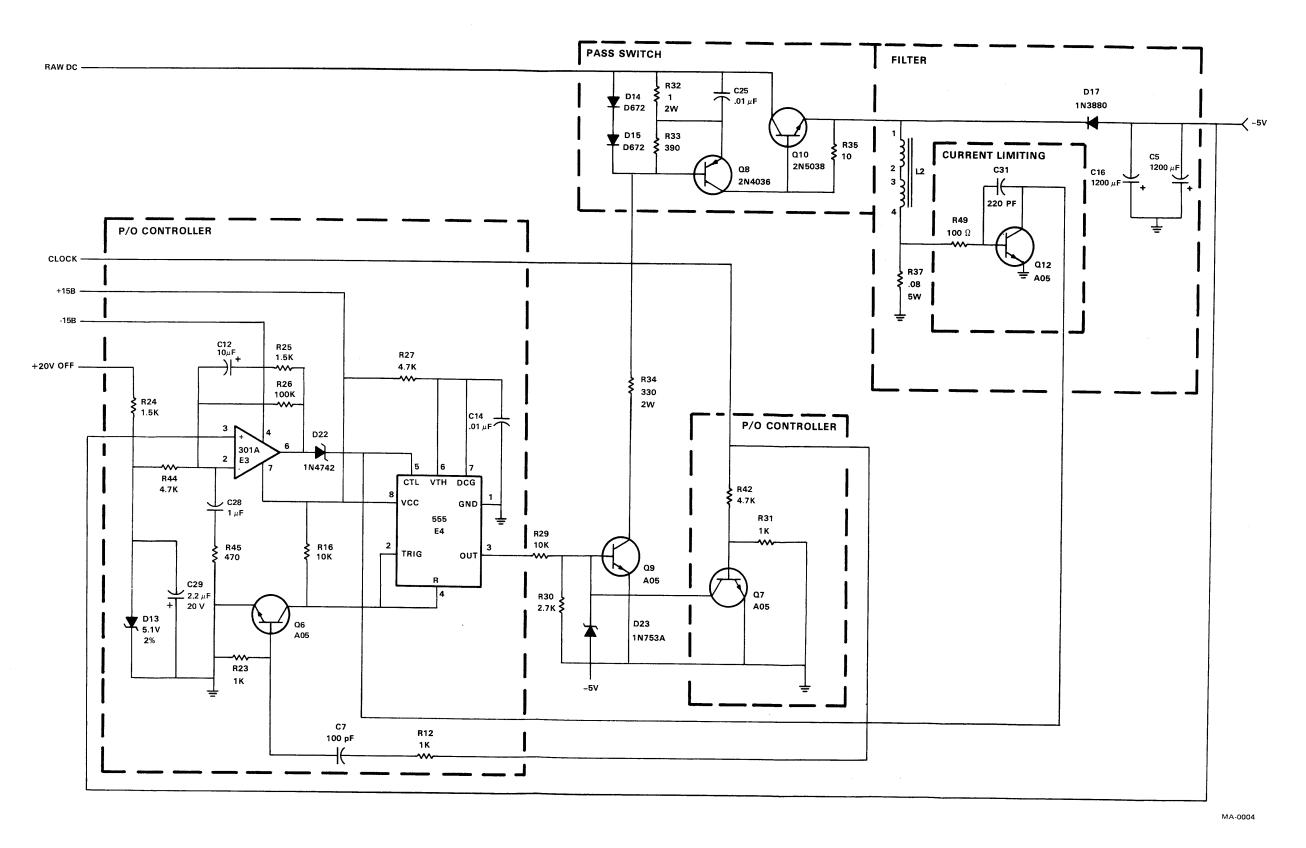

| 3-19 | +20 V Circuit                                                  |             |

| 3-20 | –5 V Circuit                                                   |             |

| 3-21 | +5 V Regulator (7011073)                                       |             |

| 3-22 | +5 V Regulator Block Diagram                                   |             |

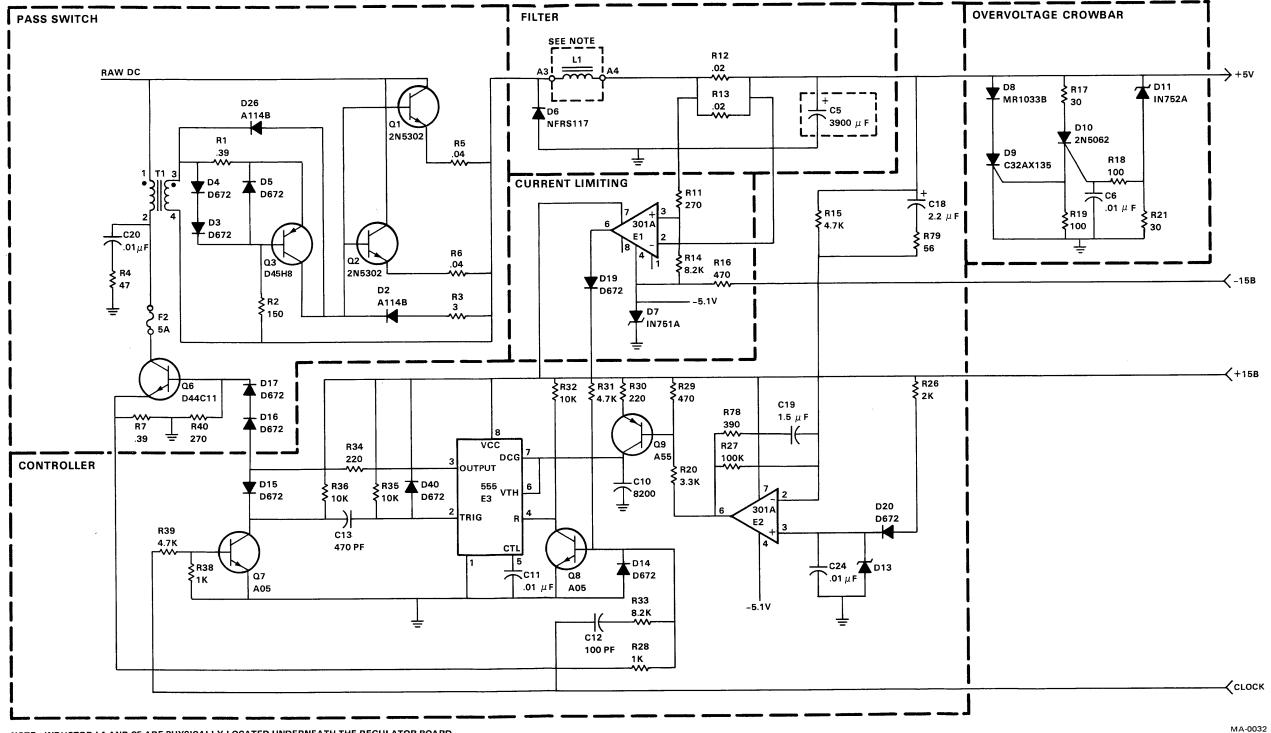

| 3-23 | +5 V Circuit                                                   |             |

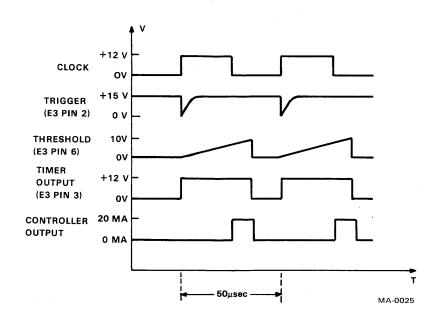

| 3-24 | +5 V Controller Waveforms                                      |             |

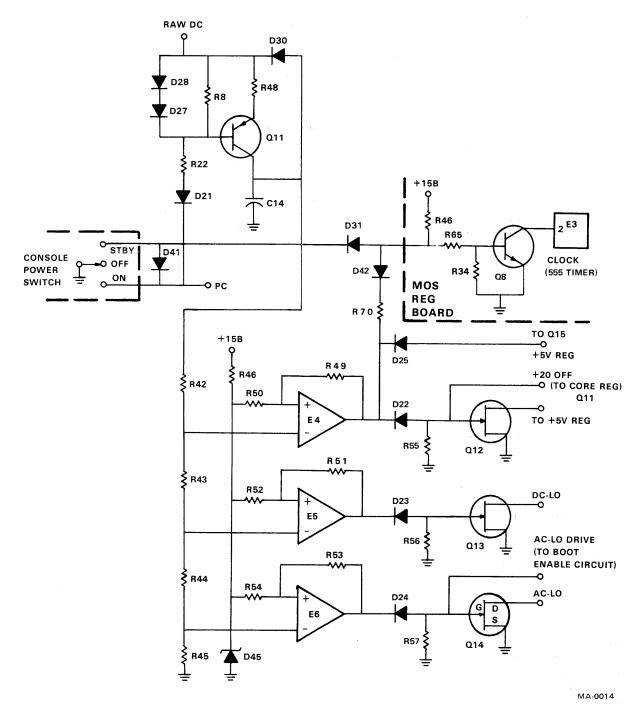

| 3-25 | Power Sequence Control Circuit                                 |             |

| 3-26 | Power Up/Down Sequence                                         |             |

|      |                                                                |             |

# FIGURES (CONT)

#### Title Page **Figure No** Power Up/Down Control of Core and +5 V Regulators......3-45 3-27 3-28 3-29 3-30 H775A Battery Backup Unit (Rear View).....4-2 4-1 Input/Output Circuit Breaker ......4-2 4-2 H775A Input/Output Cable.....4-3 4-3 H775A Block Diagram......4-4 4-4 4-5 Voltage Boost Circuit ......4-6 4-6 Battery Charge Rate Status and Control......4-9 4-7 Battery Discharge and Control Circuit......4-10 4-8 4-9 Battery Discharge Limit Circuit......4-11 5-1 5-2 5-3 5-4 AC Control Assembly Mechanical Configuration (7011075)......5-8 5-5 5-6 5-7 5-8 5-9 5-10 H775A Battery Backup Board ......5-19 5-11 5-12 5 - 13

# TABLES

#### Table No.

#### Title

#### Page

| 1-1 | BA11-L Option Designations                     | 1-1  |

|-----|------------------------------------------------|------|

| 1-2 | BA11-L Physical Specifications                 |      |

| 1-3 | H777 Major Assemblies                          |      |

| 1-4 | H777 Input Specifications                      | 1-9  |

| 1-5 | H777 Output Specifications                     | 1-10 |

| 1-6 | H775A Battery Backup Specifications            |      |

| 1-7 | Power Control Operation                        |      |

| 2-1 | Power Connector Signal Assignments for DD11-DK |      |

| 2-2 | Power Connector Signal Assignments for DD11-CK |      |

# **TABLES** (CONT)

# Table No.TitlePage3-1AC Control Assemblies3-53-2Battery Monitor Operation in 25 A Regulator3-473-3Battery Monitor Operation in 32 A Regulator3-495-1Regulator Specifications5-45-2H775A Input/Output Connector Voltages5-175-3Troubleshooting Voltages for Charge Rate Switch and Control5-24

# CHAPTER 1 CHARACTERISTICS AND SPECIFICATIONS

#### **1.1 GENERAL**

This manual describes the BA11-L mounting box. The BA11-L comes in 12 versions as listed in Table 1-1. The BA11-L can be used to house a PDP-11/04, PDP-11/34 or PDP-11/34A. It can also be used as an expander box containing various devices or options compatible with the PDP-11 family (i.e., peripheral controls).

| Mounting<br>Box<br>Designation | Usage                  | AC Input<br>Voltage<br>(Vac) | Backplane<br>Supplied    | Power<br>Supply | Regulators<br>Contained in<br>Power Supply |

|--------------------------------|------------------------|------------------------------|--------------------------|-----------------|--------------------------------------------|

| BA11-LA                        | PDP-11/04<br>or 11/34  | 115                          | DD11-CK<br>or PK         | H777-AA         | 25 A, +5 V,<br>MOS and Core                |

| BA11-LB                        | PDP-11/04<br>or 11/34  | 230                          | DD11-CK<br>or<br>DD11-PK | H777-AB         | 25 A, +5 V,<br>MOS and Core                |

| BA11-LC                        | PDP-11/04<br>or 11/34  | 115                          | DD11-CK<br>or<br>DD11-PK | H777-BA         | 25 A, +5 V<br>and MOS                      |

| BA11-LD                        | PDP-11/04<br>or 11/34  | 230                          | DD11-CK<br>or<br>DD11-PK | H777-BB         | 25 A, +5 V<br>and MOS                      |

| BA11-LE                        | Expander<br>Box        | 115                          | Not<br>Supplied          | H777-CA         | 32 A, +5 V<br>MOS and Core                 |

| BA11-LF                        | Expander<br>Box        | 230                          | Not<br>Supplied          | Н777-СВ         | 32 A, +5 V<br>MOS and Core                 |

| BA11-LH                        | Expander<br>Box        | 115                          | Not<br>Supplied          | H777-DA         | 32 A, +5 V<br>and MOS                      |

| BA11-LJ                        | Expander<br>Box        | 230                          | Not<br>Supplied          | H777-DB         | 32 A, +5 V<br>and MOS                      |

| BA11-LK                        | PDP-11/04<br>or 11/34A | 115                          | DD11-CK<br>or<br>DD11-PK | H777-CA         | 32 A, +5 V<br>MOS and Core                 |

Table 1-1

BA11-L Option Designations

| Mounting<br>Box<br>Designation | Usage                  | AC Input<br>Voltage<br>(Vac) | Backplane<br>Supplied    | Power<br>Supply | Regulators<br>Contained In<br>Power Supply |

|--------------------------------|------------------------|------------------------------|--------------------------|-----------------|--------------------------------------------|

| BA11-LL                        | PDP-11/04<br>or 11/34A | 230                          | DD11-CK<br>or<br>DD11-PK | Н777-СВ         | 32 A, +5 V,<br>MOS and Core                |

| BA11-LM                        | PDP-11/04<br>or 11/34A | 115                          | DD11-CK<br>or<br>DD11-PK | H777-DA         | 32 A, +5 V<br>and MOS                      |

| BA11-LN                        | PDP-11/04<br>or 11/34A | 230                          | DD11-CK<br>or<br>DD11-PK | H777-DB         | 32 A, +5 V<br>and MOS                      |

Table 1-1

BA11-L Option Designations (Cont)

#### NOTES

| 1. | The DD11-PK or DD11-CK is supplied in a PDP-11/04 processor box. Only the DD11-PK is supplied in a PDP-11/34 or PDP-11/34A processor box. |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | An expander box can use a DD11-DK, DD11-<br>CK or special purpose backplane                                                               |

| 3. | A PDP-11/04 housed in a BA11-LK, -LL,                                                                                                     |

3. A PDP-11/04 housed in a BAI1-LK, -LL, -LM or -LN is assigned serial #10000 or higher.

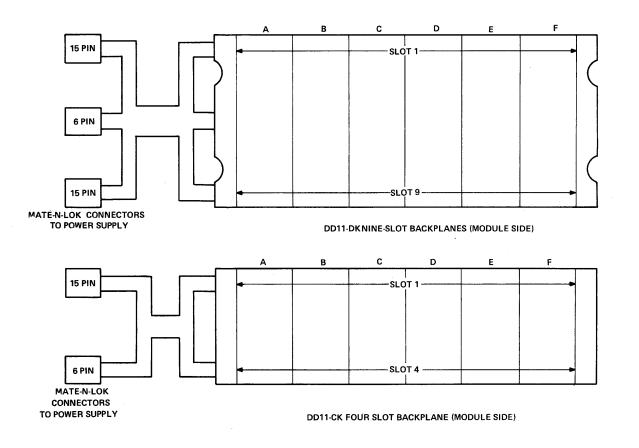

The BA11-L contains a power supply (H777) and mounting space for a backplane. A 9-slot backplane (DD11-DK) or up to two 4-slot backplanes (DD11-CK) can be placed in the BA11-L.

There are eight versions of the H777. These versions are combinations of the following: 115 Vac or 230 Vac input power source and a 25 A or 32 A + 5 V regulator (with an MOS or MOS and core regulator).

A self-contained battery backup unit (H775A) is offered as an option for use with any version of the BA11-L.

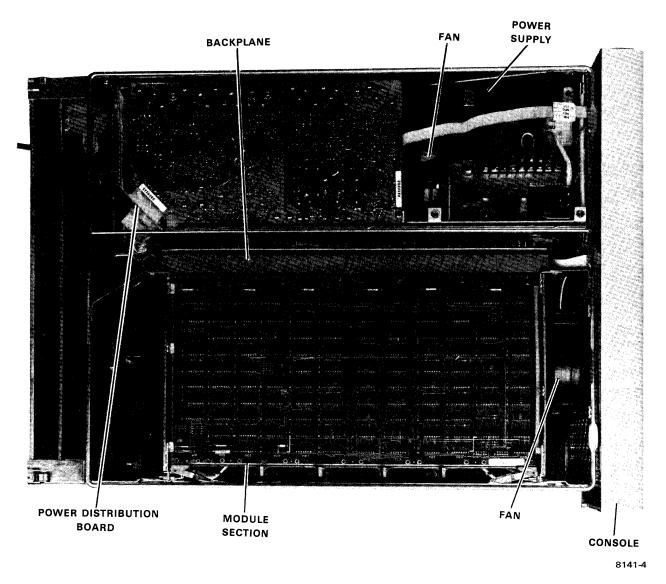

#### **1.2** PHYSICAL CHARACTERISTICS OF THE BA11-L (Figure 1-1)

The BA11-L components fit into a mounting frame designed to provide a strong enclosure with maximum accessibility. The mounting frame is divided into two major sections with the modules in one section and the H777 power supply in the other section.

There are two fans in the BA11-L. One fan cools the power supply and the other fan cools the module section. Both fans circulate air toward the back of the mounting frame. A single fan filter goes across the width of the mounting frame in the front of the box.

Figure 1-1 BA11-L Mounting Box

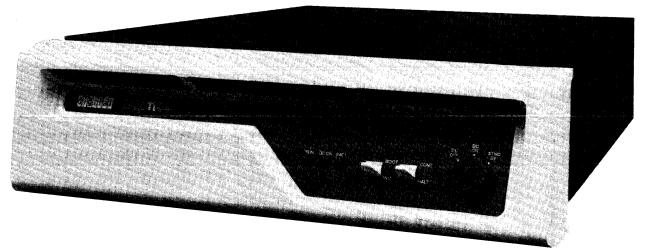

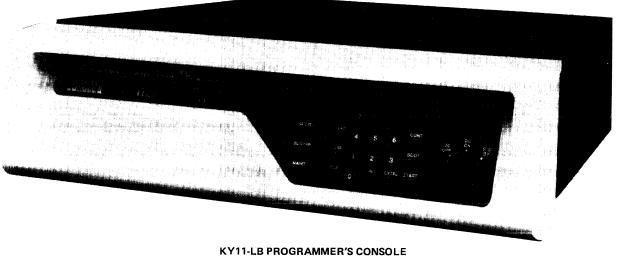

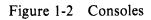

A console mounts to the front of the mounting frame. There are three consoles available with the BA11-L; the operator's console (KY11-LA), the programmer's console (KY11-LB) and the expander console (70-12540-00). The expander console comes with the BA11-LE, BA11-LF, BA11-LH and BA11-LJ; the KY11-LA and KY11-LB are used with the other versions of the BA11-L. Figure 1-2 illustrates the three consoles. Only the expander console is discussed here. For information concerning the KY11-LB, refer to the KY11-LB Programmer's Console Maintenance Manual, (EK-KY1LB-MM-001); for information concerning the KY11-LA, refer to the PDP-11/04 System User's Manual (EK-11004-0P-002).

KY11-LA OPERATOR'S CONSOLE

8141-21

8141-20

EXPANDER CONSOLE

8141-5

The expander console is a metal plate with a louvered grill for airflow. A power light (DC ON) and a battery monitor light (BATT) are displayed on the panel. The indicator lights are light-emitting diodes (LEDs) mounted to a printed circuit (PC) board attached to the console behind the grill.

A ribbon cable from the +5 V regulator in the H777 plugs into a connector on the PC board to power the display lights. (The ribbon cable also contains control lines for a power switch that is used on the KY11-LA and KY11-LB.)

The mounting frame slides into a wraparound envelope that completely encloses four sides of the mounting frame. The front and back of the envelope are open for airflow. The envelope is easily mounted and functions as a slide mechanism for withdrawing the frame and its contents. Refer to Table 1-2.

| Parameter                                                             | Specification                                                                                |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Chassis size<br>(with expansion console)                              | 13.5 cm H × 48 cm W × 64 cm D<br>(5-1/4 in H × 19 in W × 25 in D)                            |  |  |

| Chassis weight<br>(without logic modules)                             | 20 kg (45 lb)                                                                                |  |  |

| H777 power supply size                                                | 12.7 cm H $\times$ 15.3 cm W $\times$ 50.8 cm D<br>(5 in H $\times$ 6 in W $\times$ 20 in D) |  |  |

| Slide extension                                                       | 57.15 cm (22.5 in)                                                                           |  |  |

| Slideweight capacity                                                  | 18.14 kg (40 lb)                                                                             |  |  |

| (BA11-L fully extended)<br>Mounting capacity                          | 1 double system unit backplane or 2 single system unit back-<br>planes                       |  |  |

| Fan air movement direction                                            | Front to back                                                                                |  |  |

| Shock and vibration character-<br>istics<br>Operating<br>Nonoperating | 10G for 10 ms – 1/2 sine pulse<br>40G for 30 ms – 1/2 sine pulse                             |  |  |

| Temperature<br>Operating<br>Nonoperating                              | 0° to 50° C (32° to 122° F)<br>-55° to 85° C (-67° to 185° F)                                |  |  |

| Humidity                                                              | 0 to 90% (no condensation)                                                                   |  |  |

Table 1-2

BA11-L

Physical

Specifications

The H777 provides two green wires which are chassis ground. The green wire in the back is used to ground the rack; the green wire in the front is used to ground the console.

#### 1.3 H777 POWER SUPPLY

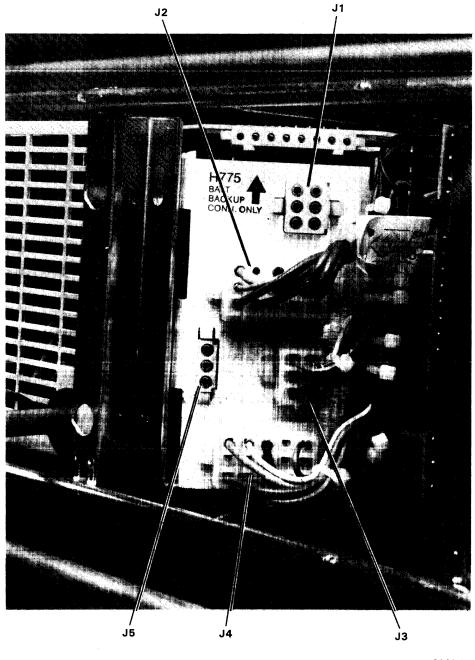

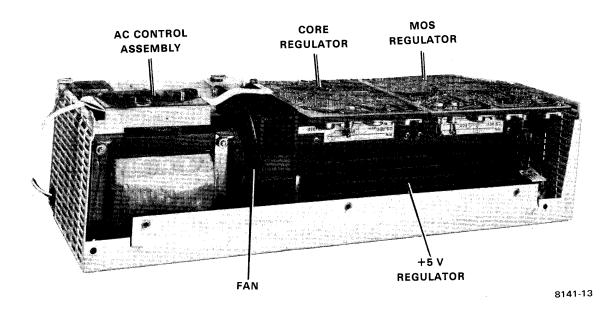

The H777 (Figure 1-3), a multivoltage power supply designed for use within the BA11-L, provides 240 W of dc power. The power supply has at last three and a maximum of four assemblies which are listed in Table 1-3.

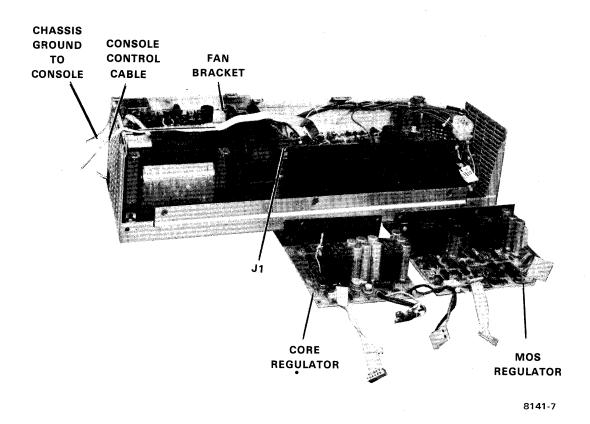

Figure 1-3 H777 Power Supply

| Assembly                               | Function                                                                                                                                                                                                                                          |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AC Input Assembly                      | Contains a transformer, line filter, and other ac utility interface equipment                                                                                                                                                                     |  |  |

| +5 V Regulator<br>(7011073 or 7012909) | Produces +5 V power for the logic modules<br>Provides AC LO and DC LO power fail signals<br>Provides an ac line clock signal (LTC)<br>Contains battery monitoring circuitry for the H775A battery<br>backup unit<br>Provides a BOOT ENABLE signal |  |  |

| MOS Regulator<br>(5411601)             | Produces $\pm 15$ V and $+5$ V power for use by MOS memory<br>(designated $\pm 15B$ and $+5B$ )<br>Provides $\pm 15$ V power to the logic modules via solid state<br>switches                                                                     |  |  |

| Table 1-3 | H777 | Major | Assemblies |

|-----------|------|-------|------------|

|-----------|------|-------|------------|

| Assembly                    |    | Function                                                                                                                                                                                                                                                                                                     |

|-----------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Regulator<br>(5411599) |    | Produces $+20$ V and $-5$ V power for use by core memory                                                                                                                                                                                                                                                     |

|                             | 1. | NOTES<br>Regulator 7011073 provides up to 25 A of +5 V<br>power to the load and regulator 7012909 pro-<br>vides up to 32 A of +5 V power to the load.                                                                                                                                                        |

|                             | 2. | In the STANDBY mode, only the $\pm 15B$ and $\pm 5B$ outputs are operational. During an ac power failure, the $\pm 15B$ and $\pm 5B$ outputs are battery supported if the H775A is present. If the H777 is in the STANDBY mode and ac input power is present, the batteries in the H755A are not discharged. |

|                             | 3. | The core regulator is optional.                                                                                                                                                                                                                                                                              |

#### Table 1-3 H777 Major Assemblies (Cont)

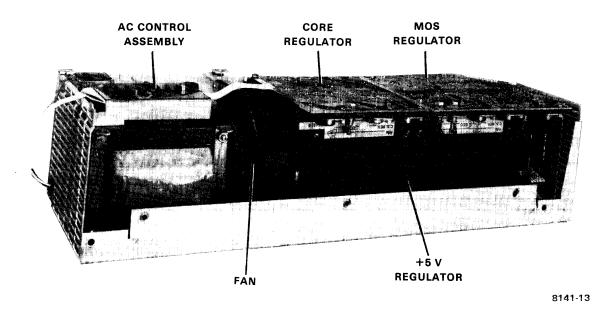

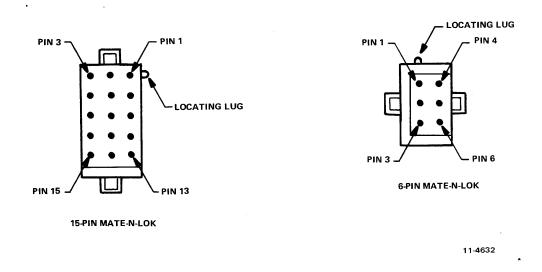

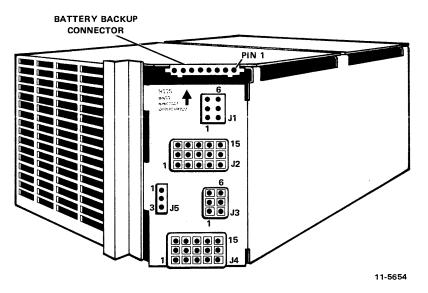

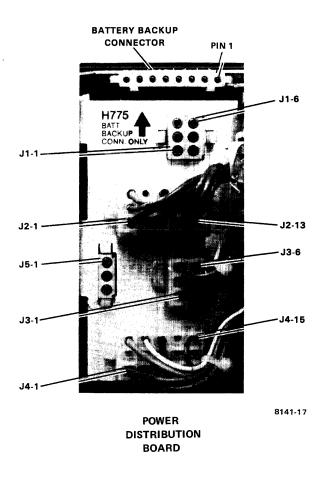

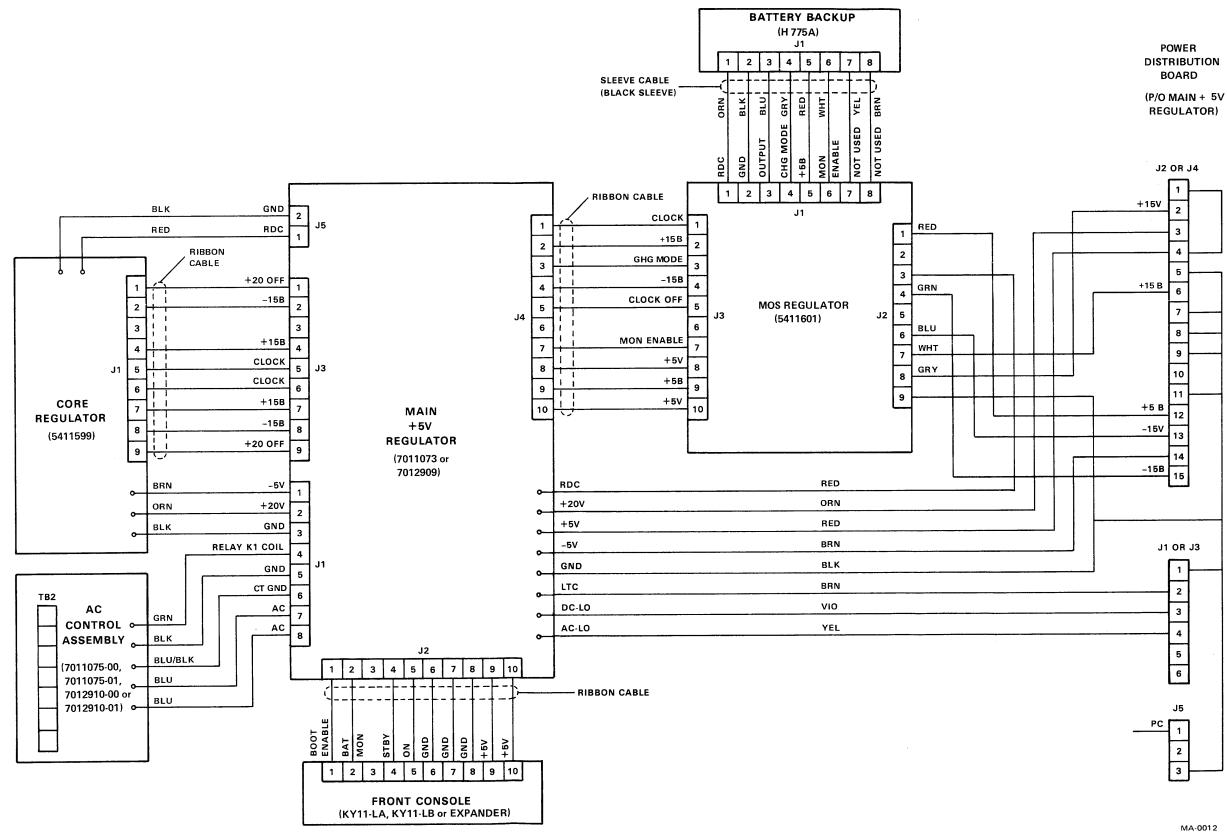

Power from the regulators is routed to the backplane via the power distribution board (Figure 1-4) on the H777. The dc voltage outputs of the H777 are available at J2 and J4 which are wired in parallel. Signals AC LO, DC LO and LTC are available at J1 and J3 which are also wired in parallel. Connector J5 is the power control (PC) connector discussed in Paragraph 1.5.

The input specifications for the H777 are listed in Table 1-4 and the output specifications are listed in Table 1-5.

8141-17

Figure 1-4 Power Distribution Board

| 104–127 Vrms                                                      |

|-------------------------------------------------------------------|

| 208–254 Vrms                                                      |

| 90–132 Vrms                                                       |

| 180–264 Vrms                                                      |

| 47–63 Hz                                                          |

|                                                                   |

| 5 A (rms)                                                         |

| 2.5 Å                                                             |

| 4 A                                                               |

| 2 A                                                               |

|                                                                   |

| 480* W                                                            |

| 480 W                                                             |

| 340 W                                                             |

| 340 W                                                             |

|                                                                   |

|                                                                   |

|                                                                   |

| 20 A peak                                                         |

| 40 A peak                                                         |

| 180/360 Vrms<br>0.1 second                                        |

| 0.1 second                                                        |

|                                                                   |

|                                                                   |

|                                                                   |

| Time interval between the start of an ac power failure and the    |

| assertion (grounding) of AC LO.                                   |

|                                                                   |

|                                                                   |

|                                                                   |

|                                                                   |

| Time interval between the start of an ap newer failure and a lass |

| Time interval between the start of an ac power failure and a loss |

| of regulated dc output.                                           |

|                                                                   |

|                                                                   |

| Internal Magnetic Circuit Breaker                                 |

| 115 V – 10 A for H777-AA and -BA, 5 A for H777-CA and -DA         |

| 230  V - 5  A                                                     |

| 100° C (212° F) NC mounted on +5 V REG heat sink. Provides        |

| electronic shutdown of that regulator and 5411599.                |

|                                                                   |

# Table 1-4 H777 Input Specifications

#### Table 1-4 H777 Input Specifications (Cont)

#### Hi Potential

1500 Vdc for 60 seconds from input to output or input to chassis.

#### \*Transformer limit.

NOTE

Except for the circuit breakers, the input specifications for the H777-CA, -CB, -DA, and -DB are the same as for the H777-AA, -AB, -BA, and -BB, respectively.

| Regulator<br>Assembly             | Output<br>Designation | Output<br>Voltage | Tolerance                     | Regulation<br>Line | Reg<br>Load | Current<br>Output |

|-----------------------------------|-----------------------|-------------------|-------------------------------|--------------------|-------------|-------------------|

| MOS Regulator (5411601)           | +15B                  | +15.3 V           | ±450 mV                       | 0.5%               | 0.5%        | 0–2 A             |

| (3411001)                         | –15 B                 | –15.3 V           | $\pm 450 \mathrm{mV}$         | 1%                 | 1%          | 0–2 A             |

|                                   | +15 V                 | +15.3 V           | -200  mV max at $+15B$ Output | 1%                 | 1.5%        | 0–1A              |

|                                   | -15 V                 | -15.3 V           | -200 mV max at<br>-15B Output | 1%                 | 1.5%        | 0–1 A             |

|                                   | +5B                   | +5.1 V            | +100 mV<br>-150               | 1%                 | 1%          | 0–4 A             |

| Core Regulator (5411599)          | +20 V                 | +20.0 V           | $\pm 500 \text{ mV}$          | 1%                 | 0.5%        | 0-6 A             |

| (5411577)                         | -5 V                  | -5.1 V            | +100 mV<br>-150               | 1%                 | 1%          | 0–4 A             |

| 5 V Regulator<br>(7011073)        | +5 V                  | +5.1 V            | +100 mV<br>-150               | 1%                 | 1%          | 0–25 A            |

| or<br>+5 V Regulator<br>(7012909) | +5 V                  | +5.1 V            | +100 mV<br>-150               | 1%                 | 1%          | 0-32 A            |

Table 1-5 H777 Output Specifications

Ripple – 2% peak to peak all outputs Temp Coefficient – +0.5 mV/°C Output Noise – 2% max peak

#### **NOTES:**

- 1. The total current output of +15 V, -15 V, +15B, and -15B cannot exceed 4 A. The +15 V and -15 V outputs can provide a maximum of 1 A each. Refer to Paragraph 3.6.3.4.

- 2. The line regulation specifies the variation in output voltage during power supply operation with a constant load. This load regulation specifies the variation in output voltage caused by varying the load from an open circuit to max load.

#### 1.4 H775A BATTERY BACKUP UNIT

ļ

A self-contained battery backup unit, the H775A, is offered as an option for use with the H777 power supply. During an ac power failure, the H775A provides a battery input voltage to the MOS regulator only allowing the  $\pm 15B$  and  $\pm 5B$  outputs to remain operational. Therefore, the MOS regulator can provide refresh power for a limited time after an ac power failure has occurred.

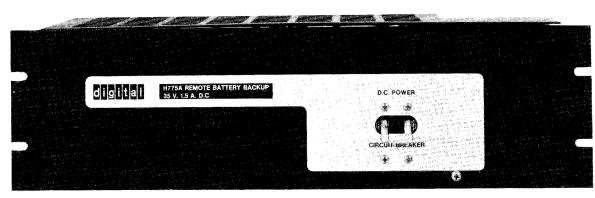

The H775A contains two batteries and charging circuitry. Figure 1-5 shows the H775A and Table 1-6 lists the specifications for the H775A.

7883-3

Figure 1-5 H775A Battery Backup Option (Front View)

| Parameter    | Specification                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------|

| Size         | 13.3 cm H $\times$ 48.25 cm W $\times$ 10.8 cm D<br>(5-1/4 in H $\times$ 19 in W $\times$ 4-1/4 in D) |

| Weight       | 6.8 kg (15 lb)                                                                                        |

| Input/Output | 25-48 Vdc/24 Vdc                                                                                      |

| Capacity     | 120 wh at 2.5 A and 50° C (122° F)                                                                    |

| Cell Type    | Sealed lead acid                                                                                      |

| Charger      | Constant current, dual rate                                                                           |

Table 1-6 H775A Battery Backup Specifications

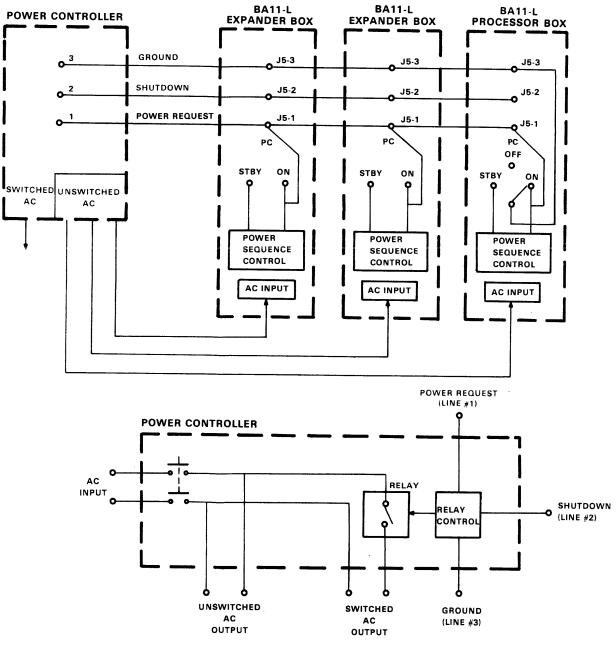

# **1.5 REMOTE POWER CONTROL (Figure 1-6)**

The power control is a power distribution system which simultaneously turns on all the power supplies in a PDP-11 system (processor box and expander boxes). The power control consists of a power controller and three power control lines: power request (line 1), emergency shutdown (line 2), and system ground (line 3).

MA-0003

Figure 1-6 Remote Power Control

The power controller routes ac power to the system via unswitched and switched outputs. The unswitched outputs are live as long as ac power is applied to the power controller via its circuit breaker. The switched outputs are controlled by a relay which, in turn, is controlled by the power request and emergency shutdown lines. These lines are either open or grounded. The operation of the power controller is summarized in Table 1-7.

| Line Status                          |                                      | Power Controller Status        |                              |  |

|--------------------------------------|--------------------------------------|--------------------------------|------------------------------|--|

| Power<br>Request<br>(Line 1)         | Emergency<br>Shutdown<br>(Line 2)    | State of<br>Relay              | Switched<br>Outputs          |  |

| open<br>open<br>grounded<br>grounded | open<br>grounded<br>grounded<br>open | open<br>open<br>open<br>closed | dead<br>dead<br>dead<br>live |  |

Table 1-7

Power Control Operation

The power control lines plug into connector J5 at the H777 power distribution board of all the BA11-L boxes in the PDP-11 system. The emergency shutdown line is not used by the H777.

Only the processor box has a power switch on the console. When the power switch is placed in the ON position, the power request line is grounded which, in turn, grounds the ON input of the power supplies in the expander boxes. Therefore, when the power switch in the processor box is turned on, all the power supplies connected to the power control lines initiate a power-up sequence.

Standby operation of an expander box is selectable via a jumper plug on the expander console. The jumper plug grounds the STBY input of the H777. If the power request line is not grounded, the power supply is in the STANDBY mode. If the STBY input is not grounded, the power supply turns off when the power request line is not grounded.

# CHAPTER 2 BACKPLANE CONFIGURATIONS AND INSTALLATION INFORMATION

#### 2.1 GENERAL

Three types of backplanes can be used in the BA11-L: a processor backplane (DD11-PK), an expander backplane (DD11-DK), or a special purpose backplane.

.

The DD11-CK can be used as an expander backplane or a processor backplane for the PDP-11/04. Only the expander backplanes, DD11-CK and DD11-DK, are discussed in this chapter.

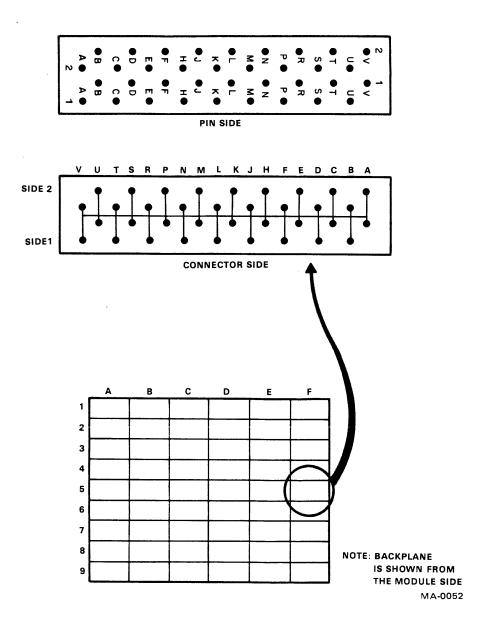

A backplane is also classified as a double system unit with nine slots or a single system unit with four slots. The DD11-DK and DD11-PK are double system units and the DD11-CK is a single system unit. The BA11-L can house any double system unit or up to two single system units.

#### 2.2 PHYSICAL DESCRIPTION

A double system unit backplane is shown in Figure 2-1. It is a grid of connectors with each connector specified by a slot (1-9) and a section (A-F). Logic modules plug into the module side of the backplane. The pin side is wired to provide power and signal interconnections to the modules.

Any pin on the backplane can be specified as shown in the following example.

Designation A01B2

- A Section letter (A–F)

- 01 Slot number (01–09)

- B Pin letter (A–V)

- 2 Connector side (1 or 2)

Figure 2-2 shows a double system unit and a single system unit. Note that the single system unit has only four slots.

A module can connect with one or more sections of a slot.

Single height module – 1 section Dual height module – 2 sections Quad height modules – 4 sections Hex height modules – 6 sections (1 full slot)

Figure 2-3 shows the connecting edge of a hex module.

8141-1

Figure 2-1 Double System Unit Backplane

.

#### 2.3 ELECTRICAL DESCRIPTION

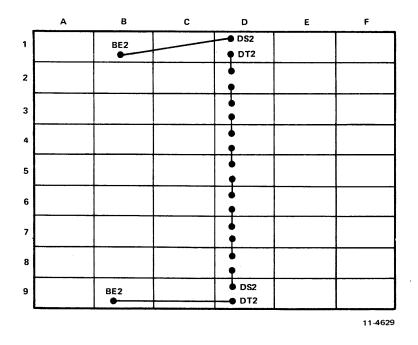

In accordance with their pin designations, the connectors in the backplane are classified into three categories: standard Unibus, modified Unibus and small peripheral control (SPC) connectors. Particular areas of the backplane are reserved for the different types of connectors as shown in Figure 2-4.

Figure 2-4 Backplane Map

The standard Unibus connectors contain all the Unibus connections. Sections A and B of slot 1 are the beginning of the Unibus in the DD11-CK and DD11-DK and should be occupied by the BC11-A Unibus cable since they are expander backplanes. Sections A and B of slot 9 in the DD11-DK or of slot 4 in the DD11-CK are the end of the Unibus on the backplane. These sections should be occupied by the BC11-A Unibus cable or a terminator module.

Slots 2 through 8 (sections A and B) are the modified Unibus in the DD11-DK and slots 2 and 3 (sections A and B) are the modified Unibus in the DD11-CK.

Figure 2-5 shows the pin designations of the standard and modified Unibus connectors. The modified Unibus differs from the standard Unibus in that certain pins have been redesignated. Some ground connections, BUS GRANT signals and the NPG signal have been removed from the standard Unibus and have been redesignated with core memory voltage pins, battery backup voltage pins for MOS memory, parity signal pins, several reserve pins and test point pins.

#### STANDARD UNIBUS PIN DESIGNATIONS

|          |     | COLI     | JMN      |          | COLL     | IN | 1N          |   |

|----------|-----|----------|----------|----------|----------|----|-------------|---|

|          |     | 4        | A B      |          | В        |    |             |   |

| \$       | ide |          |          |          |          |    |             |   |

| P        | in  | 1        | 2        |          | 1        |    | 2           |   |

| F        |     | INIT     | +5V      |          | G6       | 1  | +5V         |   |

| <u>_</u> |     | L        |          | +        | н        | _  |             | ļ |

| E        | 2   |          | GND      | Γ.       | G5       | 0  | GND         |   |

|          |     | L        |          |          | н        |    |             |   |

| (        |     | D00      | GND      |          | R5       | '  | GND         | l |

|          |     | L        |          |          | L        |    |             | ļ |

|          | þ   | D02      | D01      | G        | ND       |    | BR4         | l |

|          |     | L        | L        |          |          | Ĺ  | L           |   |

|          | E   | D04      | D03      | G        | ND       |    | BG4         | l |

|          |     | L        | L        |          |          |    | H<br>DC     |   |

|          | F   | D06      | D05      | 1        | C .      |    |             |   |

| L        |     | L        | L        |          | .0 L     | ╞  | LO L<br>A00 | 4 |

|          | н   | D08      | D07      | 1        | .01      |    | L           |   |

| L        |     | L        | L        |          | L<br>103 | ╀  | L<br>A02    |   |

|          | J   | D10      | D09      | 1        | 103<br>L |    | L L         |   |

| ŀ        |     |          | L<br>D11 | +        | L<br>405 | ╀  | A04         | ┥ |

|          | к   | D12      |          | ſ        |          |    | L           |   |

| ┞        |     | L<br>D14 | L<br>D13 | _        | L<br>407 | +  | A06         | - |

| l        | L   | L L      |          | ľ        | L.       |    | L           |   |

| ŀ        |     |          | L        | +        | A09      | ╀  | A08         | 4 |

| I        | м   | PA       | D15      | ľ        |          |    | L           |   |

| ŀ        |     | L        | L        | +        | L<br>A11 | +  | A10         | - |

| I        | N   | GND      |          | ľ        |          |    | L           |   |

| ł        |     |          | L<br>BBS | <u>_</u> | L<br>A13 | ╉  | A12         | - |

|          | P   | GNE      |          | 1        | L        |    | L           |   |

| ł        |     | GNE      |          | /        | A15      | +  | A14         | - |

|          | R   | GNL      |          | 1        | L        |    | L           |   |

|          |     | GNE      |          | ,        | A17      | +  | A16         | _ |

|          | s   | GN       |          | `        | L        |    | L           |   |

|          |     | GNI      | 4        | ,        | GND      | -  | C1          | - |

|          | т   |          |          | ' I      | 5110     |    | L           |   |

|          |     | NPC      |          | 6        | SSYN     | -  | -<br>C0     |   |

|          | υ   | H        | ן ( ה    | -        | L        |    | L           |   |

|          |     | BG       | 7 GN     | D        | MSYN     | 1  | GND         |   |

|          | v   | so       |          | _        | L        |    |             |   |

|          |     |          |          |          |          |    | L           |   |

#### MODIFIED UNIBUS PIN DESIGNATIONS

|           | COLL   |      | COLU        | MN     |

|-----------|--------|------|-------------|--------|

|           | A      |      |             |        |

| Side      |        |      |             |        |

| Pin       | 1      | 2    | 1           | 2      |

| А         | INIT   | +5V  | RESV<br>PIN | +5V    |

|           | L      |      |             |        |

| в         | INTR   | ТР   | RESV        | тр     |

| • •       | L      |      | PIN         |        |

| с         | D00    | GND  | BR5         | GND    |

|           | L      |      | L           |        |

| D         | D02    | D01  | +5          | BR4    |

|           | L      | L    | ВАТ         | L      |

| Е         | D04    | D03  | INT         | PAR    |

| E         | L      | L    | SSYN        | DET    |

| -         | D06    | D05  | AC          | DC     |

| F         | L      | L    | LOL         | LOL    |

|           | D08    | D07  | A01         | A00    |

| н         | L      | L    | L           | L      |

|           | D10    | D09  | A03         | A02    |

| J         | L      | L    | L           | L      |

|           | D12    | D11  | A05         | A04    |

| к         | L      | L    | L           | L      |

|           | D14    | D13  | A07         | A06    |

| L         | L      | L    | L           | L      |

|           | РА     | D15  | A09         | A08    |

| м         | L      | L    | L           | L      |

| <u> </u>  | PAR    | PB   | A11         | A10    |

| N         | P1     | L    | L           | L      |

| <u> </u>  | PAR    | BBSY |             | A12    |

| Р         | P0     | L    | L           | L      |

| <u> </u>  | +15    | SAC  | ( A15       | A14    |

| R         | ВАТ    | L    | L           | L      |

| <u> </u>  | -15    | NPR  | A17         | A16    |

| s         | ВАТ    | L    | L           | L      |

| <b>—</b>  | GND    | BR7  | GND         | C1     |

| т         | 1      | L    |             | L      |

|           | +20    | BR6  | SSYN        | CO     |

| U         | (CORE) | L    | L           | L      |

| $\square$ | +20    | +20  | MSYN        |        |

| v         | (CORE) |      |             | (CORE) |

| L         |        |      |             |        |

11-4631

Figure 2-5 Standard and Modified Unibus Pin Designations

Dual height modules that are standard Unibus compatible should not be placed in the modified Unibus sections. To do so would destroy the modules.

The small peripheral control sections (C, D, E, and F) collectively contain all the Unibus connections (including grant lines) as well as power voltages (+5 V, +15 V, -15 V). These sections can be occupied by hex height or SPC modules containing control logic for peripheral devices. Figure 2-6 shows the pin designations for the SPC connectors.

| NIDE<br>PIN121212121ANPG<br>(IN)+5VTP+5VGND<br>A+5VABG<br>OUT+5VBNPG<br>(OUT)-15VTP-15VASSYN-15VABG<br>OUT-15VBNPG<br>(OUT)-15VTP-15VASSYN-15VABG<br>OUT-15VCPA<br>LGNDA SELGNDA12GNDSSYNGNDLPAGNDA SELGNDA12GNDSSYNGNDDLTCD15A OUTBR7A17A15BBSYF01LLOWLLLLN1N1ETPD13A SELBR6MSYNA16F01D02FTPD13A SELBR5A02C1D05D06LLLLLLHLLQQUTLLLENB BAINTLENB BAINTAINTBG7A14A13D08AINTJBL2OUTLLLLLZAINTKTPD09A OUTBG7A14A13D08AINTAINTLLBCQUTLLLZAINTLD07AINTBG6A11A13D08AINTAINTLAINTBG7 <th></th> <th>COLU</th> <th></th> <th>COLL</th> <th></th> <th>COLL</th> <th>MN</th> <th>COLL</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | COLU   |      | COLL  |      | COLL  | MN   | COLL  |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|-------|------|-------|------|-------|-------|

| A<br>A<br>(IN)NPG<br>(IN)+5VTP+5VGND<br>(GND+5VABG<br>(OUT)+5VABG<br>(OUT)+5VBNPG<br>(OUT)15VTP-15VASSYN-15VABG-15VBNPG<br>(OUT)15VTP-15VASSYN-15VABG-15VCLGNDASELGNDA12GNDSSYNGNDCL015A OUTBR7A17A15BBSYFO1DLTCD15A OUTBR7A17A16FO1D02LLLOWLLLLN1ETPD14ASELBR6MSYNA16FO1D02LL4LLLLLLFD13ASELBR5A02C1D05D06L0LLLLLLHD11D12A INBR4A01A00D07A INTJBL2OUTLLLLAJA INTD09A OUTBG7A14A13D08A INTJA INTD09A OUTBG7A14A13D08A INTJCD09A OUTBG7A14A13D08A INTKLLCUULLLKD09A OUTBG7 <td< td=""><td>SIDE</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SIDE     |        |      |       |      |       |      |       |       |

| A     (IIN)     INP     INP <td>PIN</td> <td>1</td> <td>2</td> <td>1</td> <td>2</td> <td>1</td> <td>2</td> <td>1</td> <td>2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIN      | 1      | 2    | 1     | 2    | 1     | 2    | 1     | 2     |

| (IN)(IN)(IN)(IN)(IN)(IN)(IN)(IN)(IN)(IN)BNPG15VTP.15VASSYN.15VABG.15V.15V(IU)(IU)(II)IINIINIINIINIINIINCPAGNDASELGNDA12GNDSSYNGNDLICD15A OUTBR7A17A15BBSYF01DICUOWICICICICN1TD15A OUTBR7A17A15BBSYF01DIASELBR6MSYNA16F01D02FD14ASELBR6MSYNA16F01D02CIA SELBR5A02C1D05D06FI013A SELBR5A02C1D05D06JBI2OUTILILIRNJD11D12A INBR4A01A00D07A INTJBI2OUTILILIAJD10A SELABRSSYNC0NPRGNDJA INTD08INITBG7A14A13D08A INTKIIOUTILILILILILMID09AOUTBG7A11TPD03F01M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | NPG    | +5V  | тр    | +5V  | GND   | +5V  | ABG   | +5V   |

| B         IOU         IOU         IOU         IN         IN         IN         IN           C         L         GND         A SEL         GND         A12         GND         SSYN         GND           D         L         GND         A SEL         GND         L         L         L         IN           D         L         LOW         L         L         L         NI         SSYN         GND           P         ITC         D15         A OUT         BR7         A17         A15         BBSY         F01           E         TP         D14         A SEL         BR6         MSYN         A16         F01         D02           F         TP         D13         A SEL         BR5         A02         C1         D05         D06           L         0         L         L         L         L         L         L         K           M         D11         D12         A IN         BR4         A01         A00         D07         A INT           J         D11         D12         A IN         BR4         SYN         C0         NPR         GND           J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A        | (IN)   |      |       |      | A     |      | ουτ   |       |

| IOUT)IOUT)IOUT)ININPAGNDA SELGNDA12GNDSSYNGNDLGNDBR7A17A15BBSYF01DLLOWLLLLN1PD15A OUTBR7A17A15BBSYF01DLLOWLLLLN1PD14A SELBR6MSYNA16F01D02FTPD13A SELBR5A02C1D05D06L0LLLLLLLHD11D12A INBR4A01A00D07A INTHD11D12A INBR4A01A00D07A INTJA INTD10A SELA BRSSYNC0NPRGNDJA INTD10A SELA BRSSYNC0NPRGNDJA INTD10A SELA BRSSYNC0NPRGNDKTPD09A OUTBG7A114A13D08A117KLSOLLLLLMCSOAA11TPD03F01LENBASOLLLLLMLSOA11TPD33F01D04MLGNDAINTBG6 <t< td=""><td></td><td>NPG</td><td>-15V</td><td>тр</td><td>-15V</td><td>ASSYN</td><td>-15V</td><td>ABG</td><td>-15V</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | NPG    | -15V | тр    | -15V | ASSYN | -15V | ABG   | -15V  |

| CLIndicationIndicationIndicationIndicationIndicationDLIC0LLLIN1DLLOWLLLLN1ETPD14A SELBR6MSYNA16FO1D02LL4LLLV2LFTPD13A SELBR5A02C1D05D06L0LLLLLLHD11D12A INBR4A01A00D07A INTLLLLLLLENBBJAINTD10A SELA BRSSYNC0NPRGNDJBL2OUTLLLBJRD09A OUTBG7A14A13D08A INTKTDD08INITBG7A11TPD03F01LENBBLLOUTLLLL2MTPD07AINTBG6AINAOUTINTRF01LENBASOLLN1L2N1L2MDCD04AINTBG6AOUTA08F01D04LENBASOLLN1L2N1L2MDCD04AINTBG5A09ASELF01 <td>в</td> <td>(OUT)</td> <td></td> <td></td> <td></td> <td>IN H</td> <td></td> <td>IN</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | в        | (OUT)  |      |       |      | IN H  |      | IN    |       |

| LGGLLLLDLLBR7A17A15BBSYF01LLOWLLLLN1ETPD14ASELBR6MSYNA16F01D02CL4LLLV2LFTPD13ASELBR5A02C1D05D06L0LLLLLLPD13ASELBR5A02C1D05D06L0LLLLLLPD11D12AINBR4A01A00D07AINTHD11D12AINBR4SSYNC0NPRGNDJBL2OUTLLLAINTMD10ASELABRSSYNC0NPRGNDJBL2OUTLLLAINTMD09AOUTBG7AI14A13D08AINTKLSOLLLLLLMD09AOUTBG7AI11TPD03F01LLSOLAINTBG6AUNAUUNITMDCD04AINTBG6AUUA08F01D04MLOLAOUTLOAINTBG5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | PA     | GND  | A SEL | GND  | A12   | GND  | SSYN  | GND   |

| DLLLLLLLLLN1ETPD14A SELBR6MSYNA16FO1D02L4LLLV2LFTPD13A SELBR5A02C1D05D06L0LLLLLLLHD11D12A INBR4A01A00D07A INTHLLLLLLENB BJA INTD10A SELA BRSSYNC0NPRGNDJBL2OUTLLLAKTPD09A OUTBG7A14A13D08A INTKTPD09A OUTBG7A11TPD03F01LSOLLLLLLMD07AINTBG7A11TPD03F01LENBBLUOUTLLLLMDCD04AINTBG6AUTA08F01D04NDCD04AINTBG6AOUTA08F01D04NLOLAOUTLON1LLPBC0LSOLUN1LPBC0LSOLLN1LPGR1 <td>Ľ</td> <td>L</td> <td></td> <td>6</td> <td></td> <td>L</td> <td></td> <td>L</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ľ        | L      |      | 6     |      | L     |      | L     |       |

| Image: border                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | LTC    | D15  | A OUT | BR7  | A17   | A15  | BBSY  | F01   |

| ELALLLV2LFTPD13A SELBR5A02C1D05D06L0LLLLLLHD11D12A INBR4A01A00D07A INTLLLLLLLENBBJA INTD10A SELA BRSSYNC0NPRGNDJBL2OUTLLLAMTPD09A OUTBG7A14A13D08A INTKTPD09A OUTBG7A11TPD03F01LLOUTLLLLLMTPD08INITBG7A11TPD03F01LENBBLLOUTLLLLMTPD07AINTBG6AINAOUTINTRF01MDCD04A INTBG6A OUTA08F01D04NLOLAOUTLOWLN1LPREQLAOUTLOWLN1LPREQLAOUTLOWLN1LPREQLAOUTLAQUTP2REQLAOUTSOGQUP2N1 <t< td=""><td>Ū</td><td></td><td>L</td><td>LOW</td><td>L</td><td>L</td><td>L</td><td>L</td><td>N1</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ū        |        | L    | LOW   | L    | L     | L    | L     | N1    |

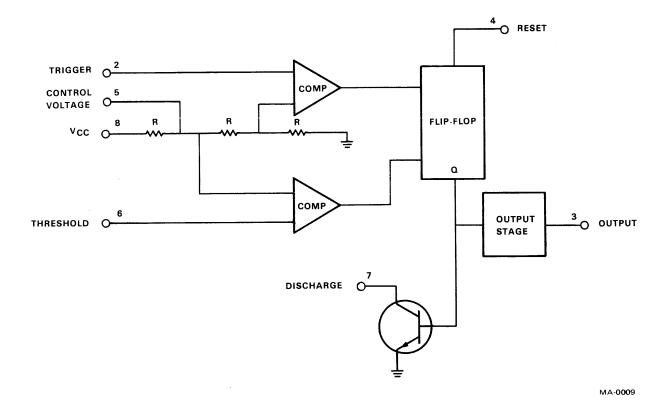

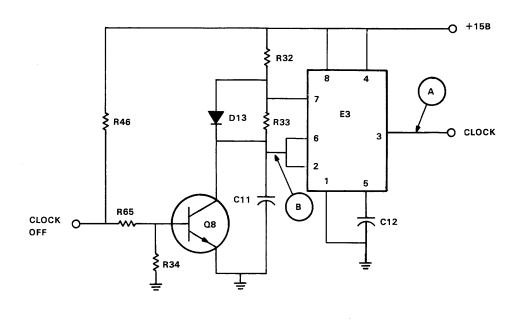

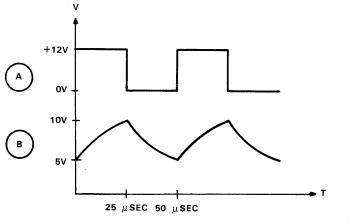

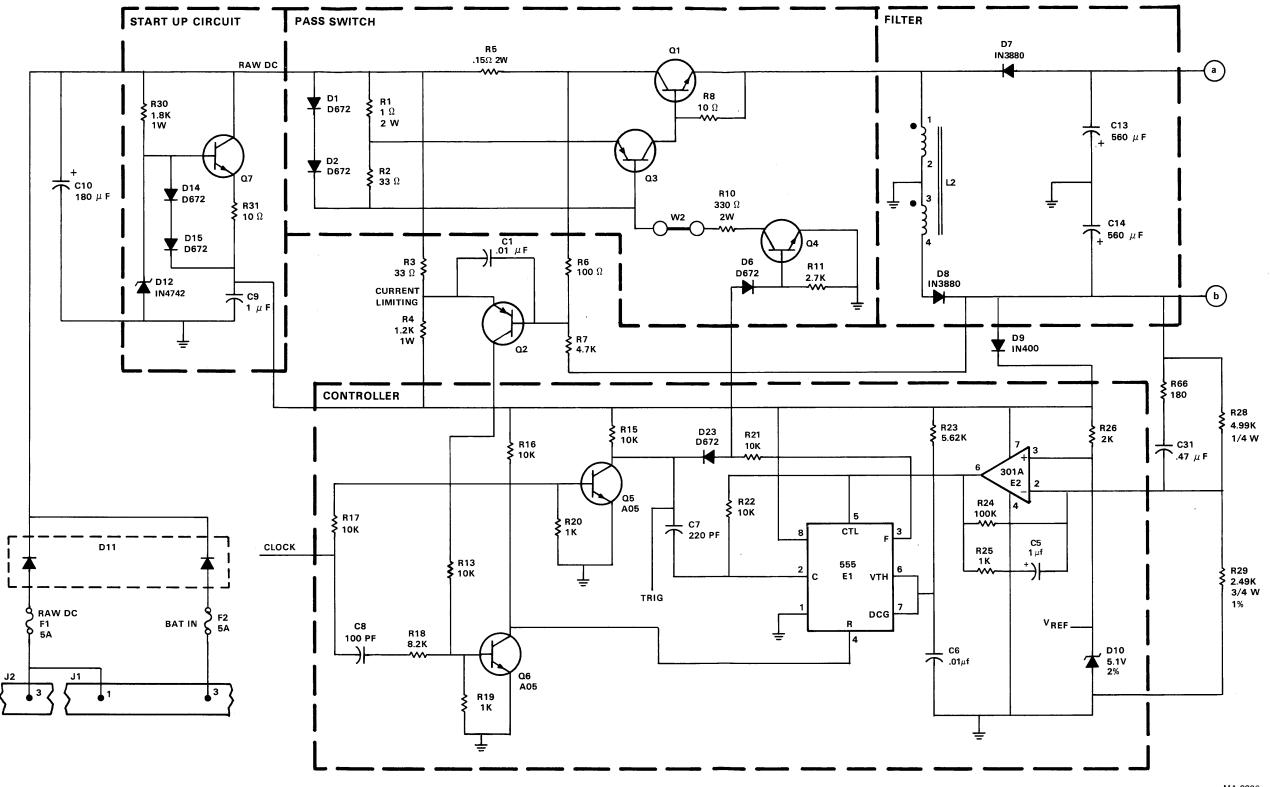

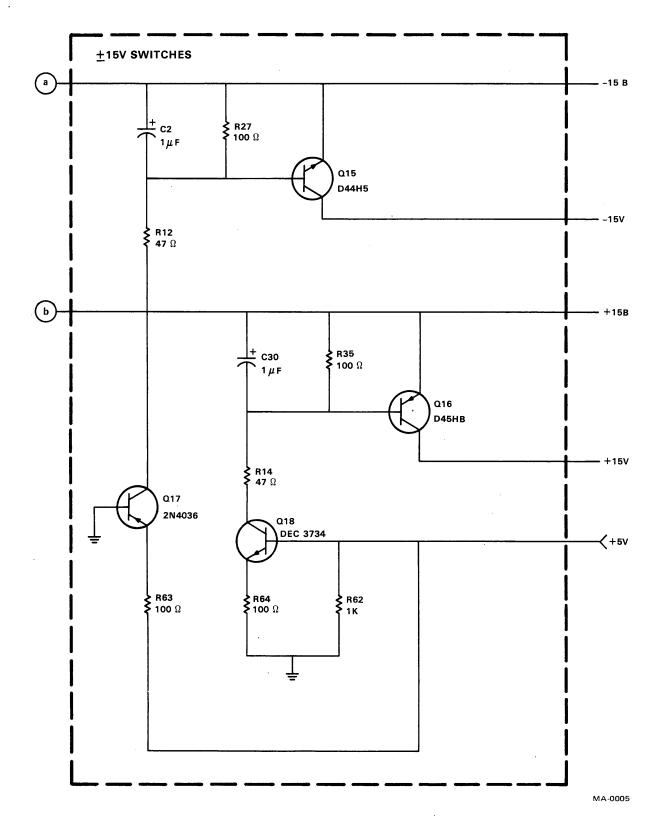

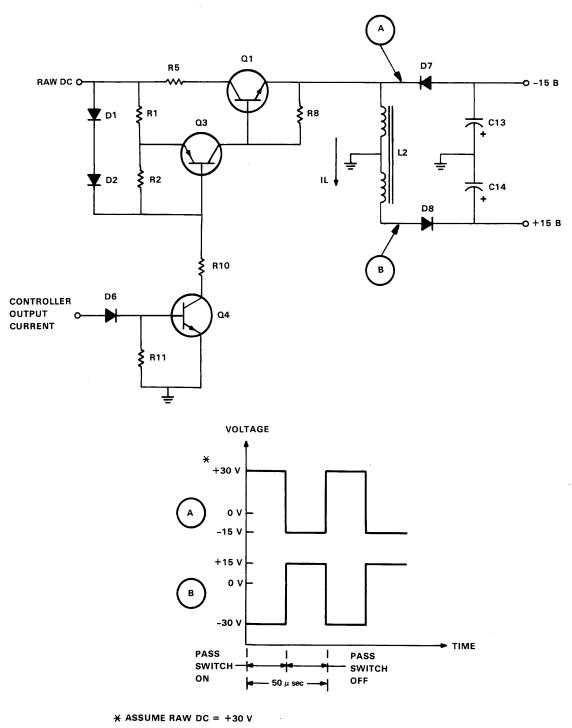

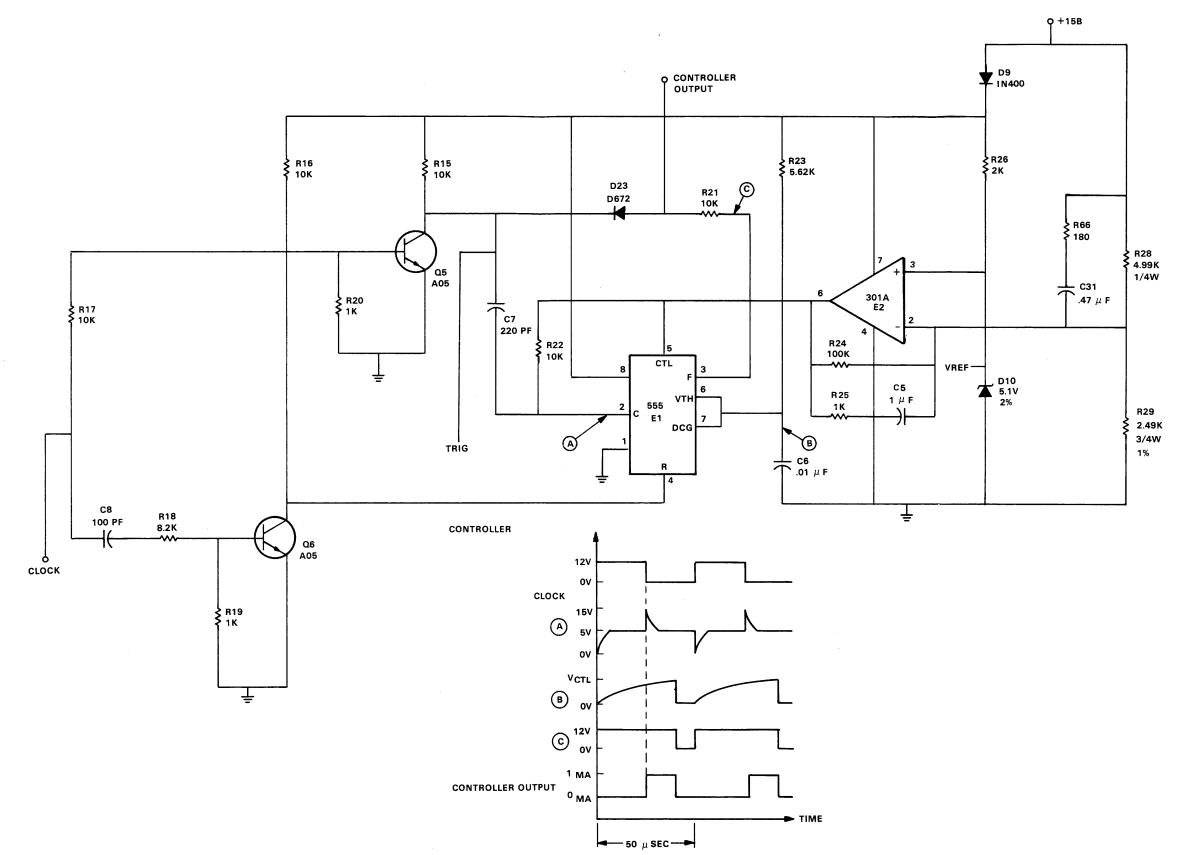

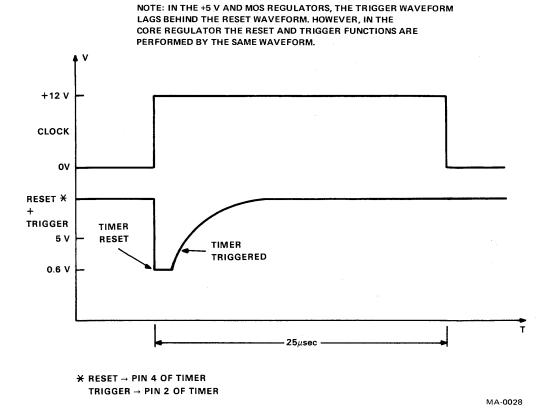

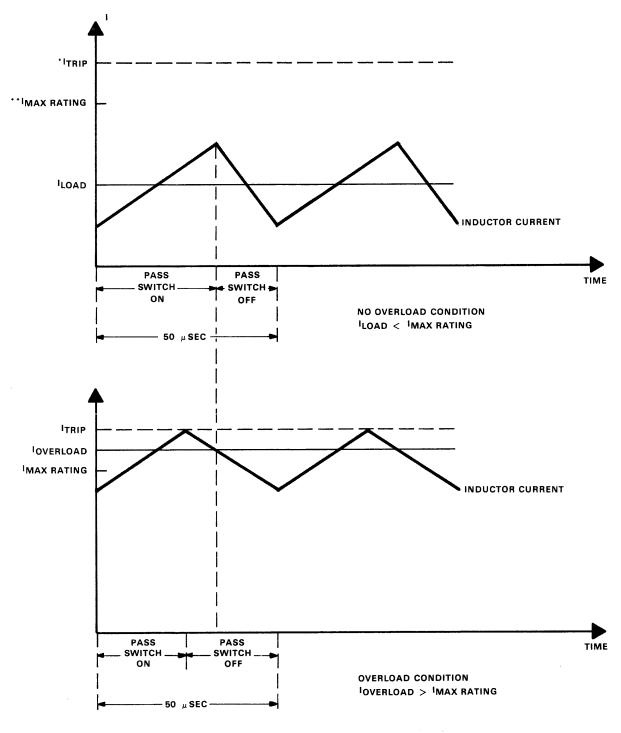

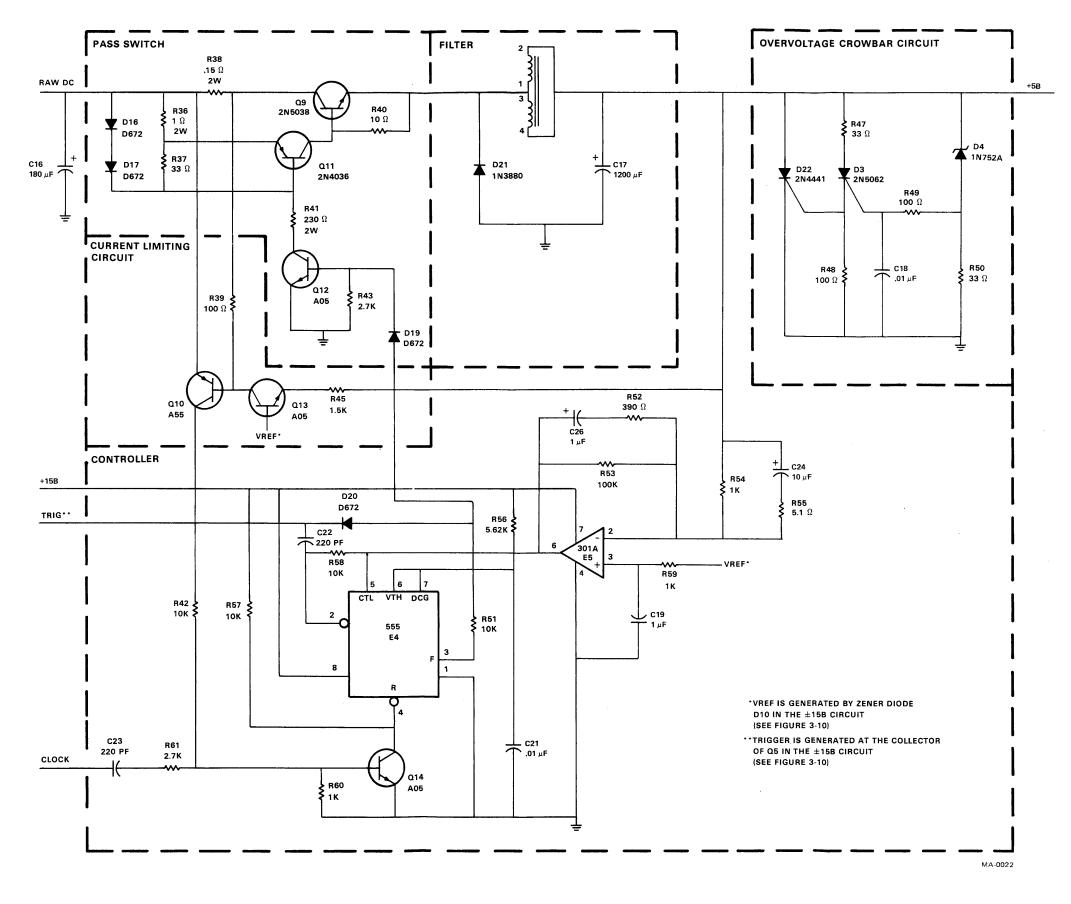

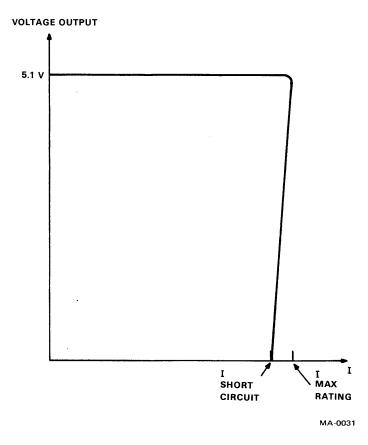

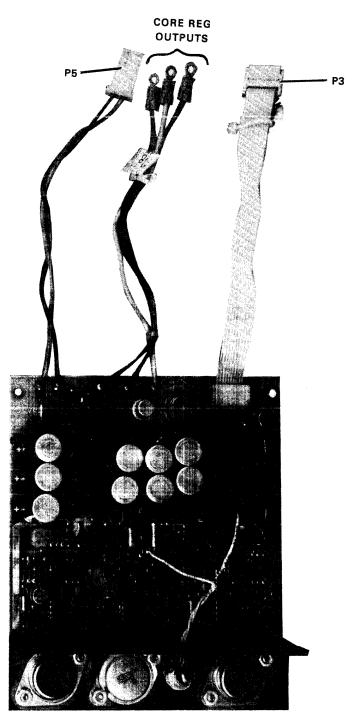

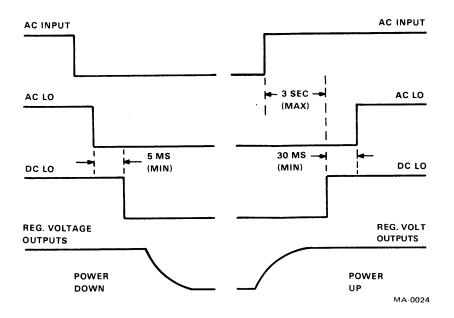

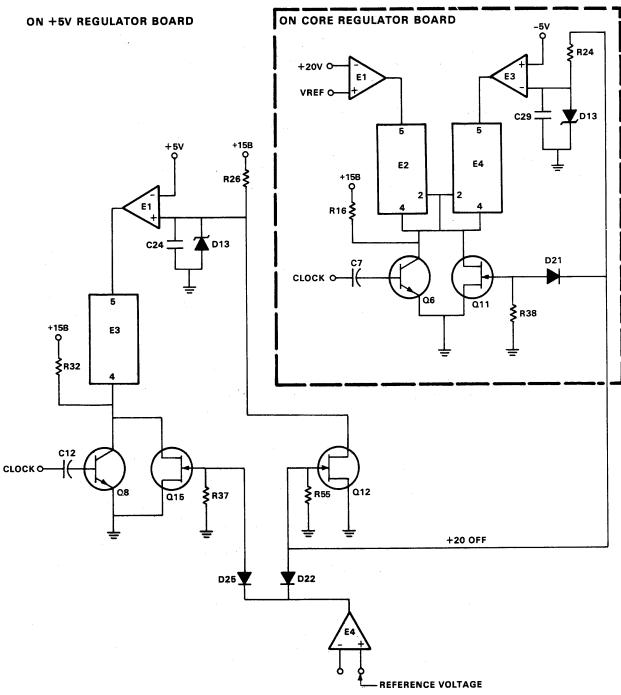

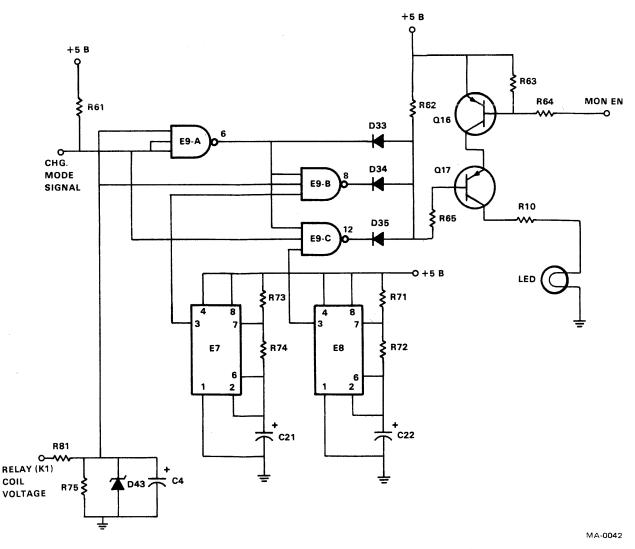

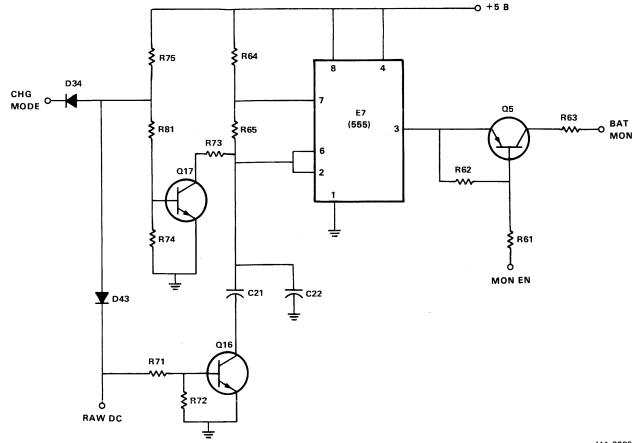

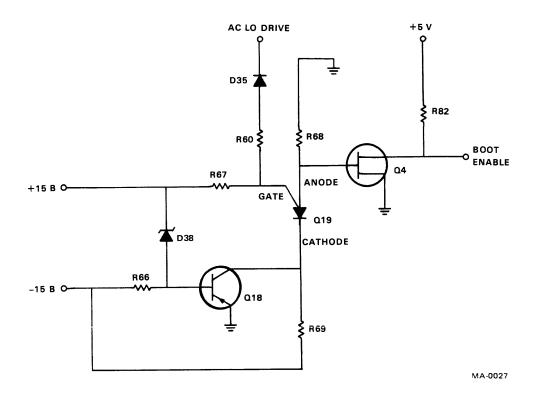

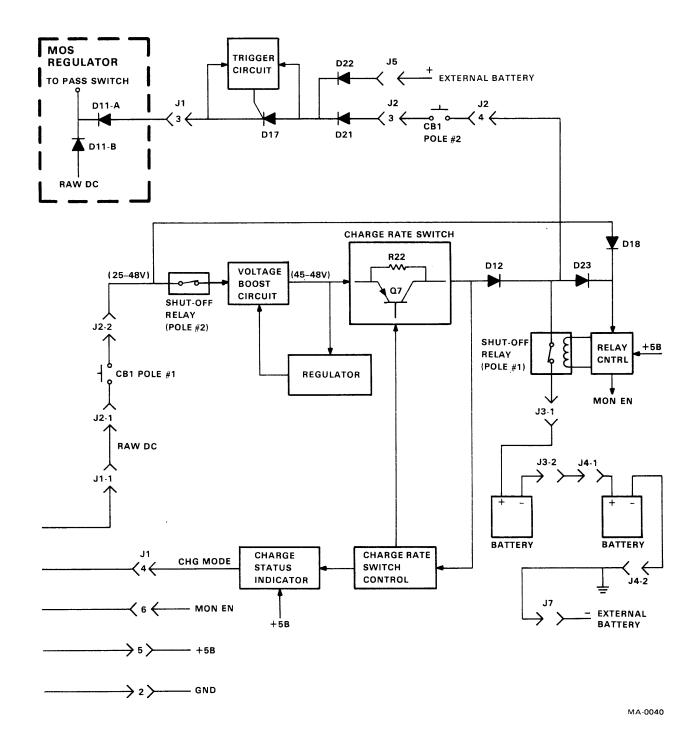

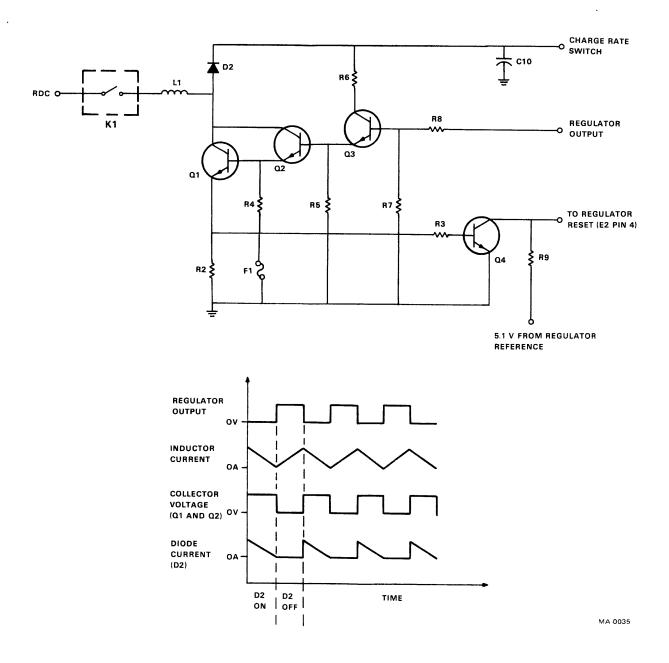

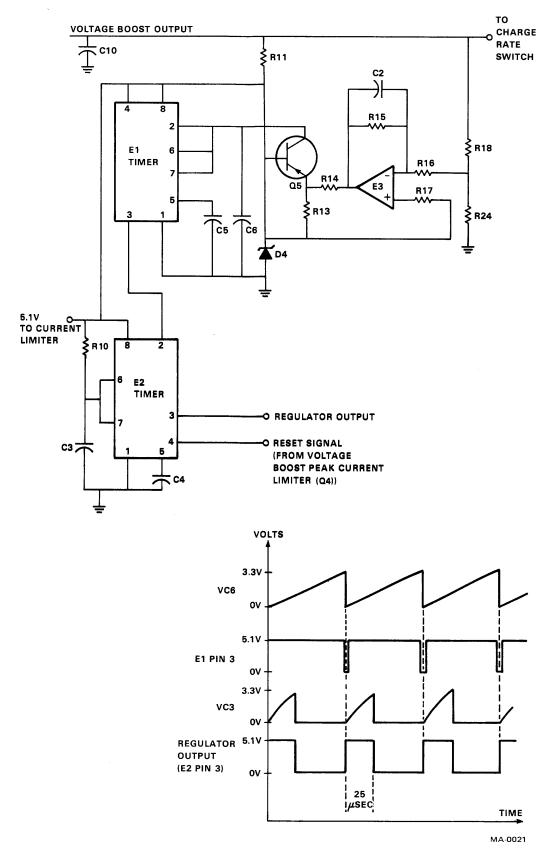

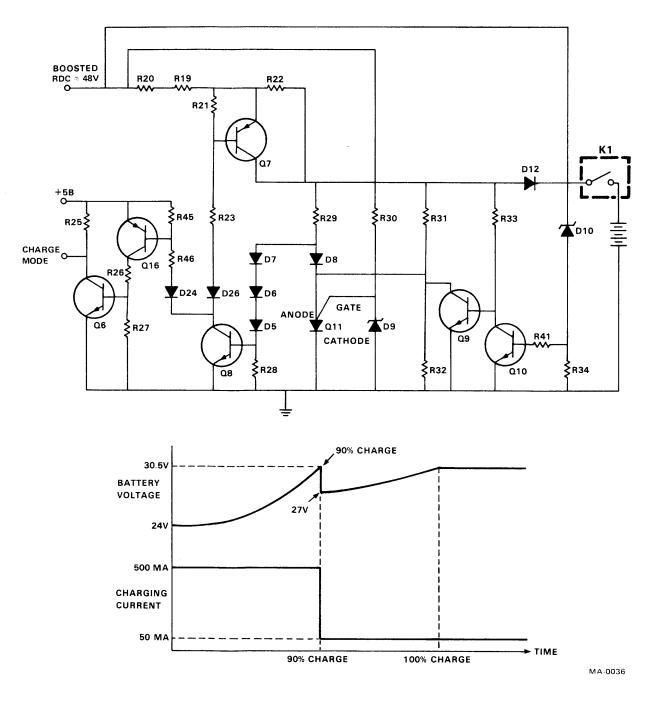

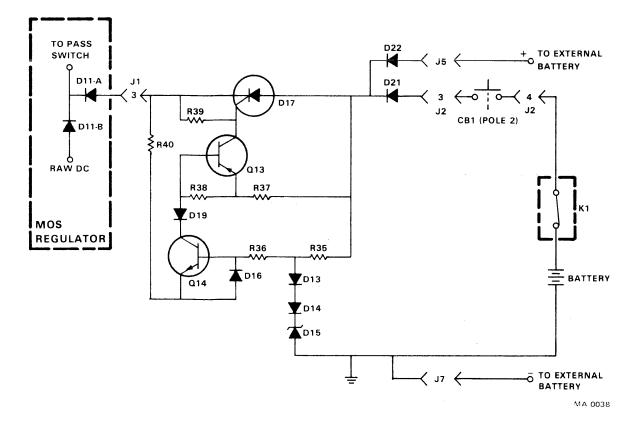

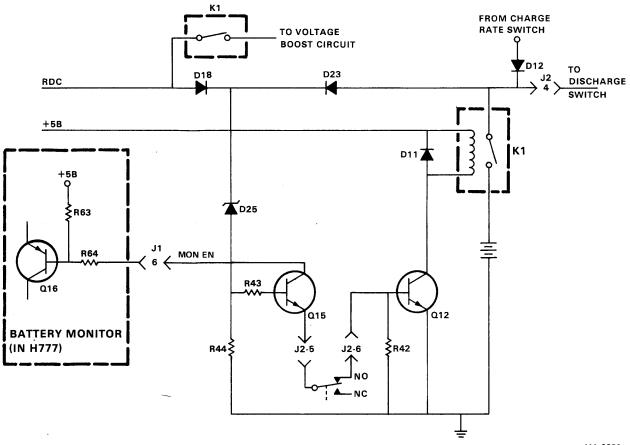

| Image: big                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _        | тр     | D14  | A SEL | BR6  | MSYN  | A16  | F01   | D02   |