## PRELIMINARY

BA11-L Mounting Box

Maintenance Manual

The information in this document is subject to change without notice, and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

Copyright C 1975,1976 by Digitial Equipment Corporation Written by PDP-11 Engineering Printed in U.S.A.

# CONTENTS

| CHAPTER | 1                                                                                                                                             | BA11-L PHYSICAL CHARACTERISTICS AND SPECIFICATIONS                                                                                                                                                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1,1,1,1                                                                                                                                       | GENERAL<br>Scope                                                                                                                                                                                                                                      |

|         | 1,2                                                                                                                                           | PHYSICAL CHARACTERISTICS                                                                                                                                                                                                                              |

|         | 1,3                                                                                                                                           | OPTIONAL I/O CABLE RETRACTOR ASSEMBLY                                                                                                                                                                                                                 |

|         | 1 • 4<br>1 • 4 • 1<br>1 • 4 • 2<br>1 • 4 • 3<br>1 • 4 • 4                                                                                     | H777 POWER SUPPLY PHYSICAL CHARACTERISTICS AC Control Assembly Physical Description Main (+5V) Regulator Assembly Physical Description MOS Regulator Assembly Core Regulator Assembly                                                                 |

| CHAPTER | 2                                                                                                                                             | SYSTEM UNITS, OPTIONS AND HARNESS                                                                                                                                                                                                                     |

| CHAPTER | 2 • 1 • 1<br>2 • 1 • 1 • 1<br>2 • 1 • 1 • 2<br>2 • 1 • 1 • 3<br>2 • 1 • 2<br>2 • 1 • 2 • 1<br>2 • 1 • 2 • 2<br>2 • 1 • 2 • 3<br>2 • 1 • 2 • 3 | SYSTEM UNITS CONCEPT System Units Single System Unit Double System Unit Power Distribution DDIP Backplane SPC (Small Peripheral Controller) Bus MUD (Modified Unibus Device) Bus NPG (Non Processor Grant) Line BG (Bus Grant) Line H777 POWER SUPPLY |

|         | 3,1                                                                                                                                           | GENERAL                                                                                                                                                                                                                                               |

|         | 3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                                                                       | PHYSICAL DESCRIPTION  AC Control Assembly +5V main Regulator  MOS Converter  Core Memory Regulator                                                                                                                                                    |

|         | 3,3,1<br>3,3,2<br>3,3,3,3<br>3,3,4                                                                                                            | BLOCK DIAGRAM DESCRIPTION  AC Control Assembly  Clock  Switch for +15V Isolation  Control for Console Interface                                                                                                                                       |

|         | 3.4                                                                                                                                           | DETAILED CIRCUIT DESCRIPTION                                                                                                                                                                                                                          |

```

Raw DC Circuitry

3,4,1

3,4,1,1

Circuit Breaker BA

3.4.1.2

Inrush Current Limiting

The 555 Timer

3,4,2

3,4,3

Clock Circuit

3,4,4

Series-Connected Power switching Stage

3,4.5

Flyback Stage (+15V Filter Scheme)

3.4.6

Control Circuit for Regulating Main +5V

3,4,6,1

Voltage Reference

3.4.6.2

Error Amplifier

3.4.6.3

Current Source

3.4.6.4

Pulse Width Modulation

3.4.7

Alternate Control Circuit for Regulating (Outputs

Other Than +5, Main)

3.4.8

Base Drive Circuit (Main +5V Regulator)

3,4,9

Protection Sequencing and Control Circuits

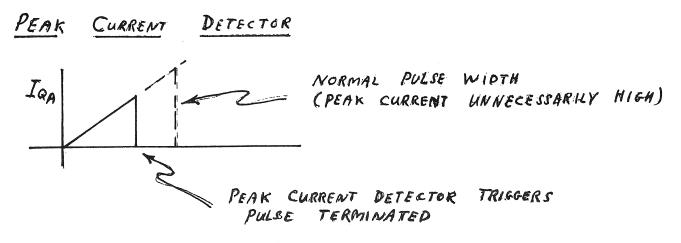

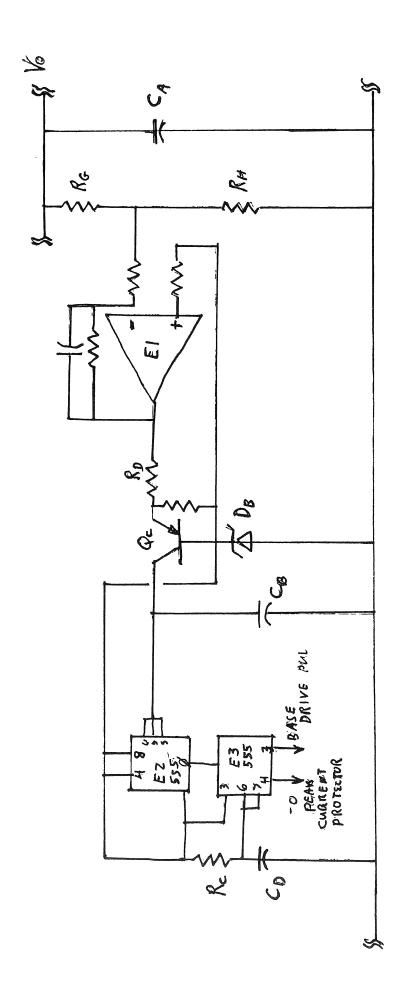

Current Limit Circuit 54-11597

3,4,9,1

3,4,9,2

Current Limit Circuit +5B Regulator

Crobar (Crowbar) Circuits Over-Voltage Protection

3,4,9,3

on +5, +5B, and +20 Volt Regulators

3,4,9,4

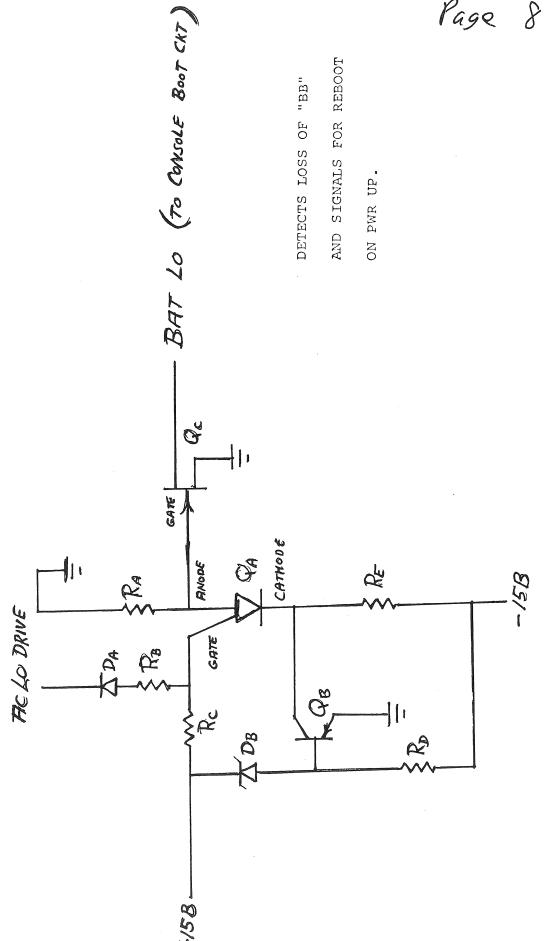

Power Fail Detectors

3.4.9.5

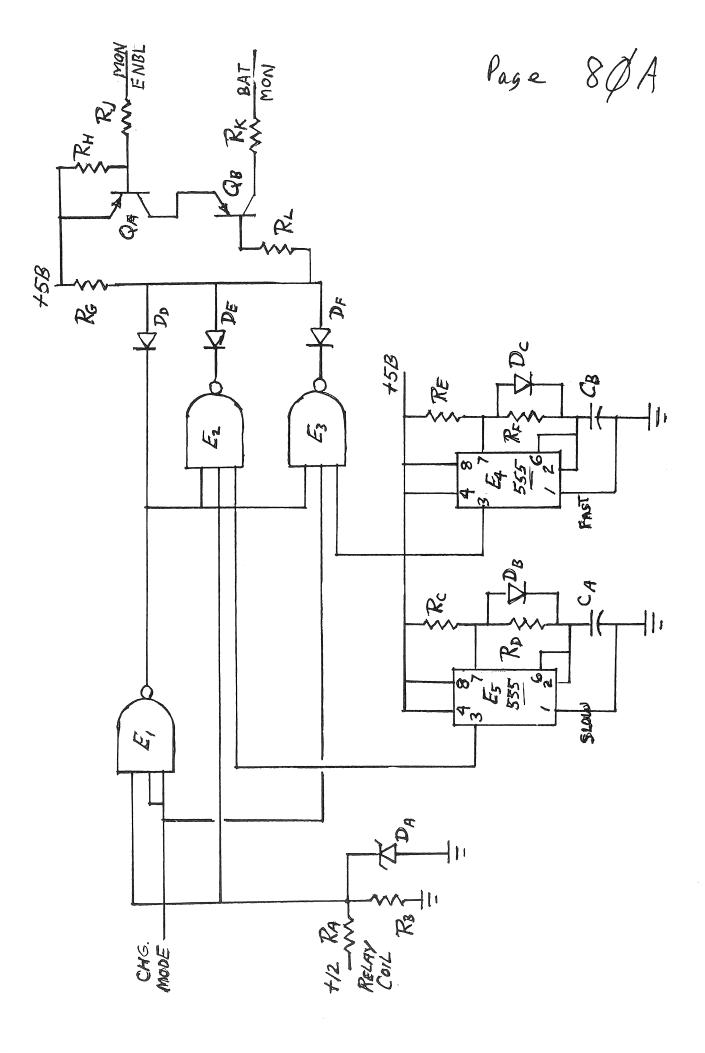

Battery Monitor Circuits

3.4.9.6

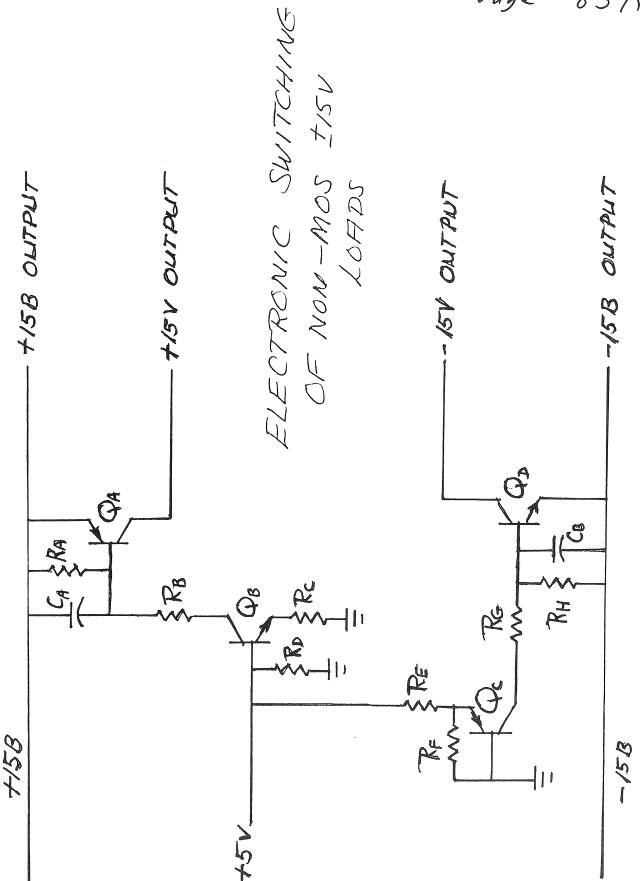

Electric Switching of Non-MOS Loads

3.4.9.7

Battery Lo Detector

Keep Alive Power

3.4.9.8

3,5

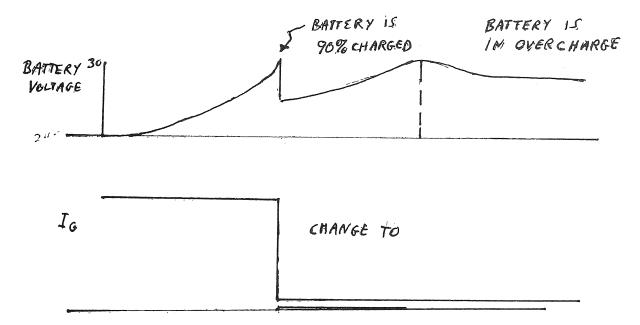

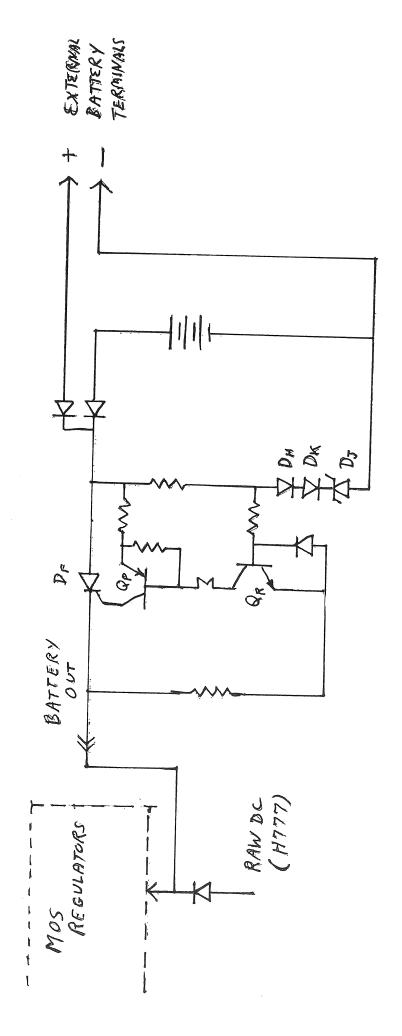

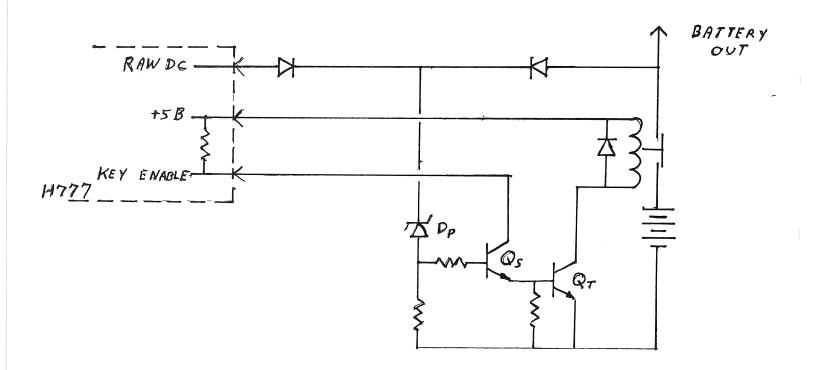

BATTERY BACKUP

General Description

3,5,1

3.5.2

mechanical Configuration

3,5,3

Detailed Circuit Description

3,5,3,1

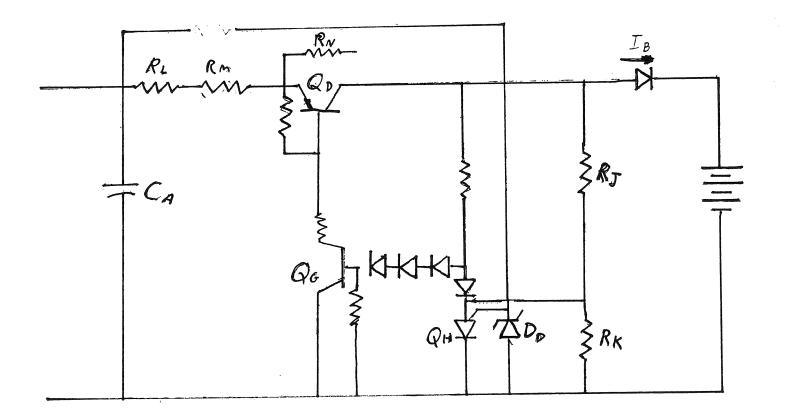

Main Power Train

3,5,3,2

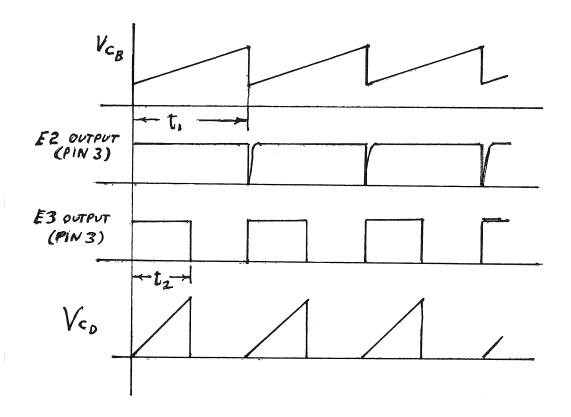

Control Circuit

3,5,3,3

Charge Rate Control

3.5.3.4

Battery Output Section

3,5,3,5

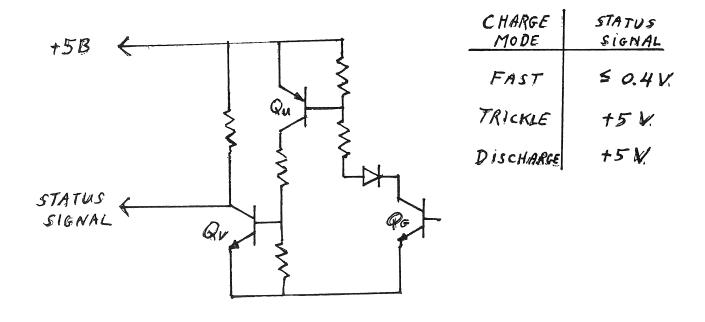

Charge Rate Signal

CHAPTER 4

BA11-L MAINTENANCE

4.1

GENERAL

4.2

PREVENTIVE MAINTENANCE

4.2.1

Mechanical/Electrical

CORRECTIVE MAINTENANCE

4.3

4.3.1

voltage Regulator Checks

H777 POWER SUPPLY

4.4

4,4,1

H777 Power Supply Removal

4,4,2

Removal of H777 Power Supply Subassemblies

4.4.3

Power Supply Cover Removal

Removal of AC Control Assembly

4.4.4

4.4.5

Fan Removal

Fan Removal - Logic

4,4,5,1

4,4,6

MOS Regulator Removal

4,4.7

Main +5V Regulator Removal

```

# FIGURES

| Number         |                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------|

| 1 = 1<br>1 = 2 | BA11-L Mounting Box Extended from Wire Frame<br>BA11-L Mounting Box (Removed from Wraparound<br>Envelope) |

| 1 - 3          | AC Control Assembly                                                                                       |

| 1-4            | +5V Main Regulator Assembly                                                                               |

| 1-5            | MOS Regulator Assembly                                                                                    |

| 1 • 6          | Core Regulator Assembly                                                                                   |

| 2-1            | Single System Unit Array                                                                                  |

| 2 • 2          | Double System Unit Array                                                                                  |

| 2 • 3          | DD11-P Power Distribution Harness                                                                         |

| 2-4            | DD11-P Slot Usage                                                                                         |

| 2=5            | NPG Signal Routing Bus Grant Routing                                                                      |

| 4 = 0          | phy ataur wontrud                                                                                         |

| 3-1            | BA11 Mounting Box Showing Connectors and Cables                                                           |

| 3-2            | H777 Major Power Supply Components                                                                        |

| 3-3            | Block Diagram of H777 Power Supply                                                                        |

| 3 * 4          | Raw DC and Relay Driver Circuits = H777                                                                   |

| 3=5            | 555 Timer<br>H777 Clock Circuit                                                                           |

| 3*6<br>3*7     | Typical Regulator Series Switching Stage                                                                  |

| 3 = 8          | Flyback Circuit Used in + or = 15V Regulator                                                              |

| 3=9            | Feedback Path-Used in Main +5V Section of H777                                                            |

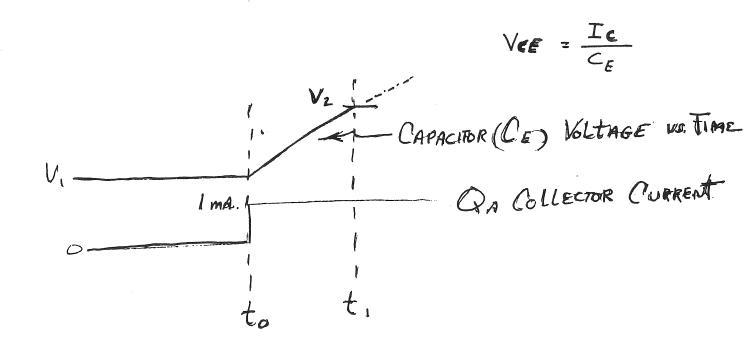

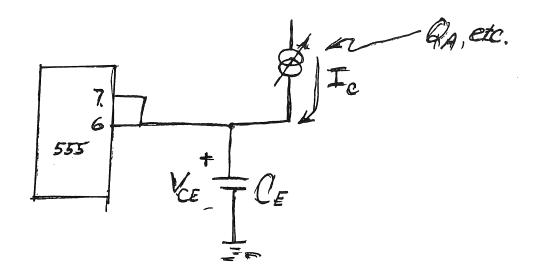

| 3-10           | Capacitor (CE) Waveform                                                                                   |

| 3-11           | QA Current Bypass                                                                                         |

| 3=12           | Summary of Timing Sequence                                                                                |

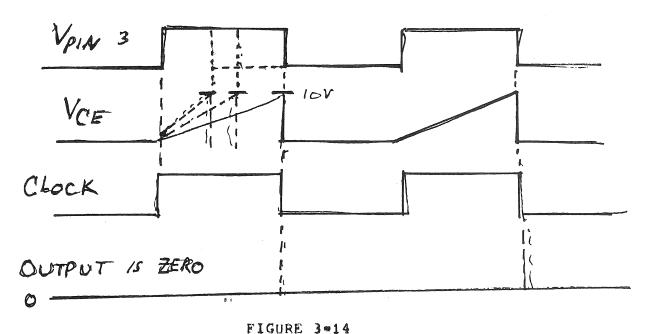

| 3-13           | Vce Waveforms with Higher Current Levels                                                                  |

| 3-14           | vce Charge Time vs. High Clock Time                                                                       |

| 3-15           | Alternate PWM Circuit (Used in Regulators other                                                           |

|                | than Main +5)                                                                                             |

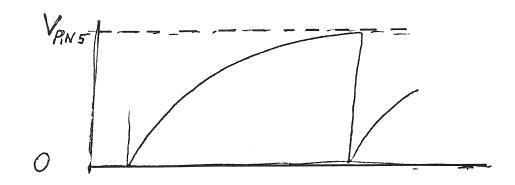

| 3-16           | Main Timing Capacitor Charging Curve                                                                      |

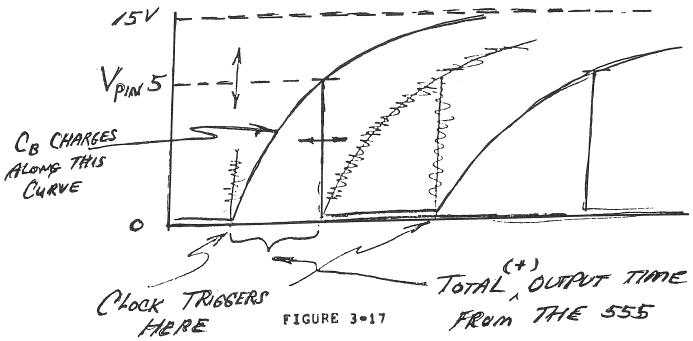

| 3-17           | Effect of Varying Threshold                                                                               |

| 3-18           | Base Drive Circuit for +5V Regulator Q(P) Collector Current Waveform                                      |

| 3-19<br>3-20   | Foldback Current Limiting Circuit for Main +5V                                                            |

| 2-66           | Regulator                                                                                                 |

| 3=21           | Current Through RA                                                                                        |

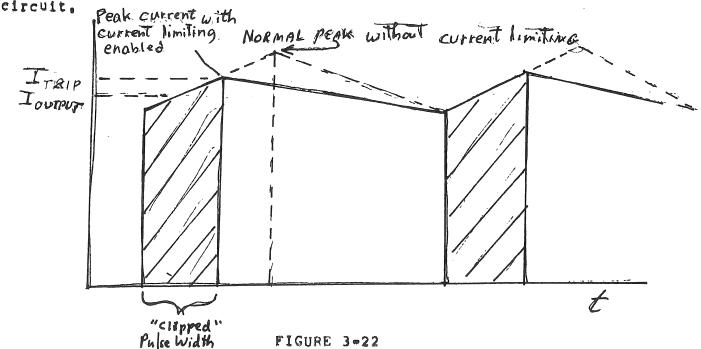

| 3-22           | Increasing Load Current Beyond Trip Level                                                                 |

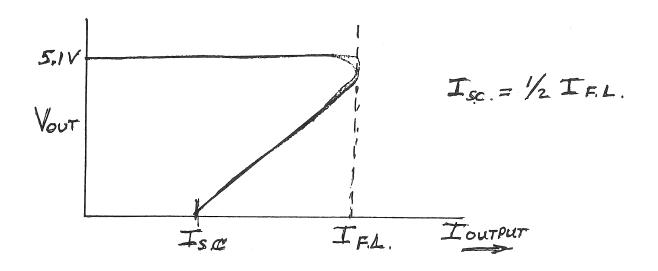

| 3-23           | Output Voltage/Current Foldback                                                                           |

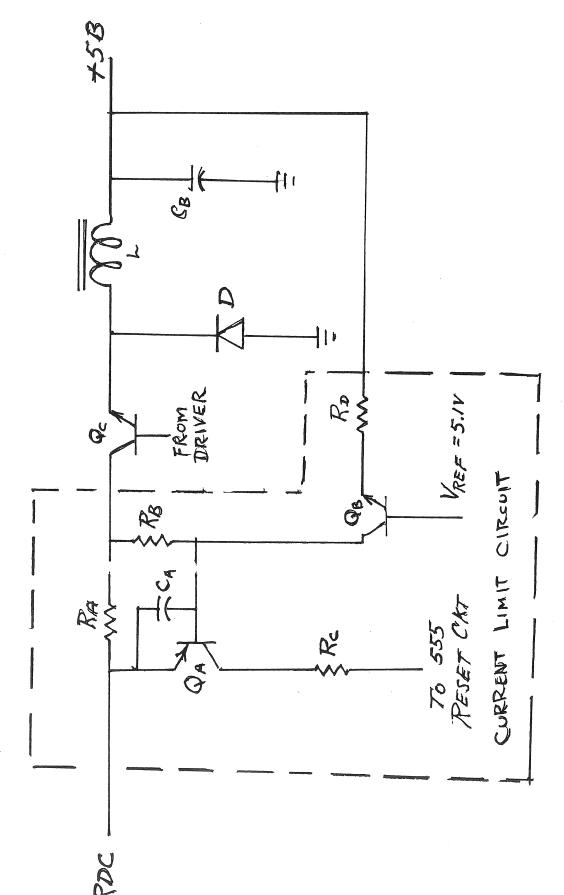

| 3-24           | Current Limit Circuit for +5B Regulator                                                                   |

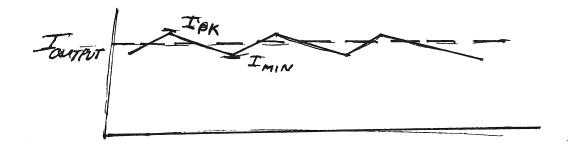

| 3-25           | Q(C) Collector Current Waveform                                                                           |

| 3-26           | Typical Crobar Circuit                                                                                    |

| 3-27           | power Fail and Sequencer Circuitry                                                                        |

| 3-28           | Power Fail Detector Waveforms                                                                             |

| 3-29           | Power Down Sequence                                                                                       |

| 3 = 30         | Battery Monitor Circuits                                                                                  |

| 3-31           | Electronic Switching of Non-MOS Loads                                                                     |

| 3=32           | Battery Lo Detector                                                                                       |

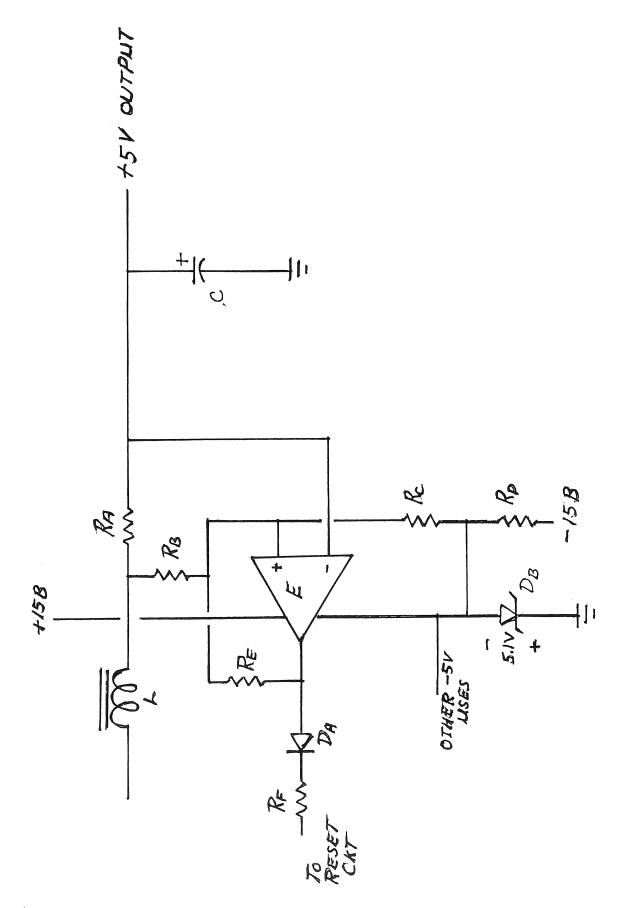

| 3-33   | Keep Alive Power                                |

|--------|-------------------------------------------------|

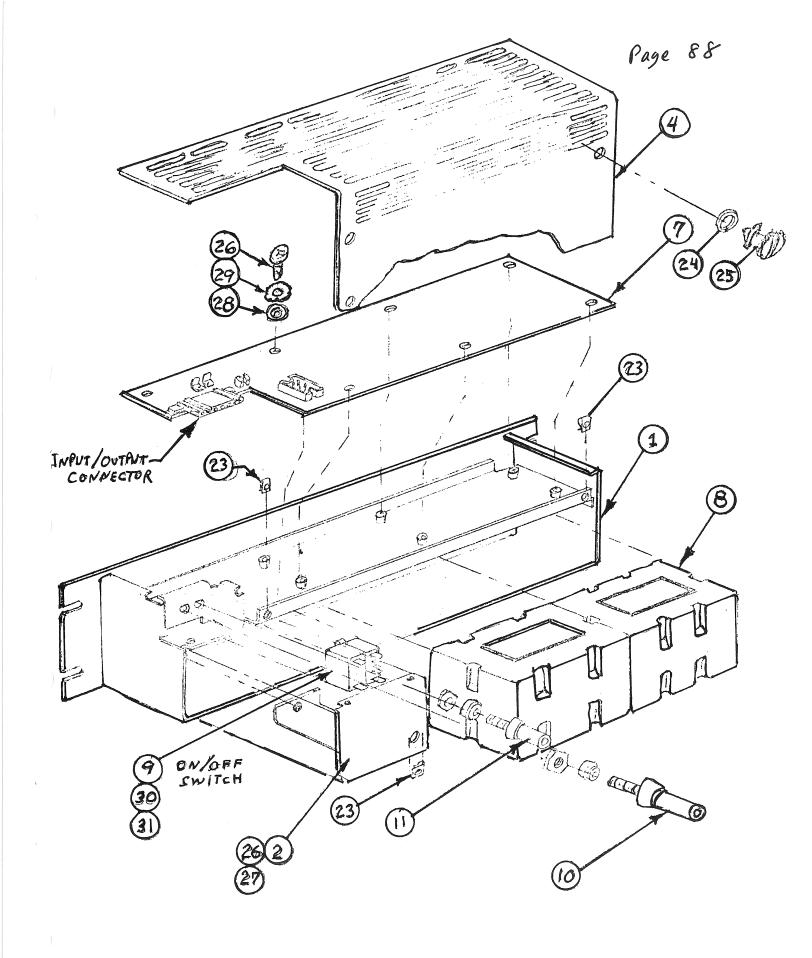

| 3-34   | Battery Backup Unit (H775)                      |

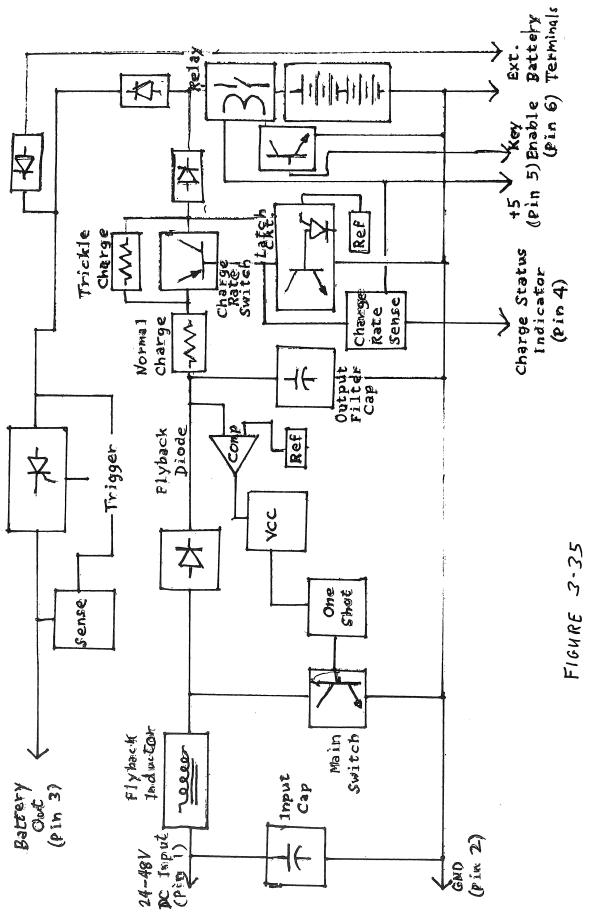

| 3=35   | Functional Block Diagram of Battery Backup Unit |

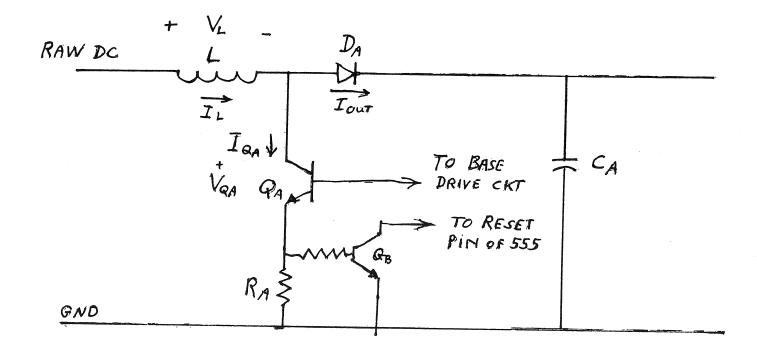

| 3=36   | Main Power Train of Boost Regulator             |

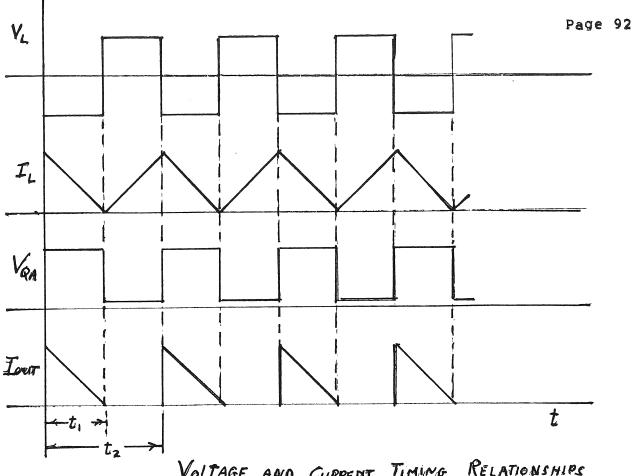

| 3-37   | Operation of Main Power Train                   |

| 3=38   | Regulation Control Circuitry                    |

| 3=39   | Relative Timing of the Two 555 Timers           |

| 3-40   | Charge Control Section                          |

| 3 = 41 | Output Circuit                                  |

| 3-42   | self=Shut Off Circuit                           |

| 3-43   | Charge Status Signal                            |

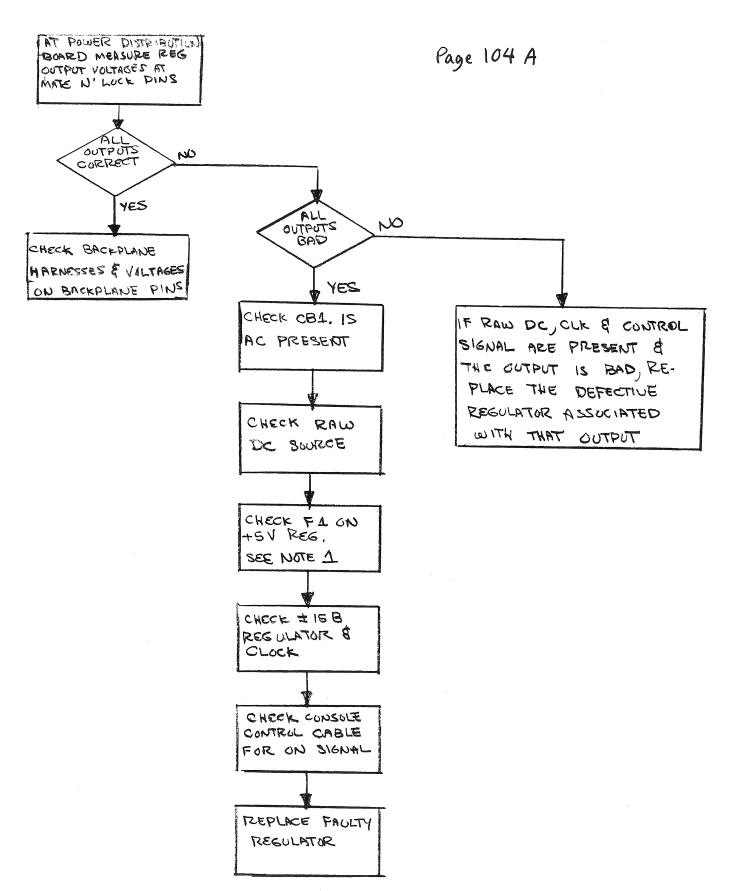

| 4 • 1  | H777 Fault Isolation Flow Chart                 |

| 4-2    | H777 With Cover On                              |

# TABLES

| Table No.               |                                                                                       |                      |

|-------------------------|---------------------------------------------------------------------------------------|----------------------|

| 1 = 1                   | BA11-L Specifications - Physica                                                       | al and Environmental |

| 2 = 1<br>2 = 2<br>2 = 3 | Backplane Power Harness to Power Modified Unibus and SPC Pins Modified Unibus Devices | er Distribution      |

| 3-1                     | PWM Design Limits                                                                     |                      |

| 4-1                     | Regulator Output Specification                                                        | 5                    |

|  |  |  | )   |

|--|--|--|-----|

|  |  |  | (1) |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

THE BA11-L MOUNTING BOX MAINTENANCE MANUAL

#### CHAPTER 1

## BA11-L PHYSICAL CHARACTERISTICS AND SPECIFICATIONS

## 1.1 GENERAL

This manual describes the BA11=L rack=mounted expander box manufactured by Digital Equipment Corporation. The BA11=L box is 19 inches wide, 5 1/4 inches high, and 25 inches deep. It provides power to the various components mounted in the box (see Figure 1=1).

## 1.1.1 Scope

This manual is designed to provide Digital Field Service and customer maintenance personnel with sufficient installation, operation, and servicing information to install and maintain the box.

## 1.2 PHYSICAL CHARACTERISTICS

The BA11-L mounting box is designed to provide a strong mounting frame with maximum accessibility and serviceability. The mounting frame is divided into two sections; one section contains all the logic modules, the other section contains the H777 power supply.

The mounting frame slides into a rack mounting wrap around envelope that completely encloses all four sides of the frame. The front and back of the envelope are open for front to back air flow. The wraparound envelope mounts directly into a cabinet, without rack slides, and functions as the slide mechanism for withdrawing the frame and its contents.

An operator's console assembly (KY11LA) mounts on the front of the BA11=L frame. The console assembly contains the power control and limited function switches required for system operations.

Table 1-1 is a list of BA11-L physical and environmental specifications.

FIGURE 1=1

BA11L Mounting Box (Extended From Wire Frame)

### TABLE 1-1

### BAll-L Specifications

BA11L Mounting Box

Chassis size with operators console

5 1/4"H x 19"w x 25"D

Unconfigured weight with H777

Module slots

9 maximum using DEC standard

backplanes

Cooling efficiency for both fans at 90vac + or = %, 50hz

Shock and vibration characteristics (operating)

1/2 sine shock pulse of 10 GPK and 10 + or =3ms, duration

(non-operating)

1/2 sine shock pulse of 40 GPK and 30 + or =10 ms. duration

Fan air movement direction

Front to rear, 2 channels

Cooling efficiency for both fans at 90vac + or -

See Bob Allen

H777 Power Supply

Size

5"H x 6 1/2"W x 20"D less power cord

Weight (MOS version)

Weight (Core Version)

Input MOS (H777-C, H777-D)

90-132, 180-264 Vac RMS

47-63 Hz.

Dual primary

Core (H777-A, H777-D)

104-127, 208-254 vac RMS

47+63 Hz Dual primary Output\*

Battery Support +5V, + or =5%, 0=25 Amp +15V, + or =5%, 0=1 Amp =15V, + or =5%, 0=1 Amp +5V, + or =5%, 0=2 Amp =5V, + or =5%, 0=2 Amp +20V, + or =3%, 0=6 Amp

Average (DC meter readings)

Noise

Ripple

3% p-p or less, of nominal voltage

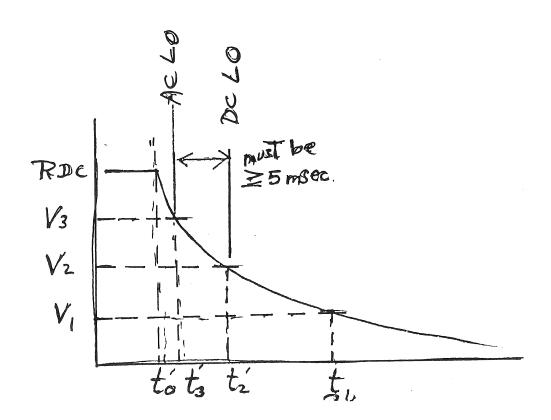

AC Lo and DC Lo must be > or =5 msec.

Protection:

Overload/short circuit protection recovers upon removal of overload.

SSC = 50% x Irated

Overvoltage crobar protection on +5 and +20 volts. Indirect overvoltage protection on MOS backup voltages.

Battery Interface:

Battery voltage 18-48V for MOS backup.

Battery voltage 24-48V for system or core backup (recabling required).

Current drain < or =2.5 Amp from 24V battery (64K MOS, MM11-S).

Charging = 2 Amp max.

available current @ 23-48 VDC.

Signals = Charger mode,

Key/Enable.

Adjustments:

+ or =15V adjusted to + or =12V by jumper. No other adjustments available.

<sup>\*</sup> Total DC power NTE 240 watts

Environmental:

Ambient; temperature Ø degrees C=60 degrees C humidity = per DEC STD, 102. Shock & Vibration; per DEC STD 102 for Class C equipment.

Coolings

300 LFPM min, airflow required (Fan mounted on BA11=L).

Efficiency:

60% minimum = overall.

BATTERY BOX

Size:

Input/Output:

Capacity:

Cell Type:

Charger:

Weight:

5 1/4" x 19" Rack Mount x 4",

+23-48 DC/+24 DC.

120 Watt hour @ 50 degrees C, @2.5 Amp rate.

Sealed lead-acid, Nickel cadmium or GEL-cell may be used with appropriate charge in capacity spec,

Constant current, dual rate

15 lb.

### 1.3 OPTIONAL I/O CABLE RETRACTOR ASSEMBLY

An optional spring-loaded cable retractor assembly (part no. )that mounts to the rear of a standard 19" rack is available. Its function is to provide a service loop for Unibus and I/O cabling to protect them against fraying when the wire frame is extended.

The retractor assembly will accommodate all the round and flat cabling styles presently available.

### 1.4 H777 POWER SUPPLY PHYSICAL CHARACTERISTICS

The H777 power supply is a compact modular assembly designed to fit into the BA11-L box. It is rectangular in shape and open at both ends for front-to-rear air flow.

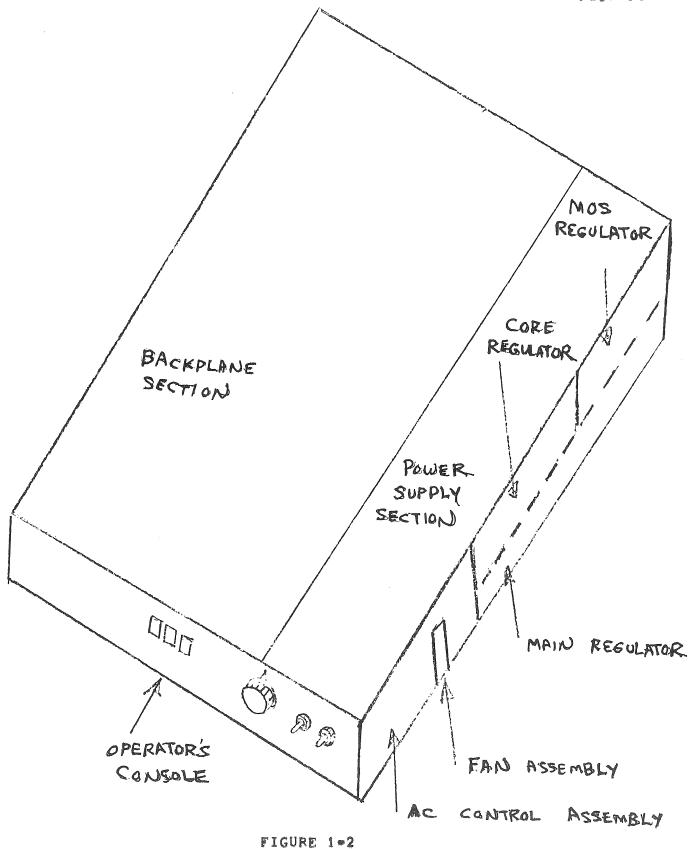

There are five modular subassemblies in the H777 (See figure 1-2):

AC control assembly +5V main regulator MOS regulator Core regulator Fan

With the exception of the AC control assembly, all the subassemblies can be removed and installed while the H777 assembly is mounted in the BA11=L box.

#### NOTE

The H777 Power Supply is available in the following designations:

H777A - 115V supply - core and MOS (metal oxide semi-conductor) memory

H777B - 230v supply - core and MOS memory

H777C = 115v supply = MOS memory only H777D = 230v supply = MOS memory only

Instructions on the top of the power supply specify the correct designation.

BA11L Mounting Box (Removed from Wraparound Envelope)

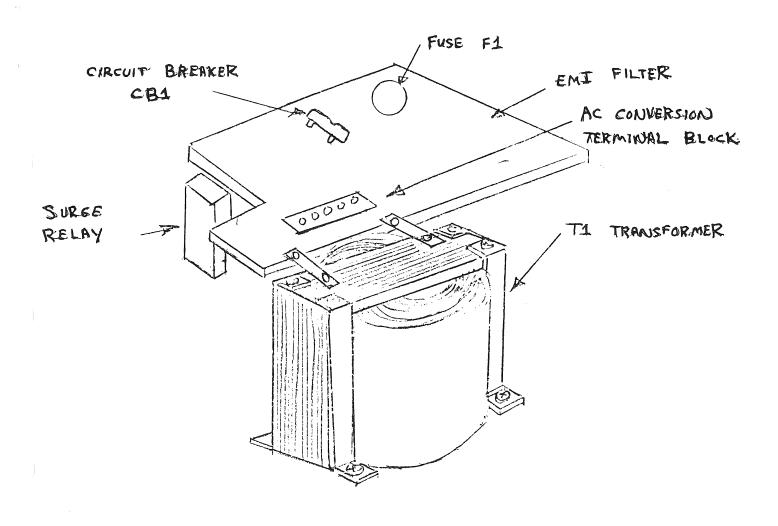

- 1.4.1 AC Control Assembly Physical Description (see Figure 1-3)

The AC control assembly contains the following components:

- Linear transformer (T1) = provides stepped=down voltage and isolation of the power supply from the AC line; operates at 47 to 63 hz.

- Circuit breaker = turns off AC power in the event of a power surge or when maintenance personnel desire to work on the power supply.

#### CAUTION

Never remove the power supply cover without turning circuit breaker off, as AC is still present.

- . AC conversion terminal block provides conversion from 115 vac to 230 vac (see directions on terminal block cover).

- Surge resistor = provides inrush current limiting when supply is connected to a=c source.

- Surge relay = bypasses surge resistor after the raw DC is established (normal operation),

- . F1 surge protector protects surge resistor if relay fails.

- EM1 line filter = keeps power supply noise isolated from AC source.

- 1,4,2 Main (+5v) Regulator Assembly Physical Characteristics

The main regulator assembly consists of a large and small printed circuit board assembly interconnected by a soldered power harness.

FIGURE 1-3

AC Control Assembly

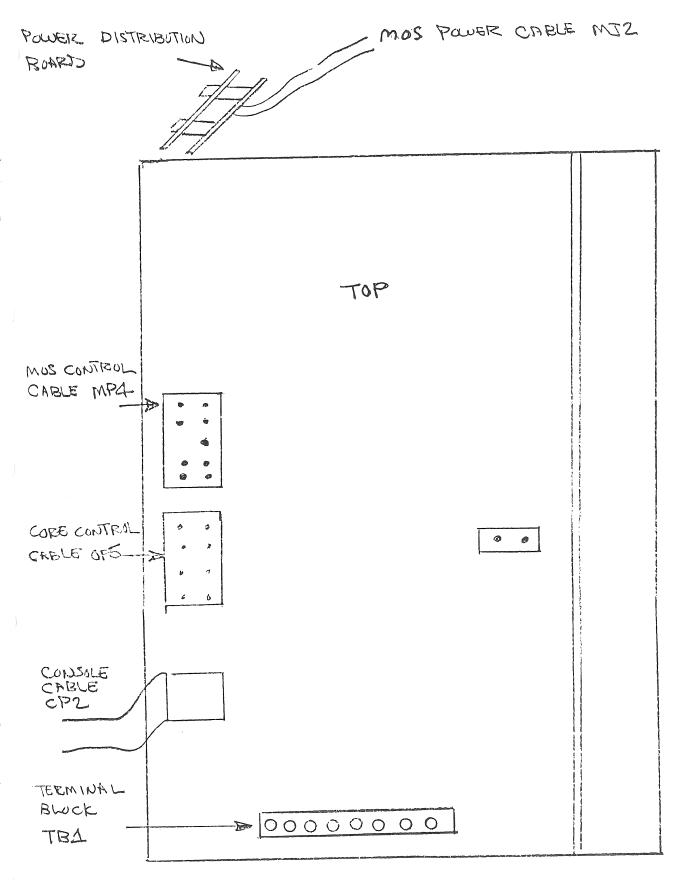

The larger board (+5V regulator) contains a +5V low=voltage switching regulator, power sequence logic (AC LO, DC LO, LTC) and battery monitor logic. The small board (power distribution board) contains power connectors which provide outputs to two system unit power cables, and a power control connector.

There are no adjustments on the main regulator assembly.

A number of module interconnect and control connectors are mounted on the larger +5V board. These connectors are identified in Figure 1-4.

## 1.4.3 MOS Regulator Assembly (see Figure 1-5)

The MOS regulator is in reality three regulators: +15V, +15V and +5V. The +15V and +15V regulators have dual switched and unswitched outputs. The unswitched set runs on battery backup to run MOS (metal oxide semi-conductor) memory modules, the switched outputs run option modules requiring + or +15V and are powered off in standby and battery backup modes.

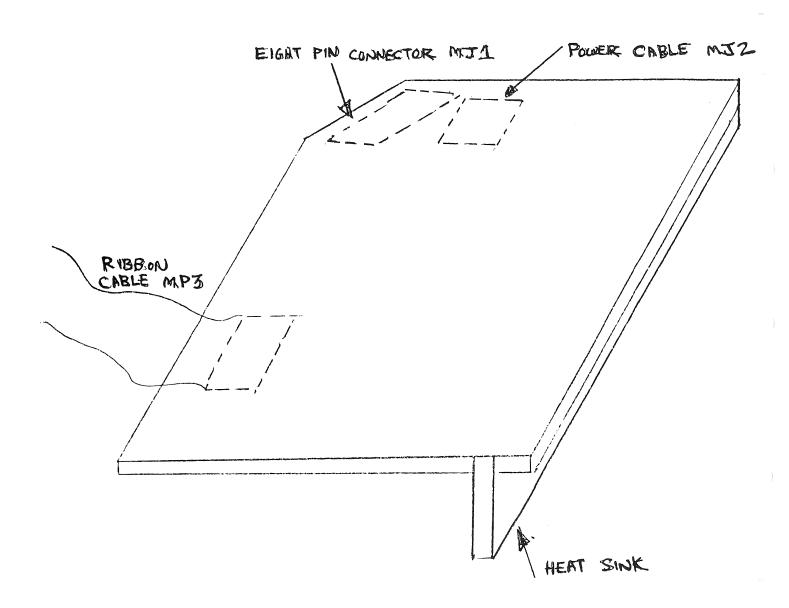

The regulator assembly mounts inverted on top of the +5 main regulator assembly. A small ribbon cable (MP3) and a large nine-pin power cable (MJ2) provide interface connections to the rest of the supply. A straight, eight-pin connector (MJ1) mounted over the power Distribution Assembly provides a Battery Backup Option interface.

## 1.4.4 Core Regulator Assembly (see Figure 1.6)

The core regulator is an optional assembly in the H777. It is required when core memory modules are used as part of a system.

The core regulator, like the MOS regulator, is a multiregulator. The core modules require +20V and -5V.

The core regulator assembly mounts inverted beside the MOS regulator and on top of the MAIN +5V regulator.

The power and control signals from the core regulator interconnect via the main regulator assembly.

Figure 1-4

+5V Main Regulator Assembly

FIGURE 1-5

MOS Regulator Assembly

To Be Supplied

FIGURE 1-6

Core Regulator Assembly

#### CHAPTER 2

#### SYSTEM UNITS, OPTIONS AND HARNESS

### 2.1 SYSTEM UNITS CONCEPT

This chapter describes the concept of the DEC System Units in general and the DD11-P nine-slot backplane in particular. These units have been developed to implement the new Modified Unibus system while maintaining a Standard Unibus input/output interface. This development allows system interfaces to remain the same and increases the flexibility of internal interconnection.

### 2.1.1 System Units

The term system units has come into usage to identify the building block concept of all DEC systems. A system unit consists of a matrix wired together to provide power and signal interconnections to accommodate a group of logic modules.

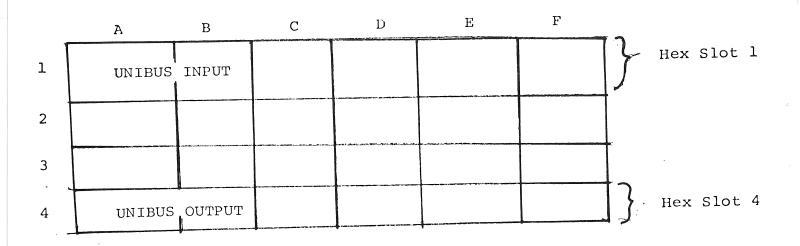

2.1.1.1 Single System Unit (see Figure 2-1) - The smallest System Unit is the Single System Unit. It consists of a four (1-4) by Six (A-F) connector array, which is four hex slots used for module mounting, (see pDp-11/04 user's Guide - Configuration Section). Many special system units are dedicated to a special set of modules, such as a disk interface. Slot 1 connectors A and B, and slot 4 connectors A and B are always used for Unibus Input and Unibus output connections, respectively.

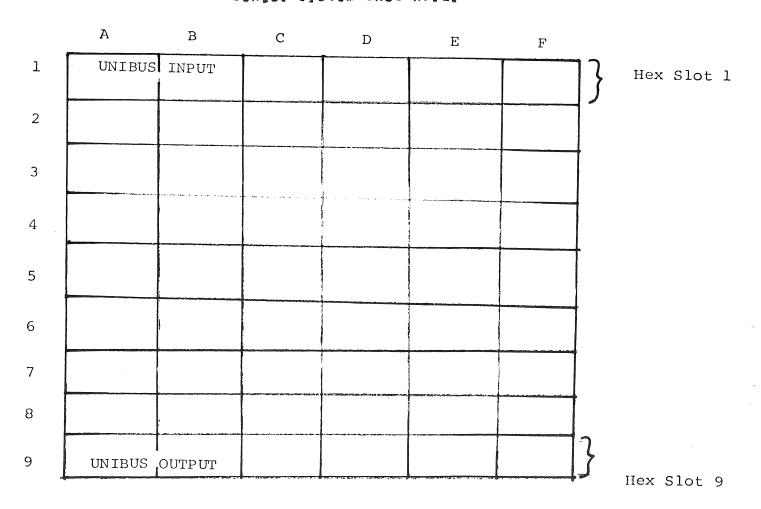

2.1.1.2 Double System Units (see Figure 2-2) - This System Unit consists of a nine by six connector matrix. This unit has nine hex slots for module mounting.

Slot 1 connector A and B and slot 9 connector A and B are dedicated to Unibus input or beginning and Unibus output or termination, respectively.

FIGURE 2-1

Single System Unit Array

FIGURE 2-2 Double System Unit Array

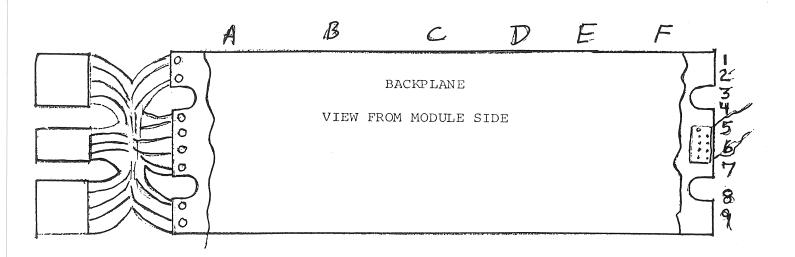

2.1.1.3 power Distribution - While Unibus control signals enter and leave a system unit via the Unibus cable, DC power for modules enters the System Unit via the DC Power Distribution Harness attached to the "A" connector end of the system unit printed circuit board backplane.

The power distribution harness, depending on type, consists of several high-current Mate-N-Lok connectors that are wired by a short harness to the System Unit (see Figure 2-3). The harness for the DD11-C backplane consists of a 15-pin Mate-N-Lok connector containing DC voltages and a 6-pin connector containing AC Lo, DC Lo and LTC signals. The harness for the DD11-P backplane consists of two 15-pin Mate-N-Lok connectors carrying DC voltages and a 6-pin connector containing AC Lo, DC Lo, and LTC signals. The power harness must be configured to match the power supply configuration employed by a given system. The H777 and H765 power supply systems used in the BA11-L (5 1/4") and BA11-K (10 1/2") expansion boxes have identical power distribution systems which means that the same power harnesses can be used in either box. See Table 2-1.

## 2.1.2. DD11-P Backplane

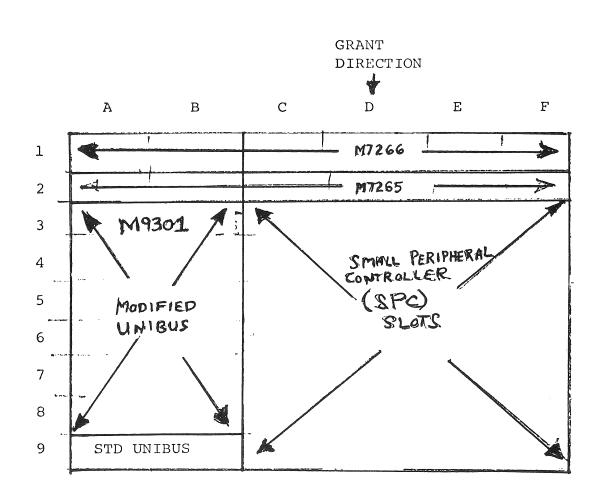

The DD11-P backplane is a double system unit designed for the PDP-11/34 and PDP-11/39 dual-hex CPU modules. Slot one is reserved for the CPU control Module (M7266) and slot two is reserved for the CPU Data Path Module (M7265). The remaining seven slots are available for system configurations involving a wide variety of standard DEC memories and interfaces. Figure 2-4 defines slot usage.

FIGURE 2-3

DD11-P Power Distribution Harness

# BACKPLANE POWER HARNESS TO POWER DISTRIBUTION

## BOARD INTERFACE

## TABLE 2=1

| BA11=L/<br>Power D<br>BD Pin | 1st.          | Wire Color                                   | DD11-C<br>Harness<br>Pin Usage<br>D=IA-7011109 | DD11-P<br>Harness<br>Pin Usage<br>D-IA-7011108 |

|------------------------------|---------------|----------------------------------------------|------------------------------------------------|------------------------------------------------|

| #1 15-P                      | in Mate-N-Lok |                                              |                                                |                                                |

| 1 +5                         |               | Red                                          | X                                              | X                                              |

| 2 +1                         | 5 V           | Gray                                         | X                                              | X                                              |

| 3 +2                         | Ø             | orange                                       | X                                              | X                                              |

| 4 +5                         |               | Red                                          | X                                              | X                                              |

| 5 GN                         | D             | Black                                        |                                                |                                                |

|                              | 5B            | white                                        | Х                                              | X                                              |

| 7 GN                         | D             | Black                                        |                                                |                                                |

| 8 GN                         | D             | Black                                        | X                                              | X                                              |

| 9 GN                         | D             | Black                                        | X                                              | X                                              |

| 10 (S                        | PARE)         |                                              |                                                |                                                |

| 11 GN                        | D             | Black                                        |                                                |                                                |

| 12 +5                        | V             | Red                                          | X                                              |                                                |

| 13 -1                        | 5 V           | Blue                                         | X                                              | <b>.X</b> ,                                    |

| 14 -5                        | V             | Brown                                        | X                                              |                                                |

| 15 -1                        | 5B            | Green                                        | X                                              | X                                              |

| #2 6*P1                      | n Mate=N=Lok  |                                              |                                                |                                                |

| 1 Lo                         | GND           | Black                                        | X                                              | X                                              |

| 2 LT                         | C             | Brown                                        | X                                              | X                                              |

| 3 DC                         | Lo            | violet                                       | X                                              | X                                              |

| 4 AC                         | Lo            | Yellow                                       | X                                              | Х                                              |

| 5 (S                         | PARE)         | <b>商                                    </b> |                                                |                                                |

| 6 (S                         | PARE)         | C O O O                                      |                                                |                                                |

| #3 15=P                      | in Mate-N-Lok |                                              |                                                |                                                |

| 1 +5                         | ٧             | Red                                          |                                                | X                                              |

|                              | 5 V           | Gray                                         |                                                | X                                              |

|                              | ØV            | Orange                                       |                                                | Х                                              |

| 4 +5                         |               | Red                                          |                                                | X                                              |

| 5 GN                         |               | Black                                        |                                                |                                                |

|                              | 58            | white                                        |                                                |                                                |

| 7 GN                         |               | Black                                        |                                                |                                                |

| 8 GN                         |               | Black                                        |                                                | X                                              |

| 9 GN                         |               | Black                                        |                                                | X                                              |

|                              | PARE)         |                                              |                                                |                                                |

| 11 GN                        |               | Black                                        |                                                |                                                |

| 12 +5                        |               | Red                                          |                                                | X                                              |

|                              | 5 V           | Blue                                         |                                                |                                                |

| 14 •5                        |               | Brown                                        |                                                | X                                              |

|                              | 5B            | Green                                        |                                                | -                                              |

| 1.7 4.1                      | had that      |                                              |                                                |                                                |

FIGURE 2-4

DD11-P Slot Usage

This backplane is very flexible, as there are no dedicated memory slots. The seven hex slots (slots 3 through 9) are broken up into two parallel bus structures: the SPC bus (paragraph 2.2.1.1) and the MUD bus (paragraph 2.2.1.2). Note that slot 9 connectors A and B are the standard unibus output slots.

2.1.2.1 Small Peripheral Controller (SPC) Bus = Small Peripheral Controllers can be quad (four -connector) or hex (six-connector) modules. The C, D, E, and F connectors are configured with all the unibus signals and some internal interconnect signals. Table 2=2 is a pin configuration chart of an SPC slot.

New layouts for SPC modules should consult to the New Module Layout Guide.

Any module specified as an SPC module can be mounted in any of the seven DD11\*P expander slots (slots 3 through 8),

2.1.2.2 Modified Unibus Device (MUD) Bus - New battery-supported power rails were developed for MOS memory (MS11) and new core voltage rails were developed for the new core (MM11) memory. These features are included on the modified Unibus, which is incorporated in the DD11-P and DD11-C backplanes. In addition, the modified Unibus contains memory parity control signals. Devices such as MOS memory and the new core memory are connected to the modified Unibus and are designated Modified Unibus Devices (MUD).

This new bus is strictly internal to the DD11=C and DD11=P backplanes. To other system units the DD11=P and DD11=C look like standard Unibus system units.

The number of MUD modules used in the PDP11/34 and PDP11/39 systems vary; the module types are listed in Table 2-3.

The MUD bus is located on the A and B connector blocks on slots  $2^{\circ}$  to 8.

The pin configuration of the MUD bus is listed in Table 2-2.

A MUD module at present is either a double or a hex module. (Note that a double width MUD and quad width SPC can mount side by side to fill a hex slot.) The end of the Unibus must be terminated with an M9302 SACK turnaround terminator; no other terminator will work. The M9302 will be plugged into the last standard Unibus slot of the last backplane in the system. For example, in an 11/34 system with a nine slot DD11=P backplane and a four slot DD11=C backplane, the M9302 is plugged into slot 4A, 4B of the last backplane (four slot backplane, in this case). As in another example, in an 11/04 system with two nine slot DD11=P backplanes, the M9302 is plugged into slot 9A, 9B of the second DD11=P backplane.

COMMECTOR SIDE

| Table 2-2 Modified Unibus and SPC Pins Slot 2-8 CONNECTOR SLOT |               |               |                  |              |              |          |               |            |               |               |              |               |

|----------------------------------------------------------------|---------------|---------------|------------------|--------------|--------------|----------|---------------|------------|---------------|---------------|--------------|---------------|

| •                                                              | A             |               |                  | B            | C            |          | D             |            |               |               | F            | -             |

| PIN#                                                           | 1             | 2             | 1                | 2            | 1            | 2        | 1             | 2          | 1             | 2             | 1            | 2             |

| A                                                              | 1N17          | +5V           | RESV<br>BUS      | +5V          | NPG<br>(IN)  | +5V      | TP            | +5V        | GND<br>A      | +5¥           | ABG          | +5V           |

| 8                                                              | INTR          | TP            | RESV             | TP           | NPG<br>(OUT) | -15V     | TP            | -15V       | ASSYN<br>IN H | -15V          | ABG          | -15V          |

| C                                                              | Døø<br>L      | GND           | BR5              | GND          | PA           | GND      | A SEL         | GND        | A12           | GND           | SSYN         | GND           |

| D                                                              | DØ2           | DØI           | +5<br>BAT        | BR4          | LTC          | D15      | Aout          | BR.7       | AI7<br>L      | A 15          | BBSY<br>L    | FOI           |

| E                                                              | DØ4<br>L      | DØ3           | 7 W.J<br>S.Z.Y.W | PAR<br>DET   | TP           | D14<br>L | A SEL         | BRB        | MSYN          | A16           | F01<br>V2    | DØ2           |

| F                                                              | DØ6           | DØ5<br>L      | A C<br>LO        | DC<br>Lo     | TP           | DI3      | ASEL          | BR5        | AØ2           | C1            | DØ5<br>L     | DØ6<br>L      |

| H                                                              | DØ8<br>L      | DØ7<br>L      | AØI              | ADD          | DII          | D12<br>L | AIN           | BR4        | 401<br>L      | AØØ           | DØ7<br>L     | A INT<br>ENEB |

| J                                                              | DIØ           | DØ9           | AØ3              | AØ2<br>L     | AINT<br>B    | DIØ      | A SEL<br>2    | ABR        | SSYN          | CØ            | NPR          | GND           |

| K                                                              | DIZ           | D //          | AØ5              | AØ4<br>L     | TP           | DØ9<br>L | Aout          | BG7<br>So  | A14           | A13.          | DØ3<br>L     | AINT          |

| L                                                              | D14           | D13           | AØ7<br>L         | A-06         | AINT<br>ENBB | DØ8      | INIT          | BG7<br>out | AII           | TP            | DØ3          | FOI           |

| M                                                              | PA            | D15           | AØ9<br>L         | AØ8<br>L     | TP           |          | A INT<br>ENBA | . ,        | AIN           | A OUT<br>HIGH | INTR<br>L    | FOI           |

| N                                                              | PAR           | PB            | AII              | AIØ          | DC<br>Lo     | DØ4      | ANT           | BG6<br>out | AouT<br>Low   | AØ8<br>L      | FOI          | DØ4<br>L      |

| Р                                                              | PAR<br>PØ     | BBSY<br>L     | A/3              | A12          | halt<br>Req  | DØ5<br>L | TP            | BG5<br>80  | AIØ<br>L.     | AØ7           | ABR          | Fol<br>P2-    |

| R                                                              | +15<br>BAT    | SACK          | AIS              | A 14         | HALT<br>GRT  | DØ1<br>L | TP            | BG5<br>out | AØ9<br>L      | A SEL<br>4    | Fol <b>4</b> | FOIMI         |

| S                                                              | -15<br>BAT    | NPR<br>L      | A17<br>L         | A16          | PB           | DØØ      | TP            | B 64<br>So | ASEL<br>6     | A SEL         | FOIM2        | FOIP2         |

| T                                                              | GND           | BR7           | GN D             | C1<br>L      | GND          | L        | GND           | BG4<br>our | GND           | ASEL<br>2     | GND          | SACK          |

| 1 61 1                                                         | +20<br>(core) | BR6           | r<br>224n        | C Ø          | +15/48       | DØ2<br>L | TP            | ABG<br>IN  | A Ø6<br>L     | A\$4<br>L-    | A INT        | ABR           |

| V                                                              | +20<br>(GRE)  | +20<br>((ore) | msyn<br>L        | -5<br>(core) | AC<br>Lo     | DØ6<br>L | ASSYN<br>IN H | ABG<br>out | AØ5<br>L      | AØ3<br>L      | AINT         | Foi V2        |

TABLE 2-3

Modified Unibus Devices

| M93Ø1 | Bootstrap/Terminator     | Dual Module                      |

|-------|--------------------------|----------------------------------|

| M93Ø6 | MUD Terminator           | Dual Module                      |

| M9850 | Memory Parity Control    | Dual Module                      |

|       |                          |                                  |

| M7847 | MOS Memory (MS-11)       | Hex Module                       |

| G221  | Core Memory (MM11-B, -C) | Hex Module<br>with Quad Daughter |

| G222  | Core Memory (MM11=D)     | Hex Module<br>with Hex Daughter  |

#### CAUTION

Never install an M9302 SACK Turnaround Terminator or an M930 Unibus in a MUD slot. Doing so will apply MUD power rails to bus grant and ground lines on the M9302.

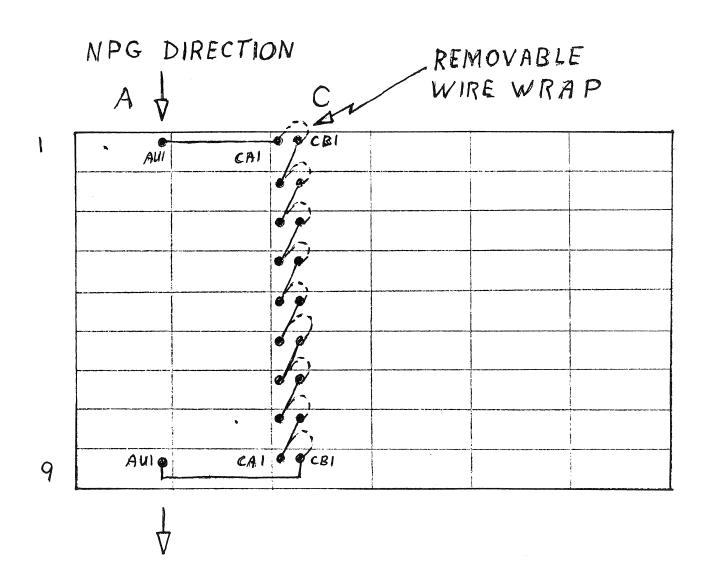

2.1.2.3 Non-Processor Grant (NPG) Line - The NPG signal is used by only those interfaces designed to do Non processor Requests. A Non-processor Request is a transfer of data from one device in a system to another device in the system without CPU intervention.

There are very few NPR devices that are also SPC devices. Therefore, the NPG line grant continuity is provided by wire-wrap jumpers on the backplane. When an NPR module is assigned to a slot, the corresponding wire-wrapped jumper on CA1 to CB1 of that slot must be removed. This jumper permits the Grant signal to be routed to the next module. The NPG signal routing through the backplane is shown in Figure 2-5.

2.1.2.4 Bus Grant (BG) Line - Bus Grant continuity cards are required in all slots that do not contain modules. These cards permit the Grant signal to be passed from module to module (see Figure 2-6).

FIGURE 2-5

NPG Signal Routing

|   |    | В                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | N- /                                                                                                           | RANT<br>RECTI | 0 N    |   |

|---|----|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|---------------|--------|---|

| / |    | BE 2                                                                 | BG4 SIG*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9      | DT2                                                                                                            |               |        |   |

|   | 'n |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q<br>Q |                                                                                                                |               |        |   |

|   |    |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ٥<br>q |                                                                                                                |               |        |   |

|   |    |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ø<br>Q |                                                                                                                |               |        |   |

|   |    |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0      |                                                                                                                |               |        |   |

| • |    |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | O      |                                                                                                                |               |        |   |

|   |    |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0      |                                                                                                                |               |        |   |

|   |    | economical Anniques Concentration on visit on the Anni Concentration | and the second of the second o | 0      | , and the second se |               |        |   |

| 9 |    | D = 5                                                                | BG4 SIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0      | D52<br>DT2                                                                                                     |               |        |   |

| 1 |    |                                                                      | and the second s | -      | 4                                                                                                              | * 1 or 4      | SIGNAL | S |

FIGURE 2=6

Bus Grant Routing

#### CHAPTER 3

#### H777 POWER SUPPLY

### 3.1 GENERAL

This chapter describes the H777 power Supply, which is housed in the BA11-L Mounting Box. This supply provides the operating voltages for the PDP-11/34 and PDP-11/39 Processing Systems. A battery backup supply is available for systems employing MOS memory. The backup is designated H775 and provides backup power in the event of a power supply failure.

### 3.2 PHYSICAL DESCRIPTION

The H777 Power Supply mounts on the righthand side of the BA11-L mounting box (see Figure 3-1), and the DD11-P backPlane is mounted on the left hand side of the box. power to the backplane is provided by a connector at the rear of the power supply; power to the operator's console is provided by a connector at the front of the power supply (see Figure 3-1).

The power supply contains the following five assemblies (see Figure 3-2):

- , AC control assembly

- +5V main regulator

- MOS regulator + or =15V, +5V

- . Core regulator +20V, =5V

- . Fan

### 3.2.1 AC Control Assembly

The AC Control Assembly contains all of the hardware (i.e., line cord, relay, filter, circuit breaker, and main transformer) associated with the line voltage control. The H777 system is limited by its main transformer to 240 watts of regulated DC output. This limit should not be exceeded in steady state operation. (See Table 3-1 for complete characterization of the limits of operation). Internal thermal protection will shut-down the individual regulator assemblies before dangerous conditions are reached. This shutdown is a power-fail sequence and is provided by a thermal switch on the main

regulator in order to preserve MOS memory data,

The H777 provides a controlled turn-on by limiting the inrush current, with no controlled turn-on, high-surge currents could trip circuit breakers causing the shut-down of rack power. This feature is important in systems containing multiple mounting boxes.

To Be Supplied

FIGURE 3=1

BA11-L Mounting Box Showing Connectors and Cables

### 3.2.2 +5V Main Regulator

The +5 Main regulator provides 25 Amps of regulated DC power and acts as a source of raw DC for other regulators. It also contains power up/down sequencing circuitry, control input (ON/OFF/STAND BY), and Unibus AC Lo, DC Lo signals.

### 3.2.3 MOS Converter

The Mos Converter provides + or =15 volts for use within the H777 and as an output to the DD11=P for MOS memory and various module options. Both switched and unswitched (battery backup) sources are provided. This assembly also supplies +5 volts (+5B) to the MOS Memories for battery-supported refresh operation. The H777 system clock is contained on the MOS converter assembly.

### 3.2.4 Core Memory Regulator (Optional)

The last assembly (optional regulator) is a removable unit capable of driving core memories at +20 and =5 volts from the raw DC source contained on the main regulator.

### 3.3 BLOCK DIAGRAM DESCRIPTION

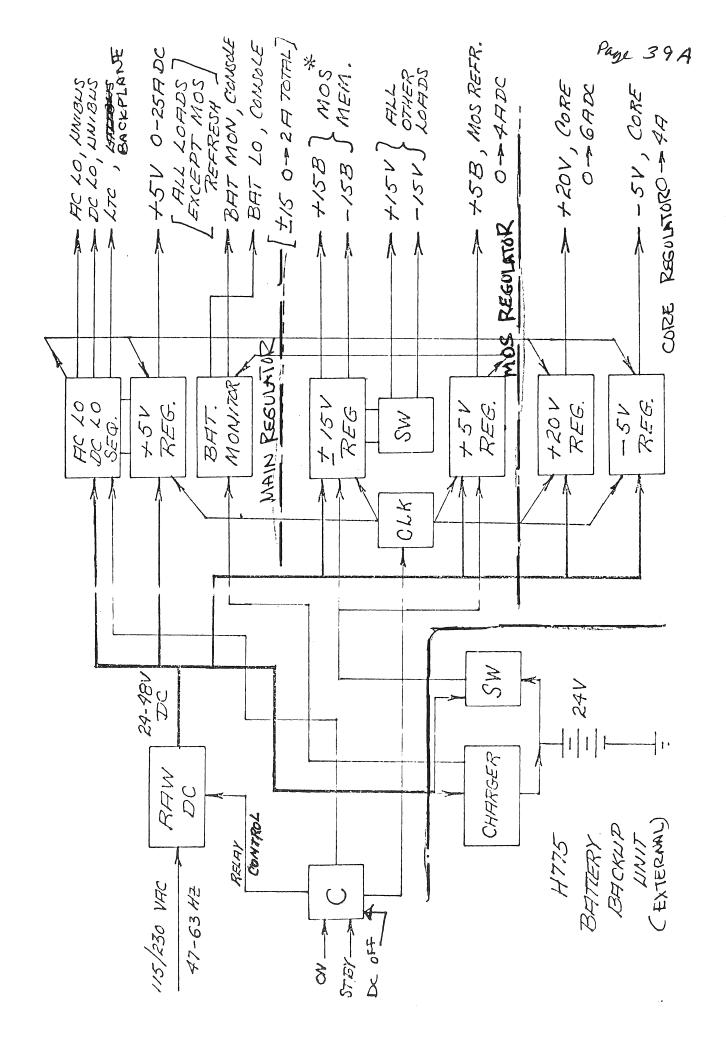

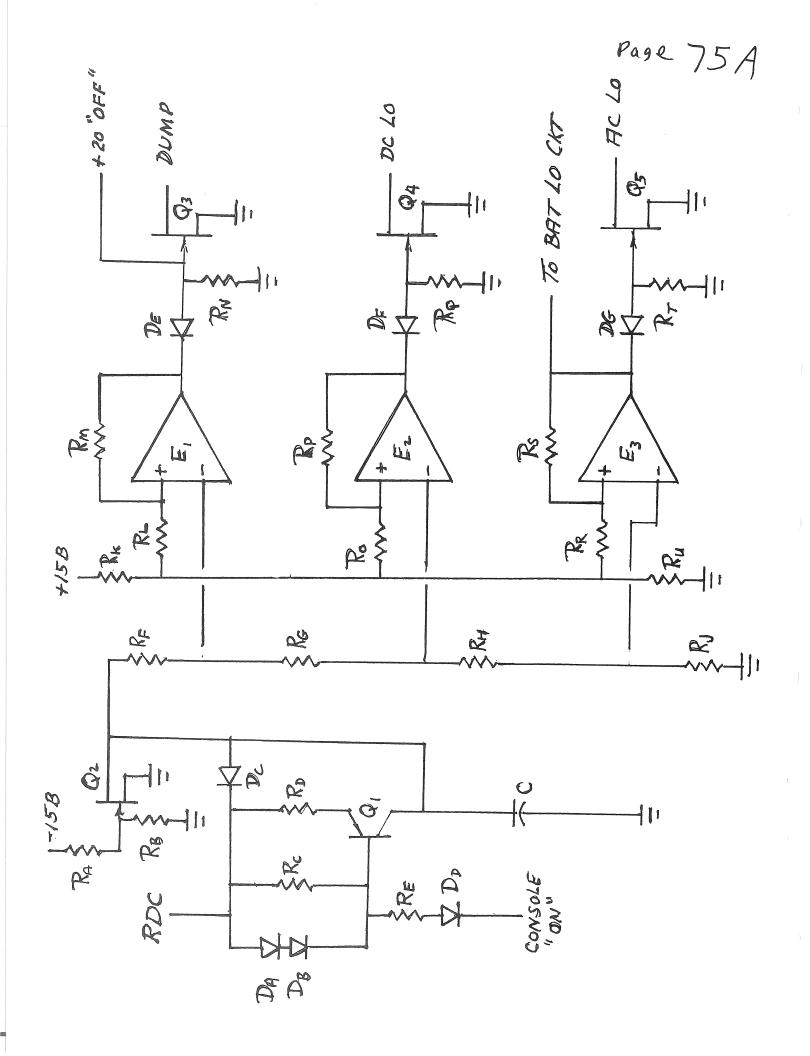

Figure 3-3 is a block diagram of the H777 power supply. The figure shows the four major assemblies of the supply plus the optional H775 battery back-up unit. Each assembly is divided into functional blocks for the following description.

### 3.3.1 AC Control Assembly

The transformer, AC Control interface, and main rectifier/filter are shown in the upper left corner of Figure 3m3, and are labelled RAW DC (RDC), RDC flows to all of the regulator blocks which are contained in:

- . the Main Regulator Assembly (upper right)

- the MOS Regulator (center right)

- the +20V Core Regulator (lower right)

Figure 3-3 also shows the type of output obtained from each power or signal producing block, along with its general destination.

The clock is a square-wave oscillator used to synchronize all of the Switching regulators within the H777 and to provide the carrier upon which each pulse width Modulator (PWM) operates. The modulated carrier is fed to each power switch element at a duty cycle that is appropriate to maintain constant and proper voltage. The modulation of the carrier within each regulator is described in subsequent paragraphs.

To Be Supplied

FIGURE 3-2

Major H777 Power supply Components

See Page 39A

FIGURE 3-3

Block Diagram of H777 Power Supply

## 3.3.3 Switch for +15V Isolation

Note the SW (switch) box associated with the + or =15v regulator. This switch isolates the + or =15v (used for peripherals) from the + or =15B (used for MOS memory). If the system should go on battery back=up, isolation of the + or =15v from the + or =15B will maximize the battery back-up time for MOS memory which represents the critical volatile storage load. The peripherals (non-critical load) will, consequently, not have battery back-up in this case.

Another feature of the switched + or =15 output is that module swapping of non-memory modules may be accomplished in STBY mode without losing the contents of memory.

# 3.3.4 Control for Console Interface

The control box (designated C) represents the console interface where the power switch ON and STBY (Stand by) functions are applied to the H777. In the "STBY" state, the + or =15 and the +5B regulators are strobed to provide regulated voltages for MOS memory. The main +5 and optional +20y and =5V regulators are not strobed. In the "DC OFF" state, the clock is inhibited so that no carrier is applied to any of the regulators. In the "DC OFF" state, AC power is still applied.

## 3.4 DETAILED CIRCUIT DESCRIPTION

The following paragraphs provide a detailed description of the circuits comprising the H777 power supply.

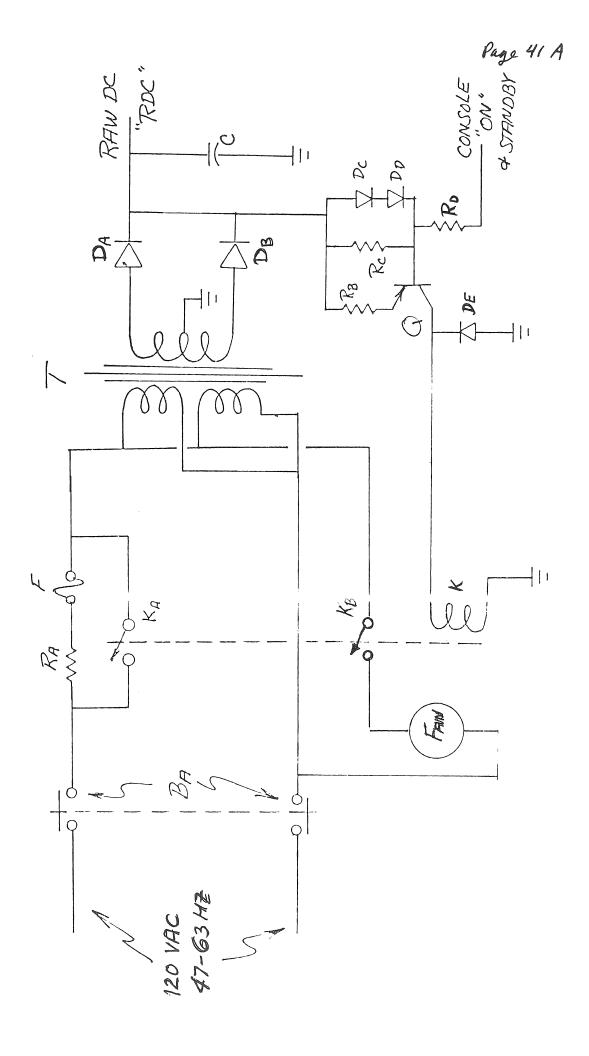

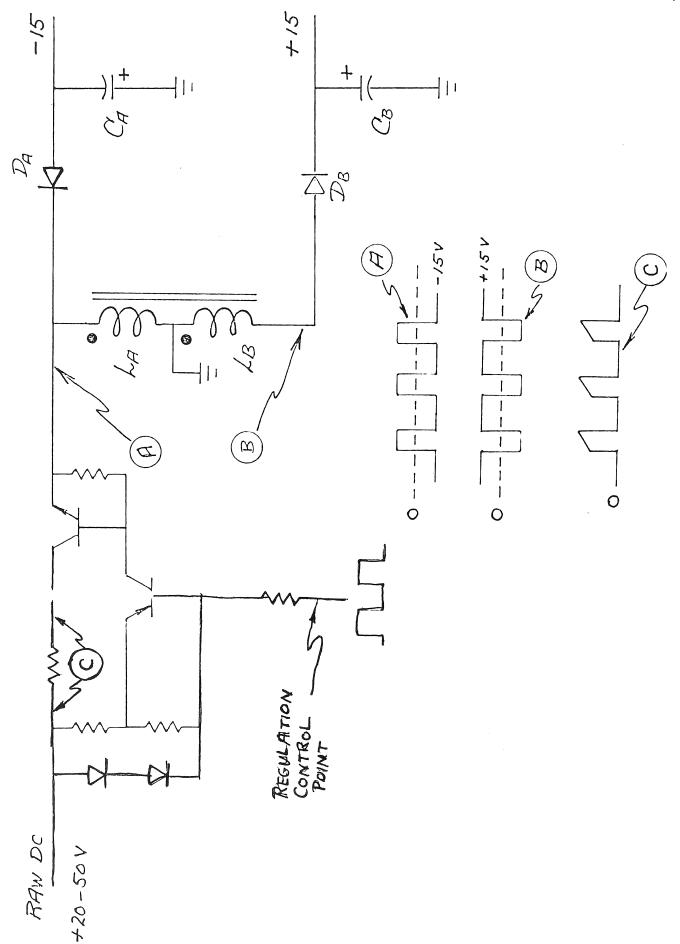

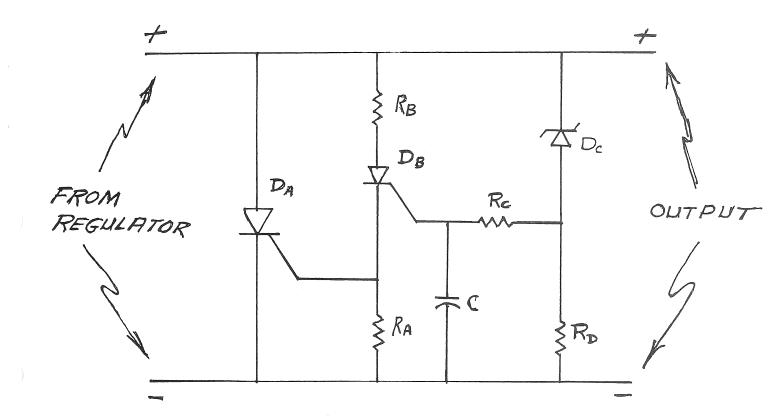

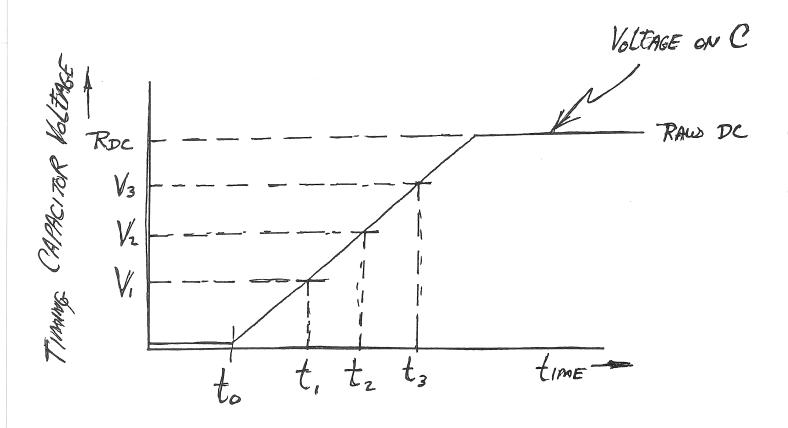

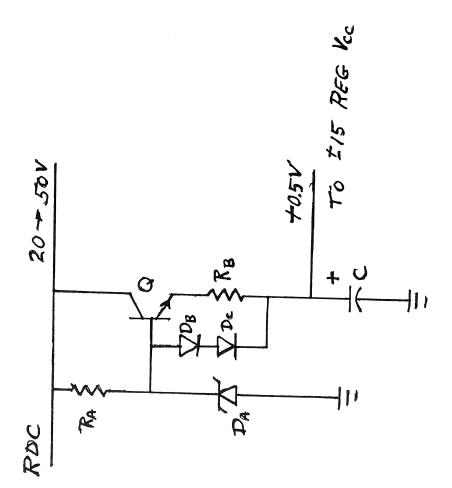

# 3.4.1 Raw DC Circuitry (Refer to Figure 3+4)

The Raw DC section produces a low DC operating voltage (normally 33 + or +9 yolts for each of the regulators. This single positive source supplies power to all of the regulators (so that battery support could be applied from one single battery). The RDC section also provides ride-through (power protection against the loss transients) for the power supply by virtue of the energy stored in capacitor "C".

### NOTE

All components to the right of "T" are located on the Main Regulator Assembly. The remaining components (except for fan) are located on the AC control assembly.

See Page 41A

3,4,1,1 Circuit Breaker BA - The Circuit Breaker (BA) provides overcurrent protection in the event of a failure within the H777 and creates a convenient line-disconnect for servicing.

3.4.1.2 Inrush Current Limiting - Resistor Ra limits inrush current on power line closure and is bypassed during operation by Relay Ka. The fuse (F) protects Ra in the event of Ka failing to close.

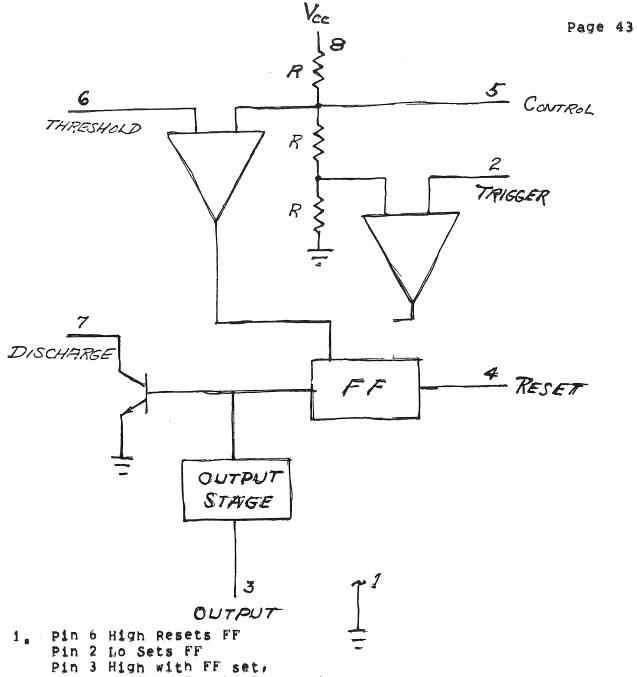

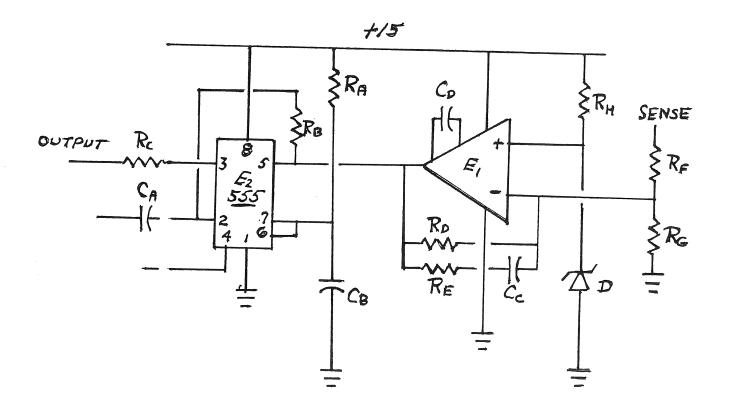

3.4.2 The 555 Timer (Refer to Figure 3=5)

The 555 Timer is located within the Clock logic. Because the 555 IC Timer performs various functions within the H777, a brief description of its operation is presented. The device, as used here, is an 8-pin DIP (dual inline package). Several of its characteristics are listed along with an internal block diagram in Figure 3-5.

The device contains a resistive divider chain to set an input to each of two comparators at 1/3 Vcc and 2/3 Vcc. The comparator outputs can set and reset a flip-flop, whose output controls a bilateral output driver, which is a device that can source or sink current.

The flip-flop can be manually reset by reducing the reset pin level at pin 4 to 0.4V. The output of the 555 inverts the state of the FF, as follows:

- \* FF set = Output High (source current)

- . FF Reset = Output Low (sink current)

- Transistor "ON" with FF reset

- Output can source or sink current (100 ma maximum) 2.

- Reset pin overrides trigger; holds output Low for reset low. 3.

- All "R" are equal value, 4

- Output will remain High as long as Trigger is Lo (Pin 4 5. High).

- V(cc) = 18V maximum6.

FIGURE 3-5

555 Timer

The so-called discharge transistor is "ON" when the output is low (FF Reset). The trigger comparator sets the FF when V(pin 2) < 1/3 Vcc(or < 1/2 V(pin 5).

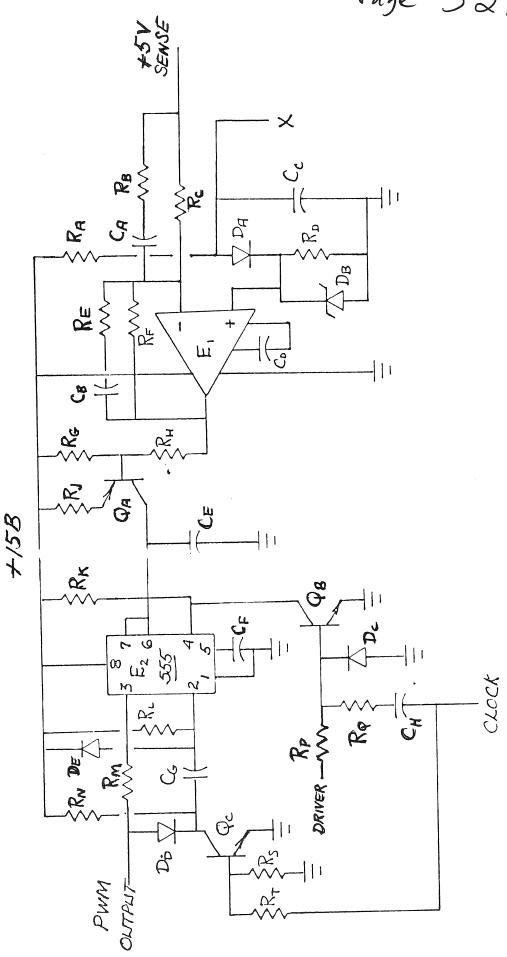

The Threshold Comparator resets the FF when V (pin6) > 2/3 VCC (or > V (pin5). Within the H777, the device is used as a relaxation (free-running) oscillator, as a one-shot, and as a pulse-width modulator (PWM).

The first application of this device is in generation of the H777 carrier or clock signal.

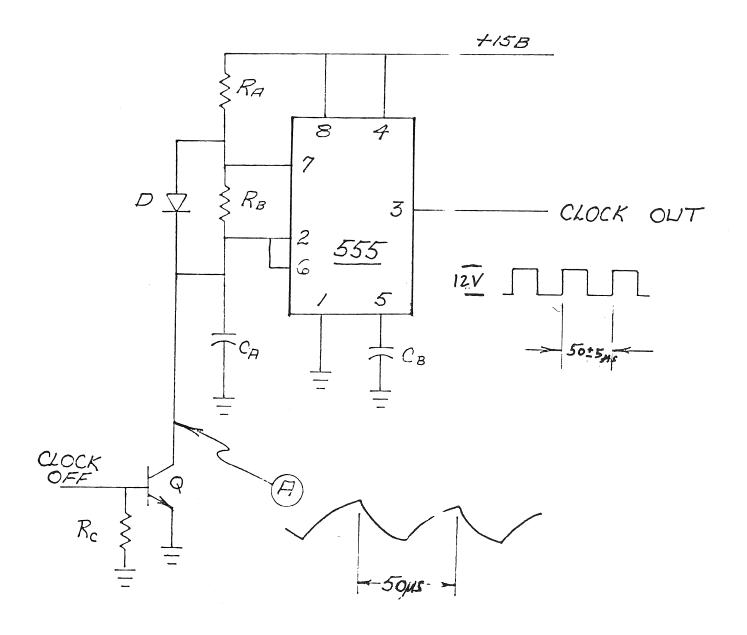

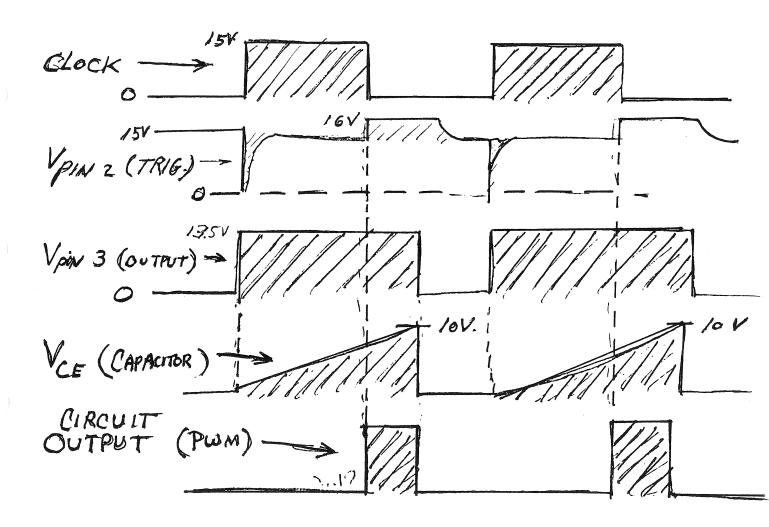

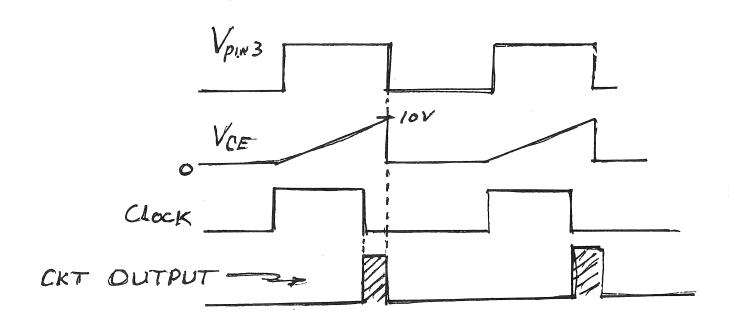

3.4.3 Clock Circuit (Refer to Figure 3=6)

The H777 Master Clock generates a 20 KHZ (+ or =2 KHZ) square wave carrier with an amplitude of 12 volts.

The circuit that generates this carrier centers around a 555 Timer as a Free Running Relaxation Oscillator.

In operation, the Timing Capacitor (Ca) is charged through Ra and D toward 15 volts. Upon reaching 10 volts (2/3 Vcc) the 555 "turns=over" and discharges Ca via Rb and its internal "discharge" transistor. That transition coincides with a negative=going transition at the output of Pin 3. When the voltage on Ca (Pin 2 & 6) falls to 5 volts (1/3 Vcc), the 555 "turns=over" again, opening the discharge transistor and allowing Ca to charge up again. That turn=over coincides with an output transition from Low to High. The cycle continues with Ca oscillating between 1/3 Vcc and 2/3 Vcc. Because the "turn=over" points are proportional to Vcc in fixed ratio, the oscillator frequency (or period) will be independent of Vcc.

The output of this clock can source and sink up to about 100 ma and still maintain an acceptable waveform.

Capacitive relaxation oscillator used to generate a 20 KHZ master clock—in the H777 MOs converter.

This clock synchronizes all of the switching regulators of the H777.

FIGURE 3=6

H777 Clock Circuit

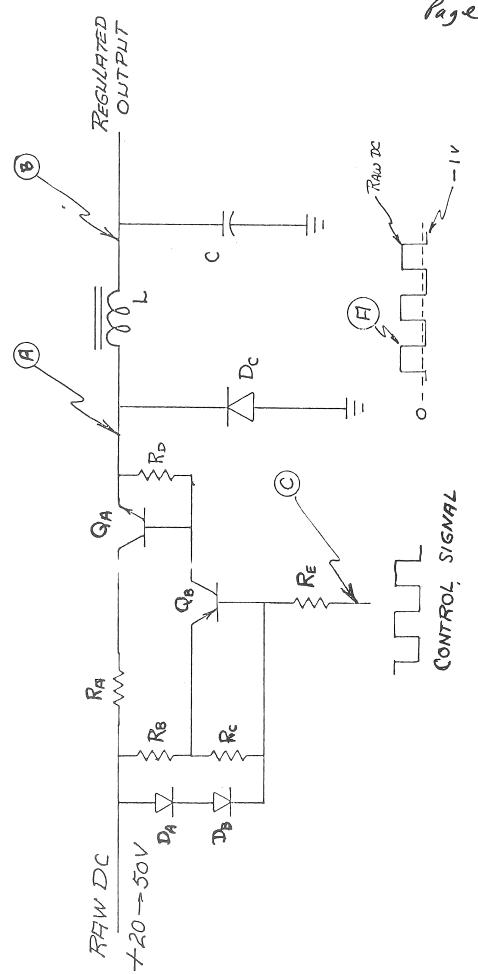

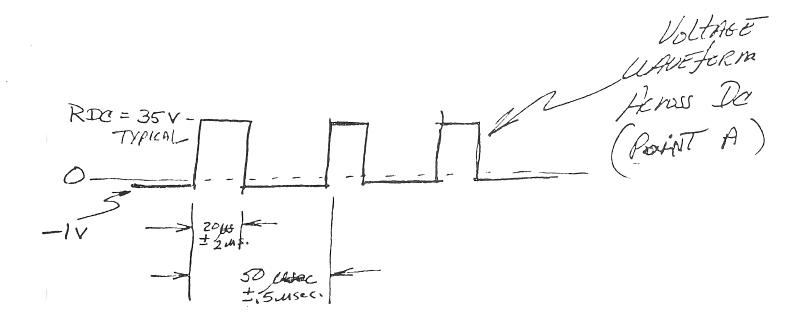

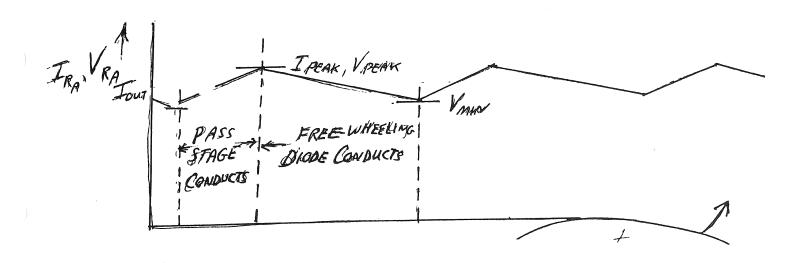

3.4.4 Series-Connected Power Switching Stage (typical +5B, +20) (Refer to Figure 3=7)

This power handling stage is identical to those used in the +5B and +20 regulators and, with a different filter section, is similar to the + or -15 and -5V regulators of the H777. The main +5V switch is described in paragraph 3.4.8.