LSI-11 WCS user's guide

EK-KUV11-TM-001

# Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

|         | VMS              | IAS     |

#### PREFACE

This manual provides the user with all the information required to write, assemble, debug and execute microprograms on the LSI-ll utilizing the Writable Control Store (WCS) option (KUVll-AA) in conjunction with microprogramming support software.

Chapter 1 provides an introduction to microprogramming the LSI-11. It discusses machine-micromachine relationships and supplies an introductory glossary of important definitions.

Chapter 2 is divided into two parts: LSI-ll machine architecture and LSI-ll machine operation. The first part is an LSI-ll family hardware overview and is included for completeness. The new LSI-ll user can gain a basic system understanding from this overview, but should refer to the Microcomputer Handbook for a more complete description. The second part is recommended reading for all LSI-ll microprogrammers because it introduces control flow diagrams which explain the transfer of control between the LSI-ll machine and micromachine.

Chapter 3 follows the same organization as Chapter 2, but concentrates on the LSI-11 micromachine. The first part covers the LSI-11 micro processor as implemented in the Control and Data chips and details their internal organization. The second part describes the micromachine operation and its relationship to higher level machine operation.

Chapter 4 presents the LSI-ll microinstruction set, organized on a functional basis. The chapter also contains a detailed explanation of each microinstruction along with an example containing assembly mnemonics and assembled octal equivalents.

Chapter 5 concentrates on the Data Access group of microinstructions and provides details sufficient to accurately determine the execution times for microprogrammed I/O transactions.

Chapter 6 presents the LSI-ll Writable Control Store hardware and its relationship to the LSI-ll micromachine. The discussion includes a description of the data buffer and control/status registers.

Chapter 7 details the microprogramming support software consisting of (1) the microassembler (MICRO), (2) the WCS loader dumper (WCSLOD) and (3) the WCS Microprogram Octal Debug Tool (MODT).

Chapter 8 discusses techniques which may be used to write microprograms.

Chapter 9 contains information on the WCS module installation and checkout.

Chapter 10 contains information on WCS maintenance.

# TABLE OF CONTENTS

| Chapter 1 | INTRODUCTION TO LSI-II, PDP-II/03 USER MICROPROGRAMMING |      |

|-----------|---------------------------------------------------------|------|

| 1.1       | GENERAL                                                 | 1-1  |

| 1.1.1     | Introductory Microprogramming Glossary                  | 1-1  |

| 1.1.2     | LSI-11 Microprogramming Features                        | 1-4  |

| 1.1.3     | Basic LSI-11 Machine-Micromachine Structure             | 1-5  |

| 1.2       | THE BENEFITS OF USER MICROPROGRAMMING                   | 1-7  |

| 1.2.1     | Arithmetic Calculations                                 | 17   |

| 1.2.2     | Critically-Timed Input/Output and Control Operations    | 1-7  |

| 1.2.3     | Data Manipulation and Relocation                        | 1-8  |

| 1.3       | SYSTEM IMPLICATIONS OF USER MICROPROGRAMMING            | 1-8  |

| 1.3.1     | Control Flow Integrity                                  | 1-8  |

| 1.3.2     | Interrupt Response Latency                              | 1-8  |

| 1.3.3     | Register Content Security                               | 1-9  |

| 1.3.4     | Processor Status Word Updating                          | 1-9  |

| 1.3.5     | Dedicated Control Store Locations                       | 1-9  |

| 1.3.6     | Machine Instruction Support                             | 1-10 |

| 1.4       | MICROPROGRAM CHARACTERISTICS                            | 1-10 |

| 1.4.1     | Vertical and Horizontal Microinstructions               | 1-10 |

| 1.4.2     | Logic Control Features                                  | 1-10 |

| 1.5       | THE MICROPROGRAMMING ENVIRONMENT                        | 1-11 |

| 1.5.1     | Creating the Source File                                | 1-11 |

| 1.5.2     | The Microassembler                                      | 1-11 |

| 1.5.3     | Writable Control Store Loader                           | 1-11 |

| 1.5.4     | Micro Octal Debugging Tool (MODT)                       | 1-11 |

| 1.5.5     | Microprogram Trace Facility                             | 1-12 |

| 1.6       | REFERENCES                                              | 1-12 |

# Chapter 2 THE LSI-11 MACHINE STRUCTURE

| 2.1     | GENERAL                           | 2-1  |

|---------|-----------------------------------|------|

| 2.2     | MACHINE ARCHITECTURE              | 2-1  |

| 2.2.1   | System Bus                        | 2-1  |

| 2.2.1.1 | System Bus Address Space          | 2-3  |

| 2.2.1.2 | System Bus Data Transfer          | 2-3  |

| 2.2.1.3 | System Bus Control Signals        | 2-5  |

| 2.2.2   | Memory                            | 2-6  |

| 2.2.2.1 | Semiconductor Memory              | 2-7  |

| 2.2.2.2 | Dynamic Memory Refreshing         | 2-7  |

| 2.2.2.3 | Magnetic Memory                   | 2-8  |

| 2.2.3   | Input/Output Devices              | 2-8  |

| 2.2.3.1 | Device Address Format             | 2-8  |

| 2.2.3.2 | Enabling Device Interrupts        | 2-9  |

| 2.2.3.3 | DMA Transfer Restrictions         | 2-9  |

| 2.2.4   | The LSI-11 Processor              | 2-9  |

| 2.2.4.1 | Arithmetic Logic Unit             | 2-9  |

| 2.2.4.2 | General Purpose Registers         | 2-9  |

| 2.2.4.3 | Processor Control                 | 2-11 |

| 2.2.5   | The LSI-11 Writable Control Store | 2-17 |

| 2.2.5.1 | LSI-ll System Bus Connection      | 2-20 |

| 2.2.5.2 | Microinstruction Bus Connection   | 2-20 |

| 2.3     | MACHINE OPERATION                 | 2-20 |

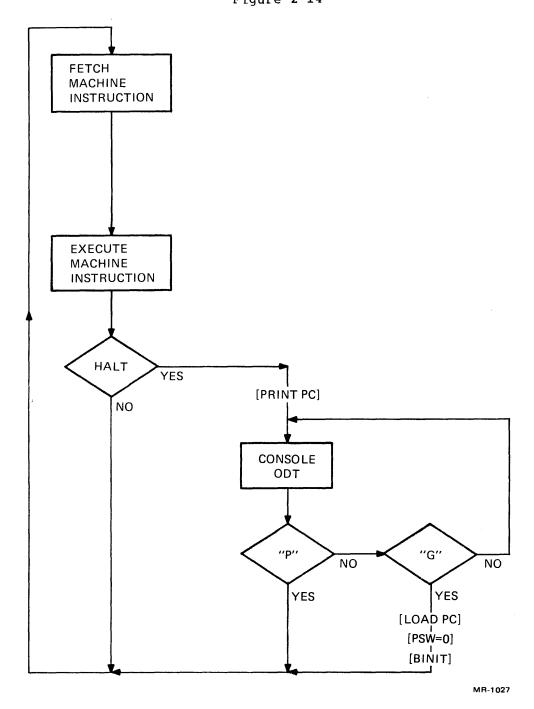

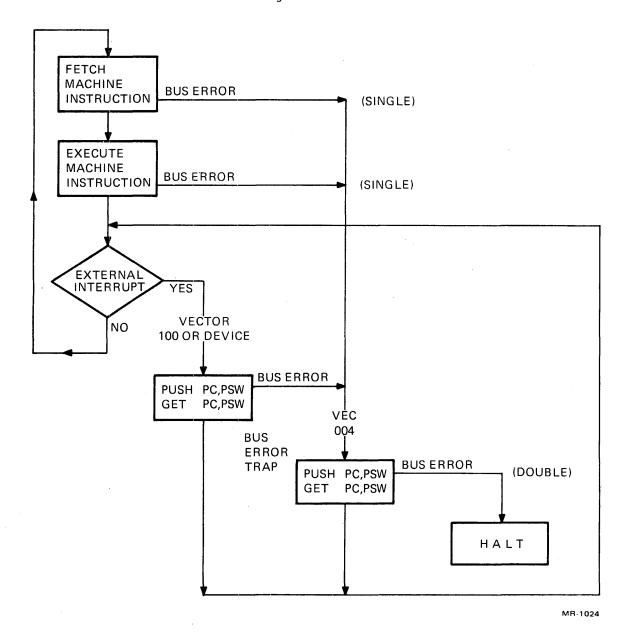

| 2.3.1   | Basic Machine Cycle               | 2-20 |

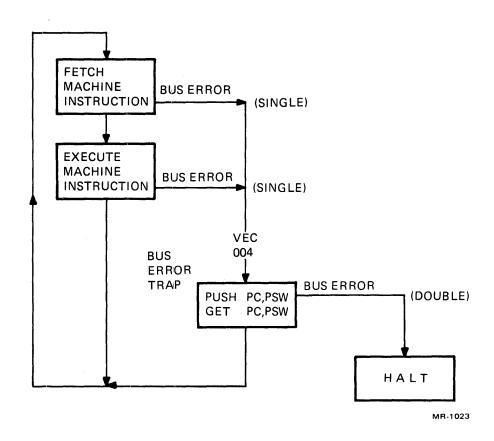

| 2.3.1.1 | Bus Error Trap                    | 2-20 |

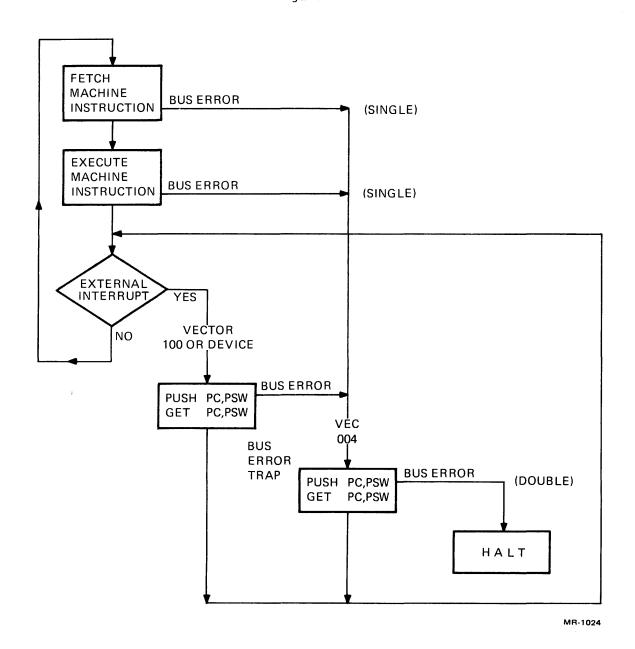

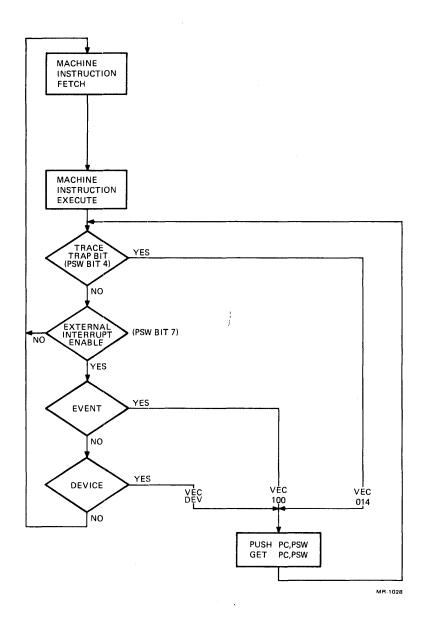

| 2.3.1.2 | External Interrupt                | 2-22 |

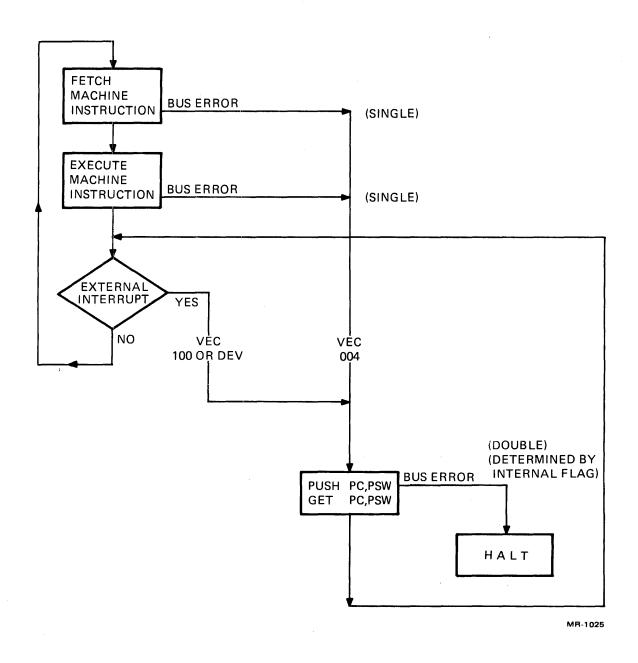

| 2.3.1.3 | Combined Trap and Interrupt Cycle | 2-22 |

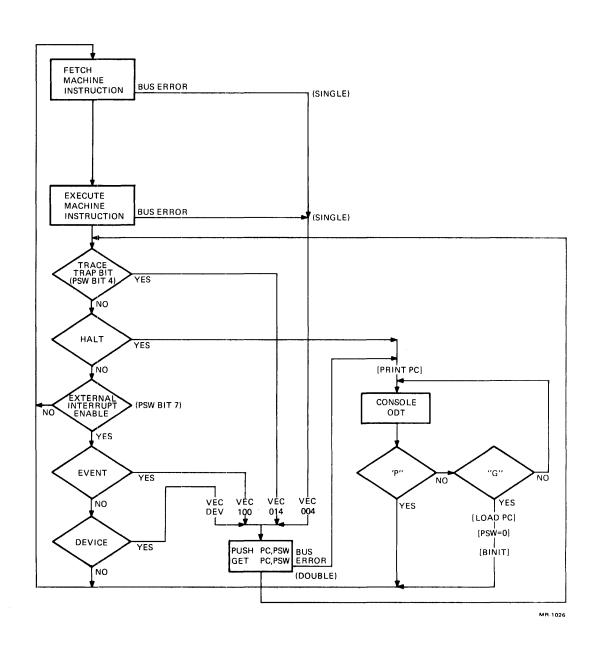

|   | 2.3.2     | Complete Machine-Level Operating Cycle            | 2-26 |

|---|-----------|---------------------------------------------------|------|

|   | 2.3.2.1   | Run/Halt Portion                                  | 2-26 |

|   | 2.3.2.2   | Trap/Interrupt Portion                            | 2-26 |

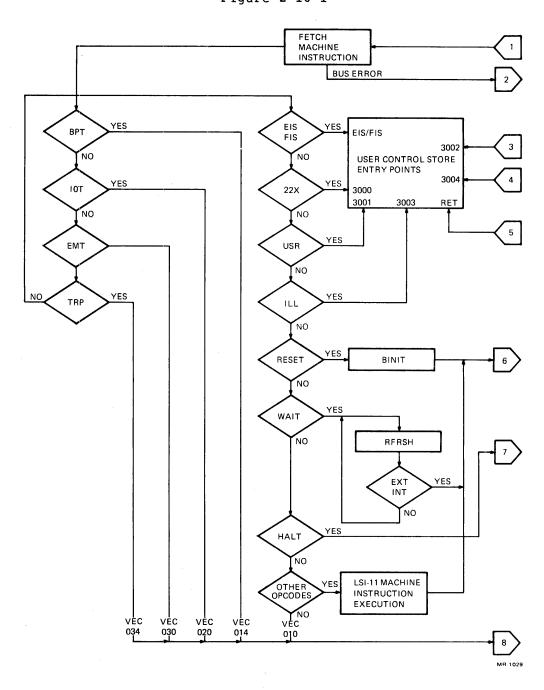

|   | 2.3.3     | Complete Machine-Micromachine Operating Cycle     | 2-30 |

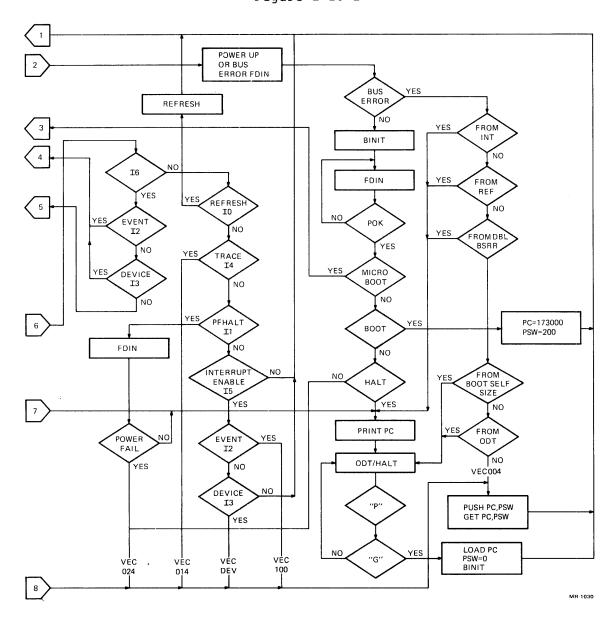

|   | 2.3.3.1   | Bus Error Processing                              | 2-30 |

|   | 2.3.3.2   | Trap/Interrupt Processing                         | 2-30 |

|   | 2.3.3.3   | Power-Up Processing                               | 2-35 |

|   | Chapter 3 | THE LSI-11 MICROMACHINE STRUCTURE                 | 3-1  |

|   | 3.1       | GENERAL                                           | 3-1  |

|   | 3.2       | THE MICROPROCESSOR                                | 3-1  |

|   | 3.3       | MICROPROCESSOR PARTITIONING                       | 3-3  |

|   | 3.3.1     | Microprocessor Data Chip                          | 3-3  |

|   | 3.3.1.1   | Microinstruction Register                         | 3-9  |

|   | 3.3.1.2   | Register File and Indirect Addressing             | 3-13 |

|   | 3.3.1.3   | Arithmetic Logic Unit                             | 3-18 |

|   | 3.3.1.4   | Status Bits and Condition Code Flags              | 3-18 |

| • | 3.3.2     | Microprocessor Control Chip                       | 3-21 |

|   | 3.3.2.1   | Microinstruction Register                         | 3-23 |

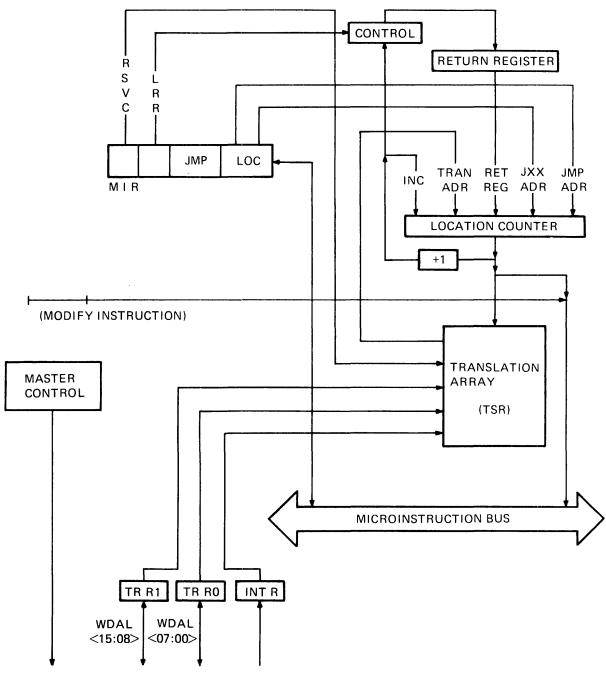

|   | 3.3.2.2   | Microinstruction Address Generation               | 3-23 |

|   | 3.3.2,3   | Control Signals                                   | 3-24 |

|   | 3.4       | MICROMACHINE OPERATION                            | 3-27 |

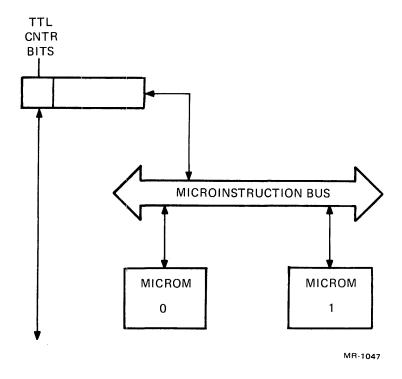

|   | 3.4.1     | Microinstruction Bus Data Transfer                | 3-27 |

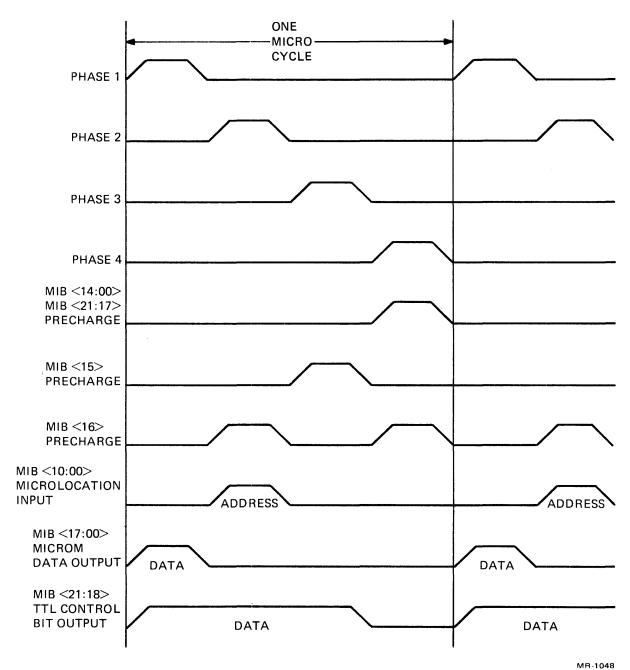

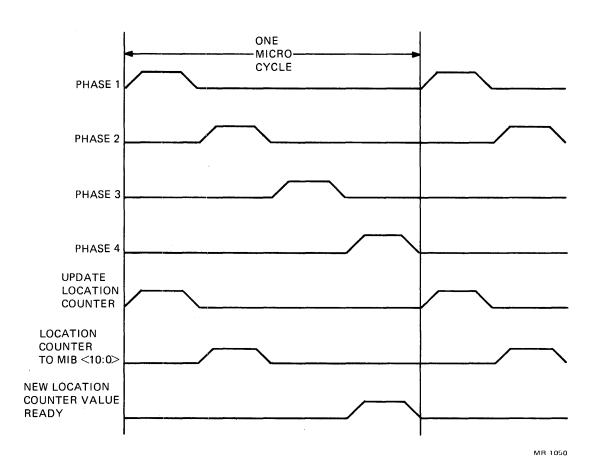

|   | 3.4.1.1   | Control Store (MICROM) Microinstruction Bus Cycle | 3-27 |

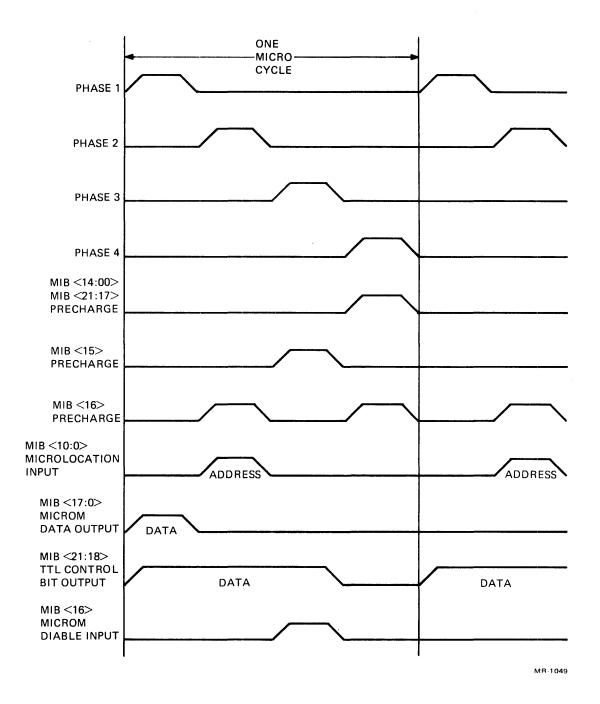

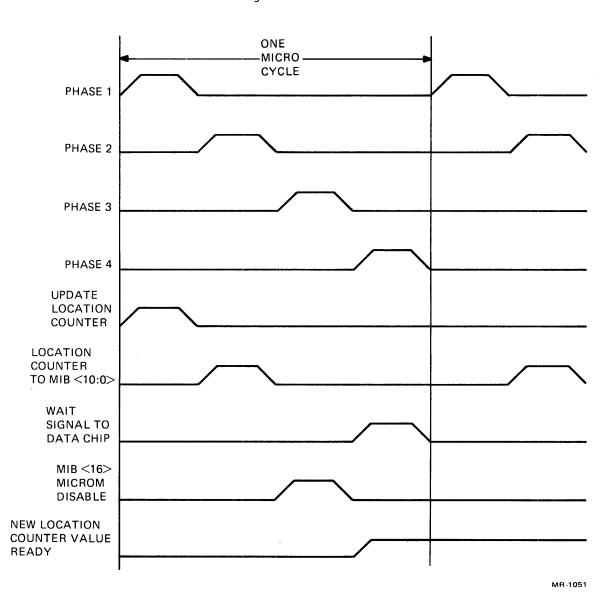

|   | 3.4.1.2   | Control Chip Microinstruction Bus Cycle           | 3-29 |

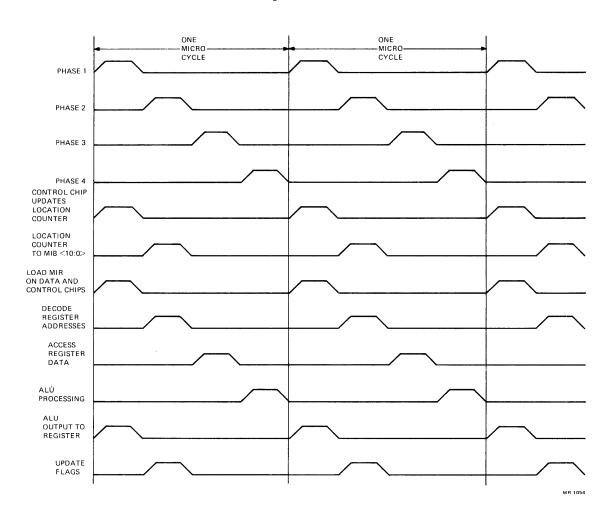

|   | 3.4.1.3   | Data Chip Microinstruction Bus Cycle              | 3-33 |

|   | 3.4.1.4   | Complete Micromachine Cycle                       | 3-33 |

|   |           |                                                   |      |

| 3.5       | MICROPROGRAMMING THE BASIC LSI-11 MACHINE CYCLE | 3-37 |

|-----------|-------------------------------------------------|------|

| 3.5.1     | Fetch-Execute Machine Cycle Microprogramming    | 3-37 |

| 3.5.2     | Fetch-Execute-Trap & Interrupt Machine Cycle    |      |

|           | Microprogramming                                | 3-37 |

| Chapter 4 | THE LSI-11 MICROINSTRUCTION SET                 | 4-1  |

| 4.1       | GENERAL                                         | 4-1  |

| 4.2       | VERTICAL MICROINSTRUCTIONS                      | 4-1  |

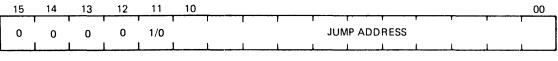

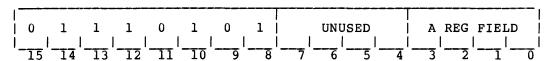

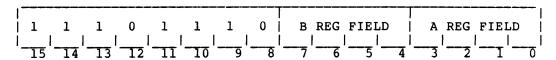

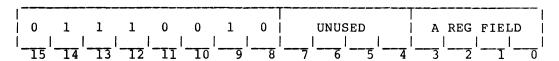

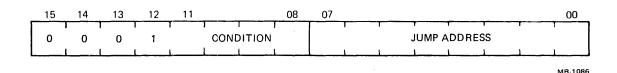

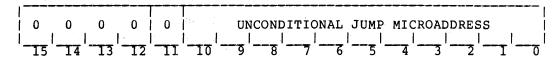

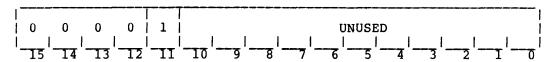

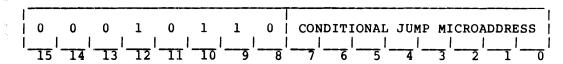

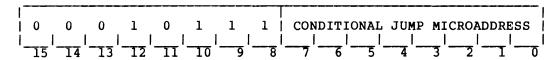

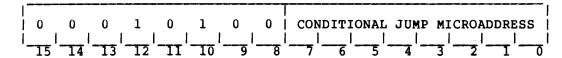

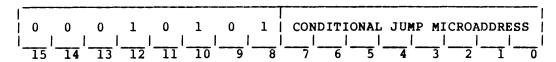

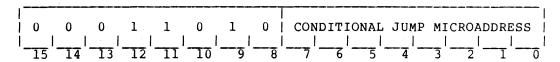

| 4.2.1     | Jump Microinstruction Format                    | 4-3  |

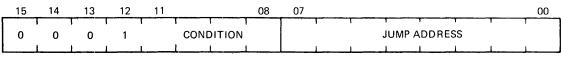

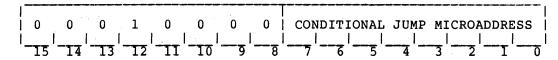

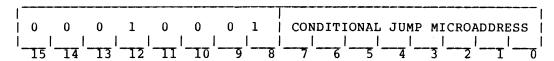

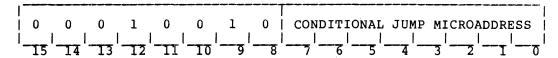

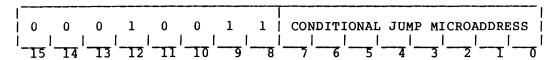

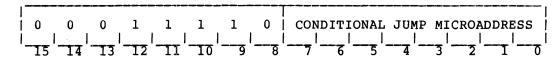

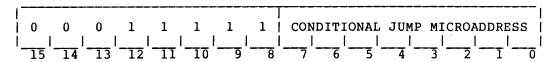

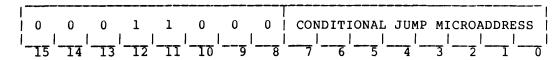

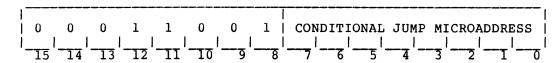

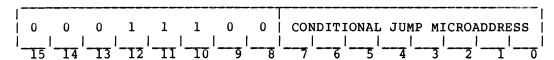

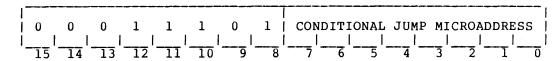

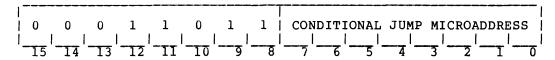

| 4.2.2     | Conditional Jump Microinstruction Format        | 4-3  |

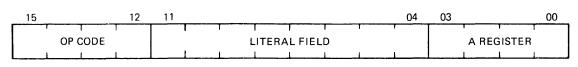

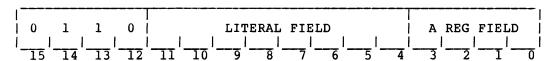

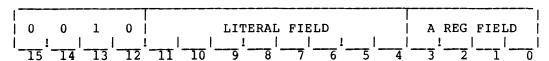

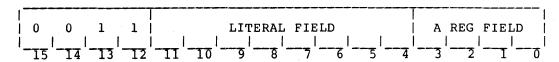

| 4.2.3     | Literal Microinstruction Format                 | 4-6  |

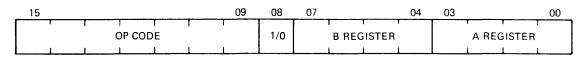

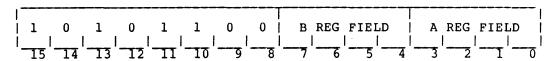

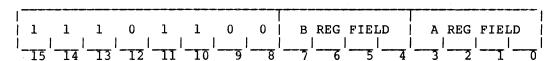

| 4.2.4     | Register Microinstruction Format                | 4-6  |

| 4.2.4.1   | Byte and Word Microinstructions                 | 4-6  |

| 4.2.4.2   | Word Operand Formation                          | 4-9  |

| 4.3       | MICROINSTRUCTION SET FUNCTIONAL ORGANIZATION    | 4-15 |

| 4.3.1     | Data Manipulation Microinstructions             | 4-15 |

| 4.3.1.1   | Move Microinstructions                          | 4-15 |

| 4.3.1.2   | Increment/Decrement Microinstructions           | 4-25 |

| 4.3.1.3   | Logical Microinstructions                       | 4-34 |

| 4.3.1.4   | Shift Microinstructions                         | 4-48 |

| 4.3.1.5   | Arithmetic Microinstructions                    | 4-57 |

| 4.3.2     | Data Access Microinstructions                   | 4-71 |

| 4.3.2.1   | Read Microinstructions                          | 4-71 |

| 4.3.2.2   | Input Microinstructions                         | 4-76 |

| 4.3.2.3   | Write Microinstructions                         | 4-81 |

| 4.3.2.4   | Output Microinstructions                        | 4-86 |

| 4.3.3     | Microprogram Control Microinstructions          | 4-90 |

| 4.3.3.1   | Jump and Return Microinstructions               | 4-90  |

|-----------|-------------------------------------------------|-------|

| 4.3.3.2   | Compare and Test Microinstructions              | 4-110 |

| 4.3.3.3   | Miscellaneous Control Microinstructions         | 4-117 |

| Chapter 5 | MICROPROGRAMMING LSI-11 SYSTEM BUS TRANSACTIONS | 5-1   |

| 5.1       | GENERAL                                         | 5-1   |

| 5.2       | LSI-11 SYSTEM BUS INTERFACE LOGIC OVERVIEW      | 5-1   |

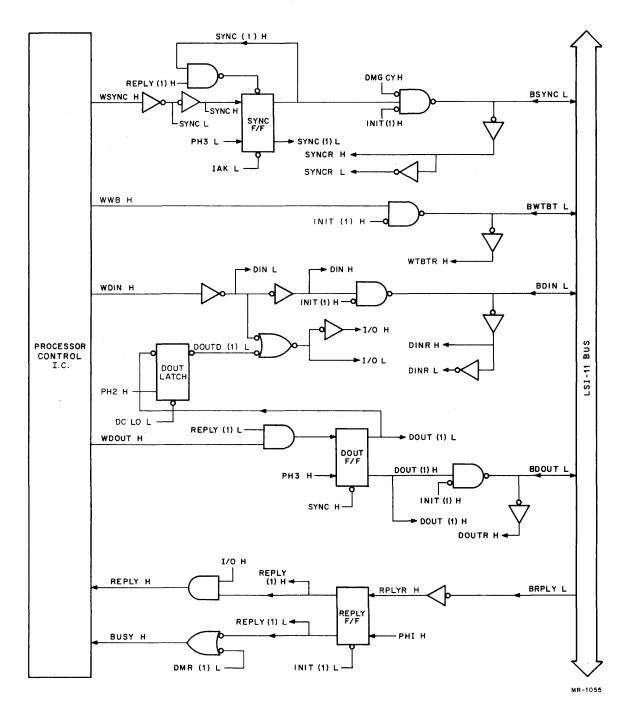

| 5.2.1     | WSYNC H - BSYNC L                               | 5-4   |

| 5.2.2     | WWB H - BWTBT L                                 | 5-4   |

| 5.2.3     | WDIN H - BDIN L                                 | 5-4   |

| 5.2.4     | WDOUT H - BDOUT L                               | 5-4   |

| 5.2.5     | BRPLY L - REPLY H                               | 5-5   |

| 5.2.6     | BRPLY L - BUSY H                                | 5-5   |

| 5.2.7     | WIAK H - BIACK H                                | 5-6   |

| 5.3       | THE DATA-INPUT (DATI) OPERATION                 | 5-6   |

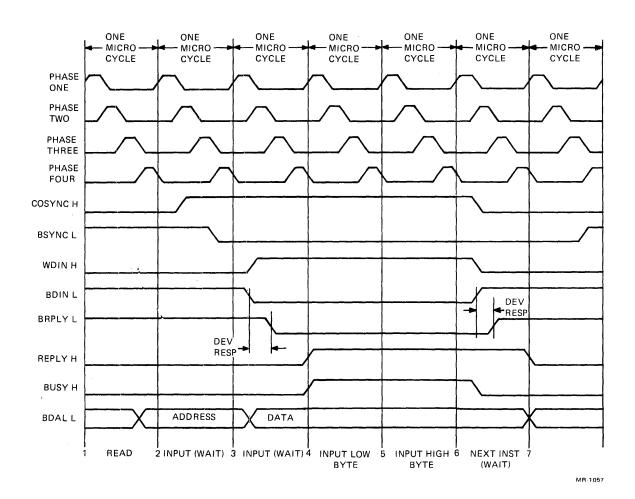

| 5.3.1     | DATI Operation, Minimum Execution Time          | 5-6   |

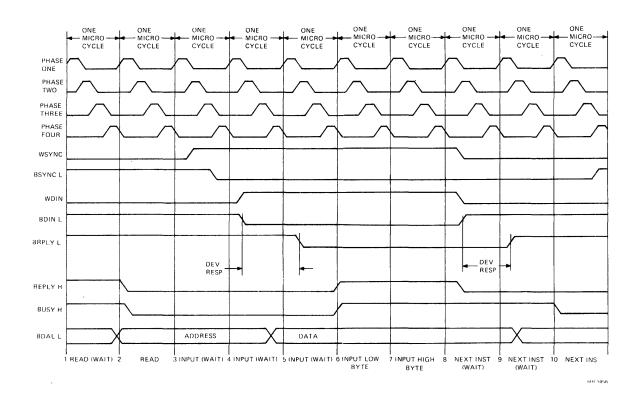

| 5.3.2     | DATI Operation, Delayed Execution Time          | 5-9   |

| 5.3.3     | DATI Microprogramming Summary                   | 5-12  |

| 5.4       | THE DATA-OUTPUT (DATO) OPERATION                | 5-13  |

| 5.4.1     | DATO Operation, Minimum Execution Time          | 5-13  |

| 5.4.2     | DATO Operation, Delayed Execution Time          | 5-15  |

| 5.4.3     | DATO Microprogramming Summary                   | 5-19  |

| 5.5       | THE DATA-INPUT-OUTPUT (DATIO) OPERATION         | 5-20  |

| 5.5.1     | DATIO Operation, Minimum Execution Time         | 5-20  |

| 5.5.2     | DATIO Microprogramming Summary                  | 5-24  |

| 5.6       | THE INTERRUPT OPERATION                           | 5-25 |

|-----------|---------------------------------------------------|------|

| 5.6.1     | Interrupt Operation Microprogramming Summary      | 5-28 |

| Chapter 6 | THE LSI-11 WRITABLE CONTROL STORE                 | 6-1  |

| 6.1       | GENERAL                                           | 6-1  |

| 6.2       | THE WRITABLE CONTROL STORE MEMORY                 | 6-1  |

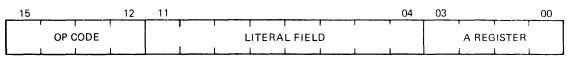

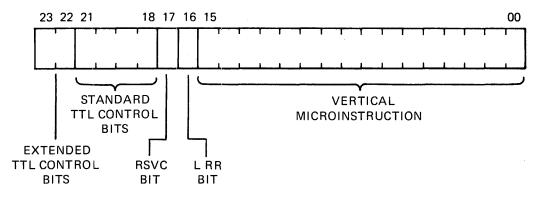

| 6.2.1     | Control Store Microword Organization              | 6-1  |

| 6.2.1.1   | Standard 22-Bit Microword MI<21:0>                | 6-4  |

| 6.2.1.2   | Extended TTL Control Bits MI<23:22>               | 6-4  |

| 6.2.2     | Control Store Microaddressing Modes               | 6-4  |

| 6.3       | WRITABLE CONTROL STORE MEMORY ACCESS              | 6-5  |

| 6.3.1     | Microinstruction Bus Access                       | 6-5  |

| 6.3.1.1   | Control Store Access Timing                       | 6-8  |

| 6.3.1.2   | Extended TTL Control Bit Timing                   | 6-8  |

| 6.3.2     | LSI-11 System Bus Access                          | 6-12 |

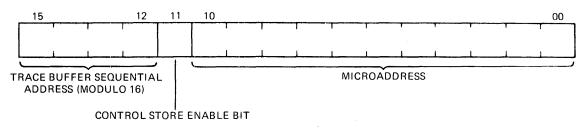

| 6.4       | THE MICROADDRESS TRACE RAM                        | 6-12 |

| 6.4.1     | Microaddress Trace RAM Operation                  | 6-12 |

| 6.4.2     | WCS Enable Bit                                    | 6-12 |

| 6.5       | LSI-11 SYSTEM BUS INTERFACE                       | 6-14 |

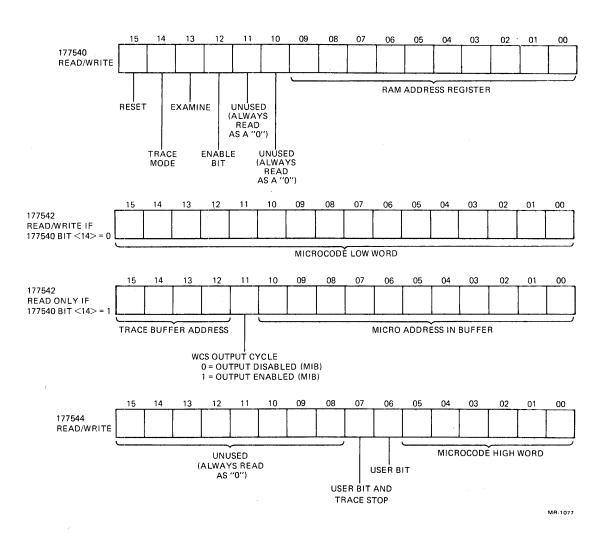

| 6.5.1     | WCS Control/Status Register                       | 6-14 |

| 6.5.2     | WCS Memory Access Registers                       | 6-16 |

| 6.5.3     | Microaddress Trace Register                       | 6-16 |

| 6.5.3.1   | Microaddress Trace RAM Dump Algorithm             | 6-17 |

| 6 6       | WDITABLE CONTROL STORE MODILE CIRCUIT DESCRIPTION | 6-17 |

| 6.6.1     | Clock Generation                                  | 6-17 |

|-----------|---------------------------------------------------|------|

| 6.6.2     | Control Store Memory and Microaddress Multiplexer | 6-20 |

| 6.6.3     | LSI-11 System Bus Interface                       | 6-20 |

| 6.6.4     | Microinstruction Bus Interface                    | 6-20 |

| 6.6.5     | Microaddress Trace RAM                            | 6-20 |

| 6.7       | WRITABLE CONTROL STORE HARDWARE SPECIFICATIONS    | 6-21 |

| 6.7.1     | Dimensions                                        | 6-21 |

| 6.7.2     | Power Requirements                                | 6-21 |

| 6.7.3     | LSI-11 System Bus Backplane Pin Assignments       | 6-21 |

| 6.7.4     | Microinstruction Bus Connector Pin Assignment     | 6-21 |

| 6.7.5     | TTL Control Bit Summary                           | 6-24 |

| Chapter 7 | LSI-11 MICROPROCESSOR ASSEMBLER                   | 7-1  |

| 7.1       | GENERAL                                           | 7-1  |

| 7.2       | MICROASSEMBLER (MICRO)                            | 7-1  |

| 7.2.1     | Statement Format                                  | 7-1  |

| 7.2.2     | Expressions                                       | 7-2  |

| 7.2.2.1   | Numeric Constants                                 | 7-2  |

| 7.2.2.2   | Symbols                                           | 7-2  |

| 7.2.2.3   | Current Location Counter                          | 7-3  |

| 7.2.2.4   | Arithmetic or Logical Operators                   | 7-4  |

| 7.2.3     | Microinstructions                                 | 7-4  |

| 7.2.3.1   | Jump Instruction                                  | 7-4  |

| 7.2.3.2   | Conditional Jump Microinstructions                | 7-4  |

| 7.2.3.3   | Literal Microinstructions                         | 7-4  |

| 7.2.3.4   | Two Register Microinstructions                    | 7-5  |

| 7.2.3.5   | Single Register Microinstructions                 | 7-5  |

| 7.2.3.6  | Reset and Set Flags Microinstructions                   | 7-5  |

|----------|---------------------------------------------------------|------|

| 7.2.3.7  | Input Microinstructions                                 | 7-5  |

| 7.2.3.8  | No-Operation Microinstruction (NOP)                     | 7-6  |

| 7.2.3.9  | Load Condition Flags Microinstructions (LCF)            | 7-6  |

| 7.2.3.10 | Return From Subroutine Microinstruction (RFS)           | 7-6  |

| 7.2.3.11 | Reset TSR Microinstruction (RTSR)                       | 7-6  |

| 7.2.4    | Microassembler Directives                               | 7-7  |

| 7.2.4.1  | NXT Directive                                           | 7-7  |

| 7.2.4.2  | TITLE Directive                                         | 7-7  |

| 7.2.4.3  | SBTTL Directive                                         | 7-7  |

| 7.2.4.4  | REG Directive                                           | 7-7  |

| 7.2.4.5  | LOC Directive                                           | 7-8  |

| 7.2.4.6  | END Directive                                           | 7-9  |

| 7.2.4.7  | Equated Symbols                                         | 7-9  |

| 7.2.4.8  | PAGE Directive                                          | 7-9  |

| 7.2.4.9  | MODE Directive                                          | 7-9  |

| 7.2.5    | Using the MICRO Assembler                               | 7-10 |

| 7.2.5.1  | Bitmap of Used Memory Locations                         | 7-10 |

| 7.2.6    | Errors in the Source Program                            | 7-10 |

| 7.2.7    | WCS Module Addressing Mode Support                      | 7-11 |

| 7.3      | LOADING AND SAVING WRITABLE CONTROL STORE (WCSLOD)      | 7-11 |

| 7.3.1    | Loading Object Modules                                  | 7-11 |

| 7.3.2    | Saving the Contents of WCS                              | 7-12 |

| 7.4      | MICRO ODT (MODT)                                        | 7-12 |

| 7.4.1    | Symbolic Examination and Modifications of WCS Locations | 7-13 |

| 7.4.2    | Executing a Microprogram                                | 7-14 |

| 7.4.3    | Dump Points                                             | 7-15 |

| 7 4 4    | Tracing Microprograms                                   | 7-16 |

| 7.4.5     | Transferring to WCSLOD                        | 7-16 |

|-----------|-----------------------------------------------|------|

| 7.4.6     | Using MODT                                    | 7-16 |

| 7.4.6.1   | Using MODT as a SAVE File                     | 7-16 |

| 7.4.6.2   | Using MODT with a MACRO-11 Object Program     | 7-17 |

|           |                                               |      |

| Chapter 8 | MICROPROGRAMMING TECHNIQUES                   | 8-1  |

| 8.1       | GENERAL                                       | 8-1  |

| 8.2       | USER MICROPROGRAMMING ENTRY POINTS            | 8-1  |

| 8.2.1     | Entry Microaddress 3000                       | 8-2  |

| 8.2.2     | Entry Microaddress 3001                       | 8-2  |

| 8.2.3     | Entry Microaddress 3002                       | 8-2  |

| 8.2.4     | Entry Microaddress 3003                       | 8-2  |

| 8.2.5     | Entry Microaddress Summary                    | 8-2  |

| 8.3       | MACHINE INSTRUCTION DECODING TECHNIQUES       | 8-3  |

| 8.3.1     | Successive Comparison Decoding                | 8-3  |

| 8.3.2     | Modified Jump Decoding                        | 8-4  |

| 8.4       | PASSING OPERANDS TO USER MACHINE INSTRUCTIONS | 8-4  |

| 8.4.1     | Predefined Operand Addressing                 | 8-4  |

| 8.4.2     | Register Operand Addressing                   | 8-5  |

| 8.5       | MICROPROGRAMMING THE USER MACHINE INSTRUCTION | 8-5  |

| 8.5.1     | Defining The Instruction                      | 8-5  |

| 8.5.2     | Documenting the Instruction                   | 8-5  |

| 8.5.3     | Temporary Flag Use                            | 8-6  |

| 8.5.4     | Executing Machine-Level I/O Operations        | 8-6  |

| 8.5.4.1   | Bus Error Trap Control                        | 8-6  |

| 8.5.5     | Scratch Register Usage                        | 8-6  |

| 8.5.5.1 | Source Operand Register (RSRC)                     | 8-6  |

|---------|----------------------------------------------------|------|

| 8.5.5.2 | Destination Operand Register (RDST)                | 8-7  |

| 8.5.5.3 | Instruction Register (RIR)                         | 8-7  |

| 8.5.5.4 | Bus Address Register (RBA)                         | 8-7  |

| 8.5.5.5 | LSI-11 Processor Registers (R0-R5)                 | 8-7  |

| 8.5.5.6 | LSI-11 Stack Pointer (R6) and Program Counter (R7) | 8-7  |

| 8.5.5.7 | Procesor Status Word Register (RPSW)               | 8-7  |

| 8.5.6   | Interrupt Considerations                           | 8-8  |

| 8.5.6.1 | Testing For Pending Interrupts                     | 8-8  |

| 8.5.6.2 | Aborting a Microprogram                            | 8-8  |

| 8.6.6.3 | Suspending and Resuming a Microprogram             | 8-8  |

| 8.6     | PROCESSOR STATUS WORD MANIPULATIONS                | 8-9  |

| 8.6.1   | Moving the PSW to a Processor Register             | 8-9  |

| 8.6.2   | Moving 8-Bits to the PSW                           | 8-9  |

| 8.7     | MICROPROGRAMMING USER-DEFINED TRAP VECTORS         | 8-11 |

| 8.7.1   | Creating the Vector Addresses                      | 8-13 |

| 8.7.2   | Joining the Base Microcode                         | 8-13 |

| 8.8     | MICROPROGRAMMING SYNCHRONIZED CONTROL SIGNALS      | 8-13 |

| 8.8.1   | Standard TTL Control Bits                          | 8-13 |

| 8.8.2   | Extended TTL Control Bits                          | 8-12 |

| 8.9     | CONTROLLING THE MICROINSTRUCTION FLOW              | 8-13 |

| 8.9.1   | Leaving User Control Store                         | 8-1  |

| 8.9.2   | Jump To Subroutine and Return Microinstructions    | 8-1  |

| 8.9.3   | Conditional Jump Microinstructions                 | 8-1  |

| Chapter  | 9 | INSTALLATION                      | 9-1  |

|----------|---|-----------------------------------|------|

| 9.1      |   | GENERAL                           | 9-1  |

| 9.2      |   | UNPACKING AND INSPECTION          | 9-1  |

| 9.3      |   | INSTALLATION PROCEDURE            | 9-1  |

| 9.3.1    |   | Switch Configurations             | 9-1  |

| 9.3.2    | • | Cable Configuration               | 9-3  |

| 9.3.3    |   | WCS Installation                  | 9-3  |

| 9.4      |   | PERFORMANCE CHECKOUT              | 9-7  |

| Chapter  | 1 | 0 MAINTENANCE                     | 10-1 |

| 10.1     |   | GENERAL                           | 10-1 |

| 10.2     |   | PREVENTIVE MAINTENANCE            | 10-1 |

| 10.3     |   | CORRECTIVE MAINTENANCE PHILOSOPHY | 10-1 |

| 10.4     |   | CORRECTIVE MAINTENANCE            | 10-1 |

| ADDENIDT | v | A INCUDICUTON CHMMADV             | A-1  |

|   |  | - |  |

|---|--|---|--|

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

| ; |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

#### CHAPTER 1

#### INTRODUCTION TO LSI-11 USER MICROPROGRAMMING

#### 1.1 GENERAL

This chapter provides an introduction to LSI-11 microprogramming. Through microprogramming, the user has access to nearly all the resources and techniques used to implement the LSI-11 architecture in four LSI (Large Scale Integration) chips. Section 1.6 lists other documents referenced by this manual.

# 1.1.1 Introductory Microprogramming Glossary

This section contains a glossary of selected terms which provide an introduction to the terminology used to describe LSI-ll microprogramming concepts.

Microprocessor

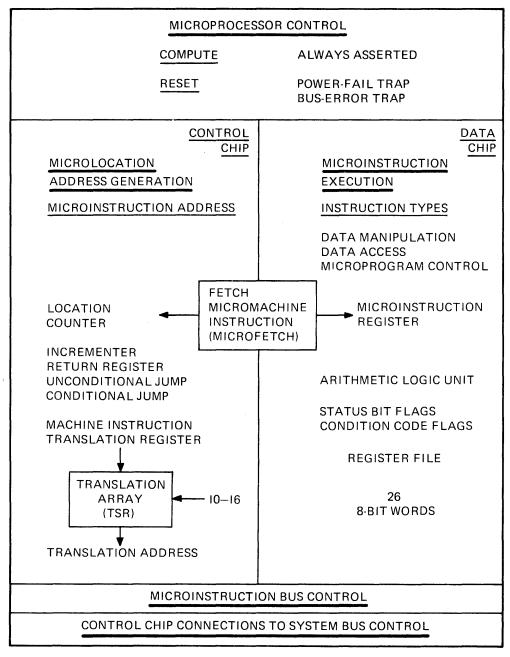

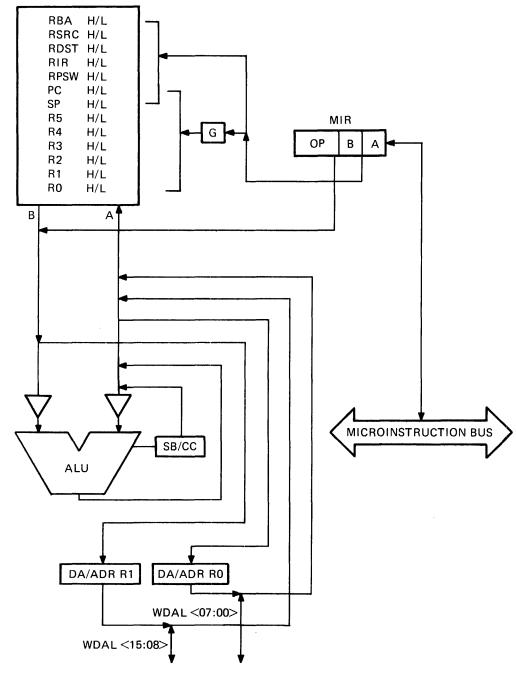

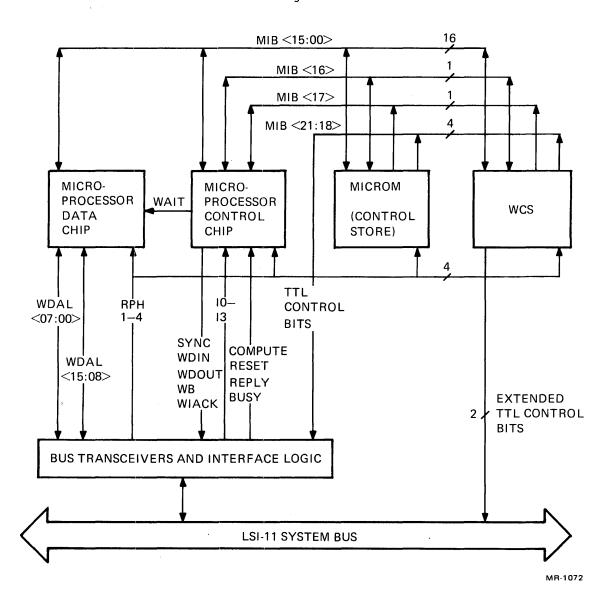

The microprocessor is implemented as a two-chip set of large scale integrated (LSI) circuits called the Data and Control chips. The Data chip contains the Arithmetic Logic Unit (ALU), the Register File and interconnection to the LSI-ll system bus data/address lines (DAL). The Control chip provides the system bus control lines and contains the translation array.

Micromachine

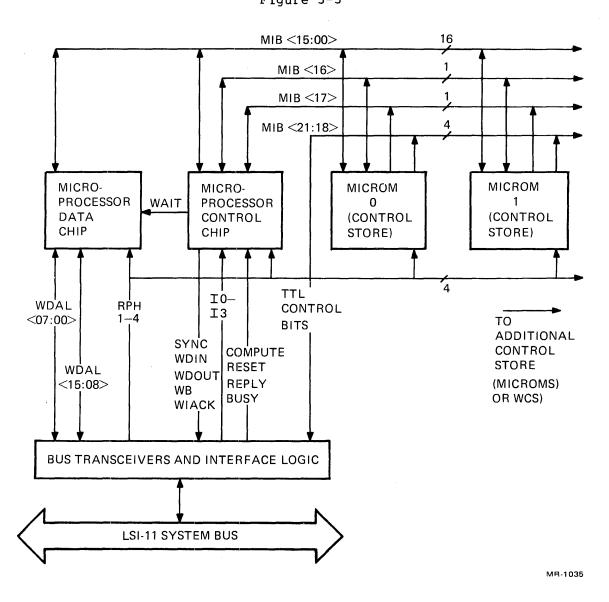

The micromachine consists of a two-chip microprocessor, two or three MICROMs (Control Store chips), and the LSI-11 system bus interface logic. The first two MICROMS contain the PDP-11 emulation microprogram as well as the console ODT microprogram. The optional KEV11 MICROM contains microprograms which execute the extended and floating point machine instructions.

Machine

The LSI-11 machine encompasses the LSI-11 Micromachine, main or program memory and input/output devices.

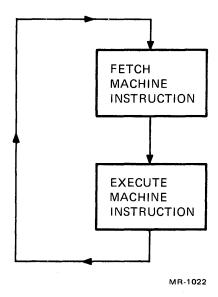

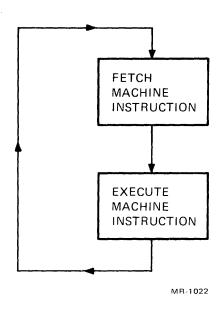

Machine Cycle

Machine cycle refers to the smallest complete cycle of operations performed by the LSI-11 machine. The three fundamental operations of the

machine cycle are (1) Fetch machine instruction, (2) Execute machine instruction (3) Trap and interrupt service. The number and type of micromachine operations which must be performed during a given machine cycle are a function of the fetched machine instruction and whether a machine interrupt or system fault is present. Consequently, the time required to complete the machine cycle is variable.

Microcycle

Microcycle refers to the smallest complete cycle (Micromachine Cycle) of operation performed by the LSI-ll micromachine. A machine cycle is composed of one or more microcycles. A microcycle consists of four equal phases (PH1-PH4).

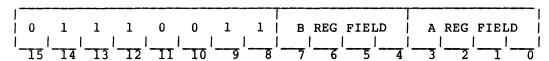

Machine Instruction (Machine Code)

A machine instruction is a 16-bit word stored in main memory. Machine instructions are commonly referred to as instructions.

Microinstruction (Microcode)

A microinstruction is a 22-bit word stored in Control Store.

Microassembler

The microassembler is a microprogram development tool which accepts as input a source file containing micromachine assembly language statements with optional comments. The microassembler output is an object file which may be loaded into the Writable Control Store.

Fetch

Fetch is the operation of presenting an address to memory and subsequently moving the contents of the addressed location to the instruction register contained in the processor.

Execute

The action of performing all operations required by a machine instruction.

Interrupt

The action of diverting control from the normal (uninterrupted) machine operating cycle of repeated Fetch-Execute events. The simplest complete operating cycle is expressed Fetch-Execute-Interrupt.

Program Counter

The Program Counter (PC) stores the main memory address of the next machine instruction to be feched during a machine cycle. It is automatically incremented by 2 as the last part of the Fetch Machine Instruction phase.

Microprogram Counter

The Microprogram Location Counter (LC) stores the address of the next microinstruction to be during a microcycle. The Location Counter may be loaded from various sources, depending upon the type of microinstruction being executed.

Program Store oth program and data inProgram Store refers to the LSI-ll machine main}

formation. Program store is accessed via the LSI-11 system bus. Program store may alternately be referred to as Main Store, Memory or sometimes as core.

Control Store

Control store refers to the storage area for microcode and consists, potentially, of 2048 locations. Control store for the LSI-ll machine is provided by two or more MICROMs and the WCS module.

Writable Control Store Writable Control Store (WCS) refers to a control store which may be altered by the user. Alterable or writable control store is implemented by read/write random access memory (RAM) devices which can be accessed by both the LSI-ll System Bus and the microinstruction bus.

Data Chip

All Data processing occurs within the Data chip. It contains the ALU and the internal registers. It also provides bi-directional connection to the LSI-ll system bus data/address lines (DAL).

Control Chip

The Control chip functions as a controller/sequencer. It provides all control signals for the system bus and also determines which microinstructions are executed. An important feature of the ConTrol chip is the translation Array. This is a large combinatorial logic network which accepts the machine instruction as input and outputs the addresses of the microprogrammed routine appropriate to that instruction.

MICROM Chip

A MICROM (MICrocode Read Only Memory) chip is the unalterable, non-volatile read only control store memory. One or more MICROMs are connected to the Data and Control chips via the microinstruction bus (MIB).

System Bus

The LSI-11 system bus is the common, bidirectional path which passes address, data and control information between the LSI-11 machine and all other modules which make up a given machine configuration.

Microinstruction Bus The Microinstruction Bus (MIB) is the common bidirectional data and control path between all elements of the micromachine. It is through connection to this bus that the WCS module makes its control store accessible to the microprocessor.

Instruction Register When an LSI-ll machine instruction is fetched from main memory, it is placed in the Instruction Register (RIR) in the Data chip as well as in the translation register in the Control chip.

Microinstruction Register A microinstruction which has been fetched from either MICROM or user control store is placed in the microinstruction register. This register is

implemented on both the Data and Control chips. The microinstruction register on each chip contains only the portion of the microinstruction relevant to the chip's function.

Translation Register The Translation Register and the instruction register (RIR) are loaded simultaneously during a machine instruction fetch. The translation register holds the machine instruction for input to the translation array.

Translation Array

The Translation Array is located in the microprocessor Control chip and receives as input either the upper or lower byte of the Translation Register, the microprogram Location Counter and the interrupt register contents. It consists of a large combinatorial logic network which determines the starting location for microcode routines appropriate to fetched machine instructions.

Return Register

The Return Register (RR) is located in the microprocessor Control chip and provides storage for a single microprogram subroutine return address.

Register File

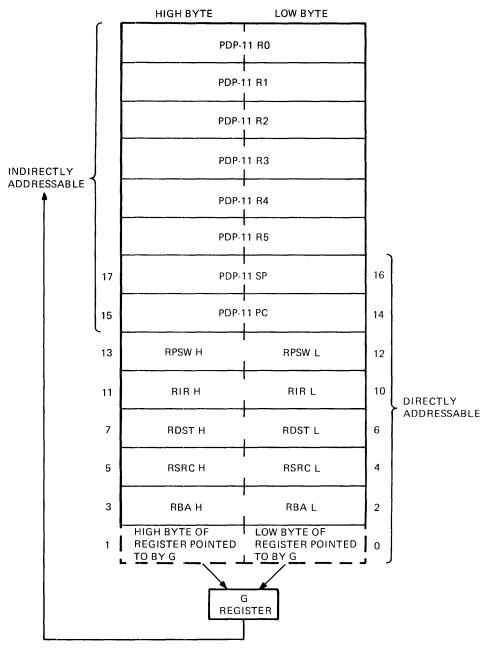

The register file is located in the Data chip and contains 26 8-bit registers which are accessed by a combination of direct and indirect addressing. Adjacent 8-bit registers may be sequentially addressed to form word operands.

## 1.1.2 LSI-11 Microprogramming Features

- LSI-11 microprogramming is provided by a Writable Control Store module in conjunction with microprogramming support software.

- The WCS module allows one half (1024) of the total (2048) control store locations to be user microprogrammed.

- 3. The microprogramming support software includes a microassembler, writable control store loader and dumper, and a Micro Octal Debugging Tool which allows simultaneous debugging at the machine and micromachine levels.

- 4. The microprogramming support software also includes the micro code for the EIS/FIS machine instructions. The user may include this microcode in the final writable control store load module, thus combining the existing advantages of the familiar extended and floating point machine instructions with user designed instructions.

- 5. LSI-ll microprogramming combines the simplicity of vertical microinstructions with the individual bit-control of horizontal microinstructions. The existing bit-control field supported by the micromachine is expanded by two additional bits

with the addition of the WCS module. This new bit-control facility is also timed with respect to the micromachine cycle, thus enabling higher control rates and more accurate control timing than can be achieved with normal LSI-11 system bus I/O control.

6. The WCS module is equipped with a 16-word recirculating microlocation Trace RAM which aids in microprogram debugging. It contains the last 16 microlocations placed on the microinstruction bus. This hardware feature is utilized by MODT to display the last 16 microlocations accessed prior to a user-specified dump point.

### 1.1.3 Basic LSI-ll Machine-Micromachine Structure

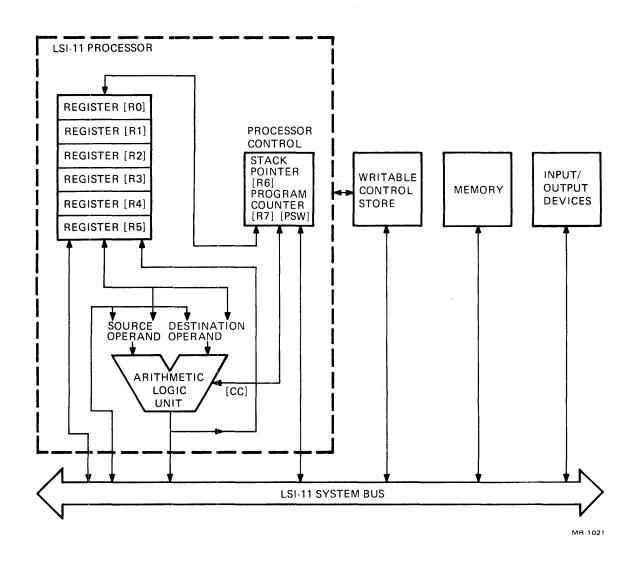

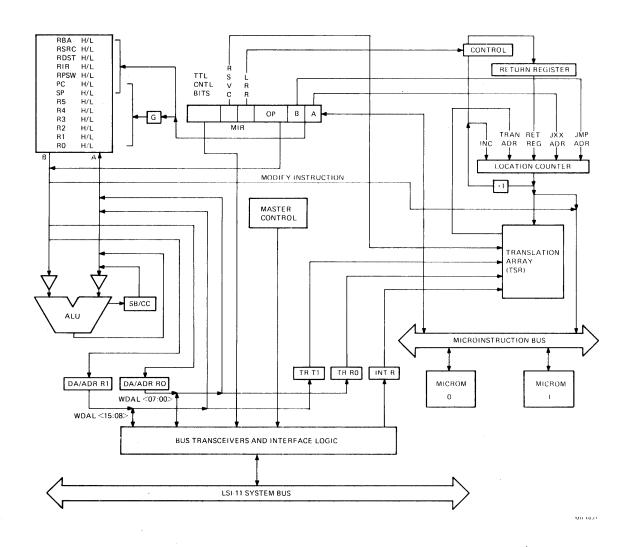

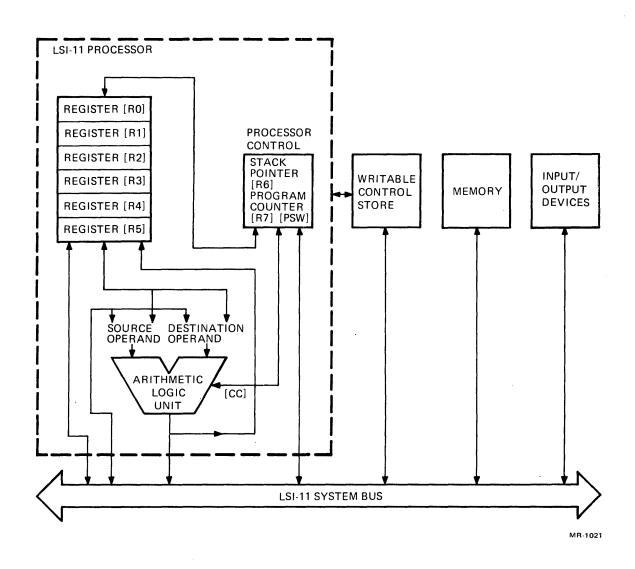

Figure 1-1 contains a simplified illustration of the LSI-11 machine. The LSI-11 machine encompasses the processor, main store or memory, and the input/output devices. These three main components are interconnected by the LSI-11 system bus. The LSI-11 processor is realized by a micromachine which contains a (micro)processor element, a storage element (control store), and external I/O capability. The microprocessor is implemented with two chips (called the Data chip and the Control chip). The Data chip contains the Arithmetic Logic Unit (ALU), the register file, and provides connection to the 16 time multiplexed data/address lines (DAL). The Control chip arbitrates all system bus transactions and determines the microinstruction execution sequence. The structure of the microprocessor chip set is presented in detail in Chapter 3.

The microinstructions are stored in a control store consisting of two or more MICROMs which provide non-alterable, non-volatile memory. The term MICROM is an acronym for MICrocode Read Only Memory. In the basic LSI-11 processor, the MICROM control store contains microcode which performs 2 functions: (1) PDP-11 emulation and (2) console ODT. When included on the processor, The KEV11 EIS/FIS option expands the control store to implement the extended and floating point machine instructions.

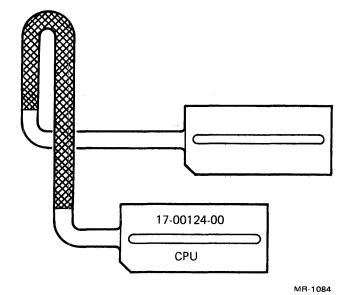

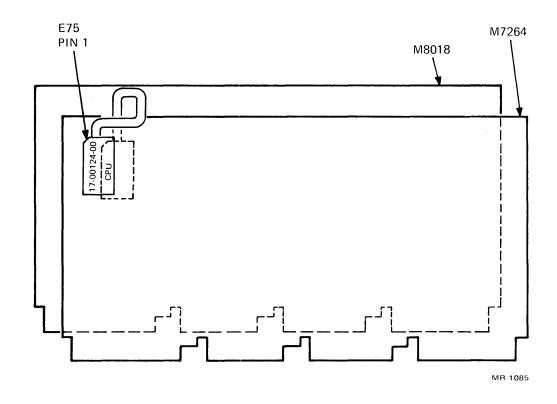

The Writable Control Store is connected to the micromachine via a cable/plug assembly (which replaces the KEV11 option in the third MI-CROM socket). This gives the WCS module access to the microinstruction bus which is the internal bus interconnecting all components of the micromachine. The WCS then may be accessed by the microprocessor in the same fashion as a MICROM. The total number of control store locations addressable by the microprocessor is 2048. The PDP-11 emulation and console ODT microcode require only 1024 locations, or two MICROMs. The WCS module supplies the remaining 1024 control store locations. The WCS memory is loaded and dumped via its LSI-11 system bus interface, which consists of normal control/status and data buffer registers.

LSI-11 Machine-Micromachine Structure

Figure 1-1

## 1.2 THE BENEFITS OF USER MICROPROGRAMMING

User microprogramming affords greater control over machine operations. The user can create new machine instructions to be used in the same manner as members of the LSI-11, PDP-11/03 machine instruction set. The following paragraphs identify specific areas in which user microprogramming may be beneficial.

### 1.2.1 Arithmetic Calculations

Many arithmetic calculations are characterized by a concisely-defined algorithm which is often repetitive in nature. The execution of the routine for such an algorithm normally requires many machine instruction fetches and operand address calculations. If the algorithm is suitable for microprogramming it can be implemented in microcode which is then executed in response to a single, user-defined machine instruction. This approach eliminates the multiple machine instruction fetch operations because control remains entirely within the micromachine until the routine is completly executed. A good example of the improvement available in this area is the KEV11 EIS/FIS option. The EIS/FIS option contains microcoded routines for the extended and floating point machine instructions. Upon execution of a single machine instruction, FDIV for example, control is transfered to the appropriate starting point in the FIS microcode. When the routine has terminated, control is returned to the LSI-11 emulation microcode contained in the 2 standard microms. The speed advantage realized by the EIS/FIS microcode ranges from a 3 to 10 times improvement over comparable PDP-11 macroinstruction routines, depending upon the instruction executed and the operand values.

## 1.2.2 Critically-Timed Input/Output and Control Operations

The rate at which real-time input/output (I/O) operations can be performed depends on three factors: (1) the speed of machine instruction execution, (2) the time delays associated with the LSI-ll system bus and (3) the speed of the device or memory being accessed. The microprogramming facility allows the user to write specialized I/O routines for execution in microcode. In this context, the user employs the "data access" group of microinstructions which are discussed generally in Chapter 4 with detailed explanations in Chapter 5. Sufficient information is provided to allow identification of where these bus delays occur so non I/O microinstructions can be inserted to utilize the delay time.

User-written microcode can make use of a special field of 4 TTL control bits within the microinstruction. Of the 16 possible states encoded in this field, 8 are presently used to control the LSI-ll system bus logic which interfaces between the system bus and the microprocessor chip set. The other 8 states are available for user-defined functions. The 4 bits from this microinstruction field appear on the LSI-ll module fingers as does the third phase of the microcycle clock (PH3 H). These TTL control bits enable the microprogrammer to produce high rate control signals which are timed with respect to the micromachine cycle.

In addition to the 4 control bits (MI<21:18>), the WCS module stores 2 extra bits (MI<23:22>) in each control store location. These two bits are available as signals directly on the LSI-ll system backplane and may be used for any user-defined purpose. The high-order bit (MI<23>) is also used to control the microlocation trace buffer.

# 1.2.3 Data Manipulation and Relocation

A block move microprogram example is discussed in Chapter 8 in which the arguments required are (1) the starting address of the block to be moved, (2) the starting address of the new block location, and (3) the block length. The execution time saved is proportional to the block length, because machine instruction fetches are eliminated for each word moved.

#### 1.3 SYSTEM IMPLICATIONS OF USER MICROPROGRAMMING

With the microprogramming facility, all the resources used to emulate the LSI-ll architecture and operation are at the user's disposal. The only resource that cannot be accessed is the Control chip translation array which is specifically configured to implement the opcodes of the standard and extended machine instruction set. However, the microprocessor instruction set does provide a means for accomplishing translations in only a few additional microcycles.

## 1.3.1 Control Flow Integrity

The first responsibility of the microprogrammer is to maintain the integrity of the control flow which implements the machine operating cycle. Control is transferred to user microcode when the microprocessor control chip, via the translation array, determines that a the fetched instruction is a user-defined machine opcode. User microcode then maintains control until the microroutine has executed, whereupon control must be returned to the trap interrupt service routine, thus maintaining the normal Fetch-Execute-Interrupt machine cycle.

An additional requirement arises when the user-microprogrammed routine performs I/O operations. In executing an I/O transfer the LSI-ll system bus transaction requires that the addressed I/O device return a reply signal to the processor, acknowledging its role in the transfer. If no reply is received by the CPU within 10 microseconds, the processor executes a bus error trap through LSI-ll memory location 4. Because a bus error can occur in a number of contexts, the microprogrammer must prepare for the proper response by setting an internal flag (see Section 8.6.4.1).

### 1.3.2 Interrupt Response Latency

Interrupts are recognized by the LSI-11 processor only during the final phase of the normal machine operating cycle (Fetch-Execute-Interrupt). The delay in acknowledging a pending in-

terrupt is directly related to the length of time of the Execute phase. The microprogrammer is provided with a means of testing for external interrupts and the Event Line interrupt during user-microprogram execution. If such an interrupt is pending, control can be transferred to a user microcode routine. This routine could save the interrupted machine state, decrement the PC and then return control to the last part of the machine cycle.

Once the normal LSI-11 interrupt service has been completed, the user-defined machine instruction is fetched again and the user microprogram can then execute to completion. The external interrupt test facility allows potentially lengthy microcoded routines to operate in a time critical environment. Interrupt testing is unnecessary when the microcode to be executed is of known short duration. See Section 8.6.7.

## 1.3.3 Register Content Security

The microprogrammer has access to the LSI-ll processor registers as well as to the internal registers in the micromachine. Several of the internal registers have predefined uses (e.g., PSW, bus error flags) and should only be modified in accordance with those uses. Manipulation of the standard processor registers (R0-R7) should only occur as part of the intended function of the user-defined machine instruction.

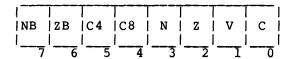

# 1.3.4 Processor Status Word Updating

The processor status word (PSW) in the LSI-ll is a composite of (1) the 4 PDP-ll Status Flags (N,Z,V,C) and (2) the Trace Bit and (3) the Interrupt Enable bit. Internally, the PDP-ll Status Flags are explicitly accessed by 2 microinstructions (LCF, CCF) and implicitly altered by executing a microinstruction capable of affecting these flags (e.g., AWF). The Trace Bit and Interrupt Enable Bit are altered by executing a Set Interrupt (SI) or Reset Interrupt (RI) for the microprocessor control flags I4 and I5 respectively. Since these flags cannot be read, a copy of these flags is kept in an internal register (RPSWH) in the bit positions that correspond to the Trace bit (bit <4>) and the Interrupt Enable bit (bit <7>) of the LSI-ll PSW.

### 1.3.5 Dedicated Control Store Locations

The 1024 Writable Control Store locations are normally configured at microaddresses 2000 through 3777 (octal). The WCS module therefore replaces the EIS/FIS MICROM which responds to addresses 2000-2777. The LSI-11 emulation microcode, in conjunction with the translation array, performs a partial decode of the extended and floating point machine instructions and transfers control to control store locations in the 2000-2777 range. The microprogrammer has the responsibility of handling such a transfer as a reserved instruction trap.

## 1.3.6 Machine Instruction Support

A newly defined machine instruction must be explicitly documented as to function, execution characteristics, and operand requirements. It should also be assigned an assembly mnemonic which is supported by a macro definition to enable the instruction to be programmed and assembled along with the standard instruction set (See Section 8.2).

### 1.4 MICROPROGRAM CHARACTERISTICS

## 1.4.1 Vertical and Horizontal Microinstructions

The user will discover that microprogramming the LSI-11 micromachine requires techniques nearly identical to those used in LSI-11 assembly language programming. This strong similarity arises because the micromachine executes vertical as opposed to horizontal microcode. One characteristic of vertical microinstructions is that microinstructions are executed out of sequential locations in control store, just as machine instruction are executed sequentially out of main or program store.

Another characteristic shared between vertical microinstructions and machine instructions is that both perform recognized complete operations upon execution. For example, the COMPLEMENT BYTE microinstruction reads the contents of the specified source operand register into the ALU, forms the complement and places the result in the specified destination register. A horizontal microinstruction, by contrast, would affect (micro) processor control at a much more detailed level, often with direct control of register read and write circuitry, data path bus drivers, ALU operating modes, and so forth. In addition, the horizontal microcode usually contains a field which holds the address of the next microinstruction to be executed.

## 1.4.2 Logic Control Features

The LSI-11 microprogramming option offers a repetoire of 149 microinstructions which support both byte (8-bit) and word (16-bit) operations. Further, the basic 16-bit vertical microinstruction word is extended by 6 control bits within the micromachine and by an additional 2 control bits in the WCS module. The 6-bit extension contains 4 bits which may be encoded for direct control of user logic. The 2-bits supplied by the WCS module enhance this logic control capability. See Section 6.7.5.

## 1.5 THE MICROPROGRAMMING ENVIRONMENT

## 1.5.1 Creating the Source File

The RT-11 Operating System environment in which the LSI-11 microprogrammer works is familiar to the experienced PDP-11 assembly language programmer. A fundamental reference is the microinstruction set description, which is contained in Chapter 4 and Appendix A of this manual. Chapter 7 describes the WCS Software Tools available.

The source file for the microprogram is created with either text editor, EDIT or TECO. The recommended extension in the file specification is .MIC signifiying a microprogram source file.

#### 1.5.2 The Microassembler

The Microassembler is described in detail in Chapter 7. It consists of a stand alone 2 pass assembler for the LSI-ll microinstruction mnemonics with several assembler directives available. The listing shows the assembled octal for each microlocation and includes a bitmap of the utilized microaddresses. The microassembler output (.OBJ extension) is then loaded into the WCS module as described in the next section.

### 1.5.3 Writable Control Store Loader

The microprogramming support software provides a WCS loader program which can initially clear the WCS RAM memory and then load from one to six specified .OBJ files produced by the Microassembler. The WCS loader is described in Chapter 7.

# 1.5.4 Micro Octal Debugging Tool (MODT)

Microprogram debugging is done using the Microprogram Octal Debugging Tool program (MODT). This program expands the familiar PDP-11 ODT so that user-written microprograms can be examined, modified, and executed. Since all microprograms are executed in response to machine instructions, MODT allows the user to write, modify and execute short programs. Breakpoints may be set in the machine instruction flow to examine program progress at the machine level. At the micromachine level, the user may establish "dump points" which display the contents of all internal registers at a selected point. Once the dump results are analyzed, the dump points can be moved and subsequent executions allow the user to examine additional portions of microcode. This dump-examine process continues until the microprogram is completely debugged and verified. MODT is described in detail in Chapter 7.

## 1.5.5 Microprogram Trace Facility

The microaddress trace hardware on the WCS module is normally controlled and examined by the Micro Octal Debugging Tool (MODT) program. It consists of a 16-word buffer which stores a sequence of 16 microinstruction locations placed on the microinstruction bus (MIB) during the execution of user-written microcode. The last location to be stored is designated by the microprogrammer (using MODT). Once the 16 addresses have been stored, MODT may display the contents of the addressed locations in both octal and symbolic forms. See Chapter 7 for a complete description.

### 1.6 REFERENCES

The following documents provide background information for this manual:

- 1. RT-11 System User's Guide, DEC-11-ORGDA-A-D

- PDP-11 TECO User's Guide, DEC-11-UTECA-A-D

- 3. The Microcomputer Handbook, EB-07948-53

- KD11-H processor schematic diagram, D-CS-M7264-0-1 (revision Y or greater)

- 5. WCS schematic diagram, D-CS-M8018-0-1

Additional copies of all items above can be ordered from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA 01532

Attn: Communications Services (NR2/M15)

Customer Services Sections

### CHAPTER 2

#### THE LSI-11 MACHINE STRUCTURE

#### 2.1 GENERAL

This discussion of the LSI-11 machine structure covers both the architecture and operation of the LSI-11. Architecture relates to the system resources and their configuration. Operation indicates how data and address information is moved between and manipulated within the system resources.

This chapter is a subset of the Microcomputer Handbook, which should be consulted for additional detail, specifically in the areas of LSI-ll options and hardware. This chapter emphasizes selected topics which are essential to the understanding of the microprocessor contained within the LSI-ll processor module. Chapter 3 enhances the information to include the additional information required to microprogram the LSI-ll micromachine.

## 2.2 MACHINE ARCHITECTURE

The LSI-11 machine consists of three general component areas connected by a common system bus. Any specific machine configuration may be accurately represented by using specialized components in these three areas:

- 1. The LSI-11 Processor

- 2. The Memory

- The Input/Output Devices

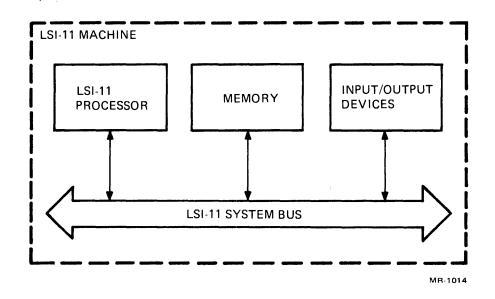

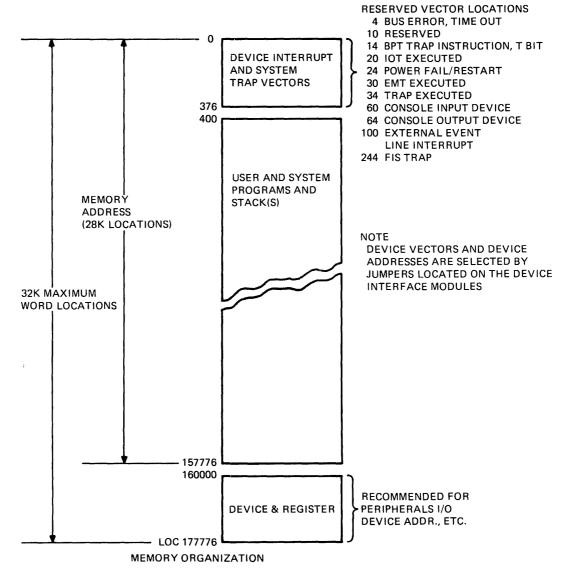

These components and their common, bidirectional access to the system bus are illustrated in Figure 2-1.

## 2.2.1 System Bus

The system bus is characterized by the number of memory or device locations addressable, the type of information transfers supported, and by the auxiliary system control signals it contains.

LSI-11 Machine Structure

Figure 2-1

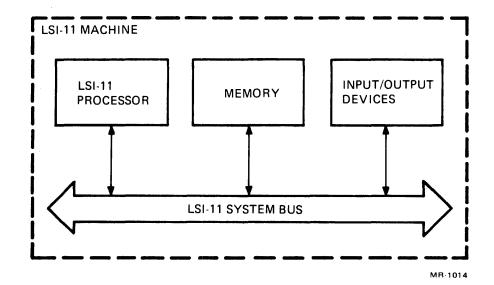

2.2.1.1 System Bus Address Space - The virtual (and physical) addressing capability of the system bus is determined by the 16-bit width of the binary addressing word. The system bus supports both 8 bit byte and 16 bit word addressing. Figure 2-2 illustrates the address space with which the LSI-11 machine operates. The bottom 28K (28,672) word addresses constitute the memory space. The top 4K (4096) word addresses are normally dedicated to the input/output devices. The LSI-11 processor does not occupy any address locations.

2.2.1.2 System Bus Data Transfer - All data transfer operations supported by the system bus are under the control of the LSI-ll processor. A portion of the processor is dedicated to the control of the system bus and administrates the transfer of data and address information between the machine components. There are three types of data transfers possible within the LSI-ll machine:

- 1. Programmed Input/Output Transactions (Programmed I/O)

- 2. Interrupt-Driven Input/Output Transactions (Interrupt I/O)

- 3. Direct Memory Access Input/Output Transactions (DMA I/O)

Programmed I/O occurs in response to programmed machine instructions. An example of Programmed I/O is the execution of a MOV instruction where at least one of the source or destination addresses is in memory or in a device register. If both source and destination operands are in the processor registers, no bus I/O transfer is required.

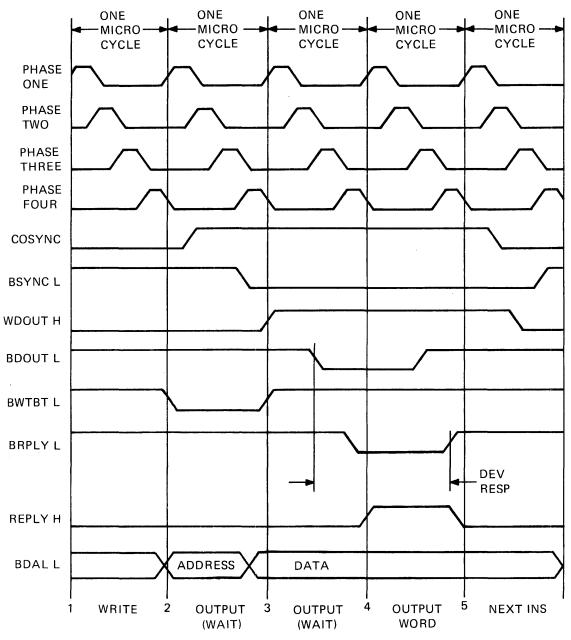

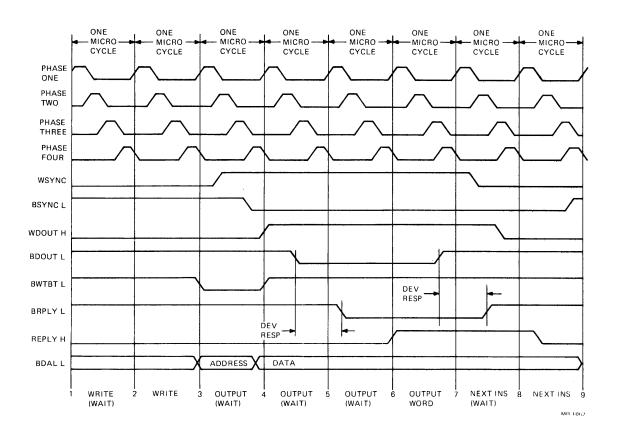

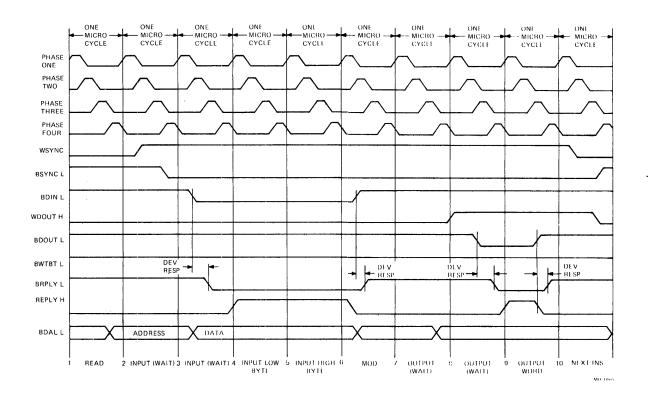

The simplest example of a Programmed I/O bus transaction is the DATI (Data-In) bus operation. This operation illustrates how the 16 Data/Address Lines (BDAL L <15:00>) are time-multiplexed between ad-The first event of the DATI cycle is dress and data information. placing the memory or device address on BDAL L <15:00>. After the address information settles (or becomes valid), the BSYNC L signal is asserted. This signal causes each memory and I/O DEVICE module connected to the bus to check whether the address corresponds to its own address(es). Recognition by the addressed device is represented by a signal internal to that device which is latched (or stored) by the assertion of BSYNC L for the duration of the bus operation. this signal constitutes the second event. The third event of the DATI cycle removes the address information from BDAL L<15:00> and asserts BDIN L. This signal informs the memory or selected device that a DATA-IN cycle is to be performed. The fourth event is in response to BDIN L; the selected device places its data on BDAL L<15:00> and returns BRPLY L to the processor. The assertion of BRPLY L is the first indication to the processor that the addressed component exists and is putting data on the bus. Upon receipt of BRPLY L, the processor accepts the information on BDAL L<15:00> as valid and stores it internally. If BRPLY L is not received within 10 microseconds after BDIN L was asserted, a processor trap occurs to memory lcoation 10. By this means, the processor avoids waiting for a reply from a memory location or device which does not exist or is malfunctioning. The bus cycle fifth event is the accepting and storing of the input data and the subsequent negation of BDIN L. In the sixth event, the selected device responds to the negation of BDIN L by terminating BRPLY L. In the seventh and final event, the processor terminates the bus cycle by negating BSYNC L.

# LSI-11 Machine Address Space

Figure 2-2

## NOTE

THERE IS 32K OF USERS MEMORY SPACE AVAILABLE; HOWEVER 0–28K IS RECOMMENDED FOR MEMORY ADDRESS LOCATIONS, AND 28K–32K FOR PERIPHERALS I/O DEVICE ADDRESSES, ETC.

MR-1202

The DATI bus cycle is described in detail in the Microcomputer Handbook along with the DATO (Data-Out), DATOB, DATIO (Data Input-Output) and DATIOB bus cycles. The "IO" (Input-Output) bus cycles enable the processor to execute a Read-Modify-Write operation. This allows data to be retrieved from an addressed location, manipulated within the processor, and re-deposited in the same location while asserting only one bus address. The "B" suffix on the DATOB and DATIOB bus cycles indicates that the output portion of the bus cycle is a byte rather than a word transfer.

Interrupt I/O is initiated by an Input/Output device. The interrupting device requests service from the LSI-ll processor by asserting the BIRQ L signal on the system bus. When the processor acknowledges a device request by asserting the BIACK H signal, it causes the interrupting device that is electrically closest to the processor on the LSI-ll bus to return a vector address. The vector address tells the processor where the address of the device service program is located in memory. Once execution of the service program has been completed, the LSI-ll processor resumes execution of the interrupted program.

Priority among multiple external devices having Interrupt I/O capability is established via electrical position relative to the processor. The device closer to the processor posesses the higher priority. The interrupt grant chain is broken by the device being serviced, thus making further interrupts from lower priority devices impossible. Further interrupts from higher priority (electrically closer) devices may still be acknowledged and serviced. Additional details regarding Interrupt I/O transactions are available in the Microcomputer Handbook.

Although the LSI-ll processor remains master of the system bus during both Programmed I/O and Interrupt I/O, DMA I/O requires that bus mastership be granted to an Input/Output device for high speed data transfer to or from memory. During a DMA I/O transaction, the Programmed I/O and Interrupt I/O operations of the LSI-ll processor are suspended. The device functioning as bus master can now perform any of the possible bus cycles (DATI, DATO, DATOB, DATIO, DATIOB). When the DMA transfer is completed, bus mastership is relinquished to the processor. Note that during DMA I/O, the CPU module waits to perform Programmed I/O or Interrupt I/O only. Any other processor activity (such as operations between registers) can continue.

2.2.1.3 System Bus Control Signals - In addition to the bus signals required to support Programmed I/O, Interrupt I/O, and DMA I/O several auxilliary control signals are contained within the bus system. System Initialization Signal

The common system initialization signal is BINIT L. It is asserted by the processor whenever BDCOK H is passive and whenever the BINIT command is issued by the processor. Examples of the latter are during the Power-up routine and in execution of the RESET machine instruction. All peripheral devices should use the BINIT L signal to initializae and clear internal flip-flops and registers.

Power Supply Signals

Two signals which indicate the status of the system power supply are

part of the bus system. These signals are generated by the power supply itself and the processor monitors them to take appropriate action during Power-Up and Power-Fail sequences. At the beginning of the Power-Up sequence, BDCOK H and BPOK H are both passive. BDCOK H is asserted first, whereupon the processor initializes itself and all system components and waits for BPOK H to be asserted. When BPOK H is asserted, the processor executes the jumper selected Power-Up routine. During a Power-Down or Power-Fail sequence, BPOK H is negated first, causing a Power-Fail trap. The processor then executes the program located at the trap vector address (24). When BDCOK H goes passive, the processor asserts BINIT L. It should be noted that a proper Power-Fail sequence will negate BDCOK H before restoring BPOK H. BDCOK H must go passive to re-initiate the Power-Up sequence.

## Processor Control Signal

The only signal in the bus system directly controlled by the operator of the processor is BHALT L. This signal is asserted by a front panel (PDP-11/03) switch or alternately by the BREAK key on the console terminal. Pressing the BREAK key causes a framing error which asserts BHALT L via the console serial line interface. When the front panel Run/Halt switch is used to halt the processor, it must be reset to RUN before the processor can proceed. However, pressing the console BREAK key asserts BHALT L only as long as the key is depressed.

### Processor Monitor Signal

The ability to monitor the Run/Halt state of the processor is provided by the SRUN signal. The SRUN signal is asserted once each time the processor performs a Machine Instruction Fetch. This signal is the input to a circuit on the PDP-11/03 console that drives a RUN indicator light.

## Memory Refresh Control

All dynamic MOS memory modules which do not have self-contained refresh capability must be refreshed via the system bus. A signal called BREF L is asserted during the addressing portion of the BSYNC/BDIN transaction to differentiate between memory refresh and the standard DATI bus cycle.

## 2.2.2 Memory

The memory component of Figure 2.1 may be implemented with either semiconductor or magnetic devices. Each memory device has operating characteristics which determine how it is to be used in a particular system.

Most memory devices function as Read/Write memory and may be accessed by either the processor or a DMA I/O device.

2.2.2.1 Semiconductor Memory - Semiconductor memory may be classified as either dynamic or static memory. The most familiar example of dynamic semiconducor memory is the 4K MOS Read/Write memory located on the KDll-F LSI-ll processor module. Dynamic memory must be periodically refreshed in order for the memory to retain its contents.

Static semiconductor memory is also available as Read/Write memory and doese refreshing. An example of this type is the 256 16-bit words of RAM found on the MRV11-BA UVPROM module. An additional static semiconductor memory type is Read Only Memory. Read Only Memory types are found on the MRV11-BA PROM module and on the MRV11-BA UVPROM module. Both the PROM and UVPROM are non-volatile types; they retain their contents even after power has been removed. The MRV11-BA PROM module contains fusible link semiconductor memory devices whose contents are established by special programming equipment. Once programmed, the fusible link PROM contents can not be altered. The MRV11-BA UVPROM is also programmed by special equipment. but its contents can subsequently be erased by exposure to UV light, effectively clearing the contents in preparation for re-programming with new data.

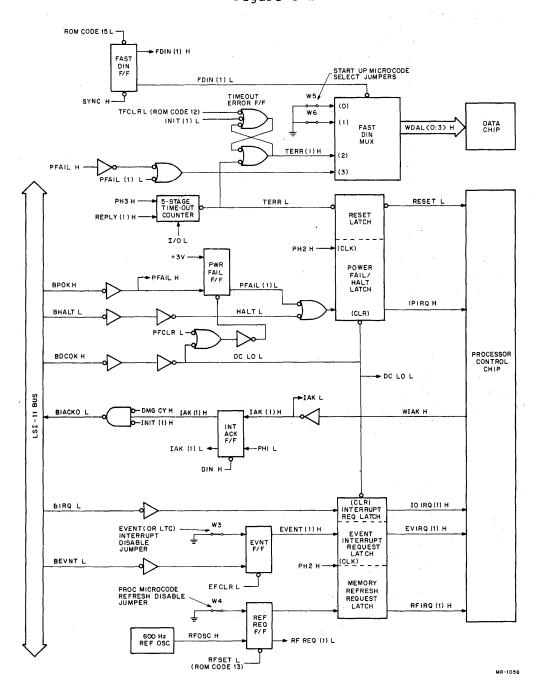

- 2.2.2 Dynamic Memory Refreshing Three techniques are available to satisfy the requirement for dynamic memory refreshing. These three techniques are:

- 1. Processor Controlled Refresh

- 2. Direct Memory Access Refresh

- 3. Distributed Refresh

Processor Controlled Refresh is a feature available on the M7264 LSI-11 processor module. This refresh mode is normally disabled, but can be enabled by removing the appropriate jumper on the module. When enabled, a 600 Hz oscillator causes an internal interrupt. This interrupt initiates the execution of a microprogrammed routine which refreshes all dynamic memory devices used in the system. The refresh routine performs 64 BSYNC/BDIN cycles with BREF L asserted, occupying the system bus for about 130 microseconds. When processor-controlled refresh is employed, all dynamic memory mocules should have their Reply During Refresh options disabled, except for the memory module located farthest from the processor. This assures that the longest bus delays will be compensated for during execution of the refresh microprogram. Note that this form of refresh is not recommended for systems utilizing lengthy microprograms.

Direct Memory Access Refresh is performed by a DMA device and relieves the processor of refresh responsibility. Examples of DMA refresh are the REV11-A and REV11-C modules. The DMA refresh technique differs from the processor-controlled method in that the memory modules are refreshed one row at a time instead of all rows at once. Therefore the DMA device controls the system bus for purposes of refresh for only 1.3 microseconds at a time, thus eliminating the 130 microsecond dead time inherent in the former method. Any user-designed DMA device may also perform refreshing as long as proper sequencing and timing assure that each row of memory is refreshed at least once each 2 milliseconds or less.

Distributed Refresh is the technique used by the MSV11-CD memory module. This module is equipped with timing and sequencing circuitry which performs refreshing for its own memory devices. It refreshes one row at a time every 25 microseconds and isolates itself from the system during each row refresh. If the LSI-11 processor, or DMA device, requires a memory access when the module is refreshing a row, the memory module merely delays its response by returning the BRPLY L signal after the row refresh is completed. The relatively short, occasional delays that occur with this technique are compatible with the essentially asynchronous system bus data transactions.

The memory component of a specific LSI-11 machine may be composed of more than one memory type to satisfy user requirements.

2.2.2.3 Magnetic Memory - Magnetic Memory is non-volatile, so it does not require refreshing. Therefore, memory contents stored in magnetic core are not lost during a power failure. Magnetic memory can maintain the information of a partially-executed program or routine when power is removed so that the routine may continue to completion when power is restored. A Power-Fail routine (which is initiated by the processor Power-Fail trap) must save all volatile machine states (e.g., the General Purpose Registers) in the magnetic portion of memory before power goes down (BDCOK H goes passive).

## 2.2.3 Input/Output Devices

The Input/Output devices connected to the LSI-ll system bus provide a means for interfacing control and data information between the LSI-ll machine and the outside world. An example of an I/O device which bidirectionally passes both data and control is the DLV11 serial line unit which connects to the console terminal.

2.2.3.1 Device Address Format - All Input/Output device locations on the LSI-ll system bus are accessed in the same manner as memory. Normally, each I/O device has four sequentially-numbered word locations associated with it. These four locations provide for both control and data transfer between the processor and I/O device according to the following convention:

| XXXXX0 | Receive Control Status Register  | (RCSR) |

|--------|----------------------------------|--------|

| XXXXX2 | Receive Buffer                   | (RBUF) |

| XXXXX4 | Transmit Control Status Register | (XCSR) |

| XXXXX6 | Transmit Buffer                  | (XBUF) |

The Receive Buffer (RBUF) holds data which has been received from the I/O device and which can be transferred to the processor or to memory. The Receive Control Status Register (RCSR) contains control flags related to the device receive function. The Transmit Buffer (XBUF) holds data which has been transferred to the I/O device for presentation to the outside world. The Transmit Control Status Register (XCSR) contains control flags related to the device transmit function.

- 2.2.3.2 Enabling Device Interrupts Input/Output devices which support interrupt-driven I/O transactions are equipped with an interrupt-enabling mechanism which must be explicitly set by the processor before the device can initiate an interrupt. The interrupt-enabling mechanism is reset or disabled at Power-Up time by the system initialization signal BINIT L.

- 2.2.3.3 DMA Transfer Restrictions A Direct Memory Access (DMA) data transfer is accomplished by the DMA device becoming master of the system bus (which suspends LSI-ll processor I/O operations). If the processor is responsible for dynamic refresh, only single byte or single word transfers are allowed to give the processor opportunity to execute a memory refresh routine. A long burst of DMA transfer could cause the refresh period to delay beyond the 2 millisecond maximum allowable time. If Processor-Controlled Refresh is not utilized, restrictions on DMA transfer are eliminated.

# 2.2.4 The LSI-ll Processor

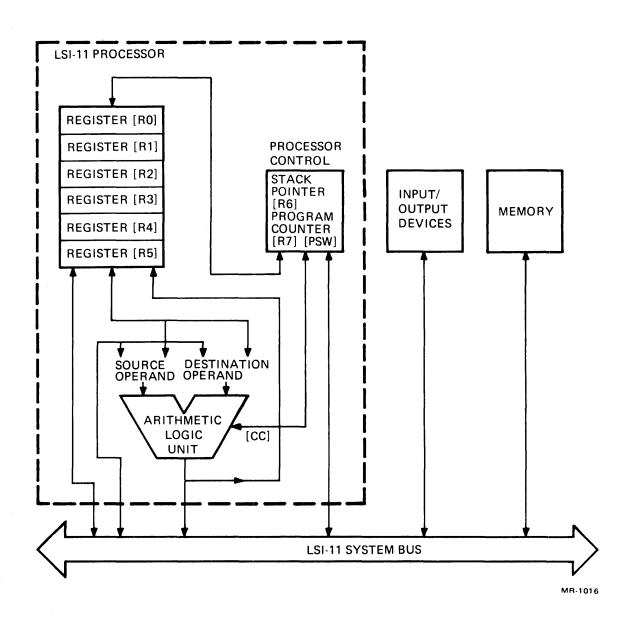

The LSI-11 Processor module which appears in Figure 2.1 is presented with greater internal detail in Figure 2.3. The three functional areas are:

- 1. The Arithmetic Logic Unit

- 2. The general Purpose Registers

- 3. The Processor Control

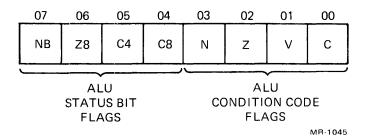

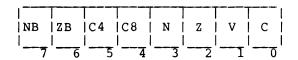

- 2.2.4.1 Arithmetic Logic Unit The Arithmetic Logic Unit (ALU) performs the operations required for the machine instruction set. Arithmetic operations employ two's complement number representation in fixed point format. With the addition of the KEV11 EIS/FIS MICROM (Extended/Floating Instruction Set), floating point arithmetic operations are also performed. Arithmetic and logical operations are executed on both byte and word data. The results of ALU operations are monitored by four Condition Code Flags (N,Z,V,C) which are part of the Processor Status Word (PSW) register. The source and destination operands which constitute the inputs to the ALU may be located in General Purpose Registers, Memory, or Input/Output device registers.

- 2.2.4.2 General Purpose Registers The General Purpose Registers are located within the Processor and thus their contents are accessed without the use of a system bus operation. The registers may contain data or address information. Registers R6 and R7 are dedicated to Stack Pointer (SP) and Program Counter (PC) use, respectively, and are therefore associated with Processor Control. Both byte and word addressing is supported for registers R0 through R5. Because of their dedicated application, registers R6 and R7 allow word addressing only.

LSI-11 Processor Detail

Figure 2-3

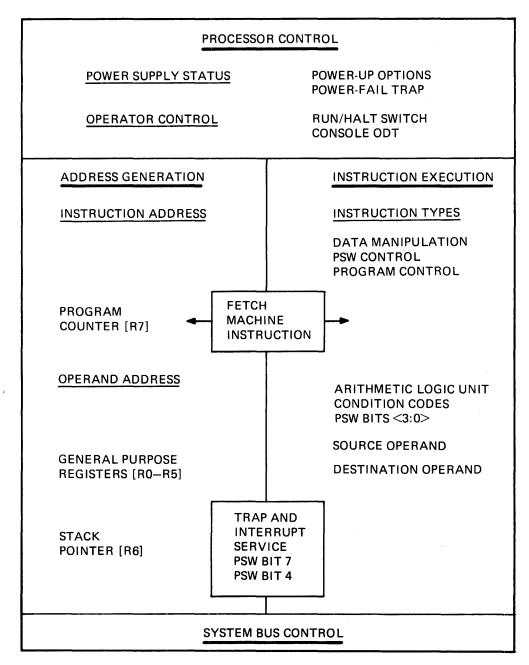

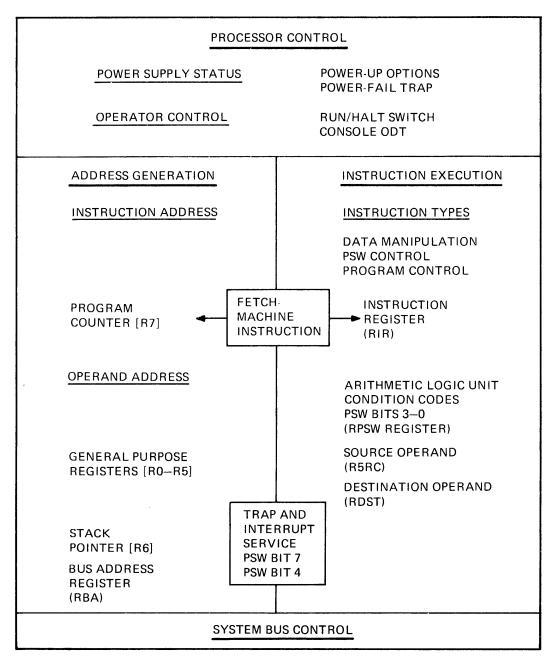

2.2.4.3 Processor Control - There are four main areas into which all functions performed by the Processor Control may be divided. These four areas are:

- Processor Control (Overall Control)

- 2. Machine Instruction Execution

- Address Generation

- 4. System Bus Control

These four areas and their associated processor resources are illustrated in Figure 2-4. Overall Processor Control is determined by (1) the status of the system power supply and (2) the operator.

In the PDP-11/03, the processor is informed of power supply status by means of the BDCOK H and BPOK H signals (see Section 2.2.1.3). The processor will cause either a Power-Up or a Power-Fail operation to be performed in response to the status of these signals. BDCOK H and BPOK H originate in the H780 power supply and their exact sequence and timing details are contained in The Microcomputer Handbook. In general, BPOK H is the last signal to be asserted in a Power-Up sequence and the first signal to go passive in a Power-Fail sequence. When BDCOK H is passive, indicating the lowest state of the system power supply, it asserts BINIT L and forces the microprocessor Control chip to the Reset state. When the processor is in the Run state, the change of BPOK H from active to passive will cause a Power-Fail trap to be performed. The Power-Up mode is determined via jumper configuration on the processor module. The means by which the Processor interprets the jumper configuration and the power supply status signals are further detailed in the control flow diagram of Figure 2.16-2 in the Machine Operation section (Section 2.3).

Operator Control over the LSI-ll processor is achieved through two means: (1) the state of the front panel Run/Halt switch and (2) Console ODT. Placing the Run/Halt switch in the Halt position causes a Halt interrupt which passes control to the microprogrammed ODT routine. Once the processor has entered the Console ODT/Halt state, the Run state may be reentered by operator execution of the "P" or "G" commands. When the Run/Halt switch is in the Halt position and the "P" command is repeatedly issued, single-step program execution is achieved. A complete description of Console ODT is in The Microcomputer Handbook.

As shown in the Figure 2.4, the contents of the LSI-ll Processor Status Word (PSW) register have been divided up and allotted to two areas. The four ALU condition code flags appear in the Machine Instruction execute sub-area and the Trace Trap and External Interrupt Enable flags appear in the Trap & Interrupt Service sub-area. The complete PSW, which the operator may access by either the "RS" ("\$S") Console ODT command or under program control via the MFPS or MTPS machine instruction, is illustrated in Figure 2.5. The four lower flags are conditionally set as a result of any processor operation which manipulates data in the ALU or moves data within the LSI-ll machine.

## Processor Control Functions Figure 2-4

## Processor Status Word (PSW) Figure 2-5

| 07 | 05       | 04 | 03 | 02 | 01 | 00 |  |

|----|----------|----|----|----|----|----|--|

| Р  | RESERVED | Т  | N  | Z  | ٧  | С  |  |

- P: EXTERNAL INTERRUPT ENABLE

- T: TRACE TRAP ENABLE

- N: NEGATIVE CONDITION CODE

- Z: ZERO CONDITION CODE

- V: OVERFLOW CONDITION CODE

- C: CARRY CONDITION CODE

Data moved between a memory location and a device register will affect the condition codes as will the execution of an arithmetic or logical operation. The specific condition code functions for each machine instruction are found in The Microcomputer Handbook. The Machine Instruction Execute area performs the operations dictated by the fetched machine instruction. All members of the LSI-11 Machine Instruction Set may be classified in the three following groups:

- 1. Data Manipulation Instructions

- 2. Program Control Instructions

- 3. Processor Status Word Control Instructions

Data Manipulation instructions include all single and double operand instructions with the exception of the PSW operators MFPS and MTPS. All instructions in this group set or reset the ALU condition codes as a result of the operation performed. None of the instructions in this group can change the processor priority, PSW BIT 7, or the trace trap enable, PSW BIT 4.

These instructions are listed below.

Single Operand

General: CLR(B), COM(B), INC(B), DEC(B), NEG(B), TST(B) Shift & Rotate: ASR(B), ASL(B), ROR(B), ROL(B), SWAB Multiple Precision: ADC(B), SBC(B), SXT

Double Operand

General: MOV(B), CMP(B), ADD, SUB Logical: BIT(B), BIC(B), BIS(B), XOR

The KEV11 EIS/FIS (Extended/Floating Instruction Set) adds four fixed point and four floating point instructions to the group.

Extended Fixed Point: MUL, DIV, ASH, ASCH

Floating Point: FADD, FSUB, FMUL, FDIV

The Program Control Instructions are divided into two sub-groups, depending on whether the PSW contents are affected. The execution by the processor of any instruction in the first sub-group has no effect on the PSW contents. This sub-group includes all Branch, Jump & Subroutine, and Miscellaneous instructions.

Branch: BR, BNE, BEQ, BPL, BMI, BVC, BVS, BCC, BCS

Signed Conditional Branch: BGE, BLT, BGT, BLE

Unsigned Conditional Branch: BHI, BLOS, BHIS, BLO

Jump & Subroutine: JMP, JSR, RTS

Miscellaneous: HALT, WAIT, RESET, SOB

The second sub-group of Program Control instructions is executed in the Trap & Interrupt Service area shown in Figure 2.4. These instructions can control every working bit in the PSW by moving a byte to the PSW register from a vector location or from the stack.

Trap & Interrupt: EMT, TRAP, BPT, IOT, RTI, RTT

Processor Status Word Control Instructions exert direct control over the PSW register contents. The condition code operators may be used to set or clear any combination of the condition code flags. The NOP instruction is also included here.

Condition Code Operators

Clear: CLC, CLV, CLZ, CLN, CCC Set: SET, SEV, SEZ, SEN, SCC NOP

Two single operand instructions belong to this group because their execution affects the PSW register contents.

Processor Status Word Operators

MFPS MTPS

The MFPS (Move byte From Processor Status word) instruction transfers the PSW register contents to the destination contained in the instruction. If the destination is mode 0, PSW BIT 7 is sign extended through the upper byte of the register. However, the movement of the PSW contents through the processor to the destination will modify the information in the PSW register according to the following rules.

N = Set if PSW Bit <7> = 1; cleared otherwise Z = Set if PSW<7:0> = 0; cleared otherwise

V = cleared

C = not affected

The MTPS (Move byte To Processor Status word) instruction transfers the 8 bits of the source operand to the PSW register. All working bits may be set or cleared, except the Trace Trap Enable (PSW Bit <4>) which may only be cleared.

The LSI-11 machine instruction set contains four additional reserved instruction groups which have no assigned mnemonic: 21R, 220-227, 075040-075777, 076000-076777.

The 21R opcode (where R is a 0 - 7) causes the contents of the internal temporary registers to be transferred to consecutive locations pointed to by the contents of register R. Register R is not restored at the end of execution. The internal registers accessed by this instruction are illustrated in Figure 2.6, which also shows their relationship to the Processor Control Functions. This instruction is used for diagnostic purposes only and belongs to the Data Manipluation group listed above.

## Processor Control Functions (With Internal Registers) $\mbox{ Figure 2-6}$

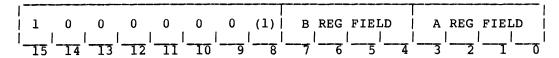

Machine-level execution of instructions in the range of 220-227 causes control to be transferred to the microinstruction located at microaddress 3000 (in user control store). If control store is not present (or if it is disabled) a reserved instruction trap through memory location 10 will occur. (See the Microcomputer Handbook for a description of illegal instruction traps).

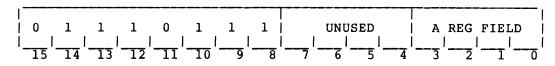

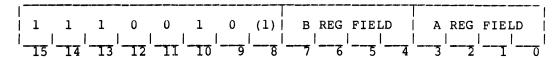

Instructions in the range 075040 through 075777 cause control to be transferred to the microinstruction located at microaddress 3003 (in user control store). If control store is not present (or if it is disabled), a reserved instruction trap through memory location 10 will occur.