# DTR01/DR01 Channel Interface Subsystem Technical Manual

digital equipment corporation • marlboro, massachusetts

# DTR01/DR01 Channel Interface Subsystem Technical Manual

digital equipment corporation • marlboro, massachusetts

#### Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

## This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

|         | VMS          | IAS          |

11/78-38

## CONTENTS

Page

## CHAPTER 1 INTRODUCTION

| 1.1       | PURPOSE AND USE                                      |

|-----------|------------------------------------------------------|

| 1.2       | GENERAL DESCRIPTION                                  |

| 1.3       | FEATURES AND CAPABILITIES1-2                         |

| 1.4       | SPECIFICATIONS1-3                                    |

| 1.4.1     | Mechanical Specifications1-3                         |

| 1.4.2     | Electrical Specifications1-4                         |

| 1.4.3     | Operational Specifications1-5                        |

| 1.4.4     | Environmental Operating Specifications1-5            |

| CHAPTER 2 | SITE PREPARATION AND PLANNING                        |

| 2.1       | SITE CONSIDERATIONS                                  |

| 2.2       | USER INTERFACE CABLING2-1                            |

| 2.3       | SYSTEM CONFIGURATION GUIDELINES2-4                   |

| CHAPTER 3 | INSTALLATION                                         |

| 3.1       | DTR01 INSTALLATION PROCEDURES                        |

| 3.2       | RH20 CLOCK DESKEW PROCEDURE                          |

| 3.3       | RH20/CHANNEL CONTROL LOGIC DIAGNOSTICS               |

| 3.4       | USER INTERFACE CABLING                               |

| 3.5       | GROUNDING                                            |

| 3.6       | POWER UP UNIT                                        |

| 3.7       | DEVICE NUMBER SELECTION                              |

| 3.8       | MAXIMUM TRANSFER RATE ADJUSTMENT                     |

| 3.9       | M5903 ENABLE SWITCHES                                |

| 3.10      | CHECKOUT AND ACCEPTANCE                              |

| CHAPTER 4 | OPERATION/PROGRAMMING                                |

| 4.1       | DTR01 OPERATION4-1                                   |

| 4.1.1     | Single-Word Transfer – Write4-1                      |

| 4.1.2     | Single-Word Transfer – Read4-1                       |

| 4.2       | PROGRAMMING                                          |

| 4.2.1     | Communication Between the DTR01 and the KL10-B, C, D |

|           | or E Processor                                       |

iii

## CONTENTS (Cont)

| 4.2.1.1    | Loading DR01/DTR01 External Registers                      |

|------------|------------------------------------------------------------|

| 4.2.1.2    | DATAO                                                      |

| 4.2.1.3    | DATAI                                                      |

| 4.2.2      | Programmable Registers in DR01-CL Channel Interface Unit   |

| 4.2.2.1    | Control and Status 1 Register (RHCS1)                      |

| 4.2.2.2    | Interface Status Register (RHIS) – REG 1                   |

| 4.2.2.3    | Input Buffer Register (RHIB) – REG 2                       |

| 4.2.2.4    | Attention Summary Register (RHAS) – REG 4                  |

| 4.2.2.5    | User Function and Status Register (RHFS) – REG 5           |

| 4.2.2.6    | Drive Type Register (RHDT) – REG 6                         |

| 4.2.2.7    | Output Buffer Register (RHB) – REG 7                       |

| 4.2.3      | Link Operation                                             |

| 4.2.3.1    | DR01-C/RH20 Registers Link Configuration4-12               |

| 4.2.3.2    | DR01-C/DR11-B Registers Link Configuration                 |

| 1.2.2.2    |                                                            |

| CHAPTER 5  | TECHNICAL DESCRIPTION                                      |

| CHAI IER J | TECHNICAL DESCRIPTION                                      |

| 5.1        | SYSTEM DESCRIPTION                                         |

| 5.2        | DATA TRANSFERS                                             |

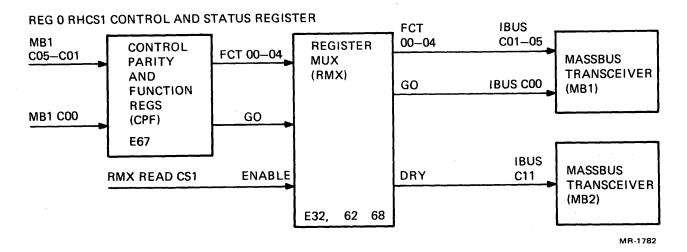

| 5.2.1      | REG 0 (RHCS1) Control and Status Register Signal Flow      |

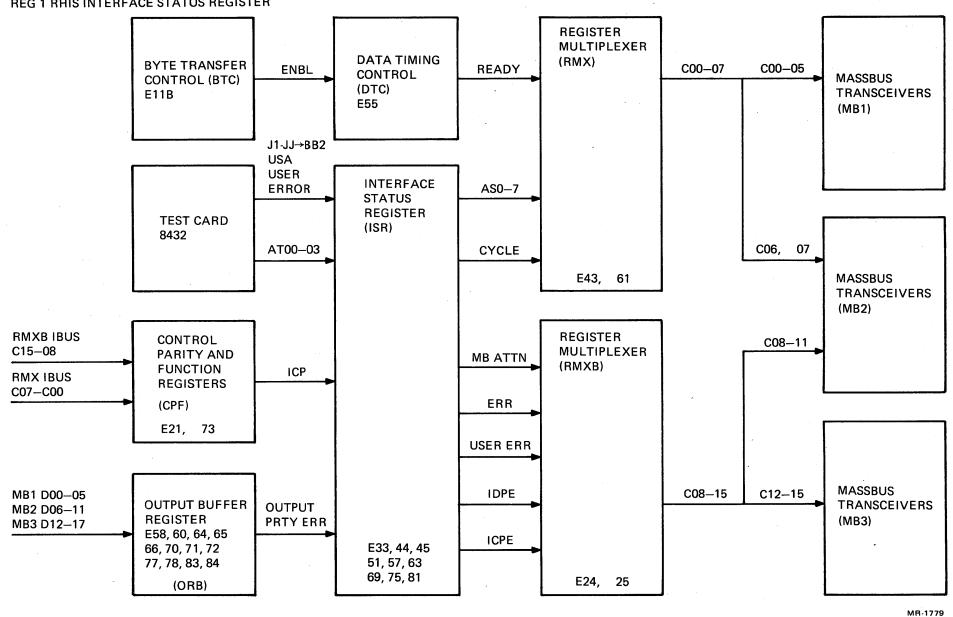

| 5.2.2      | REG 1 (RHIS) Interface Status Register Signal Flow         |

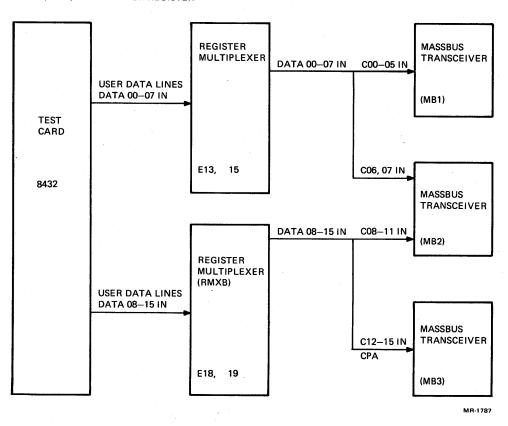

| 5.2.3      | REG 2 (RHIB) Input Buffer Register Signal Flow             |

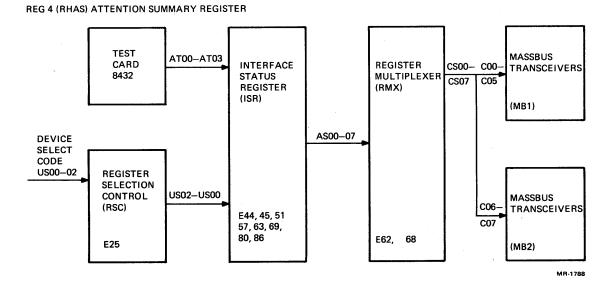

| 5.2.4      | REG 4 (RHAS) Attention Summary Register Signal Flow        |

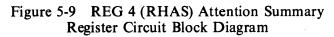

| 5.2.5      | REG 5 (RHFS) User Function and Status Register Signal Flow |

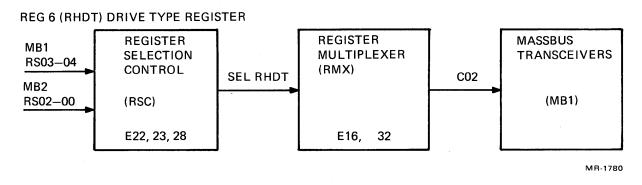

| 5.2.6      | REG 6 (RHDT) Drive Type Register Signal Flow               |

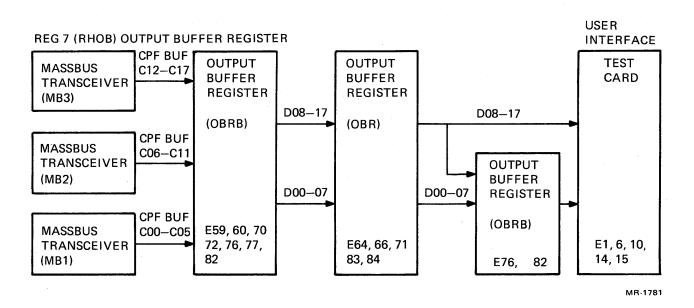

| 5.2.7      | REG 7 (RHOB) Output Buffer Register Signal Flow            |

| 5.3        | LINK OPERATION                                             |

| 5.5        | LINK OFERATION                                             |

| CHAPTER 6  | PREVENTIVE MAINTENANCE                                     |

| CHAFTERU   | FREVENTIVE MAINTENANCE                                     |

| 6.1        | GENERAL                                                    |

| 6.2        | HIGH PERFORMANCE CHECKOUT                                  |

| 0.2        | HIGH PERFORMANCE CHECKUUT0-2                               |

| CHAPTER 7  | SERVICE                                                    |

|            | SERVICE                                                    |

| 7.1        | GENERAL                                                    |

| 7.2        | CORRECTIVE MAINTENANCE                                     |

| 1.4        |                                                            |

| APPENDIX A | DTR01 INSTALLATION CONSIDERATION                           |

|            |                                                            |

| A.1        | POST INSTALLATION CONSIDERATIONS                           |

| <b>A.I</b> | rosi installation considerationsA-I                        |

## CONTENTS (Cont)

## APPENDIX B LINKING PROCEDURE

| <b>B</b> .1 | DR01/DR11-B LINKING PROCEDURE | 3-1         |

|-------------|-------------------------------|-------------|

| B.2         | DR01/DR01 LINKING PROCEDURE   | <b>3-</b> 2 |

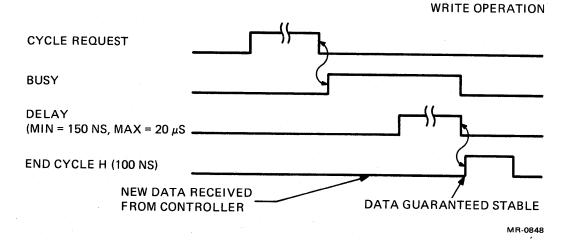

### APPENDIX C USER INTERFACE SPECIFICATION

| C.1     | USER INPUT/OUTPUT SIGNALS | C-1 |

|---------|---------------------------|-----|

| C.1.1   | Signals List              | C-1 |

| C.1.2   | Timing Considerations     | C-1 |

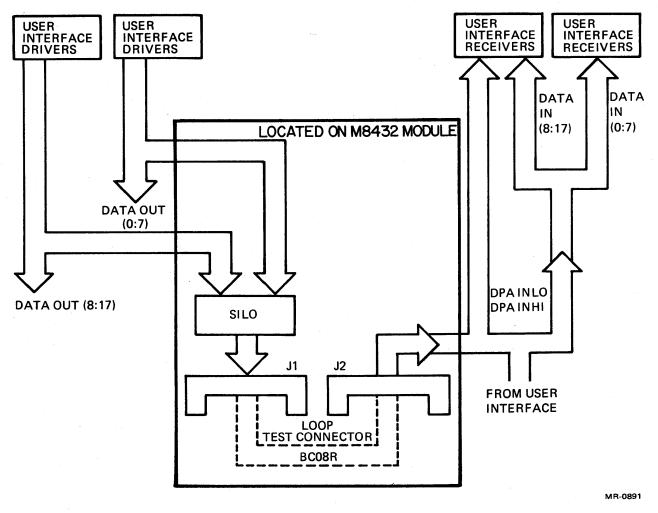

| C.1.2.1 | Read Operation            | C-1 |

| C.1.2.2 | Write Operation           |     |

## FIGURES

## Figure No.

,

#### Title

## Page

| 1-1  | Possible DTR01 Subsystem Configurations                      | 1-1  |

|------|--------------------------------------------------------------|------|

| 2-1  | DR01 User Interface Connector Slot View Shown from Backplane | 2-1  |

| 2-2  | Module M9760-YA                                              | 2-5  |

| 2-3  | DTR01 Maximum and Minimum Configuration                      |      |

| 3-1  | Massbus Cabling                                              | 3-1  |

| 3-2  | 25 MHz KL10-B, C, D or E System SCLK Setting                 |      |

| 4-1  | Communications Between DTR01 and KL10-B, C, D or E Processor | 4-4  |

| 4-2  | DATAO External Register                                      | 4-5  |

| 4-3  | DATAI Bit Format                                             | 4-5  |

| 4-4  | RHCS1 (REG 0) Bit Map                                        | 4-7  |

| 4-5  | RHIS (REG 1) Bit Map                                         | 4-7  |

| 4-6  | RHIB (REG 2) Bit Map                                         | 4-9  |

| 4-7  | RHAS (REG 4) Bit Map                                         | 4-9  |

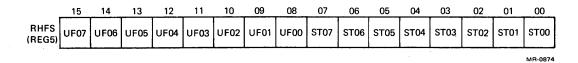

| 4-8  | RHFS (REG 5) Bit Map                                         | 4-11 |

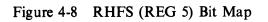

| 4-9  | RHOB (REG 7) Bit Map                                         | 4-11 |

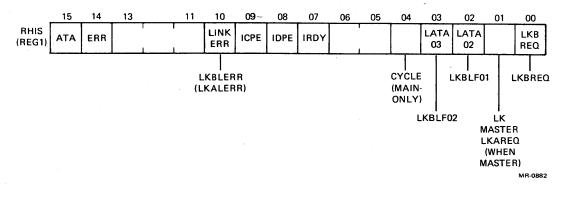

| 4-10 | RHIS (REG 1) Link A.                                         | 4-13 |

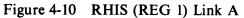

| 4-11 | RHFS (REG 5) Link A                                          | 4-13 |

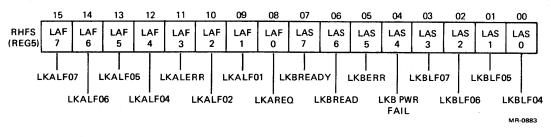

| 4-12 | RHIS (REG 1) Link B                                          | 4-16 |

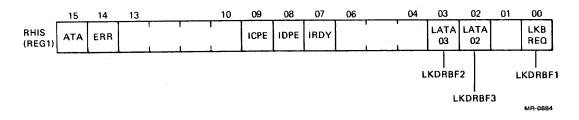

| 4-13 | RHFS (REG 5) Link B                                          | 4-16 |

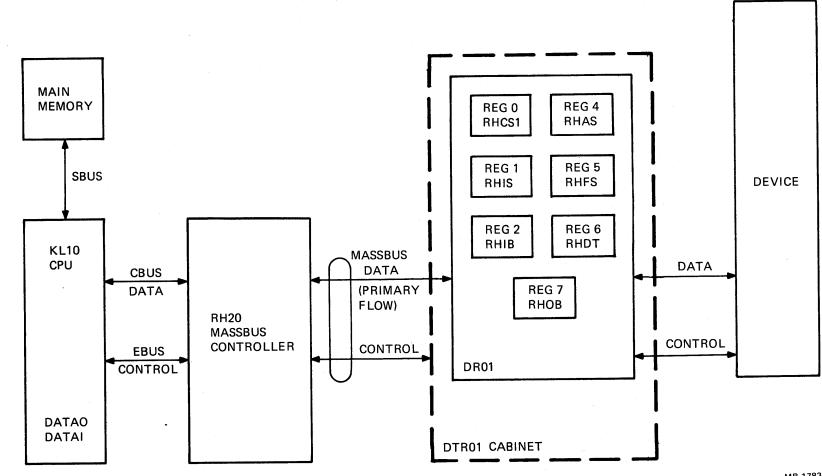

| 5-1  | A Typical DTR01 System                                       |      |

| 5-2  | Communication Between DTR01 and K L10-B, C, D or E Processor |      |

## **FIGURES**

## Figure No.

## Title

## Page

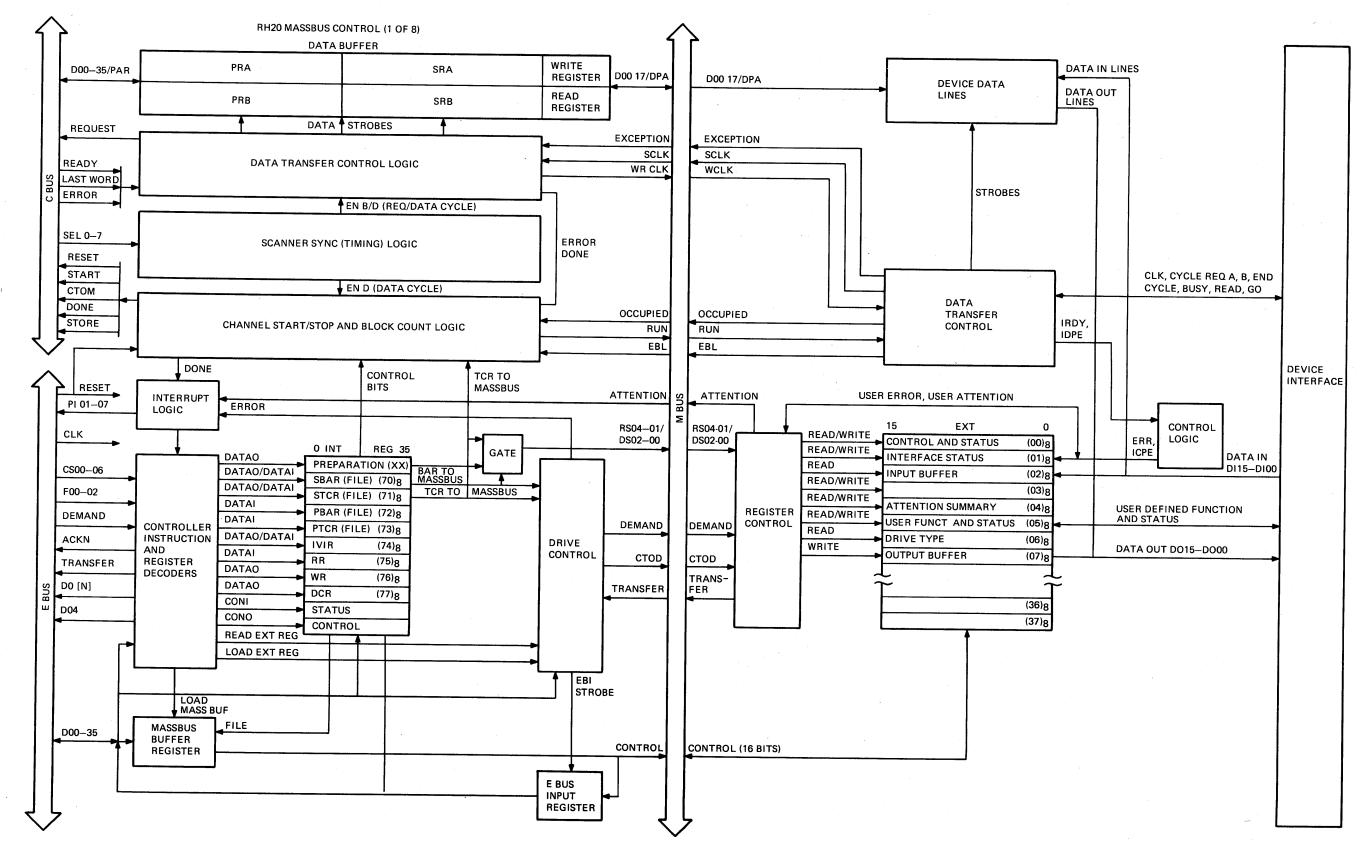

| 5-3  | DTR01 Subsystem Data Flow Block Diagram                              | 5-4  |

|------|----------------------------------------------------------------------|------|

| 5-4  | REG 0 (RHCS1) Control and Status Register Circuit Block Diagram      |      |

| 5-5  | REG 1 (RHIS) Interface Status Register Circuit Block Diagram         | 5-6  |

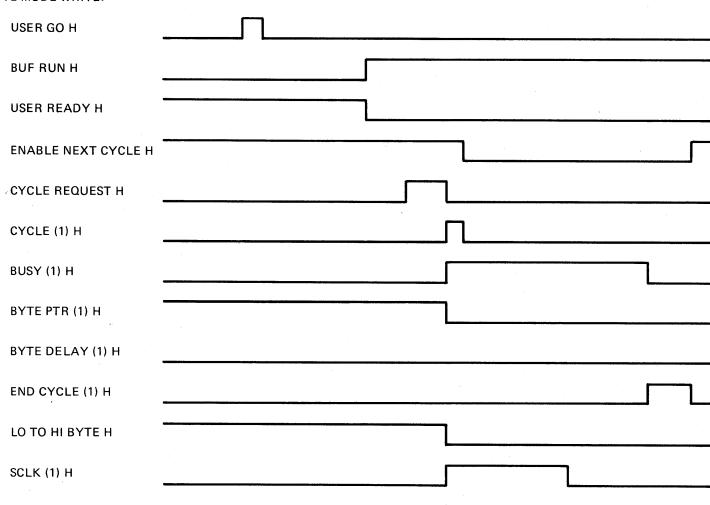

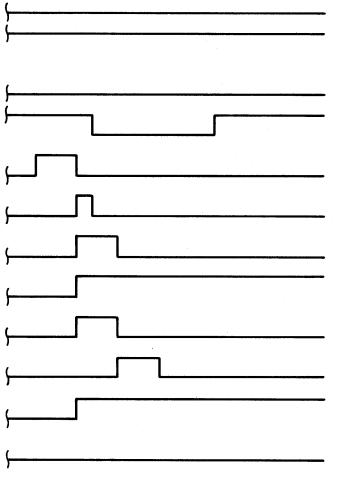

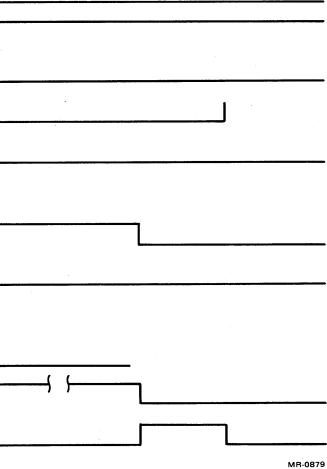

| 5-6  | DTR01 Timing                                                         |      |

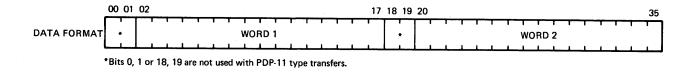

| 5-7  | Data Format                                                          |      |

| 5-8  | REG 2 (RHIB) Input Buffer Register Circuit Block Diagram             | 5-10 |

| 5-9  | REG 4 (RHAS) Attention Summary Register Circuit Block Diagram        |      |

| 5-10 | REG 5 (RHFS) User Function and Status Register Circuit Block Diagram |      |

| 5-11 | REG 6 (RHDT) Drive Type Register Circuit Block Diagram               | 5-13 |

| 5-12 | REG 7 (RHOB) Output Buffer Register Circuit Block Diagram            |      |

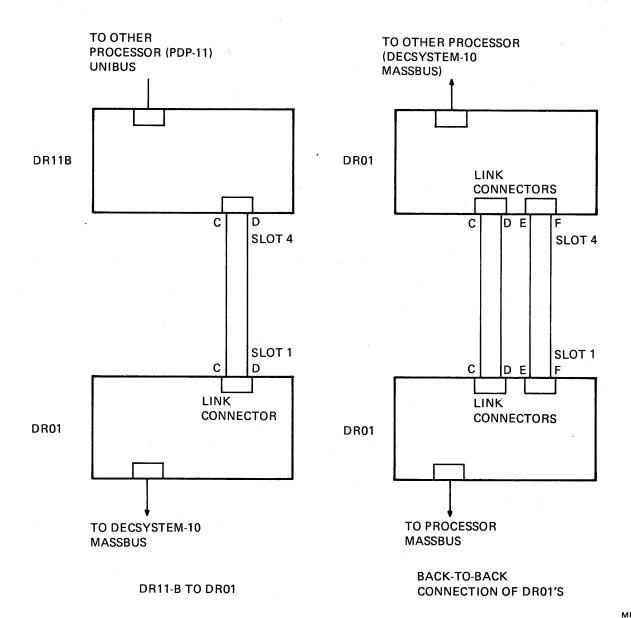

| 5-13 | DTR01 Link Connectors                                                |      |

| 5-14 | DTR01 Back-to-Back Signal Connections                                |      |

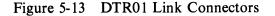

| 7-1  | M8432 Buffer/Test Module Block Diagram                               |      |

| C-1  | Read and Write Timing Diagrams                                       |      |

## **TABLES**

| Table No. | Title                                     | Page |

|-----------|-------------------------------------------|------|

| 1-1       | Electrical Specifications                 | 1-4  |

| 2-1       | Interface Signal Pin Assignments          | 2-2  |

| 4-1       | ATA Bit Status                            |      |

| 5-1       | DR01 to DR01 Signal Connections           | 5-16 |

| 5-2       | DR11-B to DR01 Signal Connections         |      |

| 6-1       | Left Half Switches – Standard Definition  | 6-1  |

| 6-2       | Right Half Switches – Standard Definition | 6-2  |

| 6-3       | Command Data Commands                     |      |

| C-1       | User Input Signals                        | C-2  |

| C-2       | User Output Signals                       |      |

|           |                                           |      |

## CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE AND USE

The DTR01 is a channel port system which provides a general-purpose access to the KL10-B, C, D or E main memory unit via a user high-speed port interface.

The DTR01 subsystem enables a user interface/device to perform high-speed block transfers to or from the system's main memory unit via the mass storage bus and appropriate RH20 controller. Although the maximum subsystem rate within a block is one megabyte, the transfer rate is primarily determined by the user interface. Therefore, an adjustment for limiting the maximum transfer rate of the DR01 has been provided so that it will not exceed the bandwidth of the system.

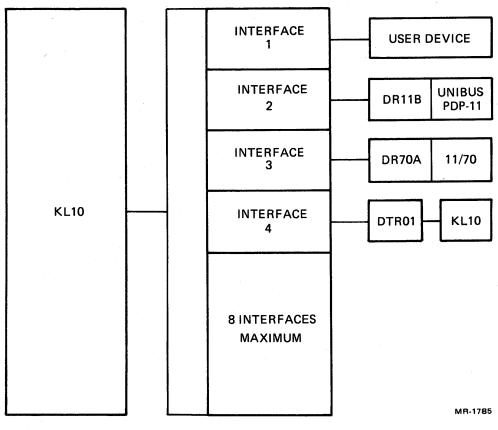

The DR01-C and DTR01 subsystems can also be used to establish a high-speed interprocessor link between a KL10-B, C, D or E and another KL10-B, C, D or E, a PDP-11, or a PDP-11/70. (See Figure 1-1.)

#### **1.2 GENERAL DESCRIPTION**

Communication and control between the DTR01 subsystem and the host processor is implemented with seven programmable registers located in each DR01-CL. Communication and control of the user interface/device is implemented via 8 status bits, 8 user function bits, 4 attention bits, and 1 user error bit along with 18 separate data in and out lines plus optional parity.

#### **1.3 FEATURES AND CAPABILITIES**

The DTR01 provides the following features.

- Performs high-speed block transfers (block can be any size to the maximum amount of core in the system) between main memory and user devices.

- Provides a high-speed channel interface with access to KL10-B, C, D or E main memory unit.

- Establishes high-speed interprocessor links between separate computer systems as follows.

KL10-B, C, D or E to KL10-B, C, D or E

KL10-B, C, D or E to Unibus PDP-11 system

KL10-B, C, D or E to PDP-11/70 system

- Currently provides an interface from any user device interfaced through a direct memory access device interface (DR11-B) to a PDP-11 Unibus.

- Provides an interface expanded beyond a PDP-11 Unibus direct memory access interface (DR11-B) with the following additional features.

Enables data input and output as either word or byte (switch selectable). Byte data is in the low order bits on 8 lines.

Provides optional parity checking for data transferred with the user device.

Provides for additional user-defined status and function bits.

• A maximum of 8 channel interfaces are available to user devices or computers.\*

The user interface connects to dedicated slots in the DR01-CL interface unit. The user device currently interfaced through the DR11-B to the Unibus can be connected to the DTR01 subsystem with a minimum of changes, since the physical signal pins out of these connector slots are almost identical.

In addition to the standard interface connector, a second expanded interface connector slot is provided in the DR01-CL unit to increase the flexibility of the user interface.

<sup>\*</sup>For link configurations, DR11-Bs or DR70As are not supplied. They are mounted externally in a PDP-11 cabinet or mounting box, not a part of the DTR01 system.

#### **1.4 SPECIFICATIONS**

#### **1.4.1** Mechanical Specifications

There are three configurations of DTR01 Channel Interface Subsystems and two configurations of DR01 Channel Interfaces available. They are as follows.

#### DTR01-AA/AB

| Description | H9502 cabinet containing power control, DR01 mounting box    |

|-------------|--------------------------------------------------------------|

| •           | and DR01-CL logic plus RH20 option set. Contains space for   |

|             | two additional DR01-CL options and cabinet space for two ad- |

|             | ditional DR01 mounting boxes (either DTR01-CC/CD or          |

| ·           | DR01-CA/CB).*                                                |

KL10-B, C, D or E

Dimensions

Prerequisite<sup>†</sup>

(60 in  $\times$  30 in  $\times$  26 in)

204 kg (450 lb)

$152 \text{ cm} \times 76 \text{ cm} \times 66 \text{ cm}$

Weight

#### DTR01-CA/CB

Description

H950 cabinet containing power control, DR01 mounting box, and DR01-CL logic plus RH20 option set. Contains space for two additional DR01-CL options and cabinet space for two additional mounting boxes (either DTR01-CC/CD or DR01-CA/CB).\*

Prerequisite<sup>†</sup>

Dimensions

Weight

159 kg (350 lb)

KL10-B, C, D or E

$175 \text{ cm} \times 48 \text{ cm} \times 68 \text{ cm}$

$(69 \text{ in} \times 19 \text{ in} \times 27 \text{ in})$

#### DTR01-CC/CD (Second System Box)

| Description                | Mounting box containing DR01-CL logic plus RH20 option<br>set. Only one DTR01-CC/CD may be added to a DTR01<br>CA/CB, AA/AB. Contains space for two additional DR01 CL<br>options. |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites <sup>†</sup> | KL10-B, C, D or E and DTR01-CA/CB or AA/AB (space per-<br>mitting)                                                                                                                 |

| Dimensions                 | 27 cm $\times$ 48 cm $\times$ 69 cm<br>(11 in $\times$ 19 in $\times$ 27 in)                                                                                                       |

| Weight                     | 50 kg (110 lb)                                                                                                                                                                     |

\*Only one DTR01-CC/CD mounting box may be added to a DTR01-CA/CB, AA/AB cabinet. † System prerequisite requires the KL10-B, C, D or E CPU to be at revision level 10 or greater.

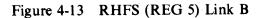

## DR01-CA/CB

| Description  | DR01 mounting box containing DR01-CL logic with space for two additional DR01-CL options. |

|--------------|-------------------------------------------------------------------------------------------|

| Prerequisite | DTR01-CA/CB or AA/AB                                                                      |

| Dimensions   | 27 cm $\times$ 48 cm $\times$ 69 cm<br>(11 in $\times$ 19 in $\times$ 27 in)              |

| Weight       | 50 kg (110 lb)                                                                            |

| DR01-CL      |                                                                                           |

| Description  | Channal interface logic writ                                                              |

| Description   | Channel interface logic unit                                                                                       |

|---------------|--------------------------------------------------------------------------------------------------------------------|

| Prerequisites | DR01-CA/CB, or DTR01-CC/CD, or DTR01-CA/CB or DTR01-AA/AB (space permitting)                                       |

| Dimensions    | $42 \text{ cm} \times 22 \text{ cm} \times 6 \text{ cm}$ $(17 \text{ in} \times 9 \text{ in} \times 3 \text{ in})$ |

| Weight        | 8 kg (18 lb)                                                                                                       |

**1.4.2 Electrical Specifications** Electrical characteristics are provided in Table 1-1.

## 1.4.3 Operational Specifications

The following are the operational characteristics of the DTR01.

| Transfer Rate             | 1 megabyte/second (max.) word mode<br>500 kilobytes/second (max.) byte mode<br>(mode is switch-selectable)      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------|

| Output Levels             | TTL, 30 unit loads max., high = logic 1                                                                         |

| Input Levels              | TTL, 8 unit loads max., high = logic 1                                                                          |

| User Cable or Link Cable* | 9 m (30 ft) max. from user device to DTR01 channel interface                                                    |

| Host Cable*               | BC06S, 30 m (100 ft) max. from RH controller to DTR sub-<br>system                                              |

| Commands                  | Read, Write, and Interface Clear (octal codes 71, 61, and 11 respectively only); all other codes are not valid. |

\*Only standard host 12 m (40 ft) and link 8 m (25 ft) cables will be supplied with the system. If special length cables are required, they must be specified at the time the system is ordered.

| Configuration | Voltage           | Current*    | Frequency   | Power | BTU  |

|---------------|-------------------|-------------|-------------|-------|------|

| DTR01-AA      | 115 Vac ±10%      | 5 A         | 50/60 ±3 Hz | 400 W | 1320 |

| DTR01-AB      | 240 Vac ±10%      | 2.5 A       | 50/60 ±3 Hz | 400 W | 1320 |

| DTR01-CA      | 115 Vac ±10%      | 5 A         | 50/60 ±3 Hz | 400 W | 1320 |

| DTR01-CB      | 240 Vac ±10%      | 2.5 A       | 50/60 ±3 Hz | 400 W | 1320 |

| DTR01-CC      | 115 Vac ±10%      | 4 A         | 50/60 ±3 Hz | 300 W | 990  |

| DTR01-CD      | 230 Vac ±10%      | 2 A         | 50/60 ±3 Hz | 300 W | 990  |

| DR01-CA       | 115 Vac ±10%      | 4 A         | 50/60 ±3 Hz | 300 W | 990  |

| DR01-CB       | 230 Vac ±10%      | 2 A         | 50/60 ±3 Hz | 300 W | 990  |

| DR01-CL       | +5 Vdc<br>-15 Vdc | 10 A<br>1 A |             | 65 W  | 215  |

Table 1-1 Electrical Specifications

Power Connector:

DTR01-CA uses NEMA L5-30P DTR01-CB uses NEMA L6-20P DTR01-AA uses NEMA L5-30P DTR01-AB uses NEMA L6-20P

\*These current values are estimated for the basic option configurations.

### 1.4.4 Environmental Operating Specifications

The following are the environmental operating specifications of the DTR01.

| Temperature | 10 - 40° C (50 - 104° F) max.<br>Temperature change rate is 10° C (18° F) max. per hour. |

|-------------|------------------------------------------------------------------------------------------|

| Humidity    | 10% to 90% (no condensation)                                                             |

| Altitude    | 2 km (8000 ft)                                                                           |

| Atmosphere  | Noncorrosive                                                                             |

| Shock       | 10 G for 10 ms                                                                           |

|             |                                                                                          |

## CHAPTER 2 SITE PREPARATION AND PLANNING

#### 2.1 SITE CONSIDERATIONS

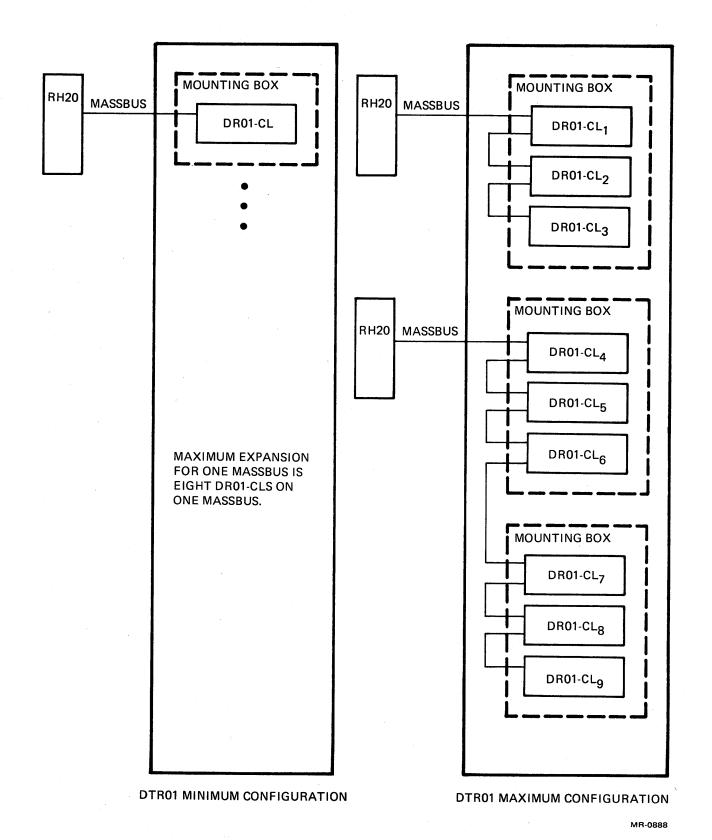

The basic system entry level unit is the DTR01, consisting of a DTR01 cabinet, DR01-CL interface and mounting box and RH20 controller. The DTR01 cabinet can be located within 30 m (100 ft) of the RH20 connected via BC06S cables. If space permits placing a second system box (DTR01-CC/CD) in the DTR01 cabinet, the DTR01 cabinet must be located within 30 m (100 ft) of each RH20 it is connected to via BC06S cables.

The DR01-CA/CB expander interface box is provided for additional system expansion and is mounted in the DTR01 cabinet.

The DR01-CL is the basic channel interface composed of a logic system unit. It provides a user interface access into the system. The DR01-CL can be mounted in either the DTR01 or DR01-CA/CB boxes. (See Paragraph 2.3 for further guidelines.) The DR01-CL is normally located as close as possible to the user interface (9 m or 30 ft maximum cable separation).

#### 2.2 USER INTERFACE CABLING

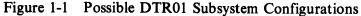

The user interface is generally located external to the DTR01 cabinet and is cabled to the DR01 with two M9760-YA modules or other suitable terminators. A cable from the user interface is normally attached to the two M9760-YA modules which mount in the two double-height connector slots. As an alternative, if the user interface is small enough, it can be located in the same cabinet with the DR01 and the two units may be connected directly with two BC11A cables. However, this configuration is not generally recommended and the user interface must be powered separately. Figure 2-1 shows the location of the two user interface connector slots in the DR01 system unit.

Table 2-1 is a list of user interface signal pin assignments for each of the DR01 connector slots.

|                                |                         |       |            | r    |            |

|--------------------------------|-------------------------|-------|------------|------|------------|

| Signal<br>Source<br>(See Note) | Signal                  | Slot  | Pin        | Zone | Lug<br>Pin |

| TCC                            | DATA 00 OUT H           | D04   | S1         | В    | · S1       |

| TCC                            | DATA 01 OUT H           | D04   | <b>R</b> 1 | B    | R1         |

| TCC                            | DATA 02 OUT H           | D04   | U2         | B    | U2         |

| TCC                            | DATA 03 OUT H           | D04   | <b>P</b> 1 | В    | P1         |

| TCC                            | DATA 04 OUT H           | D04   | T2         | В    | T2         |

| TCC                            | DATA 05 OUT H           | D04   | N1         | B    | N1         |

| TCC                            | DATA 06 OUT H           | D04   | S2         | В    | S2         |

| TCC                            | DATA 07 OUT H           | D04   | M1         | B    | M1         |

| TCC                            | DATA 08 OUT H           | D04   | R2         | В    | R2         |

| TCC                            | DATA 09 OUT H           | D04   | L1         | В    | LI         |

| TCC                            | DATA 10 OUT H           | D04   | P2         | В    | P2         |

| TCC                            | DATA 11 OUT H           | D04   | K1         | В    | K1         |

| TCC                            | DATA 12 OUT H           | D04   | N2         | В    | N2         |

| TCC                            | DATA 13 OUT H           | D04   | M2         | В    | M2         |

| TCC                            | DATA 14 OUT H           | D04   | L2         | В    | L2         |

| TCC                            | DATA 15 OUT H           | D04   | K2         | В    | K2         |

| USA                            | DATA 00 IN H            | C04   | C1         | A    | Cl         |

| USA                            | DATA 01 IN H            | C04   | D1         | A    | D1         |

| USA                            | DATA 02 IN H            | C04   | D2         | A    | D2         |

| USA                            | DATA 03 IN H            | C04   | E1         | A    | E1         |

| USA                            | DATA 04 IN H            | C04   | E2         | A    | E2         |

| USA                            | DATA 05 IN H            | C04   | <b>F</b> 1 | A    | F1         |

| USA                            | DATA 06 IN H            | C04   | F2         | A    | F2         |

| USA                            | DATA 07 IN H            | C04   | H1         | A    | H1         |

| USA                            | DATA 08 IN H            | C04   | H2         | A    | H2         |

| USA                            | DATA 09 IN H            | C04   | J1         | A    | J1         |

| USA                            | DATA 10 IN H            | C04   | J2         | Α    | J2         |

| USA                            | DATA 11 IN H            | C04   | K1         | Α    | K1         |

| USA                            | DATA 12 IN H            | C04   | K2         | Α    | K2         |

| USA                            | DATA 13 IN H            | C04   | L2         | A    | L2         |

| USA                            | DATA 14 IN H            | C04   | M2         | A    | M2         |

| USA                            | DATA 15 IN H            | C04   | N2         | A    | N2         |

| USA                            | CYCLE REQUEST A         | C04   | A1         | A    | A1         |

| USA                            | CYCLE REQUEST B         | D04   | U1         | B    | U1         |

| USA                            | DEVICE STATUS 00        | C04 . | P2         | Α    | P2         |

| USA                            | DEVICE STATUS 01        | C04   | L1         | Α    | L1         |

| USA                            | <b>DEVICE STATUS 02</b> | C04   | R2         | Α    | R2         |

| USB                            | DEVICE STATUS 03        | E04   | N2         | Α    | N2         |

| USB                            | <b>DEVICE STATUS 04</b> | E04   | P2         | Α    | P2         |

| USB                            | DEVICE STATUS 05        | E04   | R2         | A    | R2         |

| USB                            | <b>DEVICE STATUS 06</b> | E04   | D2         | A    | D2         |

| USB                            | DEVICE STATUS 07        | E04   | T2         | Α    | T2         |

| ТСВ                            | FUNCTION BIT 00 ✓       | D04   | E2         | В    | E2         |

| ТСВ                            | FUNCTION BIT 01         | D04   | J2         | В    | J2         |

| ТСВ                            | FUNCTION BIT 02         | D04   | H1         | В    | H1         |

| ТСВ                            | FUNCTION BIT 03         | F04   | H2         | B    | H2         |

| TCB                            | FUNCTION BIT 04         | F04   | N2         | В    | N2         |

| TCB                            | FUNCTION BIT 05         | F04   | K2         | В    | K2         |

| ТСВ                            | FUNCTION BIT 06         | F04   | L2         | В    | L2         |

| TCB                            | FUNCTION BIT 07         | F04   | P2         | В    | P2         |

| DTC                            | READY H                 | D04   | J1         | B    | J1         |

Table 2-1 Interface Signal Pin Assignments

|                                                                                                                                          | I Internet Sign                                                                      |                                                                                                                                                        | r                                                                                                         | ,<br>r                                                                                                                                                            | r                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Signal<br>Source                                                                                                                         | Signal                                                                               | Slot                                                                                                                                                   | Pin                                                                                                       | Zone                                                                                                                                                              | Lug<br>Pin                                                                  |

| FDC                                                                                                                                      | GOH '                                                                                | D04                                                                                                                                                    | <b>V</b> 1                                                                                                | В                                                                                                                                                                 | <b>V</b> 1                                                                  |

| TCC                                                                                                                                      | READH                                                                                | D04                                                                                                                                                    | D2                                                                                                        | B                                                                                                                                                                 | D2                                                                          |

| TCC                                                                                                                                      | END CYCLE H                                                                          | C04                                                                                                                                                    | B1                                                                                                        | Ā                                                                                                                                                                 | B1                                                                          |

| USA                                                                                                                                      | ERROR H                                                                              | C04                                                                                                                                                    | M1                                                                                                        | A                                                                                                                                                                 | M1                                                                          |

| DTC                                                                                                                                      | BUSY H                                                                               | C04                                                                                                                                                    | S2                                                                                                        | A                                                                                                                                                                 | S2                                                                          |

| TCC                                                                                                                                      | INIT H                                                                               | C04                                                                                                                                                    | U2                                                                                                        | A                                                                                                                                                                 | U2                                                                          |

| USB                                                                                                                                      | ATTN BIT 00 H                                                                        | E04                                                                                                                                                    | E2                                                                                                        | A                                                                                                                                                                 | E2                                                                          |

| USB                                                                                                                                      | ATTN BIT 01 H                                                                        | E04                                                                                                                                                    | HI                                                                                                        | Â                                                                                                                                                                 | HI                                                                          |

| USB                                                                                                                                      | ATTN BIT 02 H                                                                        | E04                                                                                                                                                    | J1                                                                                                        | A                                                                                                                                                                 | JI                                                                          |

| USB                                                                                                                                      | ATTN BIT 03 H                                                                        | E04                                                                                                                                                    | <b>K</b> 1                                                                                                | A                                                                                                                                                                 | K1                                                                          |

| USB                                                                                                                                      | DATA 16 IN H                                                                         | E04                                                                                                                                                    | Al                                                                                                        | A                                                                                                                                                                 | Al                                                                          |

| USB                                                                                                                                      | DATA 17 IN H                                                                         | E04                                                                                                                                                    | <b>F</b> 1                                                                                                | Ā                                                                                                                                                                 | F1                                                                          |

| USB                                                                                                                                      | DPA LO IN H                                                                          | E04                                                                                                                                                    | Ci                                                                                                        | Â                                                                                                                                                                 | Ci                                                                          |

| USB                                                                                                                                      | DPA HI IN H                                                                          | E04                                                                                                                                                    | D1                                                                                                        | A                                                                                                                                                                 | D1                                                                          |

| TCB                                                                                                                                      | DATA 16 OUT H                                                                        | E04                                                                                                                                                    | <b>B</b> 1                                                                                                | A                                                                                                                                                                 | B1                                                                          |

| TCB                                                                                                                                      | DATA 17 OUT H                                                                        | F04                                                                                                                                                    | HI                                                                                                        | B                                                                                                                                                                 | HI                                                                          |

| TCB                                                                                                                                      | OUT PARITY HI                                                                        | F04                                                                                                                                                    | J1                                                                                                        | B                                                                                                                                                                 | JI                                                                          |

| TCB                                                                                                                                      | OUT PARITY LO                                                                        | F04                                                                                                                                                    | <b>K</b> 1                                                                                                | B                                                                                                                                                                 | K1                                                                          |

| USB                                                                                                                                      | WORD MODE H                                                                          | E04                                                                                                                                                    | L1                                                                                                        | Ā                                                                                                                                                                 | LI                                                                          |

| USB                                                                                                                                      | INHIBIT INPUT PARITY H                                                               | E04                                                                                                                                                    | E1                                                                                                        | A                                                                                                                                                                 | El                                                                          |

| ISR                                                                                                                                      | ACLOH                                                                                | F04                                                                                                                                                    | S2                                                                                                        | B                                                                                                                                                                 | S2                                                                          |

| CPF                                                                                                                                      | +3 volts                                                                             | E04                                                                                                                                                    | U1                                                                                                        | Ā                                                                                                                                                                 | Ū                                                                           |

| Do not use<br>C04R1<br>C04V1<br>C04T2<br>D04F1<br>D04F2<br>D04H2<br>E04F2<br>E04H2<br>E04F2<br>E04L2<br>E04L2<br>E04L2<br>E04S2<br>E04U2 | Since<br>of wor<br>word<br>transf<br>the las<br>nal ch<br>or mor<br>interfa<br>The u | rd counter, it<br>count of the<br>er end. This ca<br>st word transfo<br>annel signallin<br>re additional I<br>ace.<br>ser's interface<br>nction from o | must rely or<br>KL10-B, C,<br>auses some d<br>erred and the<br>ng transfer e<br>END CYCL<br>e should be o | not contain an<br>the internal of<br>D or E to in<br>lelay to exist be<br>WCOV in the<br>end and results<br>E pulses to the<br>lesigned to pre-<br>e to these add | channel<br>ndicate<br>etween<br>e inter-<br>s in one<br>e user's<br>event a |

| Note:                                                                                                                                    | Signal<br>Source Drawing Refere<br>TCC M8432-0-1 shee                                |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          | USA DR01-0-03 shee                                                                   |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          | USB DR01-0-03 shee                                                                   |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          | TCB M8432-0-1 shee                                                                   |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   | -                                                                           |

|                                                                                                                                          | DTC DR01-0-03 shee                                                                   |                                                                                                                                                        | DTR01_0.2                                                                                                 |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          | FDC DR01-0-03 shee                                                                   |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

| •                                                                                                                                        | ISR M8431-YA-1 sh                                                                    |                                                                                                                                                        | L'I INVI-V-2                                                                                              |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          | CPF M8431-YA-1 sh                                                                    |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

|                                                                                                                                          |                                                                                      |                                                                                                                                                        |                                                                                                           |                                                                                                                                                                   |                                                                             |

,

4

.

Table 2-1

Interface Signal Pin Assignments (Cont)

All output signals are driven with 7437 drivers. These drivers can sink 60 mA in the output low state and can source 1.5 mA in the output high state. This is equivalent to a fan-out of approximately 30 unit loads.

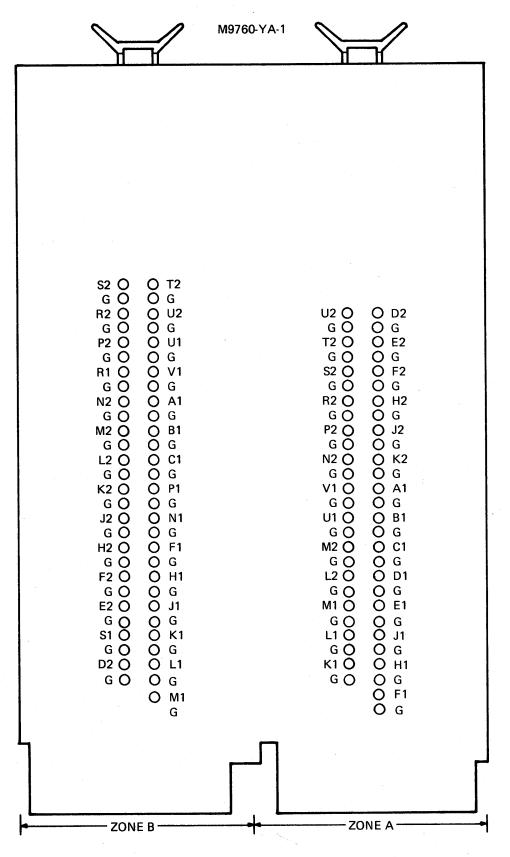

All input signals are received by 7414 Schmitt trigger receivers for noise immunity. The signal inputs are terminated at the receiver input with a 180 ohm resistor to +5 V and a 390 ohm resistor to ground on the M9760-YA module. (See Figure 2-2.) This termination requires a driver in the user interface capable of sinking at least 25 mA. A driver such as the 7437 or 74H40 will satisfy this requirement. If the use of lower powered drivers is desired, the terminators may be removed from the M9760-YA module. However, it is not recommended to use lower power drivers for cable lengths greater than 1.5 m (5 ft).

#### 2.3 SYSTEM CONFIGURATION GUIDELINES

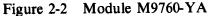

Figure 2-3 provides a graphic description of the system's expansion capability by providing the system minimum and maximum configurations. The maximum configuration rules are listed below.

- 1. Eight DR01-CLs per Massbus (RH20)

- 2. Any RH20 option set used by DR01-CLs cannot be shared with other devices.

- 3. One Massbus per DR01 mounting box

- 4. Two Massbuses per DTR01 cabinet

- 5. Three DR01-CLs per DR01 mounting box

- 6. Three DR01 mounting boxes per cabinet

- 7. One additional (second) DR01 system box per DTR01 cabinet (DTR01-CC/CD). If a second DR01 system box is placed in the DTR01 cabinet, the maximum configuration per cabinet is:

Massbus no. 1 = 3 DR01-CLs Massbus no. 2 = 6 DR01-CLs.

MR-0886

## Figure 2-3 DTR01 Maximum and Minimum Configuration

## CHAPTER 3 INSTALLATION

#### 3.1 DTR01 INSTALLATION PROCEDURES

Verify that the KL10-B, C, D or E CPU in the system is at revision level 10 before proceeding with the installation. Observe the CPU revision sticker on the module enclosure door on the CPU logic.

#### NOTE

## DO NOT proceed with the DTR01 installation if the KL10-B, C, D or E CPU is not at machine level 10.

Install the RH20 option module set into the next available channel backplane slot or another slot if preferred. Refer to the RH20 Massbus Controller Unit Description (EK-RH20-UD) and/or KL10 System Installation Manual.

#### 3.2 RH20 CLOCK DESKEW PROCEDURE

Perform the RH20 clock deskew procedure for the RH20 being installed. (Refer to the KL10 Maintenance Handbook EK-KL10-HB.)

#### 3.3 RH20/CHANNEL CONTROL LOGIC DIAGNOSTICS

Run the following RH20/Channel Control Logic Diagnostics. Refer to diagnostic listing fiche for program and error information.

| DGKBD.A11 | Version 0.10 (or later) |

|-----------|-------------------------|

| DGKBE.A11 | Version 0.10 (or later) |

| DGRHB.A10 | Version 0.11 (or later) |

Upon successfully running the diagnostics above, connect the DTR01 cabinet/DR01-C logic to the RH20 with the supplied BC06S-XX cable. (See Figure 3-1.) Jumper W1 on each H870 (Massbus terminal pack) must be cut for the proper operation of the DR01. The total length of the Massbus cable should not exceed 30 m (100 ft) with BC06S round cable from the CPU.

MR-0889

Figure 3-1 Massbus Cabling

#### 3.4 USER INTERFACE CABLING

The user interface is cabled to the DR01 with the two M9760-YA modules. A cable from the user interface is normally attached to the two M9760-YA modules which mount in the two double-height connector slots.

#### 3.5 GROUNDING

In addition to the ground wires in the user interface cable, the DR01 should be grounded to the user interface through a separate cable. This ground strap provides a low resistance path to ground. Also, the DR01 and the Massbus controller should share a common ground. Using the supplied ground cable, connect the DTR01 cabinet to the host system ground.

#### 3.6 POWER UP UNIT

Plug the unit into the appropriate ac outlet and power up the DTR01 cabinet. Check all logic voltages.

$+5 V \pm 0.25 V$ -15 V  $\pm 0.5 V$

#### **3.7 DEVICE NUMBER SELECTION**

Dual in-line package (DIP) switches, SW1-1, SW1-2, SW1-3 on the DR01 control board (M8431-YA) select the device number of the DR01 on the Massbus. (See Table 2-1.) (Switch in the ON position = 0; SW1-1 is LSB; SW1-3 is MSB.) The rocker switches represent an octal number from 0 to 7. The DR01 is shipped with the switches set for unit 7. Switch SW1-7 indicates byte mode when ON and word mode when OFF. Switch SW1-8 indicates inhibit input parity when ON and enable input parity when OFF.

#### 3.8 MAXIMUM TRANSFER RATE ADJUSTMENT

The DR01 is shipped from the factory with its maximum rate set to  $3.4 \ \mu s$  per 36-bit word. This is equivalent to a high-speed disk such as the RS04. The maximum transfer rate may be increased or decreased as required.

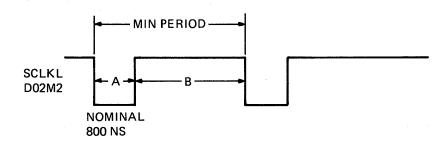

Verify that the sync clock (SCLK) timing is set up properly for the KL10-B, C, D or E version to which it is connected. Using Test 6 of the DFDRA diagnostic and a 1-word transfer, monitor pin D02M2 with an oscilloscope on the DR01-CL backplane. For a 25 MHz\* KL10-B, C, D or E CPU the maximum settings are as follows.

SCLK width = 800 nsSCLK period =  $1.7 \mu \text{s}$

The SCLK width adjustment potentiometer on the M8431-YA module is R3 located front/bottom. The SCLK period potentiometer is R6 located rear/top. Slot A of the module is at the top; Slot F is at the bottom. It may be necessary to limit the maximum transfer rate of the DR01 so that it does not exceed the bandwidth of the system. On heavily loaded systems, problems such as data late errors on other system devices or in the DR01 may occur during peak periods of system operation if the speed is not limited.

If the speed must be limited, first determine the maximum transfer rate allowable.

#### NOTE

Determining the available bandwidth to the DR01 can be a very complex system problem requiring a comprehensive knowledge of the system architecture. If the system bandwidth is not extremely critical, an estimate of the available bandwidth may suffice; however, in critically loaded systems, customers should have the system bandwidth analyzed by DIGITAL personnel.

<sup>\*</sup>For a 30 MHz KL10-B, C, D or E system the same settings are used but the period may be shortened with approval of the factory.

When the available bandwidth has been determined, adjust the DR01 as follows.

- 1. Calculate the reciprocal of the bandwidth to determine the minimum period of the transfer (for example, if the bandwidth is 500 kHz, the minimum period is 2  $\mu$ s).

- 2. Monitor the SCLK L signal located on the DR01 backplane D02M2. Run the bandwidth portion of the DR01 diagnostic DFDRA using Test 6 and a 1-word transfer. The signal in Figure 3-2 should be observed at D02M2.

FOR 25 MHZ KL10 SYSTEM, THE MAXIMUM SETTING IS AS FOLLOWS:

A = 800 NS B = 900 NS PERIOD = 1.7 μS

MR-0890

Figure 3-2 25 MHz KL10-B, C, D or E System SCLK Setting

- 3. The low portion (A) of the SCLK L signal is normally set at 800 ns. This corresponds to the minimum setting of potentiometer R3 which is located at the bottom when DR01 is mounted vertically. Do not adjust R3 unless it is necessary to make the DR01 run slower than the adjustment allowed by potentiometer R6 described in the next step.

- 4. Potentiometer R6 controls the width of the high portion (B) of the SCLK L signal. Potentiometer R6 is at the top when DR01 is mounted vertically. Adjust R6 so that the total width of the low and high portions equals the desired minimum period calculated in step 1. If the range of the R6 adjustment does not allow slowing the DR01 enough, leave R6 at its maximum setting and increase R3 until the desired value is obtained.

#### 3.9 M5903 ENABLE SWITCHES

Each M5903 Massbus transceiver has an enable switch that enables the receivers. The function of these switches is not implemented on the DR01 and the switches should always be set to the ON (up) position.

#### 3.10 CHECKOUT AND ACCEPTANCE

Make sure the BC08R loopback cable is installed between J1 and J2 on the M8432 board and that the user connector modules (M9760-YA boards) have been removed from the DR01-CL logic. Also remove any link cables (i.e., nothing in CDEF01, CDEF04). Load the DTR01 diagnostic, DFDRA.A10 and continue with the DTR01 subsystem checkout. Refer to the DTR01 Checkout/Acceptance Procedure.

## CHAPTER 4 OPERATION/PROGRAMMING

#### 4.1 DTR01 OPERATION

The user must define an operation protocol to be used in communications between the host system and the user's device. The user function, status, and attention bits and also possibly a fixed message size and/or data block size to be transferred should be considered. Once a protocol is defined, the programming of the DTR01 subsystem can be accomplished.

A data transfer can be functionally performed as follows.

- 1. Determine if the DR01 interface is ready.

- 2. Load the user function/status as defined in the protocol.

- 3. Initialize and generate the desired channel transfer command list.

- 4. Initialize and generate the desired data buffer area.

- 5. With the user's program, load the read or write command indirectly via RH20 STCR, REG 40 into the RH20 secondary transfer command register (RHCS1, REG0 bits 00-05).

- 6. Wait for DONE (indicates transfer completed).

- 7. Check status and proceed.

#### 4.1.1 Single-Word Transfer – Write

To transfer a single word of data from the host to the user interface device under program control, load the output buffer, RHOB (REG 7) with the desired data.

#### NOTE

#### This procedure assumes a single-word transfer protocol is defined so that the user interface is assured of taking stable data (i.e., some strobe signal may be provided via a dedicated user function bit).

#### 4.1.2 Single-Word Transfer – Read

To transfer a single word from the user device interface to the host under program control, read the input buffer register, RHIB (REG 2).

#### NOTE

This procedure assumes that the user device will supply the data word stable for the interface to read. Caution must be taken to ensure stable data that is not changing when the program reads it by implementing a handshake protocol possibly with dedicated user function/status bits.

#### 4.2 PROGRAMMING

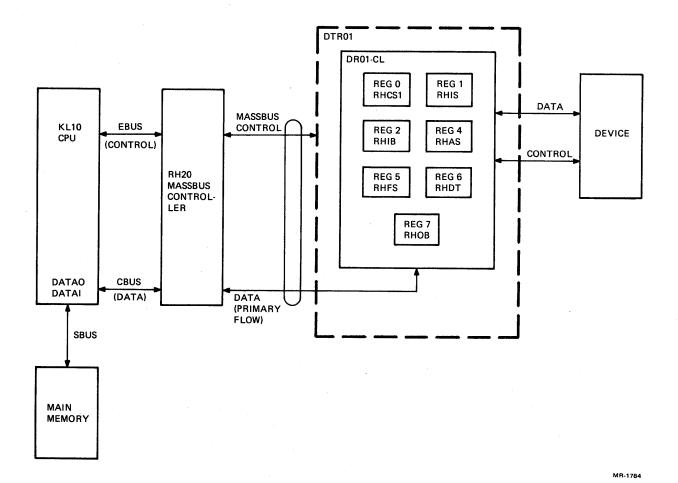

#### 4.2.1 Communication Between the DTR01 and the KL10-B, C, D or E Processor (See Figure 4-1)

Communication and control between the DTR01 subsystem (RH20 and DTR01) and the KL10-B, C, D or E processor is implemented with DATAO and DATAI instructions from the CPU. These instructions cause bits within the DR01 external registers to be loaded or cleared. The KL10-B, C, D or E CPU communicates with the RH20 Massbus controller via the EBus and the RH20 Massbus controller communicates with the DR01 via the Massbus.

Data is transferred through the DR01 registers to or from the RH20 Massbus controller via the MBus data lines. Data is transferred between the RH20 and the CPU via the CBus and between the CPU and main memory via the SBus.

A secondary method available to transfer data to and from the RH20 Massbus controller is via DR01 external registers  $2_8$  and  $7_8$ , respectively, using DATAI and DATAO instructions. (See Paragraphs 4.1.1 and 4.1.2.)

**4.2.1.1** Loading DR01/DTR01 External Registers – The CPU issues a DATAO or DATAI instruction to read or write the designated DR01/DTR01 registers. When using DATAO, setting bit 06, LR = 1 writes into the DR01 register (RS00-37<sub>8</sub>) and setting bit 06, LR = 0 loads a register address (plus control data and a drive address if RS =  $00-37_8$ ) so that a register may be read by a subsequent DATAI. Repeated DATAI commands will read the same register; that is, DATAI will always read the register specified by the last DATAO (LR = 0 or 1).

When the RH20 detects an error caused by a nonexistent drive or control bus parity during the writing or reading of an external register, an interrupt occurs and the program is inhibited from writing any more registers with a DATAO unless DRAES, DATAI bit 09, was set by the DATAO that preceded or caused the error. (A DATAI is not inhibited and it can be used to read back the failing register and drive address.)

For a more detailed description of DATAO/DATAI instructions, refer to the RH20 Massbus Controller Unit Description, EK-RH20-UD.

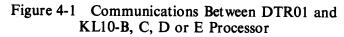

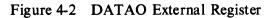

**4.2.1.2** DATAO – The DATAO command is used to write both internal and external registers. The bit format for the DTR01 DATAO (external registers) is shown in Figure 4-2.

The preparation register is not addressed directly. It is loaded with address and control information (bits 00-06, 09 and 14-18) by all DATAO commands, provided there has been no previous register access error detected (RAE, CONI bit 24 = 0) or there has been an error and it has been disabled (DRAES, DATAI bit 09 = 1). When RAE = 1 and DRAES = 0, the preparation register is not loaded and the DATAO command is not executed by the RH20. The following list explains the functions of the bits in the DATAO external register.

#### Bits Description

- 00-05 REGISTER SELECT (RS) Six-bit register select code.  $RS = 40-77_8$  when addressing an internal register of RH20.  $RS = 00-37_8$  when addressing an external register of DR01.

- 06 LOAD REGISTER (LR) When equal to 1, causes the addressed register to be written. When equal to 0, only the preparation is loaded, thus providing a means to store address and control information for a subsequent register read operation (DATAI).

- 09 DRAES Prevents RAE (CONI bit 24) from generating an RH20 interrupt request and from inhibiting subsequent register write operations.

- 15-17 DRIVE SELECT (DS) Specifies the drive number  $(0-7_8)$  when addressing an external register (RS =  $00-37_8$ ).

- 18 CBEP When writing an external register ( $RS = 00-37_8$ , LR = 1) causes even parity to be transmitted on the Massbus (control bus) data lines. Used by the diagnostics to cause parity errors in a drive.

- 20-35 EXTERNAL REGISTER DATA Specifies the register contents when an external register is written.

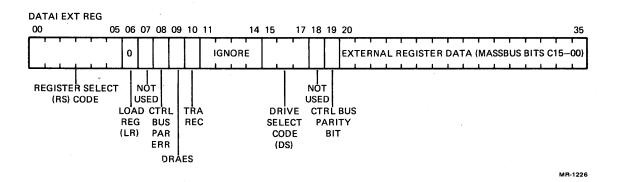

**4.2.1.3** DATAI – The DATAI command is used to read both internal and external registers. The register that is read is determined by the address and control data stored in the preparation register by a previous DATAO. Bit format for the DATAI command is shown in Figure 4-3. The following list explains the functions of the bits in the DATAI external register.

| Bits  | Description                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00–05 | REGISTER SELECT (RS) – The register select code which is stored in the preparation register.                                                                                                                            |

| 06    | LOAD REGISTER (LR) – Indicates the state of the LR bit stored in the preparation register. Equals 0 when the previous DATAO loaded only the preparation register. Equals 1 when the DATAO wrote the specified register. |

| 08    | CONTROL BUS PAR ERR (CBPE) – Indicates that bad parity was detected on the Massbus (control bus) data lines during the DATAI. Sets RAE (CONI bit 24).                                                                   |

| 09    | DRAES – Indicates that register access errors have been disabled. Set by DATAO bit $09 = 1$ .                                                                                                                           |

| 10    | TRANSFER RECEIVED (TRA) – Indicates that a drive responded (asserted transfer on the Massbus) during the DATAI.                                                                                                         |

| 15–17 | DRIVE SELECT (DS) – The drive select code stored in the preparation register by a DATAO.                                                                                                                                |

| 19    | CONTROL BUS PARITY BIT (CPA) – Indicates the state of the parity bit received on the Massbus (control bus).                                                                                                             |

| 20-35 | EXTERNAL REGISTER DATA (ERD) – The contents of the register addressed by the DATAI.                                                                                                                                     |

4-4

Figure 4-3 DATAI Bit Format

4-5

#### 4.2.2 Programmable Registers in DR01-CL Channel Interface Unit

Communication and control between the DTR01 subsystem and the host processor is implemented with seven programmable registers located in each DR01-CL channel interface unit. Paragraphs 4.2.2.1 through 4.2.2.7 describe the seven programmable registers and formats.

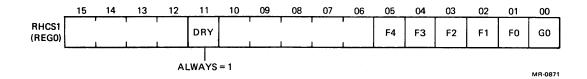

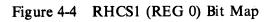

4.2.2.1 Control and Status 1 Register (RHCS1) - REG 0 - Register 0 is the control status 1 (RHCS1) register. It is used by both the controller and the DR01 to store the device commands and hold operational status. Register bits 00 through 05 and bit 11 are dedicated for use by the interface as shown in Figure 4-4.

Register bits 00–05 indicate the command to be performed and are stored in the selected device (LSB = bit 0).

| Bits  | Description                |                                  |

|-------|----------------------------|----------------------------------|

| 15-12 | Not used                   |                                  |

| 11    | Device Ready - Always read | as a 1 (DRY)                     |

| 10-06 | Not used                   |                                  |

| 05-01 | F4-F1 - Command function   | code; can be written at any time |

|       | Function                   | F4-F1 (bits 05-01) Equal         |

|       | Read                       | 708                              |

| -     | Write                      | 60 <sub>8</sub>                  |

|       | Interface Clear            | 108                              |

00

GO - The GO bit is a read/write bit that indicates interface busy. A lockout feature is not provided if the GO bit is set. Therefore, do not write this register during a data transfer.

| Function is GO  | Bits 05-00 Equal: |

|-----------------|-------------------|

| Read            | 71 <sub>8</sub>   |

| Write           | 618               |

| Interface Clear | 118               |

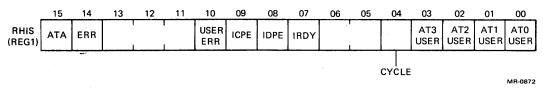

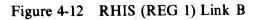

4.2.2.2 Interface Status Register (RHIS) - REG 1 - This register provides general status information for the DR01-CL, the user-defined error bit, and attention signals. The register format is shown in Figure 4-5.

15

ATA – An attention condition sets the ATA bit and the ATA summary line. An ATA condition is caused by the error bit (ERR) setting or the setting of any user-defined attention or error bits. ATA is cleared by INIT, RH CONTROLLER CLEAR, loading a data transfer command with GO set, or writing the appropriate bit in the RHAS register, REG 4. The last two methods do not clear the error condition in the device. This is a read-only bit. ATA is set on power-up.

- ERR ERR is set when one or more error conditions (USER ERR, ICPE, and IDPE) have been set. ERR is a composite error bit (logical OR) of all error conditions in the RHIS register. The ERR bit is cleared only by INIT, RH CONTROLLER CLEAR or an INTERFACE CLEAR command while ERR is set. On power-up, ERR is set. This is a read-only bit.

- 13–11 Not used.

14

10 USER ERR – User-defined error condition from user interface sets USER ERR. USER ERR is cleared by writing an INTERFACE CLEAR command into RHCS1, assuming the interface clears with INIT set. This bit may be used to terminate a data transfer if the word count has not overflowed. Therefore, USER ERR may not indicate an actual error condition. The user status bits may be used to provide more detail concerning why the USER ERR is set. This bit is read-only.

- 09 ICPE Sets ERR and indicates a parity error has occurred in transferring control data over the control bus. This bit is read-only.

- 08 IDPE Indicates a parity error in transferring data over the data bus during a write device or a data parity error in data received from the user interface during a read device, if enabled. This bit is read-only.

- 07 IRDY Indicates that the DR01-CL is ready to accept a new data transfer command. IRDY is set by completion of a block data transfer or an error condition. It is cleared by issuing a Data Transfer command with GO set. This is a read-only bit.

- 06–05 Not used.

- 04 CYCLE This write-only bit is used to prime bus cycles if the user interface is not selfstarting. Writing a 1 into this bit causes CYCLE in the interface to set, initiating transfers.

- 03-00 AT3-AT0 Read-only, user-defined attention bit. Sets ATA and causes an interrupt if enabled. Cleared by removing the attention condition in the user interface.

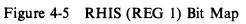

**4.2.2.3** Input Buffer Register (RHIB) – REG 2 – This register reflects the state of the DATA IN (0:15) lines from the user interface. DATA IN 16 and 17 are not readable via RHIB. This read-only register is shown in Figure 4-6.

15–0 DI15–DI0 – User input data lines

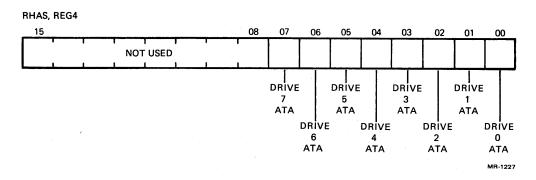

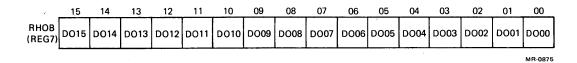

**4.2.2.4** Attention Summary Register (RHAS) – REG 4 – This register consists of eight status bits, each corresponding to the ATA status bit of one drive. Bit 00 is the ATA bit of drive 0, bit 01 is the ATA bit of drive 1, etc. to bit 07. Bits 08–15 are not used. This read/write register is shown in Figure 4-7.

The timing of transfers on the control bus to and from this register is special. When this register (REG 4) is read by the controller, each drive gates its ATA bit out onto one of the C lines (drive 00 onto C00, etc.). Because all drives are responding at once, the normal handshake sequence is not valid. Instead, the controller waits the maximum delay time and then unconditionally strobes the C lines. The controller negates DEMAND after it has strobed the C lines. No drive may disable its C line output until it has negated transfer (typically after receiving the negation of DEMAND). When the transfer line becomes negated at the controller (after each drive has negated TRANSFER), the controller knows that the cycle is complete.

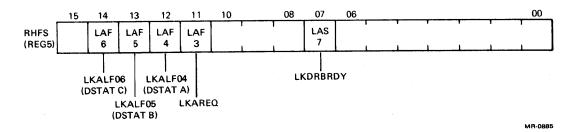

4-9