R. C.

ME11-L core memory system manual

in such das parts in mes community men differences and the second s

digital equipment corporation · maynard, massachusetts

4-A-4 12/16-11-52-11

1st Edition, July 1972

2nd Printing, October 1972

3rd Printing (Rev) December 1972

4th Printing, May 1973

5th Printing, November 1973

Mt11-L core memory system manual

Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP DIGITAL UNIBUS PDP FOCAL COMPUTER LAB

## CONTENTS

| age?             |                                           |                                                                                                                       | Page        |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|

| CHAPTER 1        | GENERAL INFORMATION                       | CLARADIN RATE COMM                                                                                                    | C SPTTLATT? |

| 1.1              | Introduction                              |                                                                                                                       | 1-1         |

| 1.2              | Functional Description                    |                                                                                                                       | 1-1         |

| 1.2.1            | Unibus                                    |                                                                                                                       | 1-2         |

| 1.2.2            | Memory                                    |                                                                                                                       | 1-2         |

| 1.2.3            | Power Supply                              |                                                                                                                       | 1-2         |

| 1.2.4            | Mounting Box                              |                                                                                                                       | 1-2         |

| 1.3              | Physical Description                      |                                                                                                                       | 1-2         |

| 1.4              | ME11-L Specifications                     |                                                                                                                       | 1-5         |

| 1.5              | Installation                              |                                                                                                                       | 1-5         |

| 1.5.1            | Mounting the Computer on Installed Slide  | s national tames data                                                                                                 | 1-7         |

| 1.5.2            | Installation of Side and Top Cover        |                                                                                                                       | 1-7         |

| 1.5.3            | Connection of the AC Power Supply         |                                                                                                                       | 1-7         |

| 1.5.4            | Instructions for Connection to Other That | n 115V                                                                                                                | 1-7         |

| 1.5.5            | Quality of AC Power Source                | DING MARKEN DATORICS                                                                                                  | 1-7         |

| 1.5.6            | ME11-L Power Control                      |                                                                                                                       | 1-8         |

| 1.5.7            | Installing the Unibus Cable               |                                                                                                                       | 1-8         |

|                  |                                           | with east a constraint                                                                                                |             |

| <b>CHAPTER 2</b> | POWER SUPPLY                              |                                                                                                                       |             |

| 2.1              | Introduction                              |                                                                                                                       | 2-1         |

| 2.1              | General Description                       |                                                                                                                       | 2-1         |

| 2.2              | Physical Description                      |                                                                                                                       | 2-1         |

| 2.2.1            | Power Control                             |                                                                                                                       | 2-1         |

| E. S.            | *                                         |                                                                                                                       | 2-1 2-2     |

| 2.2.1.2          | Power Chassis Assembly                    |                                                                                                                       | 2-2         |

| 2.2.1.3          | DC Regulator Module                       |                                                                                                                       | 2-2         |

| 2.2.1.4          | DC Cable                                  |                                                                                                                       | 1.1.1.1.1   |

| 2.2.1.5          | AC Cable                                  | with a logister                                                                                                       | 2-5         |

| 2.2.2            | Specifications                            | Truck Dart 191 Carrier                                                                                                | 2-5         |

| 2.3              | Detailed Description                      |                                                                                                                       | 2-9         |

| 2.3.1            | AC Input Circuit                          |                                                                                                                       | 2-10        |

| 2.3.2            | DC Regulator Module Operation             |                                                                                                                       | 2-10        |

| 2.3.2.1          | Generation of ± Raw DC                    | Timmer Call                                                                                                           | 2-10        |

| 2.3.2.2          | BUS AC LO L and BUS DC LO L Circuits      | S<br>State of the state of | 2-12        |

| 2.3.2.3          | +5V Regulator Circuit                     |                                                                                                                       | 2-15        |

| 2.3.2.4          | - 15V Regulator Circuit                   |                                                                                                                       | 2-16        |

| 2.4              | Maintenance                               |                                                                                                                       | 2-16        |

| 2.4.1            | Adjustments                               | beta in Prote (0% F. 7) Opens                                                                                         | 2-17        |

| 2.4.2            | Circuit waveforms                         | BOTAGI 120 MEL                                                                                                        | 2-17        |

| 2.4.3            | Iroubleshooting                           | Late ("in write (DAT()#) One                                                                                          | 2-19        |

| 2.4.3.1          | Troubleshooting Rules                     |                                                                                                                       | 2-19        |

| 2.4.3.2          | Troubleshooting Hints                     |                                                                                                                       | 2-19        |

| 2.4.3.3          | Troubleshooting Chart                     |                                                                                                                       | 2-21        |

| 2.4.4            | Parts Identification                      |                                                                                                                       | 2-22        |

## **CONTENTS** (Cont)

## CHAPTER 3 MM11-L CORE MEMORIES

| 3.1     | Introduction                                   | 3-1  |

|---------|------------------------------------------------|------|

| 3.2     | General Description                            | 3-1  |

| 3.2.1   | Physical Description                           | 3-1  |

| 3.2.2   | Specifications                                 | 3-1  |

| 3.2.3   | Functional Description                         | 3-2  |

| 3.2.3.1 | Introduction                                   | 3-2  |

| 3.2.3.2 | Control Module (G110)                          | 3-2  |

| 3.2.3.3 | Drive Module (G231)                            | 3-5  |

| 3.2.3.4 | Stack Module (H214)                            | 3-7  |

| 3.2.4   | Basic Memory Operation                         | 3-7  |

| 3.2.4.1 | Data In (DATI) Cycle                           | 3-7  |

| 3.2.4.2 | Data In, Pause (DATIP) Cycle                   | 3-7  |

| 3.2.4.3 | Data Out (DATO Cycle)                          | 3-7  |

| 3.2.4.4 | Data Out, Byte (DATOB) Cycle                   | 3-8  |

| 3.3     | Detailed Description                           | 3-8  |

| 3.3.1   | Core Array                                     | 3-8  |

| 3.3.2   | Memory Operation                               | 3-8  |

| 3.3.3   | Device and Word Selection                      | 3-11 |

| 3.3.3.1 | Memory Organization and Addressing Conventions | 3-11 |

| 3.3.3.2 | Device Selector                                | 3-15 |

| 3.3.3.3 | Word Selection                                 | 3-18 |

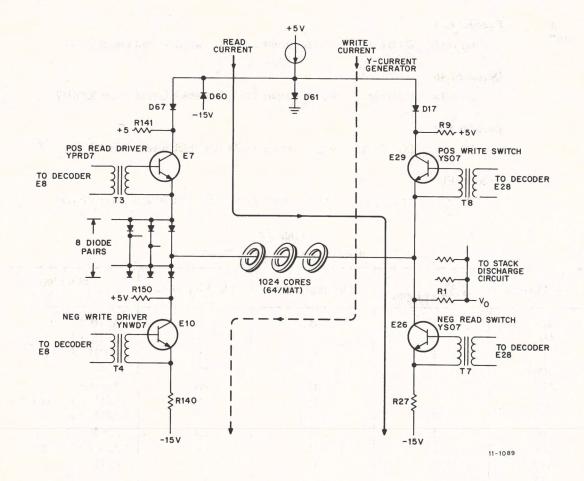

| 3.3.4   | Read/Write Current Generation and Sensing      | 3-24 |

| 3.3.4.1 | Read/Write Operations                          | 3-24 |

| 3.3.4.2 | X- and Y-Current Generators                    | 3-26 |

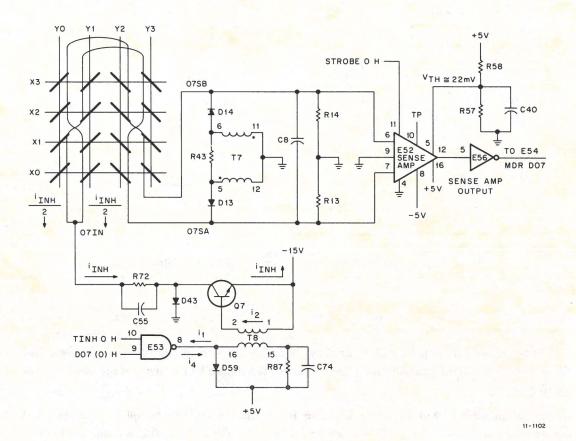

| 3.3.4.3 | Inhibit Driver                                 | 3-28 |

| 3.3.4.4 | Sense Amplifier                                | 3-29 |

| 3.3.4.5 | Memory Data Register                           | 3-29 |

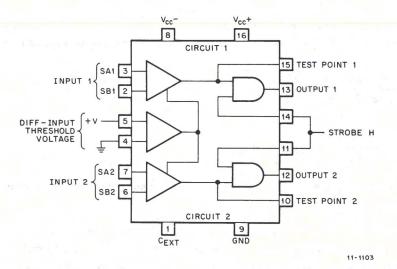

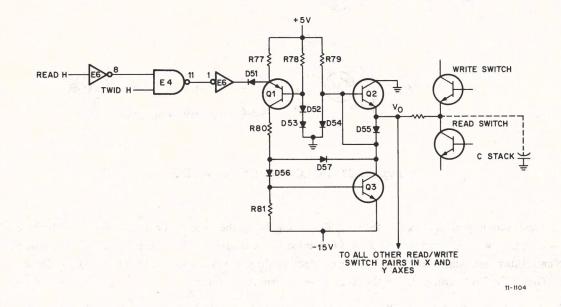

| 3.3.5   | Stack Discharge Circuit                        | 3-30 |

| 3.3.6   | DC LO Circuit                                  | 3-31 |

| 3.3.7   | Operating Mode Selection Logic                 | 3-32 |

| 3.3.8   | Control Logic                                  | 3-33 |

| 3.3.8.1 | Timing Circuit                                 | 3-33 |

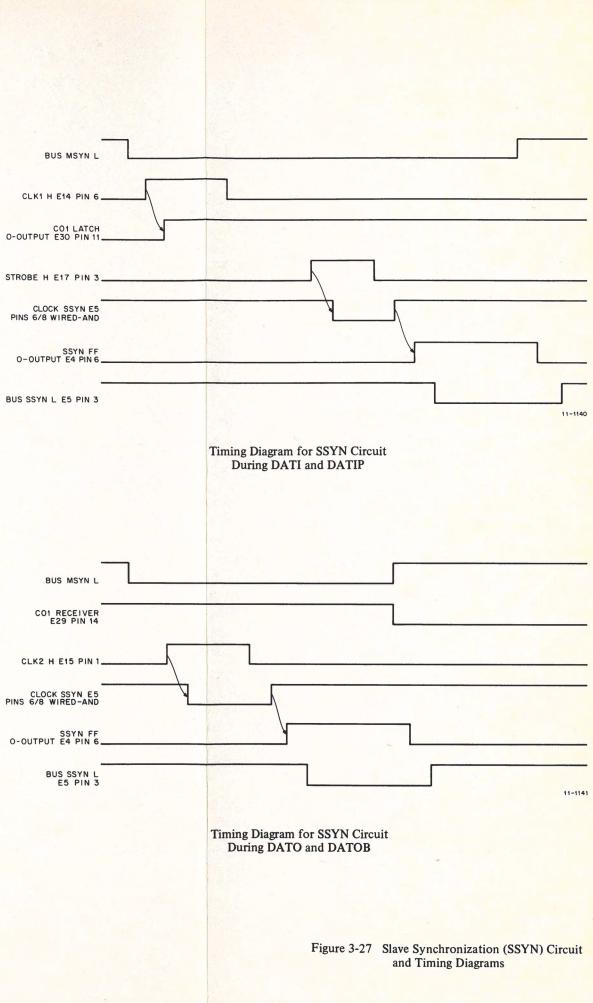

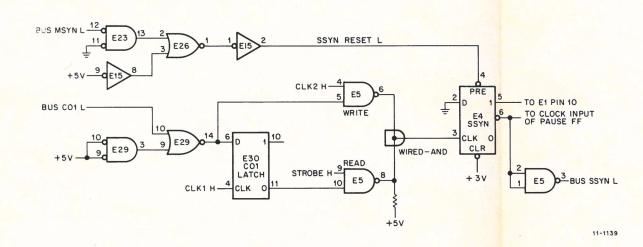

| 3.3.8.2 | Slave Synchronization (SSYN) Circuit           | 3-39 |

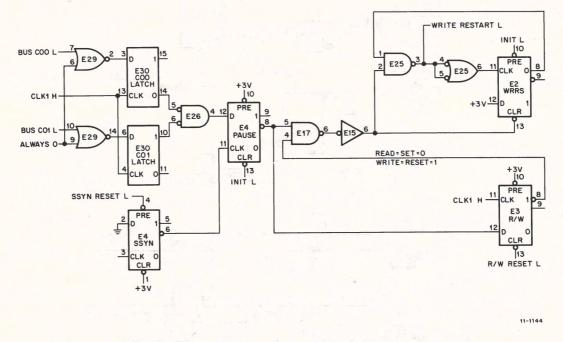

| 3.3.8.3 | Pause/Write Restart Circuit                    | 3-40 |

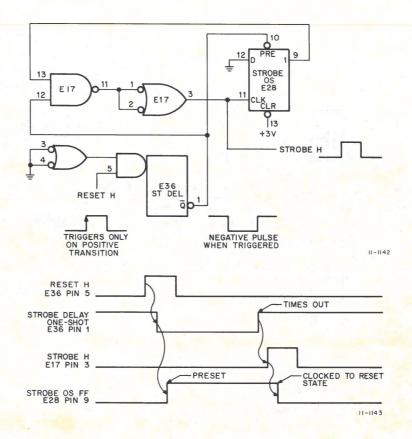

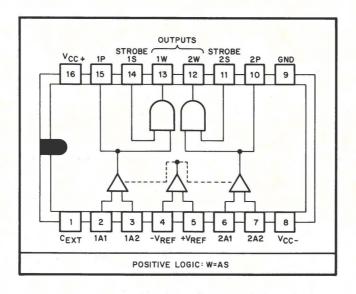

| 3.3.8.4 | Strobe Generating Circuit                      | 3-43 |

| 3.3.8.5 | Data In (DATI) Operation                       | 3-45 |

| 3.3.8.6 | Data In Pause (DATIP) Operation                | 3-47 |

| 3.3.8.7 | Data Out (DATO) Operation                      | 3-47 |

| 3.3.8.8 | Data Out Byte (DATOB) Operation                | 3-48 |

| 3.4     | Maintenance                                    | 3-48 |

| 3.4.1   | Preventive Maintenance                         | 3-49 |

| 3.4.1.1 | Initial Procedures                             | 3-49 |

| 3.4.1.2 | Checking Output of Current Generators          | 3-49 |

|         |                                                |      |

## **CONTENTS** (Cont)

|         |                                             | Page |

|---------|---------------------------------------------|------|

| 3.4.2   | Corrective Maintenance                      | 3-49 |

| 3.4.2.1 | Strobe Delay Check and Adjustment           | 3-50 |

| 3.4.2.2 | Corrective Maintenance Aids                 | 3-50 |

| 3.4.3   | Programming Tests                           | 3-50 |

| 3.4.3.1 | Address Test Up (MAINDEC-11-D1A)            | 3-50 |

| 3.4.3.2 | Address Test Down (MAINDEC-11-D1B)          | 3-57 |

| 3.4.3.3 | No Dual Address Test (MAINDEC-11-D1C)       | 3-57 |

| 3.4.3.4 | Basic Memory Patterns Test (MAINDEC-11-D1D) | 3-57 |

| 3.4.3.5 | Worst Case Noise Test (MAINDEC-11-D1G)      | 3-57 |

## APPENDIX A INTEGRATED CIRCUIT DESCRIPTIONS

| A.1 | Introduction                                               | A-1 |

|-----|------------------------------------------------------------|-----|

| A.2 | SN74121 Monostable Multivibrator                           | A-1 |

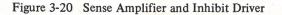

| A.3 | SN7528 Dual Sense Amplifiers with Preamplifier Test Points | A-2 |

## ILLUSTRATIONS

| Figure No. | Title                                            | Page |

|------------|--------------------------------------------------|------|

| 1-1        | ME11-L Functional Block Diagram                  | 1-1  |

| 1-2        | ME11-L Mounting Box                              | 1-3  |

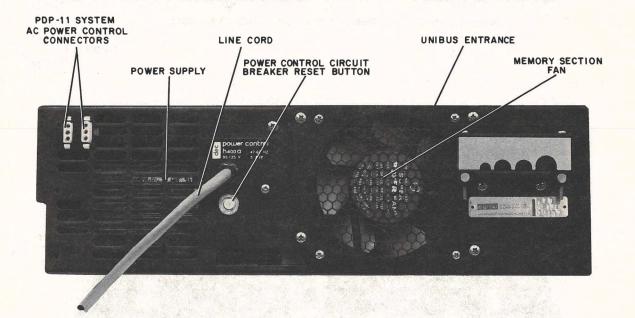

| 1-3        | Rear View of ME11-L                              | 1-3  |

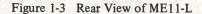

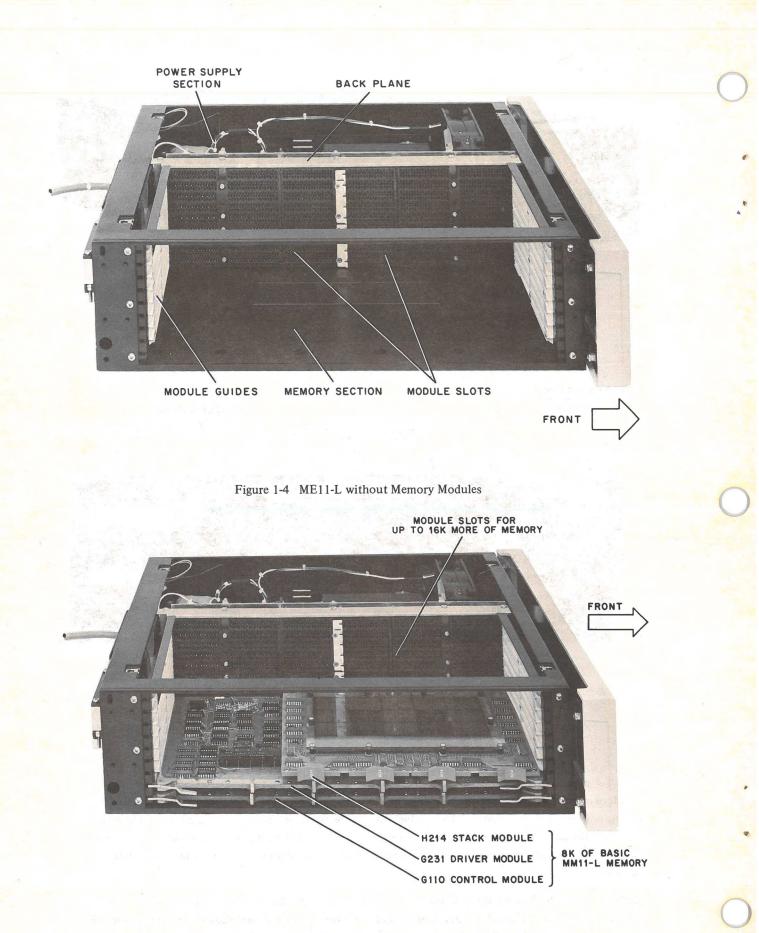

| 1-4        | ME11-L without Memory Modules                    | 1-4  |

| 1-5        | Memory Section ME11-L                            | 1-4  |

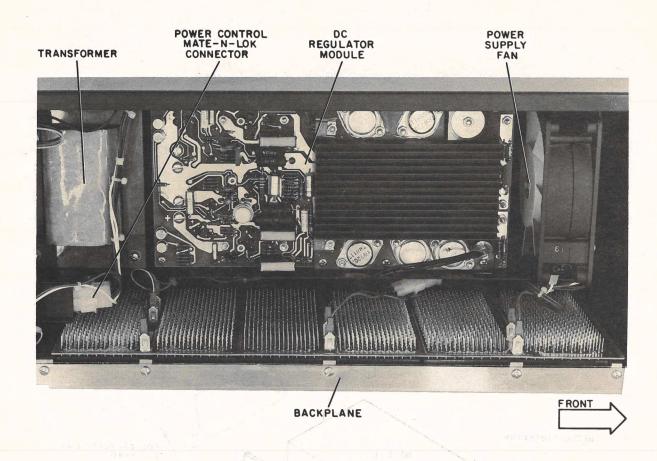

| 1-6        | Power Supply Section of ME11-L                   | 1-5  |

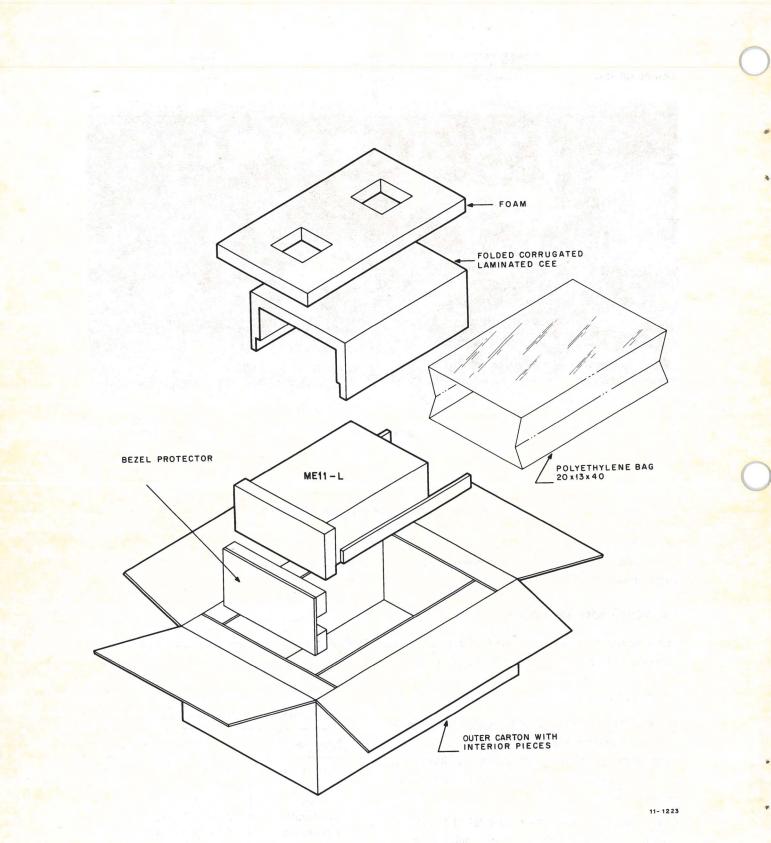

| 1-7        | ME11-L Shipping Carton                           | 1-6  |

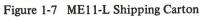

| 1-8        | Unibus Cable Connection                          | 1-8  |

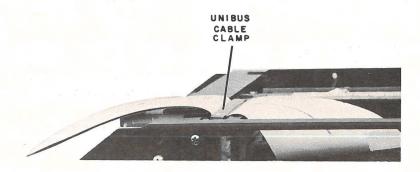

| 2-1        | Power Chassis Assembly                           | 2-3  |

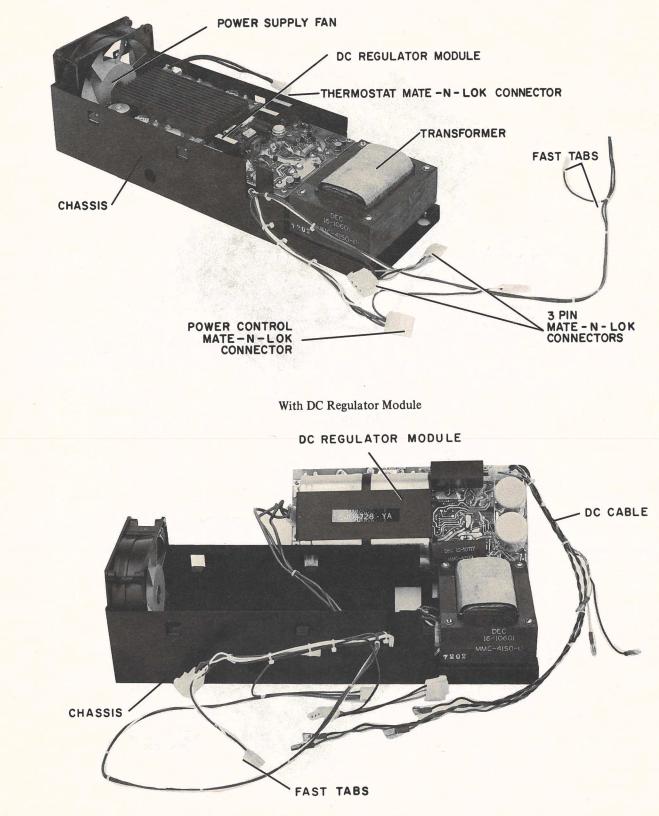

| 2-2        | DC Regulator Module                              | 2-4  |

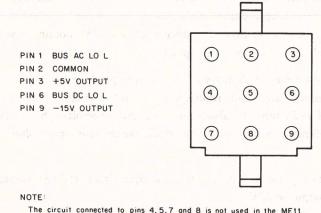

| 2-3        | H740 Output Connector (5409728 Regulator Module) | 2-9  |

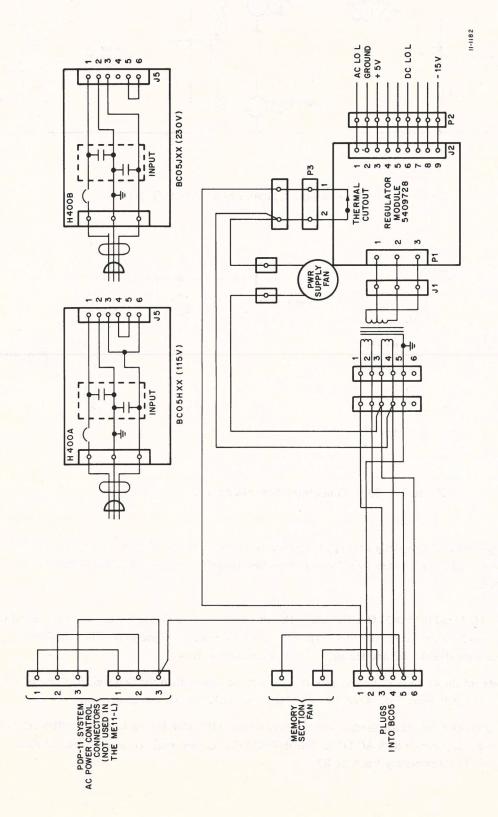

| 2-4        | AC Interconnection Diagram                       | 2-11 |

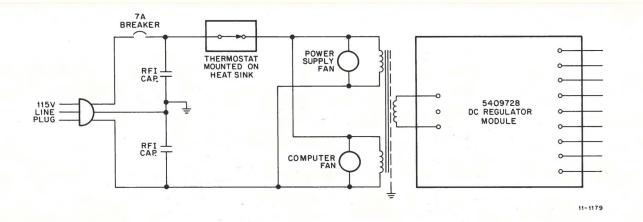

| 2-5        | 115V Connections, Simplified Schematic Diagram   | 2-12 |

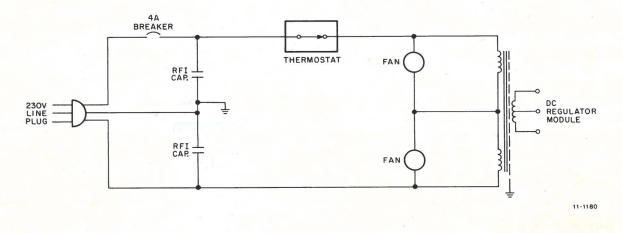

| 2-6        | 230V Connection, Simplified Schematic Diagram    | 2-12 |

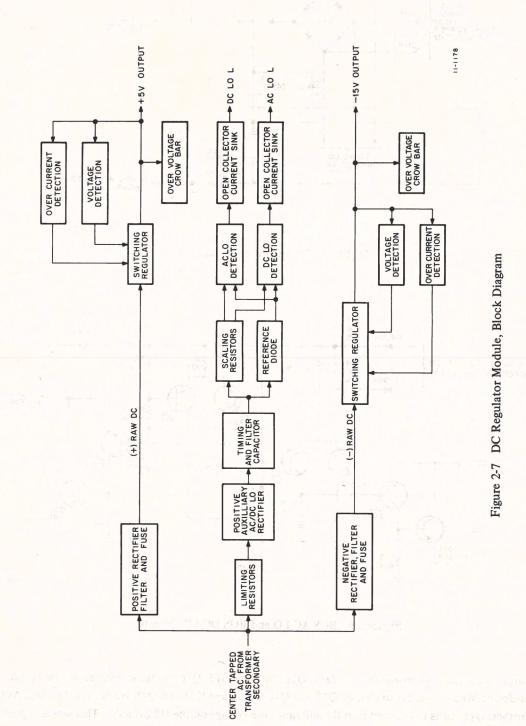

| 2-7        | DC Regulator Module, Block Diagram               | 2-13 |

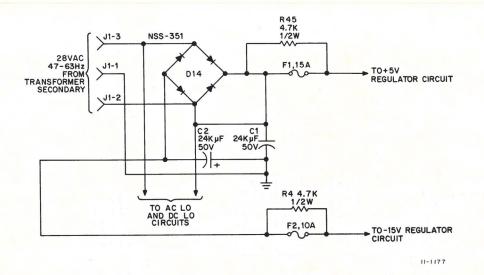

| 2-8        | Rectifier Circuit                                | 2-14 |

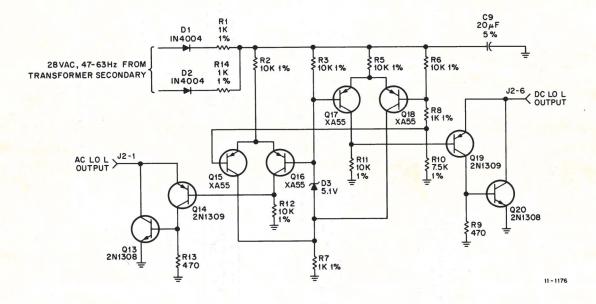

| 2-9        | BUS AC LO and BUS DC LO Circuits                 | 2-14 |

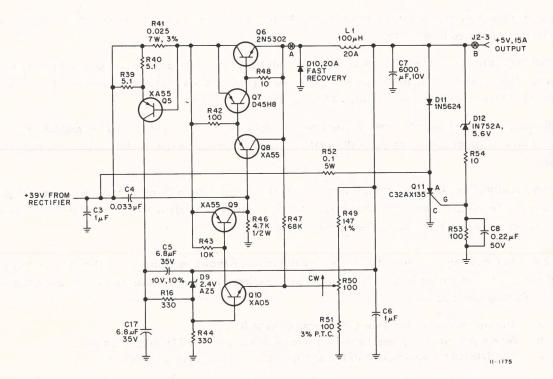

| 2-10       | +5V Regulator Circuit                            | 2-15 |

| 2-11       | -15V Regulator Circuit                           | 2-17 |

| 2-12       | +5V Regulator Circuit Waveforms                  | 2-18 |

| 2-13       | -15V Regulator Circuit Waveforms                 | 2-20 |

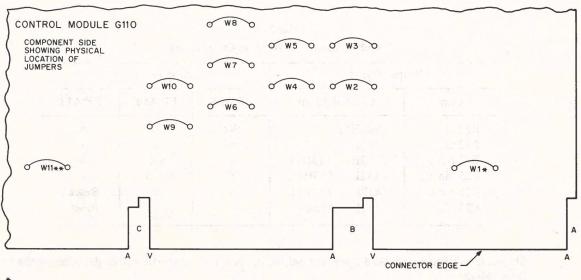

| 3-1        | Component Side of Control Module G110            | 3-2  |

| 3-2        | Component Side of Drive Module G231              | 3-3  |

| 3-3        | Component Side of 8K Stack Module H214           | 3-4  |

## ILLUSTRATIONS (Cont)

| Figure No. | Title                                                                  | Page |

|------------|------------------------------------------------------------------------|------|

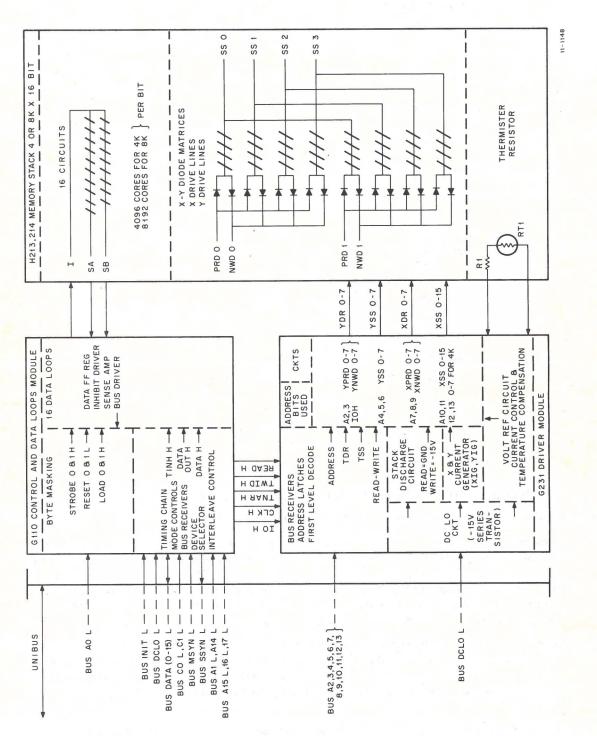

| 3-4        | MM11-L Memory Block Diagram                                            | 3-6  |

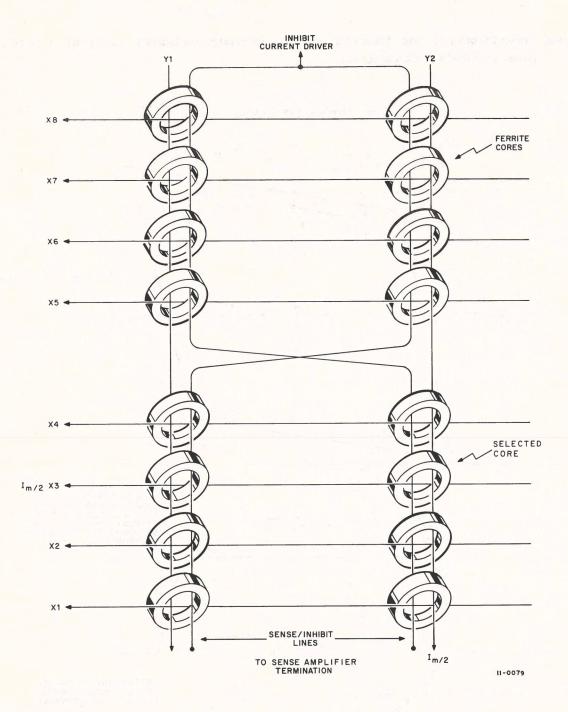

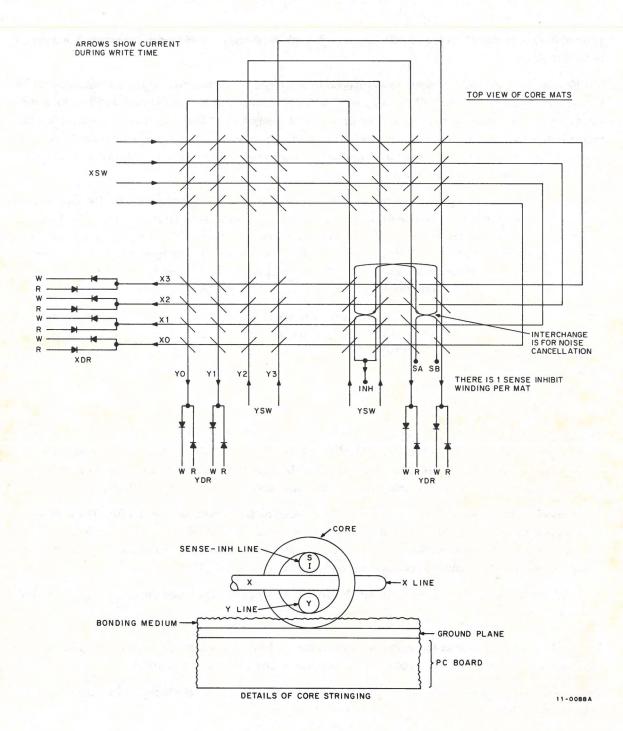

| 3-5        | Three-Wire Memory Configuration                                        | 3-9  |

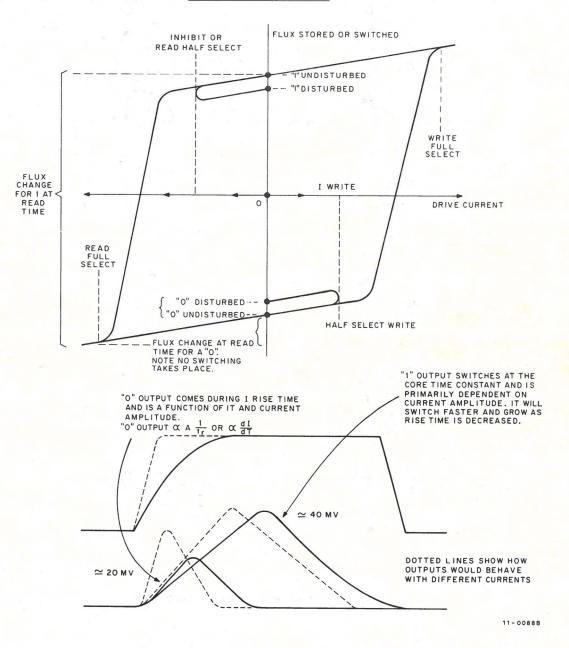

| 3-6        | Hysteresis Loop for Core                                               | 3-10 |

| 3-7        | Three-Wire 3D Memory, Four Mats Shown for a 16-Word by 4-Bit Memory    | 3-12 |

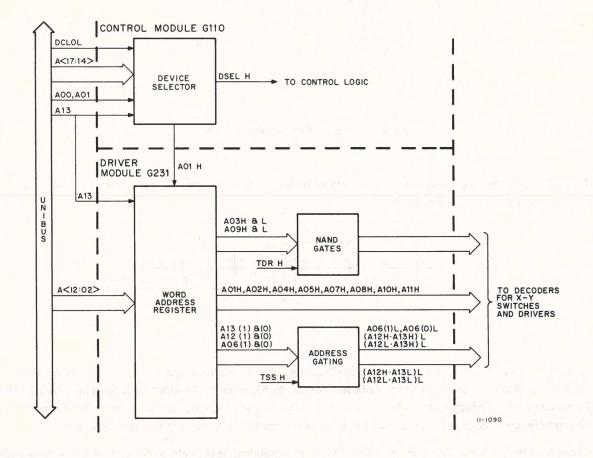

| 3-8        | Device and Word Address Selection Logic, Block Diagram                 | 3-13 |

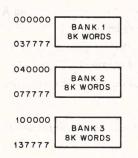

| 3-9        | Memory Organization for 8K Words                                       | 3-14 |

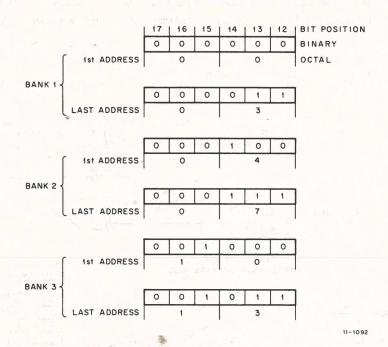

| 3-10       | Address Assignments for Three Banks of 8K Words Each                   | 3-15 |

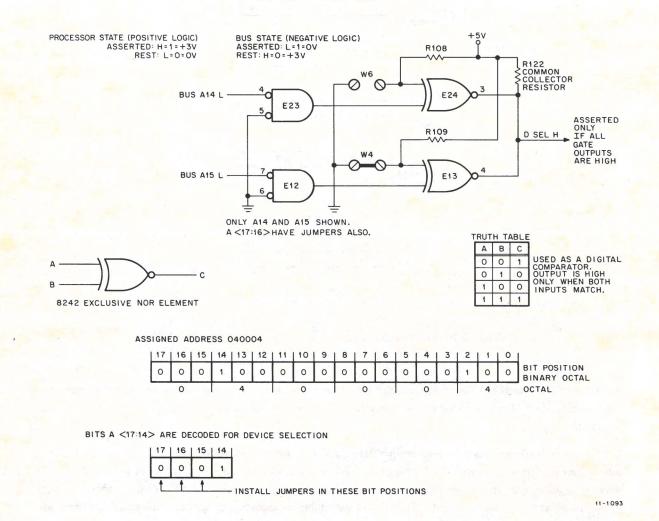

| 3-11       | Jumper Configuration for a Specific Memory Address                     | 3-16 |

| 3-12       | Device Decoding Guide                                                  | 3-17 |

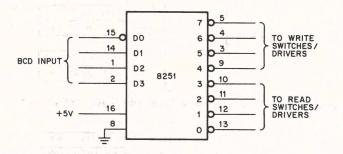

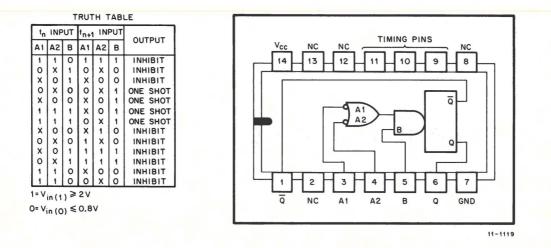

| 3-13       | Type 8251 Decoder, Pin Designation and Truth Table                     | 3-19 |

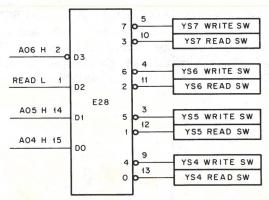

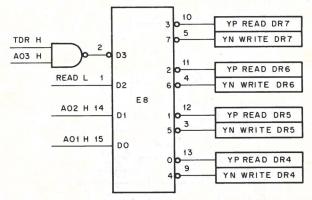

| 3-14       | Decoding of Read/Write Switches and Drivers Y4-Y7                      | 3-20 |

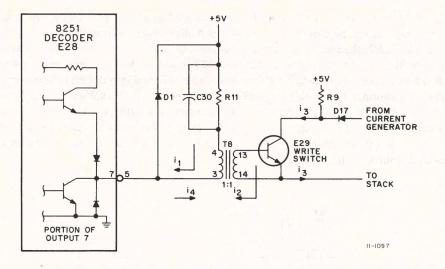

| 3-15       | Switch or Driver Base Drive Circuit                                    | 3-21 |

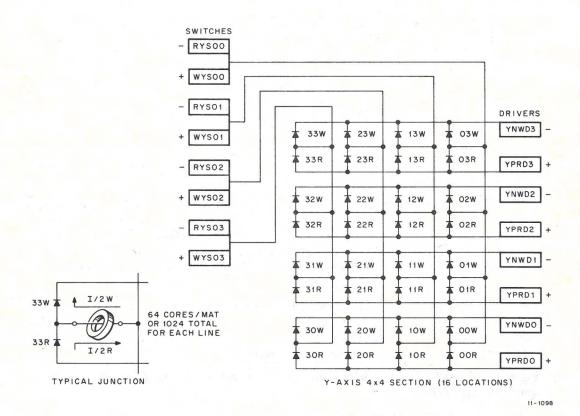

| 3-16       | Y-Line Selection Stack Diode Matrix                                    | 3-22 |

| 3-17       | Typical Y-Line Read/Write Switches and Drivers                         | 3-23 |

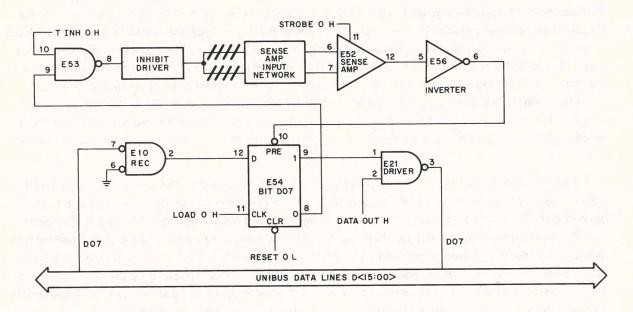

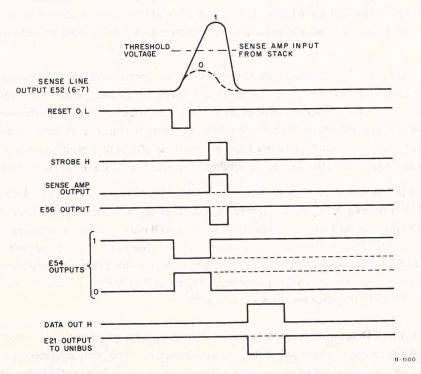

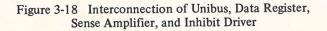

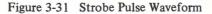

| 3-18       | Interconnection of Unibus, Data Register, Sense Amplifier, and Inhibit | 3-25 |

|            | Driver                                                                 |      |

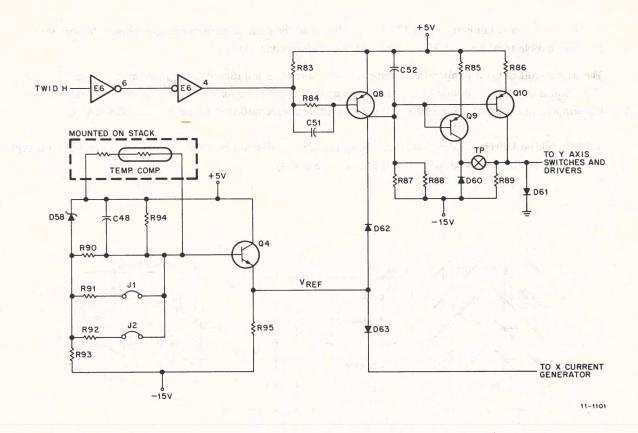

| 3-19       | Y-Current Generator and Reference Voltage Supply                       | 3-27 |

| 3-20       | Sense Amplifier and Inhibit Driver                                     | 3-28 |

| 3-21       | Type 7528 Dual Sense Amplifiers with Preamplifier Test Points          | 3-30 |

| 3-22       | Stack Discharge Circuit                                                | 3-31 |

| 3-23       | DC LO Circuit, Schematic Diagram                                       | 3-32 |

| 3-24       | Basic Timing and Control Signal Functions                              | 3-35 |

| 3-25       | TWID H and TNAR H Control Logic                                        | 3-37 |

| 3-26       | Generation of MSEL RESET L                                             | 3-38 |

| 3-27       | Slave Synchronization (SSYN) Circuit and Timing Diagrams               | 3-41 |

| 3-28       | Pause/Write Restart Circuit                                            | 3-43 |

| 3-29       | Strobe Generating Circuit and Timing Diagram                           | 3-44 |

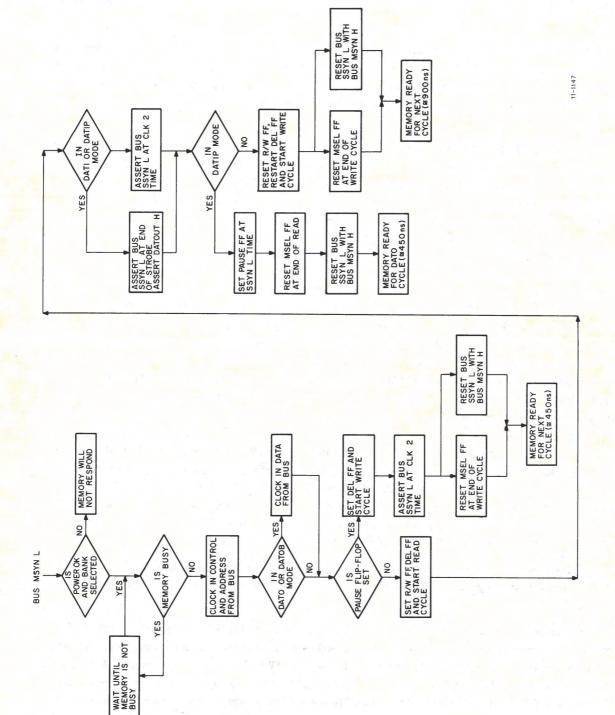

| 3-30       | Flow Chart for Memory Operation                                        | 3-46 |

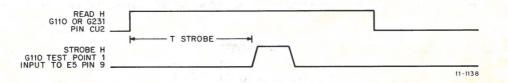

| 3-31       | Strobe Pulse Waveform                                                  | 3-50 |

| 3-32       | Troubleshooting Chart                                                  | 3-51 |

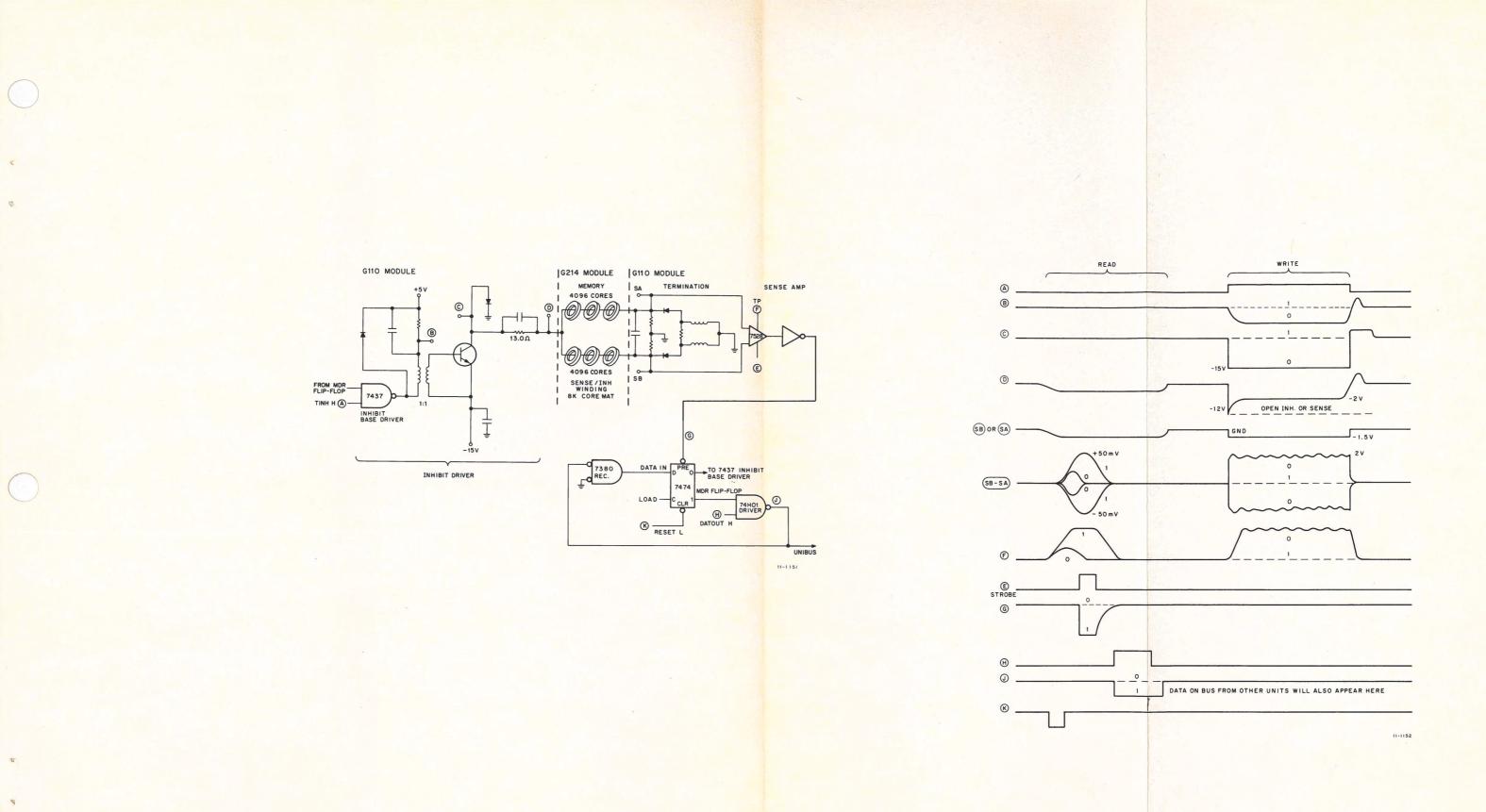

| 3-33       | MM11-L Sense/Inhibit Waveforms                                         | 3-53 |

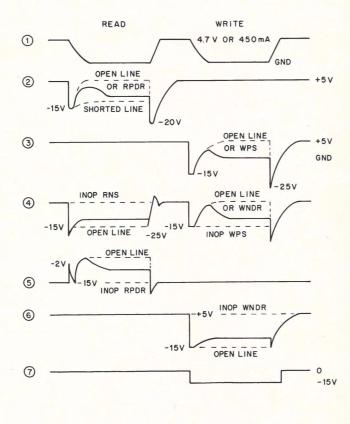

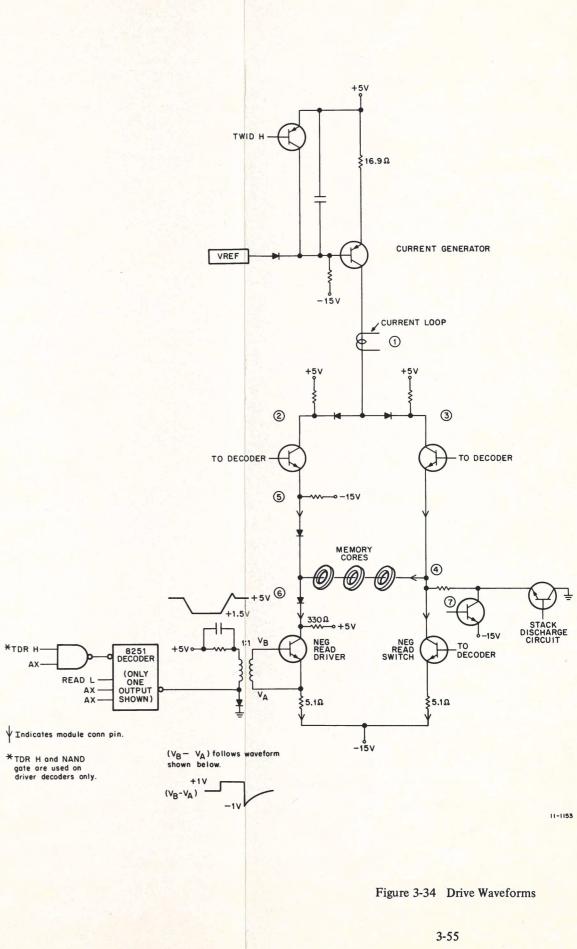

| 3-34       | Drive Waveforms                                                        | 3-55 |

## TABLES

| Table No. | Title                                       | Page |

|-----------|---------------------------------------------|------|

| 1-1       | ME11-L Basic Specifications                 | 1-5  |

| 2-1       | Power Supply Input Specifications           | 2-5  |

| 2-2       | Power Supply Output Specifications          | 2-6  |

| 2-3       | Mechanical and Environmental Specifications | 2-8  |

| 2-4       | Power Supply Troubleshooting Chart          | 2-21 |

| 3-1       | MM11-L Memory Specifications                | 3-4  |

## TABLES (Cont)

| Table No. | Title                                     | Page |

|-----------|-------------------------------------------|------|

| 3-2       | Addressing Functions                      | 3-13 |

| 3-3       | Enabling Signals for Word Register Gating | 3-18 |

| 3-4       | Word Address Decoding Signals             | 3-24 |

| 3-5       | Selection of Bus Transactions             | 3-32 |

| 3-6       | Generation of Memory Operating Signals    | 3-34 |

a

0

## INTRODUCTION

The ME11-L Core Memory System is a Unibus-compatible PDP-11 family peripheral. Throughout this manual the ME11-L Memory System is referred to as the ME11-L and core memory is referred to as the memory. The ME11-L consists of a basic 8K MM11-L Read/Write Core Memory, a Power Supply, and a mounting box. The memory within the mounting box, powered by the Power Supply, is expandable in 8K (MM11-L) increments to 24K.

This manual provides the user with the theory of operation and maintenance information necessary to understand the ME11-L. The level of discussion assumes that the user is familiar with basic digital computer theory and basic PDP-11 use.

Signals and data are transferred between the ME11-L and the PDP-11 Unibus; however, this manual does not describe the operation of the Unibus. A detailed description of the Unibus is found in the PDP-11 Peripherals and Interfacing Handbook.

Engineering drawings are referenced by drawing number and may be found in the ME11-L Engineering Drawing Manual.

This manual is divided into three chapters. Chapter 1 provides a functional description, a physical description, ME11-L specifications, and installation information. Chapter 2 contains the general description, detailed description, and maintenance information regarding the Power Supply of the ME11-L. Chapter 3 provides a general description, a detailed description, and maintenance information regarding the 8K MM11-L Memory used in the ME11-L. Appendix A contains integrated circuit (IC) descriptions for the ICs used in the ME11-L.

## CHAPTER 1 GENERAL INFORMATION

#### **1.1 INTRODUCTION**

The ME11-L is a 900-ns memory system for the PDP-11 computer family. The basic system consists of an 8K, 16-bit, read/write memory contained in its own mounting box with a Power Supply. The memory may be expanded in 8K (MM11-L) increments to 24K. All the necessary cables are included with the rack-mountable  $5-1/4 \times 19$  inch mounting box. By containing its own power supply, the memory unit saves up to 8.1A of power in the processor box.

#### **1.2 FUNCTIONAL DESCRIPTION**

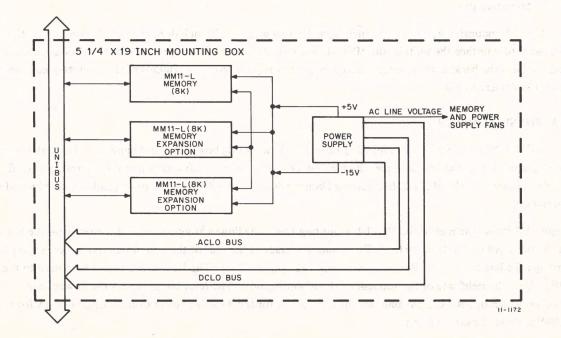

Figure 1-1 shows the functional block diagram of the ME11-L unit. The additional memories are the optional 8K increments to the basic ME11-L unit. Two configurations of the ME11-L are possible depending on the power source to the unit: ME11-LA is for a power source of 115 Vac, 60 Hz; and the ME11-LB is for a power source of 230 Vac, 50 Hz. The additional 8K memory increments, optional for the ME11-L, are designated as the MM11-L Memory. The functional units of the ME11-L are the Unibus, the memory, the Power Supply, and the mounting box.

#### 1.2.1 Unibus

The Unibus is an asynchronous, single high-speed bus. All PDP-11 components and peripherals communicate through the Unibus on its bi-directional lines. Like all PDP-11 peripherals, the ME11-L has its own bus addresses which are the memory location addresses. Communications via the Unibus do not require timing pulses; there-fore, DEC-designed memories of various speeds can be combined in the same PDP-11 System. Because all peripherals share the Unibus, the system includes direct memory accessing (DMA) which is implemented through non-processor requests (NPRs). Data rate on the Unibus is 40 megabits per second or 2.5 million words per second with a cycle of 400 ns. For detailed information regarding the Unibus, refer to the PDP-11 Peripherals and Interfacing Handbook.

#### 1.2.2 Memory

The basic 8K memory unit for the ME11-L is the MM11-L, a 16-bit read/write core-type memory. It provides 8192 (8K) 16-bit words that are word and byte addressable. Unibus address lines 14 through 17 are the ME11-L device portion of the address. This portion of the address is assigned to the ME11-L according to its use in the system. The remaining portion of the address (address lines 0 through 13) refers to the specific memory location. The memory consists of three modules: the G110 Hex Module contains the memory control logic; the G231 Hex Module contains the memory driver logic; and the H214 Quad Module is the memory core stack. The G231 is located between the G110 and the H214. See Chapter 3 for more detailed information on the memory. Paragraph 1.3 describes the memory modules in their ME11-L configuration.

#### 1.2.3 Power Supply

The Power Supply for the ME11-L supplies four outputs to the unit. These outputs are: +5V which provides the memory logic levels; -15V which supplies the memory drive circuits; and BUS AC LO and BUS DC LO which provide the power fail signals to the Unibus. The Power Supply is discussed in detail in Chapter 2.

#### 1.2.4 Mounting Box

The ME11-L mounting box is a 5-1/4 inch high, 19 inch wide, by 20 inch deep cabinet. It contains all the cabling necessary to interface the units of the ME11-L and provide power. It also provides for the Unibus connection and contains the backplane for interconnection of the memory modules. Details of the mounting box are discussed in Paragraph 1.3.

#### **1.3 PHYSICAL DESCRIPTION**

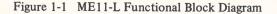

The ME11-L Memory System is shipped in the ME11-L mounting box shown in Figure 1-2. Through the use of photographs, this paragraph describes the ME11-L components and their location in the mounting box. Engineering drawings in the *ME11-L Engineering Drawing Manual* are referenced to provide additional physical information.

Figure 1-3 shows the rear of the ME11-L mounting box. The Power Supply is behind the vents on the left side of the box. All connections to the ME11-L unit are made at the rear of the mounting box. Power is supplied through the line cord to the Power Control unit (115 or 230 Vac). The Unibus enters and is secured to the ME11-L on the right side of the top rear of the mounting box. The reset button resets the Power Control circuit breaker, which opens when the line current exceeds 7A for the 115-Vac Power Control option or 4A for the 230-Vac Power Control option.

Figure 1-4 shows the memory side of the mounting box without any modules plugged into the module slots. When looking at the front of the unit, the memory side is on the left. The backplane divides the memory section of the unit from the Power Supply. The module slots of the backplane unit and the module guides secure the modules in the unit. Figure 1-5 shows the memory section again, but with modules for a basic 8K (MM11-L) of memory plugged into the unit. (Refer to engineering drawing D-MU-ME11-L-01 for module utilization information.)

Figure 1-6 shows the Power Supply section of the ME11-L mounting box. This includes the Power Supply fan at the front of the unit, the DC Regulator Module, and the Power Control Mate-N-Lok output connector. (Refer to engineering drawing E-IA-5409728-0-0 for DC Regulator Module assembly information. The wiring side of

Figure 1-5 Memory Section ME11-L

Figure 1-6 Power Supply Section of ME11-L

the backplane and the Power Supply connections to the backplane are also shown in Figure 1-6. The ME11-L unit is shown on engineering drawing D-UA-ME11-L-0 (2 sheets).

#### 1.4 ME11-L SPECIFICATIONS

The basic specifications for the ME11-L as a unit are listed in Table 1-1. Detailed specifications for the Power Supply and the memory are provided in Paragraphs 2.2.2, and Table 3-1.

#### **1.5 INSTALLATION**

The ME11-L is shipped, ready to operate, in the protective carton shown in Figure 1-7. There are no special shipping mounts internal to the carton. Additional hardware is included, however, to rack mount the ME11-L mounting box.

Prior to final electrical testing, each ME11-L is thermal cycled, vibrated, and subjected to mechanical shock with all modules in place.

The 5-1/2 by 19 inch by 20 inch ME11-L mounting box includes rack mountable slides. The removable top

| Table 1-1 |       |                |

|-----------|-------|----------------|

| ME11-L    | Basic | Specifications |

|   | Specifications | Description              |

|---|----------------|--------------------------|

| - | Cycle Time     | 900 ns                   |

|   | Power          | 350W                     |

|   | Voltage        | 115/230V                 |

|   | Temperature    | 32 to 122°F (0 to 50°C)  |

|   | Dimensions     | 5-1/4 in. (13.3 cm) high |

|   |                | 19 in. (48.3 cm) wide    |

|   |                | 20 in. (50.8 cm) deep    |

|   | Weight         | 45 lb (20.6 kg)          |

cover of the mounting box is fastened by four Cam-Loc screws. The removable side panel is fastened by four Phillips Head screws.

The ME11-L is designed to be mounted in a standard 19 inch wide by 20 inch deep equipment bay. The ME11-L is mounted on slides for easy service. To mount the unit it is first necessary to attach the fixed portion of the slides to the cabinet. The fixed portion of the slides can be removed from the ME11-L by actuating the slide release which is located toward the rear of the mounting box, when the slides are fully extended. Be sure to mount the slides such that the fixed guides are parallel and level with the ground.

## 1.5.1 Mounting the Computer on Installed Slides

Once the slide guides have been securely fastened in the cabinet using all eight screws, lift the ME11-L and slide it carefully on to the slide guides until the slide release locks. Carefully lift the slide release and push the ME11-L fully into the rack, being careful not to tear any existing cabling.

The ME11-L should then be fully extended until the slide release locks. The covers on the top and side of the ME11-L should be removed to permit installation of the Unibus. The covers are removed by loosening four Cam-Loc and Phillips Head screws, respectively.

#### 1.5.2 Installation of Side and Top Cover

Attached to the side cover is the continuation of the left-hand slide. All four 8-32 screws that hold the cover in place should be inserted and tightened securely. The top cover can now be installed using the four Cam-Loc screws.

#### 1.5.3 Connection of the AC Power Supply

The ME11-L is designed for use on 115-Vac circuits in the United States and is equipped with a 3-pronged connector. This connector, when inserted into a properly wired 115-Vac outlet, grounds the mounting box. It is dangerous to operate the ME11-L unless the mounting box is grounded because normal leakage current from the Power Supply flows into metal parts of the chassis.

If there is any question about the integrity of the ground circuit, the user is advised to measure the potential between the ME11-L mounting box and a known ground with an ac voltmeter.

#### 1.5.4 Instructions for Connection to Other Than 115V

The ME11-L operates at voltages ranging from 95V to 135V and from 190V to 270V 47 Hz-63 Hz, providing the proper power control is connected. The unit is ordered for nominal voltages of 115 or 230. The standard 3-pronged connector for 115V is identical with that found on most household appliances. A different 3-pronged connector is used for 230V.

On installations outside of the United States or where the National Electrical Code does not govern building wiring, the user is advised to proceed with caution.

#### 1.5.5 Quality of AC Power Source

The ME11-L is a complex electronic device. Computer systems consisting of a processor, memory, and peripherals are often sensitive to interference present on some ac power lines. If a computer system is to be installed in an electrically "noisy" environment, it may be necessary to condition the ac power line. DEC Field Service engineers can assist in determining if the ac line is satisfactory.

#### 1.5.6 ME11-L Power Control

The ME11-L contains two standard 3-pin connectors used for ac power control in PDP-11 Systems. These connectors are not used in the ME11-L. They do not affect the power in the ME11-L mounting box, nor does the status of the power in the ME11-L affect the power bus. The ME11-L must be plugged into a source of switched ac power in order for its power to rise and fall with the rest of the system.

#### 1.5.7 Installing the Unibus Cable

The wide BC11A Unibus Cable should be folded as shown in Figure 1-8 and routed over and through the clamp attached to the top of the fan. Note that there is a guide extending over the fan from the rear of the mounting box that prevents the Unibus cable from blocking the air flow of the ME11-L.

Figure 1-8 Unibus Cable Connection

## CHAPTER 2 POWER SUPPLY

#### 2.1 INTRODUCTION

This chapter is divided into three sections: general description, detailed description, and maintenance. The general description section provides a functional description, physical description, and specifications for the Power Supply unit. The detailed description section provides a circuit level description of the AC Input Circuit and the DC Regulator Module of the Power Supply. Finally, the maintenance section provides information necessary for troubleshooting the Power Supply and for parts identification.

#### 2.2 GENERAL DESCRIPTION

The Power Supply is a forced-air-cooled unit which converts single phase 115V or 230V nominal 47 to 63 Hz line voltage to the two regulated output voltages required by the memories. The output voltages and their principal uses and characteristics are: +5V for IC logic (switching regulated, overvoltage and overcurrent protected), and -15V for core memory (switching regulated, overvoltage and overcurrent protected).

The supply is used in conjunction with two Power Control Assemblies which contain a line cord, circuit breaker, and RFI capacitors.

The power circuitry also generates BUS AC LO L and DC LO L power fail early warning signals.

A thermal control mounted on the heat sink will interrupt the ac input should the heat sink temperature become excessive due to fan failure or other cause.

#### 2.2.1 Physical Description

The Power Supply comprises three major subassemblies and two cables: the Power Control, Power Chassis Assembly, DC Regulator Module, DC Cable, and AC Cable.

2.2.1.1 Power Control Unit – The Power Control Unit (drawing H400-0-0) is mounted on the rear of the computer by two screws. It contains a line cord, circuit breaker, RFI capacitors, 115V or 230V connections for the Power Supply transformer and a 6-socket Mate-N-Lok output connector. Physically, it consists of a sheet-metal bracket and a slide-on cover which is locked in place by one screw. A single-pole thermal breaker and a line cord strain relief grommet are mounted on the flange of the bracket making the line cord and breaker reset button accessible on the rear of the computer.

A small printed circuit (PC) card is mounted directly to the breaker terminals. This card interconnects and mounts the RFI dual-disc ceramic capacitor, the Mate-N-Lok output connector, and three fast-tabs for ac input and ground connections. A dual fast-tab is connected directly to the bracket. The black and white line cord wires are connected via fast-tab to the PC card; the green (ground) line cord wire is connected to the dual fast-tab, which in turn is connected to the third fast-tab on the PC card.

The 115V and 230V models differ in only two respects: breaker current rating and (printed circuit) jumpers for parallel or series connection of the Power Supply transformer primaries.

Power Control part numbers are: BC05HXX for the 115V, 7A assembly; and BC05JXX for the 230V, 4A assembly. Line cord length is variable and is denoted by XX; e.g., BC05H06 has a 6-foot line cord.

2.2.1.2 Power Chassis Assembly – The 7008731 Power Chassis Assembly (Figure 2-1) consists of a long inverted-U-shaped chassis, 7008726 power transformer, and a 5-inch fan. It is secured to the bottom of the ME11-L by four  $8-32 \times 3/8$  inch Phillips Pan Head bolts.

The chassis is mounted to the right (when viewed from the front) of the connector blocks and airflow is from front to rear. The fan is held to one end of the chassis by two screws; the transformer may be removed by loosening four nuts that are accessible through large holes on the bottom of the chassis.

The DC Regulator Module is mounted to the chassis assembly by six screws and must be removed for cable access. The DC Cable enters a slot on the connector block side of the chassis; the AC Cable enters a slot on the other side.

Connections to the fan are made by small fast-tabs. Connections to the transformer are made via Mate-N-Lok connectors: 6-pin for primary, 3-socket for secondary.

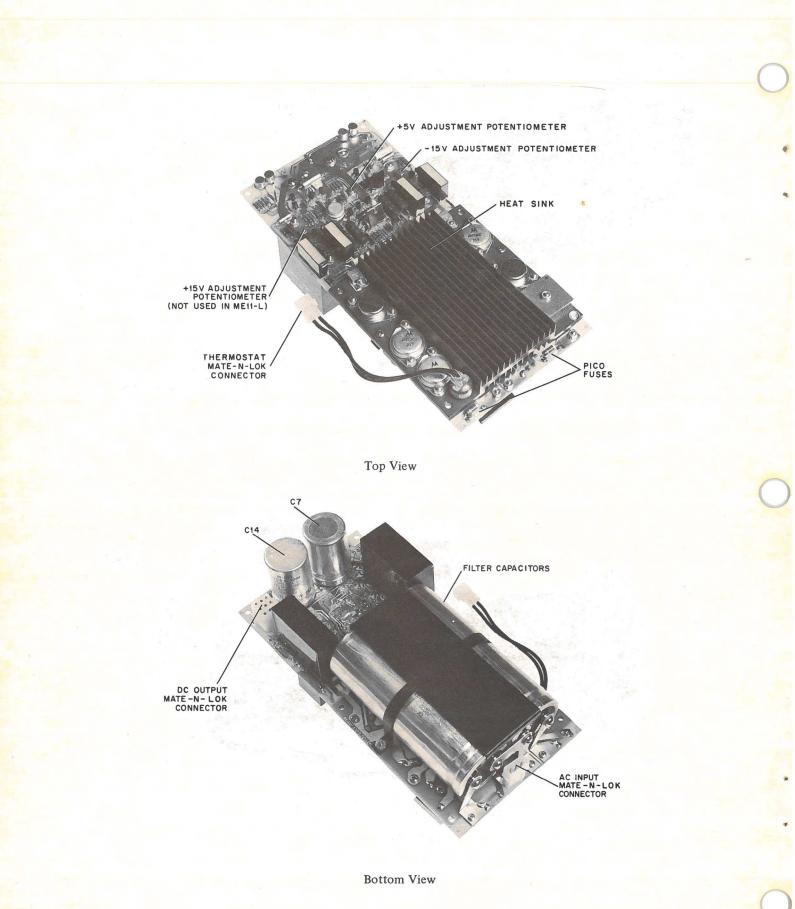

2.2.1.3 DC Regulator Module – The 5409728 DC Regulator Module (Figure 2-2) is a printed circuit assembly that is mounted to the Power Chassis Assembly by four  $6-32 \times 9/16$  inch and two  $6-32 \times 1/4$  inch Phillips Pan Head screws. It contains all the circuitry between the transformer secondary winding and the Power Supply output cable.

ME11-Ls that were shipped during the first three or four months of production of the unit use a DC Regulator Module designated 5409728-YA-0; later shipments use a module designated 5409728-0-0, E revision. There are differences in component values on the two modules. The discussion of the DC Regulator Module circuits in this manual is directed to the later module, designated 5409728-0-0. Engineering drawings applicable to the module used are shipped with each equipment. These drawings provide schematics and component values of the DC Regulator Module used in a specific unit.

The transformer secondary 3-socket Mate-N-Lok connector is plugged into a mating connector which is soldered directly to the printed circuit board and is accessible underneath it. The 9-pin Mate-N-Lok connector on the dc output cable to the memory is similarly mated to a connector underneath the other end of the board.

The DC Regulator Module may be probed for troubleshooting purposes from the top; all points on the circuit are accessible. It may also be removed from the top for cable access and for parts replacement by removing the six mounting screws.

The printed circuit is approximately  $5 \times 10$  inches, with about half of the top surface devoted to the heat sink. The power transistors and power rectifiers are bolted to two shelves on the sides of the heat sink and make contact with the circuit board directly underneath via solder and screw connections. The heat sink is hard anodized for electrical insulation.

The other half of the top surface is devoted to interconnecting and mounting the balance of the circuit. Three small output voltage adjustment potentiometers are accessible on this top portion of the board.

Two small Pico fuses are mounted on the top of the PC board on the fan end. These fast-acting fuses will typically only blow when some component is defective or when the +5 or -15 voltage is set too high.

With DC Regulator Module Removed

Figure 2-1 Power Chassis Assembly

Figure 2-2 DC Regulator Module

The two input filter capacitors are held to the under side of the board by a bracket and are connected to the circuit via jumper tabs on the fan end.

The +5V and -15V output filter capacitors and inductors are also mounted under the board, the former by screws and the latter by nuts.

Care must be taken to ensure that all electrical and mechanical connections are made securely.

2.2.1.4 DC Cable – This is a simple cable connecting the backplane to the DC Regulator Module via a 9-pin Mate-N-Lok connector. The latter is made accessible by loosening the six mounting screws and lifting out the DC Regulator Module.

Cable access is through a slot on the module side of the power chassis.

2.2.1.5 AC Cable – This cable connects all ac portions of the ME11-L chassis, which are as follows:

- a. Power supply Fan two fast-tabs

- b. Power Supply Thermostat one 2-pin Mate-N-Lok

- c. Memory Section Fan two fast-tabs

- d. Transformer Primary one 6-socket Mate-N-Lok

- e. Power Control one 6-pin Mate-N-Lok

- f. PDP-11 System AC Power Control two 3-pin Mate-N-Lok connectors on rear of mounting box (not used).

The ac cable is located on the right-hand side and rear of the ME11-L mounting box and is inherently shielded by the Power Supply chassis, and the mounting box.

#### 2.2.2 Specifications

Tables 2-1, 2-2, and 2-3 list all the Power Supply specifications according to input, output, and mechanical and environmental specifications.

| rower suppry input specifications            |                                             |  |

|----------------------------------------------|---------------------------------------------|--|

| Parameters                                   | Specifications                              |  |

| *Input Voltage (1 phase, 2 wires and ground) | 95-135/190-270V                             |  |

| Input Frequency                              | 47–63 Hz                                    |  |

| Input Current                                | 5/2.5A RMS                                  |  |

| Input Power                                  | 325W at full load                           |  |

| Inrush                                       | 80/40A peak, 1 cycle                        |  |

| Rise Time of Output Voltages                 | 30 ms max. at full load, low line           |  |

| Input Overvoltage Transient                  | 180/360V, 1 sec<br>360/720V, 1 ms           |  |

| Storage After Line Failure                   | 25 ms min., starting at low line, full load |  |

| Input Breaker (part of BC05 Power Control)   | 7A/4A single-pole, manually reset, thermal  |  |

Table 2-1Power Supply Input Specifications

\*Input voltage selection, 115V or 230V, is made by specifying the appropriate AC Input Box, DEC Model BC05 (Paragraph 2.2.1.1). All specifications are with respect to the BC05 input. (continued on next page)

| Parameter                                                            | Specification                                                                                       |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Thermostat Mounted on Heat Sink (opens<br>transformer and fan power) | 277V 7.2A contacts<br>Opens 98–105°C<br>Automatically resets 56–69°C                                |  |

| Input Connections                                                    | Line cord on BC05 Power Control, length<br>and plug type specified with BC05<br>(Paragraph 2.2.1.1) |  |

| Turn-On/Turn-Off                                                     | Application or removal of power                                                                     |  |

| Hipot (input to chassis and output)                                  | 2.1 kV/dc, 60 sec                                                                                   |  |

# Table 2-1 (Cont)Power Supply Input Specifications

| Parameter                                         | Specification                          |  |  |

|---------------------------------------------------|----------------------------------------|--|--|

| +5V                                               |                                        |  |  |

| Load Range                                        |                                        |  |  |

| Static                                            | 0–15A                                  |  |  |

| Dynamic #1                                        | ±5A (within 0–17A load range)          |  |  |

| Dynamic #2                                        | No load – full load                    |  |  |

| Max. Bypass Capacitance in load for 30-ms turn-on | 2000 µF                                |  |  |

| Overvoltage Crowbar (blows fuse)                  | 5.7–6.8V actuate (7V abs. max. output) |  |  |

| Current Limit at 25°C                             | 24–29.4A (–0.1A/°C)                    |  |  |

| Backup Fuse (series with raw dc)                  | 15A                                    |  |  |

| Adjustment Range                                  | ±5% min.                               |  |  |

| Regulation                                        |                                        |  |  |

| Line                                              | ±0.5%                                  |  |  |

| Static Load                                       | 3%                                     |  |  |

| Dynamic Load #1                                   | ±2%                                    |  |  |

| Dynamic Load #2                                   | ±10%                                   |  |  |

| Ripple and Noise                                  | 4% peak-to-peak                        |  |  |

| 1000 Hour Drift                                   | ±0.25%                                 |  |  |

| Temperature (0–60°)                               | ±1%                                    |  |  |

| -15                                               | V                                      |  |  |

| Load Range                                        |                                        |  |  |

| Static                                            | 0-7A                                   |  |  |

| Dynamic#1                                         | $\Delta I = 5A (0.5A/\mu s)$           |  |  |

| Dynamic #2                                        | No load – full load $(0.5A/\mu s)$     |  |  |

| Table 2-2 |        |        |                |

|-----------|--------|--------|----------------|

| Power     | Supply | Output | Specifications |

(continued on next page)

| Parameter                                         | Specification                     |  |  |

|---------------------------------------------------|-----------------------------------|--|--|

| -15V (Cont)                                       |                                   |  |  |

| Max. Bypass Capacitance in load for 30-ms turn-on | 1000 μF                           |  |  |

| Overvoltage Crowbar (blows fuse)                  | 17.4-20.5V (22V abs. max. output) |  |  |

| Current Limit at 25°C                             | 10–13.3A (–0.03 A/°C)             |  |  |

| Backup Fuse (series with raw dc)                  | 5A                                |  |  |

| Adjustment Range                                  | ±5% min.                          |  |  |

| Regulation                                        |                                   |  |  |

| Line and Static Load                              | ±1%                               |  |  |

| Dynamic Load #1                                   | ±2.5%                             |  |  |

| Dynamic Load #2                                   | ±3%                               |  |  |

| Ripple and Noise                                  | 3% peak-to-peak                   |  |  |

| 1000 Hour Drift                                   | ±0.25%                            |  |  |

| Temperature (0–60°C)                              | ±1%                               |  |  |

# Table 2-2 (Cont)Power Supply Output Specifications

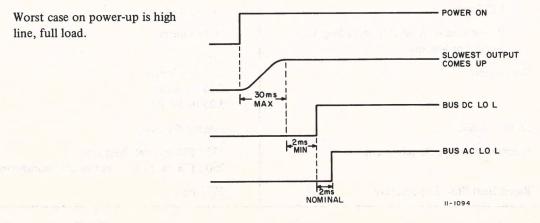

#### BUS DC LO L and BUS AC LO L

Static Performance at Full Load (for 230V connection, double below voltages)

BUS DC LO L goes to high BUS AC LO L goes to high

BUS AC LO L drops to low

BUS DC LO L drops to low

Hysteresis (contained in above specifications)

Output voltages still good

74-80 Vac line voltage

8-11V higher

80-86 Vac line voltage

7-10V lower

3-4 Vac

70 Vac line voltage

(continued on next page)

| Table 2-2 (Cont) |        |                              |

|------------------|--------|------------------------------|

| Power            | Supply | <b>Output Specifications</b> |

| Parameter                                            | Specification                                                          |

|------------------------------------------------------|------------------------------------------------------------------------|

| Weight<br>DC Regulator                               | 7 lb approx.                                                           |

| Power Chassis Assembly including AC Regulator Module | 18 lb approx.                                                          |

| Dimensions                                           | 16.50 in. length<br>5.19 in. width<br>3.25 in. height                  |

| Cooling Means                                        | Integral 5 in. fan                                                     |

| Minimum Cooling Requirements                         | 375 CFM through heat sink<br>250 CFM over caps, chokes, and transforme |

| Rated Heat Sink Temperature                          | 95°C max.                                                              |

Table 2-3

Mechanical and Environmental Specifications

(continued on next page)

| Parameter                     | Specification                                                                                                      |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Shock, Non-Operating          | 40G (duration 30 ms) 1/2 sine in each of six orientations                                                          |

| Vibration, Non-Operating      | 1.89G RMS average, 8G peak; varying<br>from 10 to 50 Hz, 8 dB/octave roll-off<br>50–200 Hz; each of six directions |

| Ambient Temperature           | 0 to +60°C operating<br>-40 to +71°C storage                                                                       |

| Relative Humidity<br>Altitude | 95% max. (without condensation)<br>10K ft                                                                          |

Table 2-3 (Cont)

Mechanical and Environmental Specifications

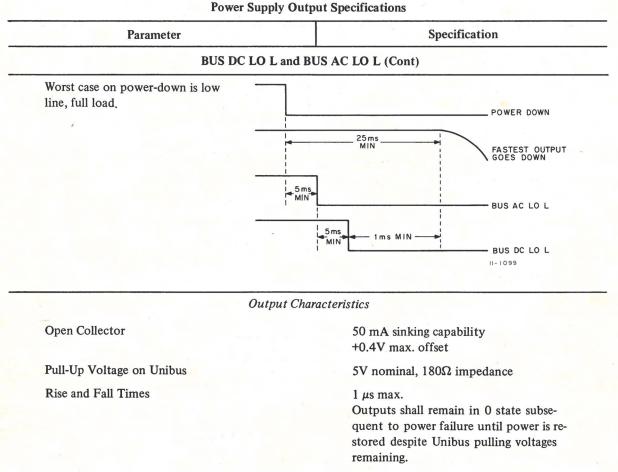

Output parameters are specified at the pins of the 9-pin Mate-N-Lok connector (Figure 2-3) which plugs into the output connector on the 5409728 module. All output voltages are given with respect to the common ground pin on this connector. IR drops in the distribution wiring are minimized to achieve good regulation at the load. Recommended distribution loss is 3 percent maximum.

The circuit connected to pins 4, 5, 7 and 8 is not used in the ME11.

Figure 2-3 H740 Output Connector (5409728 Regulator Module)

#### 2.3 DETAILED DESCRIPTION

The following paragraphs discuss the AC Input Circuit and the DC Regulator Module. A detailed circuit level description is provided. The AC Input Circuit description discusses the Power Supply interconnections, Power Control, transformer, Power Control circuit breaker, and the Power Supply thermostat. The DC Regulator Module description discusses the generation at the circuit level of each of the three Power Supply outputs.

#### 2.3.1 AC Input Circuit

A detailed ac interconnection diagram is shown in Figure 2-4. Figures 2-5 and 2-6 illustrate the connections in schematic form.

The line cord, single-pole breaker, RFI capacitors, and connections for transformer 115V or 230V wiring are contained in the Power Control Unit. To select 115V input or 230V input, use the BC05H or BC05J Power Control, respectively.

The transformer is rated for 47 to 63 Hz and is equipped with two windings that are connected by the Power Control in parallel for 115V operation, and in series for 230V. The fans are connected across half of the primary so that they are always provided with 115V nominal. There is an electrostatic shield between primary and secondary of the transformers.

The Power Control Unit contains a single-pole thermal circuit breaker which protects against input overload and is reset by pressing a button on the rear of the computer.

The thermostat is mounted on the Power Supply heat sink. It will open one side of the primary circuit and deenergize the Power Supply if the heat sink temperature rises to about 100°C. It will automatically reset at about 63°C.

#### 2.3.2 DC Regulator Module Operation

The discussion of the DC Regulator Module circuits in this manual is directed to the module designated 5409728-0-0, rather than the earlier module designated 5409728-YA-0. A block diagram of this module is shown in Figure 2-7. The center tapped output of the power transformer is applied to positive and negative rectifier and filter circuits. The rectifier circuits produce +28V and -28V nominal raw dc voltages which are unregulated but well filtered by the input storage capacitors.

The +28 Vdc is used by an efficient switching regulator circuit to produce the +5 Vdc output. Provisions for overcurrent detection are incorporated in the regulator circuit so that excess current is limited when there is a malfunction in the load. The +5V output is also protected against overvoltage by a crowbar circuit which limits the output to under 7V; before the output gets to this value, the crowbar circuit blows the fuse in the output circuit of the rectifier.

The -28 Vdc is used by the -15V circuit which is similar in operation to the +5V regulator circuit. The -15V crowbar circuit limits the output to 22V.

The BUS AC LO L and BUS DC LO L signals are used to warn the Unibus of imminent power failure. Circuits on the regulator module detect the transformer secondary voltage and generate two timed TTL-compatible open-collector signals that are used for power fail functions by devices on the Unibus. Note that this circuit does not detect the regulated dc output voltages as in some other PDP-11 processors and peripherals.

2.3.2.1 Generation of  $\pm$  Raw DC – As stated in the previous paragraph the center-tapped transformer secondary voltage is rectified and filtered prior to being fed to the two DC Regulator Module circuits.

The circuitry involved is shown in Figure 2-8. The bridge rectifier D14 is mounted on the heat sink and the input capacitors C1 and C2 are mounted on the bottom of the regulator module. These capacitors filter the dc input and are large enough to provide at least 25-ms storage when the input power is short circuited or fails.

A fuse is used on each output to protect the regulator and load during faults. The fuses will not normally blow when a regulator output is shorted since the three outputs are electronically overcurrent protected. However the appropriate fuse will blow in the case of a +5V or -15V overvoltage crowbar or a failure in one of the over-current circuits.

3

Figure 2-4 AC Interconnection Diagram

Figure 2-5 115V Connections, Simplified Schematic Diagram

Figure 2-6 230V Connection, Simplified Schematic Diagram

The resistor across each fuse provides a slow (100-150 sec) discharge of C1 or C2 after the power is turned off, should a fuse blow. The capacitors are placed ahead of the fuse to limit the energy in any fault and thus better protect the outputs.

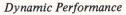

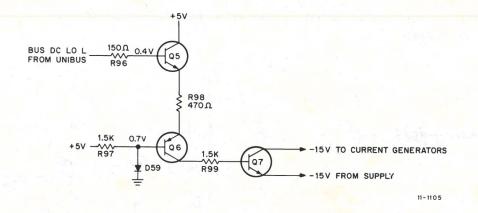

2.3.2.2 BUS AC LO L and BUS DC LO L Circuits – The circuitry shown in Figure 2-9 generates the timed Unibus power status signals described in Table 2-2. These are used for power fail functions. The transformer secondary voltage is rectified by D1 and D2 and filtered by C9 and R1, R14.

Circuit parameters are chosen so that the voltage across C9 will rise slower than the two regulated output voltages on power-up, and will decay faster than the two regulated output voltages on power-down.

Two differential amplifier circuits are used to detect power status: Q17, Q18 is used to generate BUS DC LO L; and Q15, Q16 is used to generate BUS AC LO L. The differential amplifiers share common reference Zener diode D3 which is fed approximately 1 mA by R3.

The diversion of the same product of the Revealed server and  $\frac{4}{3} \frac{8}{8}$  appendix the RV particle of the set the service of the diversion of the diversion of the RV particle of the test of the service of the same product of the service of

Figure 2-8 Rectifier Circuit

Figure 2-9 BUS AC LO and BUS DC LO Circuits

As C9 charges subsequent to power-up, first Q17, Q18 and then Q15, Q16 change states; the reverse is true during power-down. When C9 starts to charge, Q17 and Q16 are on and Q15 and Q18 are not conducting. As C9 charges further, Q18 starts to conduct into R7 and raises the voltage on the D3 cathode. This acts as a positive feedback and snaps Q17 off and Q18 on more solidly. A few milliseconds later, the voltage across C9 has risen sufficiently for the same process to take place in differential amplifier Q15, Q16. The status of each differential amplifier is followed by the germanium transistor open-collector output stages Q19, Q20 for DC LO L, and Q13, Q14 for AC LO L. These stages clamp the Unibus at about +0.4V until the differential amplifier circuits sequentially signal them across R11 and R12 that power is up. The outputs then rise sequentially to about +5V as dictated by the Unibus loading and pull-up termination resistors. The sequence is as follows:

power-up  $\rightarrow$  then BUS DC LO L = 0  $\rightarrow$  then AC LO L = 0 0 = High (+5V) power-down  $\rightarrow$  then BUS AC LO L = 1  $\rightarrow$  then DC LO L = 1 1 = Low (+0.4V)

There is sufficient storage in the regulator output capacitors C1 and C2 so that when BUS DC LO L and BUS AC LO L = 0, the output voltage is maintained long enough to permit power fail circuits to operate. Note that the open collector stages are designed to clamp the Unibus to 0.4V maximum, even when there is no ac input to the regulator. They are inherently biased by R11 and R12 until the differential amplifiers signal that power is okay.

2.3.2.3 +5V Regulator Circuit – The +5V regulator samples the output voltage and compares it to the voltage across a reference Zener with a voltage detector transistor, which in turn controls the drivers for the main pass transistor. The +5V regulator circuit is shown in Figure 2-10. An overcurrent circuit is employed.

Figure 2-10 +5V Regulator Circuit

The viewing chain consists of R49, 50, 51; the reference Zener is D9 which is fed by R44. Q10 is the detector amplifier. The pass transistor Q6 is turned on by R46. The current is diverted from the base of Q8 by off-driver Q9 which is controlled by Q10. The tendency for the output voltage to rise results in more conduction through Q10 and resultant limiting of conduction through Q6.

The +5V circuit is a regulator that operates in the switching mode for increased efficiency. To switch the regulator, positive feedback is applied to the voltage detector input via R47.

Thus, the whole regulator acts as a Schmitt trigger and is turned either completely on or off, depending on whether the output voltage is too high or too low.

When Q6 is on, it supplies current through filter choke L1 to the output smoothing capacitor C7 and the load. When Q6 is off, the L1 current decays through commutating diode D10 which becomes forward biased by the back emf of L1. The waveform across D10 is a 30V nominal rectangle pulse train. The filtered output across C7 is thus +5V with about a 200 mV peak-to-peak, 10 kHz nominal sawtooth of superimposed ripple. At the crest of the ripple, Q6 turns off, and at the valley, Q6 turns on.

This switching mode of operation limits the dissipation in the circuit to the saturated forward losses of Q6 and D10 and the switching losses of Q6. The resultant high efficiency allows the use of a small heat sink and few semiconductors.

R50 is the voltage adjustment potentiometer. R51 is a positive temperature coefficient wirewound resistor, which compensates for the negative voltage temperature coefficients of the Q10 base-emitter junction and the reference diode D9.

The overcurrent signal is generated across resistor R41, which is in series with the Q6 collector, and is detected by Q5, current limited by R39, 40.

Output fault current is limited to a safe value since conduction of Q5 decreases the reference voltage across D9 to zero. This causes Q10 to conduct and shuts down the regulator. C5 is an averaging capacitor that is necessary in the circuit because the current through R41 is pulsating.

High-frequency bypass capacitors are used on input and output of the regulator, C3 and C6, respectively. C4 is used to slow down the turn-on of Q6 to allow D10 to recover from the on state without a large reverse current spike.

Should a malfunction cause the output voltage to increase beyond about 6.8V nominal, Zener diode D2 will conduct and fire silicon-controlled rectifier Q11. This will crowbar the output voltage to a low value through D11 and will blow fuse F1 in the rectifier circuit through R52.

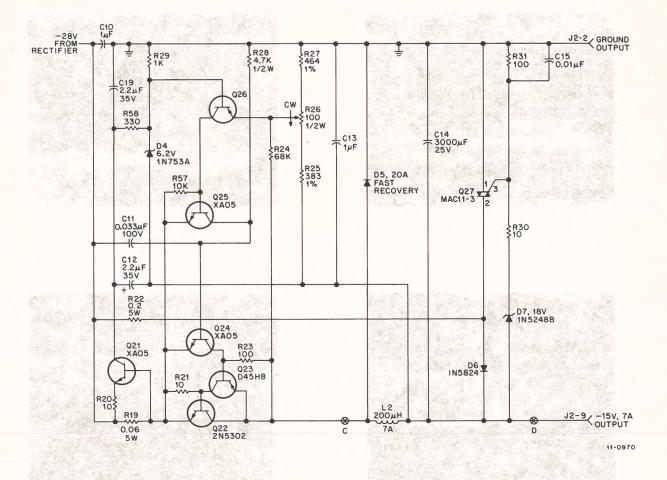

2.3.2.4 -15V Regulator Circuit – The – 15V regulator circuit is shown in Figure 2-11. The – 15V output voltage is adjusted by potentiometer R26. It is essentially the complement of the +5V regulator circuit and differs only in the following minor details:

- a. The crowbar device is a Triac Q27 instead of an SCR

- b. No temperature compensating resistor is required since Q26 and D4 track each other

- c. The detailed interconnection of the drivers and the circuit values are different

#### 2.4 MAINTENANCE

This paragraph discusses the adjustments, circuit waveforms, troubleshooting, and parts identification necessary to maintain the Power Supply. The adjustments section discusses the two output potentiometers. The circuit waveforms section provides a guide to proper operation at various places in the circuit. The troubleshooting section provides rules, hints, and a troubleshooting chart as a maintenance aid in isolating Power Supply malfunctions. Finally, the parts identification section provides a directive to obtaining parts information for the entire Power Supply unit through a parts location directory to the mechanical engineering drawings in the *ME11-L* Engineering Drawing Manual.

Figure 2-11 -15V Regulator Circuit

#### 2.4.1 Adjustments

There are only two adjustments to the Power Supply for the +5V and -15V dc output voltages. (A small screwdriver is all that is required for adjustment.) Clockwise adjustment of any of the potentiometers increases voltage. The potentiometers are located on the top side of the DC Regulator Module and are designated as R50 for +5V and R26 for -15V. A +15V adjustment potentiometer and circuitry are also located on the DC Regulator Module, but this supply voltage is not used in the ME11-L and it is not necessary to adjust the +15V potentiometer.

#### **CAUTION**

Do not adjust voltages beyond their 105 percent rating. Adjust slowly in order to avoid overvoltage crowbar blowing dc output fuses. Do use a calibrated voltmeter; preferably a digital voltmeter. Voltages should be adjusted to their center values: +5.0, and -15.0; all under load at the DC Cable termination on the system unit.

#### 2.4.2 Circuit Waveforms

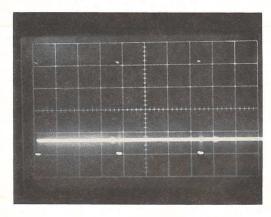

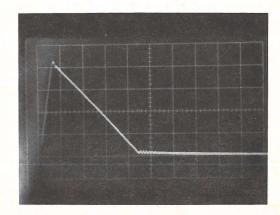

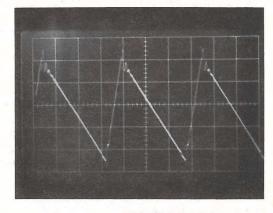

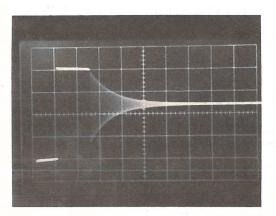

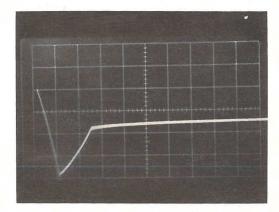

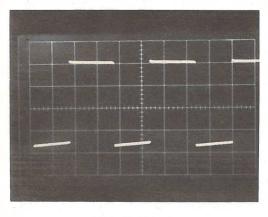

The two basic regulator circuits used on the DC Regulator Module generate +5V and -15V. Figure 2-12 shows six waveforms of the +5V regulator circuit taken at two points (A and B) in the circuit (Figure 2-10). Waveforms a, b, and c are taken at point A, which is the +5V circuit, Q6 transistor output. Waveforms d, e, and f are taken at point B, which is the +5V Power Supply output (J2-3). Figure 2-12 also indicates the load conditions and time

a) Point A, No load, 2 ms/div, and 10V/div.

à

d) Point B, No load, 2 ms/div, and 50 mV/div.

b) Point A, No load, 20 μs/div, and 10V/div.

e) Point B, No load, 20 μs/div, and 50 mV/div.

c) Point A, 20A load.

20 μs/div, and

10V/div.

f) Point B, 20A load, 20 μs/div, and 50 mV/div.

Figure 2-12 +5V Regulator Circuit Waveforms

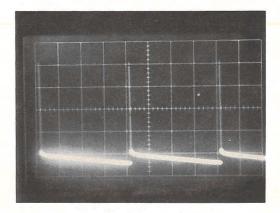

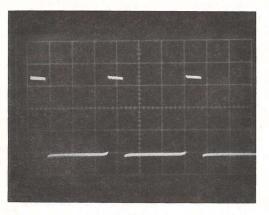

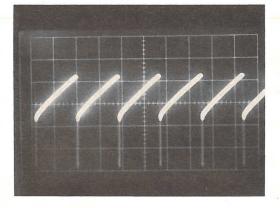

scales for each waveform. Figure 2-13 shows six waveforms of the -15V regulator circuit taken at two points (C and D) in the circuit (Figure 2-11). Waveforms a, b, and c are taken at point C, which is the -15V circuit, Q22 transistor output. Waveforms d, e, and f are taken at point D, which is the -15V Power Supply output (J2-9). The load conditions and time scales of the respective waveforms are also indicated in Figure 2-13. These waveforms were taken on a Tektronix Model 453 oscilloscope.

#### 2.4.3 Troubleshooting

Troubleshooting information for the Power Supply consists of rules, hints, and a troubleshooting chart. This information provides a maintenance aid for isolating Power Supply malfunctions.

2.4.3.1 Troubleshooting Rules - Troubleshooting rules for the Power Supply are as follows:

- a. Be sure that power is turned off and unplugged before servicing the Power Supply.

- b. Be sure that input capacitors C1 and C2 are discharged before servicing the Power Supply. A 10 to  $100\Omega$ , 10W resistor can be used to speed up discharge of the capacitors. (Be sure power is off.)

- c. The DC Regulator Module is not internally grounded to the chassis. Shorts to ground can be located after disconnecting the dc output cable from the system unit.

- d. The dc output fuses F1 and F2 can be replaced without removing the DC Regulator Module. Before unsoldering the fuses, observe the cautions described in a and b above.

- e. For proper operation, all hardware must be secured tightly with about 12 inch-pounds torque (i.e., capacitors, chokes, semiconductors). All hardware should be replaced with identical hardware replacement parts.

- f. The DC Regulator Module may be removed from the top of the Power Chassis Assembly while the latter is still bolted to the ME11-L chassis.

- g. When replacing power semiconductor components that are secured to the heat sink, apply a thin coat of Wakefield #128 compound or Dow Silicone Grease to heat sink contact side (bottom) of the semi-conductor.

#### 2.4.3.2 Troubleshooting Hints

#### CAUTION Unplug ME11-L before servicing.

The most likely source of Power Supply malfunction is the DC Regulator Module. A quick remedy for a malfunction may be to replace the entire module. The problem, however, could be a short in the system unit, a defective component, or a problem in the ac input circuit.

The +5V and -15V regulators contain overvoltage detection circuitry. If R50 or R26 are adjusted too far clockwise, the corresponding crowbar circuit trips and blows a fuse. To correct this condition, adjust the potentiometer fully counter-clockwise, replace the blown fuse, and re-adjust according to Paragraph 2.4.1.

Make a visual examination of the circuitry. Check for burned resistors, cracked transistors, burned printed circuit board etch, oil leaking from capacitors, and loose connections. If a malfunction is caused by something of this nature, a visual check can quickly locate it.

a) Point C, No load, 5 ms/div, and 10V/div.

b) Point C, No load, 50 μs/div, and 10V/div.

61

.

d) Point D, No load, 5 ms/div, and 50 mV/div.

e) Point D, No load, 50 μs/div, and 50 mV/div.

c) Point C, 5A load, 50 μs/div, and 10V/div.

f) Point D, 5A load, 50 μs/div, and 50 mV/div.

Figure 2-13 -15V Regulator Circuit Waveforms

**2.4.3.3** Troubleshooting Chart – In checking the various areas of the Power Supply, the rules listed in Paragraph 2.4.3.1 should be followed. The waveforms referenced in Paragraph 2.4.2 provide a comparison for the trouble-shooting readings. Table 2-4 provides a chart of problems and causes for troubleshooting the Power Supply.

| Problem                                                                      | Cause                                                                                                                                                          |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No +5V Output                                                                | F1 opened<br>D14 or transformer opened<br>+5V adjusted too high*                                                                                               |

| +5V Output Too Low                                                           | Q5, D9, Q10, Q9, Q11, D2, or D10 shorted<br>C5 or C7 shorted<br>R49, R50, R51, R46, or R44 opened<br>Q6, Q7, Q8, or D11 shorted<br>Q9, Q10, or D9 opened       |

| No –15V Output                                                               | F2 opened<br>D14 or transformer opened<br>–15V adjusted too high*                                                                                              |

| –15V Output Too Low                                                          | Q25, D4, Q26, Q21, Q27, D7, or D5 shorted<br>C14 or C12 shorted<br>R22, R26, R25, R27, or R29 opened<br>Q22, Q23, Q24, or D6 shorted<br>Q25, Q26, or D4 opened |

| BUS AC LO L Will Not Go High                                                 | Q13, Q14, or Q15 shorted<br>Q16 or D3 opened<br>R7, R3, R6, or R8 opened<br>C9 shorted                                                                         |

| BUS AC LO L Will Not Go Low and/or Acts<br>Erratically on Power-On/Power-Off | Q13, Q14, or Q16 opened<br>Q15 or D3 shorted<br>R12, R13, R7, or R10 opened                                                                                    |

| BUS DC LO L Will Not Go High                                                 | Q19, Q20, or Q18 shorted<br>Q17 or D3 opened<br>R7, R3, or R6 opened<br>C9 shorted                                                                             |

| BUS DC LO L Will Not Go Low and/or Acts<br>Erratically on Power-On/Power-Off | Q19, Q20, or Q17 opened<br>Q18 or D3 shorted<br>R9, R10, R11, or R8 opened                                                                                     |

Table 2-4Power Supply Troubleshooting Chart

\* These causes make the crowbar fire, which in turn blows the appropriate fuse.

#### 2.4.4 Parts Identification

Parts identification for the Power Supply is provided in the *ME11-L Engineering Drawing Manual*. The assembly drawings and associated parts lists provide the respective unit parts, their part designations, and DEC part numbers. These drawings and their numbers are as follows:

Module Utilization 15-Bit 18-Mil Memory Regulator Board Circuit Schematic Circuit Schematic Line Set BC05H AC Input Harness DC Harness Assembly Unit Assembly ME11-L Power Supply H740 Power Supply Assembly (Parts List) Software List Accessory List D-MU-ME11-L-01 B-DD-MM11-L E-IA-5409728-0-0 D-CS-5409728-0-1 C-CS-5409959-0-1 B-DD-BC05H-0 E-IA-7008889-0-0 D-IA-7008857-0-0 D-UA-ME11-L-0 D-AD-7008731-0-0 A-PL-7008731-0-0 A-SL-ME11-L-4 A-AL-ME11-L-3

## CHAPTER 3 MM11-L CORE MEMORIES

#### **3.1 INTRODUCTION**

This chapter provides the user with the theory of operation and logic diagrams necessary to understand and maintain the MM11-L Read/Write Core Memories. The level of discussion assumes that the reader is familiar with basic digital computer theory. Both general and detailed descriptions of the core memories are included.

Although memory control signals and data pass through the Unibus, it is beyond the scope of this manual to describe the operation of the Unibus itself. A detailed description of the Unibus is presented in the *PDP-11 Peripherals and Interfacing Handbook*.

A complete set of engineering logic drawings is shipped with each core memory. These drawings are bound in a separate volume entitled *MM11-L Core Memories*, *Engineering Drawings*. The drawings reflect the latest print revisions and correspond to the specific memory shipped to the user.

This chapter of the manual is divided into three sections: General Description, Detailed Description, and Maintenance.

#### 3.2 GENERAL DESCRIPTION

This paragraph provides a physical description and specifications for the memory. The major functional units of each memory are briefly described and the basic memory operations are discussed.

#### 3.2.1 Physical Description

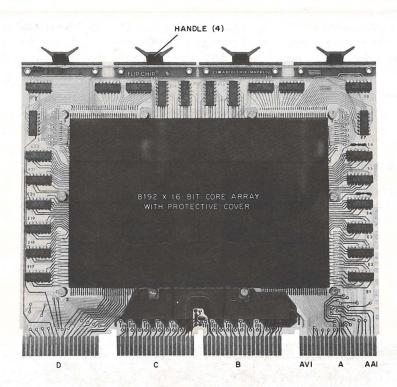

The MM11-L provides 8192 (8K) 16-bit words. This requires three standard 8-1/2 inch wide modules: two are hex-height and one is quad-height. The quad-height module contains the memory stack: module H214 for 8K. One hex-height module (G110) contains the control logic, inhibit drivers, sense amplifiers, and 16-bit data register; the other hex-height module (G231) contains the address selection logic, current generator, and switches and drivers. Pin-to-pin compatibility exists between the C, D, E, and F connectors on both these modules and the stack module connectors. The pins on the A and B connectors of both these modules are also compatible with the standard Unibus pin assignments.

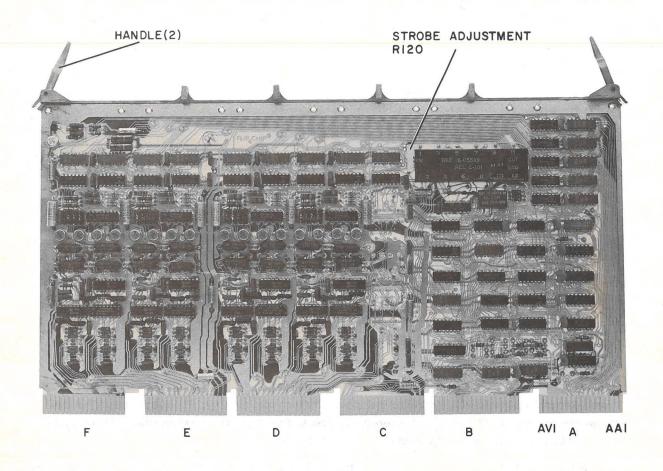

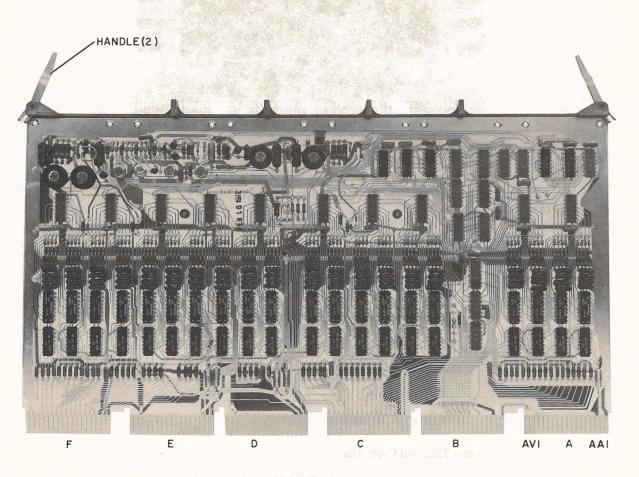

The modules are installed in the ME11-L mounting box. It is recommended that the Driver Module (G231) be installed between the Control Module (G110) and the Stack Module (H214). Photographs of the component side of the modules are shown in Figures 3-1, 3-2, and 3-3.

#### 3.2.2 Specifications

The general memory specifications are listed in Table 3-1.

Figure 3-1 Component Side of Control Module G110

#### 3.2.3 Functional Description

3.2.3.1 Introduction – The memory is a read/write, random access coincident current, magnetic core type with a cycle time of 900 ns and an access time of 400 ns. It is organized in a 3D, 3-wire planar configuration. Word length is 16 bits: MM11-L contains 8192 (8K) words.

The major functional units of the memory (Figure 3-4) are briefly described in the following paragraphs.

3.2.3.2 Control Module (G110) – The Control Module (G110) contains the memory control circuits, inhibit drivers, sense amplifiers, data register, threshold circuit, - 5V supply, and device selector.

- a. Memory Control Circuits Control circuits are provided to acknowledge the request of the master device; determine which of the four basic operations (DATI, DATIP, DATO or DATOB) is to be performed; and set up the appropriate timing and control logic to perform the desired read or write operation. If a byte operation has been selected, address line A00 L determines the byte to be selected. The actual read or write operation is selected by control lines (C00 and C01). The memory control logic also transfers data to and from the Unibus.

- b. Inhibit Drivers Each bit mat contains a single inhibit/sense line that passes through all cores on the mat. To write a 0 into a selected bit, an inhibit current is passed through the inhibit/sense line that cancels the write current in the Y line. The core does not switch so it remains in the 0 state. With no inhibit current, the currents in the X and Y lines switch the core to the 1 state.

- c. Sense Amplifiers During a read operation, the sense amplifier picks up a voltage induced in the sense/ inhibit winding when a core is switched from a 1 to a 0. This signal is detected and amplified by the sense amplifier whose output sets a data register flip-flop to store a 1. In effect, a 1 is read but the core is switched to the 0 state. Cores which were previously set to 0 are not affected.

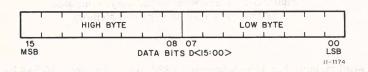

- d. Data Register The data register is a 16-bit flip-flop register used to store the contents of a word after it is destructively read out of the memory; the same word can then be written back into memory (restored) when in the DATI mode. The register is also used to accept data from the Unibus lines to accommodate the loading of incoming data into the core memory during the DATO or DATOB cycles.

- e. Device Selector The device address (bus lines A14 through A17) is decoded in the device selector to determine if the memory bank has been addressed.

- f. Threshold Circuit and -5V Supply The threshold circuit provides a reference threshold voltage to the sense amplifiers. During a read operation, if the threshold voltage ( $\pm 20$  mV) is exceeded, the sense amplifier produces an output. The -5V supply provides a negative voltage for the sense amplifiers.

Figure 3-2 Component Side of Driver Module G231

3-3

Figure 3-3 Component Side of 8K Stack Module H214

# Table 3-1 MM11-L Memory Specifications

Type:

Magnetic core, read/write, coincident current, random access

Organization:

Planar, 3D, 3-wire

#### Capacity:

8192 (8K) words for MM11-L

Access Time and Cycle Time:

|   | Bus Mode                | Cycle Time<br>Non-Interleaved | Access Time |

|---|-------------------------|-------------------------------|-------------|

| - | DATI                    | 900 ns                        | 400 ns      |

|   | DATIP                   | 450 ns                        | 400 ns      |

|   | DATO-DATOB<br>(PAUSE L) | 900 ns                        | 200 ns      |

|   | DATO-DATOB<br>(PAUSE H) | 450 ns                        | 200 ns      |

(continued on next page)

### Table 3-1 (Cont) MM11-L Memory Specifications

X-Y Current Margins:

±6% @ 0°C, ±7% @ 25°C, ±6% @ 50°C

#### Strobe Pulse Margins:

±30 ns @ 0°C, ±40 ns @ 25°C, ±30 ns @ 50°C

#### Voltage Requirements:

$+5V \pm 5\%$  with less than 0.05V ripple  $-15V \pm 5\%$  with less than 0.05V ripple

Average Current Requirements:

Stand by +5V: 1.7A -15V: 0.5A Memory Active

+5V: 3.4A -15V: 6.0A

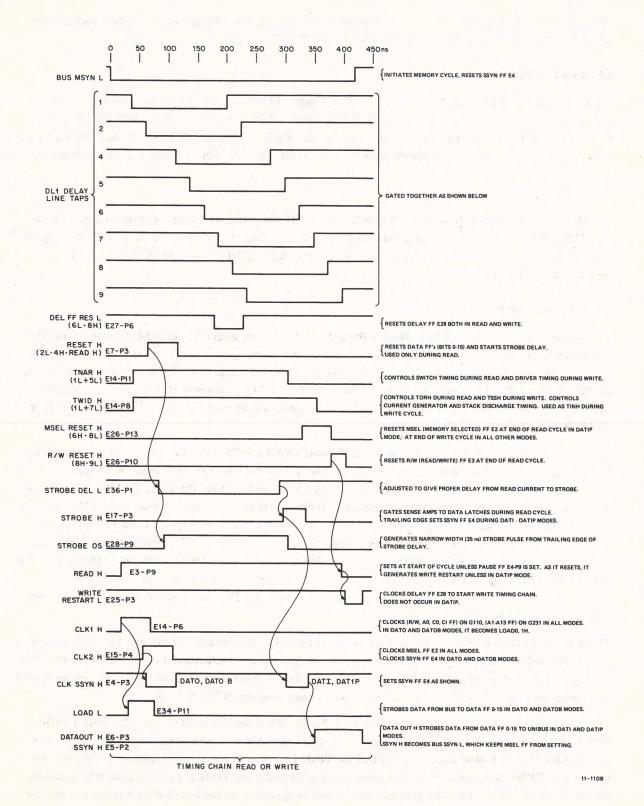

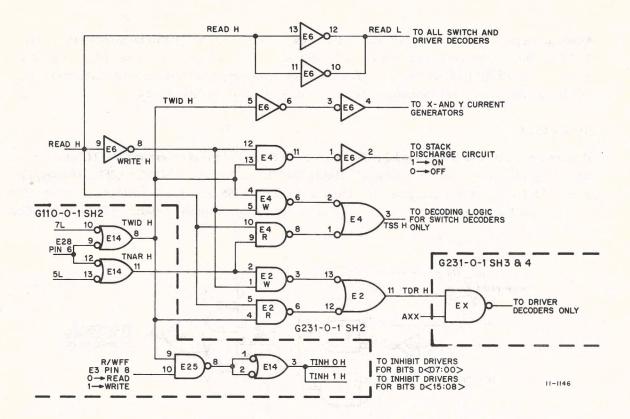

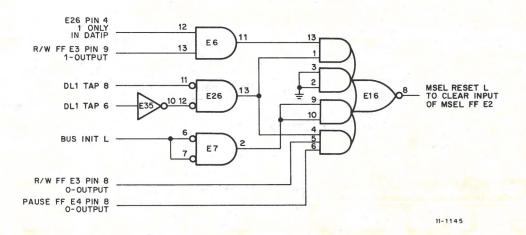

Power Dissipation (worst case):