Technical Manual Volume I Kernel System First Edition, June 1985

Copyright © 1985 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

This equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC Rules. Only peripherals (computer input/output devices, terminals, printers, etc.) certified to comply with the Class B limits may be attached to this computer. Operation with noncertified peripherals is likely to result in interference to radio or television reception.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital      | DECSYSTEM-20 | <b>MASSBUS</b> | RSX            |

|--------------|--------------|----------------|----------------|

| CTI BUS      | DECUS        | PDP            | RT             |

| DEC          | DECwriter    | P/OS           | UNIBUS         |

| DECmate      | DIBOL        | Professional   | VAX            |

| DECnet       | Digital      | Rainbow        | VMS            |

| DECsystem-10 | IVIS         | RSTS           | VT             |

|              |              |                | Work Processor |

# **CONTENTS**

### **INTRODUCTION**

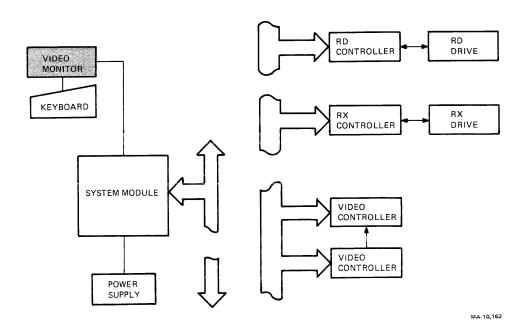

| CHAPIER                                                        | SYSTEM INTRODUCTION                                                                                                                                    |                                                      |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

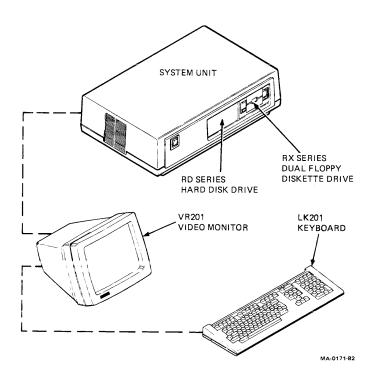

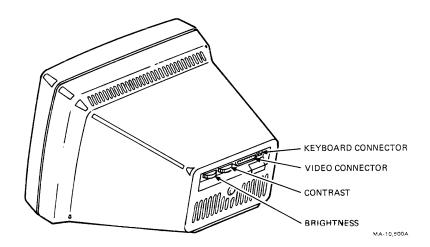

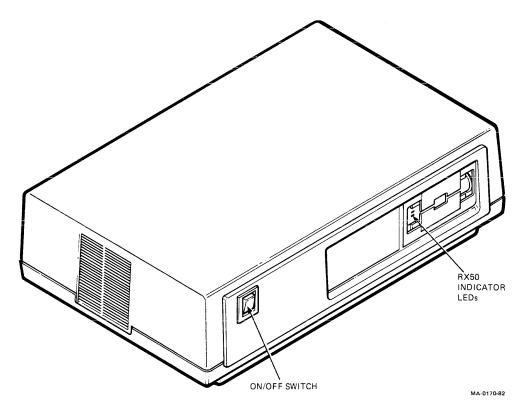

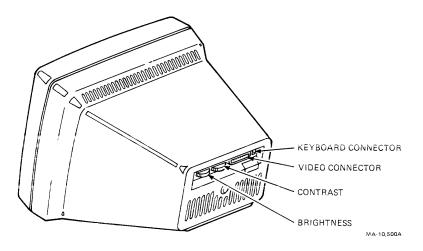

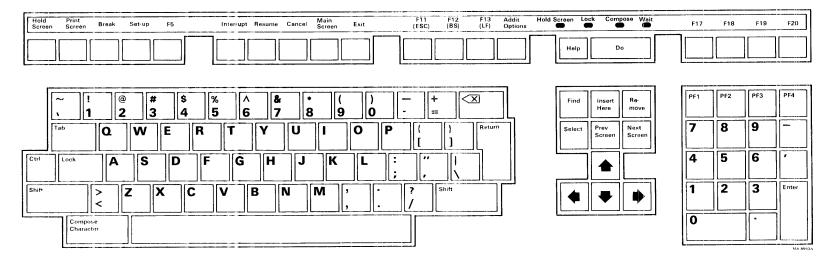

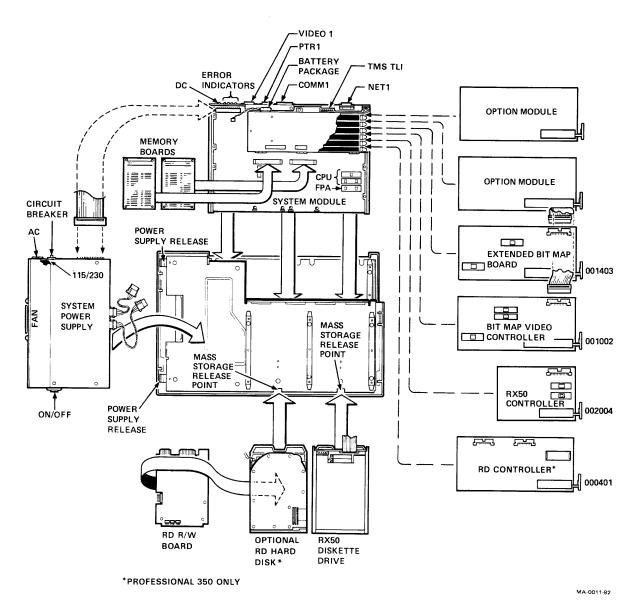

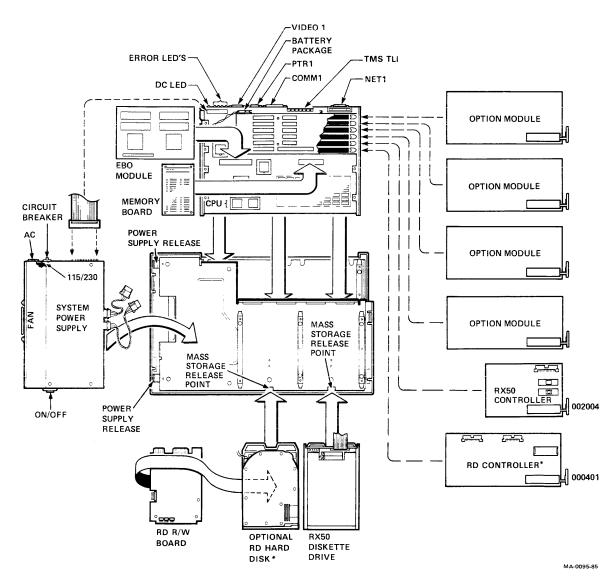

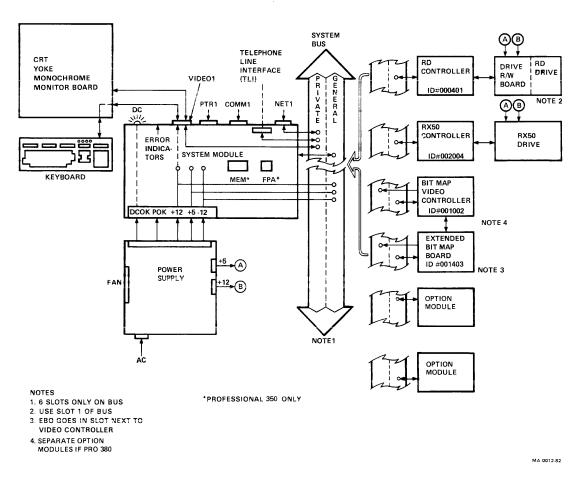

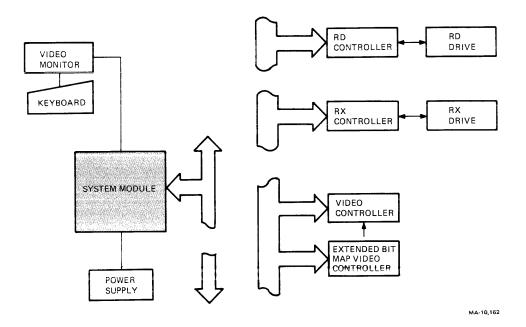

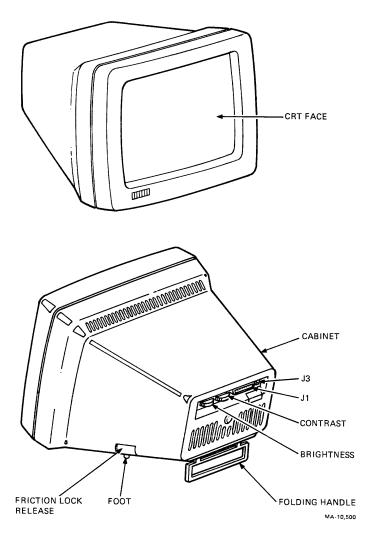

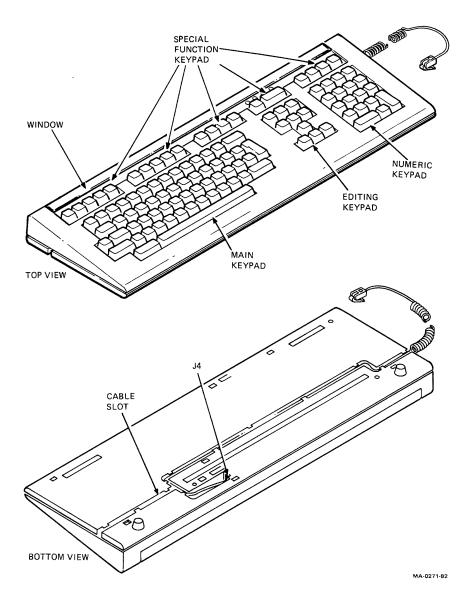

| 1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4                        | Professional 300 Series System Description System Unit Video Monitor Keyboard Professional 300 Series System Differences System Specifications         | 1-1<br>1-2<br>1-2<br>1-2<br>1-3                      |

| CHAPTER 2                                                      | INSTALLATION                                                                                                                                           |                                                      |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3<br>2.3.1 | Introduction Site Preparation Space Lighting Power Environment Professional 300 Series System Installation Packaging                                   | 2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-2<br>2-2 |

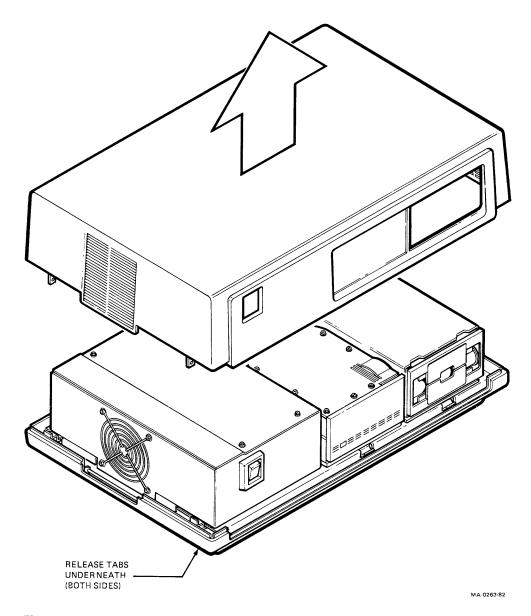

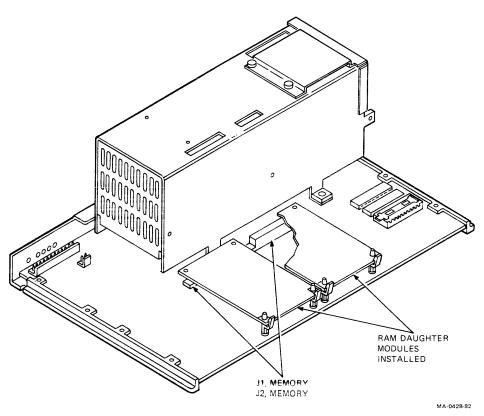

| 2.3.2<br>2.3.3<br>2.3.3.1<br>2.3.3.2                           | Installing the Professional Additional Equipment Top Cover Removal Printed Circuit Board (PCB) Module Installation                                     | 2-2<br>2-2<br>2-4<br>2-5                             |

| 2.3.3.3<br>2.3.3.4<br>2.4<br>2.4.1<br>2.4.2                    | RD-Series Mass Storage Device Installation Floating Point Adapter  Professional 300 Series System Upkeep System Cleaning Diskette Handling and Storage | 2-6<br>2-8<br>2-12<br>2-12<br>2-12                   |

## CHAPTER 3 CONTROLS AND INDICATORS

| 3.1       |                                                                             | -1                   |

|-----------|-----------------------------------------------------------------------------|----------------------|

| 3.2       |                                                                             | -1                   |

| 3.2.1     | + +=== +=+ + + + + + + + + + + + + + +                                      | -1                   |

| 3.2.1.1   |                                                                             | -1                   |

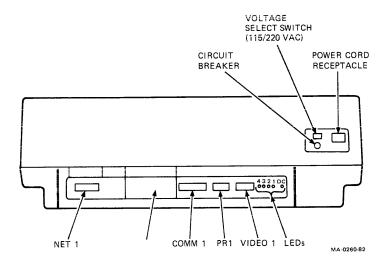

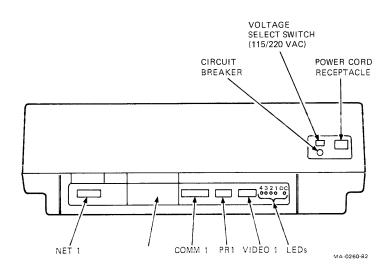

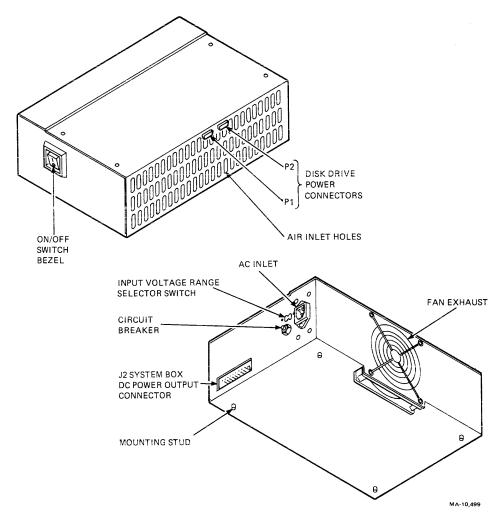

| 3.2.1.2   | Voltage Selection Switch                                                    | -2                   |

| 3.2.2     | Indicators 3                                                                | -2                   |

| 3.2.2.1   | Diskette Drive Busy Indicators                                              | -2                   |

| 3.2.2.2   | Indicators 1, 2, 3, and 4                                                   | -2                   |

| 3.2.2.3   | DC Indicator 3                                                              | -2                   |

| 3.2.2.4   |                                                                             | -2                   |

| 3.3       |                                                                             | -2                   |

| 3.3.1     |                                                                             | -2                   |

| 3.3.2     |                                                                             | -2                   |

| 3.4       |                                                                             | -4                   |

| 3.4.1     |                                                                             | -4                   |

| 3.4.1.1   | • • • • • • • • • • • • • • • • • • • •                                     | -4                   |

| 3.4.1.2   |                                                                             | -4                   |

| 3.4.1.3   |                                                                             | -4                   |

| 3.4.1.4   | - · · · · · · · · · · · · · · · · · · ·                                     | -4                   |

| 3.4.2     | - 1 · · · · · · · · · · · · · · · · · ·                                     | -4                   |

| 3.4.2.1   |                                                                             | -4                   |

| 3.4.2.2   |                                                                             | -4                   |

| 3.4.2.3   |                                                                             | -4                   |

| 3.4.2.4   |                                                                             | - <del>4</del><br>-4 |

|           |                                                                             | -4<br>-4             |

| 3.4.2.5   |                                                                             | - <del>4</del><br>-4 |

| 3.4.2.6   | TONE 3                                                                      | -4                   |

| CHAPTER 4 | SYSTEM OVERVIEW                                                             |                      |

| 4.1       | Introduction                                                                | -1                   |

| 4.2       |                                                                             | 1<br>1               |

| 4.2.1     | 2 <b>3.1.0.1.0.1.1.1.</b> 2 <b>3.0.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.</b> | 1<br>1               |

| 4.2.1.1   |                                                                             | 1<br>4               |

| 4.2.1.1   |                                                                             | 4<br>4               |

|           | <b>j</b>                                                                    | 4<br>4               |

| 4.2.1.3   |                                                                             |                      |

| 4.2.1.4   |                                                                             | -5                   |

| 4.2.2     | <b>yy</b>                                                                   | -5                   |

| 4.2.3     | ·                                                                           | -5                   |

| 4.2.3.1   | , = = =                                                                     | -5                   |

| 4.2.3.2   | 1                                                                           | -5<br>-              |

| 4.2.3.3   |                                                                             | -5                   |

| 4.2.4     |                                                                             | 6                    |

| 4.2.4.1   |                                                                             | 6                    |

| 4.2.4.2   |                                                                             | -6                   |

| 4.2.5     | •                                                                           | 6                    |

| 4.2.5.1   |                                                                             | 6                    |

| 4.2.5.2   | RD Hard Disk Drive 4                                                        | 6                    |

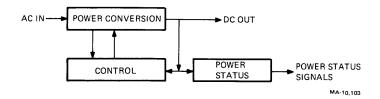

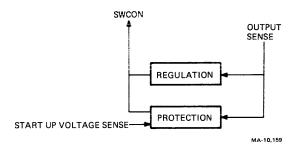

| 4.3.1       Initialization Sequence       4.8         4.3.2       Hardware Interaction Example       4.8         CHAPTER 5       SYSTEM MODULE         5.1       Introduction       5-1         5.1.1       Chapter Organization       5-3         5.1.2       Related Documentation       5-3         5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2.1       Physical Description       5-4         5.2.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9                                                                                                                          | 4.2.6     | Power Supply                          | 4-7  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|------|

| 4.3.1       Initialization Sequence       4-8         4.3.2       Hardware Interaction Example       4-8         CHAPTER 5       SYSTEM MODULE         5.1       Introduction       5-1         5.1.1       Chapter Organization       5-3         5.2       General Description       5-3         5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Physical Description       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.1       Central Processor       5-4         5.2.3.4       Power-Up Suft Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.10                                                                                                                     | 4.3       | Functional Description of Operation   | 4-7  |

| CHAPTER 5         SYSTEM MODULE           5.1         Introduction         5.1           5.1.1         Chapter Organization         5.3           5.1.2         Related Documentation         5.3           5.2         General Description         5.3           5.2.1         System Module General Description         5.4           5.2.1.1         Subsystem Characteristics         5.4           5.2.2         Physical Description         5.4           5.2.3         System Module Features         5.4           5.2.3.1         Central Processor         5.4           5.2.3.2         Memory Management         5.5           5.2.3.3         Floating Point Adapter (FPA)         5.5           5.2.3.4         Power-Up Self-Tests         5.5           5.2.3.5         Boot Sequence         5.6           5.2.4         CTI Bus Option Connectors         5.6           5.2.5         System Registers         5.6           5.2.5.1         Indicator (LED) Register and Display         5.7           5.2.6         Interrupts         5.7           5.2.7         ROM Memory         5.7           5.2.8         RAM Memory         5.7           5.2.9         V                                                               | 4.3.1     |                                       | 4-8  |

| 5.1         Introduction         5-1           5.1.1         Chapter Organization         5-3           5.1.2         Related Documentation         5-3           5.2         General Description         5-3           5.2.1.1         Subsystem Module General Description         5-3           5.2.2         Physical Description         5-4           5.2.3         System Module Features         5-4           5.2.3.1         Central Processor         5-4           5.2.3.2         Memory Management         5-5           5.2.3.3         Floating Point Adapter (FPA)         5-5           5.2.3.4         Power-Up Self-Tests         5-5           5.2.3.5         Boot Sequence         5-6           5.2.4         CTI Bus Option Connectors         5-6           5.2.5         System Registers         5-6           5.2.5.1         Indicator (LED) Register and Display         5-7           5.2.6         Interrupts         5-7           5.2.7         ROM Memory         5-7           5.2.8         RAM Memory         5-7           5.2.9         Video/Keyboard Port         5-8           5.2.10         Printer Port         5-8           5.2.11 <td>4.3.2</td> <td>Hardware Interaction Example</td> <td>4-8</td> | 4.3.2     | Hardware Interaction Example          | 4-8  |

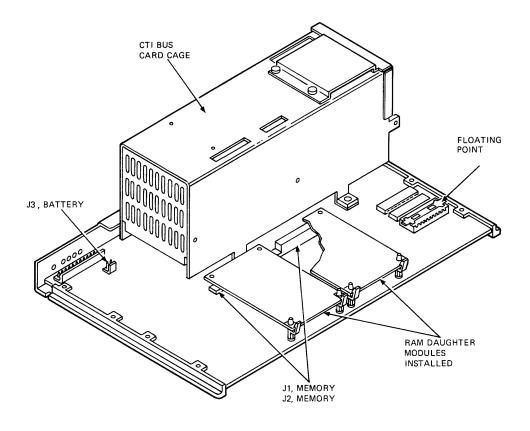

| 5.1.1       Chapter Organization       5-3         5.1.2       Related Documentation       5-3         5.2       General Description       5-3         5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Communication Port       5-8         5.2.12                                                                                                                             | CHAPTER 5 | SYSTEM MODULE                         |      |

| 5.1.2       Related Documentation       5-3         5.2       General Description       5-3         5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Comsole Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9                                                                                                                   | 5.1       | Introduction                          | 5-1  |

| 5.2       General Description       5-3         5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Communication Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-1                                                                                                                       | 5.1.1     | Chapter Organization                  | 5-3  |

| 5.2.1       System Module General Description       5-3         5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Communication Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1 <td>5.1.2</td> <td>Related Documentation</td> <td>5-3</td>                                                           | 5.1.2     | Related Documentation                 | 5-3  |

| 5.2.1.1       Subsystem Characteristics       5-4         5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-1         5.3.1.2       Data/Base Control Chip Interaction       5-15         5.3.1.3       Memory Management Interaction       5-16                                                                                              | 5.2       | General Description                   | 5-3  |

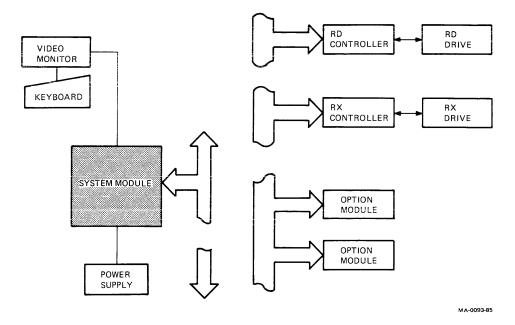

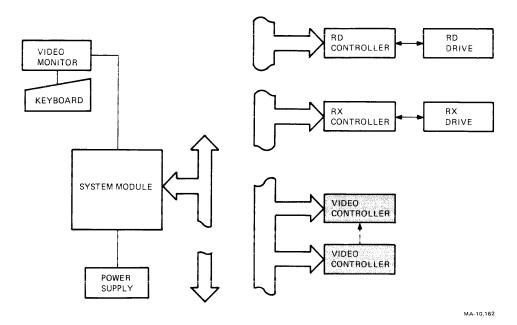

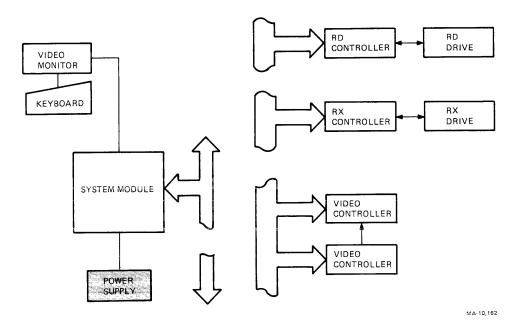

| 5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-1         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.2.1       Instruction Cycles and Timing       5-16 <td>5.2.1</td> <td>System Module General Description</td> <td>5-3</td>                     | 5.2.1     | System Module General Description     | 5-3  |

| 5.2.2       Physical Description       5-4         5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.5       System Registers       5-6         5.2.7       ROM Memory       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-1         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-15      <                                                                                                       | 5.2.1.1   | Subsystem Characteristics             | 5-4  |

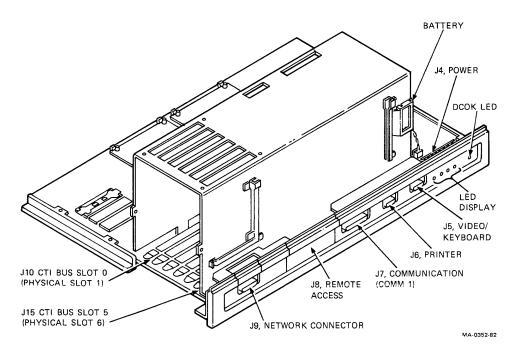

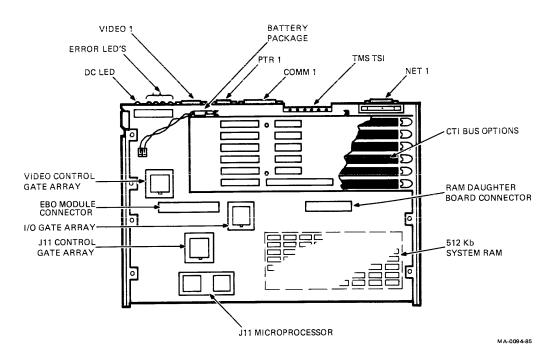

| 5.2.3       System Module Features       5-4         5.2.3.1       Central Processor       5-4         5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/ Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.2.1       Instruction Cycles and Timing       5-16 <tr< td=""><td>5.2.2</td><td></td><td>5-4</td></tr<>                                                           | 5.2.2     |                                       | 5-4  |

| 5.2.3.2       Memory Management       5-5         5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-9         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-15         5.3.1.3       Memory Management Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-21 <td>5.2.3</td> <td></td> <td>5-4</td>                                                       | 5.2.3     |                                       | 5-4  |

| 5.2.3.3       Floating Point Adapter (FPA)       5-5         5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Comsole Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-18 </td <td>5.2.3.1</td> <td>Central Processor</td> <td>5-4</td>                                       | 5.2.3.1   | Central Processor                     | 5-4  |

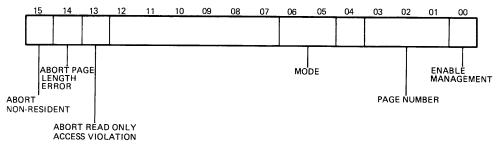

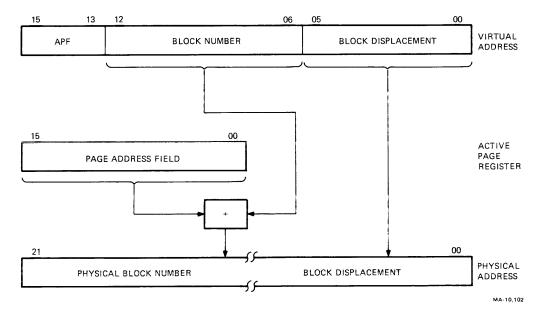

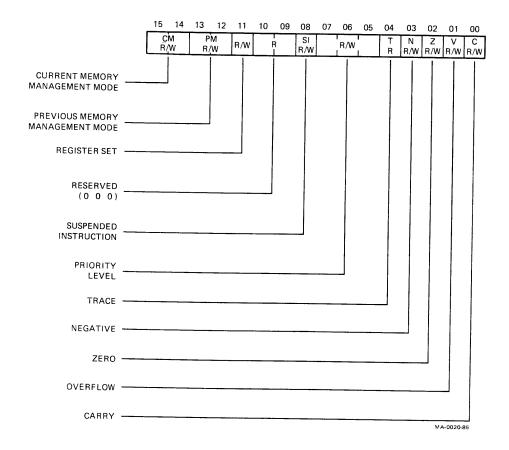

| 5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Comsole Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-18         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22<                                                                                         | 5.2.3.2   | Memory Management                     | 5-5  |

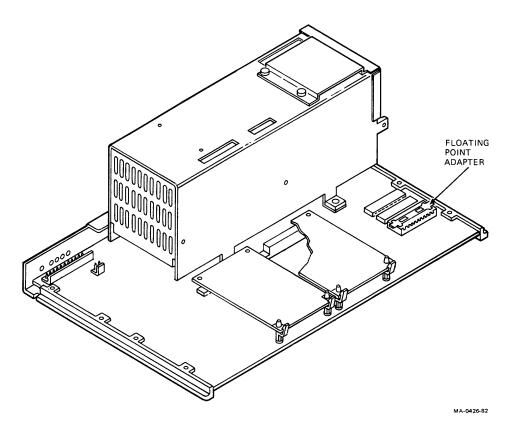

| 5.2.3.4       Power-Up Self-Tests       5-5         5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-18         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22<                                                                                         | 5.2.3.3   | Floating Point Adapter (FPA)          | 5-5  |

| 5.2.3.5       Boot Sequence       5-6         5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.5       CPU Chip Reset       5-22 <td>5.2.3.4</td> <td></td> <td>5-5</td>                                                    | 5.2.3.4   |                                       | 5-5  |

| 5.2.4       CTI Bus Option Connectors       5-6         5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Comsole Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.4       Floating Point Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.6       Service Register       5-22     <                                                                                              | 5.2.3.5   |                                       | 5-6  |

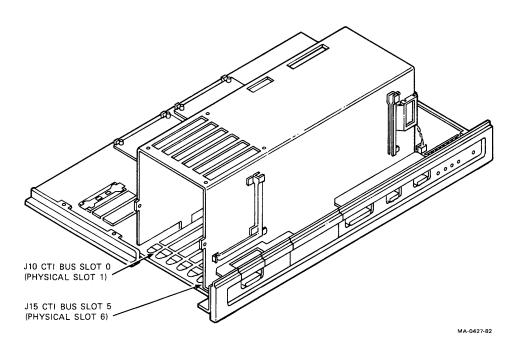

| 5.2.5       System Registers       5-6         5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.11       Console Serial Line Port       5-8         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22                                                                                              | 5.2.4     |                                       | 5-6  |

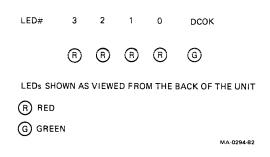

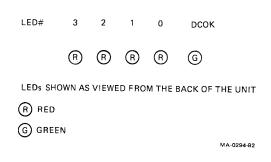

| 5.2.5.1       Indicator (LED) Register and Display       5-7         5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.8.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-15         5.3.1.3       Memory Management Interaction       5-15         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22                                                                                                         | 5.2.5     | •                                     | 5-6  |

| 5.2.6       Interrupts       5-7         5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-17         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.3       Buses       5-24 <t< td=""><td>5.2.5.1</td><td>· · · · · · · · · · · · · · · · · · ·</td><td>5-7</td></t<>                                | 5.2.5.1   | · · · · · · · · · · · · · · · · · · · | 5-7  |

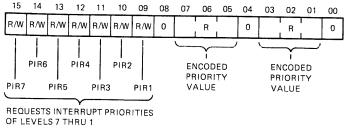

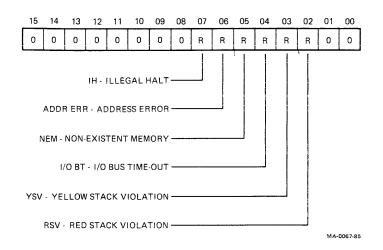

| 5.2.7       ROM Memory       5-7         5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-17         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24                                                                                                                 | 5.2.6     |                                       | 5-7  |

| 5.2.7.1       ID PROM       5-7         5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-15         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28     <                                                                                              |           | •                                     | 5-7  |

| 5.2.8       RAM Memory       5-7         5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-15         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                          |           | ·                                     | 5-7  |

| 5.2.9       Video/Keyboard Port       5-8         5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                   |           |                                       | 5-7  |

| 5.2.10       Printer Port       5-8         5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                |           | ·                                     | 5-8  |

| 5.2.10.1       Console Serial Line Port       5-8         5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                          | 5.2.10    | ·                                     | 5-8  |

| 5.2.11       Communication Port       5-9         5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                           | 5.2.10.1  |                                       | 5-8  |

| 5.2.12       Battery Backed-Up System Clock and RAM       5-9         5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                      | 5.2.11    |                                       | 5-9  |

| 5.3       Detailed Description       5-9         5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2.1       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-21         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.2.12    |                                       | 5-9  |

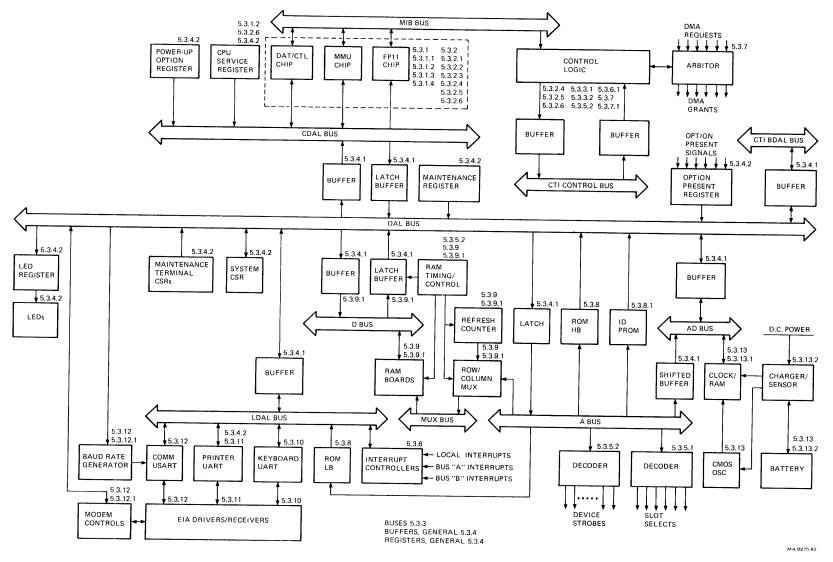

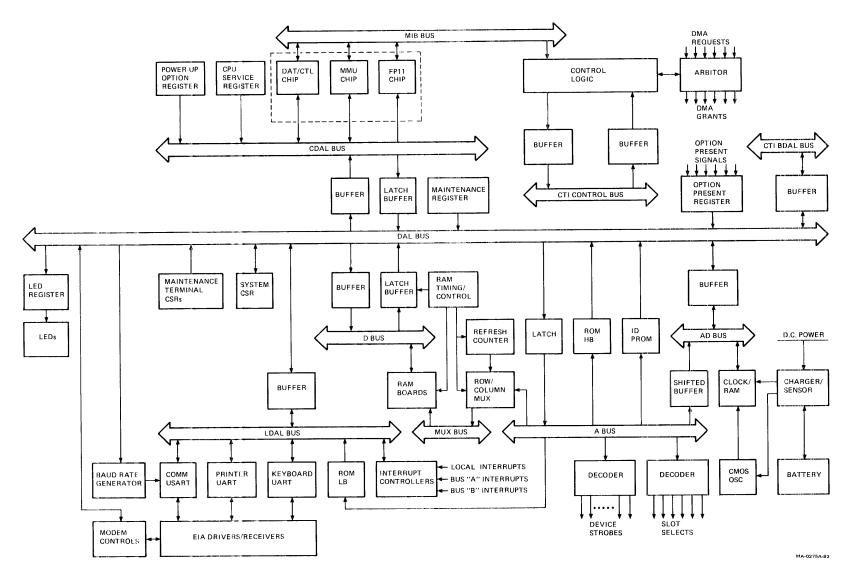

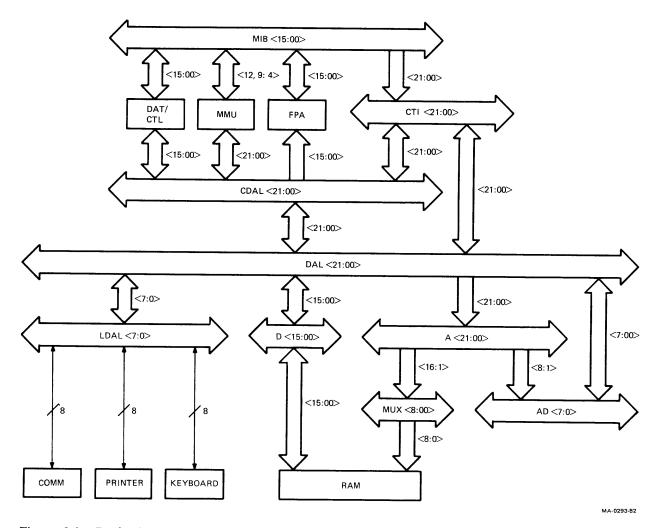

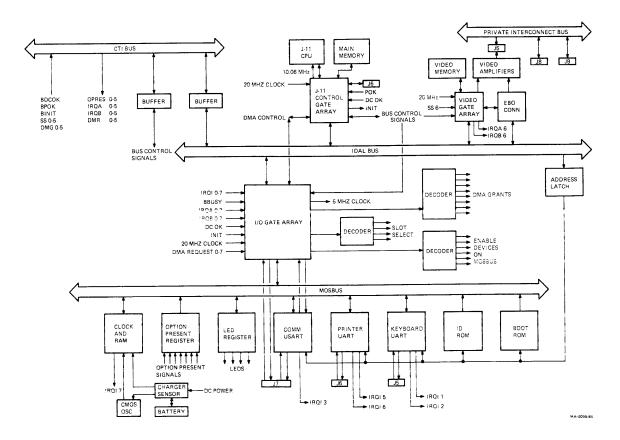

| 5.3.1       Microprocessor Overview       5-11         5.3.1.1       Chip System Architecture       5-12         5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3       |                                       | 5-9  |

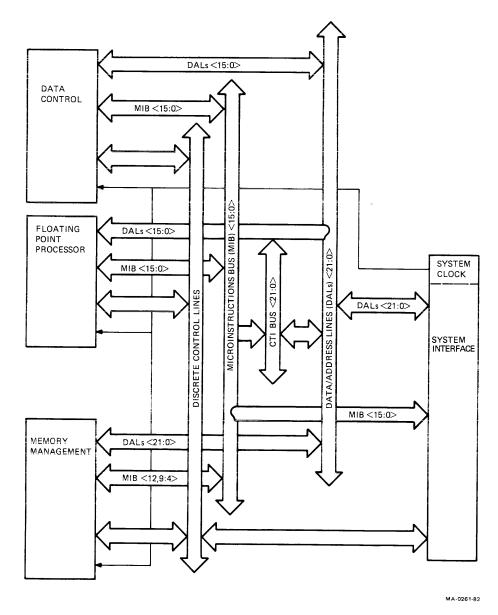

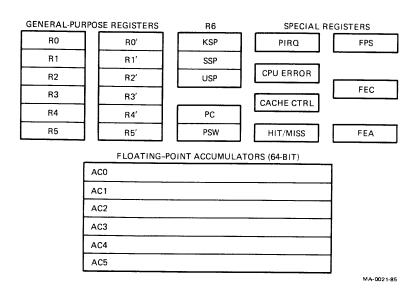

| 5.3.1.2       Data/Base Control Chip Interaction       5-12         5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3.1     | <u>-</u>                              | 5-11 |

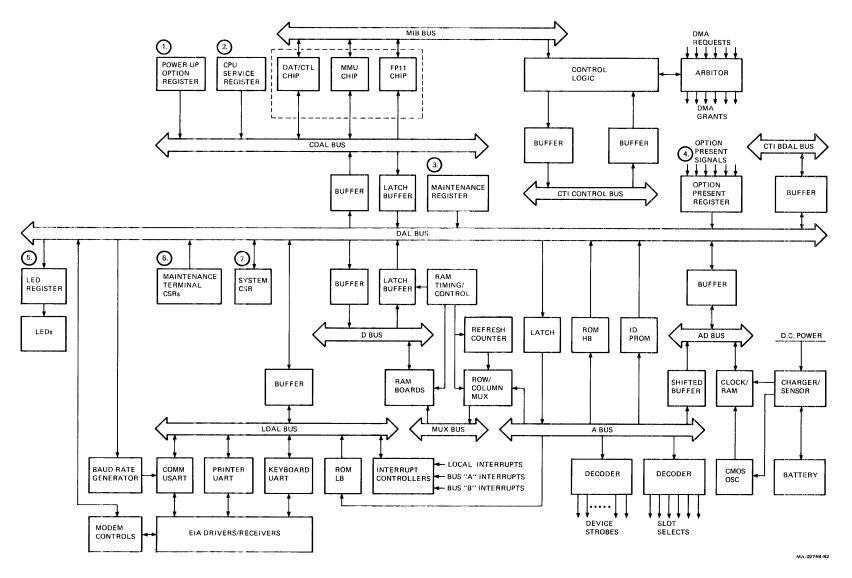

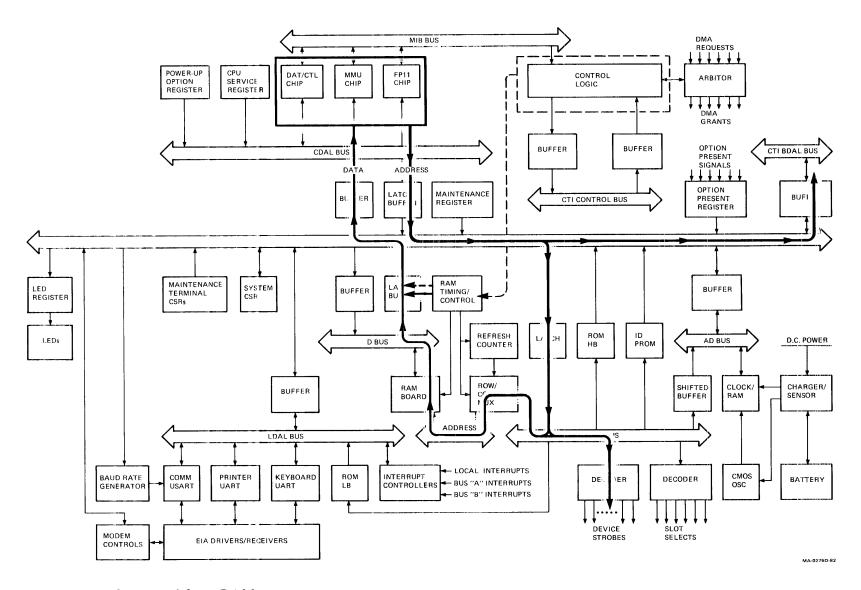

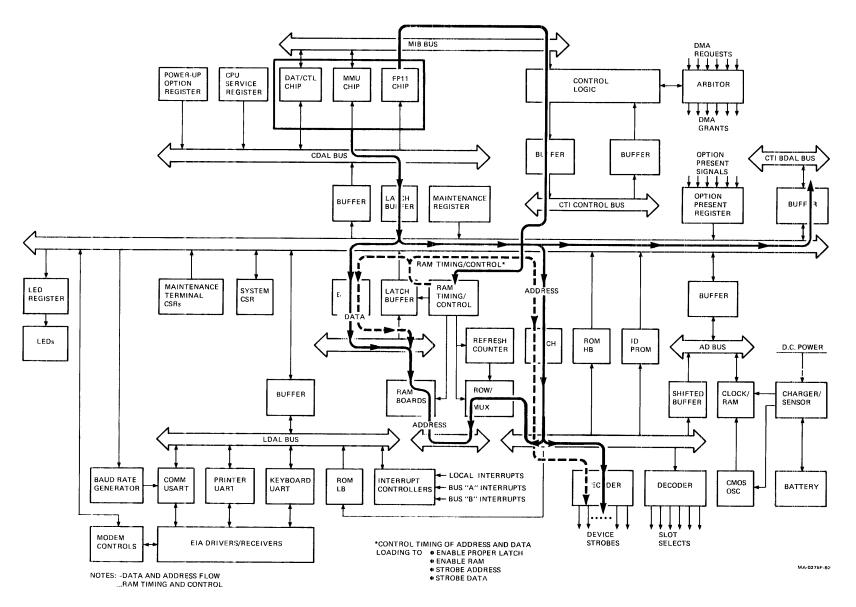

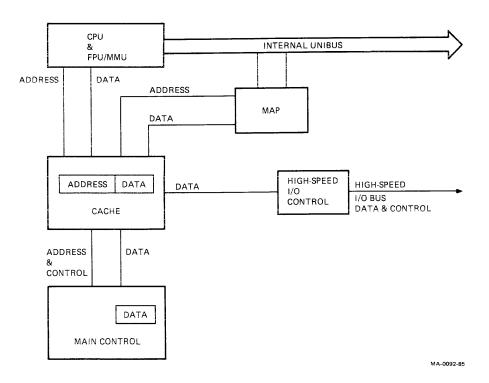

| 5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.3.1.1   | Chip System Architecture              | 5-12 |

| 5.3.1.3       Memory Management Interaction       5-15         5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.3.1.2   | Data/Base Control Chip Interaction    | 5-12 |

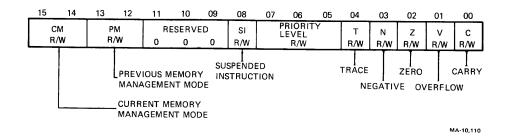

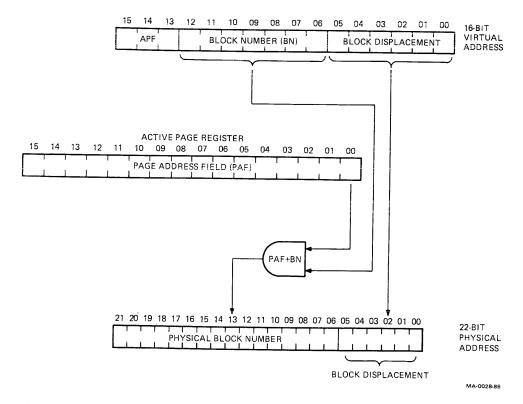

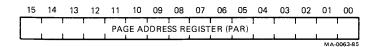

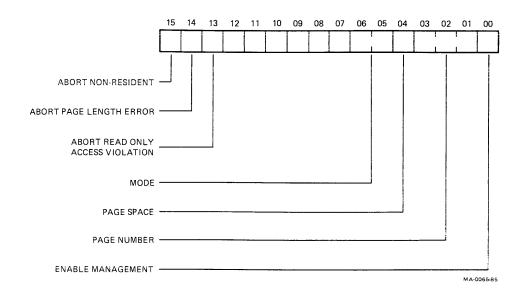

| 5.3.1.4       Floating Point Interaction       5-16         5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.3.1.3   |                                       | 5-15 |

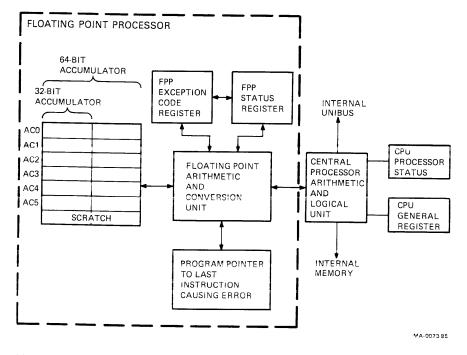

| 5.3.2       Instruction Cycles and Timing       5-16         5.3.2.1       Instruction Cycles       5-17         5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       | 5-16 |

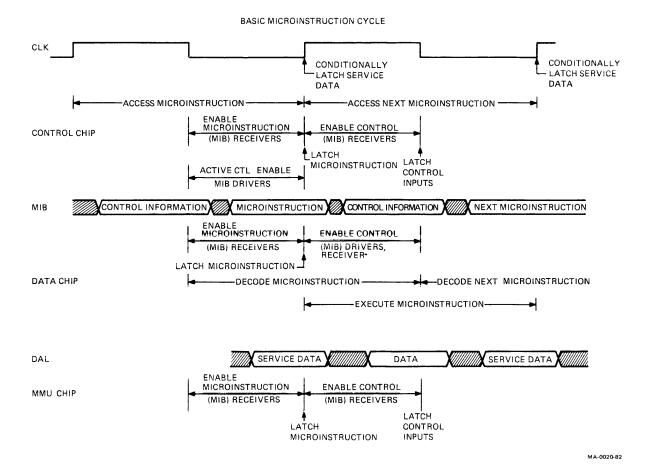

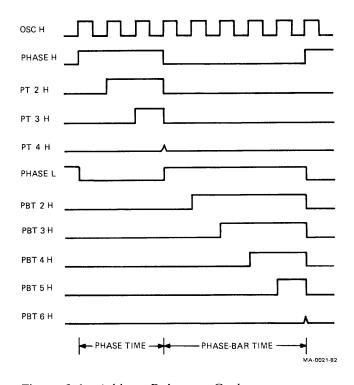

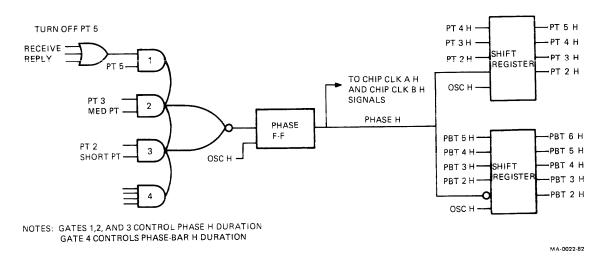

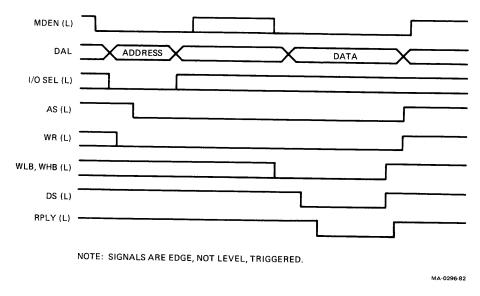

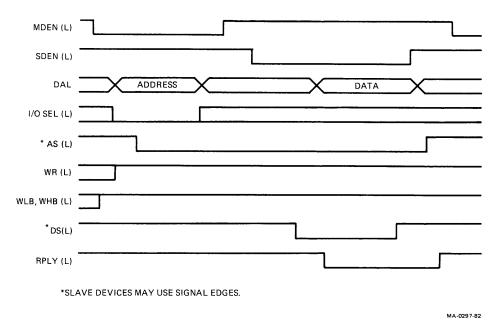

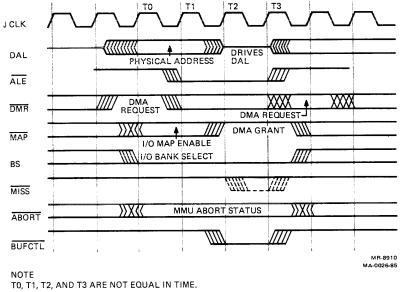

| 5.3.2.2       Basic Timing Logic       5-18         5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                       | 5-16 |

| 5.3.2.3       Detailed Timing Logic       5-21         5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.3.2.1   | Instruction Cycles                    | 5-17 |

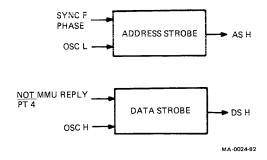

| 5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.3.2.2   | -                                     | 5-18 |

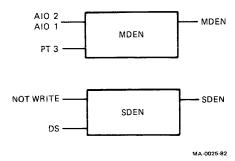

| 5.3.2.4       MIB Decode Logic       5-22         5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.3.2.3   |                                       | 5-21 |

| 5.3.2.5       CPU Chip Reset       5-22         5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3.2.4   |                                       | 5-22 |

| 5.3.2.6       Service Register       5-22         5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                       | 5-22 |

| 5.3.3       Buses       5-24         5.3.3.1       Bus Reply       5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | -                                     | 5-22 |

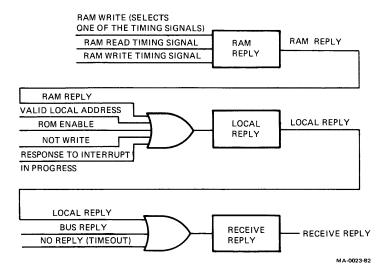

| 5.3.3.1 Bus Reply 5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | <del>-</del>                          | 5-24 |

| 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |      |

| 5.3.3.2 Other Bus Control Signals 5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | * *                                   | 5-28 |

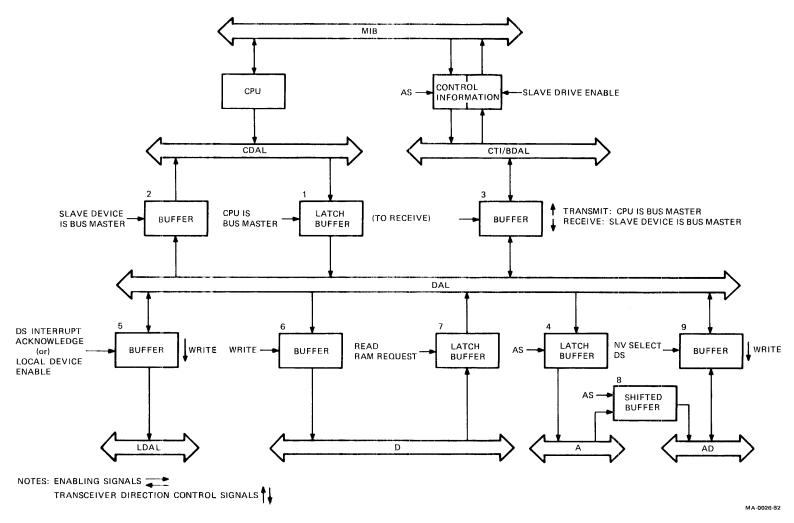

| 5.3.4    | Bus Interfaces                                    | 5-29 |

|----------|---------------------------------------------------|------|

| 5.3.4.1  | Buffers                                           |      |

| 5.3.4.2  | Registers                                         |      |

| 5.3.5    | Other Control Logic                               |      |

| 5.3.5.1  | Slot Select Decoder                               | 5-35 |

| 5.3.5.2  | I/O Page Address Decoder                          | 5-36 |

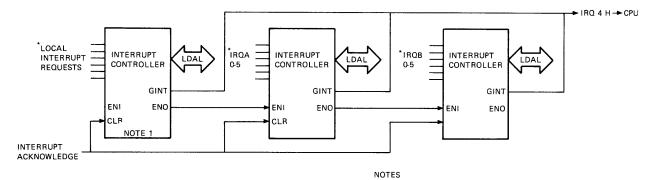

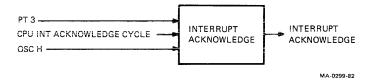

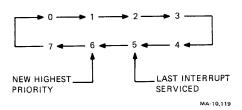

| 5.3.6    | Interrupt Vector Circuit                          | 5-42 |

| 5.3.6.1  | Interrupt Service                                 |      |

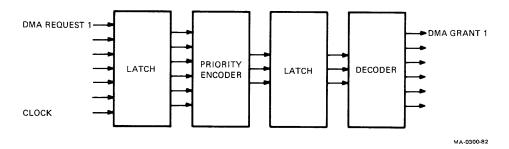

| 5.3.7    | Direct Memory Access (DMA)                        | 5-45 |

| 5.3.7.1  | DMA Detailed Description                          | 5-46 |

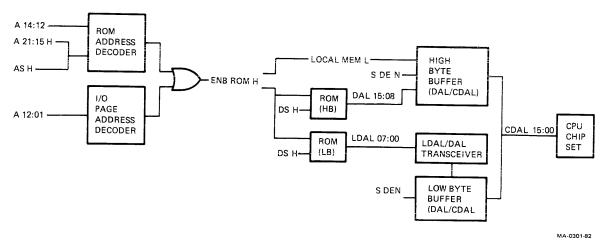

| 5.3.8    | (Read Only Memory) ROM                            | 5-46 |

| 5.3.8.1  | ID PROM                                           |      |

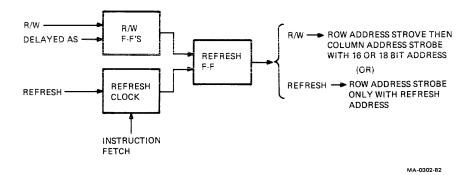

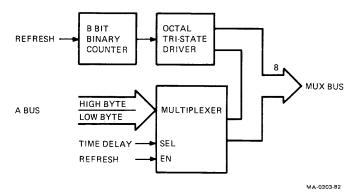

| 5.3.9    | Random Access Memory (RAM)                        | 5-48 |

| 5.3.9.1  | RAM Timing and Control (Refresh Cycles)           |      |

| 5.3.10   |                                                   |      |

| 5.3.11   | Keyboard I/O                                      |      |

| 5.3.12   | Printer I/O                                       |      |

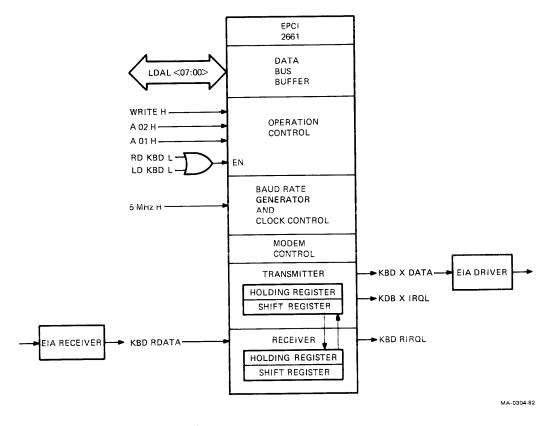

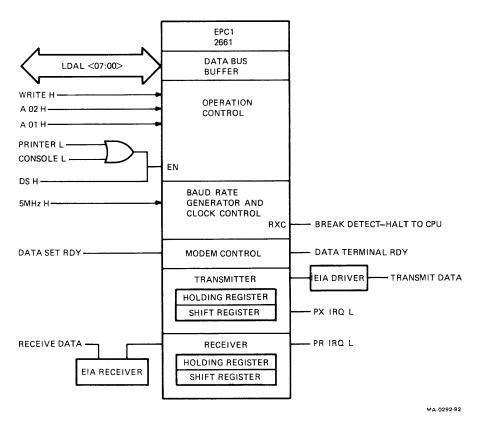

| 5.3.12.1 | Communication I/O                                 | 5-53 |

| 5.3.13   | Communications I/O Detailed Description           | 5-54 |

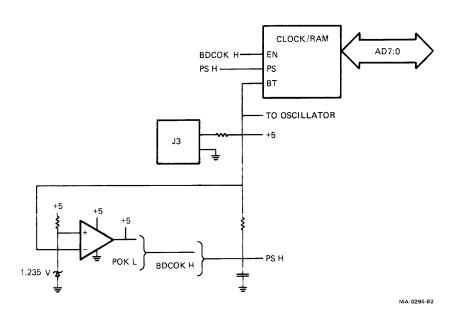

| 5.3.13.1 | Battery Backed-Up Clock and RAM                   | 5-54 |

|          | Clock and RAM Circuit                             | 5-55 |

| 5.3.13.2 | Battery Charger and Voltage Sensor                |      |

| 5.4      | Programming Information                           |      |

| 5.4.1    | Introduction                                      |      |

| 5.4.2    | General Programming Information                   | 5-56 |

| 5.4.3    | Central Processor                                 | 5-57 |

| 5.4.3.1  | Power Fail Trap                                   |      |

| 5.4.3.2  | Memory Management                                 |      |

| 5.4.3.3  | Memory Management Relocation                      |      |

| 5.4.3.4  | Default State After Power-Up                      |      |

| 5.4.3.5  | Floating Point Precision                          |      |

| 5.4.4    | Computing Terminal Interconnect (CTI) Bus         |      |

| 5.4.5    | System Control and Status Register (SCSR)         | 5-67 |

| 5.4.5.1  | Default State After Power-Up                      |      |

| 5.4.5.2  | Indicator (LED) Display                           |      |

| 5.4.5.3  | Indicator Display Default State After Power-Up    |      |

| 5.4.6    | Interrupt Controllers                             | 5-70 |

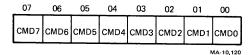

| 5.4.6.1  | Control/Status Register (CSR)                     | 5-74 |

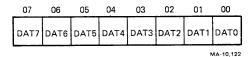

| 5.4.6.2  | Data Register                                     | 5-77 |

| 5.4.6.3  | Interrupt Controller Default State After Power-Up | 5-78 |

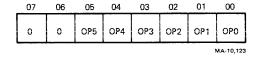

| 5.4.7    | Direct Memory Access (DMA)                        | 5-79 |

| 5.4.7.1  | Option Module Addresses                           | 5-80 |

| 5.4.7.2  | Option Module Vectors                             | 5-80 |

| 5.4.7.3  | Option Module Present Register (OMPR)             |      |

| 5.4.8    | ROM                                               |      |

| 5.4.8.1  | ID PROM                                           |      |

| 5.4.9    | RAM                                               |      |

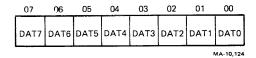

| 5.4.10   | Keyboard                                          |      |

| 5.4.10.1 | Keyboard Interface                                |      |

| 5.4.10.2 | Keyboard Default State After Power-Up             |      |

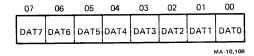

| 5.4.11    | Printer                                         | 5-90  |

|-----------|-------------------------------------------------|-------|

| 5.4.11.1  | Printer Port Interface                          | 5-91  |

| 5.4.11.2  | Printer Default State After Power Up            |       |

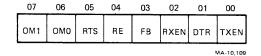

| 5.4.12    | Communications                                  |       |

| 5.4.12.1  | Communication Port Interface                    |       |

| 5.4.12.2  | Communication Port Default State After Power Up |       |

| 5.4.13    | Battery Backed-Up System Clock and RAM          |       |

| 5.4.13.1  | Clock Interface                                 |       |

| 5.4.13.2  | System Clock Default State After Power-Up       |       |

| 5.4.13.3  | Battery Backed-Up RAM                           |       |

| 5.4.14    | Maintenance ODT                                 |       |

| 5.4.14.1  | Terminal Interface                              |       |

| 5.4.14.2  | Entry Conditions                                |       |

| 5.4.14.3  | ODT Operation of Serial Line Interface          |       |

| 5.4.14.4  | Command Set                                     |       |

|           |                                                 |       |

| 5.4.14.5  | Address Specification                           |       |

| 5.4.14.6  | Invalid Characters                              |       |

| 5.4.15    | Maintenance Terminal                            |       |

| 5.4.15.1  | Maintenance Terminal Interface                  |       |

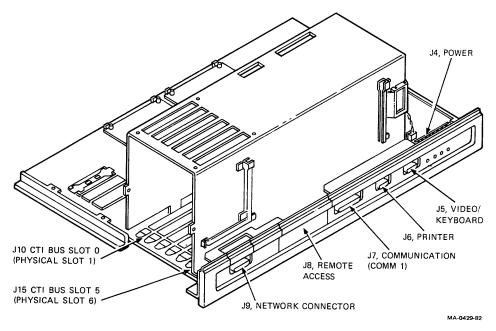

| 5.5       | Connectors                                      |       |

| 5.6       | Specifications                                  |       |

| 5.6.1     | Physical Specifications                         |       |

| 5.6.1.1   | Dimensions and Weight                           |       |

| 5.6.1.2   | Module Interconnects                            |       |

| 5.6.2     | Power Requirements                              | 5-139 |

| 5.6.2.1   | DC Power Requirements                           | 5-139 |

| 5.6.3     | Environmental Specifications                    | 5-139 |

| 5.6.3.1   | Temperature                                     |       |

| 5.6.3.2   | Relative Humidity                               |       |

| 5.6.3.3   | Altitude                                        |       |

| 5.6.3.4   | Operating Airflow                               | 5-140 |

| CHAPTER 6 | PRO380 SYSTEM MODULE                            |       |

| 6.1       | Introduction                                    | 6-1   |

| 6.1.1     | Chapter Organization                            | 6-1   |

| 6.1.2     | Related Documentation                           |       |

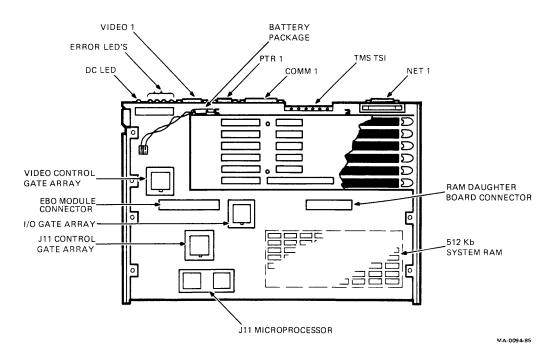

| 6.1.3     | System Module Components                        | 6-1   |

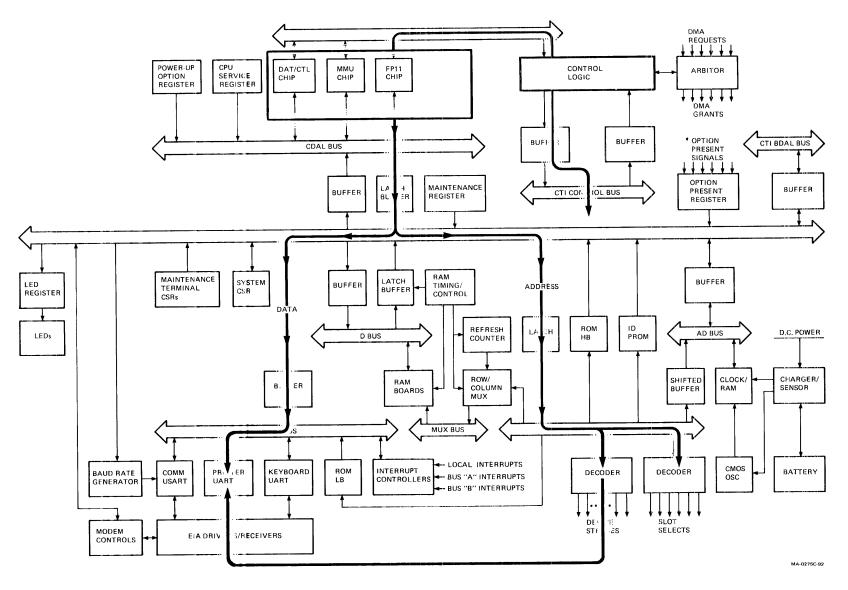

| 6.2       | Functional Description                          |       |

| 6.2.1     | J11 Microprocessor                              |       |

| 6.2.2     | J11 Microprocessor DC365 Control Gate Array     | 6-4   |

| 6.2.3     | DC362 I/O Interface Gate Array                  |       |

| 6.2.4     | System Memory                                   |       |

| 6.2.5     | Real-Time System Clock                          |       |

| 6.2.6     | Printer Interface Logic                         |       |

| 6.2.7     | Keyboard Interface Logic                        |       |

| 6.2.8     | Communication Interface Logic                   |       |

| 6.2.9     | Video Generation Integrated Logic               |       |

| 6.2.10    | LED Display Circuit                             | 6-7   |

| 6.2.11    | CTI Bus Option Connectors                           | 6-7  |

|-----------|-----------------------------------------------------|------|

| 6.2.12    | System Power-On Bootstrap Sequence                  | 6-7  |

| 6.3       | Detailed Description                                | 6-8  |

| 6.3.1     | J11 Microprocessor Overview                         |      |

| 6.3.1.1   | Memory Management Unit                              |      |

| 6.3.1.2   | Floating Point Unit                                 |      |

| 6.3.2     | Instruction Cycle Timing                            |      |

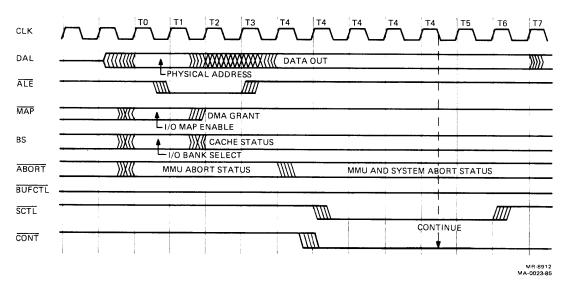

| 6.3.2.1   | Read Timing                                         |      |

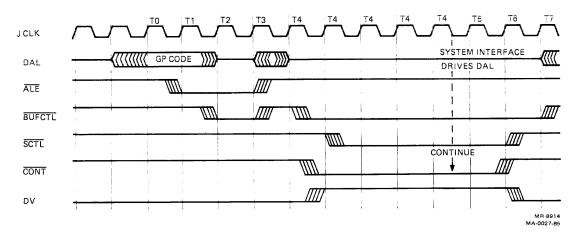

| 6.3.2.1.1 | General Purpose Read Timing                         |      |

| 6.3.2.2   | Write Timing                                        |      |

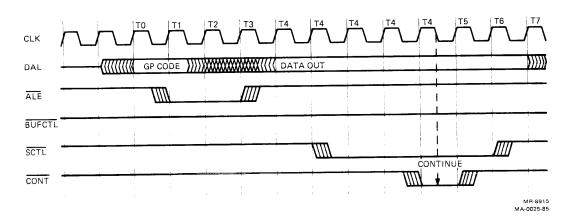

| 6.3.2.2.1 | General Purpose Write Timing                        |      |

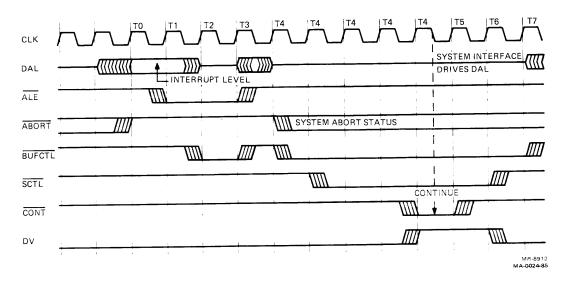

| 6.3.2.3   | Interrupt Acknowledge Timing                        |      |

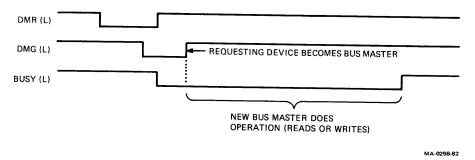

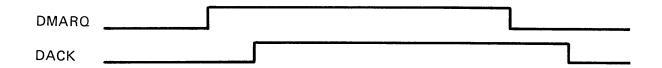

| 6.3.2.4   | DMA (Direct Memory Access Timing) Request and       | 0 13 |

| 0.3.2.4   | Grant Timing                                        | 6-16 |

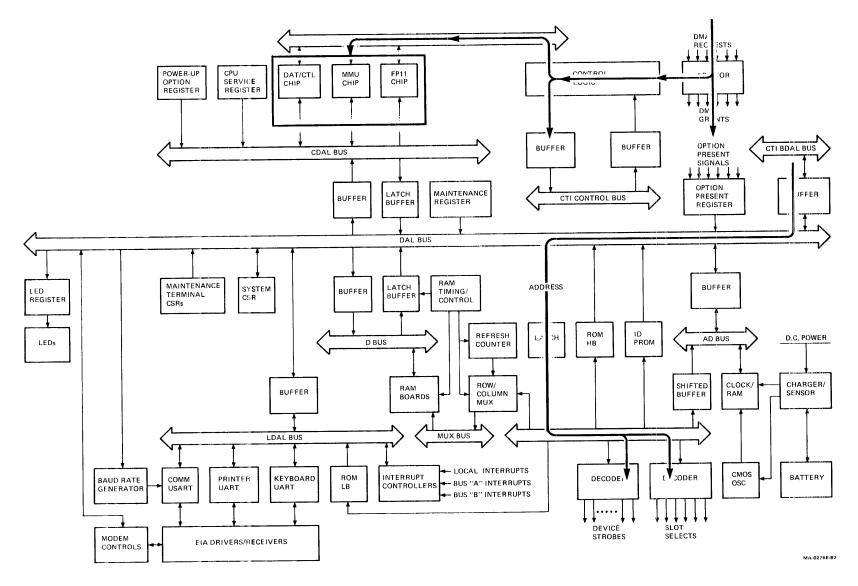

| 6.3.3     | J11 Microprocessor DC365 Control Gate Array         |      |

| 6.3.3.1   | DC365 Bus Cycle Interaction                         |      |

| 6.3.3.2   | Memory Read/Write Transaction                       |      |

| 6.3.3.3   |                                                     |      |

|           | CTI Bus/DC365 Accessing                             |      |

| 6.3.3.4   | General Purpose Read/Write Transaction              |      |

| 6.3.3.5   | Interrupt Acknowledge Transaction                   |      |

| 6.3.3.6   | DMA Device Bus Accessing                            |      |

| 6.3.4     | DC362 I/O Interface Gate Array                      |      |

| 6.3.4.1   | DC362 Bus Cycle Interaction                         |      |

| 6.3.4.2   | Address Decoding                                    |      |

| 6.3.4.3   | Boot ROM Sequencing                                 |      |

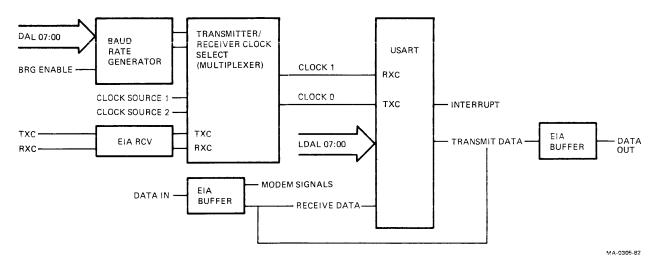

| 6.3.4.4   | Communication Port Support Logic                    |      |

| 6.3.4.5   | Baud Rate Generators                                |      |

| 6.3.4.6   | Interrupt Controller Logic                          |      |

| 6.3.4.7   | Direct Memory Access (DMA) Arbitration              |      |

| 6.3.4.8   | Buffer Direction Control                            |      |

| 6.3.4.9   | Maintenance Terminal Logic                          |      |

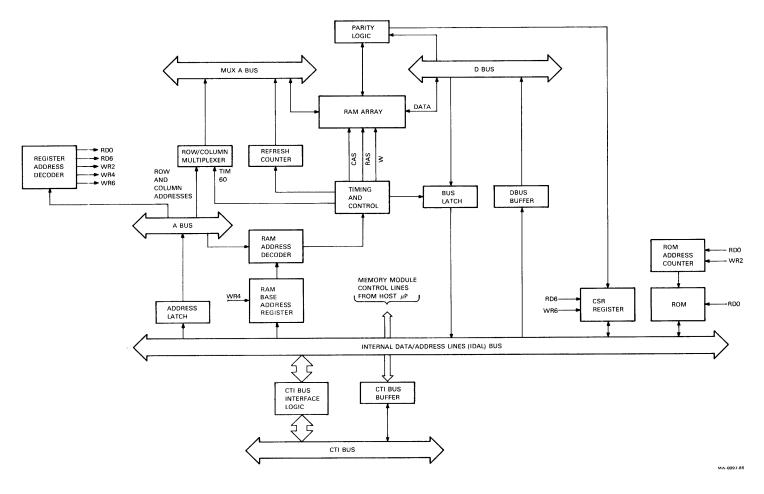

| 6.3.5     | System Memory                                       | 6-24 |

| 6.3.5.1   | Random Access Memory (RAM)                          | 6-24 |