# VAX 6000 Model 500 Mini-Reference

Order Number EK-650EA-HR-001

This manual supplies easy-to-access key information on VAX 6000 Model 500 systems.

digital equipment corporation maynard, massachusetts

#### First Printing, October 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1990 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEMNA PDP VAXcluster

DEC ULTRIX VAXELN

DEC LANcontroller UNIBUS VMS

DECnet VAX XMI

DECUS VAXBI

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# **Contents**

| Preface    |                                        | xi   |

|------------|----------------------------------------|------|

|            |                                        |      |

| Chapter 1  | Console Operation                      |      |

| <u>'</u>   | ·                                      |      |

| Chapter 2  | Self-Test                              |      |

| •          |                                        |      |

| Chapter 3  | Address Space                          |      |

| •          | Find a Register in XMI Address Space   | 3-5  |

|            | Find a Register in VAXBI Address Space |      |

|            |                                        |      |

| Chapter 4  | KA65A CPU Module Registers             |      |

| 4.1 KA65A  | Internal Processor Registers           | 4–3  |

|            | Registers in XMI Private Space         | 4–18 |

| 4.3 KA65A  | XMI Registers                          | 4-30 |

| 4.4 Machin | e Checks                               | 4-36 |

| 4.5 KA65A  | Parse Trees                            | 4–41 |

| Chapter 5  | MS65A Memory Registers                 |      |

| Chantar C  | DWMDD Adoptor Degisters                |      |

| Chapter 6  | DWMBB Adapter Registers                |      |

| Chap | oter 7 Vector Module Registers                         |      |

|------|--------------------------------------------------------|------|

| 7.1  | Console Commands to Access Registers                   | 7–1  |

| 7.2  | KA65A IPRs Related to the Vector Module                | 7–7  |

| 7.3  | FV64A Internal Processor Registers                     | 7–8  |

| 7.4  | FV64A Registers — Vector Indirect Registers            | 7–11 |

| 7.5  | FV64A Parse Trees                                      | 7–28 |

| Inde | x                                                      |      |

| Exar | nples                                                  |      |

| 2–1  | Sample Self-Test Results, Scalar Processors Only       | 2–1  |

| 2–1  | Sample Self-Test Results with VAXBI Adapter            | 2–1  |

| 2–3  | Sample Self-Test Results with Vector Processor         | 2-4  |

| 2–0  | Sample Sen-Test Results with Vector 1 Totessor         | ∠–5  |

| Figu | res                                                    |      |

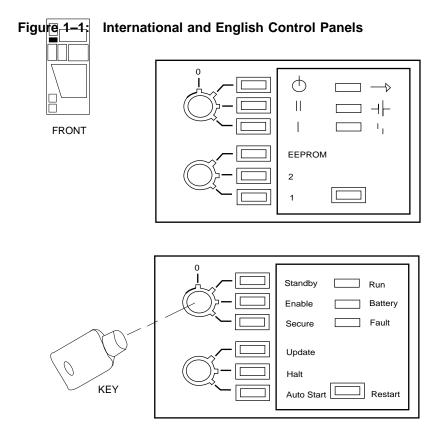

| 1–1  | International and English Control Panels               | 1–2  |

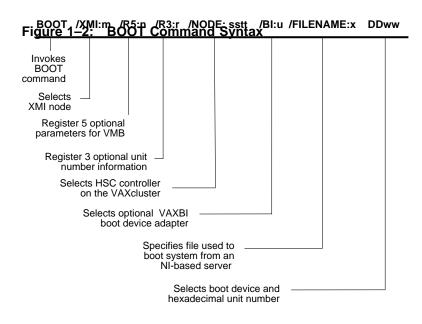

| 1-2  | BOOT Command Syntax                                    | 1–8  |

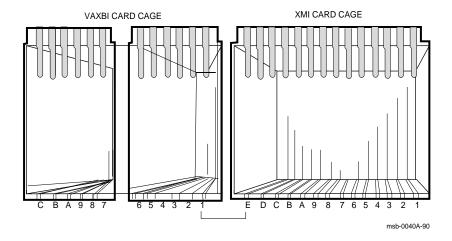

| 3–1  | VAX 6000 Model 500 Slot Numbers                        | 3–1  |

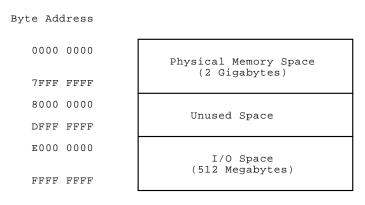

| 3-2  | XMI Memory and I/O Address Space                       | 3-2  |

| 3–3  | XMI I/O Space Address Allocation                       | 3–3  |

| 4–1  | Interval Clock Control and Status Register (ICCS)      | 4–8  |

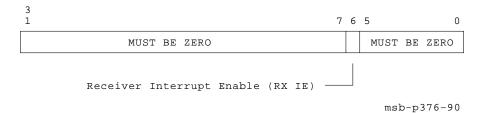

| 4-2  | Console Receiver Control and Status Register (RXCS)    | 4–8  |

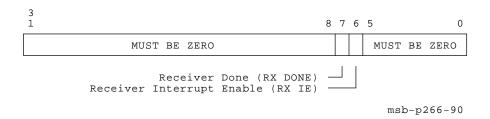

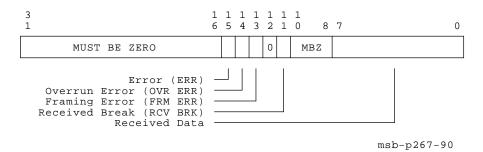

| 4-3  | Console Receiver Data Buffer Register (RXDB)           | 4–8  |

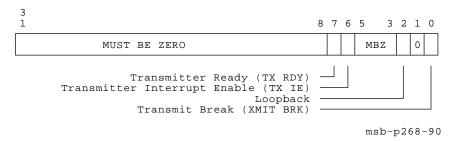

| 4–4  | Console Transmitter Control and Status Register (TXCS) | 4–9  |

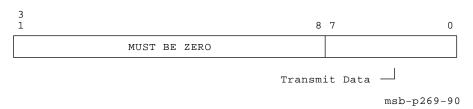

| 4-5  | Console Transmitter Data Buffer Register (TXDB)        | 4–9  |

| 4-6  | Machine Check Error Summary Register (MCESR)           | 4–9  |

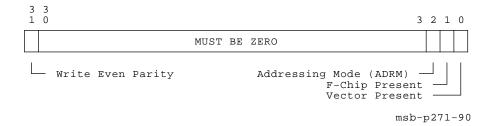

| 4-7  | Accelerator Control and Status Register (ACCS)         | 4–10 |

| 4–8  | Console Saved Program Counter Register (SAVPC)         | 4–10 |

| 4–9  | Console Saved Processor Status Longword (SAVPSL)       | 4–10 |

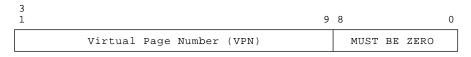

| 4–10 | Translation Buffer Tag Register (TBTAG)                | 4–11 |

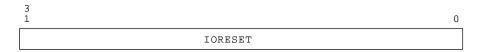

| 4–11 | I/O Reset Register (IORESET)                           | 4–11 |

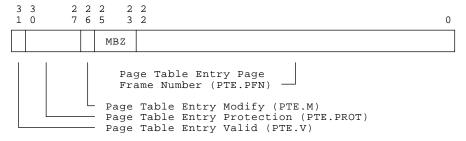

| 4-12 | Translation Buffer Data Register (TBDATA)              | 4–11 |

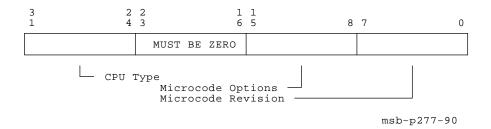

| 4–13 | System Identification Register (SID)                   | 4–12 |

| 4-14 | Backup Cache Index Register (BCIDX)                    | 4-12 |

| 4–15 | Backup Cache Status Register (BCSTS)                    | 4–13 |

|------|---------------------------------------------------------|------|

| 4–16 | Backup Cache Control Register (BCCTL)                   | 4–13 |

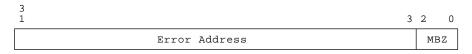

| 4–17 | Backup Cache Error Address Register (BCERA)             | 4–14 |

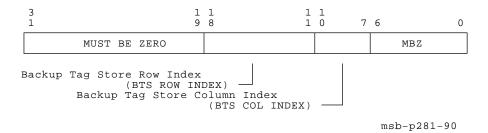

| 4–18 | Backup Cache Tag Store Register (BCBTS)                 | 4–14 |

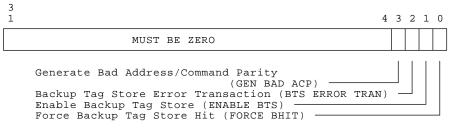

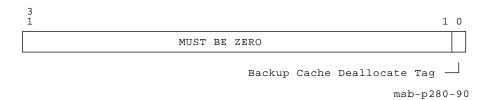

| 4–19 | Backup Cache Deallocate Tag Register (BCDET)            | 4–14 |

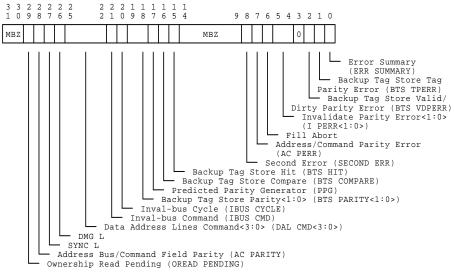

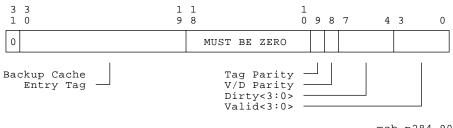

| 4–20 | Backup Cache Error Tag Register (BCERT)                 | 4-15 |

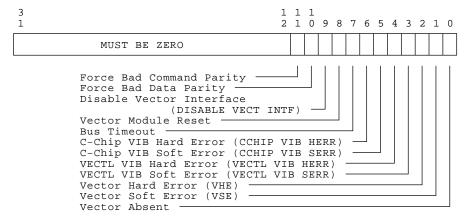

| 4–21 | Vector Interface Error Status Register (VINTSR)         | 4-15 |

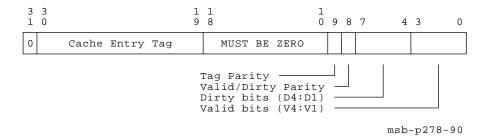

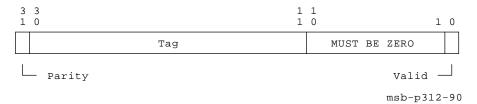

| 4–22 | Primary Cache Tag Array Register (PCTAG)                | 4–16 |

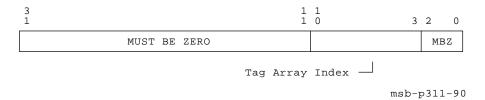

| 4–23 | Primary Cache Index Register (PCIDX)                    | 4–16 |

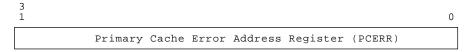

| 4–24 | Primary Cache Error Address Register (PCERR)            | 4–16 |

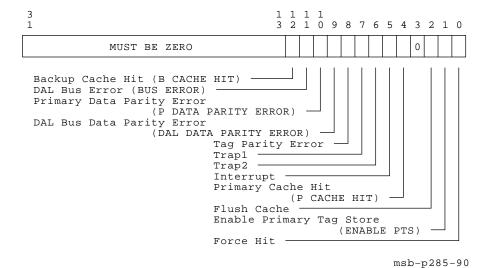

| 4-25 | Primary Cache Status Register (PCSTS)                   | 4–17 |

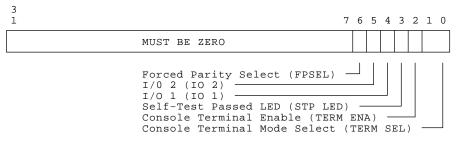

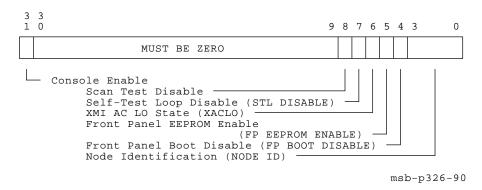

| 4–26 | Control Register 0 (CREG0)                              | 4–19 |

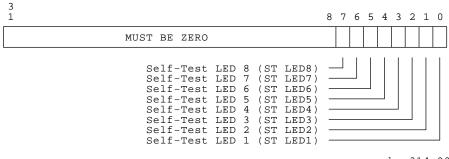

| 4-27 | Control Register 1 (CREG1)                              | 4–20 |

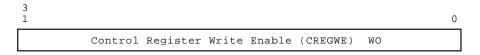

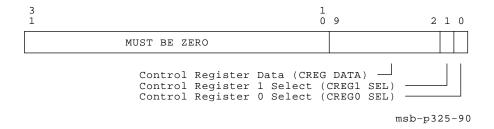

| 4–28 | Control Register Write Enable (CREGWE)                  | 4-20 |

| 4–29 | MSSC Base Address Register (SSCBAR)                     | 4-20 |

| 4–30 | MSSC Configuration Register (SSCCNR)                    | 4–21 |

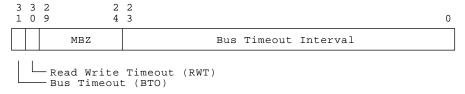

| 4–31 | MSSC Bus Timeout Control Register (SSCBTR)              | 4–21 |

| 4–32 | MSSC Output Port Register (OPORT)                       | 4–22 |

| 4–33 | MSSC Input Port Register (IPORT)                        | 4–22 |

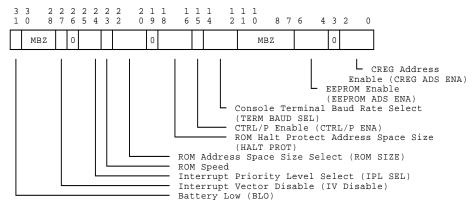

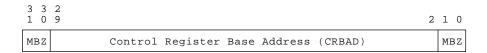

| 4–34 | Control Register Base Address Register (CRBADR)         | 4–22 |

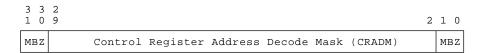

| 4–35 | Control Register Address Decode Mask Register (CRADMR). | 4–23 |

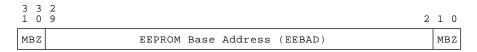

| 4–36 | EEPROM Base Address Register (EEBADR)                   | 4-23 |

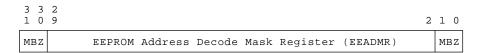

| 4–37 | EEPROM Address Decode Mask Register (EEADMR)            | 4-23 |

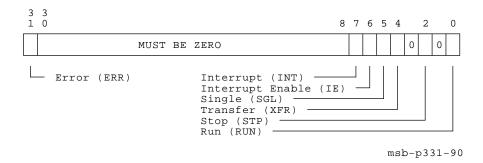

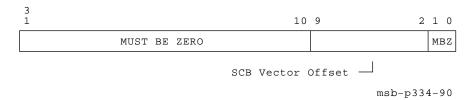

| 4–38 | Timer Control Register 0 (TCR0)                         | 4–24 |

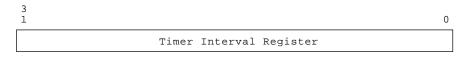

| 4–39 | Timer Interval Register 0 (TIR0)                        | 4–24 |

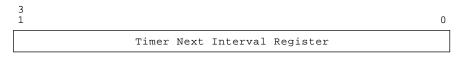

| 4–40 | Timer Next Interval Register (TNIR0)                    | 4–24 |

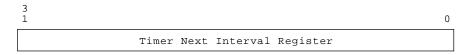

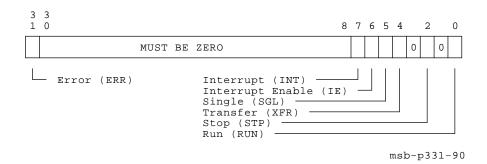

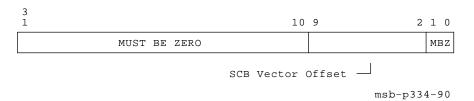

| 4–41 | Timer Interrupt Vector Register (TIVR0)                 | 4-25 |

| 4–42 | Timer Control Register 1 (TCR1)                         | 4-25 |

| 4-43 | Timer Interval Register (TIR1)                          | 4-25 |

| 4–44 | Timer Next Interval Register 1 (TNIR1)                  | 4–26 |

| 4-45 | Timer Interrupt Vector Register 1 (TIVR1)               | 4–26 |

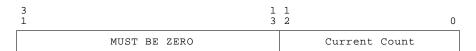

| 4–46 | MSSC Interval Counter Register (SSCICR)                 | 4–26 |

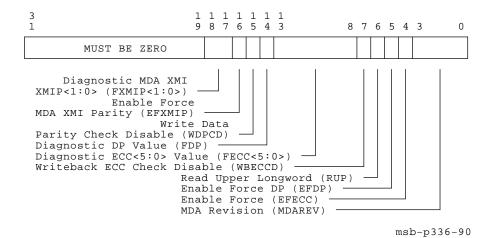

| 4-47 | DAL Diagnostic Register (DCSR)                          | 4-27 |

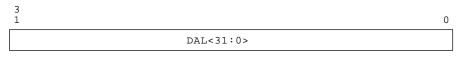

| 4–48 | Failing DAL Register 0 (FDAL0)                          | 4–27 |

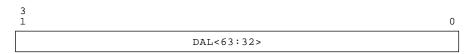

| 4–49 | Failing DAL Register 1 (FDAL1)                          | 4–27 |

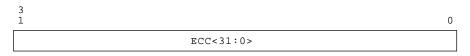

| 4–50 | Failing DAL Register 2 (FDAL2)                          | 4-28 |

|      |                                                         |      |

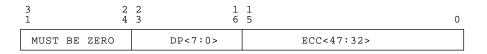

| 4–51 | Failing DAL Register 3 (FDAL3)                                         | 4-28 |

|------|------------------------------------------------------------------------|------|

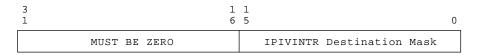

| 4–52 | Interprocessor Implied Vector Interrupt Generation Register (IPIVINTR) | 4–28 |

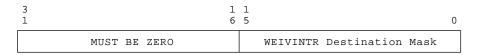

| 4–53 | Write Error Implied Vector Interrupt Generation Register (WEIVINTR)    | 4–29 |

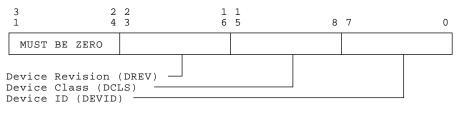

| 4–54 | Device Register (XDEV)                                                 | 4-30 |

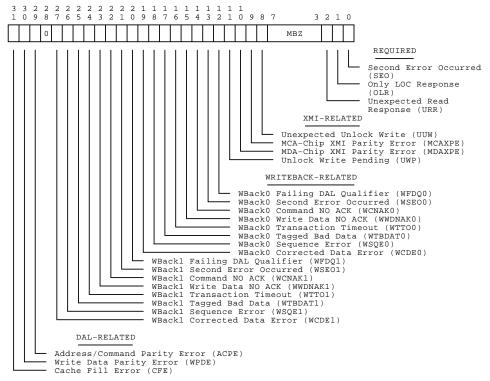

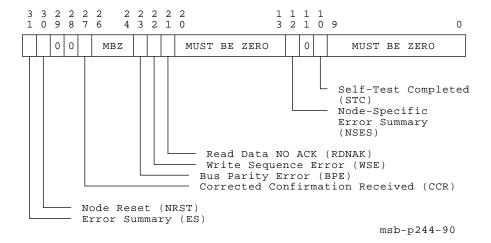

| 4–55 | Bus Error Register 0 (XBER0)                                           | 4–31 |

| 4–56 | Failing Address Register (XFADR0)                                      | 4–32 |

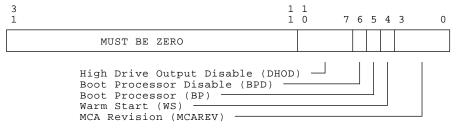

| 4–57 | XMI General Purpose Register (XGPR)                                    | 4–32 |

| 4–58 | Node Specific Control and Status Register (NSCSR0)                     | 4–32 |

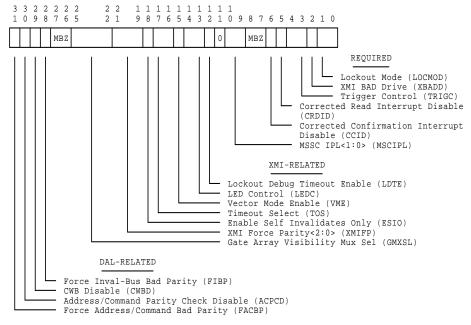

| 4–59 | XMI Control Register 0 (XCR0)                                          | 4–33 |

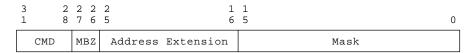

| 4–60 | Failing Address Extension Register 0 (XFAER0)                          | 4–33 |

| 4–61 | Bus Error Extension Register 0 (XBEER0)                                | 4–34 |

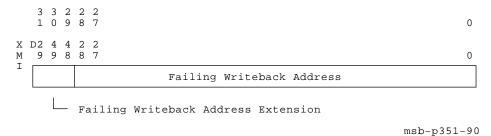

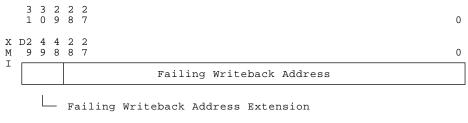

| 4–62 | Writeback 0 Failing Address Register (WFADR0)                          | 4–35 |

| 4–63 | Writeback 1 Failing Address Register (WFADR1)                          | 4-35 |

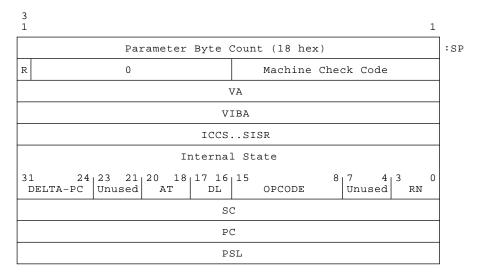

| 4–64 | Machine Check Stack Frame                                              | 4-36 |

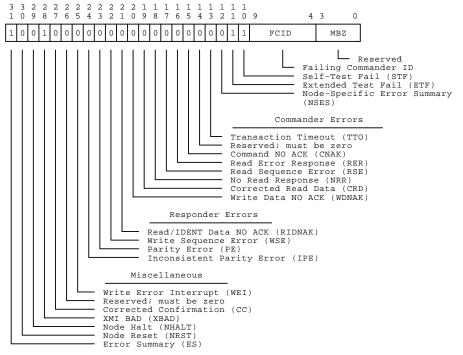

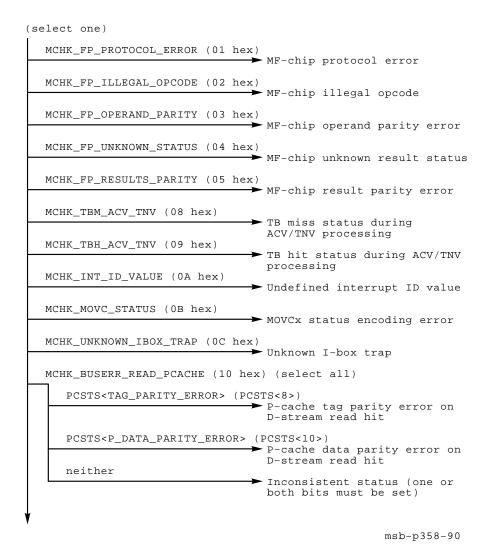

| 4–65 | KA65A Machine Check Parse Tree                                         | 4–41 |

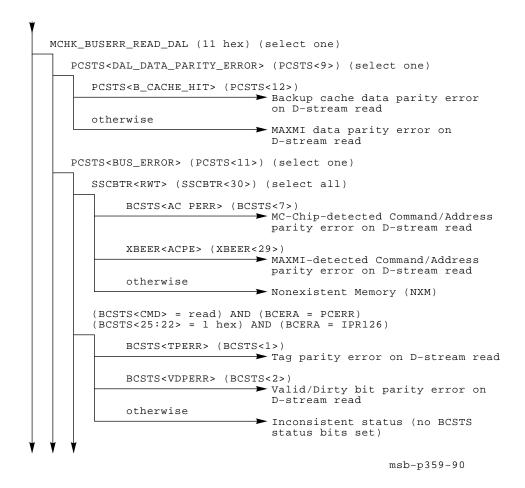

| 4–66 | KA65A Hard Error Interrupt Parse Tree                                  | 4-46 |

| 4–67 | KA65A Soft Error Interrupt Parse Tree                                  | 4–49 |

| 5–1  | Device Register (XDEV)                                                 | 5–2  |

| 5-2  | Bus Error Register (XBER)                                              | 5–2  |

| 5–3  | Starting and Ending Address Register (SEADR)                           | 5–3  |

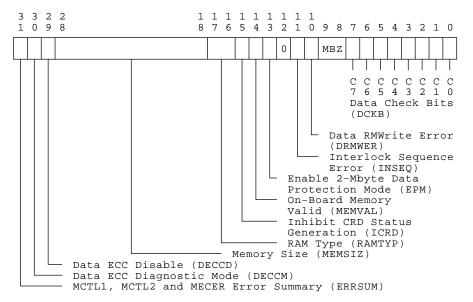

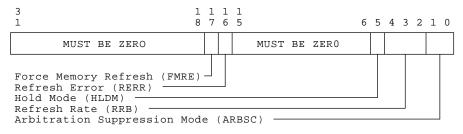

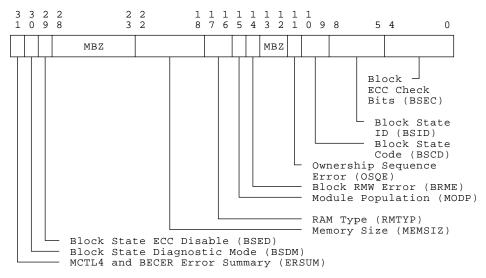

| 5–4  | Memory Control Register 1 (MCTL1)                                      | 5–3  |

| 5–5  | Memory ECC Error Register (MECER)                                      | 5–4  |

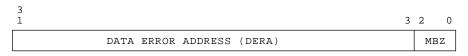

| 5-6  | Memory ECC Error Address Register (MECEA)                              | 5-4  |

| 5-7  | Memory Control Register 2 (MCTL2)                                      | 5-5  |

| 5–8  | TCY Tester Register (TCY)                                              | 5–5  |

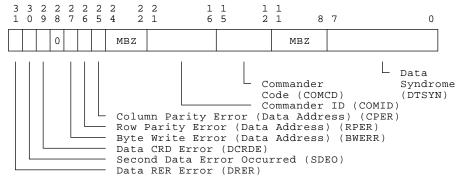

| 5–9  | Block State ECC Error Register (BECER)                                 | 5–6  |

| 5-10 | Block State ECC Address Register (BECEA)                               | 5–6  |

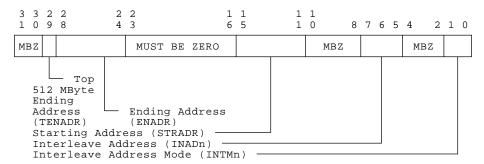

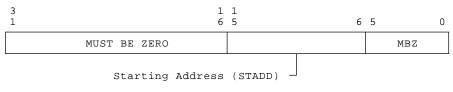

| 5–11 | Starting Address Register (STADR)                                      | 5–7  |

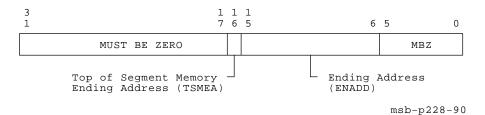

| 5-12 | Ending Address Register (ENADR)                                        | 5–7  |

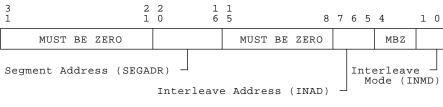

| 5-13 | Segment/Interleave Register (INTLV)                                    | 5–7  |

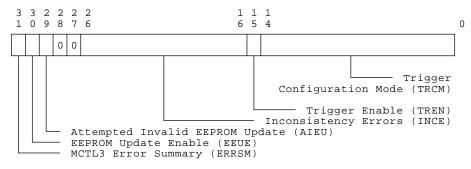

| 5–14 | Memory Control Register 3 (MCTL3)                                      | 5–8  |

| 5–15 | Memory Control Register 4 (MCTL4)                                      | 5–8  |

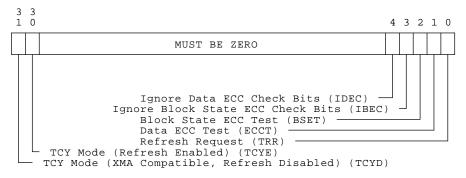

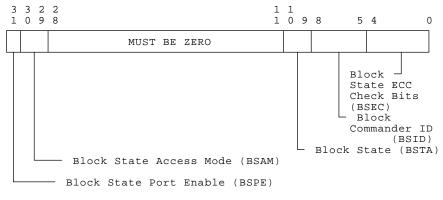

| 5–16 | Block State Control Register (BSCTL)                                   | 5–9  |

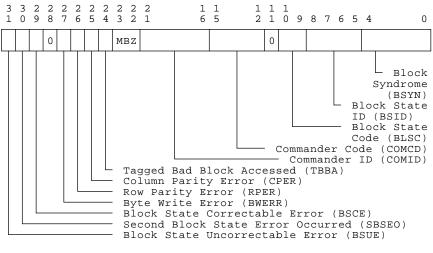

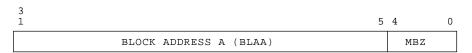

| 5-17 | Block State Address Register (BSADR)                                   | 5-9  |

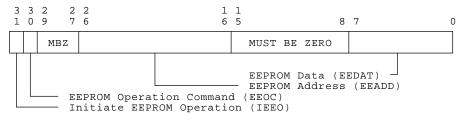

| 5-18 | EEPROM Control Register (EECTL)                                                                     | 5-10 |

|------|-----------------------------------------------------------------------------------------------------|------|

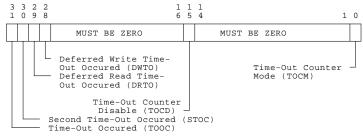

| 5–19 | Timeout Control/Status Register (TMOER)                                                             | 5-10 |

| 6–1  | Device Register (XDEV)                                                                              | 6–3  |

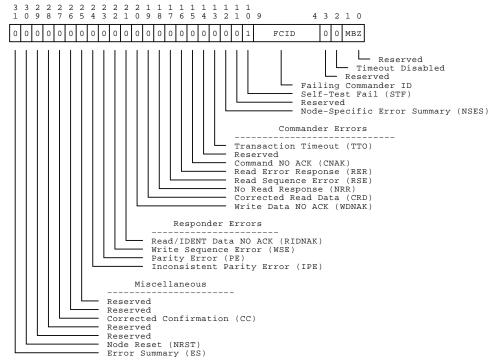

| 6-2  | Bus Error Register (XBER)                                                                           | 6–4  |

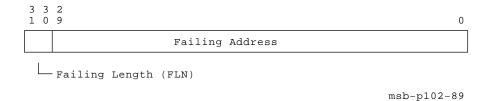

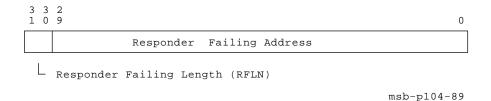

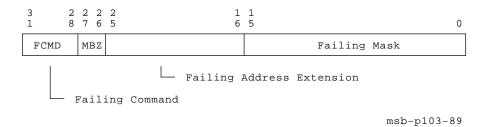

| 6–3  | Failing Address Register (XFADR)                                                                    | 6-5  |

| 6–4  | Responder Error Address Register (AREAR)                                                            | 6-5  |

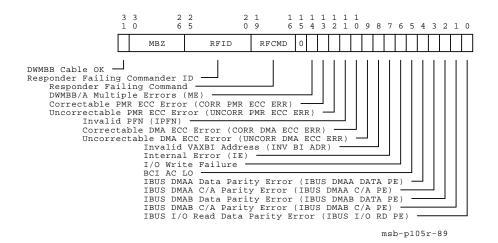

| 6–5  | DWMBB/A Error Summary Register (AESR)                                                               | 6–6  |

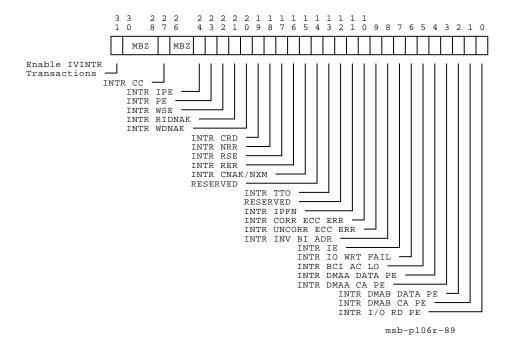

| 6–6  | Interrupt Mask Register (AIMR)                                                                      | 6-7  |

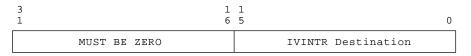

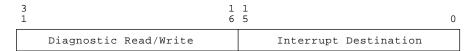

| 6–7  | Implied Vector Interrupt Destination/Diagnostic Register (AIVINTR)                                  | 6–7  |

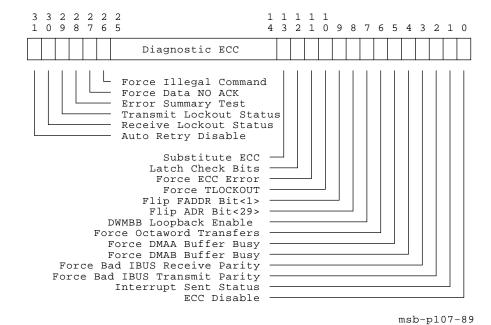

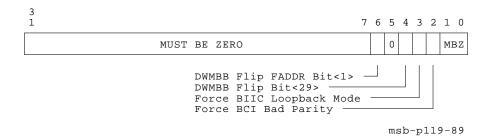

| 6–8  | Diag 1 Register (ADG1)                                                                              | 6–8  |

| 6–9  | Utility Register (AUTLR)                                                                            | 6–8  |

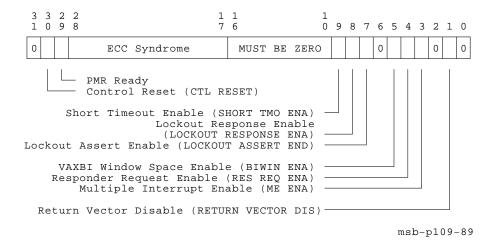

| 6–10 | Control and Status Register (ACSR)                                                                  | 6–9  |

| 6–11 | Return Vector Register (ARVR)                                                                       | 6–9  |

| 6–12 | Failing Address Extension Register (XFAER)                                                          | 6–10 |

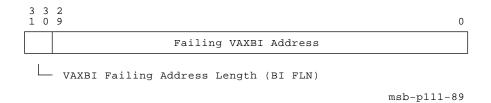

| 6–13 | BI Error Address Register (ABEAR)                                                                   | 6–10 |

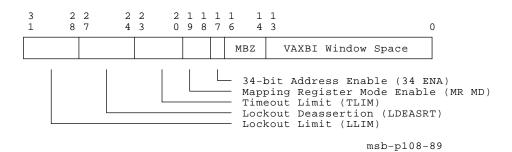

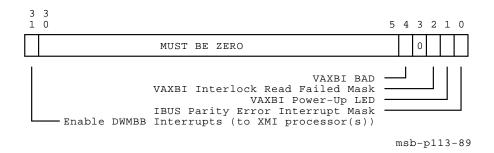

| 6–14 | Control and Status Register (BCSR)                                                                  | 6–11 |

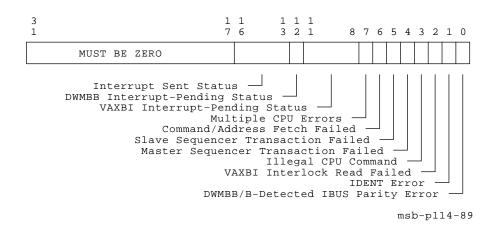

| 6–15 | DWMBB/B Error Summary Register (BESR)                                                               | 6–11 |

| 6–16 | Interrupt Destination Register (BIDR)                                                               | 6-12 |

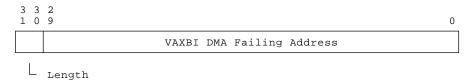

| 6-17 | Timeout Address Register (BTIM)                                                                     | 6-12 |

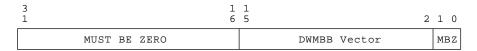

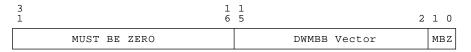

| 6–18 | Vector Offset Register (BVOR)                                                                       | 6-12 |

| 6–19 | Vector Register (BVR)                                                                               | 6–13 |

| 6–20 | Diagnostic Control Register 1 (BDCR1)                                                               | 6–13 |

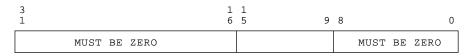

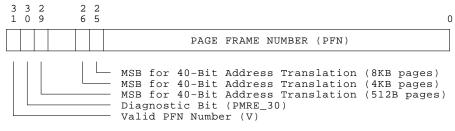

| 6–21 | Page Map Register (PMR)                                                                             | 6–13 |

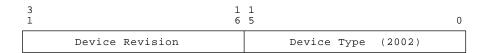

| 6-22 | VAXBI Device Register (DTYPE)                                                                       | 6–14 |

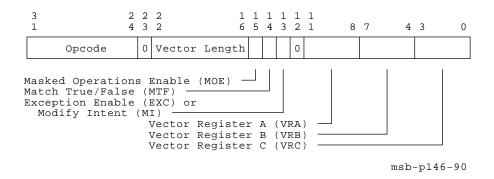

| 7-1  | Vector Length (VLR) and Vector Count (VCR) Registers $\ \ldots \ .$                                 | 7-2  |

| 7-2  | Vector Mask Register (VMR)                                                                          | 7-2  |

| 7–3  | Vector Interface Error Status Register (VINTSR)                                                     | 7–7  |

| 7-4  | Accelerator Control and Status Register (ACCS)                                                      | 7–7  |

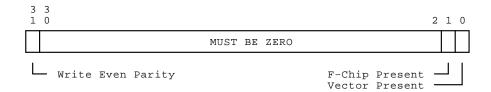

| 7-5  | Vector Processor Status Register (VPSR)                                                             | 7–8  |

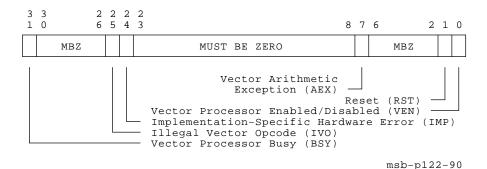

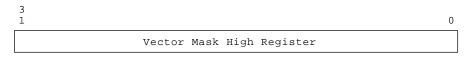

| 7–6  | Vector Arithmetic Exception Register (VAER)                                                         | 7–8  |

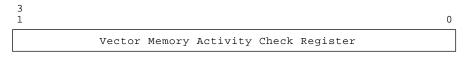

| 7–7  | Vector Memory Activity Check Register (VMAC)                                                        | 7–9  |

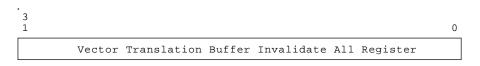

| 7–8  | $\label{thm:continuous} \mbox{Vector Translation Buffer Invalidate All Register (VTBIA)} \ \ . \ .$ | 7–9  |

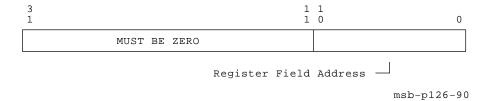

| 7–9  | Vector Indirect Address Register (VIADR)                                                            | 7–9  |

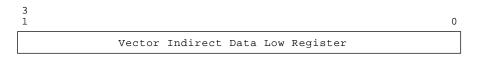

| 7–10 | Vector Indirect Data Low Register (VIDLO)                                                           | 7–10 |

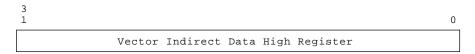

| 7-11 | Vector Indirect Data High Register (VIDHI)                                                          | 7–10 |

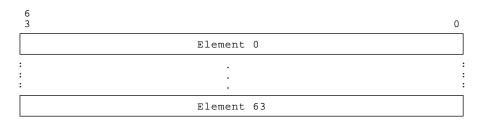

| 7-12   | Vector Register $n$ (VREG $n$ )                          | 7–11   |

|--------|----------------------------------------------------------|--------|

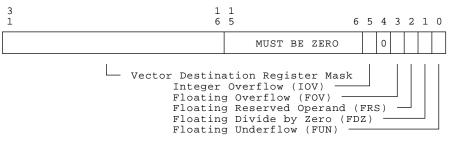

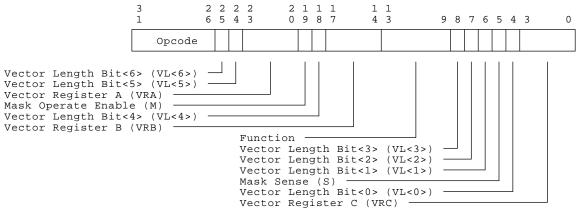

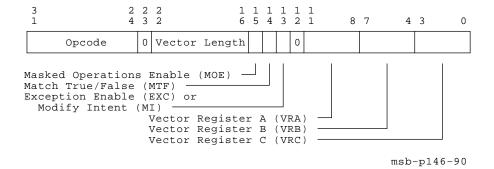

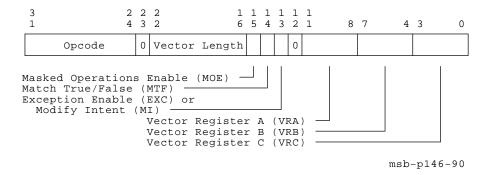

| 7–13   | Arithmetic Exception Register (ALU_OP)                   | 7–11   |

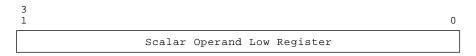

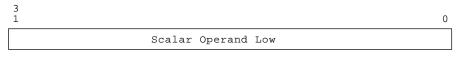

| 7–14   | Scalar Operand Low Register (ALU_SCOP_LO)                | 7-12   |

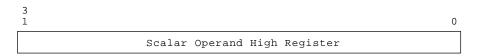

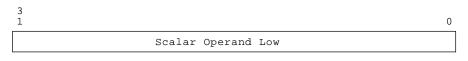

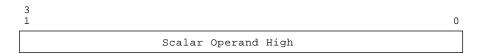

| 7–15   | Scalar Operand High Register (ALU_SCOP_HI)               | 7-12   |

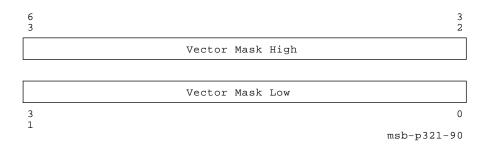

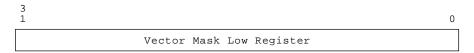

| 7–16   | Vector Mask Low Register (ALU_MASK_LO)                   | 7-12   |

| 7-17   | Vector Mask High Register (ALU_MASK_HI)                  | 7–13   |

| 7–18   | Exception Summary Register (ALU_EXC)                     | 7–13   |

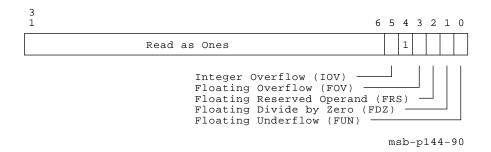

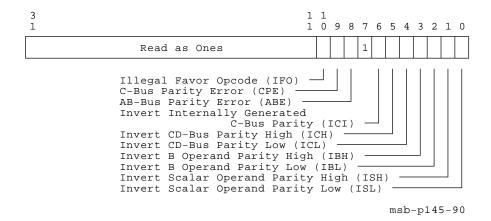

| 7–19   | Diagnostic Control Register (ALU_DIAG_CTL)               | 7-14   |

| 7–20   | Current ALU Instruction Register (VCTL_CALU)             | 7-14   |

| 7-21   | Deferred ALU Instruction Register (VCTL_DALU)            | 7-15   |

| 7-22   | Current ALU Operand Low Register (VCTL_COP_LOW)          | 7-15   |

| 7–23   | Current ALU Operand High Register (VCTL_COP_HI)          | 7-15   |

| 7-24   | Deferred ALU Operand Low Register (VCTL_DOP_LOW)         | 7–16   |

| 7-25   | Deferred ALU Operand High Register (VCTL_DOP_HI)         | 7–16   |

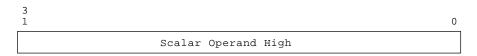

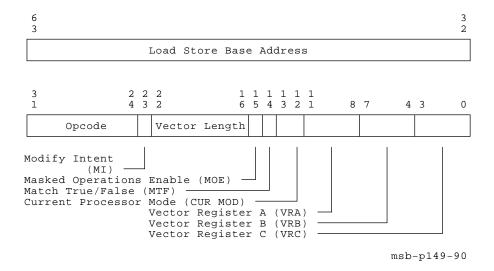

| 7–26   | Load/Store Instruction Register (VCTL_LDST)              | 7-17   |

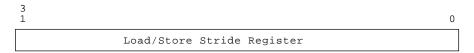

| 7-27   | Load/Store Stride Register (VCTL_STRIDE)                 | 7-17   |

| 7–28   | Illegal Instruction (VCTL_ILL)                           | 7–18   |

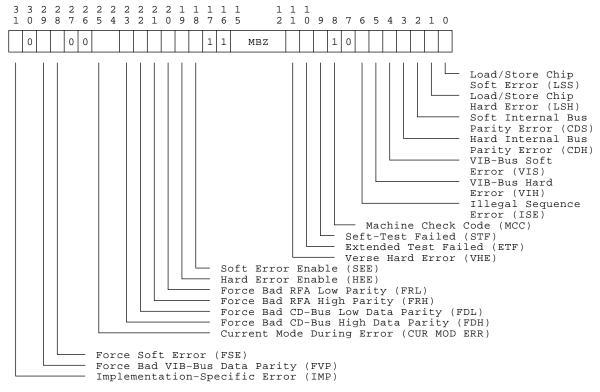

| 7-29   | Vector Controller Status (VCTL_CSR)                      | 7–19   |

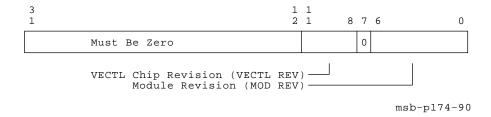

| 7–30   | Module Revision (MOD_REV)                                | 7–20   |

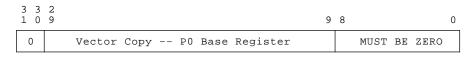

| 7–31   | P0 Base Register (LSX_P0BR)                              | 7–20   |

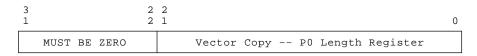

| 7–32   | P0 Length Register (LSX_P0LR)                            | 7–20   |

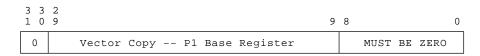

| 7–33   | P1 Base Register (LSX_P1BR)                              | 7-21   |

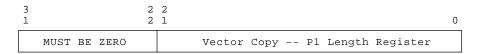

| 7–34   | P1 Length Register (LSX_P1LR)                            | 7-21   |

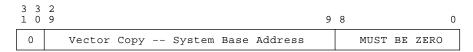

| 7 - 35 | System Base Register (LSX_SBR)                           | 7-21   |

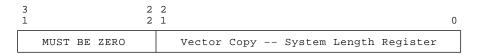

| 7–36   | System Length Register (LSX_SLR)                         | 7-22   |

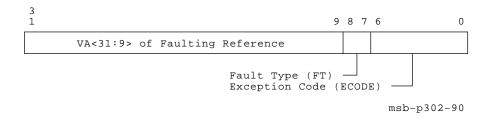

| 7–37   | Load/Store Exception Register (LSX_EXC)                  | 7-22   |

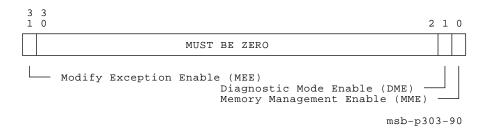

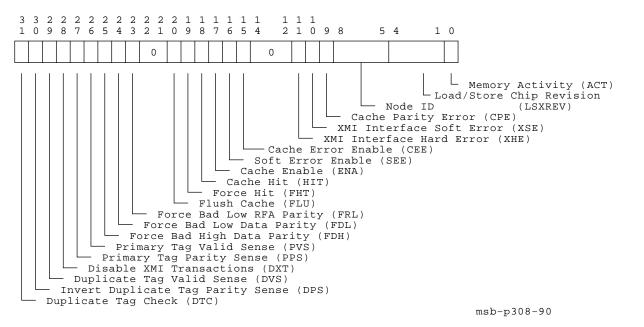

| 7–38   | Translation Buffer Control Register (LSX_TBCSR)          | 7-22   |

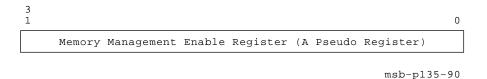

| 7–39   | Memory Management Enable (LSX_MAPEN)                     | 7-23   |

| 7–40   | Translation Buffer Invalidate All Register (LSX_TBIA)    | 7 - 23 |

| 7–41   | Translation Buffer Invalidate Single Register (LSX_TBIS) | 7-23   |

| 7-42   | Vector Mask Low Register (LSX_MASKLO)                    | 7-24   |

| 7–43   | Vector Mask High Register (LSX_MASKHI)                   | 7-24   |

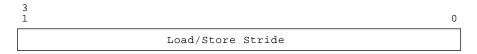

| 7–44   | Load/Store Stride Register (LSX_STRIDE)                  | 7-24   |

| 7–45   | Load/Store Instruction Register (LSX_INST)               | 7-25   |

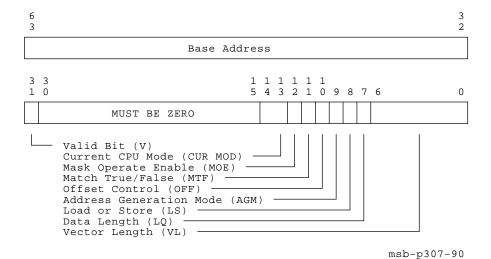

| 7–46   | Cache Control Register (LSX_CCSR)                        | 7–26   |

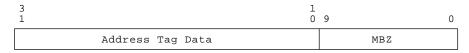

| 7-47   | Translation Buffer Tag Register (LSX TBTAG)              | 7 - 26 |

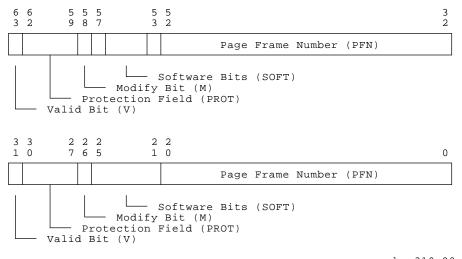

| 7 - 48 | Translation Buffer PTE Register (LSX_PTE)                       | 7-27 |

|--------|-----------------------------------------------------------------|------|

| 7–49   | FV64A Machine Check Parse Tree                                  | 7-28 |

| 7–50   | FV64A Hard Error Interrupt Parse Tree                           | 7–29 |

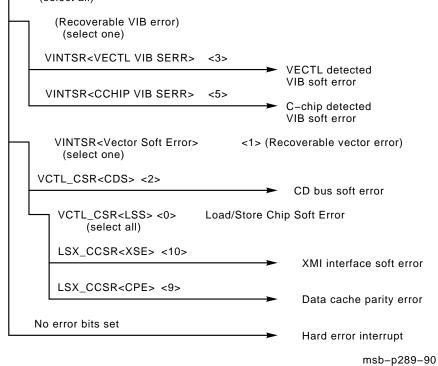

| 7–51   | FV64A Soft Error Interrupt Parse Tree                           | 7–30 |

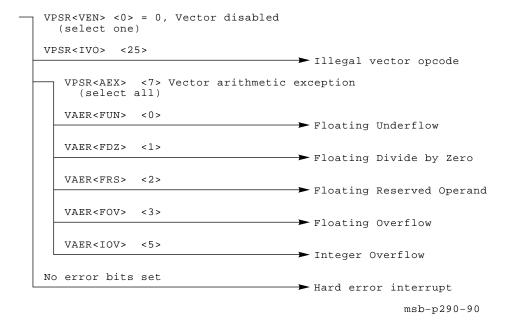

| 7 - 52 | FV64A Disable Fault Parse Tree                                  | 7–31 |

|        |                                                                 |      |

| Table  | es established                                                  |      |

| 1      | VAX 6000 Series Documentation                                   | xi   |

| 2      | Associated Documents                                            | xii  |

| 1–1    | Upper Key Switch                                                | 1–3  |

| 1-2    | Lower Key Switch                                                | 1–3  |

| 1–3    | Restart Button                                                  | 1–3  |

| 1–4    | Control Panel Status Indicator Lights                           | 1–4  |

| 1-5    | Console Commands and Qualifiers                                 | 1–4  |

| 1–6    | Console Control Characters                                      | 1–7  |

| 1–7    | BOOT Command Qualifiers                                         | 1–8  |

| 1–8    | Sample BOOT Commands                                            | 1–9  |

| 1–9    | R5 Bit Functions for VMS                                        | 1–10 |

| 1–10   | R5 Bit Functions for ULTRIX                                     | 1–10 |

| 1–11   | Console Error Messages Indicating Halt                          | 1–11 |

| 1-12   | Standard Console Error Messages                                 | 1–13 |

| 2-1    | System Configuration for Sample Self-Test                       | 2-3  |

| 2-2    | Module LEDs After Self-Test                                     | 2-6  |

| 3–1    | XMI Nodespace Addresses                                         | 3–4  |

| 3-2    | $VAXBI\ Nodespace\ and\ Window\ Space\ Address\ Assignments\ .$ | 3-7  |

| 3–3    | VAXBI Registers                                                 | 3–8  |

| 4–1    | Types of Registers, Bits, and Fields                            | 4–2  |

| 4-2    | KA65A Internal Processor Registers                              | 4–3  |

| 4–3    | KA65A Registers in XMI Private Space                            | 4–18 |

| 4–4    | XMI Registers for the KA65A CPU Module                          | 4–30 |

| 4-5    | Machine Check Parameters                                        | 4-37 |

| 4-6    | Machine Check Codes                                             | 4–39 |

| 5-1    | MS65A Memory Control and Status Registers                       | 5-1  |

| 6–1    | DWMBB Registers                                                 | 6–2  |

| 6-2    | XMI Required Registers                                          | 6–3  |

| 7-1    | Internal Processor Registers                                    | 7–3  |

| 7–2 | FV64A Registers— | -Vector | Indirect Registe | ers | 7-4 | 1 |

|-----|------------------|---------|------------------|-----|-----|---|

|-----|------------------|---------|------------------|-----|-----|---|

# **Intended Audience**

This manual is intended for the system manager and programmer.

# **Document Structure**

This manual has seven chapters:

- Chapter 1—Console Operation

- Chapter 2—Self-Test

- Chapter 3—Address Space

- Chapter 4—KA65A CPU Module Registers

- Chapter 5—MS65A Memory Registers

- Chapter 6—DWMBB Adapter Registers

- Chapter 7—FV64A Vector Module Registers

# **VAX 6000 Series Documents**

There are two sets of documentation: manuals that apply to all VAX 6000 series systems and manuals that are specific to one VAX 6000 model. Table 1 lists the manuals in the VAX 6000 series documentation set.

Table 1: VAX 6000 Series Documentation

| Title                                           | Order Number |

|-------------------------------------------------|--------------|

| Operation                                       |              |

| VAX 6000 Series Owner's Manual                  | EK-600EA-OM  |

| VAX 6000 Series Vector Processor Owner's Manual | EK-60VAA-OM  |

| VAX 6000 Vector Processor Programmer's Guide    | EK-60VAA-PG  |

Table 1 (Cont.): VAX 6000 Series Documentation

| Title                                            | Order Number |

|--------------------------------------------------|--------------|

| Service and Installation                         |              |

| VAX 6000 Platform Technical User's Guide         | EK-600EA-TM  |

| VAX 6000 Series Installation Guide               | EK-600EA-IN  |

| VAX 6000 Installationsanleitung                  | EK-600GA-IN  |

| VAX 6000 Guide d'installation                    | EK-600FA-IN  |

| VAX 6000 Guia de instalacion                     | EK-600SA-IN  |

| VAX 6000 Platform Service Manual                 | EK-600EA-MG  |

| Model 500                                        |              |

| VAX 6000 Model 500 Mini-Reference                | EK-650EA-HR  |

| VAX 6000 Model 500 Service Manual                | EK-650EA-MG  |

| VAX 6000 Model 500 System Technical User's Guide | EK-650EA-TM  |

| VAX 6000: Installing Model 500 Processors        | EK-KA65A-UP  |

# **Associated Documents**

Table 2 lists other documents that you may find useful.

**Table 2: Associated Documents**

| Title                                     | Order Number |

|-------------------------------------------|--------------|

| System Hardware Options                   |              |

| VAXBI Expander Cabinet Installation Guide | EK-VBIEA-IN  |

| VAXBI Options Handbook                    | EB-32255-46  |

Table 2 (Cont.): Associated Documents

| Title                                                    | Order Number |  |

|----------------------------------------------------------|--------------|--|

| System I/O Options                                       |              |  |

| CIBCA User Guide                                         | EK-CIBCA-UG  |  |

| CIXCD Interface User Guide                               | EK-CIXCD-UG  |  |

| DEC LANcontroller 200 Installation Guide                 | EK-DEBNI-IN  |  |

| DEC LANcontroller 400 Installation Guide                 | EK-DEMNA-IN  |  |

| InfoServer 100 Installation and Owners Guide             | EK-DIS1K-IN  |  |

| KDB50 Disk Controller User's Guide                       | EK-KDB50-UG  |  |

| KDM70 Controller User Guide                              | EK-KDM70-UG  |  |

| RRD40 Disc Drive Owner's Manual                          | EK-RRD40-OM  |  |

| RA90/RA92 Disk Drive User Guide                          | EK-ORA90-UG  |  |

| SA70 Enclosure User Guide                                | EK-SA70E-UG  |  |

| Operating System Manuals                                 |              |  |

| Guide to Maintaining a VMS System                        | AA-LA34A-TE  |  |

| Guide to Setting Up a VMS System                         | AA-LA25A-TE  |  |

| Introduction to VMS System Management                    | AA-LA24A-TE  |  |

| ULTRIX-32 Guide to System Exercisers                     | AA-KS95B-TE  |  |

| VMS Upgrade and Installation Supplement: VAX 6000 Series | AA-LB36C-TE  |  |

| VMS Networking Manual                                    | AA-LA48A-TE  |  |

| VMS System Manager's Manual                              | AA-LA00A-TE  |  |

| VMS VAXcluster Manual                                    | AA-LA27B-TE  |  |

Table 2 (Cont.): Associated Documents

| Title                                                  | Order Number |  |

|--------------------------------------------------------|--------------|--|

| Peripherals                                            |              |  |

| HSC Installation Manual                                | EK-HSCMN-IN  |  |

| H4000 DIGITAL Ethernet Transceiver Installation Manual | EK-H4000-IN  |  |

| Installing and Using the VT320 Video Terminal          | EK-VT320-UG  |  |

| RV20 Optical Disk Owner's Manual                       | EK-ORV20-OM  |  |

| SC008 Star Coupler User's Guide                        | EK-SC008-UG  |  |

| TA78 Magnetic Tape Drive User's Guide                  | EK-OTA78-UG  |  |

| TA90 Magnetic Tape Subsystem Owner's Manual            | EK-OTA90-OM  |  |

| TK70 Streaming Tape Drive Owner's Manual               | EK-OTK70-OM  |  |

| TU81/TA81 and $TU/81$ PLUS Subsystem User's Guide      | EK-TUA81-UG  |  |

| VAX Manuals                                            | _            |  |

| VAX Architecture Reference Manual                      | EY-3459E-DP  |  |

| VAX Systems Hardware Handbook — VAXBI Systems          | EB-31692-46  |  |

| VAX Vector Processing Handbook                         | EC-H0739-46  |  |

# Chapter 1 **Console Operation**

This chapter provides reference information for working at the console terminal.

## Terminal setup characteristics:

- The maximum recommended baud rate is 1200. If the console is not responding, you may need to press the Break key to increment the baud rate.

- Terminal characteristics should be set to the following: eight bits, no parity, one stop bit.

msb-0037A-90

Table 1-1: Upper Key Switch

| Position                    | Effect                                                                                                                                                                                                  | Light Color |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| O (Off)                     | Removes all power, except to the battery backup unit and optional storage.                                                                                                                              | No light    |

| Standby                     | Supplies power to XMI backplane, blowers, and incabinet console load device.                                                                                                                            | Red         |

| Enable                      | Supplies power to whole system; console terminal is enabled. Used for console mode or restart, and to start self-test.                                                                                  | Yellow      |

| Secure<br>(Normal Position) | Prevents entry to console mode; position used while machine is executing programs. Disables Restart button and causes the lower key switch to have the effect of Auto Start, regardless of its setting. | Green       |

Table 1–2: Lower Key Switch

| Position                        | Effect                                                                                                                                                                                                                                       | Light Color |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Update                          | Enables writing to CPUs and adapters. Halts boot processor in console mode on power-up or when Restart button is pressed. Used for updating parameters stored in EEPROMs (upper key switch must be set to Enable). Prevents an auto restart. | Red         |

| Halt                            | Prevents an auto restart if a failure or transient power outage occurs.                                                                                                                                                                      | Yellow      |

| Auto Start<br>(Normal Position) | Allows restart or reboot. Used for normal operation of the system.                                                                                                                                                                           | Green       |

Table 1–3: Restart Button

| Upper Key Switch     | Lower Key Switch | <b>Restart Button Function</b>                                                                                                                           |

|----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable               | Update or Halt   | Runs self-test, then halts.                                                                                                                              |

| Enable               | Auto Start       | Runs self-test, and attempts a restart. If the restart fails, then it reboots the operating system. If the reboot fails, control returns to the console. |

| Standby<br>or Secure | Any position     | Does not function.                                                                                                                                       |

Table 1-4: Control Panel Status Indicator Lights

| Light   | Color | State                | Meaning                                                                                                                                          |

|---------|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Run     | Green | On                   | System is executing operating system instructions on at least one processor.                                                                     |

|         |       | Off                  | System is in console mode, is set to Standby, or is turned off.                                                                                  |

| Battery | Green | On                   | Battery backup unit is charged to 98% of full capacity or battery backup unit is supplying power to the load.                                    |

|         |       | Flashing<br>1 x/sec  | Battery backup unit is charging.                                                                                                                 |

|         |       | Flashing<br>10 x/sec | Battery backup requires service.                                                                                                                 |

|         |       | Off                  | System does not have a battery backup unit.                                                                                                      |

| Fault   | Red   | On                   | Self-test is in progress. If light does not turn off, system has a hardware fault. See VAX 6000 Series Owner's Manual for self-test information. |

|         |       | Off                  | Self-test has completed, or the system is turned off.                                                                                            |

Table 1–5: Console Commands and Qualifiers

| Command and<br>Qualifiers                           | Function                                                                                       |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| BOOT /R3:n /R5:n /XMI:n /BI:m /NODE:n /FILENAME:xyz | Initializes the system, causing a self-test, and begins the boot program.                      |  |

| CLEAR EXCEPTION                                     | Cleans up error state in XBER and RCSR registers.                                              |  |

| CONTINUE                                            | Begins processing at the address where processing was interrupted by a CTRL/P console command. |  |

| DEPOSIT /B /G /I /L /M /N /P /Q /V /VE /W           | Stores data in a specified address.                                                            |  |

Table 1–5 (Cont.): Console Commands and Qualifiers

| Command and<br>Qualifiers                                                                                              | Function                                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXAMINE /B /G /I /L /M /N /P /Q /V /VE /W                                                                              | Displays the contents of a specified address.                                                                                             |  |

| FIND<br>/MEMORY<br>/RPB                                                                                                | Searches main memory for a page-aligned 256-Kbyte block of good memory or for a restart parameter block.                                  |  |

| HALT                                                                                                                   | Null command; no action is taken since the processor has already halted in order to enter console mode.                                   |  |

| HELP                                                                                                                   | Prints explanation of console commands.                                                                                                   |  |

| INITIALIZE [n]<br>/BI:n                                                                                                | Performs a system reset, including self-test.                                                                                             |  |

| REPEAT                                                                                                                 | Executes the command passed as its argument.                                                                                              |  |

| SET BOOT                                                                                                               | Stores a boot command by a nickname.                                                                                                      |  |

| SET CPU [n]  /ENABLED  /ALL  /NOENABLED  /NEXT_PRIMARY  /PRIMARY  /ALL  /NOPRIMARY  /VECTOR_ENABLED  /NOVECTOR_ENABLED | Specifies eligibility of processors to become the boot processor or disables a vector processor.                                          |  |

| SET LANGUAGE<br>ENGLISH<br>INTERNATIONAL                                                                               | Changes the output of the console error messages between numeric code only (international mode) and code plus explanation (English mode). |  |

| SET MEMORY /CONSOLE_LIMIT:n /INTERLEAVE:(n+n) /INTERLEAVE:DEFAULT /INTERLEAVE:NONE                                     | Designates the method of interleaving the memory modules; supersedes the console program's default interleaving.                          |  |

Table 1–5 (Cont.): Console Commands and Qualifiers

| Command and<br>Qualifiers                                                   | Function                                                                                                                                                |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| SET TERMINAL /BREAK /NOBREAK /HARDCOPY /NOHARDCOPY /SCOPE /NOSCOPE /SPEED:n | Sets console terminal characteristics.                                                                                                                  |

| SHOW ALL                                                                    | Displays the current value of parameters set.                                                                                                           |

| SHOW BOOT                                                                   | Displays all boot commands and nicknames that have been saved using SET BOOT.                                                                           |

| SHOW CONFIGURATION                                                          | Displays the hardware device type and revision level for each XMI and VAXBI node and indicates self-test status.                                        |

| SHOW CPU                                                                    | Identifies the primary processor and the status of other processors.                                                                                    |

| SHOW ETHERNET                                                               | Locates all Ethernet adapters on the system and displays their addresses.                                                                               |

| SHOW FIELD                                                                  | Displays saved boot commands, console terminal parameters, console language mode, memory configuration, type of power system, and system serial number. |

| SHOW LANGUAGE                                                               | Displays the mode currently set for console error messages, international or English.                                                                   |

| SHOW MEMORY                                                                 | Displays the memory lines from the system self-test, showing interleave and memory size.                                                                |

| SHOW TERMINAL                                                               | Displays the baud rate and terminal characteristics functioning on the console terminal.                                                                |

| START                                                                       | Begins execution of an instruction at the address specified in the command string.                                                                      |

| STOP<br>/BI:n                                                               | Halts the specified node.                                                                                                                               |

| TEST<br>/RBD                                                                | Passes control to the self-test diagnostics.                                                                                                            |

| UPDATE                                                                      | Copies contents of the EEPROM on the processor executing the command to the EEPROM of another processor.                                                |

Table 1–5 (Cont.): Console Commands and Qualifiers

| Command and<br>Qualifiers | Function                                                                                        |

|---------------------------|-------------------------------------------------------------------------------------------------|

| Z<br>/BI:n                | Logically connects the console terminal to another processor on the XMI bus or to a VAXBI node. |

| !                         | Introduces a comment.                                                                           |

Table 1-6: Console Control Characters

| Character | Function                                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| BREAK     | Increments the console baud rate if enabled.                                                                                          |

| CTRL/C    | Causes the console to abort processing of a command.                                                                                  |

| CTRL/O    | Causes console to discard output to the console terminal until the next $\boxed{\text{CTRL/O}}$ is entered.                           |

| CTRL/P    | In console mode, acts like $\fbox{CTRUC}$ . In program mode, causes the boot processor to halt and begin running the console program. |

| CTRL/Q    | Resumes console output that was suspended with CTRL/S.                                                                                |

| CTRL/R    | Redisplays the current line.                                                                                                          |

| CTRL/S    | Suspends console output on the console terminal until $\boxed{\texttt{CTRL/Q}}$ is typed.                                             |

| CTRL/U    | Discards all characters on the current line.                                                                                          |

| DELETE    | Deletes the previously typed character.                                                                                               |

| ESC       | Suppresses any special meaning associated with a given character.                                                                     |

| RETURN    | Carriage return; ends a command line.                                                                                                 |

msb-0441B-90

Table 1-7: BOOT Command Qualifiers

| Qualifier     | Function                                                                                                                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /X[MI]:number | Specifies the XMI node number of the node that connects the boot device.                                                                                                                                               |

| /R5:number    | Specifies the hexadecimal value to be loaded into register R5 immediately before the virtual memory boot (VMB) program receives control. Use as a bit mask to select VMB options and to set the system root directory. |

| /R3:number    | Specifies the hexadecimal value to be loaded into register R3 immediately before the virtual memory boot (VMB) program receives control.                                                                               |

Table 1–7 (Cont.): BOOT Command Qualifiers

| Qualifier        | Function                                                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | This qualifier is used when multiple unit numbers must be specified: for example, when booting from VMS shadow sets. If / R3 is specified, the unit number portion of the device name is ignored.                                                                                                                |

| /N[ODE]:number   | Specifies the remote node(s) that provide access to the boot device. The /XMI (and optionally /BI) qualifiers must have identified a controller that supports "nodes" such as a VAXcluster adapter. The /NODE qualifier would then specify the VAXcluster node number(s) of the HSC controlling the boot device. |

| /B[I]:number     | Specifies a VAXBI node that connects the boot device. The / XMI qualifier must have selected a node containing a DWMBB/ A.                                                                                                                                                                                       |

| /FILE[NAME]:file | Specifies the filename used to boot from an Ethernet-based server. The filename may be 1 to 16 characters in length.                                                                                                                                                                                             |

Table 1–8: Sample BOOT Commands

| <b>Boot Procedure</b>                                    | BOOT Command                             |

|----------------------------------------------------------|------------------------------------------|

| Boot from in-cabinet console load device                 | BOOT CSA1                                |

| Boot VAX/DS from an<br>in-cabinet console load<br>device | BOOT /R5:10 CSA1                         |

| Boot from local RA disk                                  | BOOT /XMI:m DUww                         |

| Boot from HSC disk                                       | BOOT /XMI:m /R5:v/NODE:sstt DUww         |

| Boot from an<br>Ethernet-based CD server                 | BOOT /XMI:m /FILENAME:ISL_LVAX EX0       |

| Boot VAX/DS from an<br>Ethernet-based CD server          | BOOT /XMI:m /FILENAME:ISL_LVAX R5:10 EX0 |

| Boot over the Ethernet with a VAXBI device               | BOOT /XMI:m /BI:x ET0                    |

| Boot VAX/DS from disk                                    | BOOT /XMI:m /R5:10 DUww                  |

| Conversational boot                                      | BOOT /XMI:m /R5:1 DUww                   |

| Boot from VMS shadow set                                 | BOOT /XMI:m /R3:w /NODE:sstt DUww        |

Table 1–9: R5 Bit Functions for VMS

| Bit   | Function                                                                                                                                                                                       |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | Conversational boot. The secondary bootstrap program, SYSBOOT, prompts you for system parameters at the console terminal.                                                                      |  |

| 1     | Debug. If this flag bit is set, the operating system maps the code for the XDELTA debugger into the system page tables of the running operating system.                                        |  |

| 2     | Initial breakpoint. If this flag bit is set, VMS executes a breakpoint (BPT) instruction early in the bootstrapping process.                                                                   |  |

| 3     | Secondary boot from boot block. The secondary boot is a single 512-byte block whose logical block number is specified in General Purpose Register R4.                                          |  |

| 4     | Boots the VAX Diagnostic Supervisor. The secondary loader is an image called DIAGBOOT. $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                              |  |

| 5     | Boot breakpoint. This stops the primary and secondary loaders with a breakpoint (BPT) instruction before testing memory.                                                                       |  |

| 6     | Image header. The transfer address of the secondary loader image comes from the image header for that file. If this flag is not set, control shifts to the first byte of the secondary loader. |  |

| 8     | File name. VMB prompts for the name of a secondary loader.                                                                                                                                     |  |

| 9     | Halt before transfer. VMB executes a HALT instruction before transferring control to the secondary loader.                                                                                     |  |

| 13    | No effect, since console program tests memory.                                                                                                                                                 |  |

| 15    | Reserved for VAX Diagnostic Supervisor.                                                                                                                                                        |  |

| 16    | Do not discard CRD pages.                                                                                                                                                                      |  |

| 31:28 | Specifies the top-level directory number for system disks.                                                                                                                                     |  |

Table 1–10: R5 Bit Functions for ULTRIX

| Bit | Function                                                                        |  |

|-----|---------------------------------------------------------------------------------|--|

| 0   | Forces ULTRIXBOOT to prompt the user for an image name (the default is VMUNIX). |  |

| 1   | Boots the ULTRIX kernel image in single-user mode.                              |  |

| 3   | Must be set, and R4 must be zero.                                               |  |

| 16  | Must be set.                                                                    |  |

Table 1–11 lists the console error messages that appear when the processor halts and the console gains control. Most messages are followed by:

- PC = xxxxxxxx program counter = address at which the processor halted or the exception occurred

- PSL = xxxxxxxx processor status longword = contents of the register

- -SP = xxxxxxxx -SP is one of the following:

ESP executive stack pointer

ISP interrupt stack pointer

KSP kernel stack pointer

SSP supervisor stack pointer

USP user stack pointer

Table 1-12 lists standard console error messages for the Model 500.

Table 1–11: Console Error Messages Indicating Halt

| Error Message                                                | Meaning                                                                                    |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| ?0002 External halt (CTRL/P, break, or external halt).       | CTRL/P or STOP command.                                                                    |

| ?0003 Power-up halt.                                         | System has powered up, had a system reset, or an XMI node reset.                           |

| ?0004 Interrupt stack not valid during exception processing. | Interrupt stack pointer contained an invalid address.                                      |

| ?0005 Machine check occurred during exception processing.    | A machine check occurred while handling another error condition.                           |

| ?0006 Halt instruction executed in kernel mode.              | The CPU executed a Halt instruction.                                                       |

| ?0007 SCB vector bits $\langle 1:0 \rangle = 11$ .           | An interrupt or exception vector in the System Control Block contained an invalid address. |

| ?0008 SCB vector bits $\langle 1:0 \rangle = 10$ .           | An interrupt or exception vector in the System Control Block contained an invalid address. |

| ?000A CHMx executed while on interrupt stack.                | A change-mode instruction was issued while executing on the interrupt stack.               |

Table 1–11 (Cont.): Console Error Messages Indicating Halt

| Error Message                                                          | Meaning                                                                                                            |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| ?0010 ACV/TNV occurred during machine check processing.                | An access violation or translation-not-<br>valid error occurred while handling an-<br>other error condition.       |

| ?0011 ACV/TNV occurred during kernel-stack-not-valid processing.       | An access violation or translation-not-<br>valid error occurred while handling an-<br>other error condition.       |

| ?0012 Machine check occurred during machine check processing.          | A machine check occurred while processing a machine check.                                                         |

| ?0013 Machine check occurred during kernel-stack-not-valid processing. | A machine check occurred while handling another error condition.                                                   |

| ?0019 PSL <26:24>= 101 during interrupt or exception.                  | An exception or interrupt occurred while on the interrupt stack but not in kernel mode.                            |

| ?001A PSL <26:24>= 110 during interrupt or exception.                  | An exception or interrupt occurred while on the interrupt stack but not in kernel mode.                            |

| ?001B PSL <26:24>= 111 during interrupt or exception.                  | An exception or interrupt occurred while on the interrupt stack but not in kernel mode.                            |

| ?001D PSL <26:24> = 101 during REI.                                    | An REI instruction attempted to restore a PSL with an invalid combination of access mode and interrupt stack bits. |

| ?001E PSL <26:24> = 110 during REI.                                    | An REI instruction attempted to restore a PSL with an invalid combination of access mode and interrupt stack bits. |

| ?001F PSL <26:24> = 111 during REI.                                    | An REI instruction attempted to restore a PSL with an invalid combination of access mode and interrupt stack bits. |

Table 1–12: Standard Console Error Messages

| Error Message                                | Meaning                                                                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?0020 Illegal memory reference.              | An attempt was made to reference a virtual address (/V) that is either unmapped or is protected against access under the current PSL.                                                                          |

| ?0021 Illegal command.                       | The command was not recognized, contained the wrong number of parameters, or contained unrecognized or inappropriate qualifiers.                                                                               |

| ?0022 Illegal address.                       | The specified address was recognized as being invalid, for example, a general purpose register number greater than 15.                                                                                         |

| ?0023 Value is too large.                    | A parameter or qualifier value contained too many digits.                                                                                                                                                      |

| ?0024 Conflicting qualifiers.                | A command specified recognized qualifiers that are illegal in combination.                                                                                                                                     |

| ?0025 Checksum did not match.                | The checksum calculated for a block of X command data did not match the checksum received.                                                                                                                     |

| ?0026 Halted.                                | The processor is currently halted.                                                                                                                                                                             |

| ?0027 Item was not found.                    | The item requested in a FIND command could not be found.                                                                                                                                                       |

| ?0028 Timeout while waiting for characters.  | The X command failed to receive a full block of data within the timeout period.                                                                                                                                |

| ?0029 Machine check accessing memory.        | Either the specified address is not implemented by any hardware in the system, or an attempt was made to write a read-only address, for example, the address of the 33rd Mbyte of memory on a 32-Mbyte system. |

| ?002A Unexpected machine check or interrupt. | A valid operation within the console caused a machine check or interrupt.                                                                                                                                      |

| ?002B Command is not implemented.            | The command is not implemented by this console.                                                                                                                                                                |

| ?002C Unexpected exception.                  | An attempt was made to examine either a nonexistent IPR or an unimplemented register in RSSC address range (20140000—20140800).                                                                                |

Table 1–12 (Cont.): Standard Console Error Messages

| Error Message                                                                   | Meaning                                                                                                                                                                                         |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?002D For Secondary Processor n.                                                | This message is a preface to second message describing some error related to a secondary processor. This message indicates which secondary processor is involved.                               |

| ?002E Specified node is not an I/O adapter.                                     | The referenced node is incapable of performing I/O or did not pass its selftest.                                                                                                                |

| ?0030 Write to Z command target has timed out.                                  | The target node of the Z command is not responding.                                                                                                                                             |

| ?0031 Z connection terminated by ^P.                                            | A CTRL/P was typed on the keyboard to terminate a Z command.                                                                                                                                    |

| ?0032 Your node is already part of a Z connection.                              | You cannot issue a Z command while executing a Z command.                                                                                                                                       |

| ?0033 Z connection successfully started.                                        | You have requested a Z connection to a valid node.                                                                                                                                              |

| ?0034 Specified target already has a Z connection.                              | The target node was the target of a previous Z connection that was improperly terminated. Reset the system to clear this condition.                                                             |

| ?0036 Command too long.                                                         | The command length exceeds 80 characters.                                                                                                                                                       |

| ?0037 Explicit interleave list is bad.<br>Configuring all arrays uninterleaved. | The list of memory arrays for explicit interleave includes no nodes that are actually memory arrays. All arrays found in the system are configured.                                             |

| ?0039 Console patches are not usable.                                           | The console patch area in EEPROM is corrupted or contains a patch revision that is incompatible with the console ROM.                                                                           |

| ?003B Error encountered during I/O operation.                                   | An I/O adapter returned an error status while the console boot primitive was performing I/O.                                                                                                    |

| ?003C Secondary processor not in console mode.                                  | The primary processor console needed to communicate with a secondary processor, but the secondary processor was not in console mode. STOP the node or reset the system to clear this condition. |

Table 1–12 (Cont.): Standard Console Error Messages

| Error Message                                               | Meaning                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?003D Error initializing I/O device.                        | A console boot primitive needed to perform I/O, but could not initialize the I/O adapter.                                                                                                                                                                                           |

| ?003E Timeout while sending message to secondary processor. | A secondary processor failed to respond to a message sent from the primary. The primary sends such messages to perform console functions on secondary processors.                                                                                                                   |

| ?003F Microcode power-up self-test failed in REX520.        | Model 400 CPU chip failed its microcoded self-test.                                                                                                                                                                                                                                 |

| ?0040 Key switch must be at "Update" to update EEPROM.      | A SET command was issued, but the key switch was not set to allow updates to the EEPROM.                                                                                                                                                                                            |

| ?0041 Specified node is not a bus adapter.                  | A command to access a VAXBI node specified an XMI node that was not a bus adapter.                                                                                                                                                                                                  |

| ?0042 Invalid terminal speed.                               | The SET TERMINAL command specified an unsupported baud rate.                                                                                                                                                                                                                        |

| ?0043 Unable to initialize node.                            | The INITIALIZE command failed to reset the specified node.                                                                                                                                                                                                                          |

| ?0044 Processor is not enabled to BOOT or START.            | As a result of a SET CPU/NOENABLE command, the processor is disabled from leaving console mode.                                                                                                                                                                                     |

| ?0045 Unable to stop node.                                  | The STOP command failed to halt the specified node.                                                                                                                                                                                                                                 |

| ?0046 Memory interleave set is inconsistent: $n\ n\ \dots$  | The listed nodes do not form a valid memory interleave set. One or more of the nodes might not be a memory array or might be of a different size, or the set could contain an invalid number of members. Each listed array that is a valid memory will be configured uninterleaved. |

| ?0047 Insufficient working memory for normal operation.     | Less than 256 Kbytes per processor of working memory were found. There is insufficient memory for the console to function normally or for the operating system to boot.                                                                                                             |

Table 1–12 (Cont.): Standard Console Error Messages

| Error Message                                                          | Meaning                                                                                                                                                                                                             |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?0048 Uncorrectable memory errors—long memory test must be performed.  | A Model 400 memory array contains<br>an unrecoverable error. The con-<br>sole must perform a slow test to lo-<br>cate all the failing locations.                                                                    |

| ?0049 Memory cannot be initialized.                                    | The specified operation was attempted and prevented.                                                                                                                                                                |

| ?004A Memories not interleaved due to uncorrectable errors:            | The listed arrays would normally have<br>been interleaved (by default or explicit re-<br>quest). Because one or more of them con-<br>tained unrecoverable errors, this inter-<br>leave set will not be constructed. |

| ?004B Internal logic error in console.                                 | The console encountered a theoretically impossible condition.                                                                                                                                                       |

| $?004\mathrm{C}$ Invalid node for Z command.                           | The target of a Z command must be a CPU or an I/O adapter and must not be the primary processor.                                                                                                                    |

| ?004D Invalid node for new primary.                                    | The SET CPU command failed when attempting to make the specified node the primary processor.                                                                                                                        |

| ?004E Specified node is not a processor.                               | The specified node is not a processor, as required by the command.                                                                                                                                                  |

| ?004F System serial number has not been initialized.                   | No CPU in the system contains a valid system serial number.                                                                                                                                                         |

| ?0050 System serial number not initialized on primary processor.       | The primary processor has an uninitialized system serial number. All other processors in the system contain a valid serial number.                                                                                  |

| ?0051 Secondary processor returned bad response message.               | A secondary processor returned an unintelligible response to a request made by the console on the primary processor.                                                                                                |

| ?0052 ROM revision mismatch. Secondary processor has revision $x.xx$ . | The revision of console ROM of a secondary processor does not match that of the primary.                                                                                                                            |

| ?0053 EEPROM header is corrupted.                                      | The EEPROM header has been corrupted. The EEPROM must be restored from the TK tape drive.                                                                                                                           |

Table 1–12 (Cont.): Standard Console Error Messages

| Error Message                                                                  | Meaning                                                                                                                                               |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| ?0054 EEPROM revision mismatch. Secondary processor has revision $x.xx/y.yy$ . | A secondary processor has a different revision of EEPROM or has a different set of EEPROM patches installed.                                          |

| ?0055 Failed to locate EEPROM area.                                            | The EEPROM did not contain a set of data required by the console. The EEP-ROM may be corrupted.                                                       |

| ?0056 Console parameters on secondary processor do not match primary.          | The console parameters are not the same for all processors . $ \\$                                                                                    |

| ?0057 EEPROM area checksum error.                                              | A portion of the EEPROM is corrupted. It may be necessary to reload the EEP-ROM from the TK tape drive.                                               |

| ?0058 Saved boot specifications on secondary processor do not match primary.   | The saved boot specifications are not the same for all processors.                                                                                    |

| ?0059 Invalid unit number.                                                     | A BOOT or SET BOOT command specified a unit number that is not a valid hexadecimal number between 0 and FF.                                           |

| ?005A System serial number mismatch.<br>Secondary processor has xxxxxxxx.      | The indicated serial number of a secondary processor does not match that of the primary.                                                              |

| ?005B Unknown type of boot device.                                             | The console program does not have a boot primitive to support the specified type of device or the device could not be accessed to determine its type. |

| ?005C No HELP is available.                                                    | The HELP command is not supported when the console language is set to International.                                                                  |

| ?005D No such boot spec found.                                                 | The specified boot specification was not found in the EEPROM.                                                                                         |

| ?005E Saved boot spec table full.                                              | The maximum number of saved boot specifications has already been stored.                                                                              |