XXXXXXXXXXXX XXXXXXXXXXXXXXX XXXXXXXXXXXXXXXXX

XXXXXXXXX XXXXXXXX XXXXXX XXX х

х XXX XXXXX XXXXXXX XXXXXXXXX XXXXXXXXXXXX

## DECsystem 5800 System Technical User's Guide

Order Number: EK-580AA-TM-001

This manual serves as a reference on how to write software to this machine and covers the information needed to do field-level repair or programming customized to the CPU. It includes information on interrupts, error handling, and detailed theory of operation.

**Bighal Equipment Corporation**

#### First Printing, July 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1990 by Digital Equipment Corporation

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation

| PDP    | VAXcluster              |

|--------|-------------------------|

| ULTRIX | VAXELN                  |

| UNIBUS | VMS                     |

| VAX    | XMI                     |

| VAXBI  | d i and all             |

|        | ULTRIX<br>UNIBUS<br>VAX |

MIPS is a registered trademark of MIPSCO. Inc.

This document was prepared using VAX DOCUMENT, Version 1.1

| PREF     | ACE                                  | xix  |

|----------|--------------------------------------|------|

| HAPTER 1 | THE DECSYSTEM 5800 SYSTEM OVERVIEW   | 1–1  |

| 1.1      | DECSYSTEM 5800 INTRODUCTION          | 1-2  |

| 1.2      | DECSYSTEM 5800 CONFIGURATIONS        | 1-3  |

| 1.3      | DECSYSTEM 5800 SYSTEM ARCHITECTURE   | 1-4  |

| 1.4      | TYPICAL SYSTEM                       | 1-6  |

| 1.5      | DECSYSTEM 5800 (FRONT VIEW)          | 1-8  |

| 1.6      | DECSYSTEM 5800 (REAR VIEW)           | 1-9  |

| 1.7      | SUPPORTED VAXBI ADAPTERS AND OPTIONS | 1–10 |

| 1.8      | XMI BACKPLANE AND CARD CAGE          | 1-11 |

| 1.9      | VAXBI BACKPLANE AND CARD CAGE        | 1-13 |

| 1.10     |                                      | 1-14 |

| 1.11     | TK70 TAPE DRIVE                      | 1-15 |

| 1.12     | I/O CONNECTIONS                      | 1-16 |

| 1.13     | POWER SYSTEM                         | 1–17 |

| 1.14     | COOLING SYSTEM                       | 1-19 |

161

| PTER 2 |           |            |                                                          | 2–1           |

|--------|-----------|------------|----------------------------------------------------------|---------------|

| 2.1    | XMI O     | /ERVIEW    |                                                          | 2-2           |

|        | 2.1.1     | XMI Syst   | em Block Diagram Description                             |               |

|        | 2.1.2     | XMI Com    |                                                          |               |

|        | 2.1.3     | XMI Data   | Transactions                                             |               |

|        | 2.1.4     |            | rupt Transactions                                        |               |

|        | 2.1.5     |            | on                                                       |               |

|        | 2.1.6     |            | grity                                                    |               |

| 2.2    |           | DRESSING   |                                                          | 2-1           |

|        | 2.2.1     |            | lory Space                                               |               |

|        | 2.2.2     |            | Space                                                    |               |

|        | ensensens | 2221       |                                                          | - <b>6</b> -1 |

|        |           |            | XMI Nodespace • 2-14                                     |               |

|        |           | 2.2.2.3    | •                                                        |               |

| 2.3    | ARBIT     | RATION CY  | CLES                                                     | 2-1           |

| 2.4    | XMI C     | YCLES      |                                                          | 2-1           |

|        | 2.4.1     | Function   | Codes                                                    | 2-1           |

|        | 2.4.2     | Comman     | d Cycles                                                 | 2-1           |

|        |           |            | Command Field • 2-20                                     |               |

|        |           |            | Mask Field • 2-21                                        |               |

|        |           | 2.4.2.3    | Length Field • 2-22<br>Address Field • 2-23              |               |

|        |           |            |                                                          |               |

|        | 040       |            | Node Specifier Field • 2-24                              | • •           |

|        | 2.4.3     |            | ta Cycles                                                | 2-2           |

|        | 2.4.4     |            | ad Data (GRD) and Corrected Read Data<br>ie (CRD) Cycles | 2-2           |

|        | 2.4.5     | -          | Response Cycle (LOC)                                     |               |

|        | 2.4.6     |            | or Response Cycle (RER)                                  |               |

|        | 2.4.7     |            |                                                          |               |

|        | 6.9.1     | 1107 TAA11 | Cycle                                                    | 6~6           |

| 2.5    |           | RANSACTIC  |                                                          | 2-2           |

|        | 2.5.1     |            | insaction                                                |               |

|        | 2.5.2     | Interlock  | Read Transaction                                         | 2-2           |

|        | 2.5.3     | Write Ma   | isk Transaction                                          | 2-2           |

|        | 2.5.4     |            | Write Mask Transaction                                   |               |

|        | 2.5.5     | Interrupt  | and identify Transactions                                |               |

|        | 2.5.6     |            | Vector Interrupt Transactions                            |               |

|           | 2.5.7          | Transact   | lion Examples                                       | 232  |

|-----------|----------------|------------|-----------------------------------------------------|------|

|           |                | 2.5.7.1    | Single Data Cycle Reads • 2-32                      |      |

|           |                | 2.5.7.2    | Multiple Data Cycle Reads • 2-34                    |      |

|           |                | 2.5.7.3    | Longword and Quadword Writes • 2-37                 |      |

|           |                | 2.5.7.4    | Multiple Data Cycle Writes • 2-37                   |      |

| 2.6       | XMI IN         | ITIALIZATI | ON                                                  | 2-38 |

|           | 2.6.1          | Ceuses     | of an initialization                                | 2-39 |

|           | 2.6.2          | Power-U    | lp                                                  | 2-39 |

|           | 2.6.3          | System     | Reset                                               | 240  |

|           | 2.6.4          | Node R     | 9set                                                | 2-40 |

| 2.7       | XMI R          | EGISTERS   |                                                     | 2-41 |

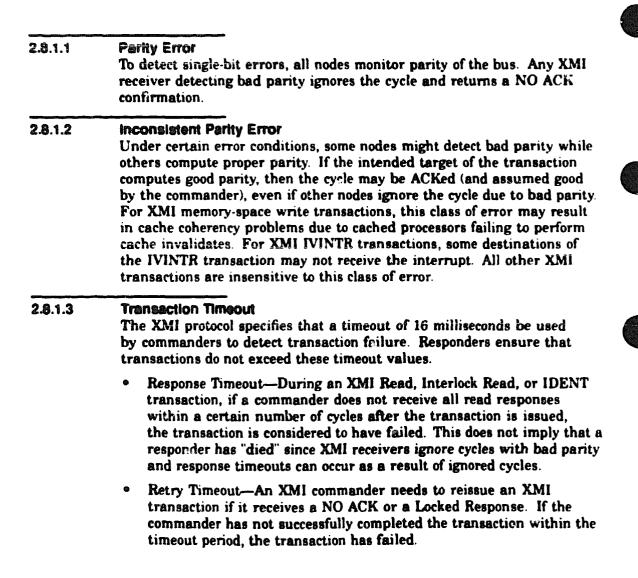

| 2.8       | XMI E          | RRORS      |                                                     | 2-42 |

|           | 2.8.1          | Error Co   | onditions                                           | 2-42 |

|           |                | 2811       |                                                     |      |

|           |                | 2812       |                                                     |      |

|           |                | 2.8.1.3    | Transaction Timeout • 2-42<br>Sequence Error • 2-43 |      |

|           | 2.8.2          |            | •                                                   | 2-44 |

|           |                |            | andling                                             |      |

|           | 2.8.3<br>2.8.4 |            | eporting                                            |      |

| CHAPTER 3 | KN58           | A/A INTE   | RFACE MODULE                                        | 3–1  |

|           |                |            |                                                     |      |

| 3.1       | KN58/          | A/A INTER  | FACE MODULE FEATURES                                | 3–2  |

| 3.2       | PRIVA          | TE VO AD   | DRESS SPACE MAP                                     | 3-4  |

| 3.3       | MAIN           |            | PROCESSOR                                           | 36   |

|           | 3.3.1          | CVAX H     | lardware Restart Sequence                           |      |

|           | 3.3.2          | Clock (    | Chip                                                | 3-6  |

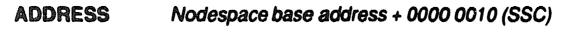

| 3.4       | SYST           | EM SUPPO   | DRT CHIP (SSC)                                      | 3-7  |

|           | 3.4.1          | SSC FL     | Inctions                                            | 3_7  |

| 3.5       | EEPP           | IOM        |                                                     | 3-8  |

Q

|     | 3.5.1 | EEPROM Access                                                               |                                                                                                                 | 3-8  |

|-----|-------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|

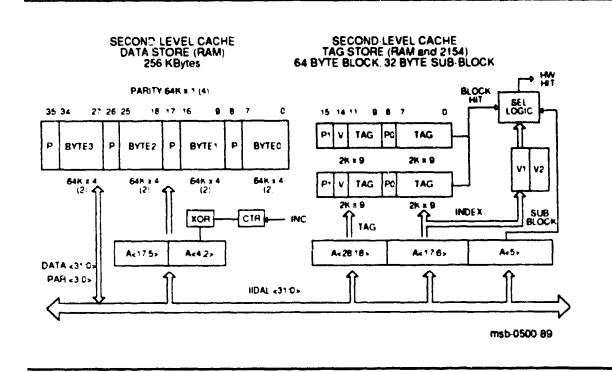

| 3.6 | SECO  | ID-LEVEL CACHE                                                              |                                                                                                                 | 3-9  |

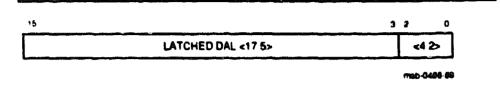

|     | 3.6.1 | Second-Level Cache Description                                              |                                                                                                                 | 3–10 |

|     | 3.6.2 |                                                                             |                                                                                                                 | 3-14 |

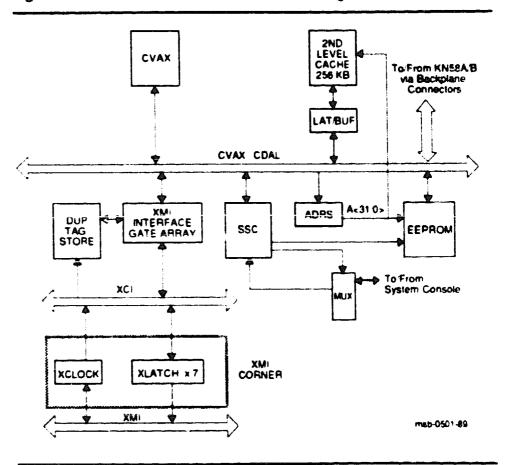

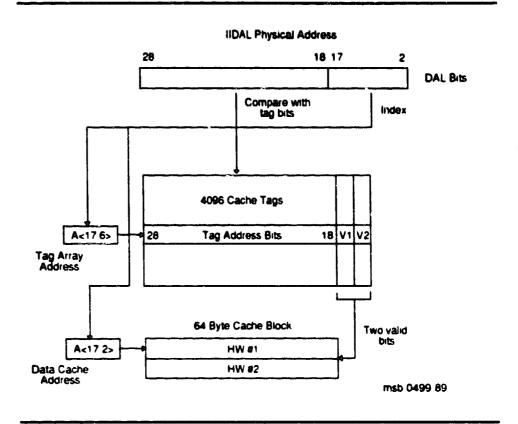

| 3.7 | XMI C | ORNER-TO-KN58A/A INTERFACE                                                  |                                                                                                                 | 3-15 |

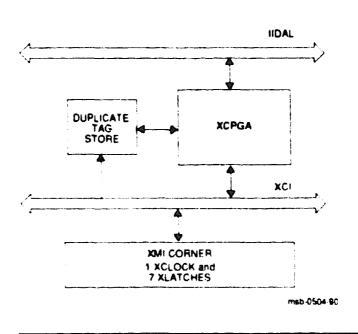

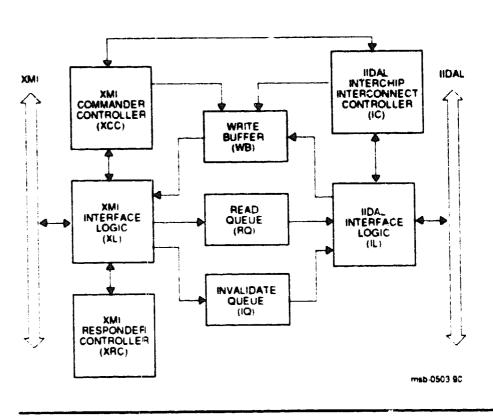

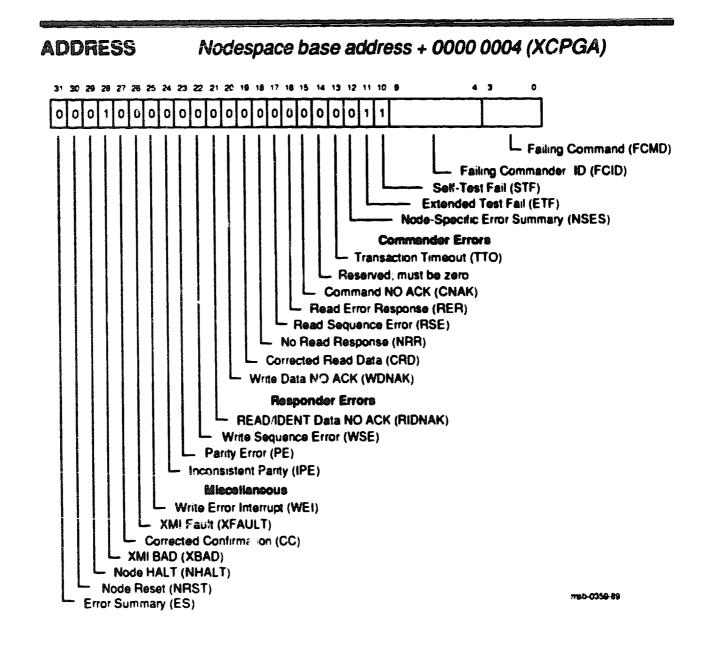

|     | 3.7.1 | The XCPGA Chip                                                              |                                                                                                                 | 3–19 |

|     | 3.7.2 | The XCPGA Write Buffer                                                      |                                                                                                                 | 3-21 |

|     | 3.7.3 | Duplicate Tag Store                                                         |                                                                                                                 | 3-22 |

|     | 3.7.4 | XMI Interrupt Operation                                                     |                                                                                                                 | 3-23 |

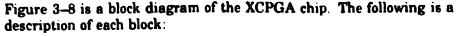

|     | 3.7.5 | Implied Vector Interrupts (IVINTR)                                          |                                                                                                                 | 3-25 |

| 3.8 | KN58/ |                                                                             | in a state of the st | 3-27 |

|     | 3.8.1 | XMI Registers and Control and Status Register 1<br>Characteristics          |                                                                                                                 | 3-27 |

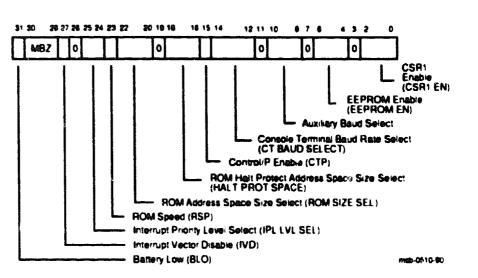

|     |       | CONTROL AND STATUS REGISTER 1 (CSR1)                                        | 3-29                                                                                                            |      |

|     |       | SYSTEM TYPE (SYSTYPE)                                                       | 3-37                                                                                                            |      |

|     |       | SSC BASE ADDRESS REGISTER (SSCBR)                                           | 3-39                                                                                                            |      |

|     |       | SSC CONFIGURATION REGISTER (SSCCR)                                          | 3-41                                                                                                            |      |

|     |       | HDAL BUS TIMEOUT CONTROL REGISTER (CBTCR)                                   | 3-46                                                                                                            |      |

|     |       | TIME OF YEAR CLOCK REGISTER (TODR)                                          | 3-47                                                                                                            |      |

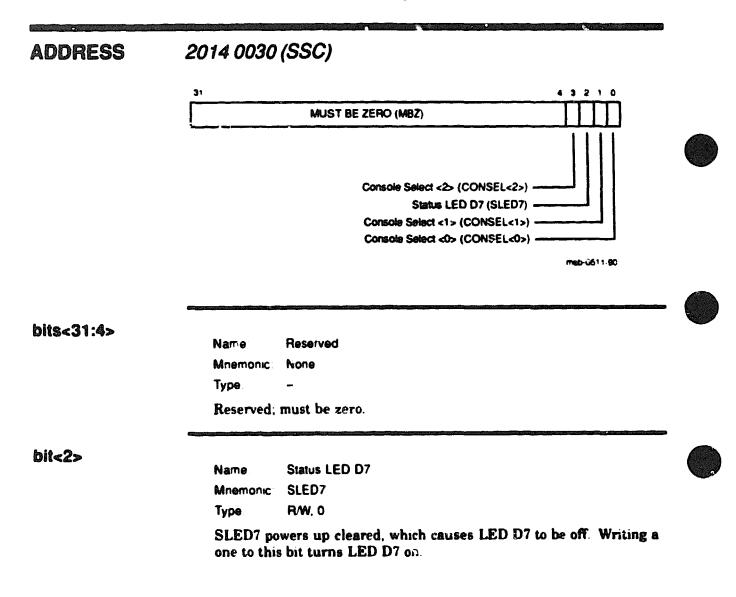

|     |       | CONSOLE SELECT REGISTER (CONSEL)                                            | 3-48                                                                                                            |      |

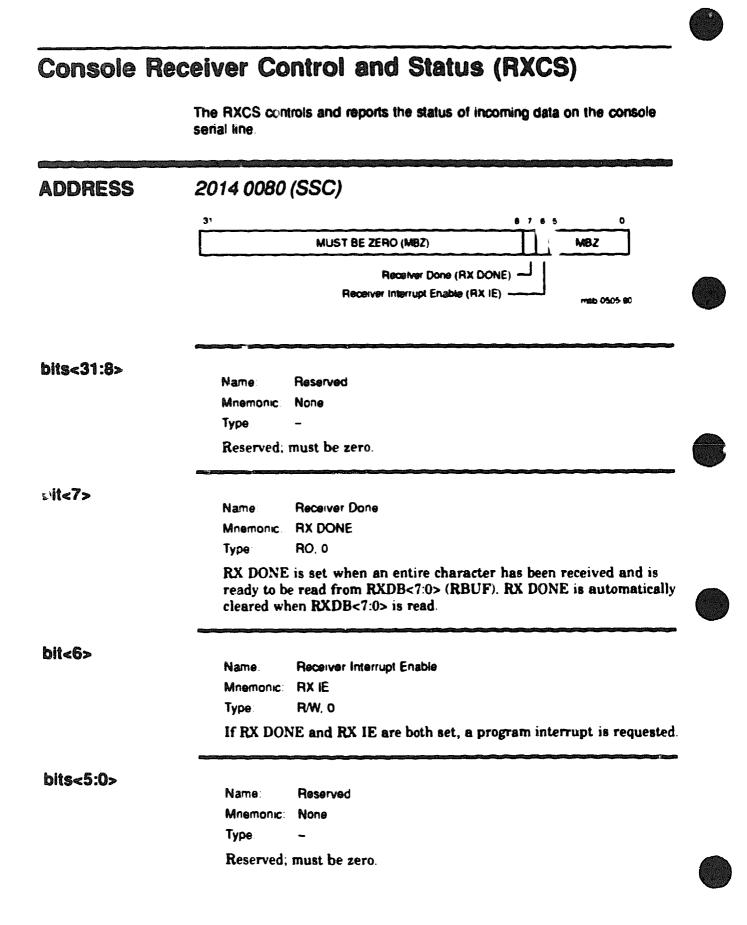

|     |       | CONSOLE RECEIVER CONTROL AND STATUS                                         | 3-50                                                                                                            |      |

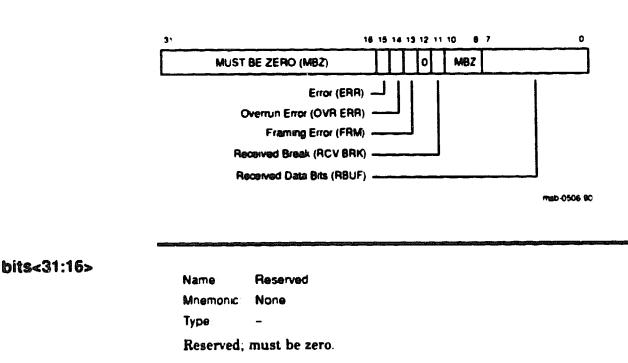

|     |       | (RXCS)<br>Console Receiver Data Buffer (RXDB)                               | 3-30<br>3-51                                                                                                    |      |

|     |       | CONSOLE TRANSMITTER CONTROL AND STATUS                                      | 3-31                                                                                                            |      |

|     |       | (TXCS)                                                                      | 3-53                                                                                                            |      |

|     |       | CONSOLE TRANSMITTER DATA BUFFER (TXDB)                                      | 3-55                                                                                                            |      |

|     |       | VO SYSTEM RESET REGISTER (IORESET)                                          | 3-56                                                                                                            |      |

|     |       | TIMER CONTROL REGISTER 0 (TCR0)                                             | 3-57                                                                                                            |      |

|     |       | TIMER INTERVAL REGISTER 0 (TIR0)                                            | 3-60                                                                                                            |      |

|     |       | TIMER NEXT INTERVAL REGISTER 0 (TNIRO)                                      | 3-61                                                                                                            |      |

|     |       | TIMER INTERRUPT VECTOR REGISTER 0 (TIVRO)                                   | 3-62                                                                                                            |      |

|     |       | TIMER CONTROL REGISTER 1 (TCR1)                                             | 3-63                                                                                                            |      |

|     |       | TIMER INTERVAL REGISTER 1 (TIR1)                                            | 3-66                                                                                                            |      |

|     |       | TIMER NEXT INTERVAL REGISTER 1 (TNIR1)                                      | 3-67                                                                                                            |      |

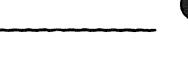

|     |       | TIMER INTERRUPT VECTOR REGISTER 1 (TIVR1)                                   | 368<br>369                                                                                                      |      |

|     |       | CSR1 BASE ADDRESS REGISTER (CSR1BADR)<br>CSR1 ADDRESS DECODE MASK REGISTER  | 3-08                                                                                                            |      |

|     |       | (CSR1ADMR)                                                                  | 7-10                                                                                                            |      |

|     |       | EEPROM BASE ADDRESS REGISTER (EGRADR)                                       | 3-71                                                                                                            |      |

|     |       | EEPROM ADDRESS DECODE MASK REGISTER                                         |                                                                                                                 |      |

|     |       | (EEADMR)                                                                    | 3-72                                                                                                            |      |

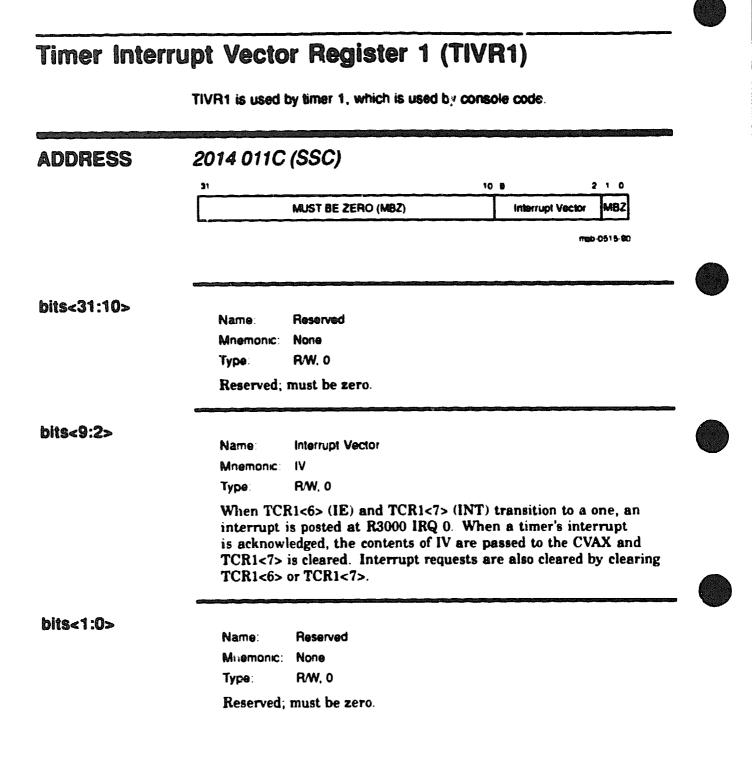

|     |       | DEVICE REGISTER (XDEV)                                                      | 3-73                                                                                                            |      |

|     |       | BUS ERROR REGISTER (XBER)                                                   | 3-75                                                                                                            |      |

|     |       | FAILING ADDRESS REGISTER (XFADR)                                            | 3-84                                                                                                            |      |

|     |       | XMI GENERAL PURPOSE REGISTER (XGPR)<br>CONTROL AND STATUS REGISTER 2 (CSR2) | 3-85<br>3-86                                                                                                    |      |

| 3.9   | INITIAL | IZATICH, SELF-TEST, AND BOOTING                              | 394        |

|-------|---------|--------------------------------------------------------------|------------|

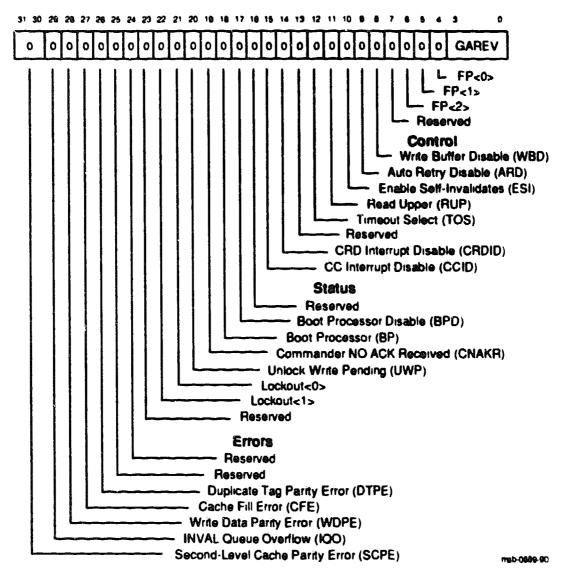

|       | 3.9.1   | Initialization Overview                                      | 394        |

|       | 3.9.2   | Initialization Details                                       | 3-96       |

|       |         | 3.9.2.1 Restart Sequence • 3-98                              |            |

|       |         | 3 9 2.2 Node Reset • 3-100<br>3 9 2.3 Halt Interrupt • 3-101 |            |

|       |         | 3.9.2.3 Halt Interrupt • 3-101                               |            |

|       |         | 3.9.2.4 Errors • 3-101                                       |            |

|       | 3.9.3   | Memory Configuration                                         | 3-101      |

|       |         | 3.9.3.1 Selection of Interleave + 3–102                      |            |

|       |         | 3.9.3.2 Memory Testing and the Bitmap • 3–103                |            |

|       | 3.9.4   | DWMBA Configuration                                          | 3-104      |

|       | 3.9.5   | Initialized State                                            | 3-10       |

|       | 3.9.6   | Restarting or Bootstrapping the Operating System             | 3-106      |

|       |         | 3.9.6.1 Operating System Restart • 3-106                     |            |

|       |         | 3.9.6.2 Operating System Bootstrap • 3-107                   |            |

|       |         | 3 9.6.2.1 Bootstrap Support Routines in the Console • 3-108  |            |

|       | 3.9.7   | Console Use of Address Space                                 | 3-10       |

|       | 3.9.8   | Bootstrap of the VAX Diagnostic Supervisor (VAX/DS)          | 3-110      |

|       | 0.010   | 3.9.8.1 Parameters Passed to the Boot Primitive • 3–110      |            |

|       |         | 3982 Parameters Passed to the Bootblock Program • 3-112      |            |

|       |         | 3.9.8.3 Parameters Required by the Boot Primitive • 3–112    |            |

|       |         | 3.9.8.4 Considerations for Tape Drives • 3–112               |            |

| 3.10  |         |                                                              |            |

|       | PROG    | NAR I I I I I I I I I I I I I I I I I I I                    | 3-11       |

|       | 3.10.1  | Required Communications Paths                                | 3-11       |

|       | 3.10.2  | Console Communications Area                                  | 3-11       |

|       | 3.10.3  | Sending a Message to Another Processor                       | 3-12       |

| 3.11  | KN58A   | A INTERFACE MODULE ERROR HANDLING                            | 3-12       |

|       | 3.11.1  | Parity Generation and Checking for Error Detection           | 3-12       |

|       | 3.11.2  | Error Interrupt Service Routines                             | 3-12       |

|       | 3.11.3  | •                                                            | 3-12       |

|       | 3.11.3  |                                                              | J 14       |

| TER 4 | KN58/   | VB CPU MODULE                                                | <b>4</b> — |

| 4.1   | KN584   | B CPU MODULE FEATURES                                        | 4-         |

| R3000 CPU |                 |  |     |  |

|-----------|-----------------|--|-----|--|

|           | D2000 Decletore |  | 4-4 |  |

|     | 4.2.2                          | Coproces   | sor 0 (CP0) Registers                                                                                            |                        | 4-5          |

|-----|--------------------------------|------------|------------------------------------------------------------------------------------------------------------------|------------------------|--------------|

|     |                                |            | YHI REGISTER (ENTRYHI)                                                                                           | 4-6                    |              |

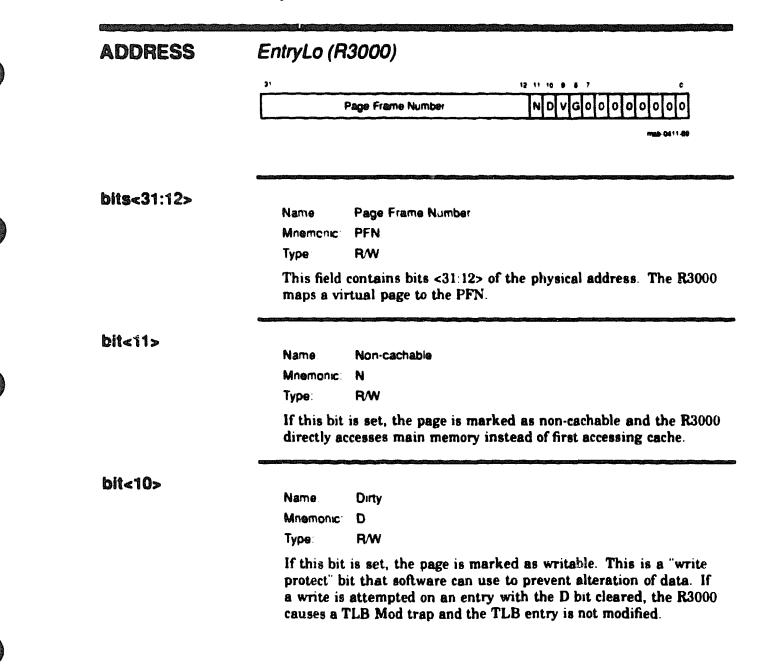

|     |                                | TLB ENTR   | YLO REGISTER (ENTRYLO)                                                                                           | 4-7                    |              |

|     |                                | TLB INDE)  | ( REGISTER (INDEX)                                                                                               | 4-9                    |              |

|     |                                | TLB RAND   | IOM REGISTER (RANDOM)                                                                                            | 4-10                   |              |

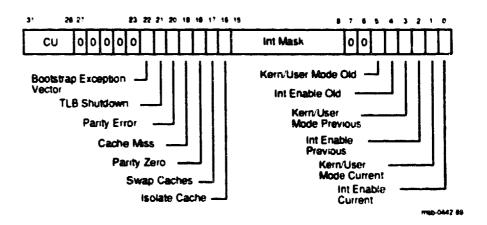

|     | R3000 STATUS REGISTER (STATUS) |            |                                                                                                                  |                        |              |

|     |                                |            | EGISTER (CAUSE)                                                                                                  | 4-15                   |              |

|     |                                | EXCEPTIO   | N PROGRAM COUNTER REGISTER (EPC)                                                                                 | 4-18                   |              |

|     |                                | CONTEXT    | 4-19                                                                                                             |                        |              |

|     |                                |            | UAL ADDRESS REGISTER (BADVADDR)                                                                                  | 4-20                   |              |

|     |                                | PROCESS    | OR REVISION IDENTIFIER REGISTER                                                                                  |                        |              |

|     |                                | (PRID)     |                                                                                                                  | 4-21                   |              |

|     | 4.2.3                          | R3000 Pi   | peline Architecture                                                                                              |                        | 422          |

|     | 4.2.4                          | Data Type  | es                                                                                                               |                        | 4-22         |

|     | 4.2.5                          | Instructio | on Set                                                                                                           |                        | 4-23         |

|     |                                | 4.2.5 1    | Load and Store Instructions • 4-24                                                                               |                        |              |

|     |                                | 4.2.5.2    | Computational Instructions • 4-24                                                                                |                        |              |

|     |                                | 4.2.5.3    | Jump and Branch Instructions • 4-25                                                                              |                        |              |

|     |                                | 4.2.5.4    | Coprocessor Instructions • 4-25                                                                                  |                        |              |

|     |                                | 4.2.5.5    | Special Instructions • 4-25                                                                                      |                        |              |

|     | 4.2.6                          | Memory     | Management                                                                                                       | فالديب الترجيع والمرجع | 4-26         |

|     |                                | 4.2.6.1    | Translation Lookaside Buffer • 4-26                                                                              |                        |              |

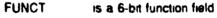

|     |                                | 4.2.6.2    | R3000 Operating Modes • 4-25                                                                                     |                        |              |

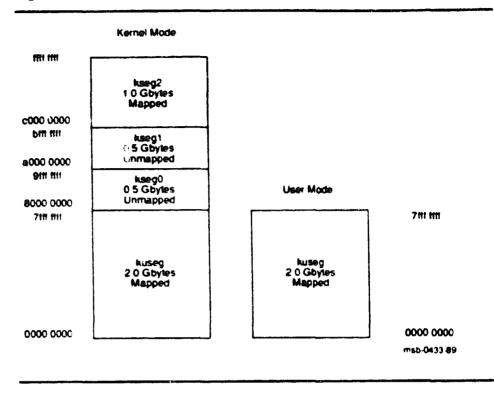

|     | 4.2.7                          | Memory     | Mapping                                                                                                          |                        | 4-28         |

|     |                                | 4.2.7.1    |                                                                                                                  |                        |              |

|     |                                | 4.2.7 2    |                                                                                                                  | Associated             | with I/O     |

|     |                                |            | Adapter 7 • 4-29                                                                                                 |                        |              |

|     | 4.2.8                          | Interrupt  | S                                                                                                                |                        | 4-30         |

|     | 4.2.9                          |            | ns                                                                                                               |                        | 4-31         |

|     |                                |            |                                                                                                                  |                        |              |

|     |                                |            | المواسم والمريز الأريز الأربية والمراجع والمراجع والمراجع والمراجع والمراجع والمراجع والمواصية والمواحي والمراجع |                        | 4-33         |

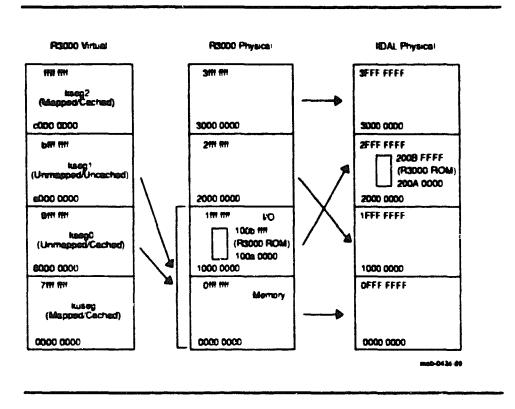

| 4.3 | R3010                          |            |                                                                                                                  |                        | 4-33<br>4-33 |

|     | 4.3.1                          | FPA Reg    | listers                                                                                                          |                        |              |

|     |                                |            | Floating-Point General Registers (FGRs) • 4                                                                      | F-34                   |              |

|     |                                | 4.3.1.2    |                                                                                                                  | -34                    |              |

|     |                                | 4.3.1.3    |                                                                                                                  | -J-4<br>435            |              |

|     |                                |            | ITROL/STATUS REGISTER (FCR31)<br>LEMENTATION/REVISION REGISTER (FCR0)                                            | 4-37                   |              |

|     |                                |            |                                                                                                                  |                        | 438          |

|     | 4.3.2                          | FPA For    |                                                                                                                  |                        |              |

|     | 4.3.3                          |            | essor Operation                                                                                                  |                        | 4-38         |

|     |                                | 4.3.3.1    |                                                                                                                  |                        |              |

|     |                                |            | Floating-Point Operations • 4-39                                                                                 |                        |              |

|     |                                |            | Exceptions • 4-39                                                                                                |                        |              |

|     | 4.3.4                          | instruct   | ion Set Ovorview                                                                                                 |                        | 4-39         |

|     | 4.3.5                          | R3010 P    | Pipeline Architecture                                                                                            |                        | 4-40         |

|     |                                |            |                                                                                                                  |                        |              |

|     |                                |            |                                                                                                                  |                        |              |

| FIRST- | LEVEL CACHE MEMORY                      |

|--------|-----------------------------------------|

| 4.5.1  | First-Level Cechable References         |

| 4.5.2  | First-Level Cache Organization          |

| 4.5.3  | Initializing the First-Level Cache      |

| 4.5.4  | First-Level Cache Address Translation   |

| 4.5.5  | First-Level Cache Data Block Allocation |

| 4.5.6  | First-Level Cache Behavlor on Writes    |

| 4.5.7  | First-Level Cache Coherency             |

| 4.5.8  | First-Level Cache Error Detection       |

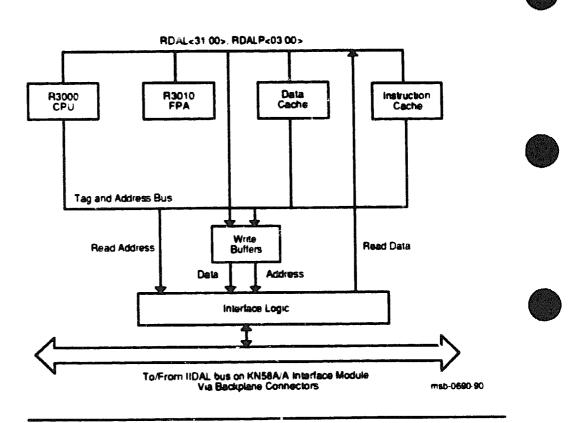

| INTER | FACE LOGIC                      |                                                                                                      |

|-------|---------------------------------|------------------------------------------------------------------------------------------------------|

| 4.6.1 | The IIDAL Bus                   |                                                                                                      |

| 4.6.2 | Read Operation                  |                                                                                                      |

| 4.6.3 | Write Operation                 | و معروف و معرف و |

| 4.6.4 | Interrupt Acknowledge Operation |                                                                                                      |

| 4.6.5 | Lock Transactions               |                                                                                                      |

| 4.6.6 | DMA on the IIDAL Bus            |                                                                                                      |

| 4.6.7 | ldie                            |                                                                                                      |

## CHAPTER 5 MS62A MEMORY MODULE

4.5

4.6

| 5.1 | MODULE FEATURES                     | 5-2 |

|-----|-------------------------------------|-----|

| 5.2 | TECHNICAL DESCRIPTION               | 5-3 |

| 5.3 | SELF-TEST AND INITIALIZATION        | 5-4 |

| 5.4 | STARTING ADDRESS AND INTERLEAVING   | 5-5 |

|     | 5.4.1 Starting and Ending Addresses | 5-5 |

|     | 5.4.2 Interleaving                  | 5-5 |

5-1

| 5.5 | CONTROL AND STATUS REGISTERS         |      | 5E |

|-----|--------------------------------------|------|----|

|     | DEVICE REGISTER (XDEV)               | 58   |    |

|     | BUS ERROR REGISTER (XBER)            | 59   |    |

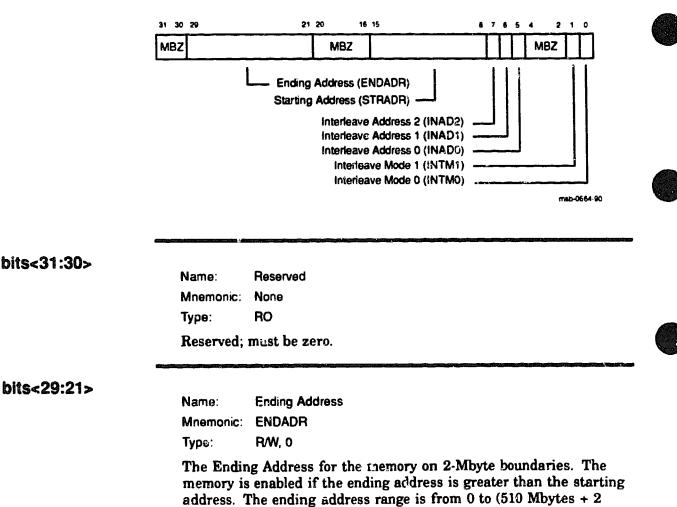

|     | STARTING AND ENDING ADDRESS REGISTER |      |    |

|     | (SEADR)                              | 5-12 |    |

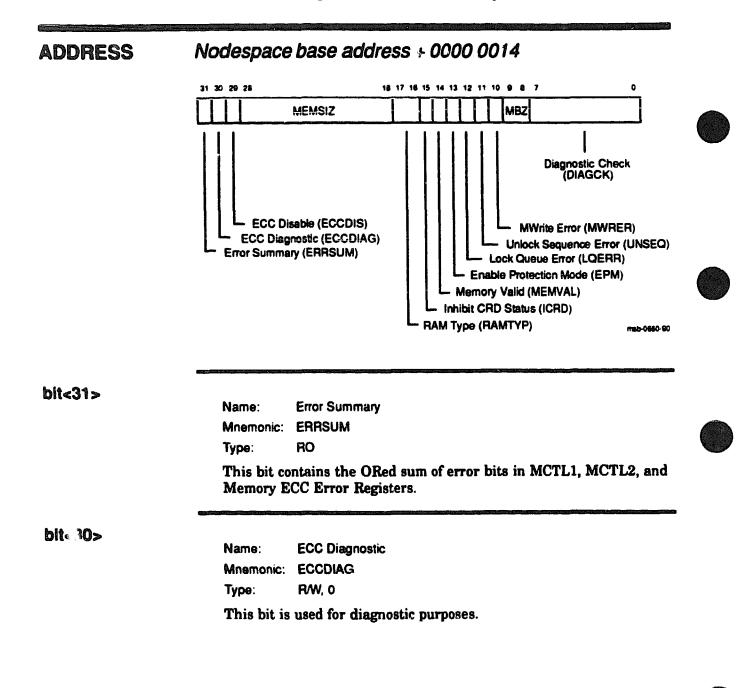

|     | MEMORY CONTROL REGISTER 1 (MCTL1)    | 5-14 |    |

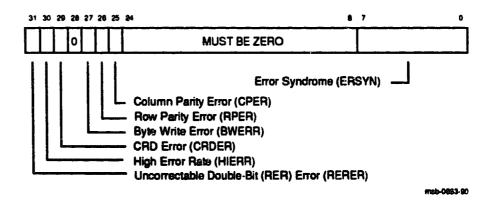

|     | MEMORY ECC ERROR REGISTER (MECER)    | 5-18 |    |

|     | MEMORY ECC ERROR ADDRESS REGISTER    |      |    |

|     | (MECEA)                              | 5-21 |    |

|     | MEMORY CONTROL REGISTER 2 (MCTL2)    | 5-22 |    |

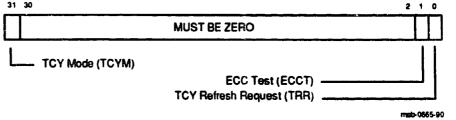

|     | TCY TESTER REGISTER (TCY)            | 5-24 |    |

|     | INTERLOCK FLAG REGISTER (IFLGM)      | 5-25 |    |

| 5.6 | ERROF | R HANDLING AND COMMAND RESPONSES | 5-27 |

|-----|-------|----------------------------------|------|

|     | 5.6.1 | Read Errors                      | 5-27 |

|     | 5.6.2 | Full Write Errors                | 5-27 |

|     | 5.6.3 | Partial Write Errors             | 5-28 |

#### CHAPTER 6 DWMBA XMI-TO-VAXBI ADAPTER

6.3.4

| 6.1 | DWMBA  | OVERVIE    | W                                                | 6-2  |

|-----|--------|------------|--------------------------------------------------|------|

| 6.2 | CPU TR | ANSACTIC   | INS                                              | 6-4  |

|     | 6.2.1  | General C  | peration                                         | 6-5  |

|     | 6.2.2  | VAXBI I/O  | Space Reads                                      | 66   |

|     | 6.2.3  | VAXBI I/O  | Space Writes                                     | 66   |

|     | 6.2.4  | interrupts | •<br>• • • • • • • • • • • • • • • • • • •       | 67   |

|     |        | 6.2.4.1    | XMI IDENT to VAXBI IDENT • 6-7                   |      |

|     |        | 6.2.4.2    | XMI IDENT with DWMBA Adapter Pending Interrupt • | 67   |

|     |        | 6.2.4.3    | Passive Release of VAXBI Interrupts • 6-7        |      |

| 6.3 | DMA TF |            | DNS                                              | 68   |

|     | 6.3.1  | VAXBI-to-  | XMI Memory Space Reads                           | 6–9  |

|     | 6.3.2  | VAXBI-to-  | XMI Memory Space Interlock Reads                 | 6-10 |

|     | 6.3.3  | VAXBI-to-  | XMI Memory Writes                                | 6-10 |

VAXBI-Generated Interrupts

6-1

6-10

6-10

| 5.4 | DWMBA                  | XMI-TO-V                                                                                                                                                                        | AXBI ADAPTER REGISTERS                           | القائلة بودي بيبية بريو بيبي في ع                   | 6-11 |

|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|------|

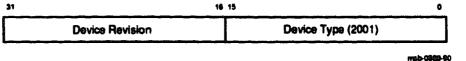

|     |                        | DEVICE REGISTER (XDEV) 6-14                                                                                                                                                     |                                                  |                                                     |      |

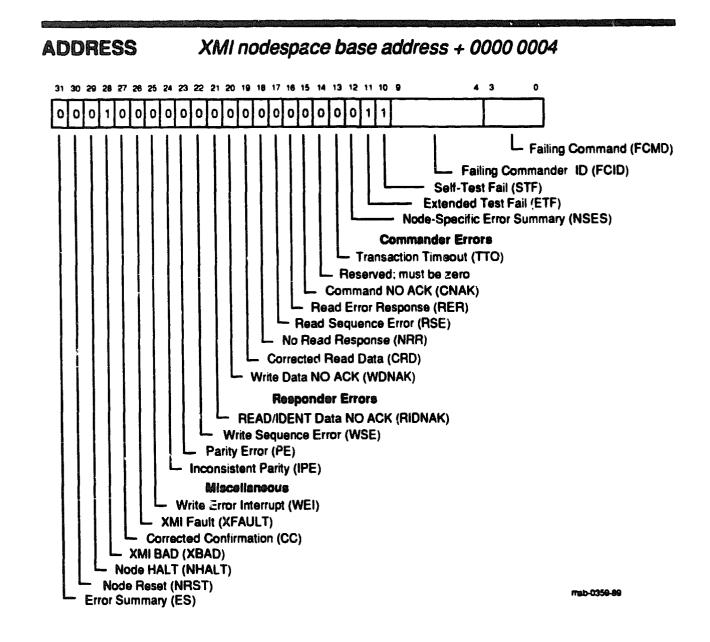

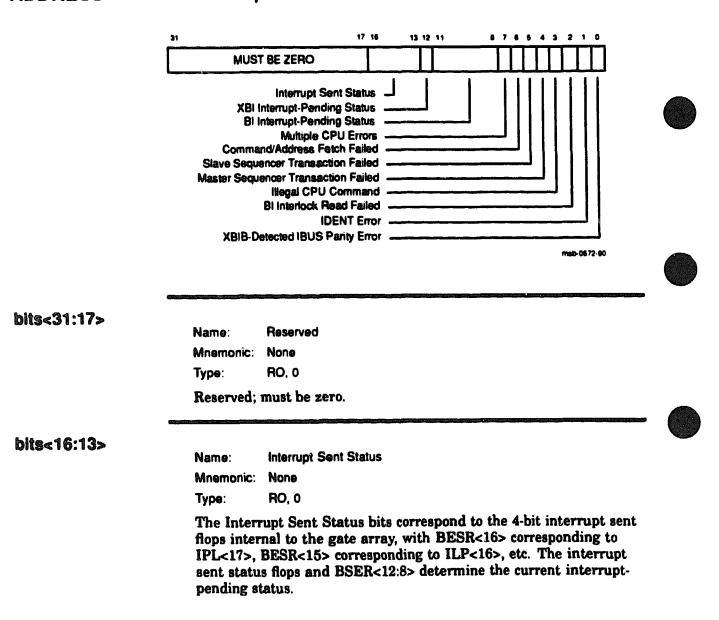

|     |                        | BUS ERROR REGISTER (XBER)6-15FAILING ADDRESS REGISTER (XFADR)6-21RESPONDER ERROR ADDRESS REGISTER (AREAR)6-22ERROR SUMMARY REGISTER (AESR)6-23INTERRUPT MASK REGISTER (AMR)6-28 |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 |                                                  |                                                     |      |

|     |                        | INTERRUPT MASK REGISTER (AIMR) 6-28 IMPLIED VECTOR INTERRUPT                                                                                                                    |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 | 10N/DIAGNOSTIC REGISTER (AIVINTR)                | 6-33                                                |      |

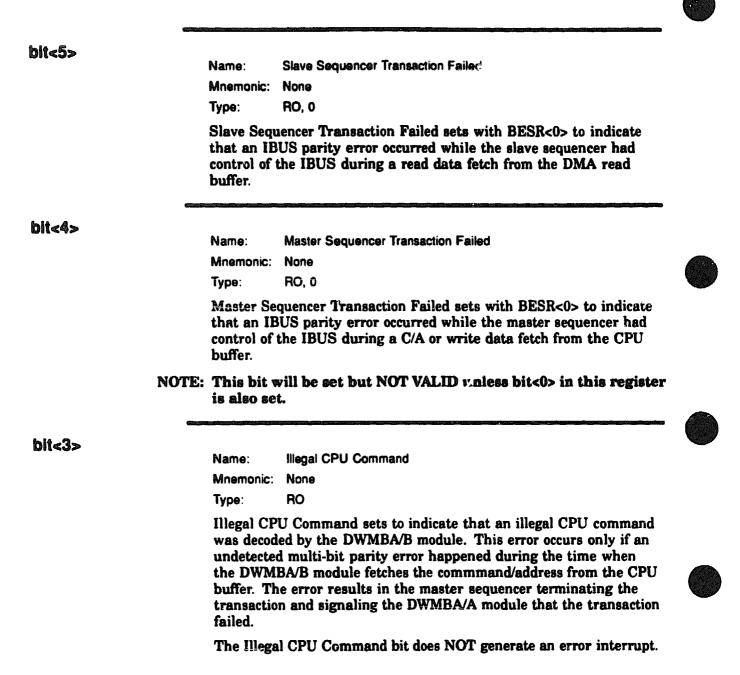

|     |                        |                                                                                                                                                                                 | EGISTER (ADG1)                                   | 6-34                                                |      |

|     |                        |                                                                                                                                                                                 | AND STATUS REGISTER (BCSR)                       | 6-37                                                |      |

|     |                        | ERROR SUMMARY REGISTER (BESR)6-40INTERRUPT DESTINATION REGISTER (BIDR)6-45TIMEOUT ADDRESS REGISTER (BTIM)6-46                                                                   |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 |                                                  |                                                     |      |

|     |                        |                                                                                                                                                                                 | DFFSET REGISTER (BVOR)                           | 6-47                                                |      |

|     |                        |                                                                                                                                                                                 | REGISTER (BVR)                                   | 6-48                                                |      |

|     |                        | DIAGNOS                                                                                                                                                                         | TIC CONTROL REGISTER 1 (EDCR1)                   | 6-49                                                |      |

|     | RESERVED REGISTER 6-51 | 6-51                                                                                                                                                                            |                                                  |                                                     |      |

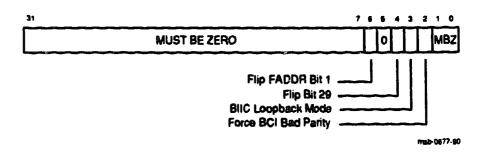

|     |                        | DEVICE R                                                                                                                                                                        | EGISTER (DTYPE)                                  | 6-52                                                |      |

| 6.5 | INTERR                 | UPTS                                                                                                                                                                            |                                                  |                                                     | 6-53 |

|     | 6.5.1                  |                                                                                                                                                                                 | XMI-to-VAXBI Adapter Vector Formats and<br>nents | l                                                   | 6-54 |

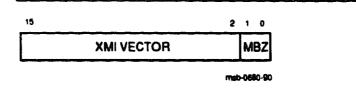

|     |                        | 65.1.1                                                                                                                                                                          | XMI Bus Vector Format • 6-55                     |                                                     |      |

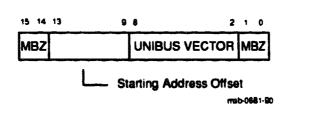

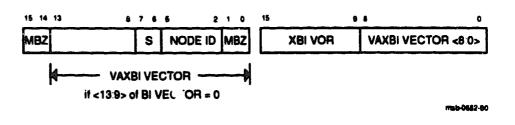

|     |                        |                                                                                                                                                                                 | Offsettable Bus Vectors • 6-55                   |                                                     |      |

|     |                        |                                                                                                                                                                                 | VAXBI Node Vectors • 6-55                        |                                                     | _    |

|     | 6.5.2                  | -                                                                                                                                                                               | Levels and Vectors                               |                                                     | 6-5  |

|     | 6.5.3                  |                                                                                                                                                                                 |                                                  |                                                     | 6-5  |

|     |                        | 6531                                                                                                                                                                            |                                                  |                                                     |      |

|     | 6 F A                  |                                                                                                                                                                                 | VAXBI-Generated Interrupts • 6-57                |                                                     | 65   |

|     | 6.5.4                  |                                                                                                                                                                                 | XMI to VAXBI IDENT • 6-58                        |                                                     | 03   |

|     |                        |                                                                                                                                                                                 | XMI to VAXBI IDENT (DWMBA Interrupt P            | ending) • 6-                                        | 58   |

| 6.6 | ERROR                  | REPORTI                                                                                                                                                                         | ING                                              | an dia ang sa panangan ang sa                       | 65   |

|     | 6.6.1                  | VAXBI E                                                                                                                                                                         | rrors                                            |                                                     | 6-5  |

|     | 6.6.2                  | DWMBA                                                                                                                                                                           | Errors                                           |                                                     | 6-5  |

|     | 6.6.3                  | DWMBA                                                                                                                                                                           | XMI-to-VAXBI Adapter Error Response Ma           | itrix                                               | 6-6  |

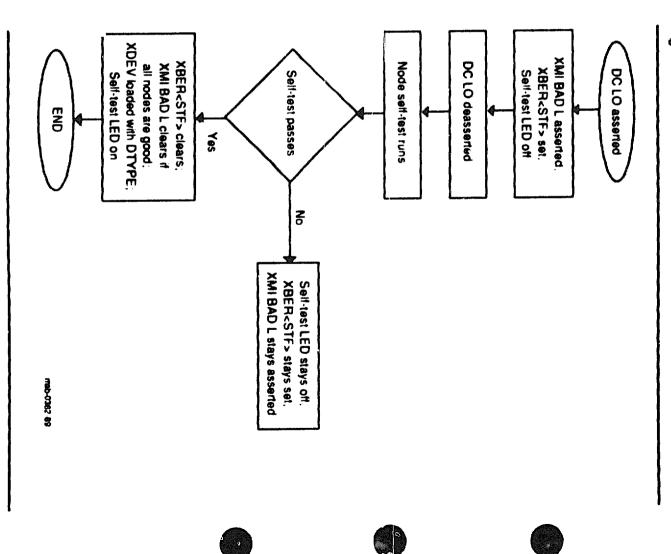

| 6.7 | DWMB                   |                                                                                                                                                                                 | ZATION, SELF-TEST, AND BOOTING                   | ay kana ga Kaling Atta ng Kaling Shing Atta. Iyo ka | 6-6  |

|     | 6.7.1                  | DWMBA                                                                                                                                                                           | Initialization                                   |                                                     | 66   |

|     | 6.7.2                  | DWMBA                                                                                                                                                                           | Self-Test and Diagnostics                        |                                                     | 66   |

|     |                        | 6.7.2.1                                                                                                                                                                         | Loopback • 6-68                                  |                                                     |      |

|     |                        | ~ 7 ~ ~                                                                                                                                                                         | Self-Test • 6-68                                 |                                                     |      |

## CHAPTER 7 POWER AND COOLING SYSTEMS

| 7.1 | POWER | SYSTEM    |                                        |  |

|-----|-------|-----------|----------------------------------------|--|

|     | 7.1.1 | Input Pov | ver                                    |  |

|     | 7.1.2 | H7206 Po  | wer and Logic Unit                     |  |

|     | 7.1.3 | H7214 Po  | wer Regulator                          |  |

|     | 7.1.4 | H7215 Pa  | wer Regulator                          |  |

|     | 7.1.5 | XTC Pow   | er Sequencer                           |  |

|     |       | 7.1.5.1   | XMI Resol Timing Control Logic • 7–3   |  |

|     |       | 7.1.5.2   | TOY Circuits • 7–3                     |  |

|     |       | 7.1.5.3   | Console Line Driver and Receiver • 7-3 |  |

|     | 7.1.6 | Power Sy  | vstem Signals                          |  |

7-1

7-5

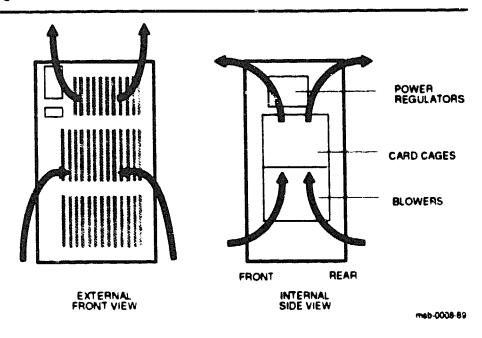

7.2 COOLING SYSTEM

#### APPENDIX A CONSOLE ENTRY POINTS A-1 RESET · POWER-UP CONSOLE ENTRY · ENTRY 0 A.1 A-1 A.2 PROMEXEC - EXEC NEW PROGRAM - ENTRY 1 A-1 A.3 EXIT - REENTER CONSOLE - ENTRY 2 A-1 A.4 A--1 REINIT CONSOLE - REINITIALIZE THE CONSOLE - ENTRY 3 A.5 CONDITIONAL\_BOOT - INVOKE POWER-UP ACTION - ENTRY 4 A-2 REBOOT - REBOOT THE SYSTEM - ENTRY 5 A-2 A.6 A.7 OPEN - OPEN A FILE - ENTRY 6 A-2 A.7.1 filename \_\_\_\_\_ A-2 A.7.2 flags \_\_\_\_\_ A-3 A.8 READ - READ FROM A FILE - ENTRY 7 A-3 A.9 WRITE - WRITE TO A FILE - ENTRY 8 A-3

Æ

٠

| A.10         | IOCTL - DEVICE-SPECIFIC I/O OPERATION - ENTRY 9               | A-4         |

|--------------|---------------------------------------------------------------|-------------|

| A.11         | CLOSE - CLOSE AN OPEN FILE - ENTRY 10                         | A-4         |

| A.12         | LSEEK - POSITION WITHIN A FILE - ENTRY 11                     | A-4         |

| A.13         | GETCHAR - INPUT A SINGLE CHARACTER - ENTRY 12                 | A-4         |

| A.14         | PUTCHAR - OUTPUT A SINGLE CHARACTER - ENTRY 13                | A-5         |

| <b>A</b> .15 | SHOWCHAR - OUTPUT A SINGLE CHARACTER - ENTRY 14               | A-5         |

| <b>A</b> .16 | GETS - GET LINE OF INPUT - ENTRY 15                           | A-5         |

| A.17         | PUTS - DISPLAY A LINE OF OUTPUT - ENTRY 16                    | A-5         |

| A.18         | PRINTF - PRINT FORMATTED VALUES - ENTRY 17                    | A-6         |

| A.19         | FLUSH_CACHE - FLUSH PROCESSOR CACHE - ENTRY 28                | A6          |

| A.20         | CLEAR_CACHE - CLEAR PART OF THE PROCESSOR CACHE -<br>ENTRY 29 | A-6         |

| A.21         | SET MP - SAVE PROGRAM CONTEXT - ENTRY 30                      | A-6         |

| A.22         | LONGJMP - RESTORE PROGRAM CONTEXT - ENTRY 31                  | <b>A</b> -7 |

| A.23         | UTLBMISS_EXCEPT · CONSOLE UTLB MISS VECTOR · ENTRY 32         | A-7         |

| A.24         | GETENV - GET VALUE OF AN ENVIRONMENT VARIABLE - ENTRY<br>33   | <b>A</b> -7 |

| A.25         | SETENV - SET VALUE OF AN ENVIRONMENT VARIABLE - ENTRY<br>34   | <b>A</b> -7 |

xiii

| A.26        | ATOB - CONVERT ASCII TO BINARY - ENTRY 35                       | A-7          |

|-------------|-----------------------------------------------------------------|--------------|

| A.27        | STRCMP - COMPARE TWO STRINGS - ENTRY 36                         | 88           |

| A.28        | STRLEN - FIND STRING LENGTH - ENTRY 37                          | 8-A          |

| A.29        | STRCPY - COPY A STRING - ENTRY 38                               | A-8          |

| A.37        | STRCAT - CONCATENATE TWO STRINGS - ENTRY 39                     | A-8          |

| A.31        | PARSE - PARSE A SIMPLE COMMAND - ENTRY 40                       | A-9          |

| A.32        | PARSE_RANGE - PARSE AN ADDRESS RANGE - ENTRY 41                 | A-9          |

| <u>A 33</u> | ARGVIZE - PARSE STRING INTO TOKENS - ENTRY 42                   | A-9          |

| A.::4       | HELP - PRINT HELP FROM A COMMAND TABLE - ENTRY 43               | A-10         |

| A.35        | DUMPCMD - INVOKE CONSOLE DUMP COMMAND - ENTRY 44                | A-10         |

| A.36        | SETENVCMD - INVOKE CONSOLE SETENV COMMAND - ENTRY 45            | A-10         |

| A.37        | UNSETENVCMD - INVOKE CONSOLE SETENV COMMAND - ENTRY<br>46       | <b>A</b> -11 |

| A.38        | PRINTENVCMD - INVOKE CONSOLE PRINTENV COMMAND -<br>ENTRY 47     | <b>A</b> -11 |

| A.39        | GENERAL_EXCEPT - CONSOLE GENERAL EXCEPTION VECTOR -<br>ENTRY 48 | <b>A</b> -11 |

| A.40        | CLEAR_NOFAULT - CLEAR CONSOLE FAULT HANDLERS - ENTRY<br>51      | <b>A</b> -11 |

| A.41        | NOT_IMPLEMENTED - UNIMPLEMENTED FUNCTION - ENTRY 52             | <b>A</b> -11 |

| AND IN THE R |  |

|--------------|--|

|              |  |

| A.42 | HALT_INTERRUPT · SERVICE HALT INTERRUPT - ENTRY 54                            | A-12                 |

|------|-------------------------------------------------------------------------------|----------------------|

| A.43 | ENTER_MAINTMODE - ENTER MAINTENANCE MODE - ENTRY 96                           | A-12                 |

| A.44 | START_MAINT - START CODE ON THE MAINTENANCE<br>PROCESSOR - ENTRY 97           | <b>A</b> -12         |

| A.45 | PROM DEVICE DRIVERS                                                           | <b>A-1</b> 3         |

|      |                                                                               |                      |

|      | A.45.1 bootp - BOOTP protocol Ethernet driver                                 | A-13                 |

|      | A.45.1 bootp - BOOTP protocol Ethernet driver<br>A.45.2 ra - MSCP disk driver |                      |

|      |                                                                               | A-13<br>A-13<br>A-13 |

|      | A.45.2 ra - MSCP disk driver                                                  | A-13                 |

## INDEX

| EXAMPLES |                             |      |

|----------|-----------------------------|------|

| 3-1      | Flushing Second-Level Cache | 3-14 |

| 4-1      | I/O Mapping                 | 4-29 |

| FIG | UR | ES |

|-----|----|----|

|-----|----|----|

| 1-1  | DECsystem 5807 System Architecture            |  |

|------|-----------------------------------------------|--|

| 1-2  | Typical DECsystem 5800 System                 |  |

| 1–3  | DECsystem 5800 (Front View)                   |  |

| 1-4  | DECsystem 5800 System (Rear View)             |  |

| 1-5  | VAXBI Adapters                                |  |

| 1-6  | DECsystem 5800's XMI                          |  |

| 1–7  | DECsystem 5800's VAXBI                        |  |

| 18   | VAXBI Expander Cabinet                        |  |

| 1-9  | TK70 Tape Drive                               |  |

| 1–10 | Console and Terminal Connectors               |  |

| 1-11 | Power System (Rear View)                      |  |

| 1-12 | Airliow Pattern                               |  |

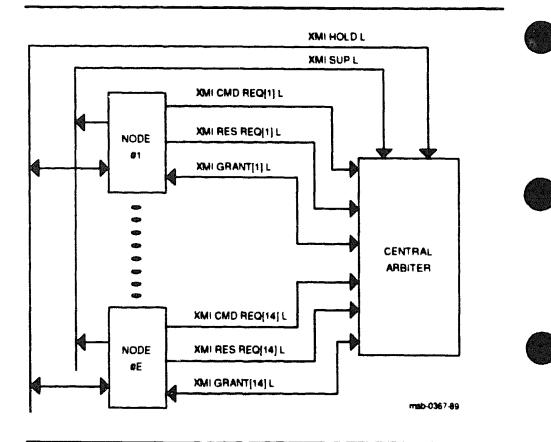

| 2-1  | XMI System Block Diagram                      |  |

| 2-2  | XMI Node Block Diagram Showing the XMI Corner |  |

| 2-3  | XMI Memory and I/O Address Space              |  |

| 2-4  | XMI I/O Space Address Allocation              |  |

| 2-5  | XMI Arbitration Block Diagram                 |  |

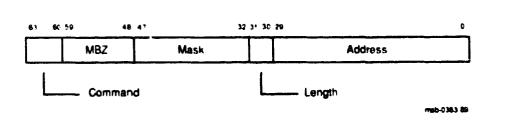

| 2-6  | Data Transaction Command Cycle Format         |  |

|      |                                               |  |

| Co | nte | nts |

|----|-----|-----|

|----|-----|-----|

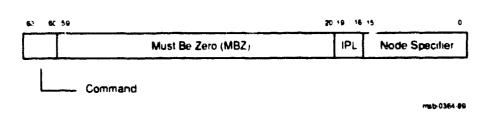

| 2-7  | Interrupt Transaction Command Cycle Format                   | 2-19  |

|------|--------------------------------------------------------------|-------|

| 28   | Mask Field Bit Assignments                                   | 2-21  |

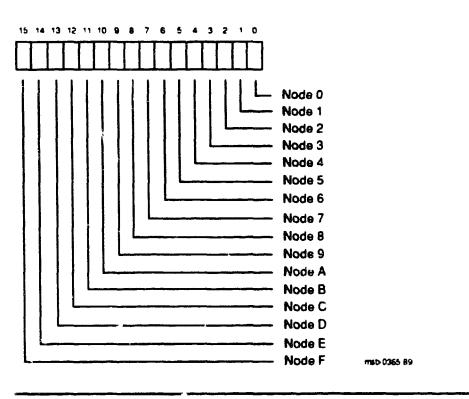

| 2-9  | Node Specifier Field                                         | 2-24  |

| 2-10 | Read Transaction                                             | 2-32  |

| 2-11 | Interlock Read Transaction to a Locked Location              | 2-33  |

| 2-12 | Multiple Data Cycle Reads Command Cycle                      | 2-34  |

| 2-13 | Read Data Cycles                                             | 2-34  |

| 2-14 | Read Data Cycles with HOLD                                   | 235   |

| 2-15 | Hexword Read with Single Correctable Read Error              |       |

| 2-16 | Hexword Data Return with Uncorrectable Read Error            |       |

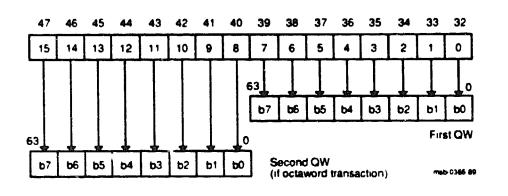

| 2-17 | Longword and Quadword Writes                                 | 237   |

| 2-18 | Multiple Date Cycle Writes                                   | 2-37  |

| 2-19 | XMI Initialization Flowchart                                 |       |

| 2-20 | Falled Octaword Write Transaction                            |       |

| 3-1  | KN58A/A Interface Module Block Diagram                       |       |

| 3-2  | Private I/O Address Space Map                                |       |

| 3-3  | Second-Level Cache Block Diagram                             |       |

| 3-4  | Cache Address Line Contents During a Cache Read              |       |

| 3-5  | Cache Address Line Contents During a Second-Level Cache Fili |       |

| 3-6  | Second-Level Cache Addressing                                |       |

| 3-7  | XMI Corner-to-KN58A/A Interface                              |       |

| 3-8  | XCPGA Block Diagram                                          |       |

| 3-9  | Interprocessor IVINTR Generation Address Example             |       |

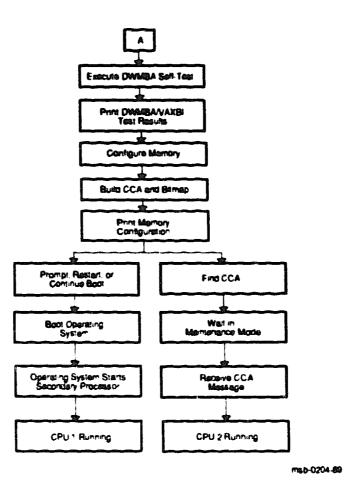

| 3-10 | Initialization Flowchart                                     | 3-96  |

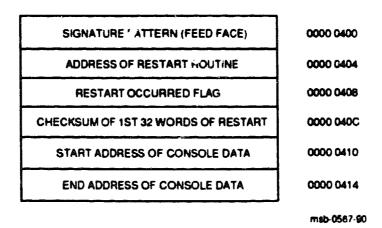

| 3-11 | Restart Parameter Block Format                               | 3-106 |

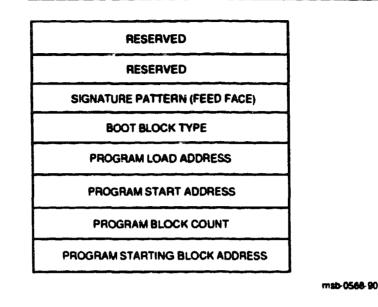

| 3-12 | Bootblock Format                                             |       |

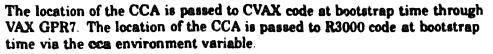

| 3-13 | CCA Layout, Part 1                                           |       |

| 3-14 | CCA Layout, Part 2                                           |       |

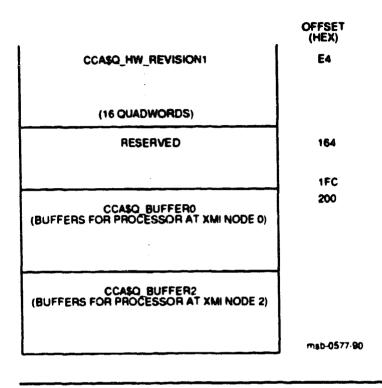

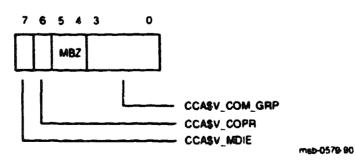

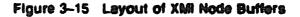

| 3-15 | Layout of XMI Node Buffers                                   |       |

| 4-1  | KN58A/B CPU Module Block Diagram                             |       |

| 4-2  | R3000 Registers                                              |       |

| 4-3  | Instruction Formats                                          |       |

| 4-4  | Virtual Memory for Kernel and User Modes                     |       |

| 4-5  | R3000 Memory Mapping                                         |       |

| 46   | FPA General-Purpose Registers                                |       |

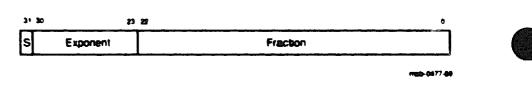

| 4-7  | Single-Precision Floating-Point Format                       |       |

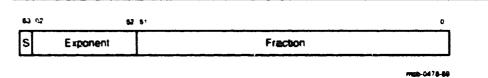

| 4-8  | Double-Precision Floating-Point Format                       |       |

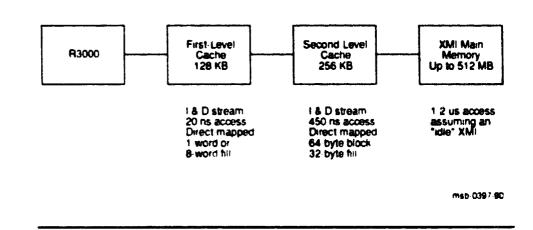

| 4_9  | Cache Organization                                           |       |

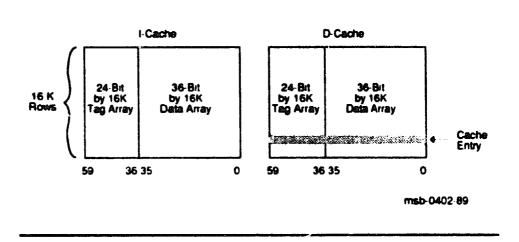

| 4-10 | First-Level Cache Organization                               |       |

| 4-11 | Cache Entry                                                  |       |

| 4-12 | Cache Address Translation                                    |       |

| 6-1  | DWMBA XMI-to-VAXBI Adapter Block Diagram                     |       |

| 6-2  | XMI Bus Vector Format                                        |       |

| 6-3  | UNIBUS Vector Format                                         |       |

| 6-4  | VAXBI Node Bus Vector Format                                 |       |

| 6-2            | VAXBI-to-XMI Command Translations                          | 6-8  |

|----------------|------------------------------------------------------------|------|

| 6-3            | XMI Registers on the DWMBA/A Module                        | 611  |

| 6-4            | XMI Registers on the DWMBA/B Module                        | 6-12 |

| 65             | VAXBI Registers                                            | 6-13 |

| <del>6</del> 6 | DWMBA Adapter Interrupt Levels and Vectors                 | 6-66 |

| 6–7            | XMI Errors During DMA Transactions (VAXBI to XMI Memory)   | 660  |

| 68             | XMI Errors During CPU I/O Transactions (XMI to VAXBI)      | 6-61 |

| 6-9            | DWMBA Errors During DMA Transactions (VAXBI to XMI Memory) | 6-62 |

| 6-10           | DWMBA Errors During CPU I/O Transactions (XMI to VAXBI)    | 6-63 |

| 6-11           | VAXBI Errors During DMA Transactions (VAXBI to XMI Memory) | 6-64 |

| 6-12           | VAXBI Errors During CPU I/O Transactions (XMI TO VAXBI)    | 6-65 |

| 7-1            | Power System Signals                                       | 7-4  |

## Preface

## **Intended Audience**

This manual is written for Digital customer service engineers installing and repairing in the field and for OEMs who are writing specialized applications, such as their own operating systems.

## **Document Structure**

This manual has seven chapters.

- Chapter 1 gives you a basic introduction to the DECsystem 5800 system and its parts.

- Chapter 2 tells you about the XMI bus and protocol.

- Chapter 3 explains the KN58A/A interface module, and Chapter 4 explains the KN58A/B CPU module, the two modules that comprise a DECsystem 5800 processor.

- Chapter 5 explains the MS62A memory module.

- Chapter 6 tells you about the DWMBA and its DWMBA/A module and DWMBA/B module.

- **Chapter 7** explains the components of the power system and the cooling system.

- The Index provides additional reference support.

## **Associated Documents**

Other documents in the DECsystem 5800 documentation set include:

| Title                                                                | Order Number |  |

|----------------------------------------------------------------------|--------------|--|

| DECsystem 5800 Installation Guide                                    | 2K-580AA-IN  |  |

| DECsystem 5800 Owner's Manual                                        | EK-580AA-OM  |  |

| DECsystem 5800 Options and Me. Construct                             | EK-580AA-MG  |  |

| You may also find the following docume                               | nts useful:  |  |

| Title                                                                | Order Number |  |

| CIBCA User Guide                                                     | EK-CIBCA-UG  |  |

| DEBNI Installation Guide                                             | EK-DEBNI-IN  |  |

| Guide to Ethernet Communication Services                             | AA-NL22A-TE  |  |

| Guide to Languages and Programming for<br>RISC Processors            | AA-ML94A-TE  |  |

| Guide to Networking for RISC Processors                              | AA-ML88A-TE  |  |

| Guide to System Environment Setup                                    | AA-NL18A-TE  |  |

| H4000 DIGITAL Ethernet Transceiver<br>Installation Manual            | EK-H4000-IN  |  |

| H9657-EU Installation Guide                                          | EK-VBIEU-IN  |  |

| HSC Installation Manual                                              | EK-HSCMN-IN  |  |

| Introduction to System and Network<br>Management for RISC Processors | AA-ML80A-TE  |  |

| KDB50 Disk Controller User's Guide                                   | EK-KDB50-UG  |  |

| RA82 Disk Drive User's Guide                                         | EK-ORA82-UG  |  |

| RA90 Disk Drive User's Guide                                         | EK-ORA90-UG  |  |

| SA70 Enclosure User Guide                                            | EK-SA70E-UG  |  |

| SC008 Star Coupler User's Guide                                      | EK-SC008-UG  |  |

| Technical Summary for RISC Processors                                | AA-MM35A-TE  |  |

| TK70 Streaming Tape Drive Owner's Manual                             | EK-OTK70-OM  |  |

| TU81/TA81 and TU81 PLUS Subsystem<br>User's Guide                    | EK-TUA81-UG  |  |

| VAXBI Options Handbook                                               | EB-32255-46  |  |

| VAX Diagnostic Architecture Reference<br>Manual                      | EY-3459E-DP  |  |

| VAX Diagnostic Supervisor User's Guide                               | AA-FK66A-TE  |  |

| VAX Systems/DECsystems Systems and<br>Options Catalog                | EC-10413-46  |  |

XXXXXXXXXXXXXXXXXXX XXXXXXXXXXX XXXXXXXXX XXXXXXX XXXXX XXX х

> Х XXX XXXXX XXXXXXX XXXXXXXXX XXXXXXXXXXXX XXXXXXXXXXXXXX XXXXXXXXXXXXXXXXXXX \*\*\*\*\*

# The DECsystem 5800 System Overview

4

This chapter describes the system packages and system components and notes the location of components in the cabinet.

This chapter includes the following section:

- DECsystem 5800 Introduction

- DECsystem 5800 Configurations

- DECsystem 5800 System Architecture

- Typical System

- DECsystem 5800 (Front View)

- DECsystem 5800 (Rear View)

- Supported VAXBI Adapters and Options

- XMI Backplane and Card Cage

- VAXBI Backplane and Card Cage

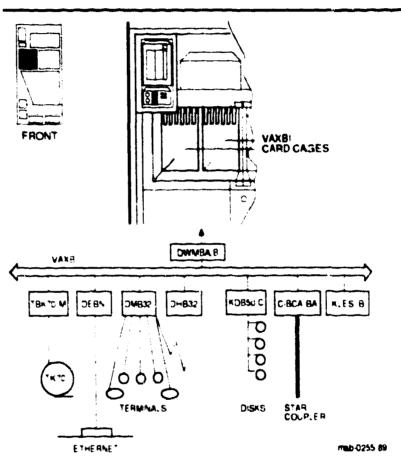

- VAXBI Expander Cabinet

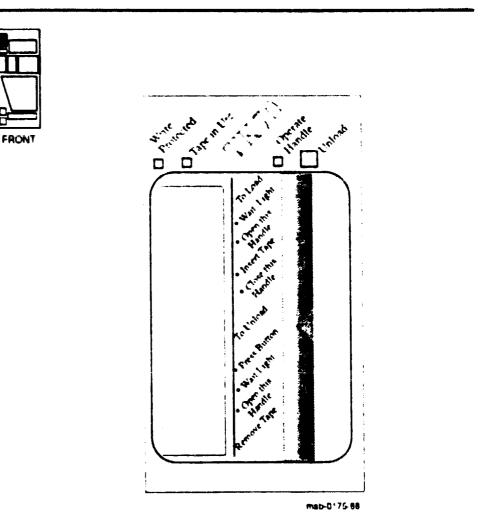

- TK70 Tape Drive

- I/O Connections

- Power System

- Cooling System

## 1.1 DECsystem 5800 Introduction

The DECsystem 5800, a general purpose computer system based on a reduced instruction set computer (RISC) CPU, is designed for growth and can be configured for many different applications. The DECsystem 5800 can support many users in a time-sharing environment.

The DECsystem 5800 does the following:

- Supports a full set of ULTRIX-32 applications

- Functions as a stand alone system or as the node of a network

- Allows for expansion of processors, memory, and LO

- Implements multiprocessing where all processors have equal access to memory

- Uses the VAXBI bus as the I/O interconnect

- Uses a high-bandwidth internal system bus (XMI) designed for multiprocessing

- Interleaves memory bank accesses in a user definable sequence

- Performs automatic self-test on power-up, reset, reboot, or system initialization

## 1.2 DECsystem 5800 Configurations

#### The DECsystem 5800 system family has configuration packages that differ in the number of processors and amount of memory.

Refer to the VAX Systems / DECsystems Systems and Options Catalog for the available configurations.

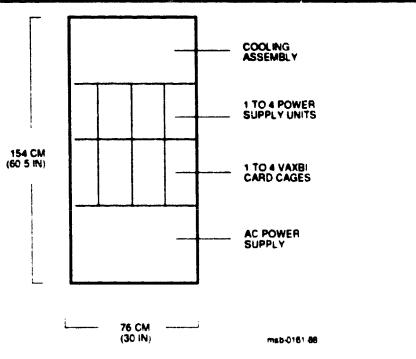

Each configuration has a 60-inch system cabinet that includes one 14-slot high-bandwidth internal system bus backplane (XMI) and one 12-slot VAXBI backplane.

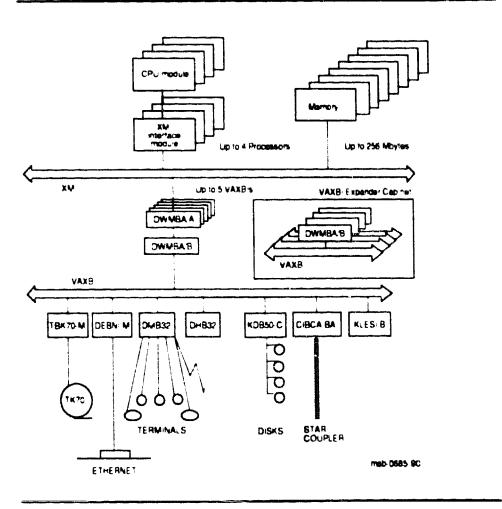

## 1.3 DECsystem 5800 System Architecture

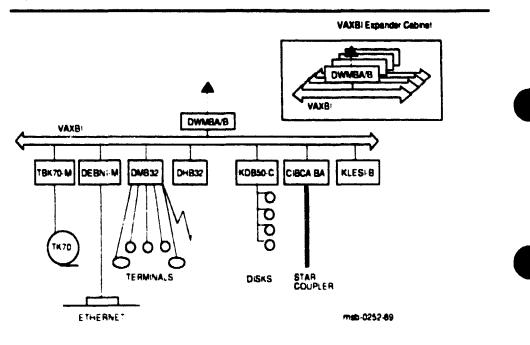

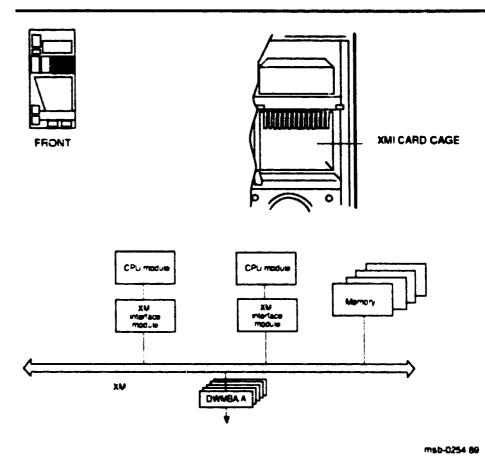

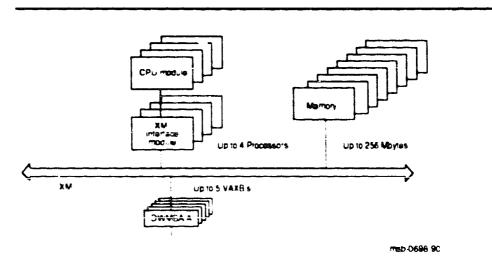

The DECsystem 5800 system supports multiprocessing with up to four KN58A processors. The system uses a high-speed system bus called the XMI bus to interconnect its KN58A processors and its MS62A memory modules. All I/O devices connect to the VAXBI bus.

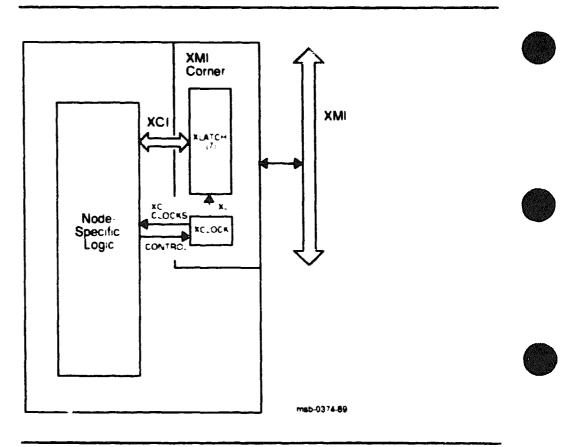

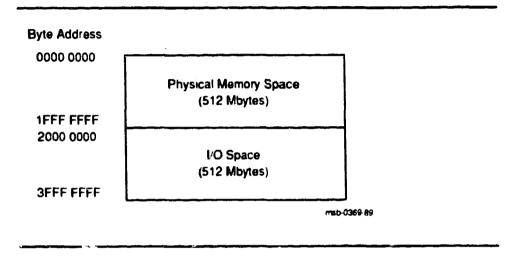

The XMI bus is the DECsystem 5800 system bus; the VAXBI bus supports the I/O subsystem. The XMI bus is a 64-bit system bus<sup>1</sup> that interconnects the central processors, memory modules, and VAXBI I/O adapters.

The VAXBI and XMI buses share similar but incompatible connector and module architecture. Both the VAXBI and XMI buses use the concept of a node. A node is a single functional unit that consists of one or more modules.

The XMI bus has three types of nodes: processor nodes (KN58A), memory nodes (MS62A memory modules), and the XMI-to-VAXBI L/O adapters (DWMBA).

A processor node, called a KN58A, is a two-board set. It consists of a KN58A/A interface module and a KN58A/B CPU module. The KN58A/B CPU module is the processor's computational engine and contains a MIPS<sup>2</sup> R3000 CPU chip, an R3010 floating-point chip, R3020 the buffers, and primary cache. The KN58A/A interface module provides the buffers, and primary cache. The KN58A/A interface module provides the means by which the KN58A/B CPU module accesses the XMI bus and contains a CVAX chip, a second-level cache, a system support chip ( $\gtrsim$  3C), and XMI interface logic. The module also participates in the system self-test.

Processors communicate with main memory over the XMI bus. The system supports multiprocessing with up to four processors. One processor is designated as the boot processor according to its physical location in the card cage and that processor handles all system communication. The other processors (if any) are called secondary processors. The processor node number corresponds to the number of the XMI slot holding the KN58A/A interface module.

A memory node is an MS62A memory module. Memory is a global resource equally accessible by all processors on the XMI bus. Each MS62A memory module has 32 Mbytes of memory, consisting of MOS 1-Mbit dynamic RAMs, ECC logic, and control logic. The system supports up to eight MS62A memory modules (256 Mbytes of memory). The memories are interleaved by the console on power-up. The default can be changed by console command.

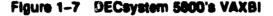

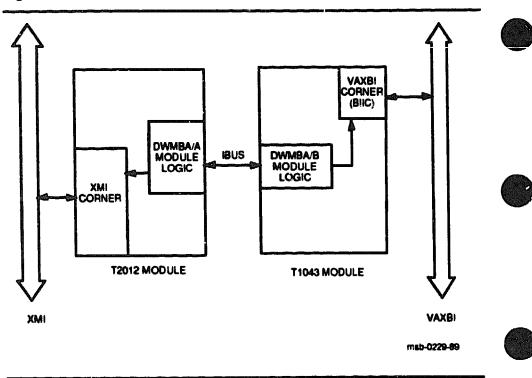

An XMI-to-VAXBI adapter, called a DWMBA, is a two-board adapter that transfers data between these two buses. The DWMBA/A module is installed on the XMI bus; it is cabled to the DWMBA/B module on the VAXBI bus. The system supports up to five VAXBI buses. Every VAXBI bus on this system must have a DWMBA adapter. Therefore, systems with two VAXBI channels have two DWMBA/A modules on the XMI bus, and each VAXBI channel has a DWMBA/B module. Systems with more than one VAXBI require a VAXBI expander cabinet. System error messages and self-test results refer to the pair of DWMBA modules as XBI.

<sup>&</sup>lt;sup>1</sup> The XMI bus has a 64-nanosecond bus cycle, with a maximum throughput of 100 Mbytes per second.

<sup>&</sup>lt;sup>2</sup> MIPS is a registered trademark of MIPSCO, Inc

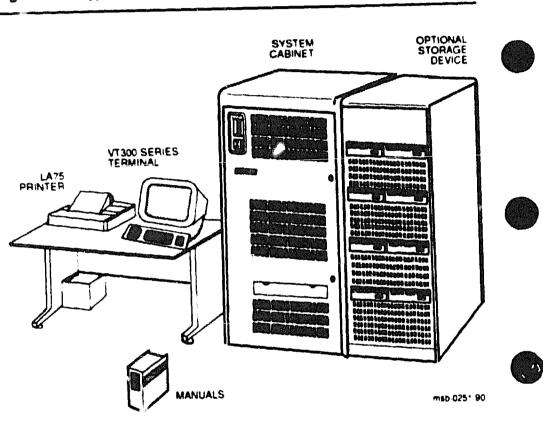

## 1.4 Typical System

A typical DECsystem 5800 system has a main cabinet with a TK70 type drive and optional RA disks, a console terminal and printer, an accessories kit, and a set of documentation. The system may have additional tape or disk drives.

Figure 1-2 Typical DECsystem 5800 System

Figure 1-2 shows a typical system.

- The main cabinet houses a TK70 tape drive, up to eight RA disks (optional), the XMI card cage (which contains the processors and memories), VAXBI card cages, the control panel awitches, status indicators, and restart controls.

- The TK70 tape drive in the main cabinet is used for installing operating systems, software, and some diagnostics.

- The optional RA disk drive(s) in the main cabinet are used for installing operating systems and software and are used for local storage and archiving.

- The optional disk drive cabinet provides additional local storage and archiving.

- The console terminal is used for console and system management operations.

- DECsystem 5800 hardware information kit that ships with the system includes:

- DECsystem 5800 Installation Guide

- DECsystem 5800 Ouner's Manual

- DECsystem 5800 Console Patch TK50 (tape)

- DECsystem 5800 Console TK50 (tape)

See the Preface for a complete list of system documentation and associated documents.

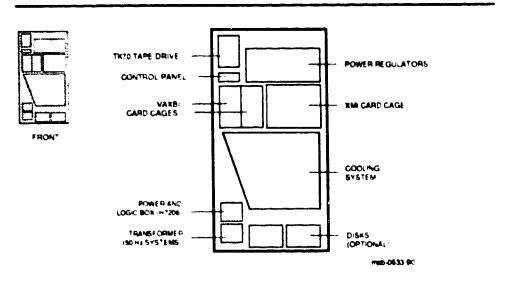

## 1.5 DECsystem 5800 (Front View)

The TK70 tape drive and control panel are on the front of the system cabinet, accessible with the doors closed. With the front door open, Digital customer service engineers can access the VAXBI and XMI card cages, the cooling system, the RA disk(s), if present, and power regulators.

Figure 1-3 DECsystem 5800 (Front View)

These components are visible from the inside front of the cabinet (see Figure 1-3 for their location):

- TK70 tape drive

- Control panel

- Power regulators

- Two VAXBI card cages hardwired together to form a single VAXBI channel. Only one VAXBI is permitted in the main cabinet. Additional VAXBIs require an expander cabinet.

- XMI card cage

- Cooling system (one of the two blowers is visible)

- Transformer (on 50 Hz systems only)

- Power and logic box (H7206)

- RA disks (if installed)

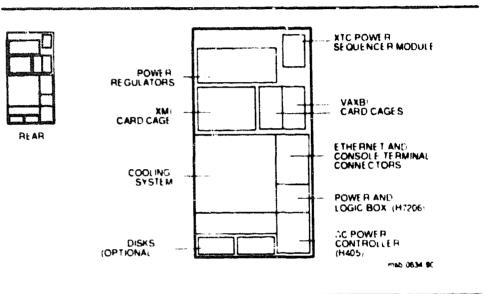

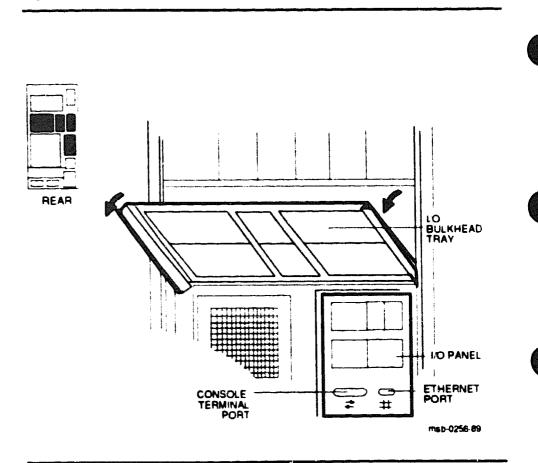

## 1.6 DECsystem 5800 (Rear View)

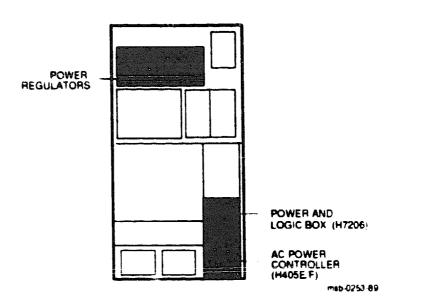

With the rear door open, Digital customer service engineers can access the power regulators; power sequencer module (XTC); cooling system; power and logic box; RA disk(s), if present; AC power controller; Ethernet and console terminal connectors; and the I/O bulkhead space.

Figure 1-4 DECsystem 5800 System (Rear View)

These components are visible from the rear of the cabinet (see Figure 1-4):

- Five field-replaceable power regulators

- Power sequencer module (XTC) located on the back of the TK70 tape drive and control panel unit

- I/O bulkhead space The panel covering the XMI and VAXBI areas is the I/O bulkhead panel and provides space for additional I/O connections.

- Cooling system, with open grid over a blower

- VAXBI and XMI adapter bulkhead cables

- Ethernet and console terminal connectors

- Power and logic box (H7206)

- RA disk(s) (if installed)

- AC power controller (H405)

The system supports the use of the following VAXBI adapters: CIBCA, DEBNI, DHB32, DMB33, KDB50, TBK70, TU81E, and DWMBA.

See the VAX Systems/DECsystems Systems and Options Catalog for a complete list of VAXBI adapters available for the DECsystem 5800 and the VAXBI Options Handbook for detailed information on each VAXBI adapter.

# 1.8 XMI Backplane and Card Cage

The XMI high-speed system bus interconnects processors and memory modules. It has a maximum bandwidth of 100 Mbytes per second and supports up to four processors. The 14-slot XMI card cage houses XMI-to-VAXBI adapters, processors, and memories.

The XMI is a limited-length, pended synchronous bus with centralized arbitration. The XMI bus can process several transactions simultaneously, making efficient use of the bus bandwidth. The bus includes the XMI backplane, the electrical environment of the bus, the protocol that nodes use on the bus, and the logic to implement this protocol.

The XMI backplane and 14-slot (nodes 1 through E) card cage are located in the upper third of the cabinet on the right side, as viewed from the front of the cabinet. A clear latched door protects the components housed in the XMI card cage and helps to direct the airflow over the modules. Indicator lights on the XMI modules can be viewed through this clear front door.

Each slot of the XMI card cage is hardwired to a 4-bit node ID code that corresponds to the physical slot number in the card cage. The node ID number of the module is its slot position. The nodes are numbered 1 through E (hex) from right to left, as you view the card cage from the front of the cabinet.

For information on installing modules in the XMI card cage, see the *DECsystem 5800 Options and Maintenance* manual. For in-depth technical information, see the appropriate chapter of this manual.

| Slot | Node | Permissible Modules'       |

|------|------|----------------------------|

| 1    | 1    | KN58A/A, I/O, Mem          |

| 2    | 2    | KN59A/A, KN58A/B, I/O, Mem |

| 3    | 3    | KN58A/A, KN58A/B, I/O, Mem |

| 4    | 4    | KN58A/A, KN58A/B, I/O, Mem |

| 5    | 5    | KN58A/B, Mem               |

| 6    | 6    | Mem                        |

| 7    | 7    | Mem                        |

| 8    | 8    | Mem                        |

| 9    | 9    | Mem                        |

| 10   | A    | KN58A/A, Mem               |

| 11   | B    | KN58A/B, I/O, Mem          |

| 12   | С    | KN58A/A, I/O, Mem          |

| 13   | D    | KN58A/B, I/O, Mem          |

| 14   | E    | I/O, Mem                   |

Table 1-1 XMI Slots

'Key to permissible modules:

KN56A/A = Interface Friedule KN56A/B = CPU Module Mem = MS62A Memory Module I/O = DWMBA

1-12

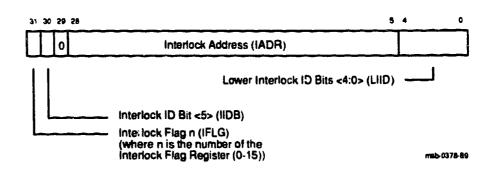

## 1.9 VAXBI Backplane and Card Cage