# KS10-BASED DECSYSTEM-2020 TECHNICAL MANUAL

digital equipment corporation • marlboro, massachusetts

Copyright © 1978, 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

|         | VMS              | IAS     |

### **CONTENTS**

|           |                                                   | Page                  |

|-----------|---------------------------------------------------|-----------------------|

| PREFACE   |                                                   |                       |

| CHAPTER 1 | OVERVIEW                                          |                       |

| 1.1       | INTRODUCTION                                      | 1-1                   |

| 1.2       | SYSTEM HARDWARE                                   | 1-2                   |

| 1.3       | K S10 PHYSICAL DESCRIPTION                        | 1-6                   |

| 1.3.1     | KS10-PA Card Cage                                 | 1-6                   |

| 1.3.2     | BA11-K Unibus Option Drawer                       | 1-6                   |

| 1.3.3     | Power System                                      | 1-11                  |

| 1.3.4     | Masshus Transition Plate                          |                       |

| 1.3.5     | Asynchronous Terminal Distribution Panel (H317-E) | 1-11                  |

| 1.3.6     | Operator's Switch Panel                           | 1-13                  |

| 1.4       | DNHXX PHYSICAL DESCRIPTION                        | 1-13                  |

| CHAPTER 2 | SITE PREPARATION AND PLANNING                     |                       |

| 2.1       | SITE PLANNING                                     | 2-1                   |

| 2.2       | ENVIRONMENTAL REQUIREMENTS                        | 2-1                   |

| 2.3       | SYSTEM CABLING                                    | 2-2                   |

| 2.4       | PRIMARY POWER (AC)                                | 2-6                   |

| 2.5       | OPTION DATA SHEETS                                | 2-6                   |

| CHAPTER 3 | INSTALLATION                                      |                       |

| CHAPTER 4 | OPERATION/PROGRAMMING                             |                       |

| 4.1       | CONTROLS AND INDICATORS                           | 4-1                   |

| 4.2       | INSTRUCTION SET                                   | 4-3                   |

| 4.3       | NIIMRER SYSTEM                                    | , , , , , , , , , 4-8 |

| 4.4       | FFFFCTIVE ADDRESS CALCULATION                     | 4-ბ                   |

| 4.5       | MACHINE MODES                                     | 4-14                  |

| 4.6       | PROCESS TABLES                                    | 4-14                  |

| 4.7       | MEMORY ADDRESS MAPPING BY THE CPU                 | 4-1/                  |

| 4.8       | MEMORY ADDRESS MAPPING BY THE UBA                 | 4-19                  |

| 4.9       | GENERAL-PURPOSE REGISTER BLOCKS                   | 4-19                  |

| 4.10      | MEMORY SYSTEM                                     | 4-22                  |

| 4.11      | PRIORITY INTERRUPT SYSTEM                         | 4-22                  |

| 4.12      | KS10 PROCESSOR STATUS WORDS                       | 4-25                  |

| 4.13      | OPERATOR CONSOLE                                  | 4-32                  |

| 4.14      | REMOTE DIAGNOSIS (KLINIK) LINE                    | 4-42                  |

| CHAPTER 5 | TECHNICAL DESCRIPTION                             |                       |

| 5.1       | INTRODUCTION                                      | 5-1                   |

| 5.1.1     | Console                                           | 5-1                   |

| 5.1.2     | CPU                                               | 5-2                   |

| 5.1.3     | MOS Memory                                        | 5-5                   |

| 5.1.4     | Unibus Adapter                                    | 5-7                   |

# **CONTENTS** (Cont)

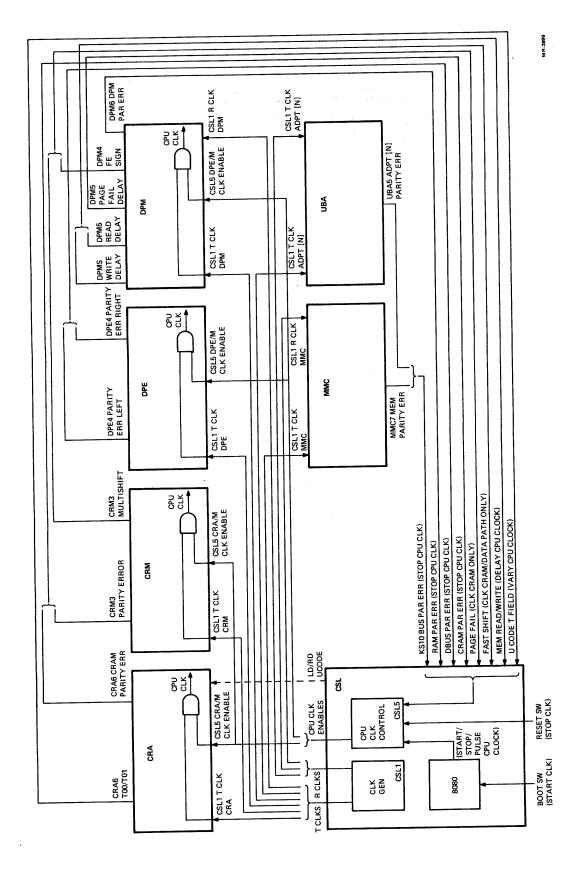

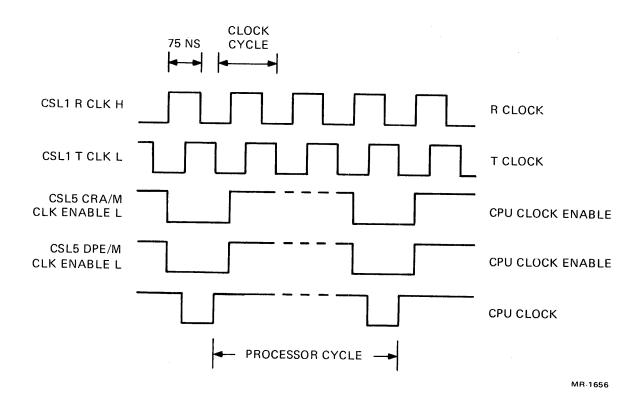

| 5.2               | SYSTEM TIMING                        | 5-8  |

|-------------------|--------------------------------------|------|

| 5.2.1             | Basic Clocks                         | 5-8  |

| 5.2.2             | CPU Clock Control                    | 5-10 |

| 5.3               | KS10 (BACKPLANE) BUS                 | 5-12 |

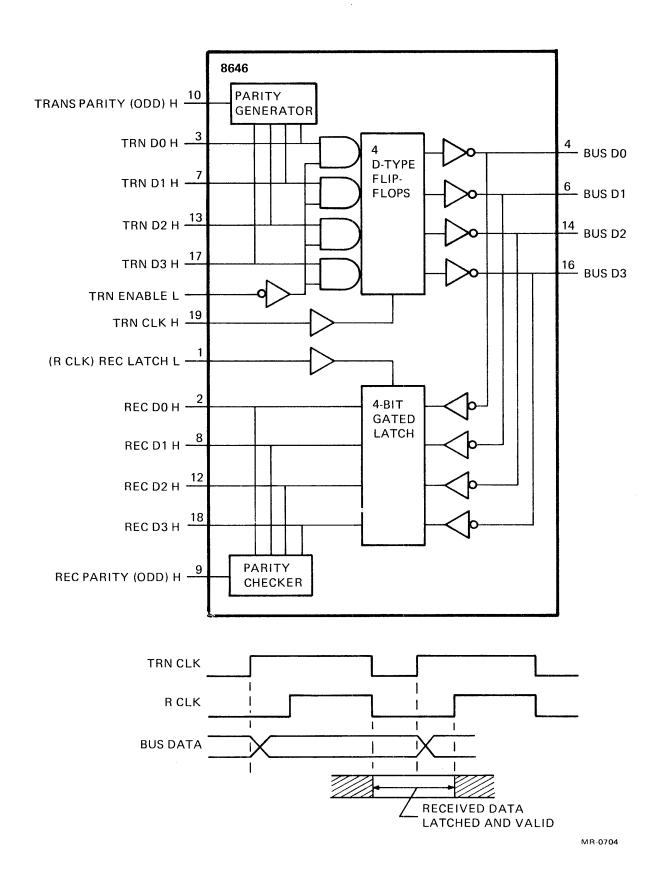

| 5.3.1             | 8646 Bus Transceiver                 | 5-14 |

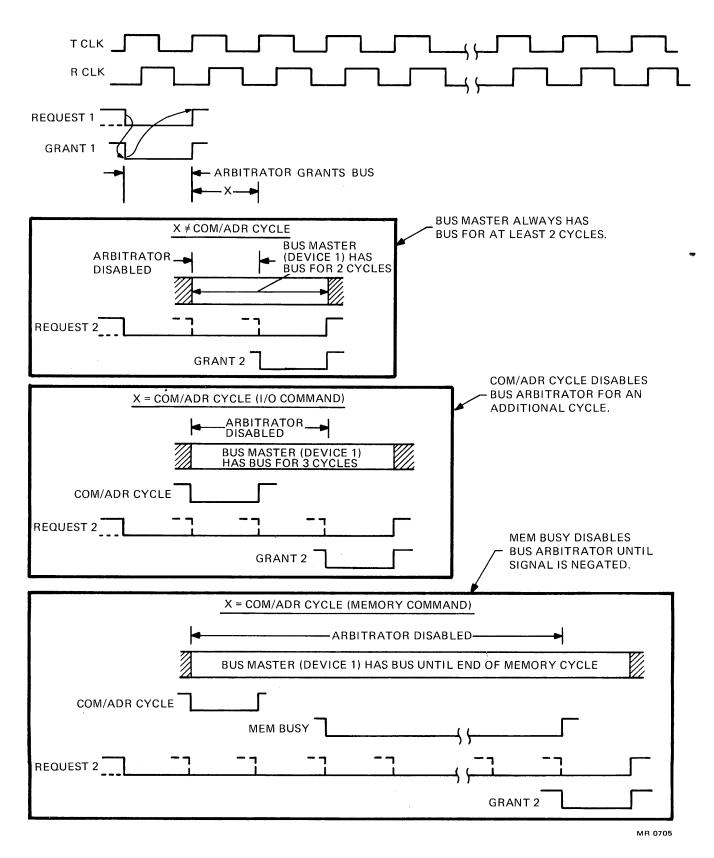

| 5.3.2             | Bus Arbitration                      | 5-17 |

| 5.3.3             | Bus Usage                            | 5-18 |

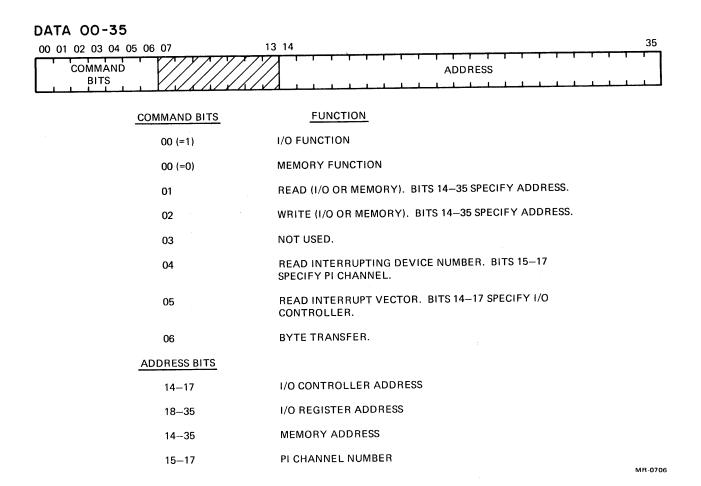

| 5.3.4             | Command/Address Cycle                | 5-20 |

| 5.3.5             | Bus Memory Operation                 | 5-23 |

| 5.3.6             | Bus I/O Operation                    | 5-26 |

| 5.3.7             | Bus PI Operation                     | 5-30 |

| 5.3.8             | Diagnostic Operations                | 5_37 |

| 5.3.9             | Bus Parity Error                     | 5 21 |

| 5.4               | MICROCONTROLLER                      | 5 24 |

| 5.4.1             | Microword                            | 5 24 |

| 5.4.2             | Dispatch Word                        | 5 20 |

| 5.4.3             | Control RAM                          | 5 40 |

| 5.4.4             | Skip and Dispatch Logic              |      |

| 5.4.4.1           | Dispatch ROM                         |      |

| 5.4.4.2           | Other Dispatch Procedures            | 5-41 |

| 5.4.5             | Subroutine Stack                     | 5-42 |

| 5.4.6             | Booting and Diagnosis                |      |

| 5.5               | DATA PATH EXECUTE                    |      |

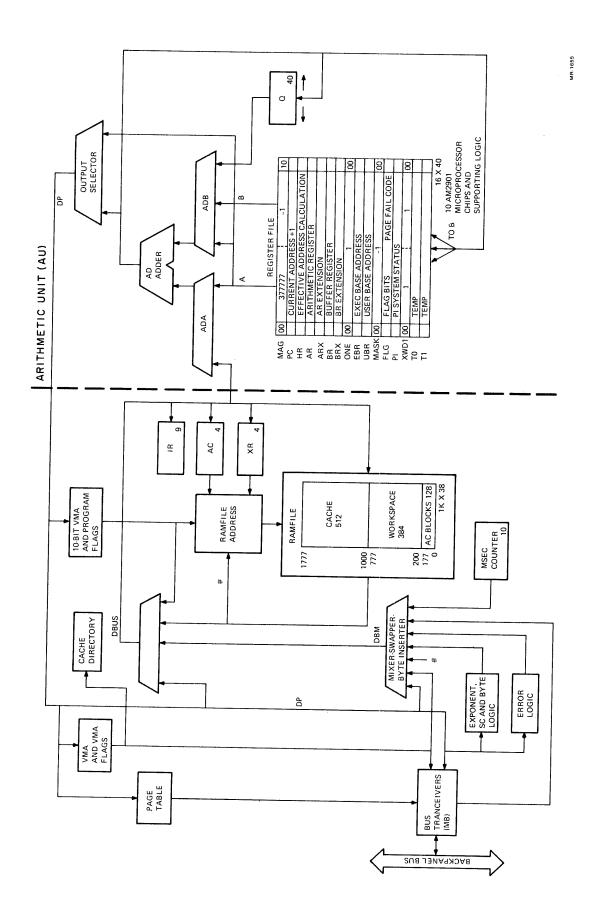

| 5.5.1             | Arithmetic Unit                      | 5-44 |

| 5.5.2             | Main Dath                            | 5-44 |

| 5.5.3             | Main Path                            | 5-45 |

| 5.5.4             | RAM File                             | 5-48 |

| 5.5.5             | Ten-Bit Logic                        | 5-48 |

| 5.6               | Program Flags                        | 5-49 |

| 5.6.1             | DATA PATH MEMORY                     | 5-49 |

| 5.6.2             | Memory and I/O Setup                 | 5-50 |

| 5.6.3             | Bus Operation                        | 5-54 |

| 5.6.4             | Paging                               | 5-54 |

| 5.6.5             | Cache                                | 5-55 |

| 5.6.6             | Error Logic                          | 5-56 |

| 5.7               | Priority Interrupt                   | 5-56 |

| 5.7.1             | MEMORY                               | 5-57 |

| 5.7.2 ·           | Storage Organization and Addressing  | 5-5/ |

| 5.7.3             | MOS Data Bus                         | 5-61 |

| 5.7.4             | Command/Address Load (Memory Access) | 5-62 |

| 5.7. <del>5</del> | Memory Write                         | 5-62 |

| 5.7.6             | Memory Read                          | 5-62 |

| 5.7.0<br>5.7.7    | Read-Pause-Write                     | 5-64 |

|                   | Error Detection and Correction       | 5-64 |

| 5.7.8<br>5.7.9    | Status Read/Write                    | 5-67 |

| 5.7.9<br>5.8      | Refresh Cycle                        | 5-68 |

| 5.8.1             | CONSOLE                              | 5-70 |

|                   | 8080 Console Processor               | 5-70 |

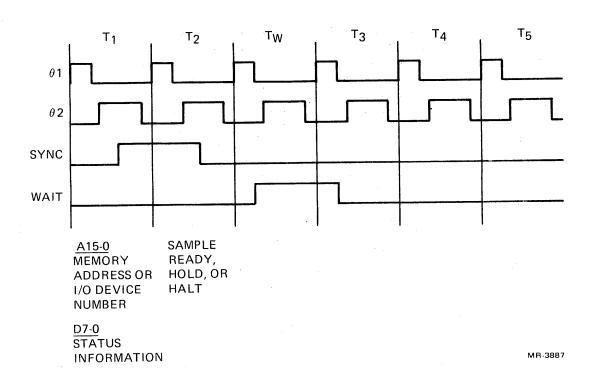

| 5.8.1.1           | 8080A Timing                         | 5-72 |

| 5.8.1.2           | 8080A Operation                      | 5-74 |

| 5.8.1.3           | Console Operations                   | 5_74 |

### **CONTENTS (Cont)**

| 5.8.2<br>5.8.2.1 | CPU/Bus Control                                 | 5-76  |

|------------------|-------------------------------------------------|-------|

| 5.8.2.2          | Instruction Register Read Operation             |       |

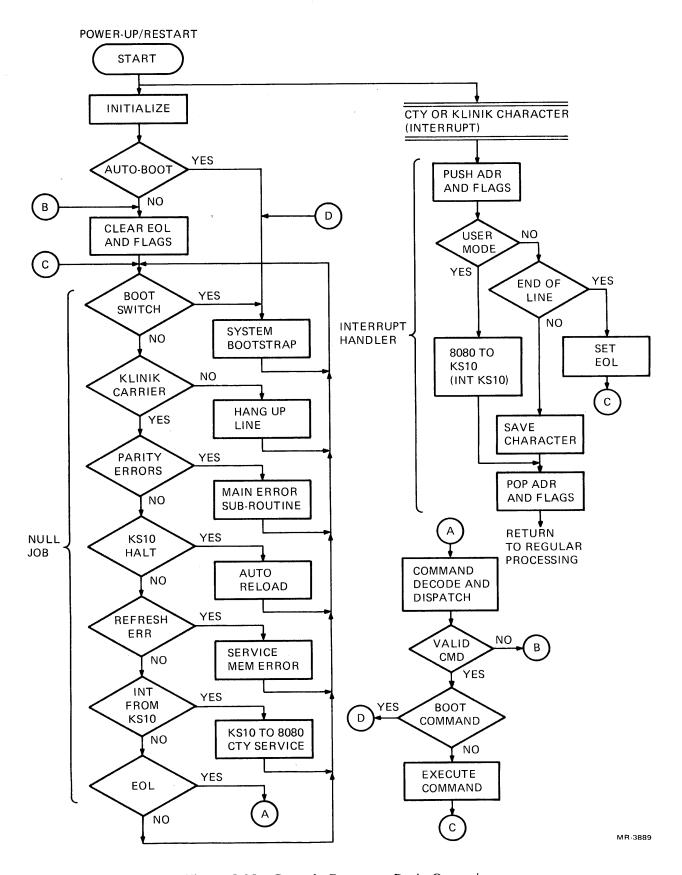

| 5.8.3            | Console Program                                 |       |

| 5.8.3.1          | Power-Up/Initialization                         |       |

| 5.8.3.2          | Console Commands                                |       |

| 5.8.3.3          | System Bootstrap                                |       |

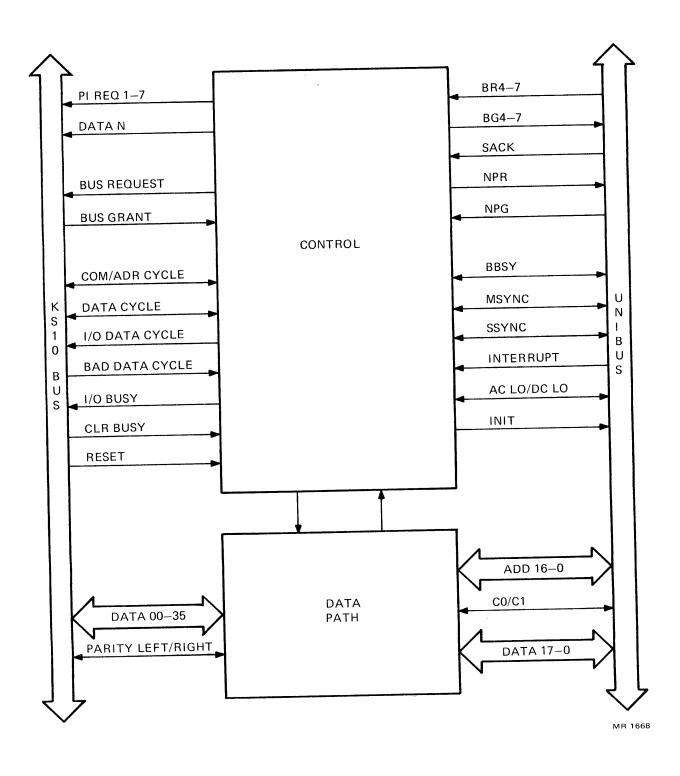

| 5.9              | UNIBUS ADAPTER.                                 |       |

| 5.9.1            | Basic Operation                                 |       |

| 5.9.1.1          | NPR Data Transfers                              |       |

| 5.9.1.2          | I/O Register Data Transfers                     |       |

| 5.9.1.3          | PI Operation                                    |       |

| 5.9.2            | UBA Status and Control Registers                |       |

| 5.9.2.1          | Paging RAM                                      |       |

| 5.9.2.2          | Status Register                                 |       |

| 5.9.2.3          | Maintenance Register                            |       |

| 5.9.3            | Logical Organization                            |       |

| 5.9.4            | NPR Data Transfer Operation                     |       |

| 5.9.5            | I/O Data Transfer Operation                     |       |

| 5.9.6            | PI Operation                                    |       |

| 5.9.7            | Wraparound Data Transfer                        | 5-133 |

| 5.10             | KS10 POWER SYSTEM                               | 5-134 |

| 5.10.1           | 861 Power Controller                            |       |

| 5.10.2           | H7130 Power Supply and 5413261 Power            | 5 151 |

| 3.10.2           | Distribution Module                             | 5-137 |

| 5.10.3           | H765 Power Supply (BA11-K)                      |       |

| APPENDIX A       | KS10 DIFFERENCES (KS10 VS. KL10)                |       |

| APPENDIX B       | KS10 UNIBUS                                     |       |

| APPENDIX C       | MICROCODE OPERATION                             |       |

|                  | FIGURES                                         |       |

| Figure No.       | Title                                           | Page  |

| 1.1              | Basic KS10 System Configuration                 | 1_1   |

| 1-1<br>1-2       | Detailed KS10 System Configuration              |       |

| 1-2              | KS10 Cabinet                                    |       |

| 1-3              | KS10 Cabinet (Front View – Skins Removed)       | 1_8   |

| 1-4              | KS10-PA Card Cage Module Utilization List (MUL) | 1_0   |

| 1-6              | BA11-K Drawer (KS10 Cabinet) MUL                |       |

| 1-7              | KS10 Cabinet (Rear View – Skins Removed)        | 1-12  |

| 1-8              | DNHXX Cabinet (Front View – Skins Removed)      |       |

| 1-9              | DNHXX Cabinet (Rear View – Skins Removed)       | 1-15  |

| 1-10             | BA11-K Drawer (DNHXX Cabinet) MUL               | 1-16  |

| 2-1              | Typical KS10 System Configuration               |       |

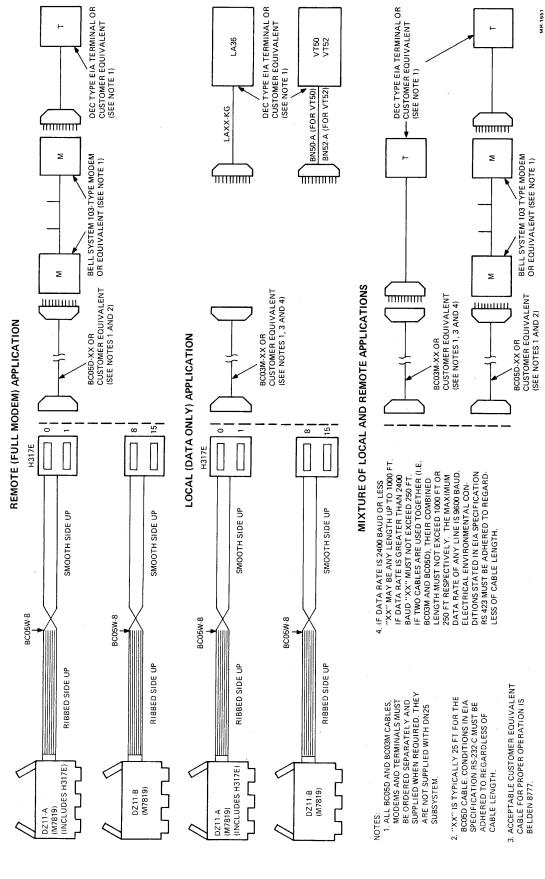

| 2-1              | KS10 Asynchronous Communications Lines          | 2-4   |

| ~ <b>~</b>       |                                                 | •     |

# FIGURES (Cont)

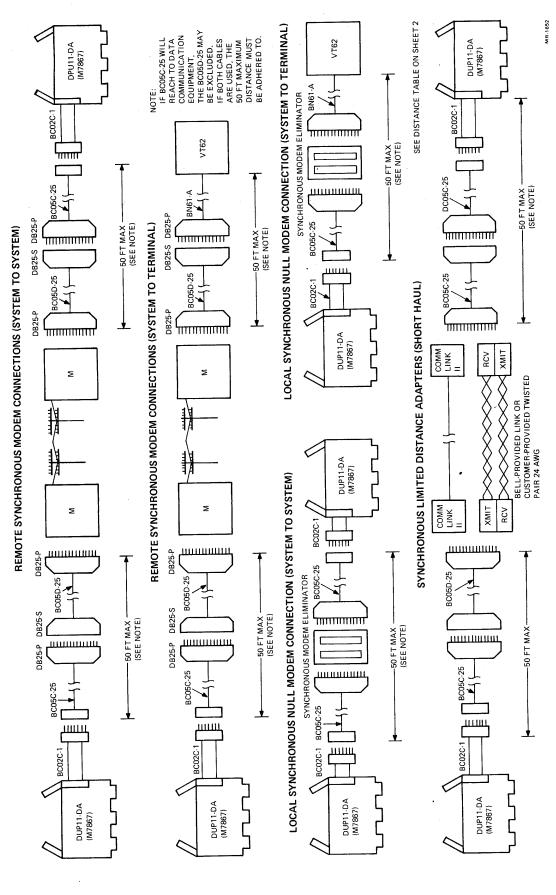

| 2-3  | KS10 Synchronous Communications Lines                      | 2-5          |

|------|------------------------------------------------------------|--------------|

| 4-1  | KS10 Switch and Indicator Panel                            | 4-1          |

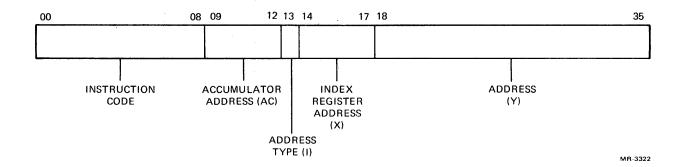

| 4-2  | Instruction Format                                         |              |

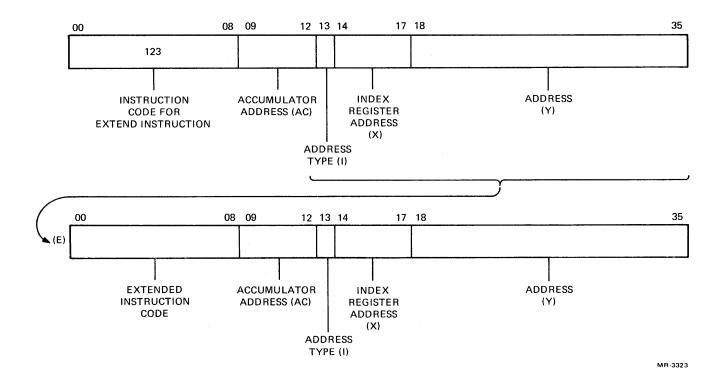

| 4-3  | Extended Instruction Format                                |              |

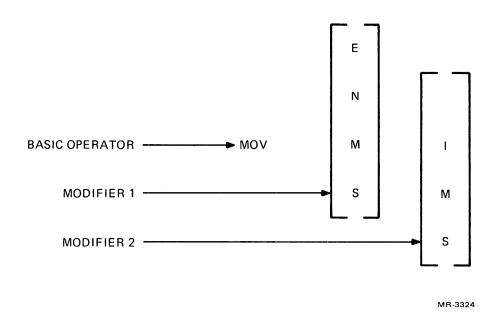

| 4-4  | Move Instruction Mnemonic Construction                     |              |

| 4-5  | Move Instructions                                          |              |

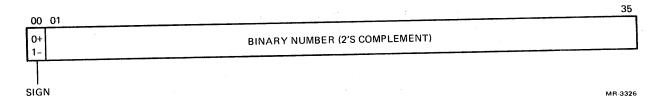

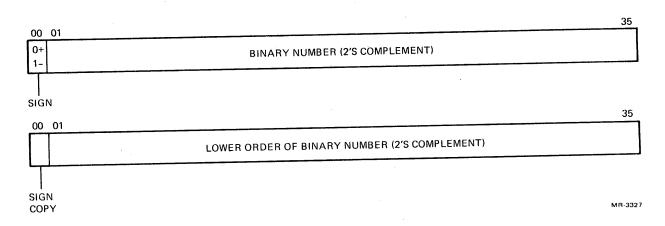

| 4-6  | Single-Length Fixed-Point Operand                          | 4-9          |

| 4-7  | Double-Length Fixed-Point Operand                          |              |

| 4-8  | Single-Precision Floating-Point Operand                    | 4-9          |

| 4-9  | Double-Precision Floating-Point Operand                    | 4-9          |

| 4-10 | KS10 Effective Address Calculation (Not Valid for External |              |

|      | I/O Instructions)                                          | 4-10         |

| 4-11 | KS10 Effective Address Calculation for External            |              |

|      | I/O Instructions                                           | 4-12         |

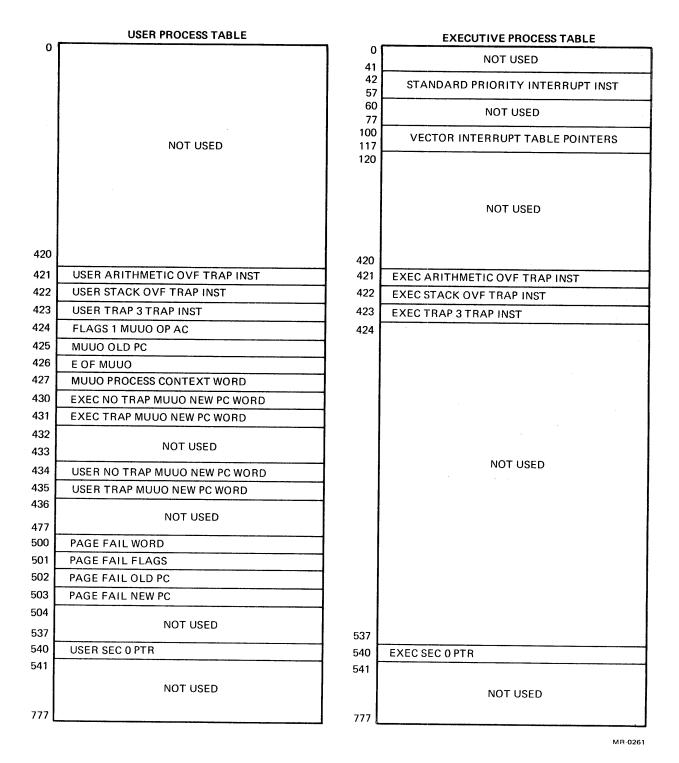

| 4-12 | I/O Address Format                                         | 4-13         |

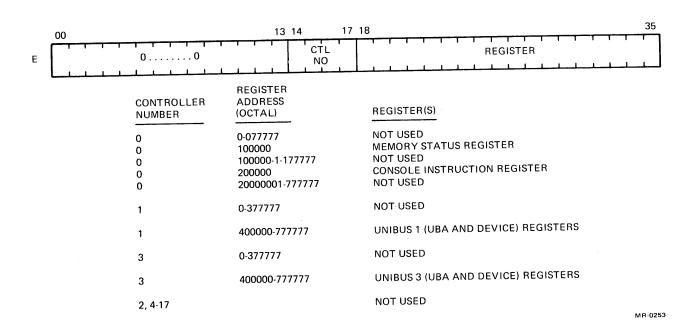

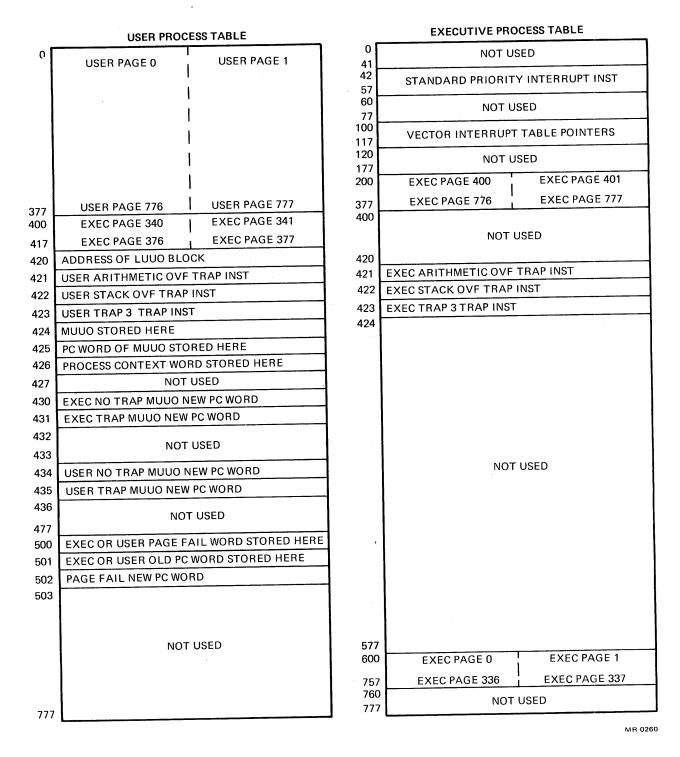

| 4-13 | KS10 EPT/UPT (TOPS-10 Paging)                              | 4-15         |

| 4-14 | KS10 EPT/UPT (TOPS-20 Paging)                              |              |

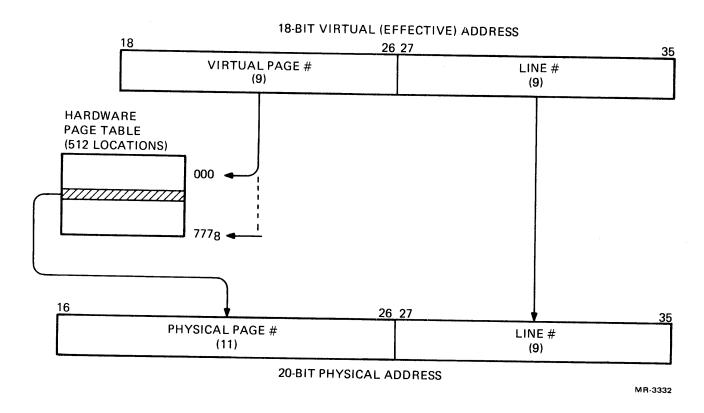

| 4-15 | CPU Virtual to Physical Address Conversion                 |              |

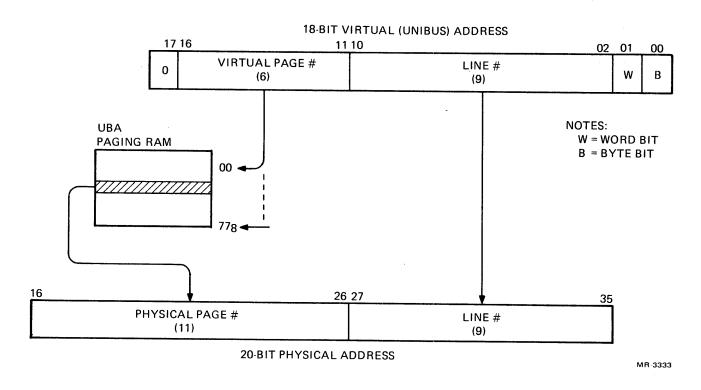

| 4-16 | UBA Virtual to Physical Address Conversion                 |              |

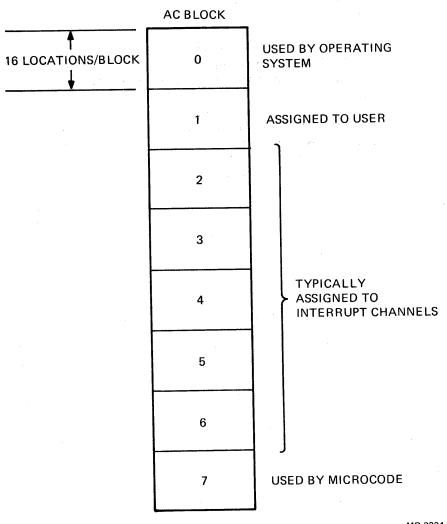

| 4-17 | AC Block Usage                                             |              |

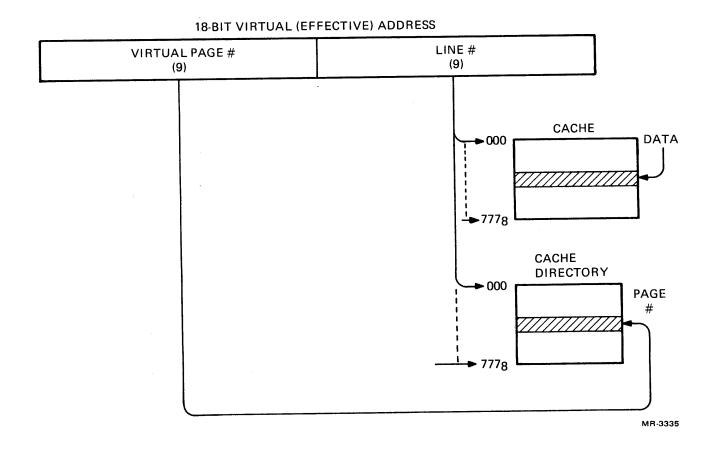

| 4-18 | Loading the Cache                                          |              |

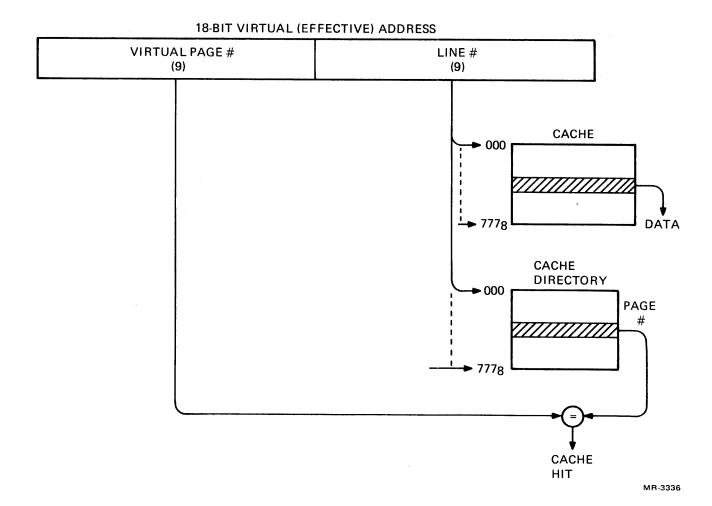

| 4-19 | Reading the Cache (Cache Hit)                              |              |

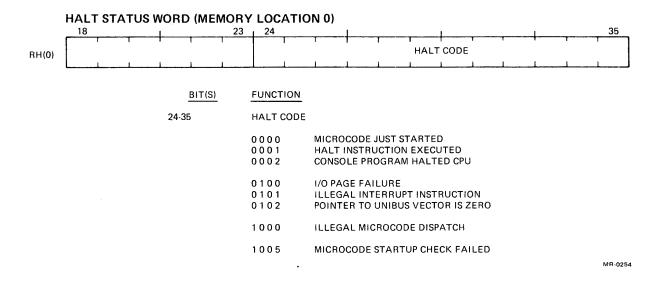

| 4-20 | Halt Status Word                                           |              |

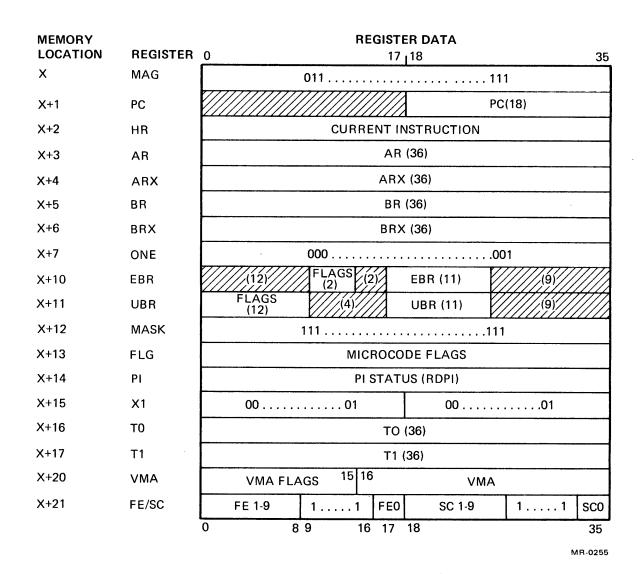

| 4-21 | Halt Status Block                                          |              |

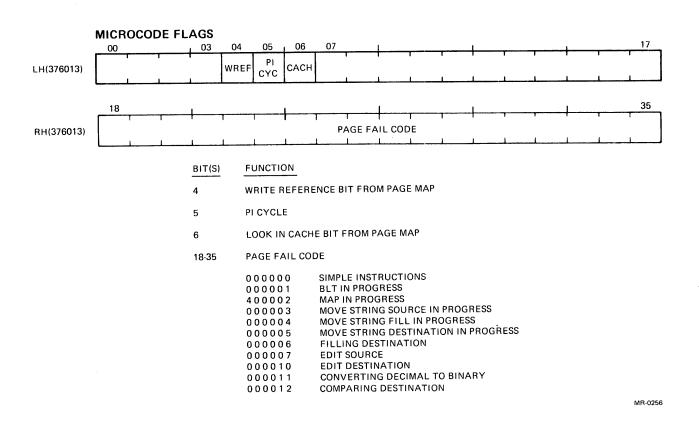

| 4-22 | Microcode Flags.                                           |              |

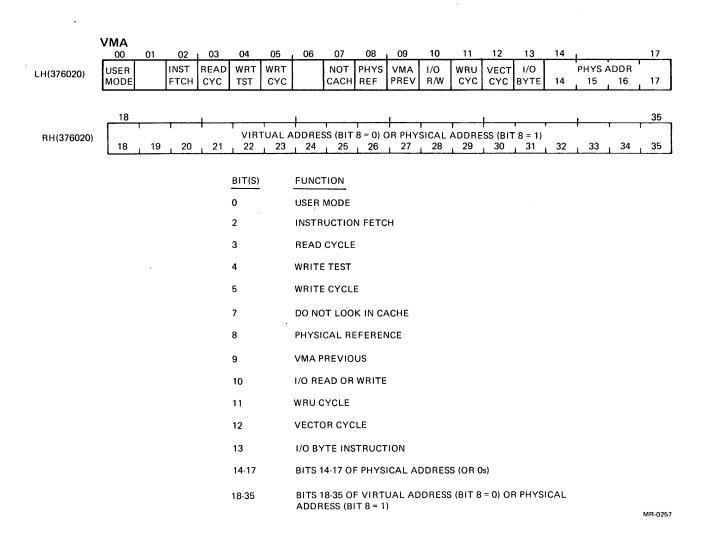

| 4-23 | VMA                                                        |              |

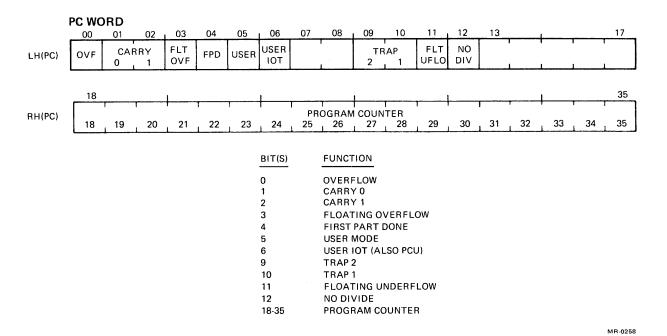

| 4-24 | PC Word                                                    |              |

| 4-25 | Page Fail Word                                             |              |

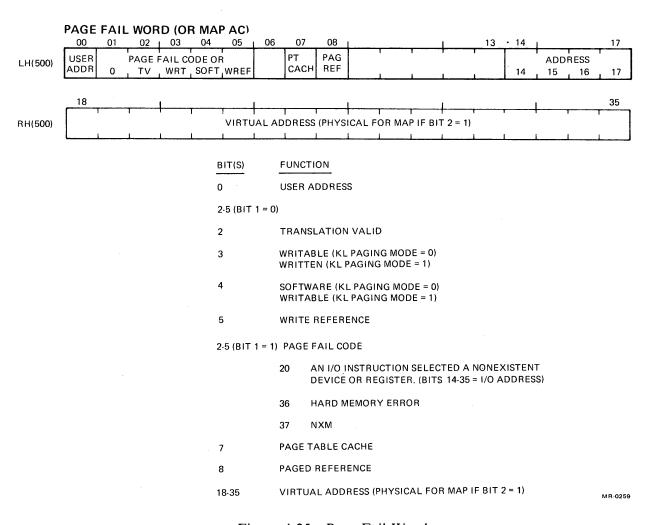

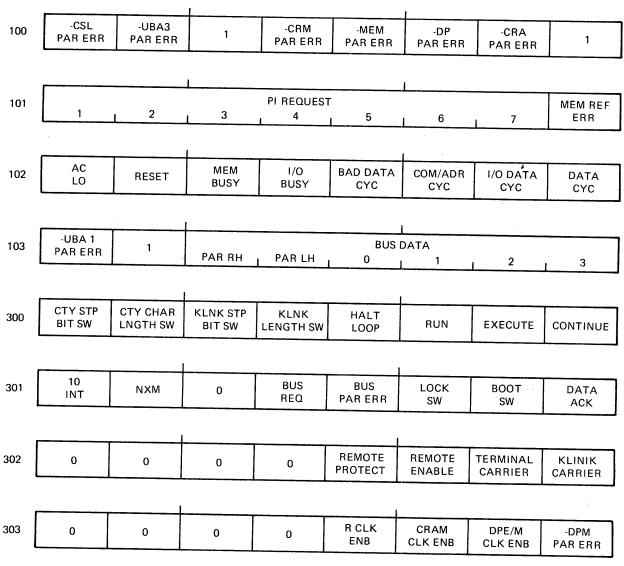

| 4-26 | Console Status Registers.                                  |              |

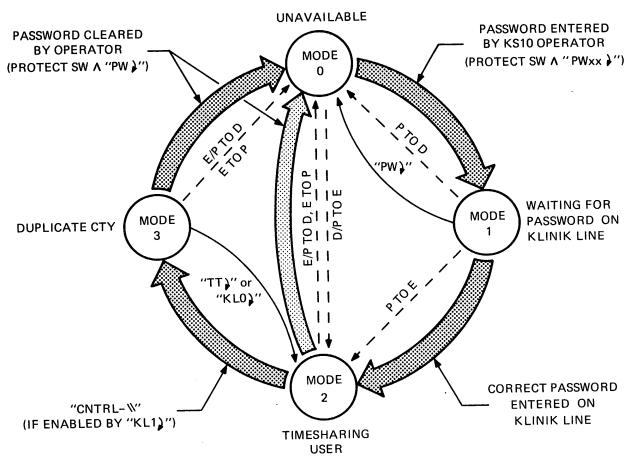

| 4-27 | KLINIK Line Modes                                          |              |

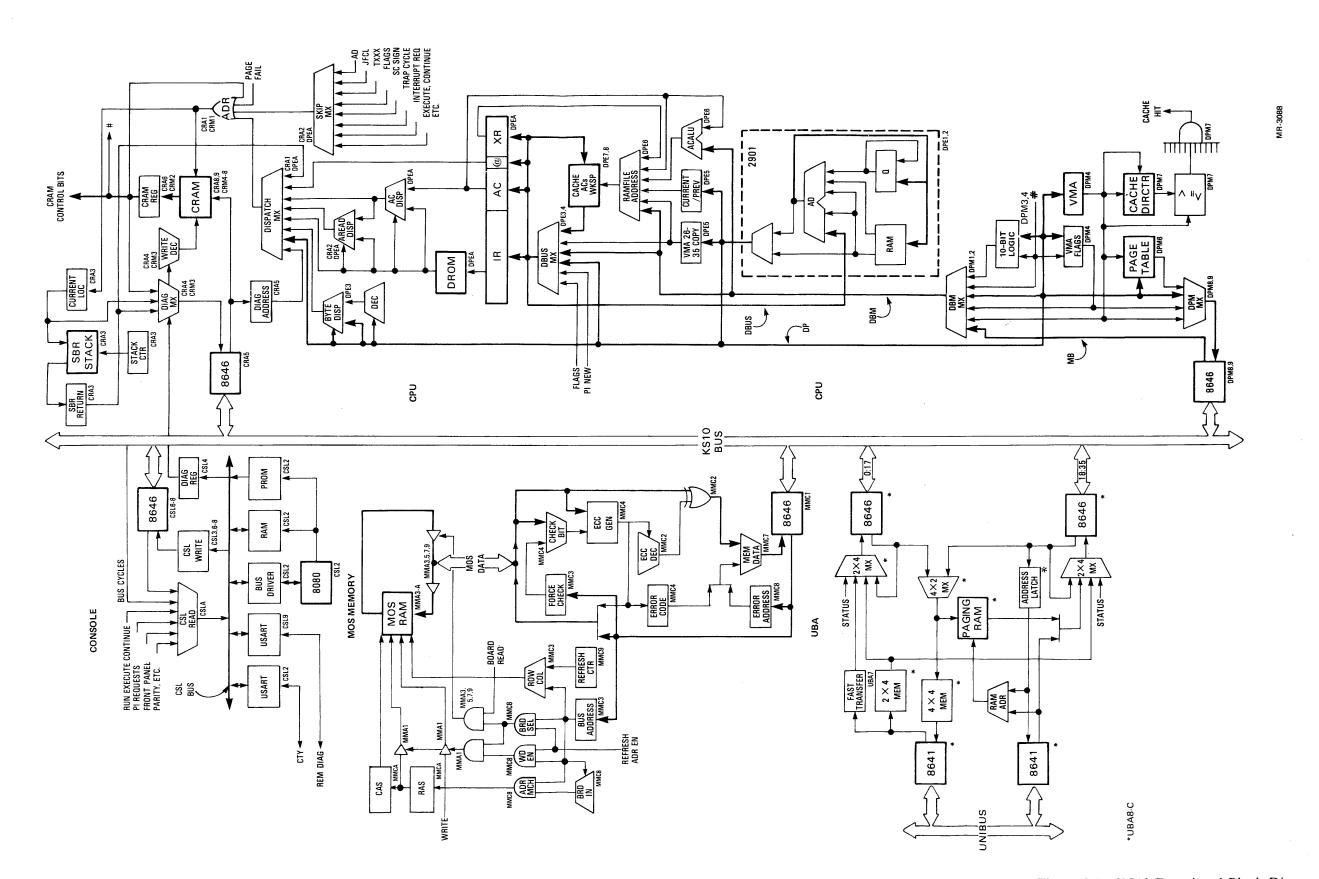

| 5-1  | KS10 Functional Block Diagram                              |              |

|      | Processor Data Flow                                        |              |

| 5-2  | Clock Distribution and CPU Clock Control                   | 5-0<br>5-0   |

| 5-3  | Clock Distribution and CPU Clock Control                   | 9-ر<br>۱۸ ۶  |

| 5-4  | System Clocks                                              | 10-5         |

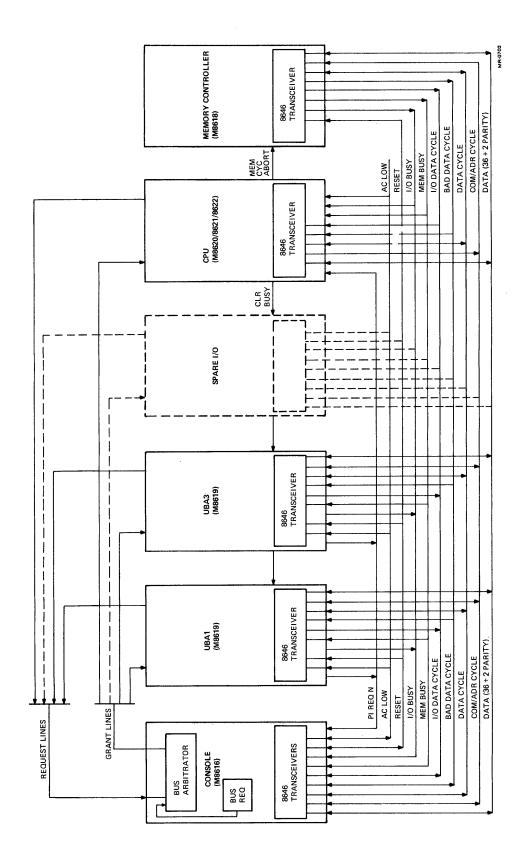

| 5-5  | KS10 (Backplane) Bus                                       |              |

| 5-6  | 8646 Bus Transceiver                                       |              |

| 5-7  | Request/Grant, Bus Timing Diagram                          |              |

| 5-8  | Basic KS10 Command/Address Format                          |              |

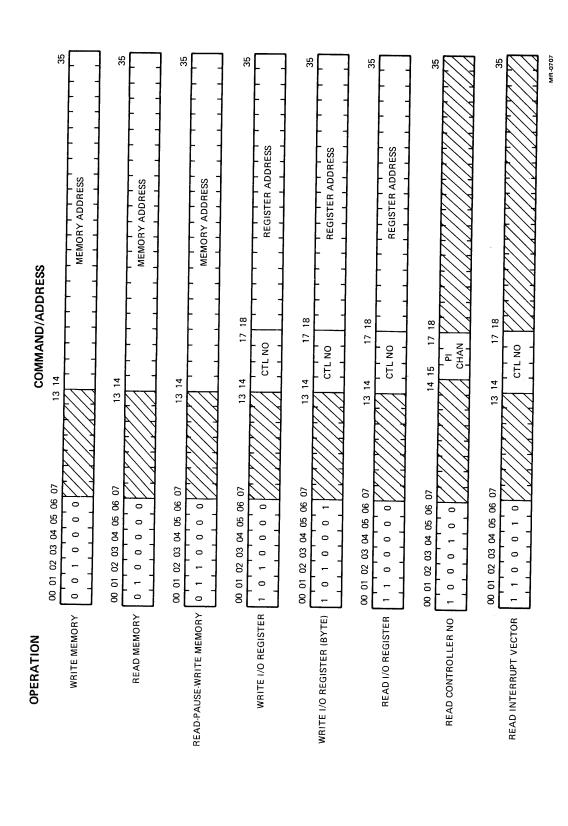

| 5-9  | Command/Address Bits                                       | 5-22         |

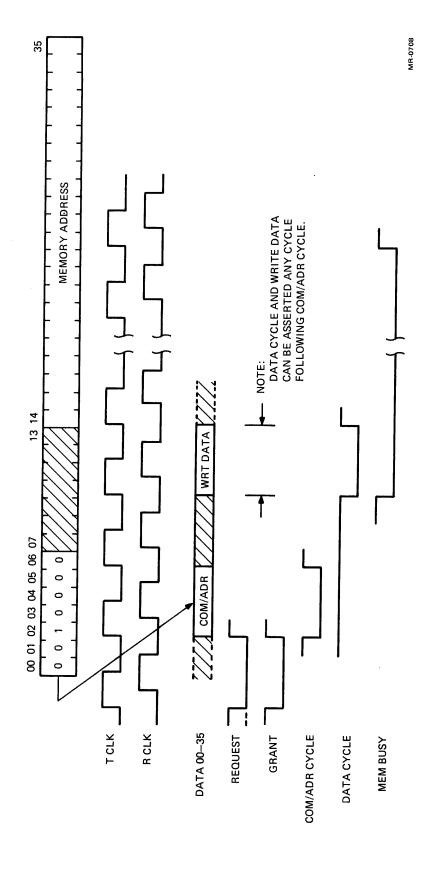

| 5-10 | Memory Write, Bus Timing Diagram                           |              |

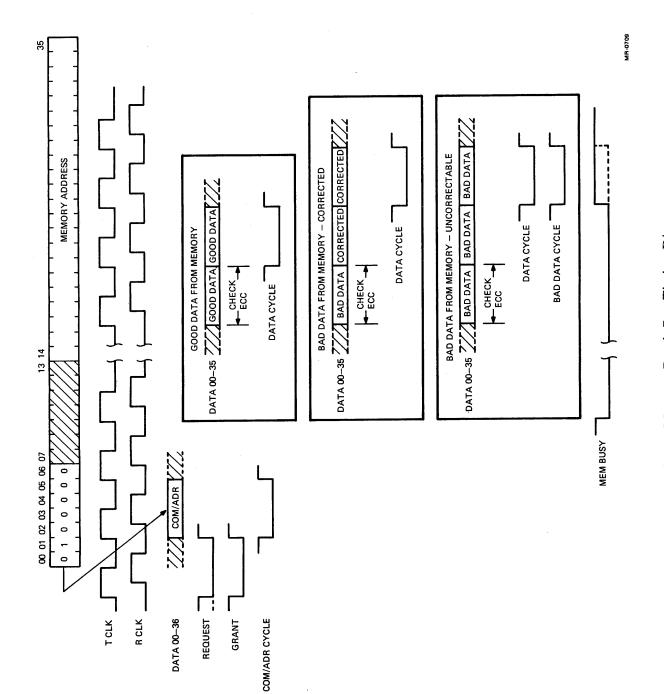

| 5-11 | Memory Read, Bus Timing Diagram                            | 5-25<br>5-27 |

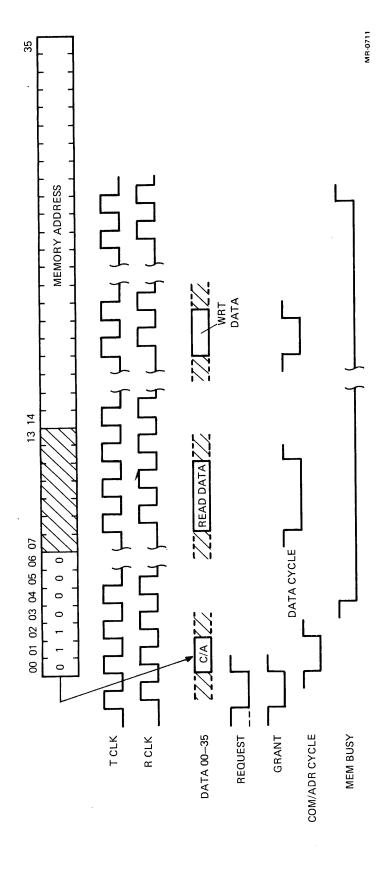

| 5-12 | Memory Read-Pause-Write, Bus Timing Diagram                |              |

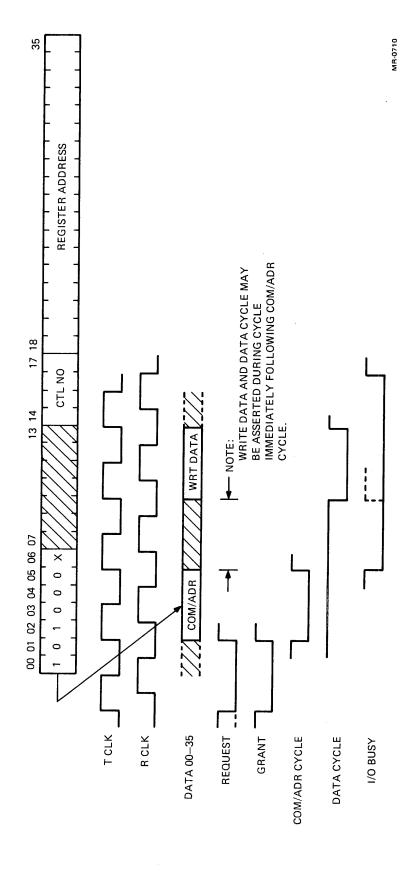

| 5-13 | I/O Register Write, Bus Timing Diagram                     |              |

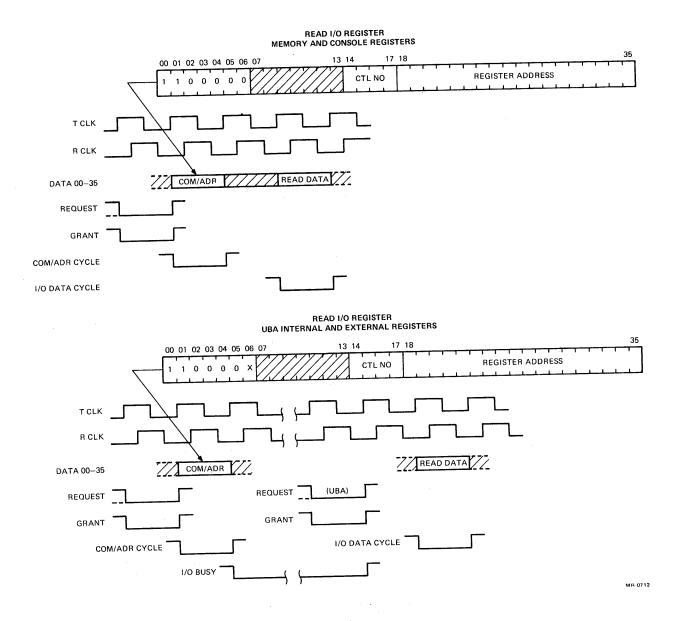

| 5-14 | I/O Register Read, Bus Timing Diagram                      |              |

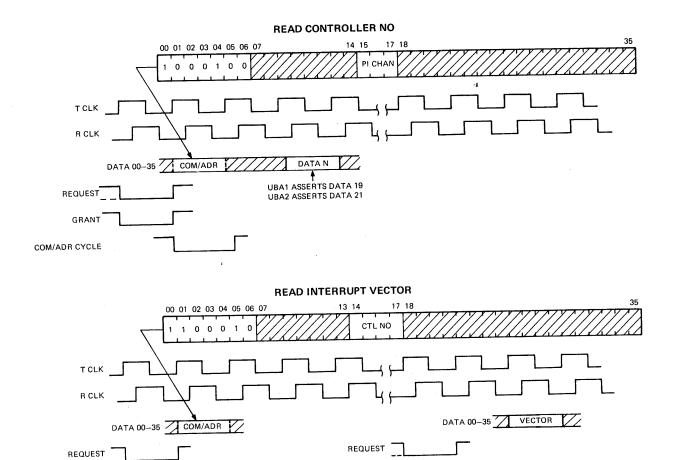

| 5-15 | PI Operation, Bus Timing Diagram                           | 5-31         |

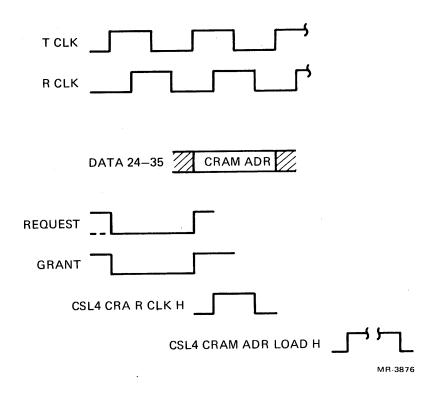

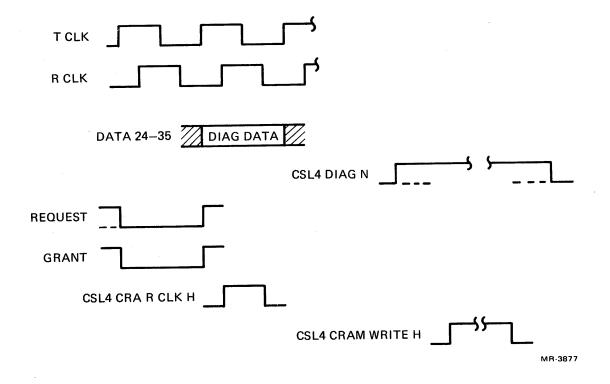

| 5-16 | CRAM Address Load, Bus Timing Diagram                      | 5-33         |

| 5-17 | Diagnostic Write, Bus Timing Diagram                       | 5-33         |

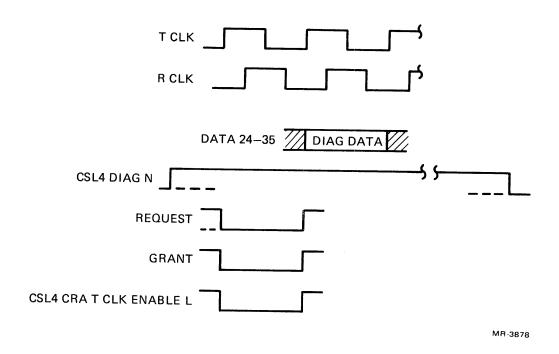

| 5-18 | Diagnostic Read, Bus Timing Diagram                        | 5-34         |

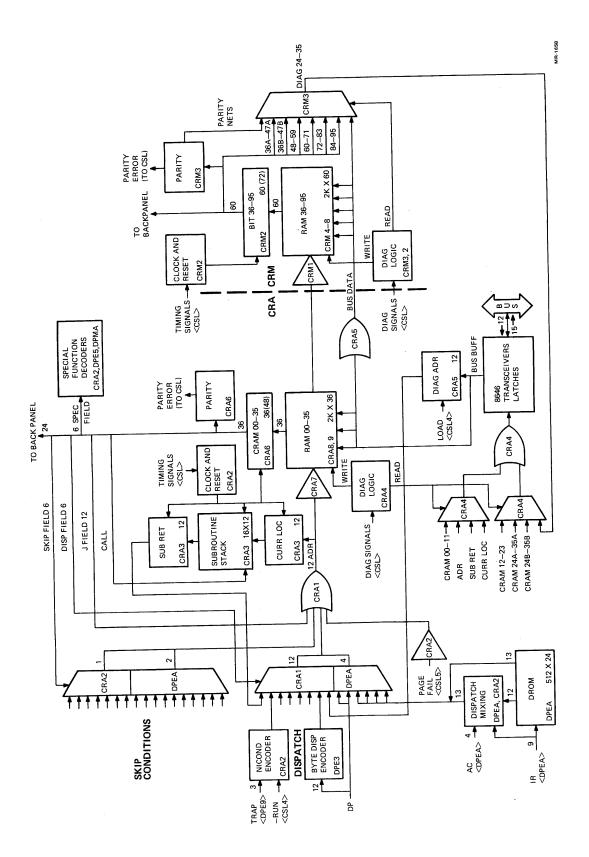

| 5-19 | Microcontroller, Block Diagram                             | 5-35         |

# FIGURES (Cont)

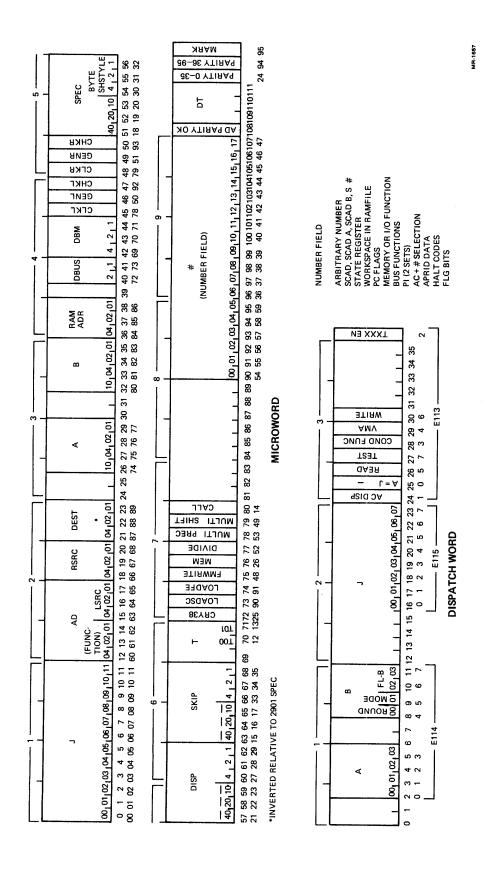

| 5-20 | Microword Formats                           | 5-36    |

|------|---------------------------------------------|---------|

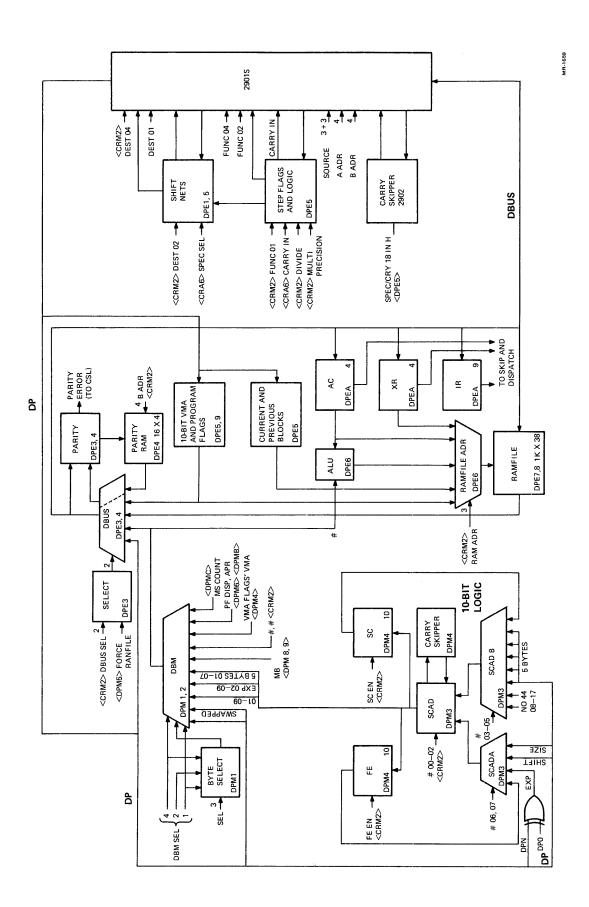

| 5-21 | Data Path (Execute), Block Diagram          |         |

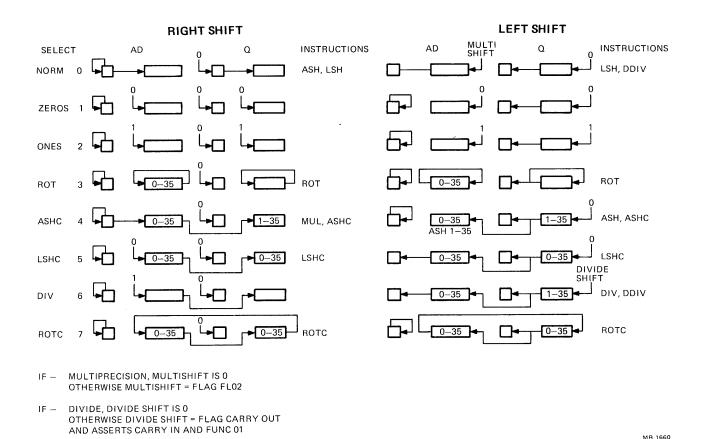

| 5-22 | Shift Configurations                        |         |

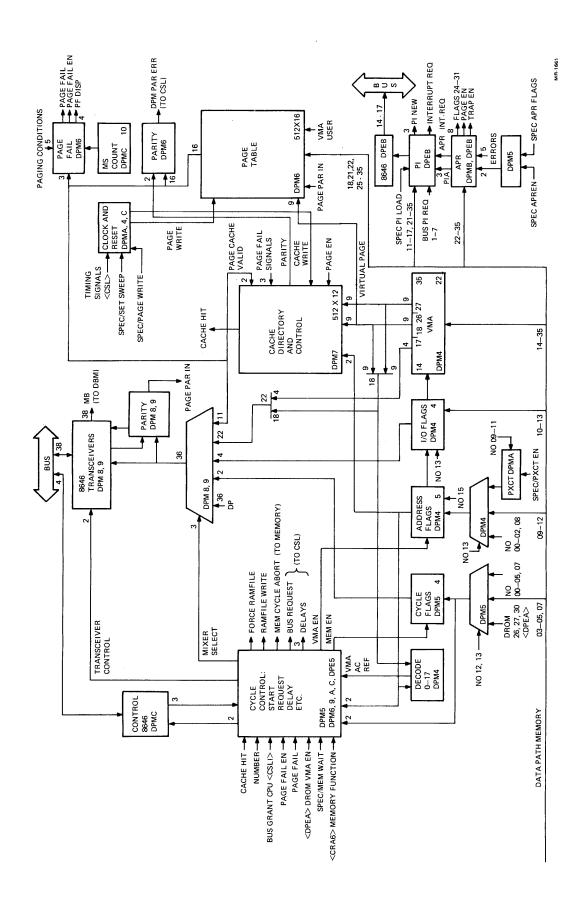

| 5-23 | Data Path (Memory), Block Diagram           |         |

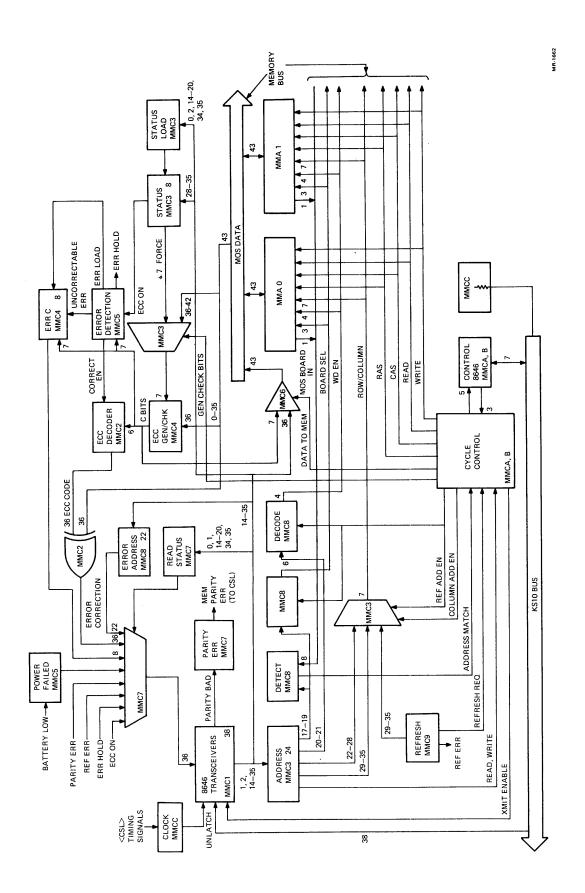

| 5-24 | MOS Memory, Block Diagram                   |         |

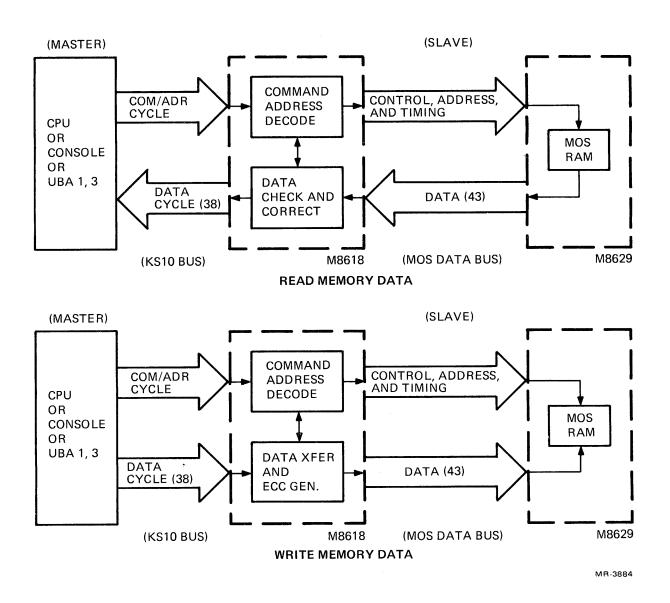

| 5-25 | Memory Read/Write Operation                 |         |

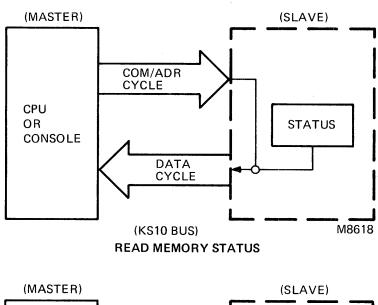

| 5-26 | Status Read/Write Operation                 |         |

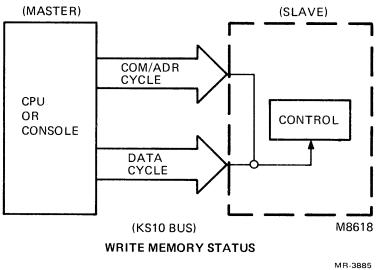

| 5-27 | Memory Write, Timing Diagram                |         |

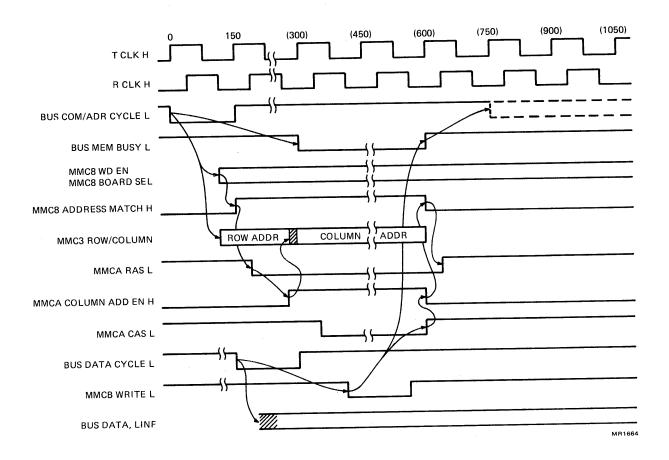

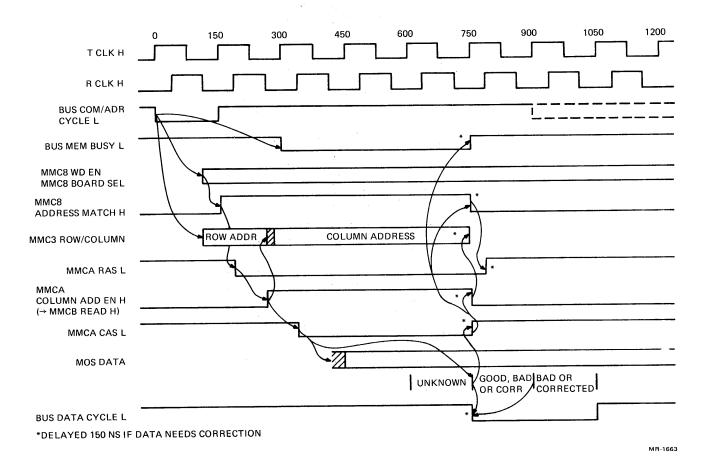

| 5-28 | Memory Read, Timing Diagram                 |         |

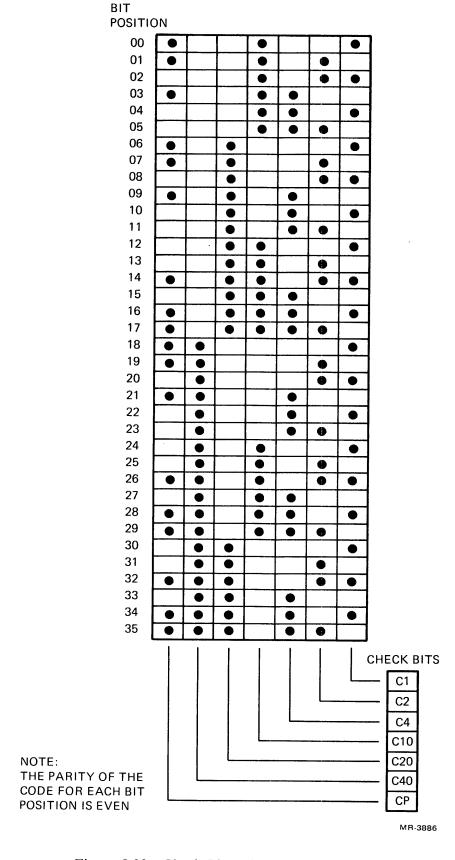

| 5-29 | Check Bit and Data Bit Relationship         |         |

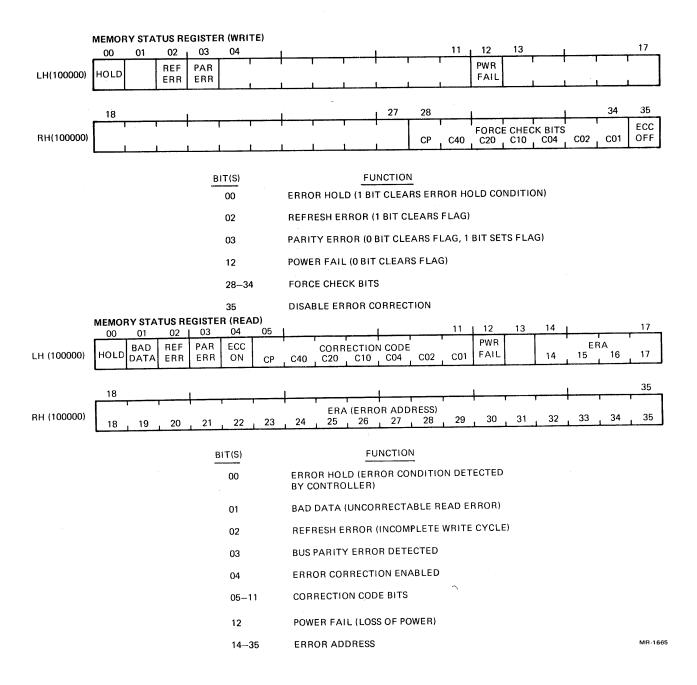

| 5-30 | Memory Status                               | 5-69    |

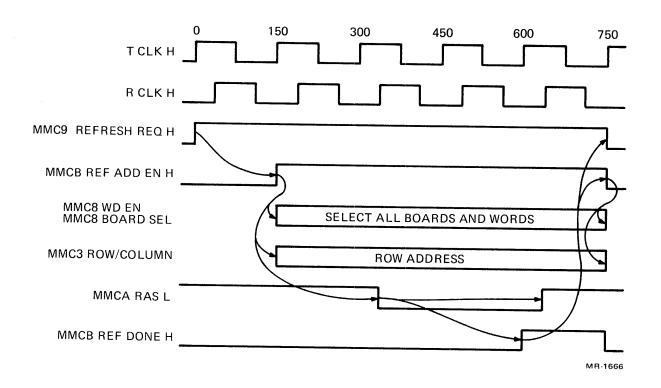

| 5-31 | Memory Refresh, Timing Diagram              |         |

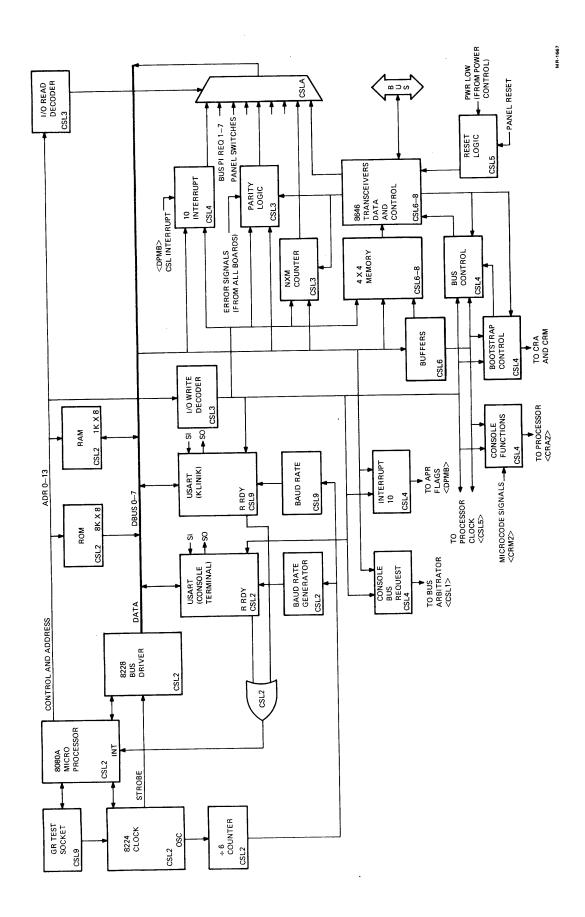

| 5-32 | Console, Block Diagram                      |         |

| 5-33 | 8080A, Basic Timing                         |         |

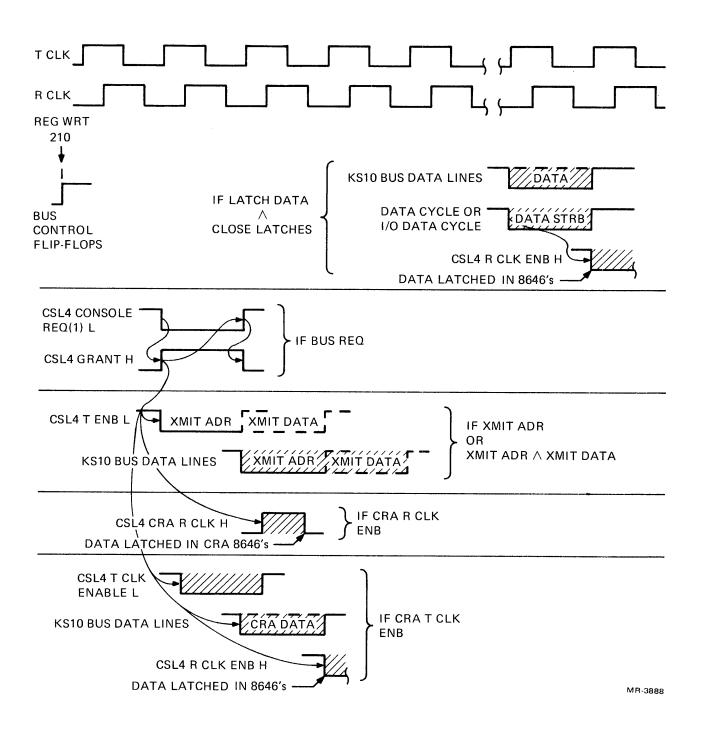

| 5-34 | Console Bus Functions, Basic Timing         |         |

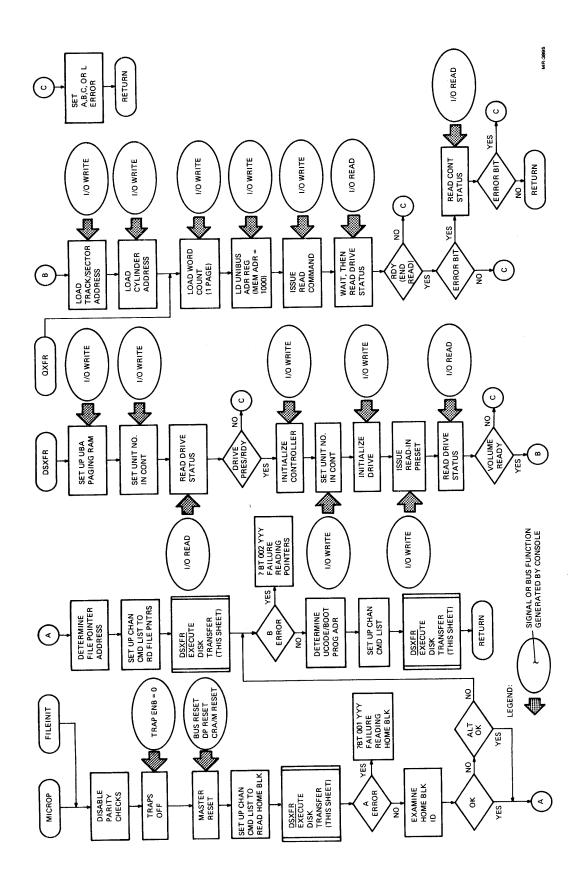

| 5-35 | Console Program, Basic Operation            |         |

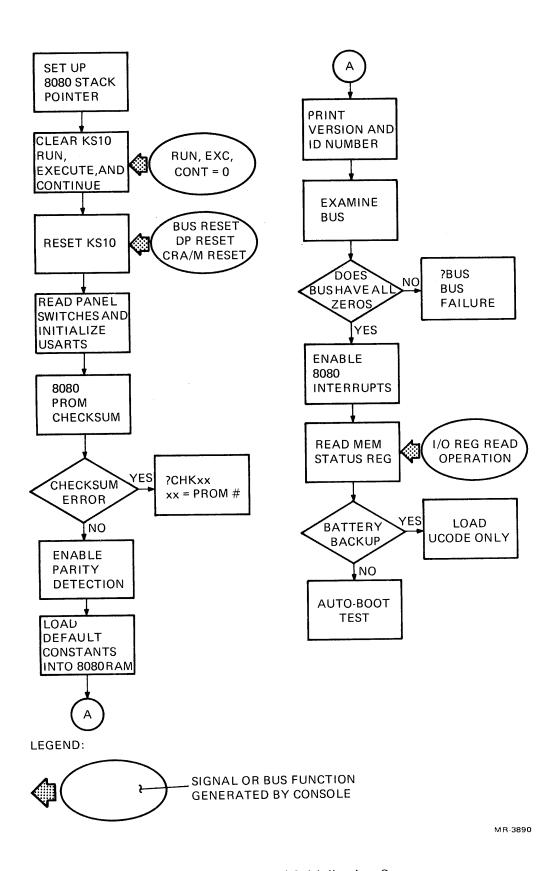

| 5-36 | Power-Up and Initialization Sequence        |         |

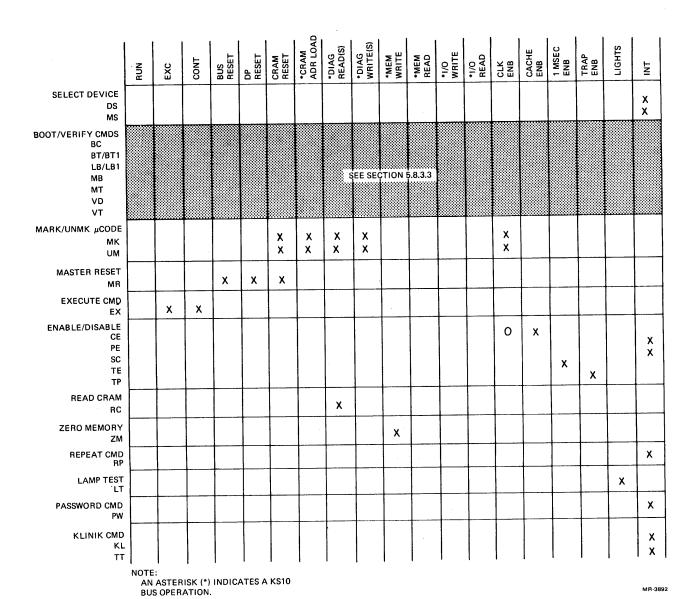

| 5-37 | Signals and KS10 Bus Operation Initiated by |         |

| 3-37 | Console Commands                            | 5.86    |

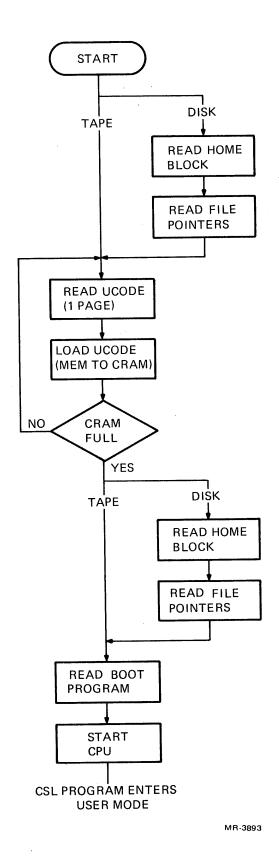

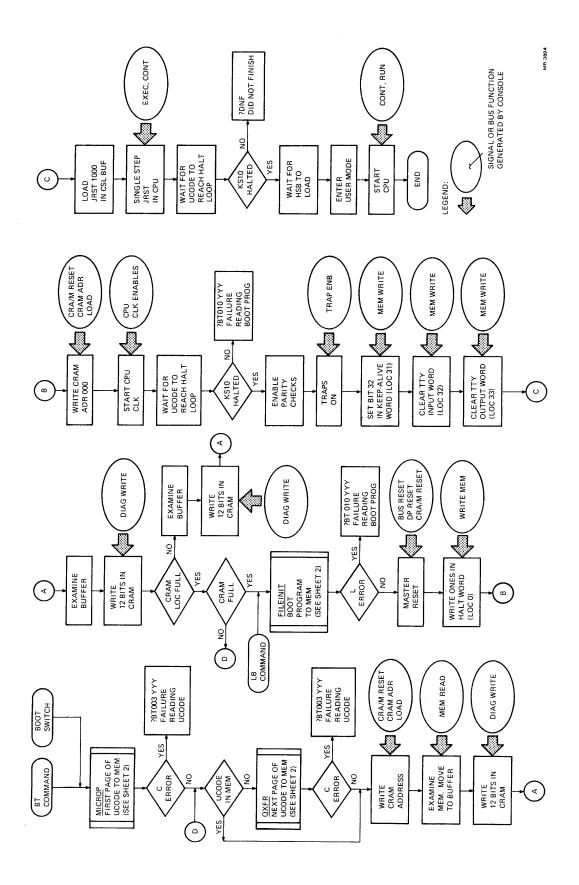

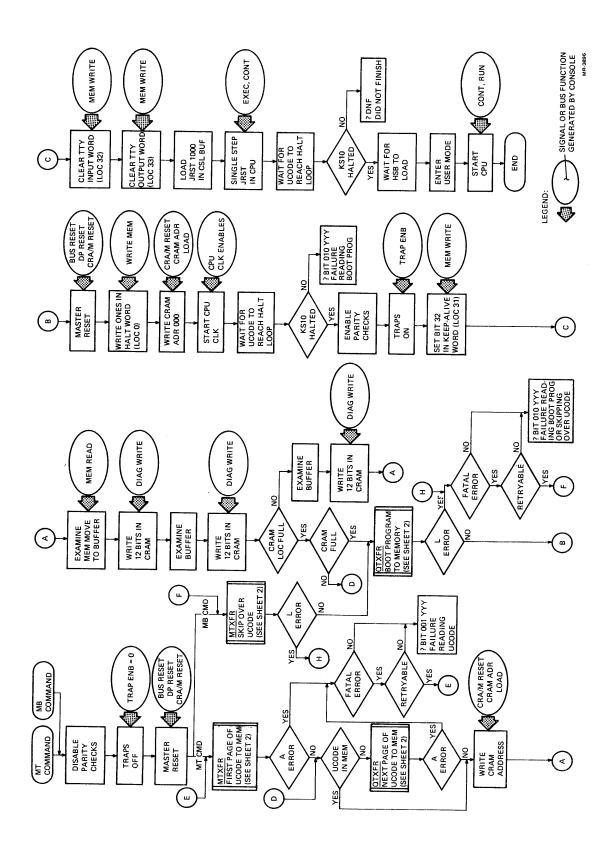

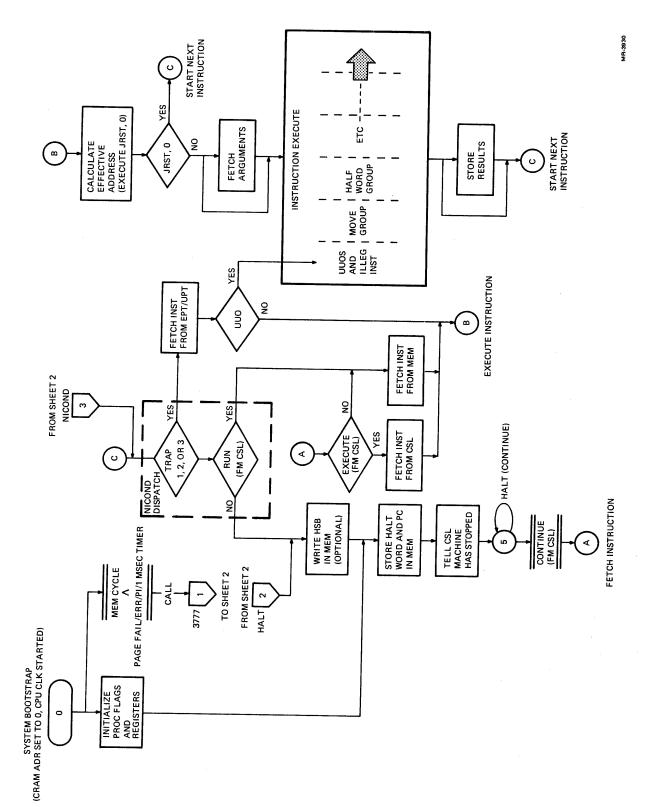

| 5 20 | System Bootstrap, Basic Operation           |         |

| 5-38 |                                             |         |

| 5-39 | Bootstrap from Disk, Detailed Operation     | ۶ معربی |

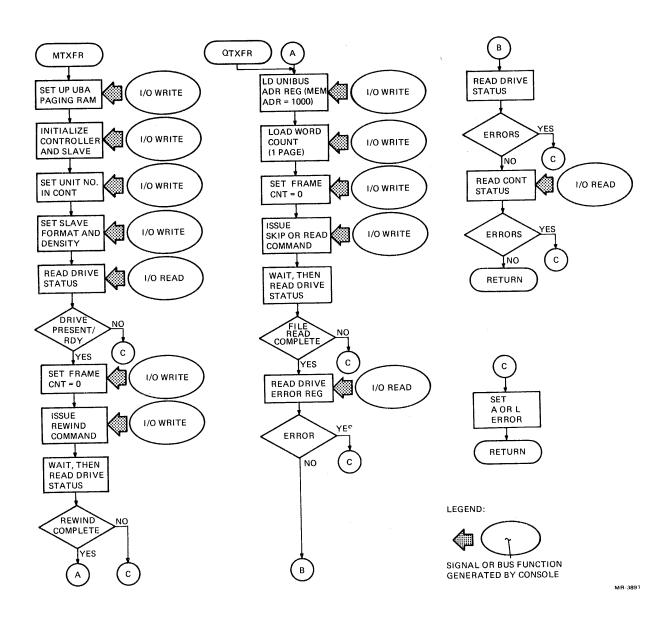

| 5-40 | Bootstrap from Tape, Detailed Operation     |         |

| 5-41 | UBA, Simplified Block Diagram               | 5-93    |

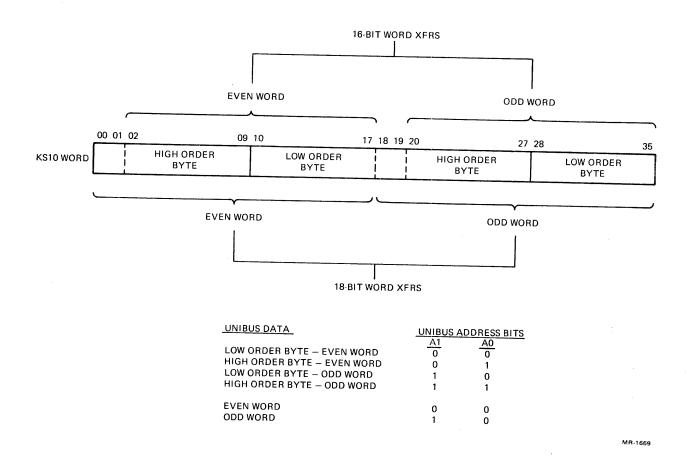

| 5-42 | Unibus Data Positioning Within KS10 Word    |         |

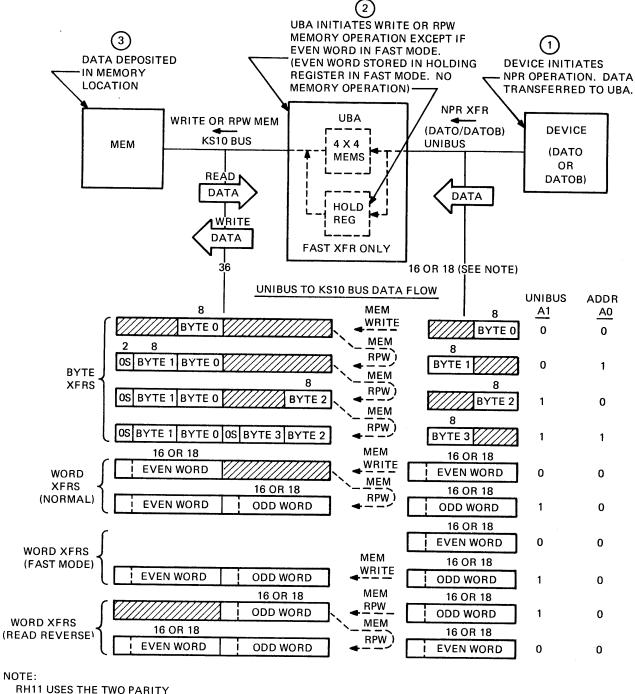

| 5-43 | NPR Write (to Memory), Data Flow            | 5-98    |

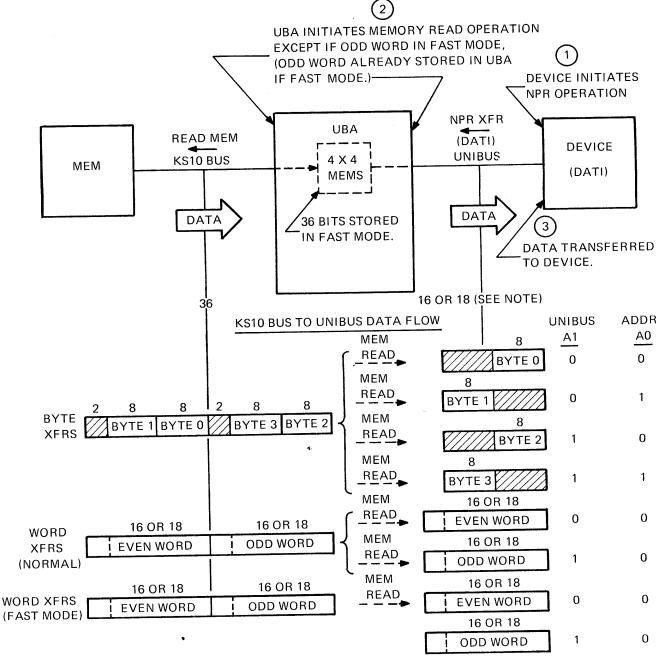

| 5-44 | NPR Read (from Memory), Data Flow           |         |

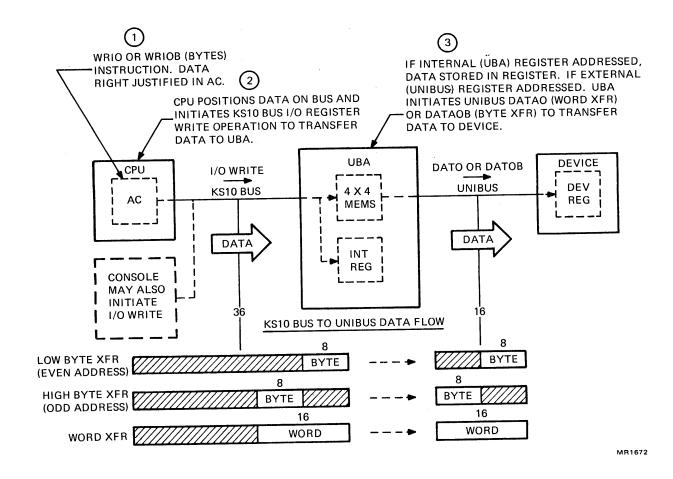

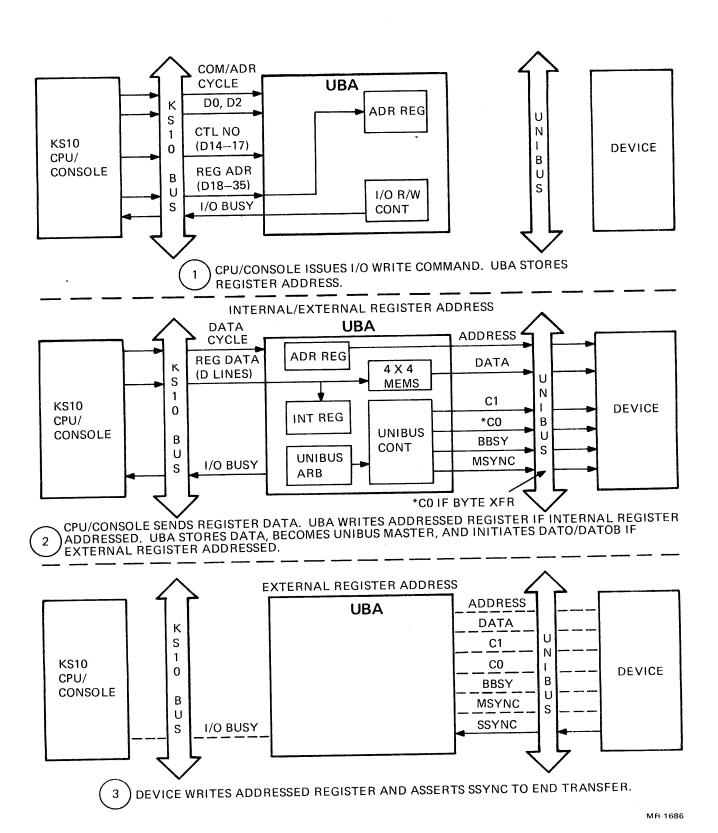

| 5-45 | I/O Write, Data Flow                        | 5-101   |

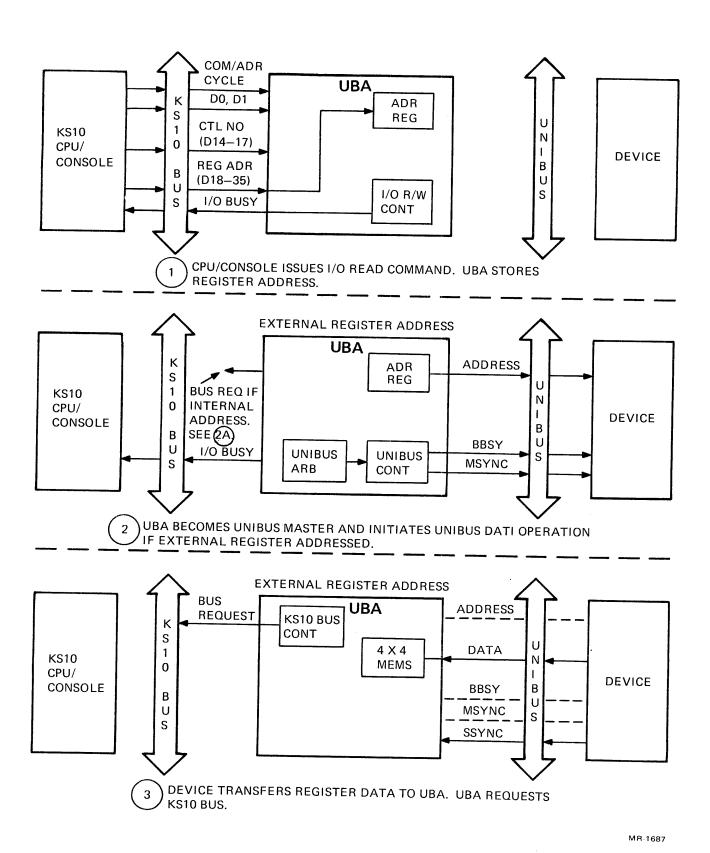

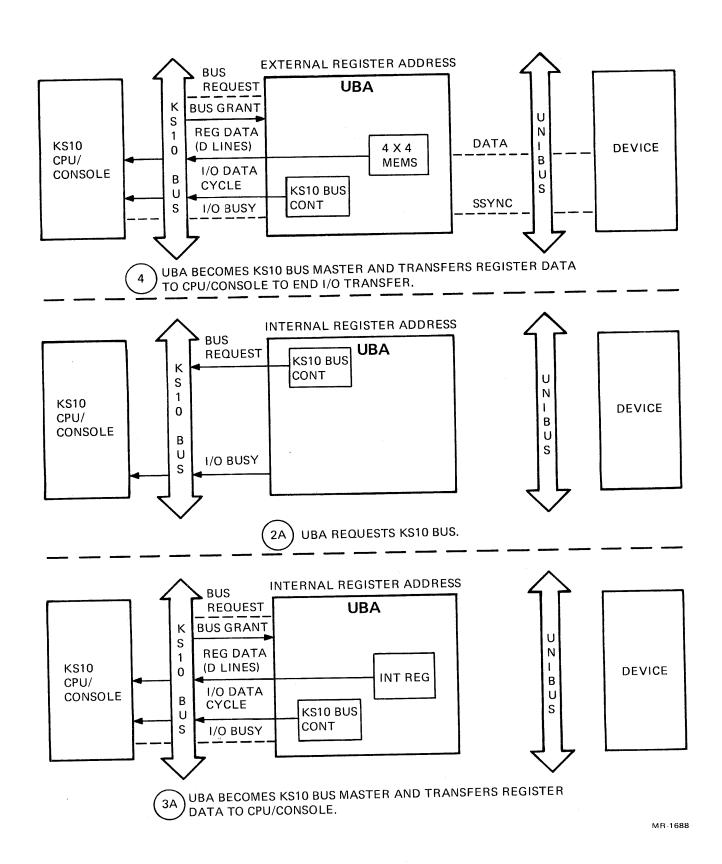

| 5-46 | I/O Read, Data Flow                         |         |

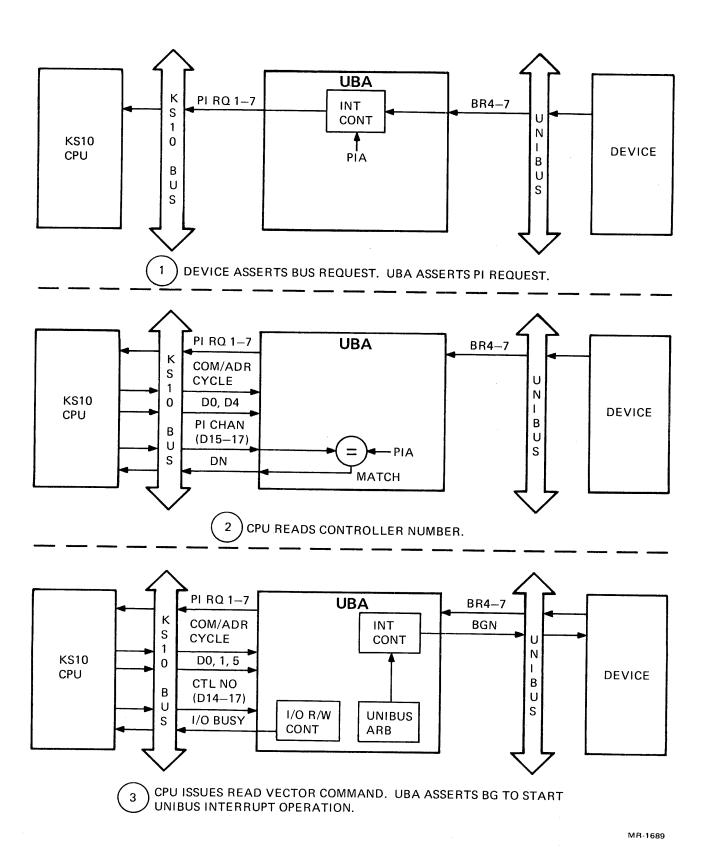

| 5-47 | PI Operation, Data Flow                     |         |

| 5-48 | Paging RAM                                  | 5-106   |

| 5-49 | Unibus to Memory Address Translation        |         |

| 5-50 | UBA Status                                  |         |

| 5-51 | Maintenance Register                        |         |

| 5-52 | UBA, Detailed Block Diagram                 | 5-112   |

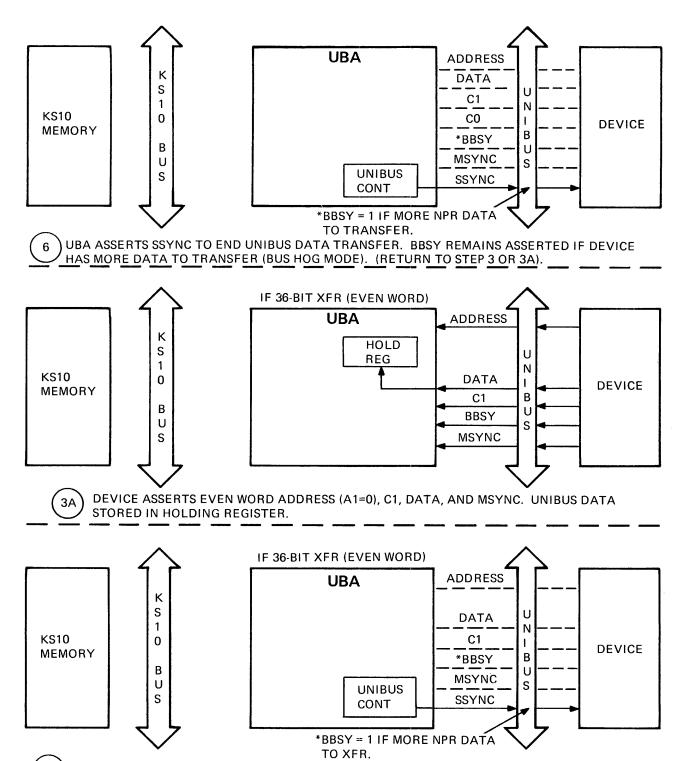

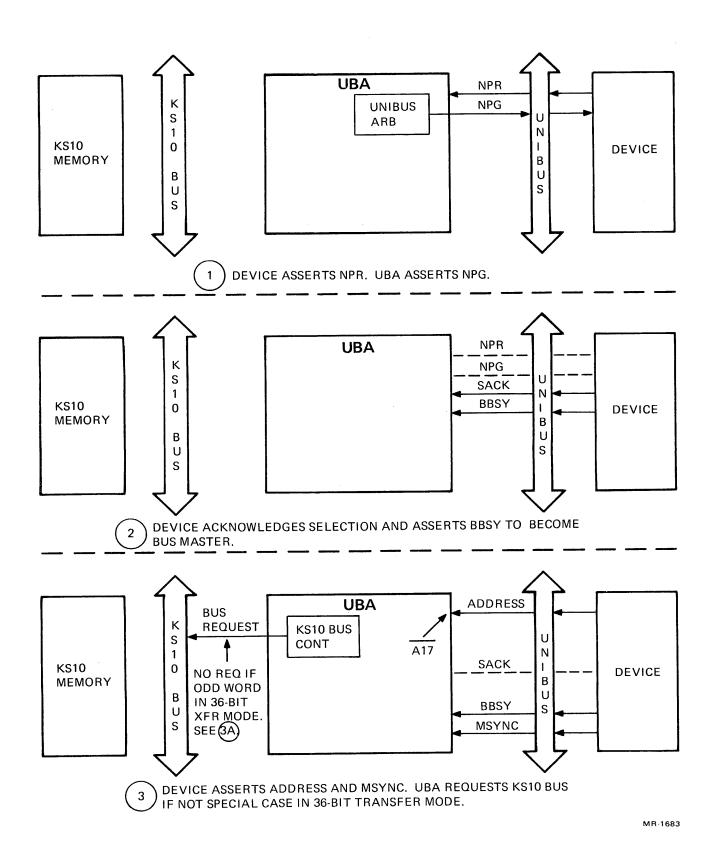

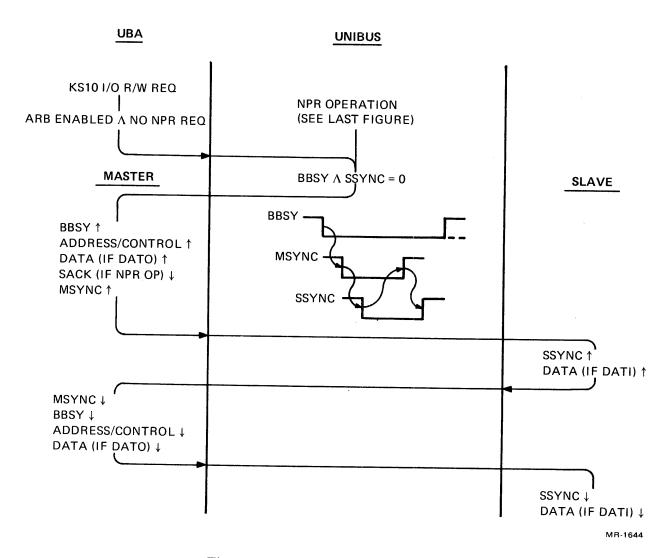

| 5-53 | NPR Write, Bus Dialogue                     | 5-114   |

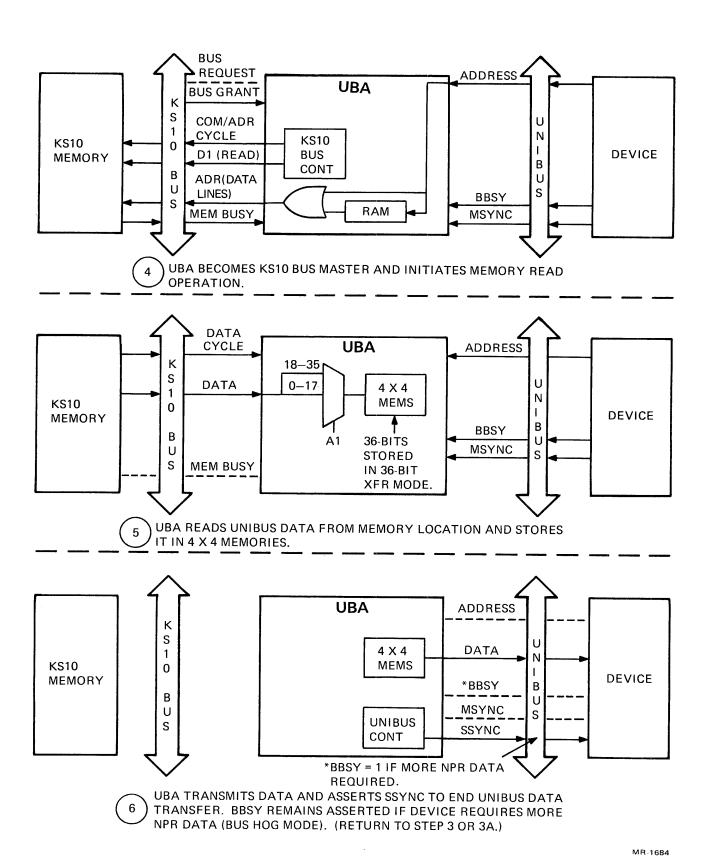

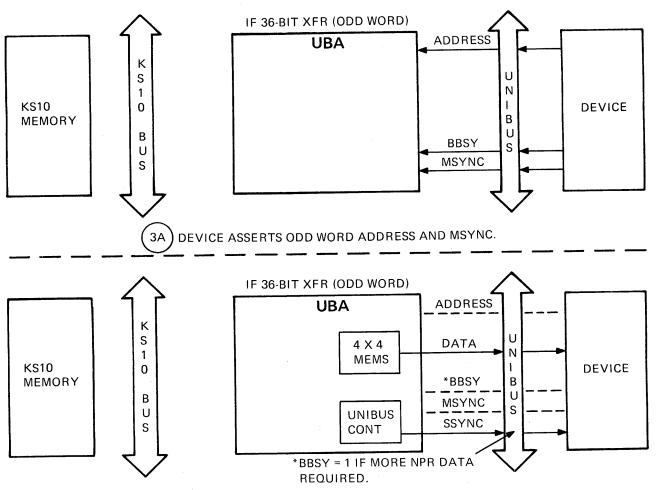

| 5-54 | NPR Read, Bus Dialogue                      | 5-117   |

| 5-55 | I/O Write, Bus Dialogue                     |         |

| 5-56 | I/O Read, Bus Dialogue                      | 5-126   |

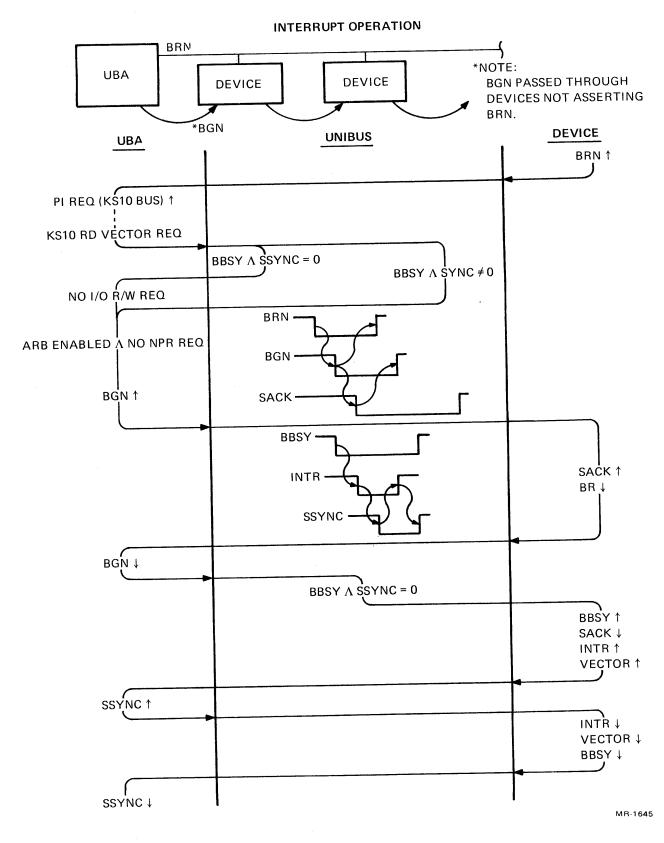

| 5-57 | PI Operation, Bus Dialogue                  | 5-130   |

| 5-58 | KS10 Power System                           | 5-135   |

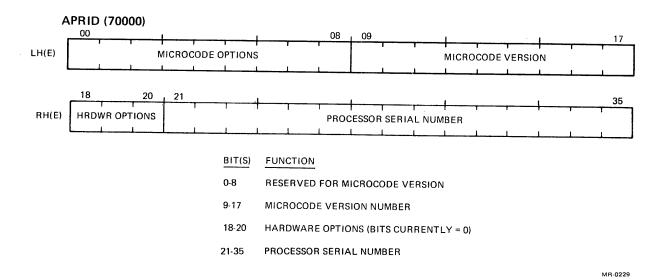

| A-1  | APRID Instruction                           |         |

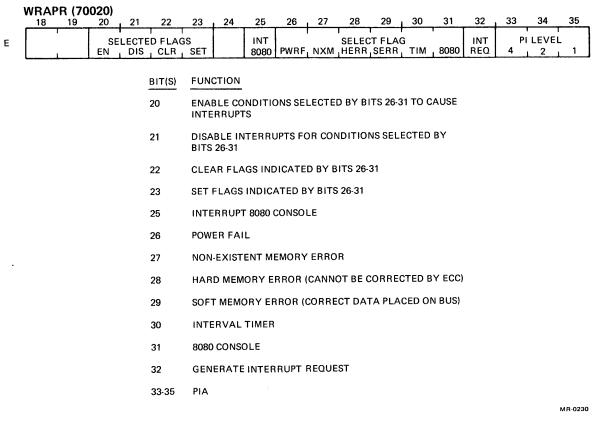

| A-2  | WRAPR Instruction                           |         |

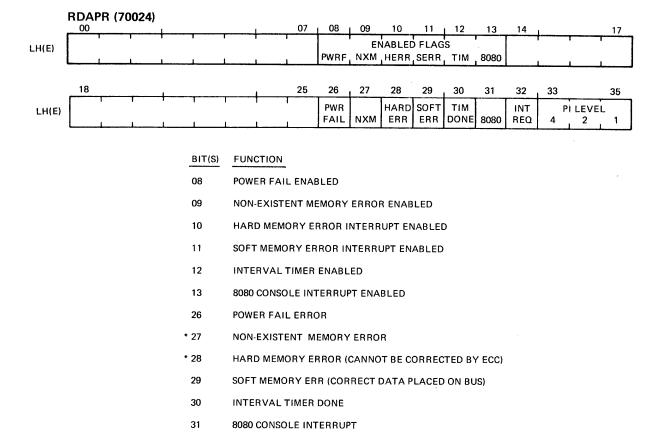

| A-3  | RDAPR Instruction                           |         |

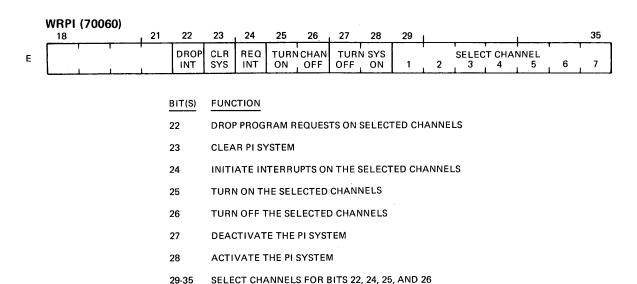

| A-4  | WRPI Instruction                            | A-9     |

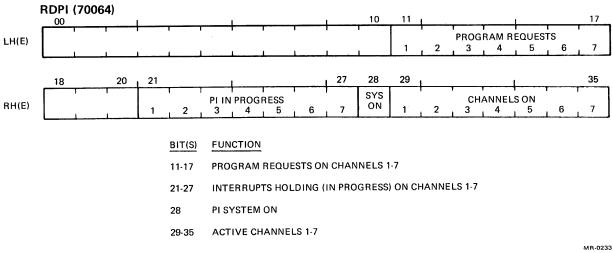

| A-5  | RDPI Instruction                            |         |

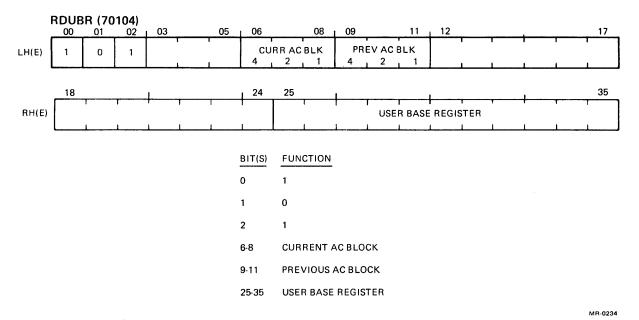

| A-6  | RDUBR Instruction                           | A-10    |

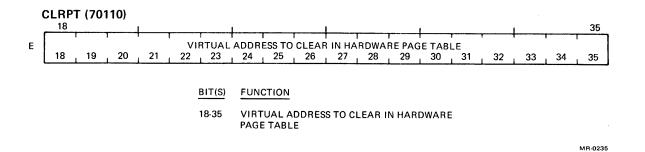

| A-7  | CLRPT Instruction                           | A-10    |

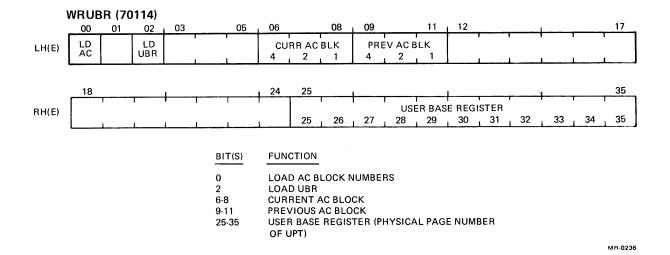

| A-8  | WRUBR Instruction                           |         |

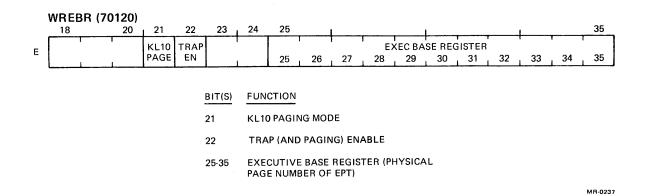

| A-9  | WREBR Instruction.                          |         |

| A-10 | RDEBR Instruction                           |         |

# FIGURES (Cont)

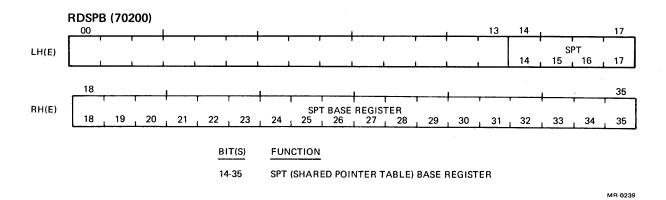

| A-11       | RDSPB Instruction                                     | A-12                      |

|------------|-------------------------------------------------------|---------------------------|

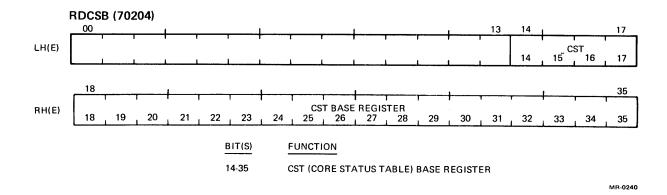

| A-12       | RDCSB Instruction                                     | A-12                      |

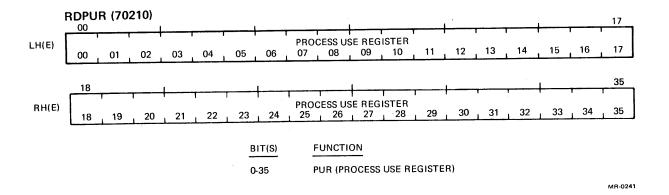

| A-13       | RDPUR Instruction                                     | A-13                      |

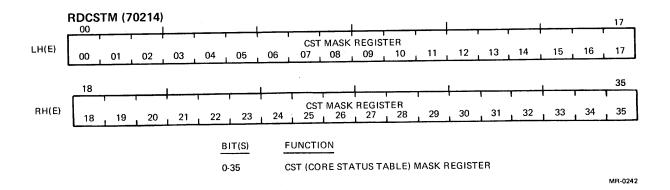

| A-14       | RDCSTM Instruction                                    | A-13                      |

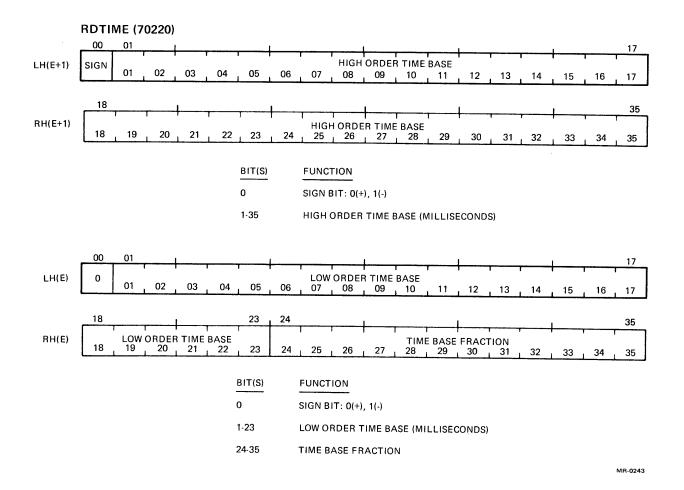

| A-15       | RDTIME Instruction                                    | A-14                      |

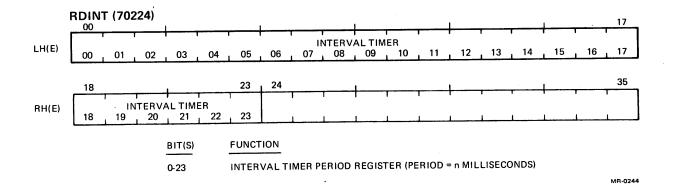

| A-16       | RDINT Instruction                                     | A-15                      |

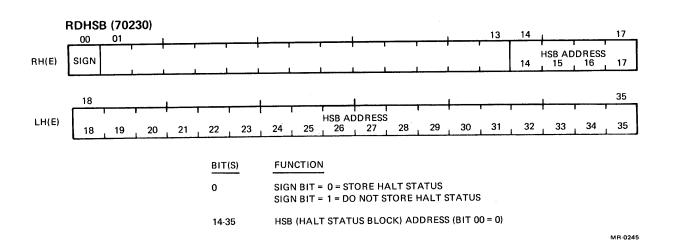

| A-17       | RDHSB Instruction                                     | A-15                      |

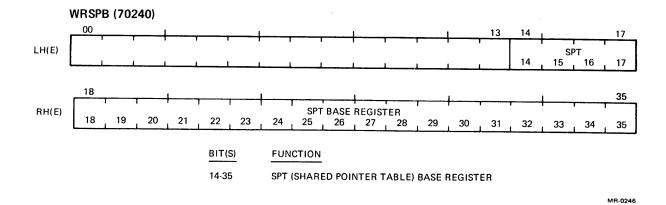

| A-18       | WRSPB Instruction                                     | A-16                      |

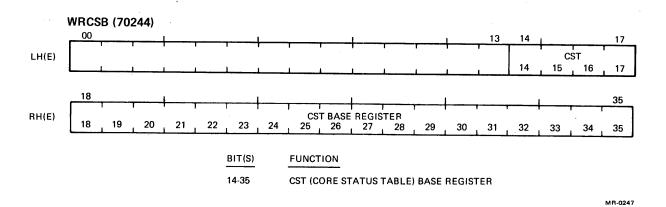

| A-19       | WRCSB Instruction                                     | A-16                      |

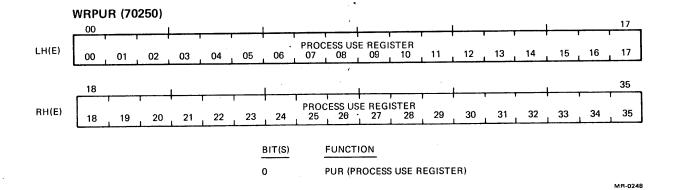

| A-20       | WRPUR Instruction                                     | A-17                      |

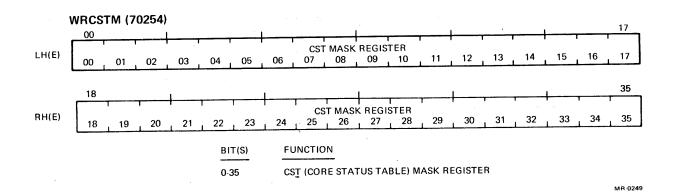

| A-21       | WRCSTM Instruction                                    | A-1/                      |

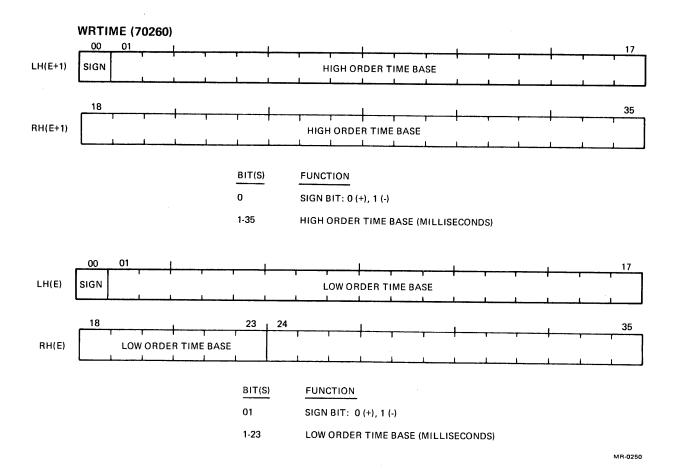

| A-22       | WRTIME Instruction                                    | A-18                      |

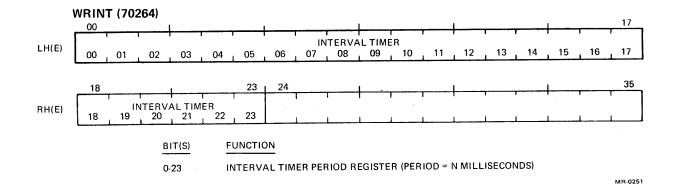

| A-23       | WRINT Instruction                                     | A-19                      |

| A-24       | WRHSB Instruction                                     | A-19                      |

| B-1        | KS10 Unibus Connection                                | B-1                       |

| B-2        | Unibus Interface                                      | B-2                       |

| B-3        | Arbitrator Inputs/Outputs                             | B-4                       |

| B-4        | NPR Priority Transaction                              | B-5                       |

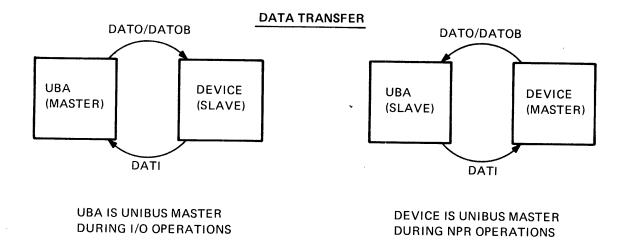

| B-5        | Data Transfer Operation                               | B-6                       |

| B-6        | Interrupt Operation                                   | B-/                       |

| C-1        | Basic Microcode Operation                             |                           |

| Table No.  | TABLES                                                | Page                      |

|            |                                                       | 2.1                       |

| 2-1        | Recommended KS10 System Environmental Specifications  | 2-1                       |

| 2-2        | Massbus Cabling                                       | 2-3                       |

| 2-3        | Device Cabling                                        | 2-3                       |

| 4-1        | KS10 Switch FunctionsKS10 Indicator Functions         | 4-2                       |

| 4-2        | Console Mode Commands                                 | 4-2<br>1 33               |

| 4-3        | 8080 Console Error Messages                           | 4-33<br>1 <sub>-</sub> 40 |

| 4-4<br>4-5 | Other 8080 Console Messages                           | 4-40 A                    |

| 4-3<br>5-1 | KS10 Bus Signal Summary                               | 5-13                      |

| 5-1<br>5-2 | Bus Operations                                        | 5-20                      |

| 5-2<br>5-3 | Selection of Memory and I/O Functions                 | 5-52                      |

| 5-4        | MOS Data Bus Signal Summary                           | 5-61                      |

| 5-5        | Correction Codes                                      | 5-67                      |

| 5-6        | Failure Modes                                         | 5-68                      |

| 5-7        | 8080A State Definitions                               | 5-73                      |

| 5-8        | Console Register Reads and Writes                     | 5-75                      |

| 5-9        | CPU/Bus Control Flip-Flops                            | 5-76                      |

| 5-10       | Control Flip-Flops for CSL Bus Functions              | 5-79                      |

| 5-11       | Error Printouts During System Bootstrap               | 5-94                      |

| 5-12       | Data Path Mixer Selection for NPR Transfers           | 5-122                     |

| A-1        | I/O Instruction Op Codes (Octal)                      | A-2                       |

| A-2        | AC Field Assignments (Octal) for APR I/O Instructions | A-3                       |

| B-1        | Unibus Signal Summary                                 | B-2                       |

| B-2        |                                                       |                           |

|            | I/O (Unibus) Device Vectors and BR Levels             | B-8                       |

| B-3        | I/O (Unibus) Device Vectors and BR Levels             | B-8                       |

### **PREFACE**

This technical manual is designed to support the maintenance and training effort for the volume phase of the DECSYSTEM-2020 project. The first release of the manual supported the field test phase of the project and was for use by Digital Field Service personnel already trained and experienced on KL10-based systems. This revision of the manual contains additional overview material for use in training new-hires and Digital Field Service personnel not experienced on 10/20 systems. Also, some sections in Chapter 5, (the console description, for example) have been expanded at the request of Educational Services and Field Service/Product Support.

Related KS10 documents are as follows.

Title Document No.

KS10-Based DECSYSTEM-2020 Installation Manual KS10 Maintenance Guide, Volume I

EK-0KS10-IN-001 EK-OKS10-MG-001

### 1.1 INTRODUCTION

The KS10 mainframe is the hardware base for the DECSYSTEM-2020, the current low-end member of the DECsystem-10 and DECSYSTEM-20 families of 36-bit computer systems. It contains a microprogrammed central processor unit (CPU) that executes the DEC 10/20 instruction set and supports both the TOPS-10 and TOPS-20 operating systems. It also contains a metal oxide semiconductor (MOS) memory with up to 512K 36-bit word capacity, an 8080A microprocessor console, and various peripheral device controllers depending on the system configuration. (Figure 1-1 shows a typical KS10 system configuration.) Peripherals connecting to the KS10 are selected Unibus and Massbus devices. System minimum/maximum configurations are as follows.

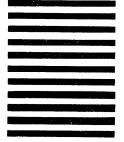

Figure 1-1 Basic KS10 System Configuration

| Unit(s)                                            | Minimum System | Maximum System |

|----------------------------------------------------|----------------|----------------|

| KS10                                               | 1              | 1              |

| Memory (internal to KS10)                          | 128 <b>K</b>   | 512K           |

| RM03/RP06 Disk Drive                               | 1              | 8              |

| TU45 Magnetic Tape Drive                           | 0 (See note)   | 4              |

| LP05/LP14 Line Printer                             | 0              | 1              |

| CR04 Card Reader (Requires DNHXX Expander Cabinet) | 0              | 1              |

| Asynchronous Lines                                 | 8              | 32             |

| Synchronous Lines                                  | 0              | 2              |

# NOTE Systems serviced by DIGITAL require at least one

tape drive to ensure two independent load paths for diagnostics and other system software.

#### 1.2 SYSTEM HARDWARE

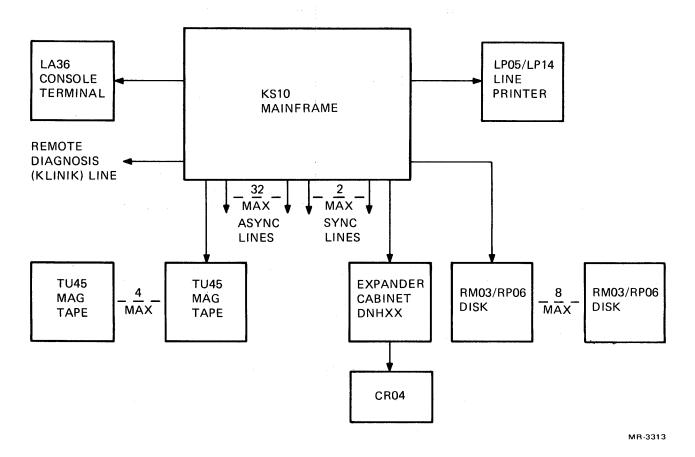

Figure 1-2 shows in detail the typical KS10 system configuration. The diagram indicates quantities and types of system buses and modules for the various mainframe components. The numbers in parentheses are module slot numbers.

The heart of the KS10 is an internal backplane bus called the KS10 bus that provides a control and data path between the processor, memory, console, and peripheral (I/O) devices. It is a multiplexed 2-cycle bus that allows command and address information to be transmitted by one bus device to another during one bus cycle; data is then transferred to/from the addressed device during a following bus cycle.

The KS10 CPU consists of four extended-hex modules: two data path modules (DPE and DPM), and two control-store modules (CRA and CRM). The CPU uses low-power Schottky TTL and the AM2901 4-bit data path slice. Other features include the following.

- A 512-word virtual-address cache memory

- Eight blocks of sixteen fast, general-purpose registers

- Parity checking in control-store, on data paths, and on the backplane bus

- Fast byte operations on 7-bit ASCII characters

- A 2K word (96 bits/word) writable RAM control-store with address provision for 4K words

- A basic microinstruction cycle time of 300 ns

Figure 1-2 Detailed KS10 System Configuration,

The KS10 memory system consists of a single extended-hex control module (MMC) that connects to the backplane bus and from two to eight extended-hex storage array modules (MMAs). Each storage module contains 64K of MOS memory. Memory features include the following.

- $0.9 \mu s$  cycle time

- Single-bit error correction

- Double-bit error detection

- 128K words minimum capacity and up to 512K words maximum capacity

The console consists of a single extended-hex module (CSL) that uses an 8080A microprocessor to perform console and diagnostic functions. Two USART interfaces are provided: one for console (CTY) operation and one for remote (KLINIK) line operation. The KLINIK connection operates in parallel with the CTY to allow diagnosis of the system via a remote link. The console module also contains the system clock and the arbitrator for the KS10 bus.

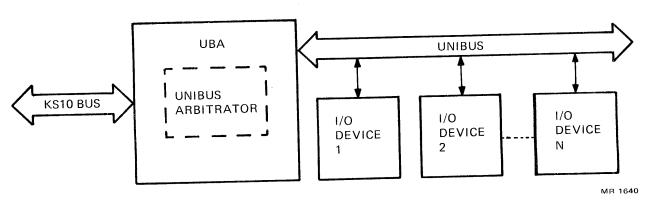

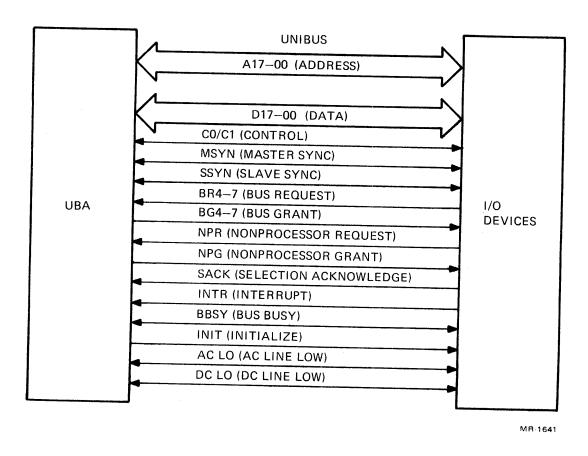

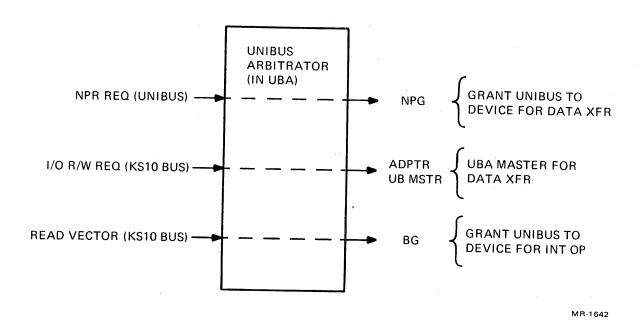

The KS10 I/O devices interface to the system through Unibus adapters (UBAs). Each adapter is a single extended-hex module connecting to both the backplane bus and a Unibus. Up to three UBAs may be installed in the KS10, although two UBAs are standard in the typical KS10 end-user configuration. One UBA and Unibus is reserved for disks only. The second UBA and Unibus is used for all other devices; that is, for tape drives, line printer, card reader, and synchronous and asynchronous communications lines.

Characteristics and features of the I/O devices supported on the KS10 are as follows.

#### **Disk Drives**

### RP06 (RH11 controller)

- Average access time of 36.3 ms

- Average seek time of 28 ms

- Formatted capacity of 176 megabytes

- Maximum data transfer rate of 166K 36-bit words per second

- Sector size of 128 36-bit words

- Removable (20-surface) disk pack

### RM03 (RH11 controller)

- Average access time of 38.3 ms

- Average seek time of 30 ms

- Formatted capacity of 67 megabytes

- Maximum data transfer rate of 250K 36-bit words per second

- Sector size of 128 36-bit words

- Removable (5-surface) disk pack

### Magnetic Tape Drive

#### TU45 (RH11 controller)

- Tape speed of 1.9 meters (75 inches) per second

- Recording density of 32/64 characters per millimeter (800/1600 characters per inch), 9-track format on industry-standard 1/2-inch magnetic tape

- Maximum data transfer rate of 120K characters (bytes) per second

### **Line Printers**

### LP05 (LP20 controller)

- 132 columns

- EDP font, 96 or 64 characters depending on model number (model V or W)

- 230 lines per minute with 96 characters

- 300 lines per minute with 64 characters

### LP14 (LP20 controller)

- 132 columns

- EDP font, 96 or 64 characters operator-selectable

- 650 lines per minute with 96 characters

- 890 lines per minute with 64 characters

#### Card Reader

### CR04 (CD11 controller in DNHXX expander cabinet)

- 285 cards per minute, card hopper capacity of 550 cards (models C, D).

- 1200 cards per minute, card hopper capacity of 2200 cards (models K, L)

### **Synchronous Communications Interface**

- DUP11 controllers (1 per line)

- KMC11 NPR microprocessor (1 per system)

- Bit rate of 2000-19,200 bits per second

- DDCMP data protocol

- Two lines per system maximum

#### **Asynchronous Communications Interface**

- DZ11 controllers (one per eight lines)

- RS-232-C interface standard with baud rates of 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 3600, 4800

- Line units available in 8-line groups: 8, 16, 24, or 32 lines per system

- Character lengths of 5, 6, 7, or 8 bits with 1, 1.5, or 2 stop bits and either odd or even parity

- Carrier, ring, data, terminal ready, and break modem control

- Full duplex

- 64 character silo receive buffer (alarm at 16 characters)

### 1.3 KS10 PHYSICAL DESCRIPTION

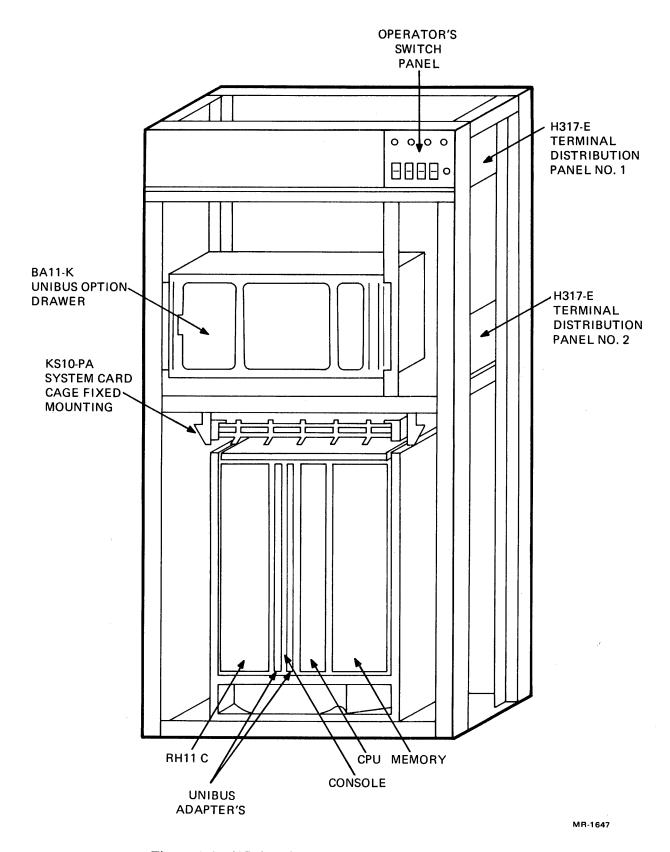

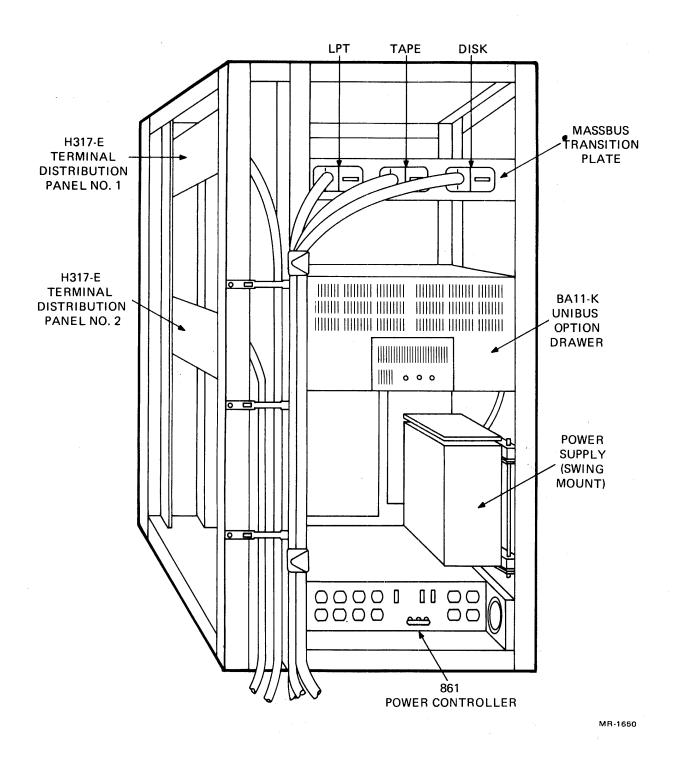

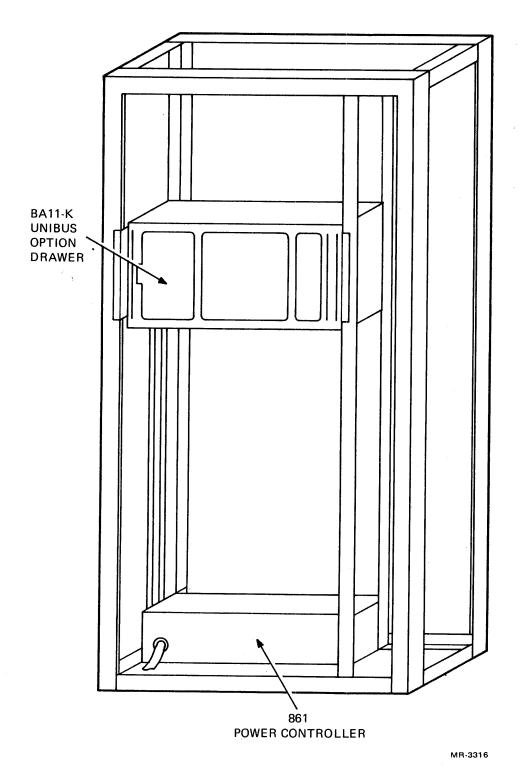

The KS10 is compactly configured in a single-width corporate hiboy cabinet (H9502H-7). This cabinet, shown in Figure 1-3, houses the KS10-PA card cage, BA11-K Unibus option drawer, power system, Massbus transition plate, asynchronous terminal distribution panel, and operator's switch panel.

#### 1.3.1 KS10-PA Card Cage

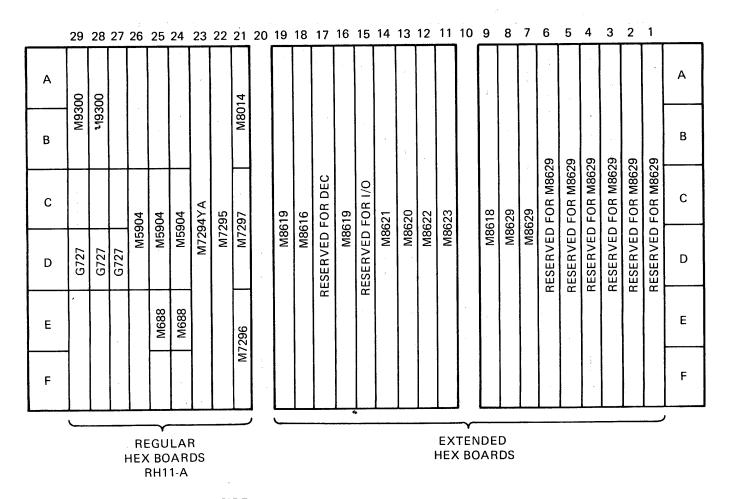

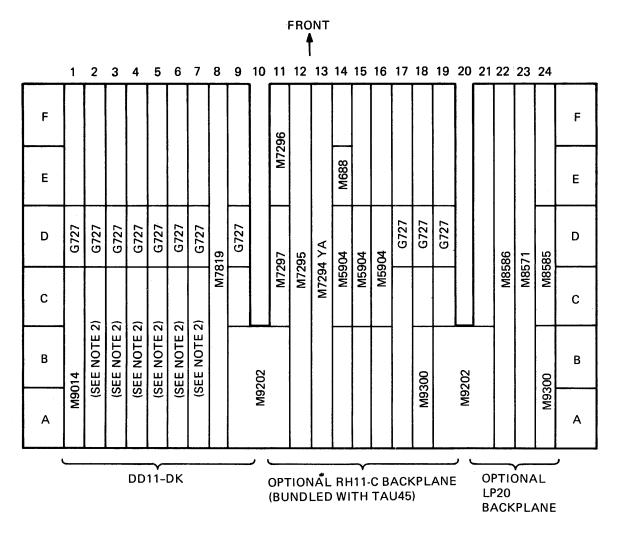

The KS10-PA assembly is a hybrid-style card cage; that is, it contains both extended-hex and standard-hex modules. It is located in the lower front portion of the KS10 cabinet as shown in Figure 1-4. This assembly contains the KS10 CPU, the MOS memory (128K words minimum, 512K words maximum), two Unibus adapters (UBAs), and the RH11 Unibus disk controller. Module utilization is shown in Figure 1-5.

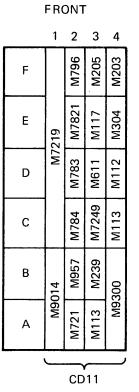

### 1.3.2 BA11-K Unibus Option Drawer

The BA11-K Unibus option drawer (Figure 1-4) contains the KS10 system's I/O peripheral controllers. It has dedicated locations for the following.

- 1. DZ11 asynchronous communications controllers: 1 minimum (8 lines), 4 maximum (32 lines)

- 2. DUP11/KMC11 synchronous communications controller: 0 minimum, 2 DUP11s maximum (2 lines)

- 3. LP20 line printer controller: 0 minimum, 1 maximum

- 4. RH11 magnetic tape system controller: 0 minimum, 1 maximum (This option is bundled into the TAU45 tape system.)

BA11-K module utilization is shown in Figure 1-6.

Figure 1-3 KS10 Cabinet

Figure 1-4 KS10 Cabinet (Front View - Skins Removed)

NOTE: VIEW IS FROM MODULE SIDE

MR-1648

Figure 1-5 KS10-PA Card Cage Module Utilization List (MUL)

#### NOTES:

- 1. VIEW IS FROM MODULE SIDE.

- 2. OPTION VARIATIONS ARE LISTED BELOW.

### **OPTION VARIATIONS**

| SLOTS | ASYNC LINES<br>8–15 | ASYNC LINES<br>16–23 | ASYNC LINES<br>24-32 | SYNC FIRST  | SYNC SECOND |

|-------|---------------------|----------------------|----------------------|-------------|-------------|

| 2     |                     |                      |                      | M8204 KMC11 |             |

| 3     |                     |                      |                      |             | M7867 DUP11 |

| 4     |                     |                      |                      | M7867 DUP11 |             |

| 5     |                     |                      | M7819 DZ11           |             |             |

| 6     | (M7819 DZ11)        | M7819 DZ11           |                      |             |             |

| 7     | M7819 DZ11          |                      |                      |             |             |

3. M7819 FOR ASYNC LINES 8–15 IS INSTALLED IN SLOT 6 WHEN CONFIGURATION EQUALS 0–23 LINES.

MR-3315

Figure 1-6 BA11-K Drawer (KS10 Cabinet) MUL

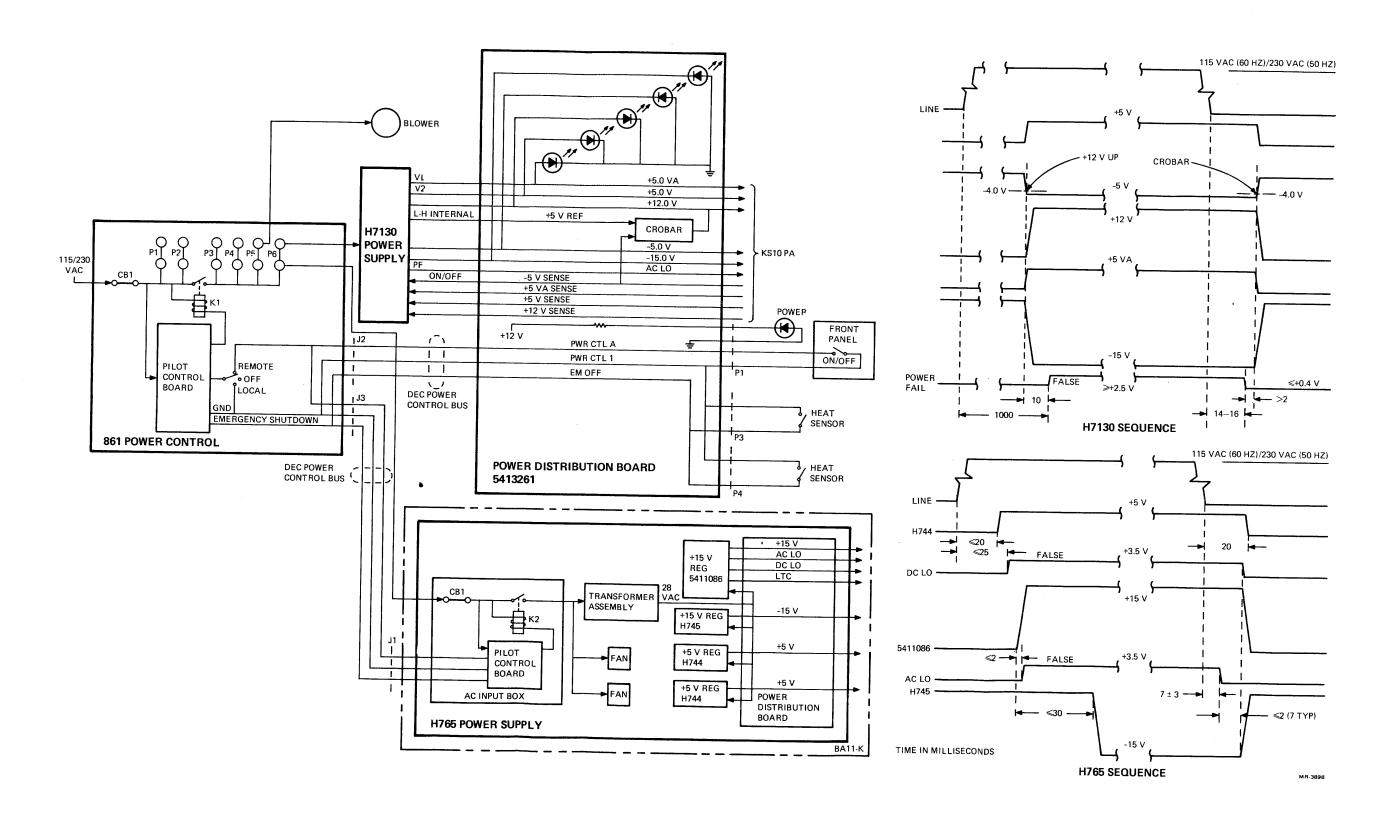

### 1.3.3 Power System

The major components in the KS10 power system are the 861 power control for ac power distribution, the LH switcher power supply for powering the KS10-PA, and the H765 switcher power supply for powering the BA11-K. Component designations for 60 Hz and 50 Hz machines are as follows.

KS10-AA (115 V, 60 Hz)

KS10-AB (230 V, 50 Hz)

861C LH Power Supply (H7130C) H765A (powers BA11-K) 861B LH Power Supply (H7130D) H765B (powers BA11-K)

# NOTE TO DIGITAL IN-HOUSE FIELD SERVICE PERSONNEL

Some in-house KS10 systems contain the H7130A (60 Hz) and H7130B (50 Hz) power supplies. Although input and output power specifications for these A and B (blue) models are the same as for the C and D (silver) models that are installed in other machines, there are differences in power harness wiring. When replacing a power supply, always install the same color as was removed.

#### 1.3.4 Massbus Transition Plate

The Massbus transition plate is located at the top of the KS10 cabinet as shown in Figure 1-7. It is a connection plate that holds three Massbus connectors plus two 25-pin communications cable connectors. The Massbus connectors are allocated from right to left as follows.

- 1. Disk Massbus

- 2. Tape Massbus

- 3. Line printer Massbus

The two communication cable connectors are allocated as follows.

- 1. CTY (BC03L to BC03M)

- 2. KLINIK remote maintenance port (BC03L to BC05D)

### 1.3.5 Asynchronous Terminal Distribution Panel (H317-E)

The KS10 is configured with a minimum of one H317-E (up to 16 lines) and a maximum of two H317-Es (32 lines). It is configured with EIA communication only.

### Minimum Configuration

Lines 0-7:

One DZ11 module (8-line multiplexer) One H317-E terminal distribution panel One BC05W-8 cable

Figure 1-7 KS10 Cabinet (Rear View - Skins Removed)

### **Optional Expansion**

Lines 8-15 (defined as a DZ11BA):

One DZ11 module (8-line multiplexer) One BC05W-8 cable

Lines 16-23 (defined as a DZ11AA):

One DZ11 module (8-line multiplexer) One BC05W-8 cable One H317-E terminal distribution panel

Lines 24-32 (defined as a DZ11BA):

One DZ11 module (8-line multiplexer) One BC05W-8 cable

1.3.6 Operator's Switch Panel

The operator's switch panel is located at the top front in the KS10 cabinet (Figure 1-3). Switch and indicator functions are described in Paragraph 4.1.

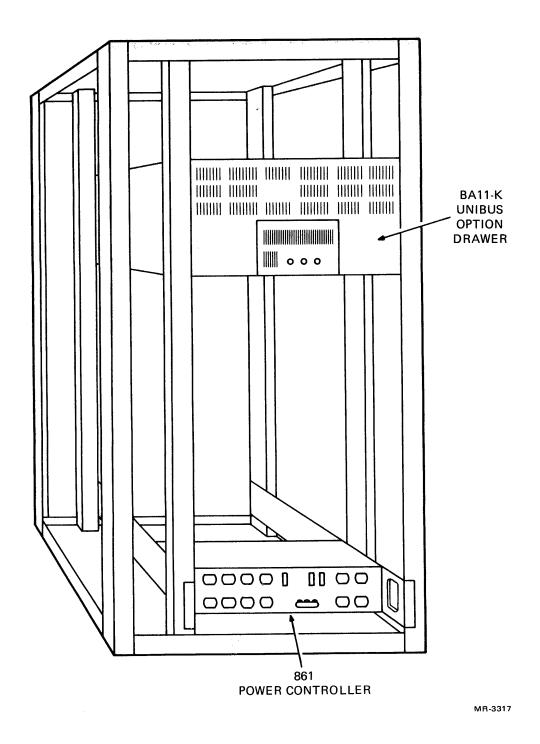

1.4 DNHXX PHYSICAL DESCRIPTION

The DNHXX expander cabinet is required to house the CD11 card reader controller when a CR04 card reader is installed on a KS10 system. Like the KS10 cabinet, it is a single-width corporate hi-boy cabinet (H9502H-7). It contains only a BA11-K drawer and an 861 power controller, however. (Component locations are shown in Figures 1-8 and 1-9.) The BA11-K holds just the CD11 on standard enduser systems. (Module utilization is shown in Figure 1-10.) Power system component designations for the 60 Hz and 50 Hz machines are as follows.

| DNHXX-AA (120 V, 60 Hz) | DNHXX-AB (230 V, 50 Hz) |  |

|-------------------------|-------------------------|--|

| 861C                    | 861B                    |  |

| H765A (powers BA11-K)   | H765B (powers BA11-K)   |  |

Figure 1-8 DNHXX Cabinet (Front View - Skins Removed)

Figure 1-9 DNHXX Cabinet (Rear View - Skins Removed)

NOTE: VIEW IS FROM MODULE SIDE. MR-3318

Figure 1-10 BA11-K Drawer (DNHXX Cabinet) MUL

# CHAPTER 2 SITE PREPARATION AND PLANNING

### 2.1 SITE PLANNING

Refer to Chapter 1 (Paragraphs 1.1-1.5) of the *DECSYSTEM-20 Site Preparation Guide* (EK-DEC20-SP) for the following information.

- Schedule of site preparation prior to system delivery

- Summary of site preparation functions and responsibilities

- Site consideration and selection

- Building requirements

### 2.2 ENVIRONMENTAL REQUIREMENTS

The environmental specifications for DECSYSTEM-20 systems (including KS10 systems) are listed in Table 2-1. The environmental specifications for individual KS10 system components are on data sheets at the end of this chapter. Heat dissipation and air flow rate of internal fans are also given. To estimate cooling and other environmental requirements, refer to Paragraph 1.6 of the DECSYSTEM-20 Site Preparation Guide.

Table 2-1 Recommended KS10 System Environmental Specifications

| Parameter                  | Specification                                                |

|----------------------------|--------------------------------------------------------------|

| Temperature                | 18° C to 24° C (65° F to 75° F)                              |

| Humidity                   | 40% to 60%                                                   |

| Temperature Rate of Change | 2° C/h (3.6° F/h)                                            |

| Humidity Rate of Change    | 2%/h                                                         |

| Voltage Tolerance          | 120/208 V ± 10% for single phase/<br>three phase (60 Hz)     |

|                            | 240/380 V $\pm$ 10% for single phase/<br>three phase (50 Hz) |

| Frequency Tolerance        | 60 Hz ± 1 Hz<br>50 Hz + 1 Hz                                 |

### NOTE

Compliance to the environmental specifications above may be required if the system is under a DIGITAL Maintenance Agreement.

### 2.3 SYSTEM CABLING

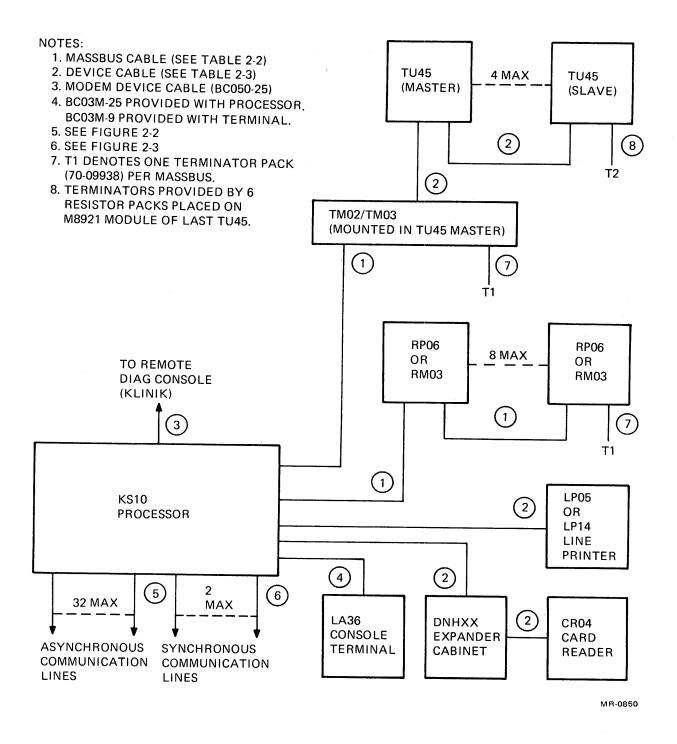

Figure 2-1 shows cabling for a typical KS10 system configuration. Reference is made on the figure to Tables 2-2 and 2-3, which provide Massbus and device cable data, and to Figures 2-2 and 2-3, which show interconnections of the asynchronous and synchronous communications lines.

Figure 2-1 Typical KS10 System Configuration

Table 2-2 Massbus Cabling

|      |           |                               | Available Length |       |

|------|-----------|-------------------------------|------------------|-------|

| From | То        | Cable*                        | Meters           | Feet  |

| CPU  | R P06     | BC06S (AMP ZIF to<br>AMP ZIF) | 4.5              | 15    |

| CPU  | RM03      | BC06S (AMP ZIF to<br>AMP ZIF) | 7.5              | 25    |

| RP06 | R P06     | BC06S (AMP ZIF to<br>AMP ZIF) | 0.6/0.75         | 2/2.5 |

| RM03 | RM03      | BC06S (AMP ZIF to<br>AMP ZIF) | 4.5              | 15    |

| RP06 | RM03      | BC06S (AMP ZIF to<br>AMP ZIF) | 4.5              | 15    |

| CPU  | TM02/TM03 | BC06S (AMP ZIF to<br>AMP ZIF) | 4.5              | 15    |

|      |           |                               | 7.5              | 25†   |

<sup>\*</sup>ZIF = zero insertion force

Table 2-3 Device Cabling

|               |           |                                                | Available L | ength      |

|---------------|-----------|------------------------------------------------|-------------|------------|

| From          | То        | Cable                                          | Meters      | Feet       |

| CPU           | LP05/LP14 | 7011426 (AMP ZIF to<br>Winchester)             | 7.5*<br>30  | 25*<br>100 |

| CPU           | DNHXX     | BC11A (M9014 to M9014)                         | 3.9         | 13         |

| DNHXX         | CR04      | 7008764 (AMP to M957)                          | 7.5         | 25         |

| TM02/<br>TM03 | TU45      | BC06R (BERG to<br>BERG – cabled<br>internally) | 3           | 10         |

| TU45          | TU45      | BC06R (BERG to BERG)                           | 3           | 10         |

<sup>\*</sup>The 7.5 m (25 ft) 7011426 cable is the standard length that will be provided if no cable information is provided 60 days prior to scheduled shipment.

<sup>†</sup> A 7.5 m (25 ft) BC06S cable is provided with the DNHXX to allow reconfiguration of the TU45A-E (master) drive. Reconfiguration may be necessary because the DNHXX must be installed adjacent to the KS10 cabinet.

Figure 2-2 KS10 Asynchronous Communications Lines

Figure 2-3 KS10 Synchronous Communications Lines

### 2.4 PRIMARY POWER (AC)

Primary power specifications for KS10 system components are provided on data sheets at the end of this chapter. Refer to Chapter 1 (Paragraphs 1.7-1.8) of the DECSYSTEM-20 Site Preparation Guide for the following information.

- Definition of data sheet parameters (surge current, leakage current, etc.)

- Description of power regulation systems

- Phase balancing, grounding, and service outlet requirements

- Description of receptacles and plugs specified (on data sheets) for KS10 system components

### 2.5 OPTION DATA SHEETS

Option data sheets for the various KS10 system components are contained in this section. They are arranged in alphanumeric sequence by device designations as follows.

CR04-C/D CR04-K/L DNHXX-AA/AB KS10-AA/AB Processor LA36 LP05-V/W LP14-C/D RM03 RP06-A/B TU45A-E (Master) TU45A-E (Slave)

### CR04-C/D

### MECHANICAL

| Mounting<br>Code | Weight         | Height         | Width          | Depth            | Cab Type If Used | Skid<br>Type |

|------------------|----------------|----------------|----------------|------------------|------------------|--------------|

| TT               | 27 kg<br>60 lb | 28 cm<br>11 in | 49 cm<br>19 in | 35.5 cm<br>14 in | VE               | N/A          |

### POWER (AC)

| A<br>Low | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State<br>Current (RMS) | Surge<br>Current | Surge<br>Duration |

|----------|---------|------------|------------------------|----------|-------------------------------|------------------|-------------------|

| 104      | 120     | 127        | 60 Hz ± 1              | 1        | 5 A                           | 13 A             | 6 s               |

| 208      | 230     | 254        | 50 Hz ± 1              | 1        | 2.5 A                         | 6.5 A            | 6 s               |

### POWER (AC)

| Interrupt Tolerance (Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------|------------------------------|-------|------|--------------------|--------------------------|-----------------------------|

| 5 ms                      | 439 kg-cal/hr<br>1740 Btu/hr | 510   | 0.60 | 2.7 m<br>9.0 ft    | NEMA 5-15P<br>NEMA 6-15P | 0.545 mA                    |

### **ENVIRONMENTAL (DEVICE)**

| Temperature                  |                              | Relative Humidity |         | Rate of Change      |             | Air Volume                        |

|------------------------------|------------------------------|-------------------|---------|---------------------|-------------|-----------------------------------|

| Operating                    | Storage                      | Operating         | Storage | Temp                | Rel. Humid. | Inlet                             |

| 15° to 32° C<br>59° to 90° F | 5° to 50° C<br>40° to 120° F |                   | 0 - 95% | 7° C/hr<br>12° F/hr | 2%/hr       | 75 ft <sup>3</sup> /min<br>(rear) |

### **ENVIRONMENTAL (MEDIA)**

| Temp                         | erature                      | Relative Humidity |         | Rate o              | f Change    |

|------------------------------|------------------------------|-------------------|---------|---------------------|-------------|

| Operating                    | Storage                      | Operating         | Storage | Temp                | Rel. Humid. |

| 15° to 32° C<br>59° to 90° F | 4° to 49° C<br>40° to 120° F | 20-80%            | 0-95%   | 7° C/hr<br>12° F/hr | 2%/hr       |

| Γ | Memory | I/O Bus | Massbus | Device         | Other |

|---|--------|---------|---------|----------------|-------|

|   | N/A    | N/A     | N/A     | 7.5 m<br>25 ft | N/A   |

# CR04-K/L

### **MECHANICAL**

| Mounting<br>Code | Weight          | Height          | Width          | Depth           | Cab Type<br>If Used | Skid<br>Type |

|------------------|-----------------|-----------------|----------------|-----------------|---------------------|--------------|

| FS               | 91 kg<br>200 lb | 102 cm<br>40 in | 64 cm<br>25 in | 102 cm<br>40 in | VE                  | N/A          |

### POWER (AC)

| А          | C Volta    | ge         | Frequency              |          | Steady State   | Surge          | Surge      |

|------------|------------|------------|------------------------|----------|----------------|----------------|------------|

| Low        | Nom        | High       | Tolerance              | Phase(s) | Current (RMS)  | Current        | Duration   |

| 104<br>208 | 120<br>230 | 127<br>254 | 60 Hz ± 1<br>50 Hz ± 1 | 1<br>1   | 9.0 A<br>4.5 A | 25 A<br>12.5 A | 6 s<br>6 s |

### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|-----|--------------------|--------------------------|-----------------------------|

| .5 ms                           | 473 kg.cal/hr<br>1877 Btu/hr | 550   | 1.1 | 4.5 m<br>15 ft     | NEMA 5-15P<br>NEMA 6-15P | 0.655 mA                    |

### **ENVIRONMENTAL (DEVICE)**

| Temp                         | erature                      | Relative I | Humidity | Rate o              | f Change    | Air Volume                         |

|------------------------------|------------------------------|------------|----------|---------------------|-------------|------------------------------------|

| Operating                    | Storage                      | Operating  | Storage  | Temp                | Rel. Humid. | Inlet                              |

| 15° to 32° C<br>59° to 90° F | 5° to 50° C<br>40° to 120° F | 20 - 80%   | 0 - 95%  | 7° C/hr<br>12° F/hr | 2%/hr       | 150 ft <sup>3</sup> /min<br>(Rear) |

### **ENVIRONMENTAL (MEDIA)**

| Temperature                  |                              | Relative  | Humidity | Rate of Change      |             |

|------------------------------|------------------------------|-----------|----------|---------------------|-------------|

| Operating                    | Storage                      | Operating | Storage  | Temp                | Rel. Humid. |

| 15° to 32° C<br>59° to 90° F | 4° to 49° C<br>40° to 120° F | 20 - 80%  | 0 - 95%  | 7° C/hr<br>12° F/hr | 2%/hr       |

| Memory | I/O Bus | Massbus | Device         | Other |

|--------|---------|---------|----------------|-------|

| N/A    | N/A     | N/A     | 7.5 m<br>25 ft | N/A   |

### DNHXX-AA/AB

### MECHANICAL

| Mounting<br>Code | Weight           | Height          | Width          | Depth          | Cab Type<br>If Used | Skid<br>Type |

|------------------|------------------|-----------------|----------------|----------------|---------------------|--------------|

| FS               | 181 kg<br>400 lb | 152 cm<br>60 in | 69 cm<br>27 in | 76 cm<br>30 in | H9502H-7            | N/A          |

### POWER (AC)

| Low | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State<br>Current (CRMS) | Surge<br>Current | Surge<br>Duration |

|-----|---------|------------|------------------------|----------|--------------------------------|------------------|-------------------|

| 104 | 120     | 127        | 60 Hz ± 1              | 1        | 1.3 A                          | 3.3 A            | 6 cycles          |

| 208 | 230     | 254        | 50 Hz ± 1              | 1        | 0.65 A                         | 1.7 A            | 6 cycles          |

### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation         | Watts | KVA   | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type   | Leakage<br>Current<br>(Max) |

|---------------------------------|-----------------------------|-------|-------|--------------------|----------------------------|-----------------------------|

| 16 ms                           | 121 kg·cal/hr<br>480 Btu/hr | 140.5 | 0.156 | 4.5 m<br>15 ft     | NEMA L5-30P<br>NEMA L6-20P | 1.15 mA                     |

### ENVIRONMENTAL (DEVICE)

| Temp      | erature                        | Relative  | Relative Humidity |                     | f Change    | Air Volume               |  |

|-----------|--------------------------------|-----------|-------------------|---------------------|-------------|--------------------------|--|

| Operating | Storage                        | Operating | Storage           | Temp                | Rel. Humid. | Inlet                    |  |

|           | -40° to 66° C<br>-40° to 151°F |           | 0 – 95%           | 7° C/hr<br>12° F/hr | 2%/hr       | 500 ft <sup>3</sup> /min |  |

### **ENVIRONMENTAL (MEDIA)**

| Tempe     | rature  | Relative Humidity |         | Rate of Change |             |

|-----------|---------|-------------------|---------|----------------|-------------|

| Operating | Storage | Operating         | Storage | Temp           | Rel. Humid. |

| N/A       | N/A     | N/A               | N/A     | N/A            | N/A         |

| Memory | I/O Bus | Massbus       | Device        | Other |

|--------|---------|---------------|---------------|-------|

| N/A    | N/A     | See Table 2-2 | See Table 2-3 | N/A   |

# KS10-AA/AB Processor

### **MECHANICAL**

| Mounting<br>Code | Weight           | Height          | Width          | Depth          | Cab Type<br>If Used | Skid<br>Type |

|------------------|------------------|-----------------|----------------|----------------|---------------------|--------------|

| FS               | 267 kg<br>590 lb | 152 cm<br>60 in | 69 cm<br>27 in | 76 cm<br>30 in | H9502H-7            | N/A          |

### POWER (AC)

| А          | C Volta    | ge         | Frequency              |          | Steady State     | Surge            | Surge                |

|------------|------------|------------|------------------------|----------|------------------|------------------|----------------------|

| Low        | Nom        | High       | Tolerance              | Phase(s) | Current (RMS)    | Current *        | Duration             |

| 104<br>208 | 120<br>230 | 127<br>254 | 60 Hz ± 1<br>50 Hz ± 1 | 1<br>1   | 9.90 A<br>4.95 A | 25.0 A<br>12.5 A | 6 cycles<br>6 cycles |

### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type   | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|------|--------------------|----------------------------|-----------------------------|

| 16 ms                           | 920 kg•cal/hr<br>3652 Btu/hr | 1070  | 1.18 | 4.5 m<br>15 ft     | NEMA L5-30P<br>NEMA L6-20P | 4.93 mA                     |

### **ENVIRONMENTAL (DEVICE)**

| Temp                         | erature                         | Relative I | Humidity | Rate of Change      |             | Air Volume                |  |

|------------------------------|---------------------------------|------------|----------|---------------------|-------------|---------------------------|--|

| Operating                    | Storage                         | Operating  | Storage  | Temp                | Rel. Humid. | Inlet                     |  |

| 15° to 32° C<br>59° to 90° F | -40° to 66° C<br>-40° to 151° F | 20-80%     | 0-95%    | 7° C/hr<br>12° F/hr | 2%/hr       | 1100 ft <sup>3</sup> /min |  |

### **ENVIRONMENTAL (MEDIA)**

| Temperature |         | Relative  | Humidity | Rate of Change |             |  |

|-------------|---------|-----------|----------|----------------|-------------|--|

| Operating   | Storage | Operating | Storage  | Temp           | Rel. Humid. |  |

| N/A         | N/A     | N/A       | N/A      | N/A            | N/A         |  |

|             |         |           | ·        | ,              |             |  |

| Memory | I/O Bus | Massbus       | Device        | Other          |

|--------|---------|---------------|---------------|----------------|

| N/A    | N/A     | See Table 2-2 | See Table 2-3 | N/A (internal) |

### LA36

### MECHANICAL

| Mounting<br>Code | Weight          | Height           | Width            | Depth          | Cab Type If Used | Skid<br>Type                        |

|------------------|-----------------|------------------|------------------|----------------|------------------|-------------------------------------|

| FS               | 46 kg<br>102 lb | 85 cm<br>33.5 in | 70 cm<br>27.5 in | 61 cm<br>24 in | VE               | 86.4 cm X 128.3 cm<br>34" X 50-1/2" |

### POWER (AC)

| AC Voltage |            | Frequency  |                        | Steady State | Surge          | Surge        |            |

|------------|------------|------------|------------------------|--------------|----------------|--------------|------------|

| Low        | Nom        | High       | Tolerance              | Phase(s)     | Current (RMS)  | Current      | Duration   |

| 90<br>180  | 120<br>230 | 132<br>264 | 60 Hz ± 1<br>50 Hz ± 1 | 1<br>1       | 2.0 A<br>1.0 A | 30 A<br>15 A | 1 s<br>1 s |

### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation         | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|-----------------------------|-------|------|--------------------|--------------------------|-----------------------------|

|                                 | 175 kg·cal/hr<br>696 Btu/hr | 204   | 0.24 | 2.4 m<br>8 ft      | NEMA 5-15P<br>NEMA 6-15P | 0.107 mA                    |

### **ENVIRONMENTAL (DEVICE)**

| Temperature Operating Storage |                                | Relative<br>Operating | Humidity<br>Storage | Rate o              | f Change<br>Rel. Humid. | Air Volume<br>Inlet      |

|-------------------------------|--------------------------------|-----------------------|---------------------|---------------------|-------------------------|--------------------------|

| 10° to 40° C                  | -40° to 66° C<br>-40° to 151°F |                       | 0 - 95%             | 7° C/hr<br>12° F/hr | 2%/hr                   | 100 ft <sup>3</sup> /min |

### **ENVIRONMENTAL (MEDIA)**

| Temperature                  |                              | Relative  | Humidity | Rate of Change |             |

|------------------------------|------------------------------|-----------|----------|----------------|-------------|

| Operating                    | Storage                      | Operating | Storage  | Temp           | Rel. Humid. |

| 15° to 32° C<br>59° to 90° F | 15° to 32° C<br>59° to 90° F | 20 - 80%  | 20 - 80% |                |             |

| Memory | I/O Bus | Massbus | Device*     | Other |

|--------|---------|---------|-------------|-------|

|        |         | N1/A    | 3 m<br>9 ft | N/A   |

| N/A    | N/A     | N/A     | 911         | IN/ A |

<sup>\*3</sup> m (9 ft) for EIA Interface 5 m (15 ft) for 20 mA Loop

# **LP05-V/W**

#### **MECHANICAL**

| Mounting<br>Code | Weight           | Height            | Width          | Depth          | Cab Type If Used | Skid<br>Type                        |

|------------------|------------------|-------------------|----------------|----------------|------------------|-------------------------------------|

| FS               | 155 kg<br>340 lb | 113 cm<br>44.5 in | 84 cm<br>33 in | 66 cm<br>26 in | VE               | 84 cm X 103 cm<br>33 in X 40-1/2 in |

#### POWER (AC)

| А          | C Volta    | ge         | Frequency              |          | Steady State   | Surge       | Surge      |

|------------|------------|------------|------------------------|----------|----------------|-------------|------------|

| Low        | Nom        | High       | Tolerance              | Phase(s) | Current (RMS)  | Current     | Duration   |

| 104<br>208 | 120<br>230 | 127<br>254 | 60 Hz ± 1<br>50 Hz ± 1 | 1        | 4.5 A<br>2.3 A | 10 A<br>5 A | 2 s<br>2 s |

#### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|------|--------------------|--------------------------|-----------------------------|

| 5 ms                            | 395 kg·cal/hr<br>1570 Btu/hr | 460   | 0.54 | 2.7 m<br>9 ft      | NEMA 5-15P<br>NEMA 6-15P | 0.55 mA                     |

#### **ENVIRONMENTAL (DEVICE)**

| Temperature                   |                               | Relative Humidity |         | Rate of Change      |             | Air Volume              |

|-------------------------------|-------------------------------|-------------------|---------|---------------------|-------------|-------------------------|

| Operating                     | Storage                       | Operating         | Storage | Temp                | Rel. Humid. | Inlet                   |

| 10° to 38° C<br>50° to 100° F | -18° to 66° C<br>0° to 150° F | 20–80%            | 0–95%   | 7° C/hr<br>12° F/hr | 2%/hr       | 300 ft <sup>3</sup> /hr |

#### **ENVIRONMENTAL (MEDIA)**

| Temperature                   |                               | Relative  | Humidity | Rate of Change      |             |

|-------------------------------|-------------------------------|-----------|----------|---------------------|-------------|

| Operating                     | Storage                       | Operating | Storage  | Temp                | Rel. Humid. |

| 10° to 38° C<br>50° to 100° F | -18° to 66° C<br>0° to 150° F | 20-80%    | 0-95%    | 7° C/hr<br>12° F/hr | 2%/hr       |

| Memory | I/O Bus | Massbus | Device         | Other |

|--------|---------|---------|----------------|-------|

| N/A    | N/A     | N/A     | 30 m<br>100 ft | N/A   |

# LP14-C/D

#### **MECHANICAL**

| Mounting<br>Code | Weight           | Height          | Width          | Depth          | Cab Type<br>If Used | Skid<br>Type                            |

|------------------|------------------|-----------------|----------------|----------------|---------------------|-----------------------------------------|

| VE               | 198 kg<br>435 lb | 114 cm<br>45 in | 84 cm<br>33 in | 70 cm<br>27 in | VE                  | 86.4 cm X 128.3 cm<br>34 in X 50-1/2 in |

#### POWER (AC)

| А   | AC Voltage Frequency |      |           | Steady State | Surge         | Surge   |          |

|-----|----------------------|------|-----------|--------------|---------------|---------|----------|

| Low | Nom                  | High | Tolerance | Phase(s)     | Current (RMS) | Current | Duration |

| 104 | 120                  | 127  | 60 Hz ± 1 | 1            | 7 A           | 140 A   | 2 s      |

| 208 | 230                  | 254  | 50 Hz ± 1 | 1            | 3.5 A         | 70 A    | 2 s      |

#### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|------|--------------------|--------------------------|-----------------------------|

| 5 ms                            | 670 kg-cal/hr<br>2662 Btu/hr | 780   | 0.84 | 3.7 m<br>12 ft     | NEMA 5-15P<br>NEMA 6-15P | 0.394 mA                    |

#### **ENVIRONMENTAL (DEVICE)**

| Temp<br>Operating             | erature<br>Storage            | Relative Operating | Humidity<br>Storage | Rate o              | f Change<br>Rel. Humid. | Air Volume<br>Inlet      |

|-------------------------------|-------------------------------|--------------------|---------------------|---------------------|-------------------------|--------------------------|

| 10° to 38° C<br>50° to 100° F | -18° to 66° C<br>0° to 150° F | 20-80%             | 0–95%               | 7° C/hr<br>12° F/hr | 2%/hr                   | 300 ft <sup>3</sup> /min |

#### **ENVIRONMENTAL (MEDIA)**

| Temperature                   |                               | Relative  | Humidity | Rate of Change      |             |  |

|-------------------------------|-------------------------------|-----------|----------|---------------------|-------------|--|

| Operating                     | Storage                       | Operating | Storage  | Temp                | Rel. Humid. |  |

| 10° to 38° C<br>50° to 100° F | -18° to 66° C<br>0° to 150° F | 2080%     | 0-95%    | 7° C/hr<br>12° F/hr | 2%/hr       |  |

| Memory | I/O Bus | Massbus | Device         | Other |

|--------|---------|---------|----------------|-------|

| N/A    | N/A     | N/A     | 30 m<br>100 ft | N/A   |

### **RM03**

#### MECHANICAL

| Mounting<br>Code | Weight           | Height         | Width          | Depth          | Cab Type<br>If Used | Skid<br>Type |

|------------------|------------------|----------------|----------------|----------------|---------------------|--------------|

| FS               | 195 kg<br>430 lb | 99 cm<br>39 in | 56 cm<br>22 in | 79 cm<br>31 in | H9691<br>(modified) |              |

#### POWER (AC)

| Low | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State<br>Current (CRMS) | Surge<br>Current | Surge<br>Duration |

|-----|---------|------------|------------------------|----------|--------------------------------|------------------|-------------------|

| 102 | 120     | 128        | 60 Hz ± 1              | 1        | 7.0 A                          | 30 A             | 14 s              |

| 213 | 230     | 257        | 50 Hz ± 1              |          | 3.5 A                          | 15 A             | 14 s              |

#### POWER (AC)

| Interrupt Tolerance (Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------|------------------------------|-------|------|--------------------|--------------------------|-----------------------------|

| 8 ms                      | 614 kg·cal/hr<br>2436 Btu/hr | 714   | 0.84 | 1.8 m<br>6 ft      | NEMA 5-15P<br>NEMA 6-15P | 1.218 mA                    |

#### ENVIRONMENTAL (DEVICE)

| Temperature |                               | Relative  | Humidity | Rate o              | f Change    | Air Volume |

|-------------|-------------------------------|-----------|----------|---------------------|-------------|------------|

| Operating   | Storage                       | Operating | Storage  | Temp                | Rel. Humid. | Inlet      |

|             | -40° to 70° C<br>-40° to 158° |           | 5 – 95%  | 7° C/hr<br>12° F/hr | 2%/hr       |            |

#### **ENVIRONMENTAL (MEDIA)**

| Temperature                   |                                 | Relative  | Humidity | Rate of Change           |             |  |

|-------------------------------|---------------------------------|-----------|----------|--------------------------|-------------|--|

| Operating                     | Storage                         | Operating | Storage  | Temp                     | Rel. Humid. |  |

| 10° to 57° C<br>50° to 135° F | -40° to 65° C<br>-40° to 150° F | 8 – 80%   | 8 – 80%  | 0.1° C/min<br>0.2° F/min |             |  |

| Memory | I/O Bus | Massbus *      | Device | Other |

|--------|---------|----------------|--------|-------|

| N/A    | N/A     | 48 m<br>160 ft | N/A    | N/A   |

<sup>\*</sup>Total system (maximum)

# RP06-A/B

#### **MECHANICAL**

| Mounting<br>Code | Weight           | Height            | Width          | Depth          | Cab Type If Used | Skid<br>Type |

|------------------|------------------|-------------------|----------------|----------------|------------------|--------------|

| FS               | 272 kg<br>600 lb | 118 cm<br>46.5 in | 81 cm<br>32 in | 81 cm<br>32 in | VE               | 12-10568-02  |

#### POWER (AC)

| AC Voltage |            | Frequency  |                        | Steady State   | Surge                           | Surge        |              |

|------------|------------|------------|------------------------|----------------|---------------------------------|--------------|--------------|

| Low        | Nom        | High       | Tolerance              | Phase(s)       | Current (RMS)                   | Current      | Duration     |

| 104<br>208 | 120<br>240 | 127<br>254 | 60 Hz ± 1<br>50 Hz ± 1 | 3-wye<br>3-wye | 12.6 A (total)<br>6.3 A (total) | 30 A<br>15 A | 10 s<br>10 s |

#### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation           | Watts | KVA            | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|-------------------------------|-------|----------------|--------------------|--------------------------|-----------------------------|

| 10 ms                           | 1105 kg·cal/hr<br>4384 Btu/hr | 1285  | 1.5<br>(total) | 4.5 m<br>15 ft     | NEMA #<br>L21-20P        | 4.36 mA                     |

#### **ENVIRONMENTAL (DEVICE)**

| Temperature                  |                               | Relative  | Humidity | Rate o              | f Change    | Air Volume               |

|------------------------------|-------------------------------|-----------|----------|---------------------|-------------|--------------------------|

| Operating                    | Storage                       | Operating | Storage  | Temp                | Rel. Humid. | Inlet                    |

| 15° to 32° C<br>59° to 90° F | 10° to 44° C<br>50° to 110° F | 20-80%    | 0–95%    | 7° C/hr<br>12° F/hr | 2%/hr       | 100 ft <sup>3</sup> /min |

#### **ENVIRONMENTAL (MEDIA)**

| Temperature                   |                                | Relative  | Humidity | Rate of Change      |             |  |

|-------------------------------|--------------------------------|-----------|----------|---------------------|-------------|--|

| Operating                     | Storage                        | Operating | Storage  | Temp                | Rel. Humid. |  |

| 15° to 50° C<br>60° to 120° F | 40° to 65° C<br>-40° to 150° F | 8-80%     | 8-80%    | 7° C/hr<br>12° F/hr | 2%/hr       |  |

| Memory | I/O Bus | Massbus        | Device | Other |

|--------|---------|----------------|--------|-------|

| N/A    | N/A     | 48 m<br>160 ft | N/A    | N/A   |

# TU45A-E (Master)

#### **MECHANICAL**

| Mounting<br>Code | Weight           | Height          | Width          | Depth          | Cab Type If Used | Skid<br>Type |

|------------------|------------------|-----------------|----------------|----------------|------------------|--------------|

| FS               | 290 kg<br>640 lb | 152 cm<br>60 in | 69 cm<br>27 in | 76 cm<br>30 in | H9502            | N/A          |

#### POWER (AC)

| Low | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State<br>Current (RMS) | Surge<br>Current | Surge<br>Duration |

|-----|---------|------------|------------------------|----------|-------------------------------|------------------|-------------------|

| 104 | 120     | 127        | 60 Hz ± 1              | 1        | 8.5 A                         | 14 A             | 1 s               |

| 208 | 230     | 254        | 50 Hz ± 1              | 1        | 4.3 A                         | 7 A              | 1 s               |

#### POWER (AC)

| Interrupt Tolerance (Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type   | Leakage<br>Current<br>(Max) |

|---------------------------|------------------------------|-------|------|--------------------|----------------------------|-----------------------------|

| 5 ms                      | 757 kg·cal/hr<br>3003 Btu/hr | 880   | 1.02 | 4.5 m<br>15 ft     | NEMA L5-30P<br>NEMA L6-20P | 3.16 mA                     |

#### **ENVIRONMENTAL (DEVICE)**

| Temperature                  |                                 | Relative Humidity |         | Rate of Change      |             | Air Volume               |

|------------------------------|---------------------------------|-------------------|---------|---------------------|-------------|--------------------------|

| Operating                    | Storage                         | Operating         | Storage | Temp                | Rel. Humid. | Inlet                    |

| 15° to 32° C<br>59° to 90° F | -40° to 66° C<br>-40° to 151° F | 20-80%            | 0–95%   | 7° C/hr<br>12° F/hr | 2%/hr       | 400 ft <sup>3</sup> /min |

#### **ENVIRONMENTAL (MEDIA)**

| Temp                         | erature                         | Relative Humidity Rate of |         | Change |             |

|------------------------------|---------------------------------|---------------------------|---------|--------|-------------|

| Operating                    | Storage                         | Operating                 | Storage | Temp   | Rel. Humid. |

| 16° to 32° C<br>60° to 90° F | -40° to 60° C<br>-40° to 140° F | 20-80%                    | 5-95%   | N/A    | N/A         |

| Memory | I/O Bus | Massbus        | Device       | Other |

|--------|---------|----------------|--------------|-------|

| N/A    | N/A     | 30 m<br>100 ft | 3 m<br>10 ft | N/A   |

## TU45A-E (Slave)

#### **MECHANICAL**

| Mounting<br>Code | Weight           | Height          | Width          | Depth          | Cab Type<br>If Used | Skid<br>Type |

|------------------|------------------|-----------------|----------------|----------------|---------------------|--------------|

| FS               | 272 kg<br>600 lb | 152 cm<br>60 in | 69 cm<br>27 in | 76 cm<br>30 in | H9502               | N/A          |

#### POWER (AC)

| А          | AC Voltage Frequency |            | ge Frequency Steady    |          | Steady State   | Surge       | Surge      |

|------------|----------------------|------------|------------------------|----------|----------------|-------------|------------|

| Low        | Nom                  | High       | Tolerance              | Phase(s) | Current (RMS)  | Current     | Duration   |

| 104<br>208 | 120<br>230           | 127<br>254 | 60 Hz ± 1<br>50 Hz ± 1 | 1<br>1   | 6.8 A<br>3.4 A | 14 A<br>7 A | 1 s<br>1 s |

#### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA  | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type   | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|------|--------------------|----------------------------|-----------------------------|

| 5 ms                            | 605 kg·cal/hr<br>2402 Btu/hr | 704   | 0.82 | 4.5 m<br>15 ft     | NEMA L5-30P<br>NEMA L6-20P | 3.16 mA                     |

#### **ENVIRONMENTAL (DEVICE)**

| Temperature |                                 | Relative  | Humidity | Rate of Change      |             | Air Volume               |  |

|-------------|---------------------------------|-----------|----------|---------------------|-------------|--------------------------|--|

| Operating   | Storage                         | Operating | Storage  | Temp                | Rel. Humid. | Inlet                    |  |

|             | -40° to 66° C<br>-40° to 151° F | 20-80%    | 0-95%    | 7° C/hr<br>12° F/hr | 2%/hr       | 400 ft <sup>3</sup> /min |  |

#### **ENVIRONMENTAL (MEDIA)**

| Temperature                  |                                 | Relative          | Humidity | Rate of Change |             |

|------------------------------|---------------------------------|-------------------|----------|----------------|-------------|

| Operating                    | Storage                         | Operating Storage |          | Temp           | Rel. Humid. |

| 16° to 32° C<br>60° to 90° F | -40° to 60° C<br>-40° to 140° F | 20-80%            | 5-95%    | N/A            | N/A         |

#### MAXIMUM CABLE LENGTH AND TYPE(S)

| Memory | I/O Bus | Massbus | Device       | Other |

|--------|---------|---------|--------------|-------|

| N/A    | N/A     | N/A     | 3 m<br>10 ft | N/A   |

(3) BC06R

# **CHAPTER 3 INSTALLATION**

Refer to KS10-Based DECSYSTEM-2020 Installation Manual (Document number EK-0KS10-IN).

# CHAPTER 4 OPERATION/PROGRAMMING

#### 4.1 CONTROLS AND INDICATORS

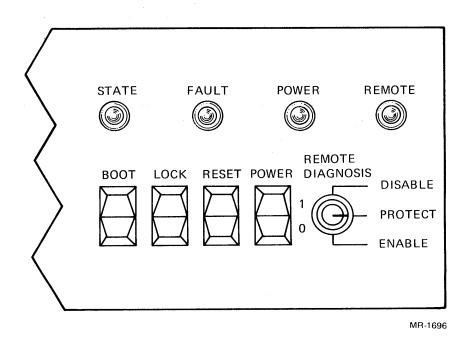

The KS10 switch and indicator panel is shown in Figure 4-1. There are five switches, three of which provide for powering-up, resetting, and bootstrapping the system. The fourth switch serves as an interlock to prevent an inadvertent reset or bootstrap by the operator once the system is in operation. The last switch controls the remote diagnosis link to the system. Switch functions are listed in Table 4-1.

The panel also has four indicators. One indicates power-on. The other three are under control of the 8080 console program. They indicate the system's run state, detection of a system fault, and enabling of the system's remote diagnosis line. Indicator functions are detailed in Table 4-2.

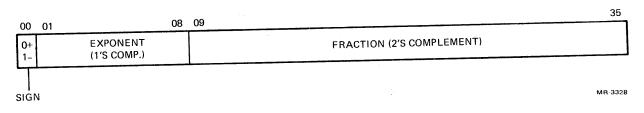

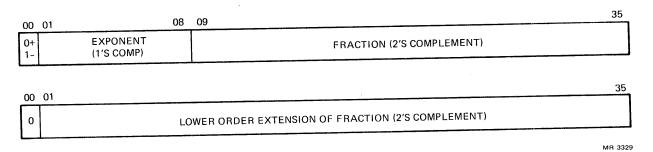

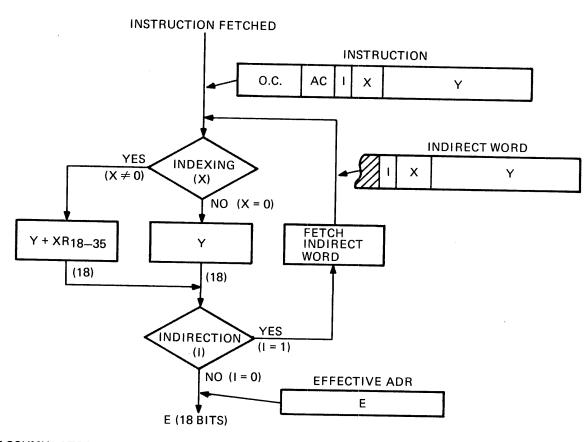

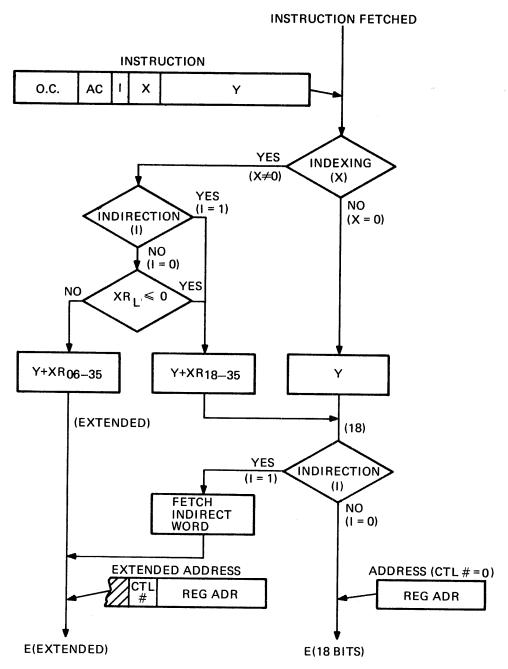

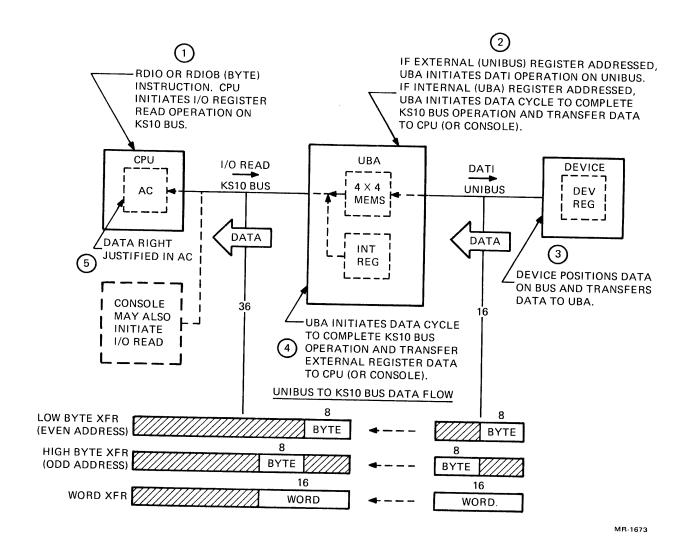

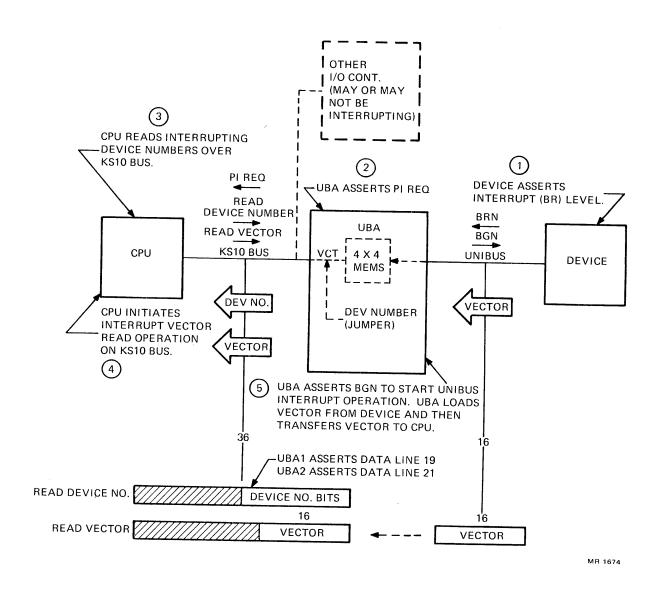

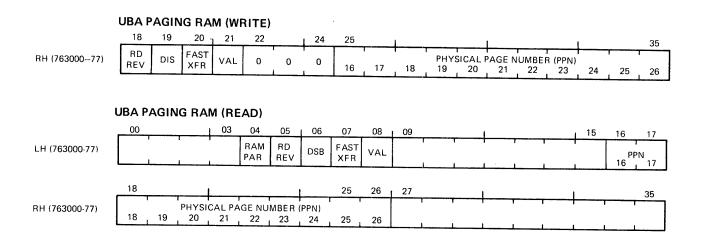

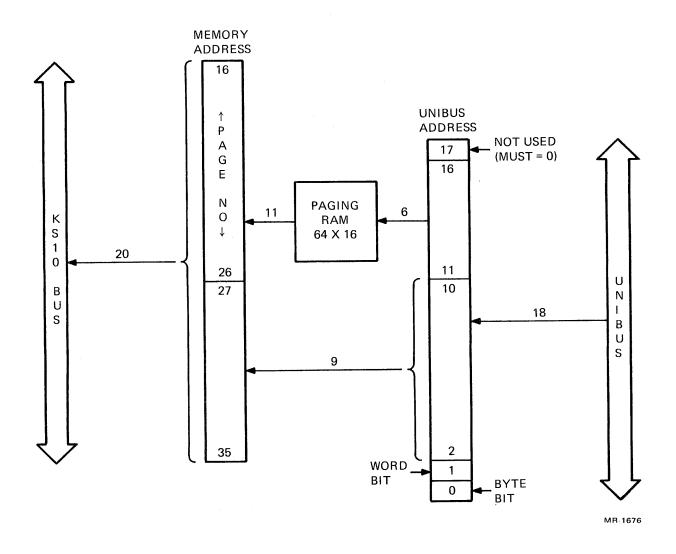

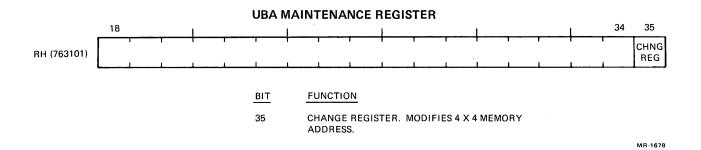

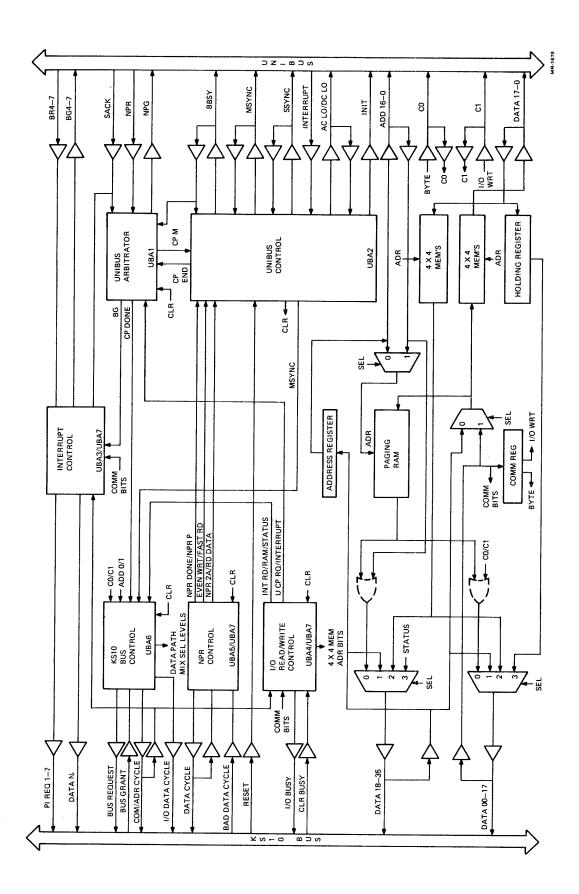

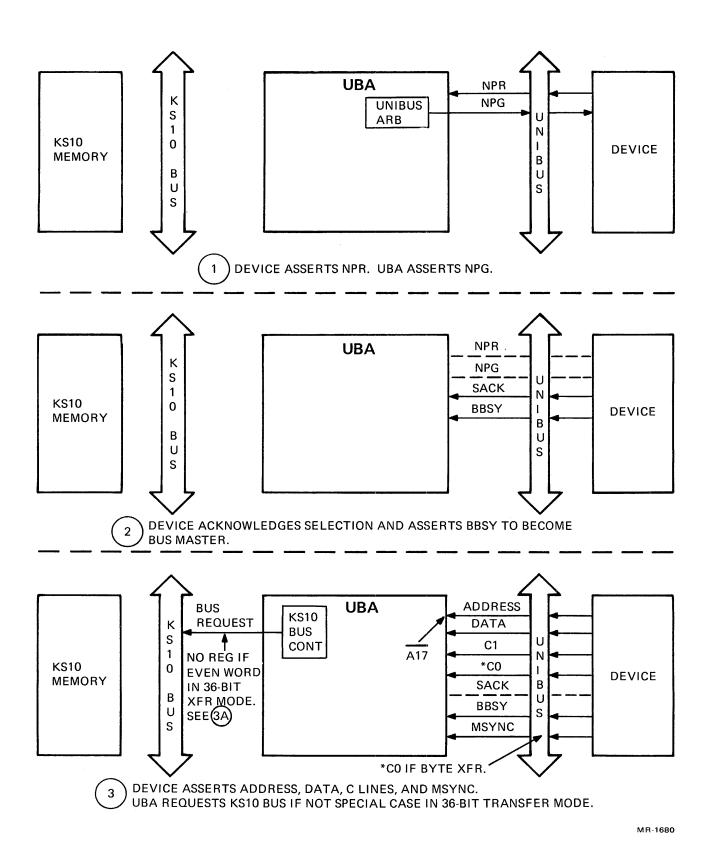

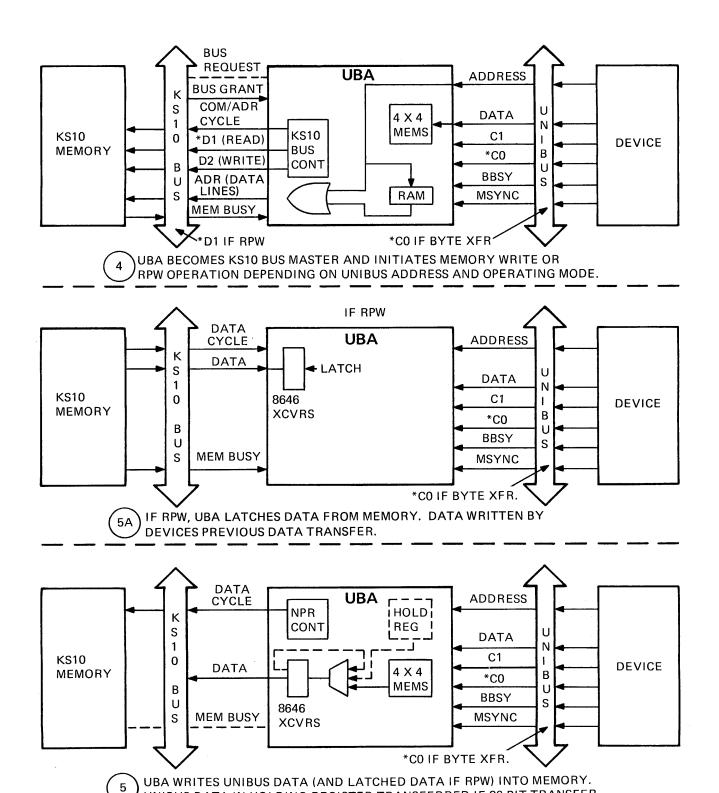

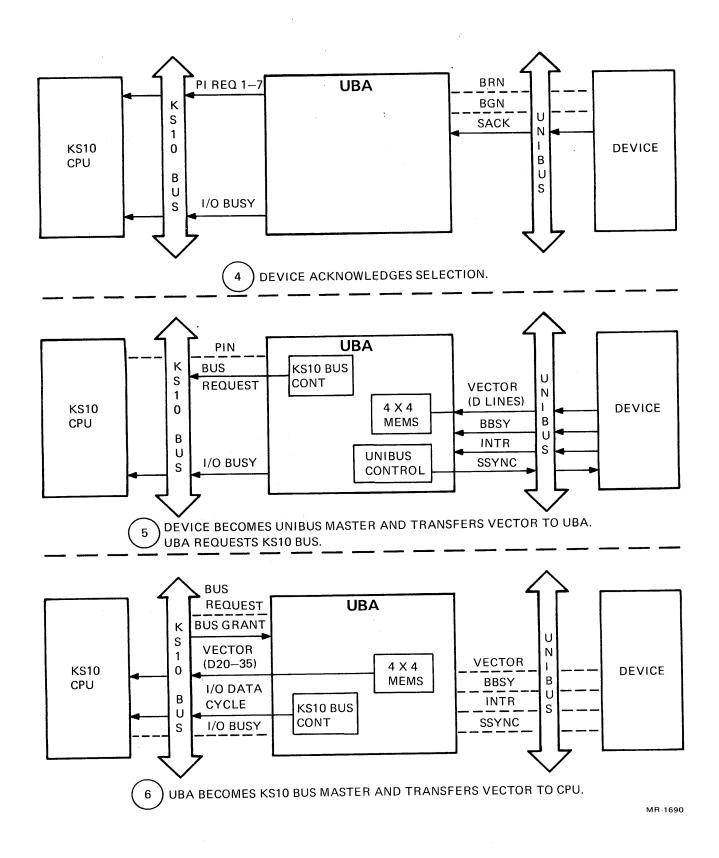

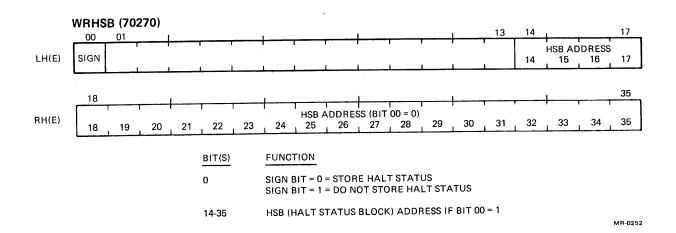

Figure 4-1 KS10 Switch and Indicator Panel