HARDWARE HANDBOOK

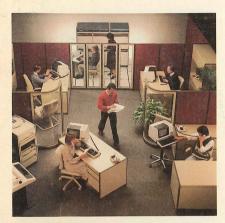

DIGITAL Facility, Colorado Springs, Colorado

### **CORPORATE PROFILE**

Digital Equipment Corporation designs, manufactures, sells and services computers and associated peripheral equipment, and related software and supplies. The Company's products are used worldwide in a wide variety of applications and programs, including scientific research, computation, communications, education, data analysis, industrial control, timesharing, commercial data processing, word processing, health care, instrumentation, engineering and simulation.

G. Rees

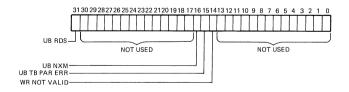

### digital

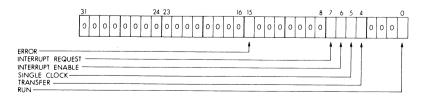

### Copyright© 1982 Digital Equipment Corporation. All Rights Reserved.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

DEC, DECnet, DECsystem-10, DECSYSTEM-20, DECtape

DECUS, DECwriter, DIBOL, Digital logo, IAS, MASSBUS, OMNIBUS

PDP, PDT, RSTS, RSX, SBI, UNIBUS, VAX, VMS, VT

are trademarks of

Digital Equipment Corporation

This handbook was designed, produced, and typeset by DIGITAL's New Products Marketing Group using an in-house text-processing system.

### **TABLE OF CONTENTS**

| PREFACEIX                                  |

|--------------------------------------------|

| PART I INTRODUCTION                        |

|                                            |

| CHAPTER 1 AN INTRODUCTION TO VAX           |

| THE VAX FAMILY                             |

| ARCHITECTURE OVERVIEW                      |

| HARDWARE OVERVIEW9                         |

| READING THIS HANDBOOK                      |

|                                            |

| PART II THE VAX-11/730                     |

| CHAPTER 2 VAX-11/730 CONSOLE SUBSYSTEM     |

| INTRODUCTION                               |

| CONSOLE MODES                              |

| CONSOLE TERMINAL23                         |

| CONSOLE COMMAND LANGUAGE24                 |

| INTEGRAL TU58 TAPE DRIVES35                |

| BOOTING THE VAX-11/730 SYSTEM35            |

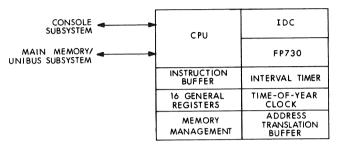

| CHAPTER 3 VAX-11/730 CENTRAL PROCESSOR     |

| INTRODUCTION                               |

| PROGRAMMED ARRAY LOGIC TECHNOLOGY          |

| HARDWARE ELEMENTS41                        |

| CHAPTER 4 VAX-11/730 MAIN MEMORY SUBSYSTEM |

| INTRODUCTION                               |

| BASIC MEMORY OPERATIONS                    |

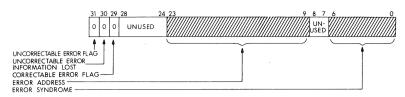

| ERROR CHECKING AND CORRECTION              |

|                                            |

| CHAPTER 5 VAX-11/730 UNIBUS SUBSYSTEM      |

| INTRODUCTION                               |

| VAX-11/730 UNIBUS SUMMARY                  |

| PROCESSOR ACCESS TO UNIBUS                 |

| UNIBUS INITIATED DATA TRANSFERS            |

| DMF32 COMMUNICATION BOARD67                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 6VAX-11/730 PRIVILEGED REGISTERSINTRODUCTION69CONSOLE TERMINAL REGISTERS70TU58 REGISTERS73TIME-OF-YEAR CLOCK AND INTERVAL TIMER REGISTERS75FLOATING POINT ACCELERATOR REGISTER77                                                                                                                                                               |

| PART III THE VAX-11/750                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 7 VAX-11/750 CONSOLE SUBSYSTEM           INTRODUCTION         81           CONSOLE MODES         82           VAX-11/750 FRONT PANEL         84           CONSOLE TERMINAL         86           CONSOLE COMMAND LANGUAGE         86           INTEGRAL TU58 CARTRIDGE TAPE DRIVE         96           BOOTING THE VAX-11/750 SYSTEM         96 |

| CHAPTER 8VAX-11/750 CENTRAL PROCESSORINTRODUCTION105GATE ARRAY TECHNOLOGY107HARDWARE ELEMENTS107                                                                                                                                                                                                                                                       |

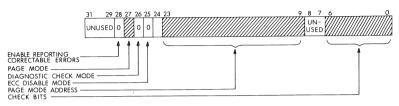

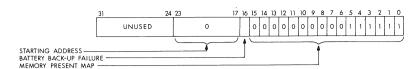

| CHAPTER 9VAX-11/750 MAIN MEMORY SUBSYSTEMINTRODUCTION113BOOT ROMS114BASIC MEMORY OPERATIONS115CONTROL AND STATUS REGISTERS116BATTERY BACKUP120ERROR CHECKING AND CORRECTION120                                                                                                                                                                         |

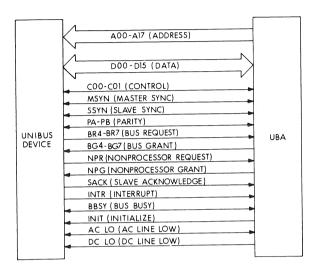

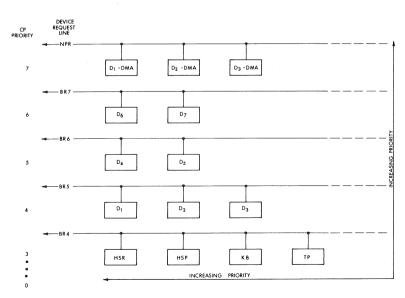

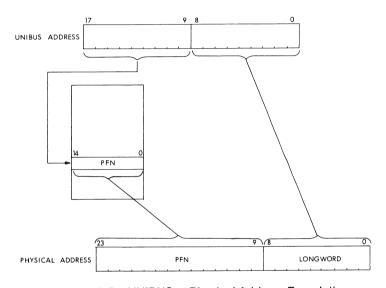

| CHAPTER 10         VAX-11/750 UNIBUS SUBSYSTEM           INTRODUCTION         123           VAX-11/750 UNIBUS SUMMARY         124           VAX-11/750 UNIBUS ADAPTER         128           PROCESSOR ACCESS TO UNIBUS         129           UNIBUS INITIATED DATA TRANSFERS         130                                                               |

| CHAPTER 11 VAX-11/750 MASSBUS SUBSYSTEM                                                                                                                                                                                                                                                                                                                |

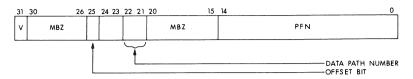

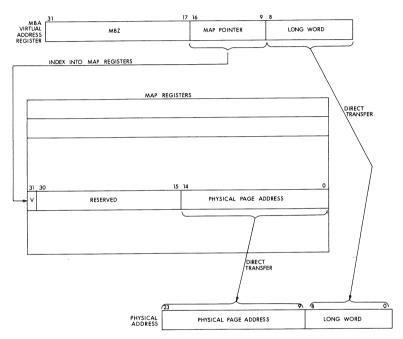

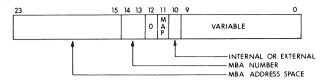

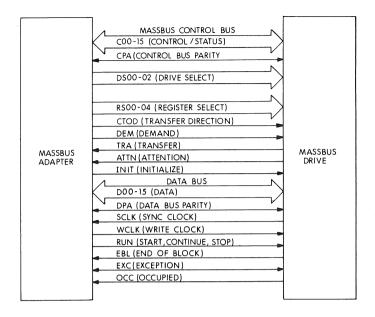

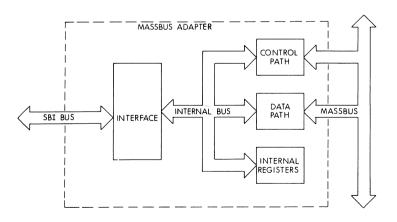

| MASSBUS ADAPTER OPERATION141MBA REGISTERS142DATA PATH142MBA ACCESS143DATA TRANSFER PROGRAM FLOW153                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 12 VAX-11/750 PRIVILEGED REGISTERS  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PART IV THE VAX-11/780                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

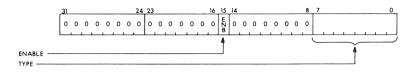

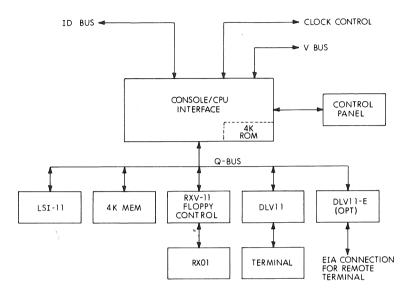

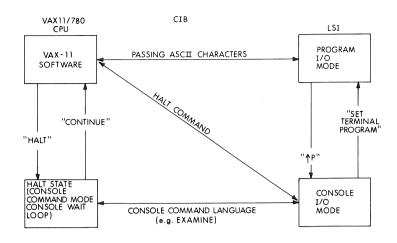

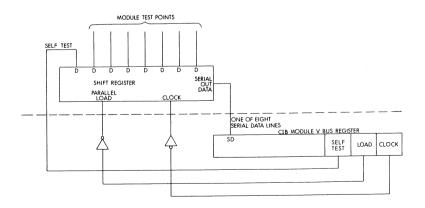

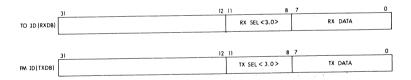

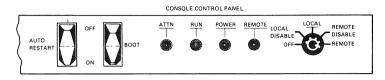

| CHAPTER 13 VAX-11/780 CONSOLE SUBSYSTEM         INTRODUCTION       173         CONSOLE INTERFACE BOARD       174         CONSOLE BUS STRUCTURE       177         INTERNAL DATA BUS       177         Q BUS       178         V BUS       178         CONSOLE/VAX-11 INTERACTION       179         READ-ONLY MEMORY (ROM)       179         VAX-11/780 PROCESSOR CONTROL PANEL       179         CONSOLE COMMAND LANGUAGE       182         CONSOLE ERROR MESSAGES       189         BOOTING THE VAX-11/780       192         DEFAULT BOOTSTRAP COMMAND PROCEDURE       195 |

| CHAPTER 14 VAX-11/780 CENTRAL PROCESSOR  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CHAPTER 15 SYNCHRONOUS BACKPLANE INTERCONNE      |      |

|--------------------------------------------------|------|

| INTRODUCTION                                     |      |

| SBI STRUCTURE                                    |      |

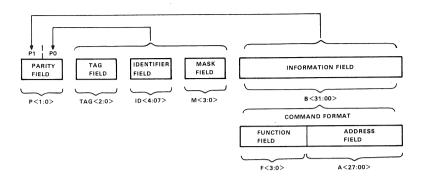

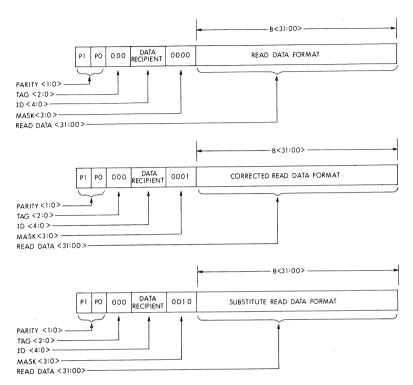

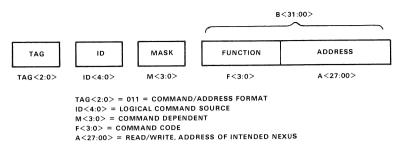

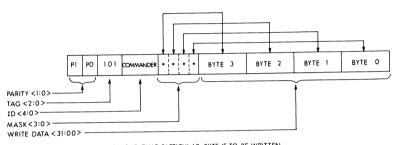

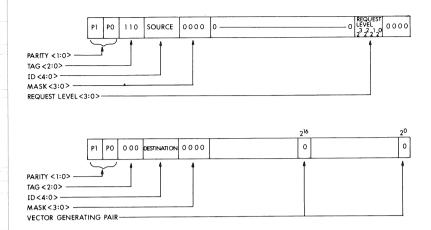

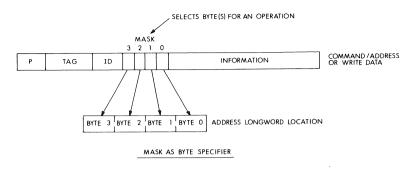

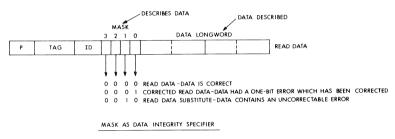

| PARITY FIELD                                     |      |

| SBI THROUGHPUT                                   | 228  |

| CHAPTER 16 VAX-11/780 MAIN MEMORY SUBSYSTEM      |      |

| INTRODUCTION                                     |      |

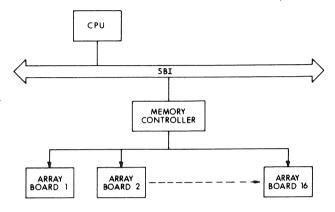

| MEMORY CONTROLLER                                |      |

| BASIC MEMORY OPERATIONS                          |      |

| INTERLOCK CYCLES                                 |      |

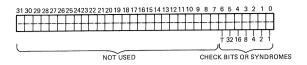

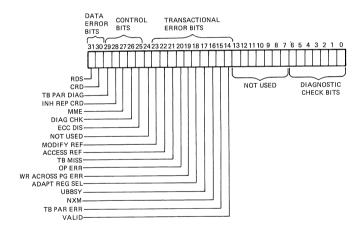

| ERROR CHECKING AND CORRECTION (ECC)              |      |

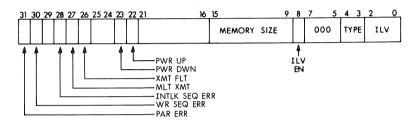

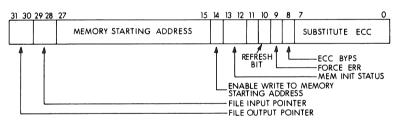

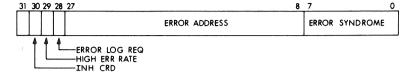

| MEMORY CONFIGURATION REGISTERS                   |      |

| MEMORY INTERLEAVING                              |      |

| ROM BOOTSTRAP                                    |      |

| BATTERY BACKUP                                   |      |

|                                                  |      |

| CHAPTER 17 VAX-11/780 UNIBUS SUBSYSTEM           |      |

| INTRODUCTION                                     |      |

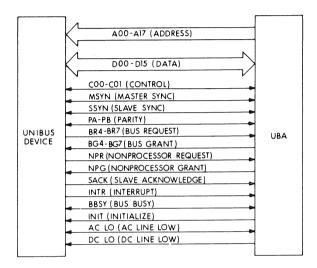

| UNIBUS SUMMARY                                   |      |

| THE UNIBUS ADAPTER                               |      |

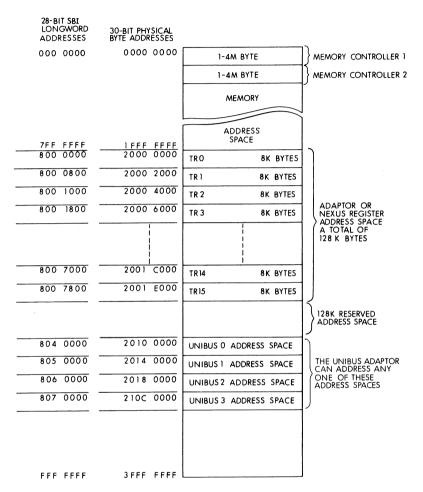

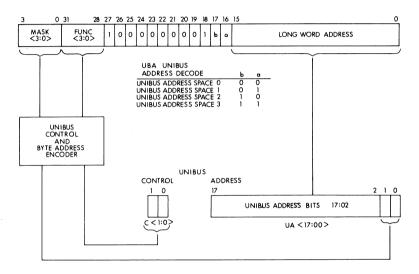

| SBI ACCESS TO THE SBI ADDRESS SPACE              |      |

| UNIBUS ACCESS TO THE SBI ADDRESS SPACE           |      |

| UNIBUS ADAPTER DATA TRANSFER PATHS               |      |

| INTERRUPTS                                       | 274  |

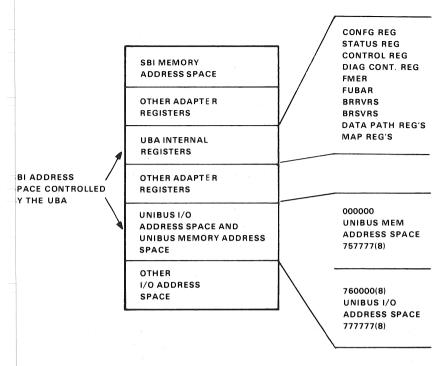

| UNIBUS ADAPTER (NEXUS) REGISTER SPACE            |      |

| SBI ADDRESSABLE UNIBUS ADAPTER REGISTERS         |      |

| POWER FAIL AND INITIALIZATION                    |      |

| SBI UNJAM                                        |      |

| EXAMPLE                                          | 303  |

| CHAPTER 18 VAX-11/780 MASSBUS SUBSYSTEM          |      |

| INTRODUCTION                                     |      |

| MASSBUS ADAPTER OPERATION                        |      |

| CONTROL PATH                                     |      |

| MBA ACCESS                                       |      |

| INTERNAL REGISTERS                               |      |

| EXAMPLE                                          |      |

|                                                  | .020 |

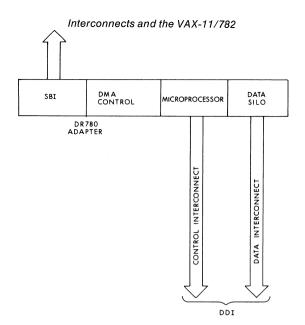

| CHAPTER 19 INTERCONNECTS AND THE VAX-11/782      |      |

| OVERVIEW                                         |      |

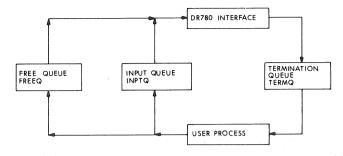

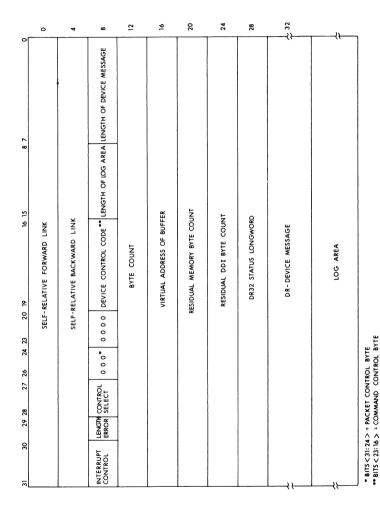

| DR780 HIGH PERFORMANCE 32-BIT PARALLEL INTERFACE |      |

| DR32 DEVICE INTERCONNECT (DDI)                   | 333  |

|            | VAX-11//30 IN LERNAL PROCESSOR       | 419 |

|------------|--------------------------------------|-----|

|            | VAX-11/750 INTERNAL PROCESSOR        | 425 |

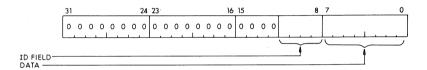

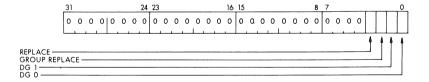

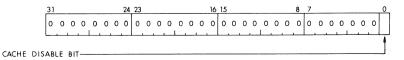

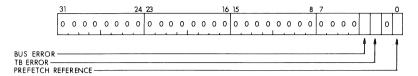

|            | VAX-11/780 INTERNAL DATA (ID) BUS    | 435 |

| APPENDIX H | OPERAND SPECIFIER NOTATION           | 449 |

| APPENDIX I | I/O SPACE RESTRICTIONS               | 453 |

|            | TECHNICAL SPECIFICATIONS FOR DCESSOR | 455 |

|            | TECHNICAL SPECIFICATIONS FOR DCESSOR | 461 |

|            | TECHNICAL SPECIFICATIONS FOR DCESSOR | 469 |

| GLOSSARY   | SYSTEM THROUGHPUT CONSIDERATIONS     | 483 |

#### **PREFACE**

VAX is DIGITAL's family of 32-bit minicomputers. This handbook provides a brief introduction to VAX and detailed descriptions of the VAX family members: the new VAX-11/730, the VAX-11/750, the VAX-11/780, and the new VAX-11/782.

PART I introduces the reader to VAX with an overview of the VAX architecture and the capabilities of the newly enhanced VAX/VMS operating system. To complete the VAX family picture, a hardware overview of the VAX processors is provided.

For detailed information on the new entry-level VAX, PART II of this book describes the VAX-11/730 console subsystem, the central processing unit, the main memory subsystem, the UNIBUS subsystem, and the privileged registers.

PART III covers the VAX-11/750, including the topics listed above and a chapter on the MASSBUS subsystem.

Both the VAX-11/780 and the VAX-11/782 are discussed in PART IV. Additional chapters for the VAX-11/780 include Chapter 15 on the Synchronous Backplane Interconnect and Chapter 19 on Interconnects and the VAX-11/782.

PART V details the wide range of dependability features built into VAX computer systems. These features were designed to ensure VAX reliability, availability, and maintainability.

PART VI of this book contains 13 appendices, a glossary, and an index for your convenience.

In addition to this handbook, two other VAX handbooks are available:

- The VAX Architecture Handbook, describing the VAX system architecture, addressing modes, and the native mode instruction set

- The VAX Software Handbook, describing the VAX/VMS operating system, its operation, hardware interaction, data structures, features, and capabilities

As with all VAX handbooks, a comment card has been placed in the back of the book. All comments are greatly appreciated, as they help us make the VAX handbook set meet your needs.

# PART I INTRODUCTION

xii

## CHAPTER 1 AN INTRODUCTION TO VAX

#### THE VAX FAMILY

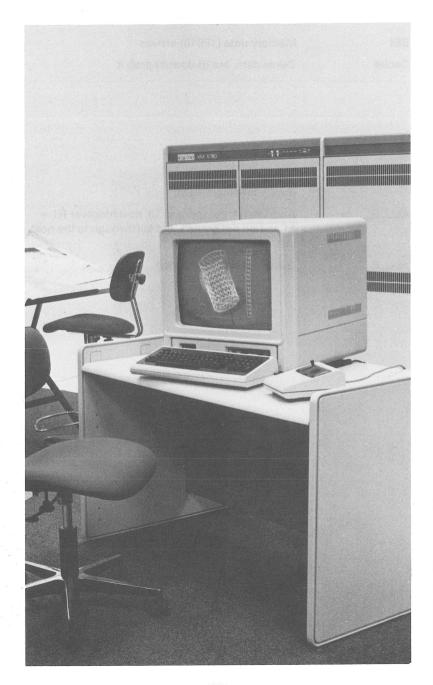

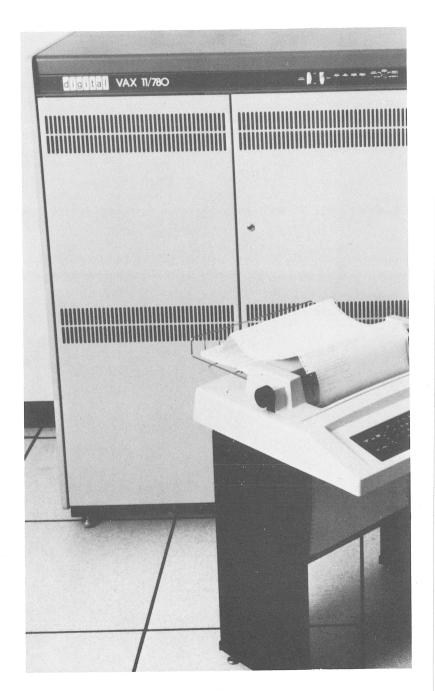

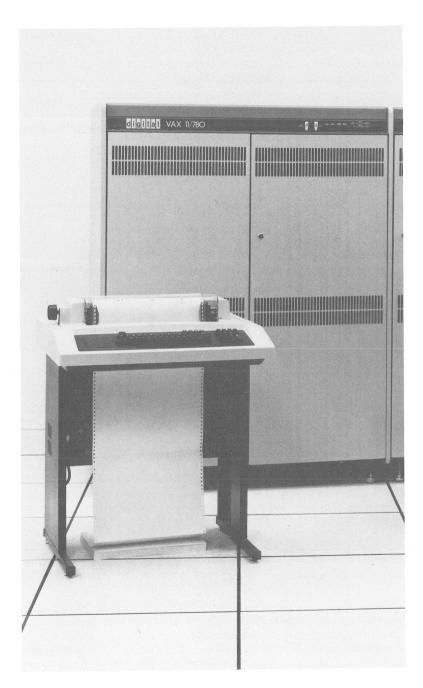

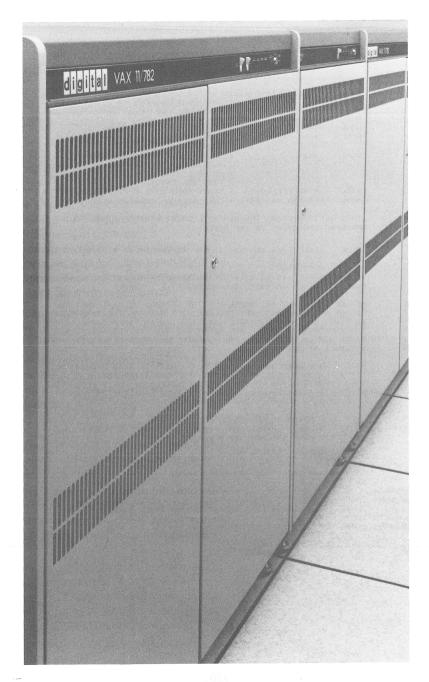

VAX is DIGITAL's family of 32-bit minicomputer systems. The new family members—the VAX-11/730 and the VAX-11/782 attached processor system—together with the VAX-11/750 and VAX-11/780, make the power of VAX systems available to a wide range of users, applications and budgets.

All VAX processors implement a 32-bit architecture, an extensive instruction set with numerous data types, and a 32-bit bus structure for high throughput. All VAX system hardware is complemented by the newly enhanced VAX/VMS operating system, a powerful multiprogramming operating system that handles multiuser, realtime and multistream batch applications, plus online program development.

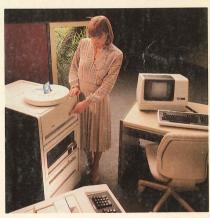

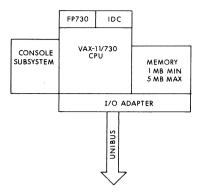

The newest member of the VAX family, the VAX-11/730, incorporates bit-slice and Programmed Array Logic (PAL) technology. Like the other family members, the VAX-11/730 implements the VAX architecture and runs the VAX/VMS operating system and layered software. With the VAX-11/730, however, VAX functionality is available at a much lower price, providing the ability to move VAX power down to the project or section level. The VAX-11/730 can also be used as a powerful, remote DECnet node, allowing its users access to higher performance members of the VAX family when necessary. Connection to mass storage devices and other peripherals is provided through a UNIBUS adapter.

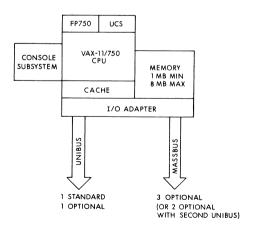

The VAX-11/750, the mid-range member of the VAX family, incorporates many innovations designed to increase performance and to reduce the overall cost of ownership. The VAX-11/750 is the first 32-bit minicomputer to be implemented primarily in custom bipolar LSI Schottky logic (designed entirely by DIGITAL engineers). One UNIBUS adapter (integral to the processor) and up to three MASSBUS adapters or one additional UNIBUS and two MASSBUS adapters may be used for connection to mass storage devices and other peripherals.

The VAX-11/780 was designed to meet the needs of many users with large databases and extensive processing needs. Central to its I/O system is a 32-bit wide data and control path that can move up to 13.3 MB of data per second among the system's major hardware components. Up to four UNIBUS and four MASSBUS adapters may be used for connection to mass storage devices and other peripherals. The support of high-performance disks and tapes by the VAX-11/750,

VAX-11/780 and VAX-11/782, combined with their ability to network with the other VAX family members provides significant and varied configuration possibilities.

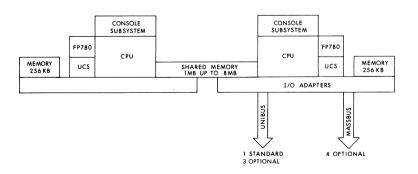

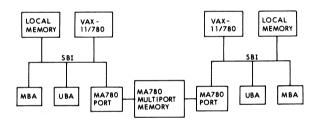

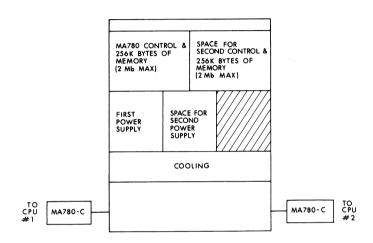

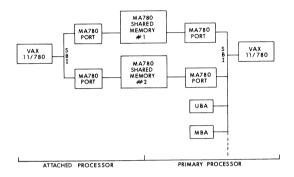

The VAX-11/782 attached processor computer system is a tightly-coupled asymmetrical multiprocessor system that can provide up to 1.8 times the performance of a single VAX-11/780 system for compute-intensive applications. Consisting of two VAX-11/780 CPUs, the VAX-11/782 attached processor computer system can support up to 8 MB of MA780 shared memory.

#### NOTE

Specific information on the VAX-11/782 attached processor system is contained in Chapter 19, Interconnects and the VAX-11/782. Unless otherwise specified, most of the VAX-11/780 features in this chapter apply to the VAX-11/782.

#### **Application Performance**

VAX hardware and software were designed to complement each other. Hardware implementation combined with the VAX/VMS operating system, 32-bit addressing, a 4 billion byte virtual memory, an address translation buffer, a prefetch instruction buffer, an optional floating point accelerator, and the powerful VAX instruction set, give VAX systems their impressive performance.

The impressive CPU power and throughput, plus the high performance-to-cost ratio, make VAX systems ideal for interactive applications. The high computational ability and large program size mean VAX systems can handle tough realtime applications as well. Furthermore, the VAX/VMS operating system provides extensive facilities for good batch performance—including job control, multistream, spooled input and output, operator control, conditional command branching, and accounting functions. A choice of options such as additional physical memory, user control store, and additional peripheral equipment interfaces, allow even greater flexibility in configuring systems to optimize performance for specific applications.

#### Ease of Use

VAX systems are user-oriented systems designed for easy operation. The DIGITAL Command Language (DCL) interface used by VAX/VMS is easy to learn and is suitable for both interactive and batch environments. The software compatibility of VAX systems allows software developed for one VAX system to run on another VAX system without modification. Because VAX systems use the same instruction set, it

also means that users need not learn a new series of instructions to take full advantage of another VAX system's capabilities.

VAX/VMS provides extensive system management facilities, giving system managers and operators the tools necessary to control the system configuration and the operations of system users for maximum efficiency. Users will appreciate the extensive HELP commands and complete multiuser security. The VAX family processors also implement a PDP-11 Compatibility Mode which recognizes almost all PDP-11 instructions. This allows users to execute code written for the PDP-11 with few modifications.

The VAX console subsystem also contributes to ease of use. A separate console terminal replaces the traditional toggle switches and lights, and a carefully designed console command language lets the user perform operations such as EXAMINEs and DEPOSITs, or boot the system, using simple commands. This console terminal also provides a hardcopy record for complete documentation of console transactions. Furthermore, switches on the front panel of the CPU can be set up to reboot the system automatically, with no operator intervention, in the event of a power failure or system crash.

Additionally, VAX systems are designed to facilitate rapid, low-cost applications development. With the complete set of VAX/VMS development tools, file system features, optional information management products, and other software packages, applications are easier to develop and require far less debugging time. DIGITAL's extensive educational services are also available to train and assist users in exploiting the wide and varied capabilities of VAX systems.

#### **Easy Installation and Maintenance**

A variety of system configurations is available so customers can purchase exactly what is required. VAX systems are easily tuned and adapted allowing additional peripherals and options to be interfaced at any time. Customers may choose from a wide variety of peripherals and packaging options to configure a VAX system to suit their requirements—whether the site is an office, a laboratory, or an industrial setting.

Once the system is installed, extensive reliability, availability, and maintainability features (discussed in Part V of this book) in both the hardware and the software ensure data integrity and increase system uptime. Features such as ECC (Error Correcting Code) memory, online error logging, and a complete range of online and stand-alone diagnostics verify system integrity and help ensure proper system

operation. The Remote Diagnosis option for the VAX-11/750 and VAX-11/780 allows a customer to be directly linked to a DIGITAL Diagnostic Center for diagnosis of hardware and software failures. For VAX-11/730 users, customer runnable diagnostics allow a system user the capability of verifying proper hardware operation and the quick isolation of system failures to the subsystem or device level. The Remote Support option, utilizing Remote Diagnosis technology, provides the DIGITAL service engineer with a further level of technical resources.

#### Sound Long-Term Investment

The features of the VAX series described above, together with the many other features described in the chapters that follow, make VAX systems a sound long-term investment. The new VAX-11/730 and VAX-11/782 systems are a reflection of DIGITAL's ongoing commitment to the VAX family of 32-bit minicomputers and further proof that the VAX family exemplifies the architecture of the 1980s. The wide range of systems possible with the VAX-11/730, VAX-11/750, VAX-11/780,and VAX-11/782 ensures that these systems can be tailored to individual application requirements and can be easily reconfigured if those needs should change in the future—an important consideration for customers involved in long-term projects and implementations.

The following sections in this chapter will introduce the reader to a variety of VAX family architectural and software features, as well as to many of the important hardware features of the various VAX implementations. Appendix A in the back of this book contains a table of commonly used VAX family mnemonics.

#### **ARCHITECTURE OVERVIEW**

The VAX family architecture is characterized by a powerful and complete instruction set of 304 instructions (see Appendix B), a wide range of data types, an efficient set of addressing modes, full demand paging memory management, and a very large virtual address space of over 4 billion bytes.

The VAX Native Instruction Set is an extension of the PDP-11 instruction set. Instructions can be grouped into classes based on their functions and uses:

Instructions to manipulate arithmetic and logical data types.

These include integer, floating point, packed decimal, character string, and bit field instructions.

The data type identifies how many stored bits are to be treated as a unit and how the unit is to be interpreted. Data types that may be used are:

| Data Type           | Represented As                                                                                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Integer             | Byte (8 bits), word (16 bits), longword (32 bits), quadword (64 bits)                                                                               |

| Floating point      | 4-byte F_floating, 8-byte D_floating, 8-<br>byte G_floating, 16-byte H_floating                                                                     |

| Packed decimal      | String of bytes (up to 31 decimal digits, 2 digits per byte)                                                                                        |

| Character string    | String of bytes interpreted as character codes (up to 64 KB); a numeric string is a character string of codes for decimal numbers (up to 31 digits) |

| Bits and bit-fields | Field length is arbitrary and is defined<br>by the programmer (0 to 32 bits in<br>length)                                                           |

Integer, floating point, packed decimal, and character data are stored starting on an arbitrary byte boundary. Bit and bit field data start on an arbitrary bit boundary. A collection of data structures can be packed together to use less storage space.

- Instructions to manipulate special kinds of data. These include queue manipulation instructions (i.e., those that insert and remove queue entries), address manipulation instructions, and user-programmed general register load and save instructions. These instructions are used extensively by the VAX/VMS operating system.

- Instructions to control basic program flow. These include BRANCH, JUMP, and CASE instructions, subroutine CALL instructions, and procedure CALL instructions.

- 4. Instructions to perform special operating system functions quickly. These include process control instructions (such as two special context switching instructions which allow process context variables to be loaded and saved using only one instruction for each operation), and the FIND FIRST instruction which (among other uses) allows the operating system to locate the highest priority executable process. These instructions contribute to rapid and efficient rescheduling.

- 5. Instructions provided specifically for high-level language constructs. During the design of the VAX family architecture, special attention was given to implementing frequently-used, high-level language constructs as single VAX instructions. These instructions contribute to decreased program size and increased

#### Introduction to VAX

execution speed. Some of the constructs which have become single VAX instructions include:

- The FORTRAN-computed GOTO statement (translates into the CASE instruction).

- The loop construct (e.g., add, compare, and branch translates into the ACB instruction).

- An extensive CALL facility (which aligns the stack on a longword boundary, saves user-specified registers, and cleans up the stack on return); the CALL facility is used compatibly among all native mode languages and operating system services.

VAX instructions and data are variable in length. They need not be aligned on longword boundaries in physical memory, but may begin at any odd or even byte address. Therefore, instructions not requiring arguments use only one byte, while other instructions may take two, three, or up to 54 bytes depending on the number of arguments and their addressing modes. The advantage of byte alignment is that instruction streams and data structures can be stored in much less physical memory.

The VAX processors offer several addressing modes. Eleven of these use the general registers to identify the operand location and operate similarly to the PDP-11 addressing modes. The names of the modes are:

- Register

- Register deferred

- Autoincrement

- Autoincrement deferred

- Autodecrement

- Byte, word and longword displacement (similar to the PDP-11 index mode)

- Byte, word, and longword displacement deferred (similar to the PDP-11 index deferred mode)

The two additional addressing modes implemented by VAX family processors are:

- Indexed

- Literal

Because the VAX instruction set is so flexible, most functions require fewer instructions and less storage than on non-VAX processors. The result is more compact and efficient programs, faster program execution, faster context switching, more precise and faster math functions, and improved compiler-generated code.

General Registers and Stacks — The VAX family CPUs provide sixteen 32-bit general registers which can be used for temporary storage, or as accumulators, index registers, and base registers. Registers R0 through R11 can be used as general purpose registers and the remaining four have special significance depending on the instruction being executed: Register 12 (the Argument Pointer); Register 13 (the Frame Pointer); Register 14 (the Stack Pointer); and Register 15 (the Program Counter).

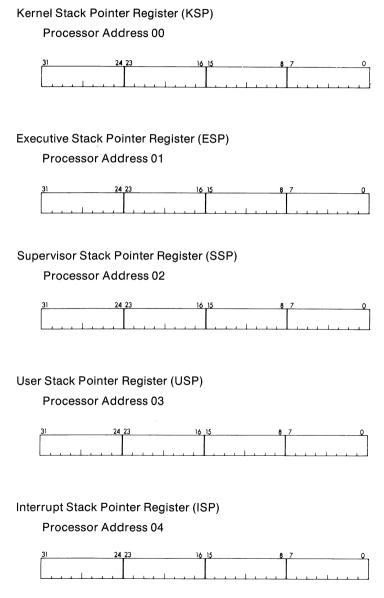

Stacks are associated with the processor's execution state. The processor may be in a process context (in one of four modes: kernel, executive, supervisor, or user) or in the systemwide interrupt service context. A stack pointer is associated with each of these states. Whenever the processor changes from one state to another, Register 14 (the Stack Pointer) is updated accordingly.

For further information concerning the VAX architecture, refer to the VAX Architecture Handbook.

#### SOFTWARE OVERVIEW

VAX/VMS is the multiuser, multifunction operating system for the VAX family processors. The software compatibility between VAX family members means that users with any VAX system can run existing software on any other VAX system without having to make modifications. Furthermore, VAX/VMS provides a reliable, high performance environment for the concurrent execution of multiuser timesharing, batch, and time-critical applications. VAX/VMS also provides:

- Virtual memory management for executing large programs

- Event-driven priority scheduling

- Shared memory, file, and interprocess communication data protection based on ownership and application groups

- Programmed system services for process and subprocess control and interprocess communication

VAX/VMS uses the VAX memory management features to provide swapping, paging, protection, and sharing of both code and data. Memory is allocated dynamically. Applications can control the amount of physical memory allocated to executing processes, to the protection of pages, and to swapping; furthermore, these controls can be added after the application is implemented.

CPU time and memory residency are scheduled on a pre-emptive priority basis. Thus, time-critical processes do not have to compete with lower priority processes for scheduling services. Scheduling rotates among processes of the same priority.

VAX/VMS includes system services to control processes and process execution, control time-critical response, control scheduling, and obtain information. Process control services allow the creation of subprocesses as well as independent detached processes. Processes can communicate and synchronize using mailboxes, shared areas of memory, or shared files. A group of processes can also communicate and synchronize, using multiple common-event flag clusters.

Memory access protection is provided both between and within processes. Each process has its own independent virtual address space which can be mapped to private pages or shared pages. VAX/VMS uses the four processor access modes to read- and/or write-protect individual pages within a process. Protection of files, shared pages of memory, and interprocess communication facilities such as mailboxes and event flags, is based on user identification codes individually assigned to accessors and data.

A complete program development environment is offered and supported by VAX/VMS. It includes the native assembly language, VAX-11 MACRO, and the following high-level programming languages: VAX-11 FORTRAN, VAX-11 COBOL, VAX-11 BASIC, VAX-11 BLISS, VAX-11 PASCAL, VAX-11 PL/I, VAX-11 CORAL 66, VAX-11 C, VAX-11 DSM, and VAX-11 DIBOL. It provides the tools necessary to write, assemble or compile, and link programs, as well as to build libraries of source, object, and image modules.

VAX Information Management Facilities — VAX/VMS supports a set of software tools that provide a full range of information management capabilities. These information management products can be used to organize, maintain, retrieve and manipulate data quickly and easily. They include:

- VAX-11 FMS, a forms management system with interactive and language-callable video forms

- VAX-11 DATATRIEVE, a multifaceted data management facility that can store, update, and retrieve information and generate reports

- VAX-11 Common Data Dictionary, a central repository for data about data, allowing the information management tools to use a single set of data descriptions as a common resource

- VAX-11 RMS, a record management facility for sequential, relative, and multikey ISAM (Indexed Sequential Access Method) file organizations

- VAX-11 DBMS, a CODASYL-compliant database management system for creating, maintaining, and updating databases

The VAX/VMS on-disk structure provides a multiple-level hierarchy of named directories and subdirectories. Files can extend across multi-

ple volumes and can be as large as the volume set on which they reside. Volumes are mounted to identify them to the system. VAX/VMS also supports multivolume ANSI format magnetic tape files with transparent volume switching.

**Communications** — The variety of communications interfaces supported by the VAX/VMS operating system allows VAX systems to be connected to other VAX systems, other DIGITAL systems, and to other manufacturers' computer systems.

Synchronous, point-to-point, and multipoint connections are supported for interprocessor communication. For terminal to host communications, asynchronous connections are supported. (For further information, see the Terminals and Communications Handbook.)

Using DECnet communications software, various types of computer system networks can be constructed to facilitate remote communications, resource sharing, and distributed computation. DECnet-VAX Phase III software offers adaptive routing, task-to-task communications, network file transfer, network command terminals, and network resource sharing and network management capabilities. Other communications software supported by VAX/VMS includes:

- VAX-11 2780/3780 protocol emulator for transferring data between a VAX system and an IBM or other manufacturer's system by means of remote job entry protocols

- VAX-11 3271 protocol emulator for an interactive program-to-program link to an IBM host running CICS or IMS

- MUX200/VAX emulator for communication with a CDC6000, CYBER series or other host computer system capable of using 200UT mode 4A communications protocol

- VAX-11 PSI (Packetnet System Interface) for connection to a public data network using the X.25 communications protocol

For further information concerning VAX software and the VAX/VMS operating system, refer to the VAX Software Handbook or the VAX Technical Summary.

#### HARDWARE OVERVIEW

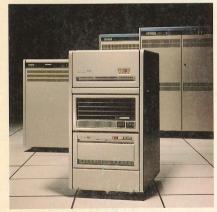

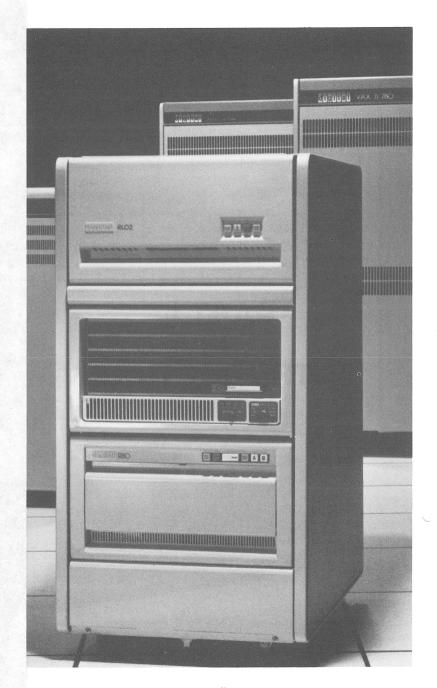

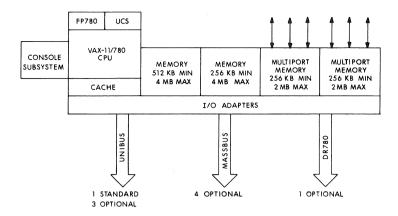

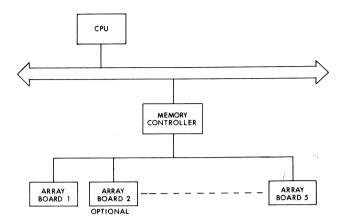

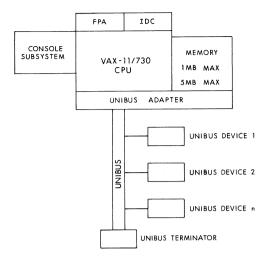

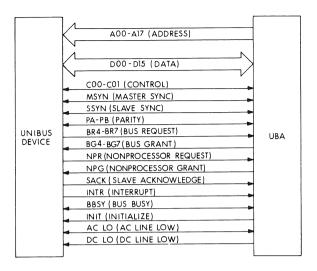

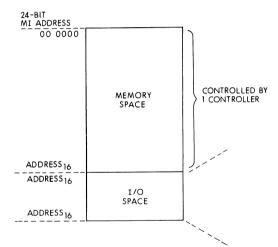

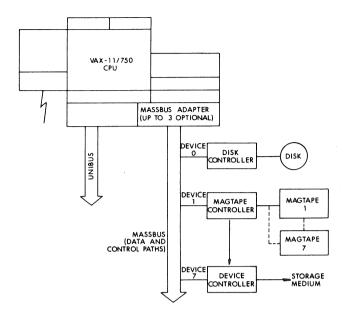

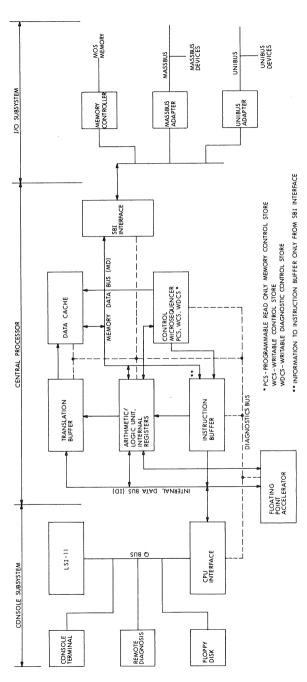

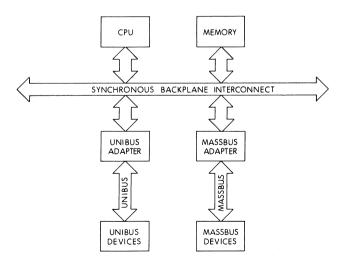

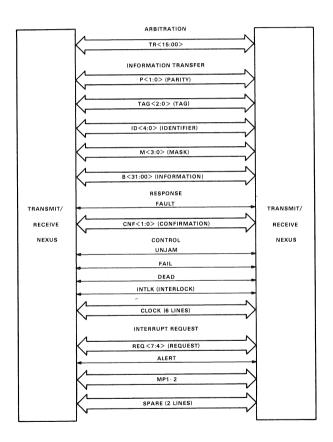

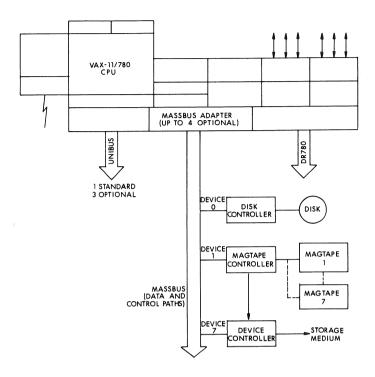

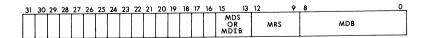

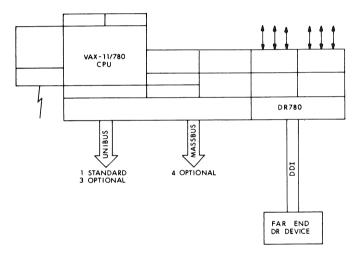

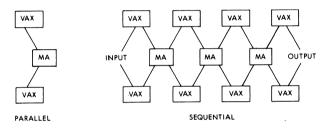

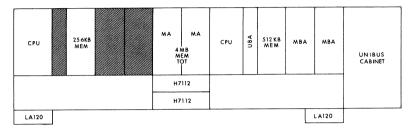

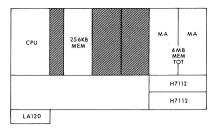

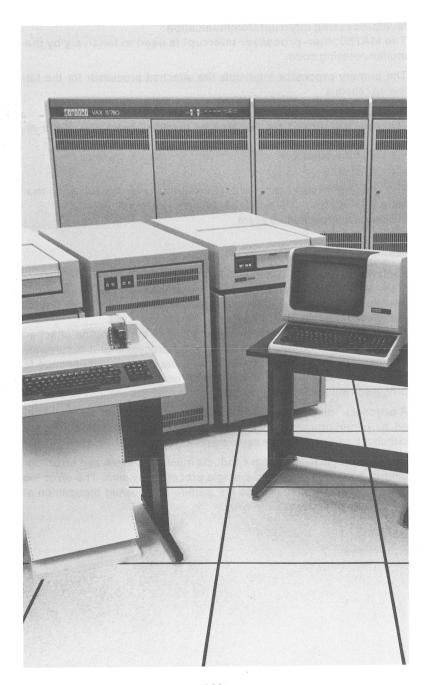

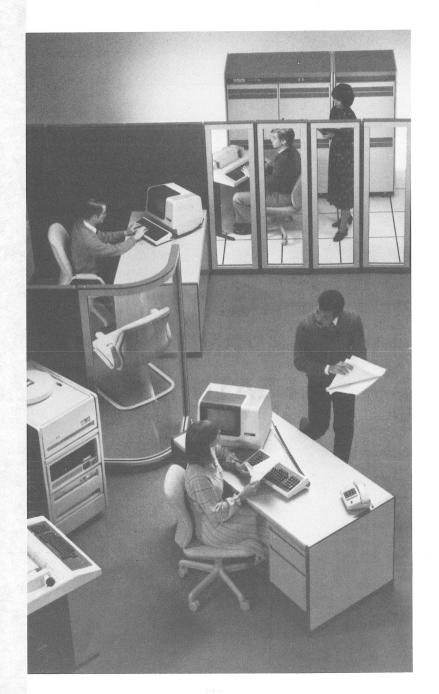

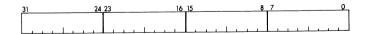

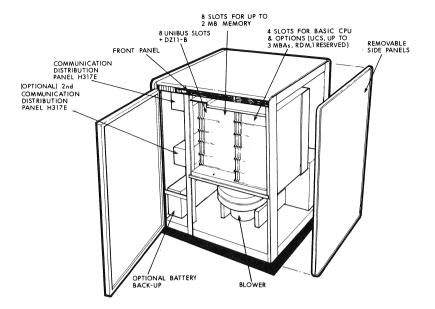

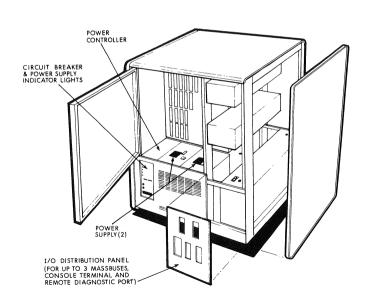

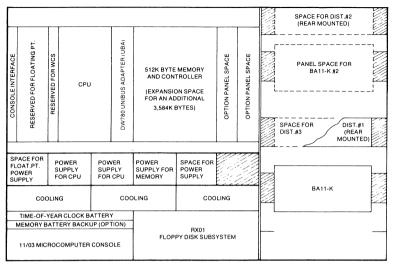

VAX computer systems consist of the central processing unit, the console subsystem, the main memory subsystem, and the input/output (I/O) subsystems—the UNIBUS, the MASSBUS (VAX-11/750, VAX-11/780, and VAX-11/782 only), and the DR780 (VAX-11/780 only) subsystems. The VAX hardware configurations are illustrated in Figures 1-1 through 1-4.

Figure 1-1 VAX-11/730 Hardware Configuration

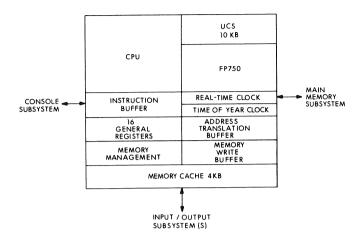

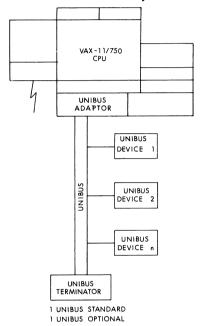

Figure 1-2 VAX-11/750 Hardware Configuration

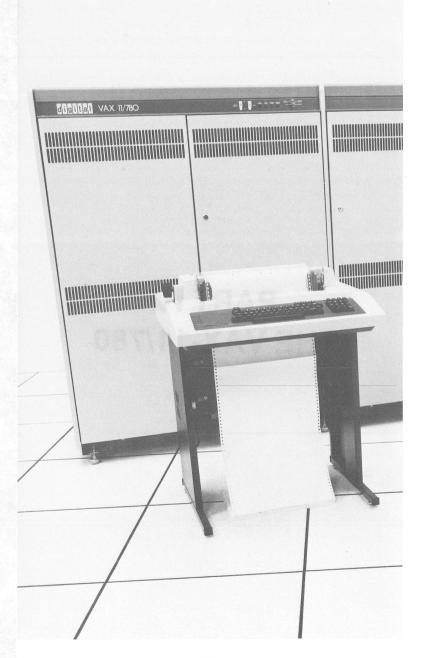

Figure 1-3 VAX-11/780 Hardware Configuration

Figure 1-4 VAX-11/782 Hardware Configuration

#### **VAX Central Processing Units (CPUs)**

VAX processors are 32-bit high-speed microprogrammed computers that execute instructions in native mode, and nonprivileged PDP-11 instructions in compatibility mode.

The processors can directly address four billion bytes of virtual address space, and provide a complete and powerful instruction set that includes integral decimal, character string, and floating point instructions. Each VAX processor includes memory management hardware, sixteen 32-bit general registers, 32 interrupt priority levels, and a console subsystem which is linked directly to the processor. In addition, the VAX-11/750 and VAX-11/780 each have a memory cache, 4 KB and 8 KB respectively.

An optional high-performance Floating Point Accelerator (FPA) is available for each of the VAX processors. The FPA works in parallel with the basic CPU to execute the standard floating point instruction set. The FPA decreases instruction execution time of floating point arithmetic and some integer arithmetic operations.

**Caches** — The VAX-11/750 and the VAX-11/780 provide three cache systems: the memory cache, an address translation buffer, and an instruction buffer. The VAX-11/730 does not have a memory cache, but has the two buffers.

The memory cache (typically 90% hit rate on the VAX-11/750 and 95% on the VAX-11/780) provides the central processor with high-speed data access by storing frequently referenced addresses, data and instruction items. The memory cache significantly reduces the effective memory access time for the CPU.

The instruction buffer is an 8-byte buffer that enables the CPU to fetch and decode the next instruction while the current instruction completes execution. The instruction buffer in combination with the parallel data paths (which can perform integer arithmetic, shifting, and memory access at the same time) significantly enhances VAX performance because the CPU seldom has to wait for the next instruction to be fetched.

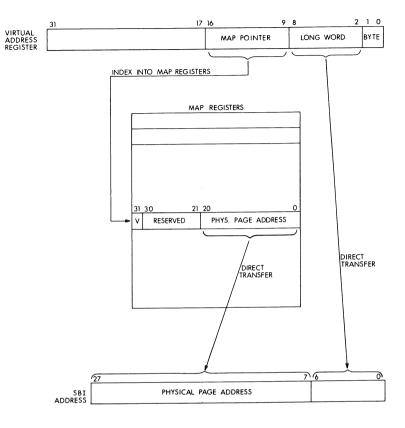

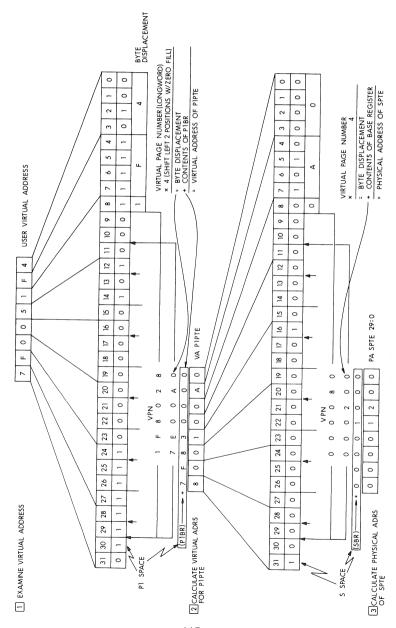

VAX systems provide an address translation buffer that eliminates extra memory accesses during virtual-to-physical address translations. The address translation buffer contains frequently used virtual-to-physical address translations: 128 page table entry translations in the VAX-11/730 and VAX-11/780, and 512 in the VAX-11/750.

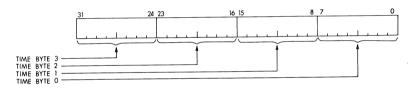

Clocks — The VAX CPUs each have two clocks. The VAX-11/750 and VAX-11/780 have a programmable realtime clock used by system diagnostics and by the VAX/VMS operating system for accounting and

scheduling, and a time-of-year clock, which insures the correct time of day and date. The VAX-11/730 has an interval timer and a time-of-year clock.

**Memory Management** — The VAX memory management hardware enables the VAX/VMS operating system to provide a flexible and efficient virtual memory programming environment. Hardware memory management, with the operating system, provides both paging (with user control) and swapping.

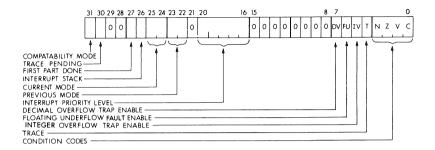

In addition, memory management provides four hierarchical modes: kernel, executive, supervisor, and user, with read/write access control for each mode.

The memory management hardware facilitates program and data sharing, and allows larger program size and increased performance.

#### The Console Subsystem

The console subsystem configuration makes the VAX series extremely approachable systems. Four elements combine to give the user access to the system's capabilities: a set of machine status switches and lights on the CPU front panel, a console terminal, a console command language, and an integral mass storage device. Simple console commands, entered through the console terminal, replace the traditional toggle switches and provide operational control (i.e., bootstrapping, initialization, self-testing, examining/depositing data in memory, etc.). When it is not being used to communicate console command language instructions to the CPU, the same terminal functions as a VAX system terminal and is available to authorized users for normal system operations. This dual-purpose console terminal results in significant hardware savings.

The VAX console subsystem and the console command language also facilitate the loading of diagnostics and software updates from the mass storage device: a TU58 tape cartridge on the VAX-11/730 and VAX-11/750, and an RX01 floppy disk system on the VAX-11/780.

With the customer's cooperation, the VAX-11/750 and VAX-11/780 console subsystems may also be equipped with a Remote Diagnosis option which allows connection to a host computer at the DIGITAL Diagnostic Center for fault detection or preventive maintenance procedures. This option can significantly lower maintenance costs as well as contribute to system availability and maintainability. The diagnostic strategy for the VAX-11/730 makes use of a new feature called Customer Runnable Diagnostics (CRD). For more information on CRDs, see Chapter 21 of this handbook. The VAX-11/730 Remote Support option, utilizing Remote Diagnosis technology, provides the DIGITAL

service engineer with a further level of technical resources.

#### The Main Memory Subsystem

VAX-11/730 Systems — The main memory subsystem consists of a controller and from one to five memory array modules that use 64 Kbit MOS (metal oxide semiconductor) RAM chips for data storage. The array modules are 1 MB each, to give a maximum memory capacity of 5 MB. ECC (Error Correcting Code) allows the correction of all single-bit errors, and the detection of all double-bit errors, to insure data integrity.

VAX-11/750 Systems — The main memory subsystem consists of a controller and from one to eight memory array modules that use 64 K MOS (metal oxide semiconductor) RAM chips for data storage. The array modules are 1 MB each, to give a maximum memory capacity of 8 MB. ECC (Error Correcting Code) allows the correction of all single-bit errors, and the detection of all double-bit errors, to insure data integrity.

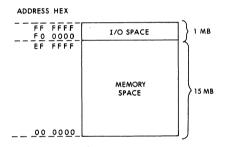

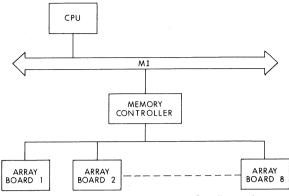

VAX-11/780 Systems — The main memory subsystem consists of a controller and from one to sixteen array boards utilizing 16 Kbit MOS RAM chips. Each array board contains 256 KB of physical memory, which can be increased to a maximum array size of 8 MB by means of a second controller. Two memory controllers with equal amounts of memory can be interleaved to improve I/O throughput.

For the VAX-11/782, the local memory is used only for stand-alone diagnostics.

A multiport memory option, the MA780, is also available on VAX-11/780 systems. It can be applied either as a processor interconnect or it can be used to upgrade to a VAX-11/782.

If the MA780 is used as an interconnect, up to two multiport options can be added to a system, each supporting up to 2 MB of shared memory. This increases the VAX-11/780's maximum physical memory from the 8 MB limit for local main memory to 12 MB. Up to four VAX-11/780 systems may share an MA780 memory.

When the MA780 is part of a VAX-11/782 configuration, it is used differently. All main memory resides in the MA780 and is shared by two VAX-11/780 processors. In this instance, up to two MA780s can be used, providing a total of 8 MB of shared main memory.

### The Input/Output Subsystems

VAX-11/730 Systems — The UNIBUS subsystem connects most medium and low speed peripheral devices to the VAX-11/730 system. An asynchronous, bidirectional bus, the UNIBUS lets the user select

from a range of existing peripherals (those supported by VAX/VMS and diagnostics) and also provides easy connection for customer-designed special devices.

VAX-11/750 Systems — The VAX-11/750 system configuration includes one UNIBUS adapter as standard equipment. Up to three MASSBUS adapters or one additional UNIBUS and two MASSBUS adapters can be added for connection to mass storage devices and other peripherals.

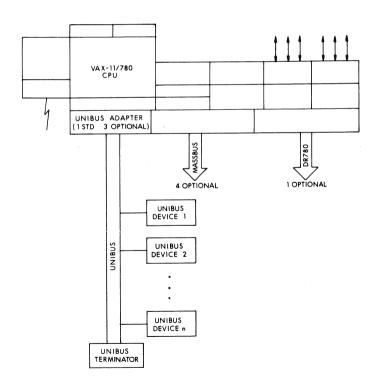

VAX-11/780 Systems — The VAX-11/780's I/O subsystems also include UNIBUS and MASSBUS adapters. Each system's configuration includes one UNIBUS adapter as standard equipment with the capability to add up to three more as options. Up to four MASSBUS adapters can also be included.

The VAX-11/780 offers as an option a very high performance, 32-bit, general purpose parallel interface which allows user devices to be connected directly to the system's Synchronous Backplane Interconnect. Called the DR780, it is capable of transferring data to and from memory at speeds of up to 6.67 MB per second. (The VAX-11/782 does not support this option.)

#### READING THIS HANDBOOK

For more information on the specific VAX processors, refer to the following parts of the book:

- Part II—The VAX-11/730

- Part III—The VAX-11/750

- Part IV—The VAX-11/780

The VAX-11/782 is covered in Chapter 19. Part V of the book discusses the reliability, availability, and maintainability features of VAX systems. Part VI includes the Appendices and the Glossary.

# PART II THE VAX-11/730

# CHAPTER 2 VAX-11/730 CONSOLE SUBSYSTEM

| FEATURES                                       | BENEFITS                                                                                                                                                                                                     |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Console terminal                               | Dual function as console and user terminal results in hardware savings                                                                                                                                       |

| Console command language                       | Gives the user a powerful, yet easy-to-use, debugging tool                                                                                                                                                   |

| Standard ASCII terminal                        | Provides a high degree of flexibility                                                                                                                                                                        |

| EIA communications interfacing                 | Allows standard industry-compatible communications                                                                                                                                                           |

| Front panel switches and indi-<br>cator lights | Offer control and status of certain aspects of the machine operation                                                                                                                                         |

| Remote access port                             | Allows use of a second or remote console terminal for automated product test and the Remote Support option                                                                                                   |

| Dual TU58 cartridge tape drives                | Provide inexpensive, reliable devices and mediums for: loading CPU microcode; booting; diagnostics; field updates to microcode, diagnostics, and software; and convenient personal data storage on cartridge |

| Unattended reboot                              | The system reboots itself upon recovery of electricity after a power failure or other system crash if the Auto Restart switch is in the ON position                                                          |

#### INTRODUCTION

The VAX-11/730 console subsystem is designed to allow the user to interactively communicate instructions to the central processing unit using the console terminal and the console command language. Five major elements make up the VAX-11/730 console subsystem:

- A front panel on the CPU cabinet with switches and indicator lights

- 2. A separate ASCII terminal, called the console terminal

- 3. A remote access port

- 4. A dual TU58 tape cartridge drive in the CPU box

- 5. A special console command language with simple commands the user types from the console terminal

The integral TU58 tape cartridge drives are used to load the CPU microcode, boot the system, load diagnostics, and update the operating system software. DIGITAL also supports the TU58 under VAX/VMS for data storage and retrieval.

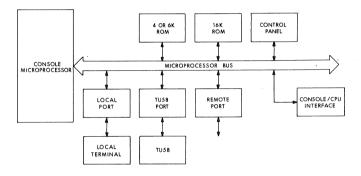

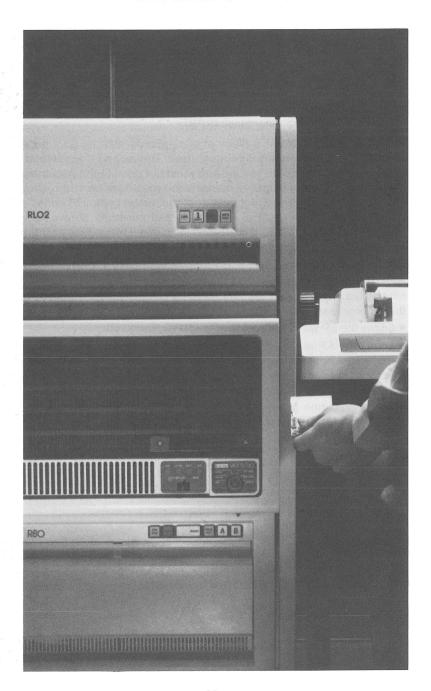

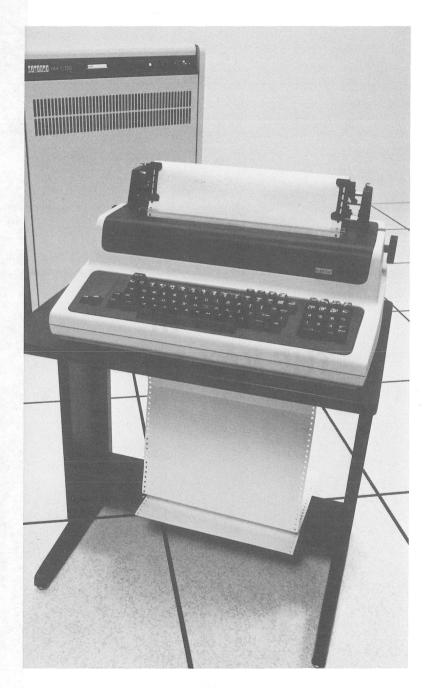

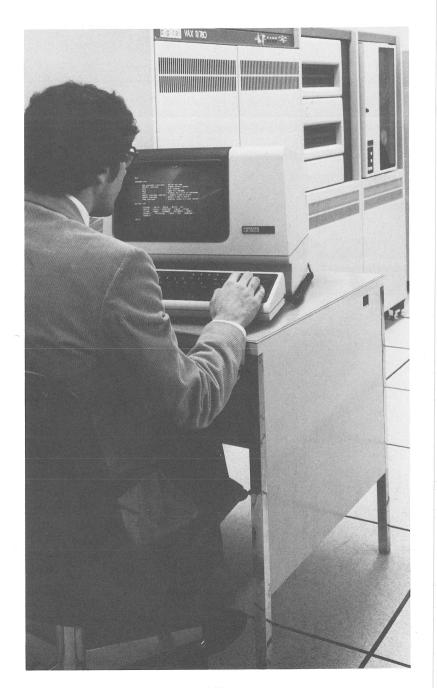

Figure 2-1 illustrates the hardware elements of the VAX-11/730 console subsystem.

Figure 2-1 VAX-11/730 Console Subsystem

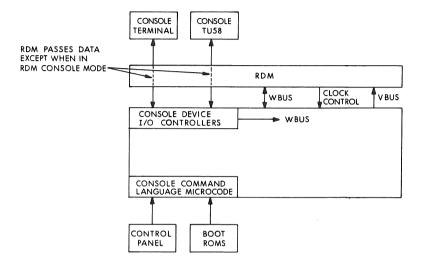

#### **CONSOLE MODES**

The VAX-11/730 console runs in two modes: program mode and console mode. These modes are mutually exclusive. One of the modes will always be enabled while there is power to the machine. In program mode (also known as the system terminal mode), the console functions like the other terminals on the VAX-11/730 system. In this mode the console passes characters between the terminal and the program.

When the CPU is not executing instructions, it is halted, and the console terminal is in console mode. In this mode, the CPU is receptive to console commands.

Direct Memory Access (DMA) activity to memory can also occur with the terminal in console mode, and all DMA transactions in progress will continue even when the CPU is halted. This allows the machine to be halted without destroying these transactions; however, interrupts will not be serviced while the machine is halted. They will be serviced following a CONTINUE from the console.

Table 2-1 lists the actions that cause the CPU to halt and enter console mode. When the keylock switch is in either Disable position (discussed in the Six-Position Keylock Switch section) and a CTRL P is typed, the machine will not halt.

Table 2-1 Console Halt Codes

| Code | Meaning                       |

|------|-------------------------------|

| 02   | CTRL P typed on the console   |

| 04   | Interrupt stack not valid     |

| 05   | CPU double error              |

| 06   | Halt instruction executed     |

| 07   | Invalid SCB vector            |

| 0A   | CHMX from the interrupt stack |

| 0B   | CHMX to the interrupt stack   |

| 0C   | SCB physical read error       |

When the processor enters the console mode it types on the console terminal the address contained in the program counter (PC), a two-digit code which identifies the reason for the halt, and the console prompt symbol, >>>. The prompt symbol shows that the console program is looping, waiting for a command.

#### **VAX-11/730 FRONT PANEL**

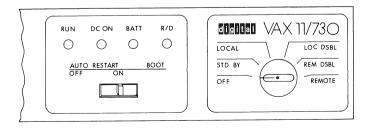

The front panel of the VAX-11/730 has 2 switches and 4 red indicator lights. Figure 2-2 illustrates the front panel controls and indicators.

Figure 2-2 VAX-11/730 Front Panel Controls and Indicators

#### Six-Position Keylock Switch

When the keylock switch is in the **Off** position, no power is applied to the CPU.

Power is applied to the WCS module and Main Memory if the switch is in the **Standby** position.

Table 2-2 describes the remaining four keylock positions.

#### NOTE

In Table 2-2, "characters" refer to console command language commands and control characters.

Table 2-2

| Position       | Console Mode                                                                                                                                                                                            | Program Mode                                                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Local          | The console accepts and interprets all characters. The Remote Support (RS) line is disabled.                                                                                                            | All characters except for CTRL P are passed to the program. The RS line is disabled.                                                           |

| Remote         | The local terminal will be disabled upon establishing the RS connection and may be re-enabled by commands from the RS host. The console accepts and interprets all characters from the remote terminal. | All characters except CTRL P passed by the remote terminal (or the local terminal if it has been re-enabled by the remote host) to the program |

| Local/Disable  | All characters are ignored. The remote line is disabled.                                                                                                                                                | All characters are passed to the program.                                                                                                      |

| Remote/Disable | All characters are ignored. The local terminal is disabled and the remote line is enabled.                                                                                                              | The remote line may be used as a normal terminal, passing all characters to the program.                                                       |

## **Auto Restart Switch**

The Auto Restart switch is a three position toggle switch that controls the machine on a power-up sequence. It has the following three positions:

- OFF—The console will halt after loading the microcode. The processor remains halted after a HALT instruction is executed or power is restored

- ON—The console will load microcode and execute a command file called DEFBOO.CMD. If any halt except a CTRL P halt is executed, or if power is restored following a powerfail, the console will attempt to restart the operating system.

- Boot (momentary)—The console will execute DEFBOO.CMD if the console is in the console mode idle loop (>>>).

## State Indicator Lights

The lights on the front panel indicate the following:

- Run—Indicates that the processor is executing instructions

- DC On—Indicates the +5 V is between 4.75 and 5.25 volts, and ±15

V is at least ±13.5 volts

- Remote—Indicates that a remote connection has been made. The light blinks during modem transitions. This light only works if the Remote Support option is used

# **Diagnostic and Maintenance Aids**

The independent console processor of the VAX-11/730 allows testing of other system components by console-based microdiagnostics. Other diagnostic aids related to the console subsystem include:

- Remote Support (RS) option that provides automated checkout capability and an RS or ASCII port

- ROM-resident self-test that can be optionally invoked at power-up and on command

- Voltage monitoring circuits that are incorporated to check +5 V and +15 V

- Monitoring of UNIBUS AC LO

- Customer Runnable Diagnostics

### CONSOLE TERMINAL

The console terminal is a powerful tool within the VAX-11/730 console subsystem. By using the console command language, the user can instruct the CPU to perform a wide variety of functions. When the console terminal is in console mode, it is dedicated exclusively to controlling CPU functions such as examining and depositing data in

memory. Console mode also allows the processor to be started, self-tested, initialized to a known state, and single-stepped through instructions. In contrast, program mode dedicates the console terminal to user application processes and the VAX/VMS operating system. In program mode, the CPU will not recognize console commands.

## **Console Terminal Communications**

The electrical interface for the console terminal is an industry-standard full-duplex EIA RS232-C line. The speed of the line is switch-selectable to 300, 1200, 2400, and 9600 baud.

## CONSOLE COMMAND LANGUAGE

The VAX-11/73O console command language gives the user an efficient way of communicating with the console subsystem. Instead of using the traditional toggle switches and lights, a user can communicate with the console subsystem by typing simple commands on the console terminal. These instructions to the CPU can only be communicated when the console terminal is in console mode.

Console commands, with the exception of the Directory command, are specified by a single letter with optional modifiers. (The Directory command is specified by DIR.)

# **Console Command Syntax and Semantics**

The syntax and semantics for the console command language are as follows:

| Symbol              | Function                                                                                                                                                                                                                                  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <>                  | Angle brackets are used to denote category names. For example, the category name <address> may be used to represent any valid address, instead of actually listing all the strings of characters that can represent an address.</address> |

| []                  | Brackets surrounding part of an expression indicate that part of the expression is optional.                                                                                                                                              |

| <space></space>     | Represents one typed space.                                                                                                                                                                                                               |

| <count></count>     | Represents a numeric count in hexadecimal, 32 bits. Leading zeros may be omitted.                                                                                                                                                         |

| <address></address> | Represents an address argument. Valid<br><address> types are explained later in<br/>relation to specific commands. Virtual ad-</address>                                                                                                  |

dresses that reference nonexistent or nonresident pages will cause the console to abort execution of the console command which referenced that address. An appropriate error message will be displayed. Leading zeros may be omitted.

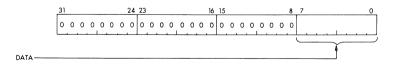

<DATA> Represents a numeric argument. Leading

zeros may be omitted.

< QUALIFIER> Represents a command modifier (also

called a *switch*). Valid < QUALIFIER> types are explained later in relation to specific

commands.

<INPUT-PROMPT> Represents the console's input prompt

string >>>.

<CR> Carriage return.

<LF> Line feed.

# **Prompts**

There are three different prompts given by the system:

ROM> The console subsystem is not able to boot

itself and is running in a limited mode. A CTRL-C can be typed to try to reboot the

system.

>>> The console terminal is in console mode

MIC> The micromonitor is controlling the console

subsystem.

# Typing Errors and Illegal Characters

Typing errors may be corrected using the DELETE key as long as a <CR> for the line has not been typed. When the DELETE key is typed, the console prints a backslash (\) and the character being deleted. The console also adds a backslash between the last deletion and the next input character.

Example:

Operator types: 1278 < del > 34

Console prints: 1278\87\34

Console sees: 1234

## **Control and Special Characters**

CTRL-C

Control characters are typed by holding down the CTRL key and typing the named letter. Unless otherwise specified, the control characters listed are for use when in console mode.

|                       | instructs the console program to return to its idle loop and reissue the prompt. |  |

|-----------------------|----------------------------------------------------------------------------------|--|

| CTRL-P (console mode) | Same as CTRL C.                                                                  |  |

| CTRL-P (program mode) | Halts the machine if key switch is in any of the Enable positions.               |  |

| CTRL-O                | Throws away output until pressed again.                                          |  |

| CTRL-R                | Retypes current contents of input buffer.                                        |  |

| CTRL-S                | Stops printing. Only control characters are                                      |  |

recognized while in this state.

CTRL-Q Resumes printing.

CTRL-U Aborts accepting current input line. Returns

to idle loop and reissues prompt.

Aborts current operation. This command

Break Same action as CTRL-C and CTRL-P in

console mode.

ESC In console mode, causes console to re-exe-

cute the last command typed at the console

terminal

# **Special Notes**

- 1. Qualifier switches (/B, /P, /N:, etc.) may be used anywhere in the command string, except at the beginning. They act as field terminators, just as spaces and carriage returns do.

- Until the POWER.CMD and CODE0n.CMD files have finished execution, the CPU will not respond properly to user commands that access the CPU. These command files should not be aborted.

User commands that require the CPU microcode are:

```

В

C

D and E

/M

/P

/V

/G

/1

PS[L], PC, Rn, SP

L/P

M

Ν

S/P

W

(Used to detect completion of POWER.CPU)

X/P

```

# **Console Command Language Instructions**

## **BOOT Command**

SYNTAX:

B[<SPACE><TU58-SELECT>][<SPACE><DEVICE-NAME>]<CR>

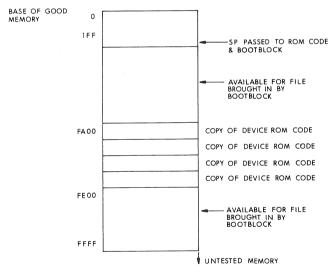

This command causes the Stack Pointer (SP) to be loaded with <the address of the start of a 64 KB block of good memory> +\f\X200. (The block of good memory was found by POWER.CPU at power-up time.) It then causes a boot command file to be read from one of the console TU58 drives and executed. Which boot command file is read in and executed is determined by the remaining parameters.

If <TU58-SELECT> is not specified, the console searches for the boot command file on the default TU58. The default TU58 is the TU58 which was used to load microcode when the CPU was powered up.

If <TU58-SELECT> is specified as DD0:, then the console searches on the external TU58.

If <TU58-SELECT> is specified as DD1:, then the console searches on the internal TU58.

If <DEVICE-NAME> is not specified, the file DEFBOO.CMD is read from the indicated TU58 drive and executed.

If <DEVICE-NAME> is specified, it is of the format DQn where n is the unit number of the R80 or RL02 drive which holds the system disk. The file DQnBOO.CMD is read in from the indicated TU58 drive and executed.

### **CONTINUE Command**

SYNTAX: C<CR>

If the CPU clock is running, the CONTINUE command restarts execution of a halted program at the address currently contained in the Program Counter.

If the CPU clock is not running due to a microcode break point while in program mode, the clock is restarted and the console enters program mode. If the clock is off not as the result of a microcode break point, the console turns the clock on and remains in console mode.

RESPONSE (Clock on): <CR><LF>(Console enters Program I/O mode.)

RESPONSE (Clock off): >>>

## **DEPOSIT and EXAMINE Commands**

SYNTAX:

DI<QUALIFIER-

LIST><SPACE><ADDRESS><SPACE><DATA><CR>

E[<QUALIFIER-LIST>][<SPACE><ADDRESS>]<CR>

DEPOSIT and EXAMINE commands will be treated together because their formats are quite similar. Both commands require definition of the address space and the size of the operand in addition to the address.

#### Table 2-3 DEPOSIT and EXAMINE QUALIFIERS

## **Data Length Qualifiers**

/B Byte

/W Word

/L Longword

**Repetition Qualifiers**

/N:<COUNT> Executes the EXAMINE or

DEPOSIT < COUNT>+1 times. For example, this allows five locations to be examined

by specifying /N:4.

**Address Space Qualifiers**

/V Virtual Address

/P Physical Address

## VAX-11/730 Console Subsystem

/I Internal Register

/G General Register

/M Machine Dependent Internal

Register

/U Console microcomputer

/C Writable Control Store (WCS)

# **Address Specification**

nnnnnnn Hex Number

PSL or PS. PC.SP

Rn n=0 to  $\uparrow XF$  (Hex)

\* Last Location

+ Next Location

- Previous Location

Last data used as address

(DEPOSIT only)

Data

nnnnnnn Hex Number

DEPOSITs (writes) or EXAMINES (reads) < DATA> at the <AD-DRESS> specified. The address space and size used will depend upon the qualifier or qualifiers specified with the command. If no address space qualifier is used, the default is the last used address space and data length; following another DEPOSIT or EXAMINE, the same space as that of the previous command will be used as the default.

If no size qualifier is typed, the default for a physical or virtual DEPO-SIT or EXAMINE is whatever the size was in the previous EXAMINE or DEPOSIT.

<ADDRESS> must be one to eight hexadecimal digits. The initial default is zero; however, the default is unpredictable when the address space is changed. Following another virtual or physical DEPOSIT or EXAMINE, the default is the sum of the address from the last EXAMINE/DEPOSIT plus the size from the last EXAMINE/DEPOSIT. Typing a + or - for <ADDRESS> (for DEPOSIT only) will also get this default. Following another IPR or GPR EXAMINE/DEPOSIT, the default is the sum of the address from the last EXAMINE/DEPOSIT plus one. Using

a PSL for <ADDRESS> performs a longword reference of the Processor Status Longword, independent of the address space and size

<DATA> must be represented by one to eight hex digits. If more digits than specified by the size are supplied, the extra digits on the left are ignored; if fewer digits are supplied, zeros are appended to the left.

Sample DEPOSIT response: A successful DEPOSIT always receives <INPUT-PROMPT>.

Sample EXAMINE responses (in bold print):

>>> E/P 1234

Examine physical address 1234

## P 00001234 ABCDEF89

>>> E/V 1234

Examine virtual address 1234

P 00005634 01234567

Note that virtual

EXAMINEs display the translated physical

address

>>> F/G 0

Examine general register R0

## G 00000000 98765432

Index of EXAMINEs and DEPOSITS

E\*<CR>

E<CR>

E<SPACE><ADDRESS><CR>

E/G<SPACE><ADDRESS><CR>

E/I<SPACE><ADDRESS><CR>

E/P<SPACE><ADDRESS><CR>

E/V<SPACE><ADDRESS><CR>

E<SPACE>PSL<CR>

E<SPACE>PSL<CH>

E/W/P<SPACE><ADDRESS><CR>

E/P/W<SPACE><ADDRESS><CR>

E/L/V<SPACE><ADDRESS><CR>

D\*<DATA><CR>

Examine the last location examined or deposited into

Examine the next location

Examine <ADDRESS>; all switches are defaulted to last EXAMINE or DEPOSIT

Examine GPR; register number is <ADDRESS>; <ADDRESS> must be a value from 0 to

Examine IPR; register number is <ADDRESS>

Examine physical <ADDRESS>

Examine virtual <ADDRESS>-

Examine PSL

Examine a word at physical

<ADDRESS>

Examine a word at physical <ADDRESS>

Examine a longword at virtual <ADDRESS>

Deposit <DATA> in the last location that was deposited into or examined

## VAX-11/730 Console Subsystem

D+<DATA><CR>

D/G<SPACE><ADDRESS><SPACE><DATA><CR>

D/I<SPACE><ADDRESS><SPACE><DATA><CR>

D/P<SPACE><ADDRESS><SPACE><DATA><CR>

D/V<SPACE><ADDRESS><SPACE><DATA><CR>

D<SPACE>PSI <SPACE><DATA><CR>

D<SPACE><ADDRESS><SPACE><DATA><CR>

D/V/W<SPACE><ADDRESS><SPACE><DATA><CR>

D/L/P<SPACE><ADDRESS><SPACE><DATA><CR>

Deposit <DATA> in the next sequential address

Deposit < DATA> in GPR

<ADDRESS>

Deposit < DATA> in IPR <ADDRESS>

Deposit <DATA> in physical

<ADDRESS>

Deposit < DATA> in virtual <ADDRESS>

Deposit < DATA > in PSL

Deposit < DATA> in < ADDRESS>

Switches are defaulted to

previous switches

Deposit a word of <DATA> in virtual <ADDRESS>

Denosit a longword of <DATA> in physical <ADDRESS>

## **DIRECTORY Command**

SYNTAX: DIR < CR >

Takes a directory of the specified TU58 drive or the default if none is specified.

DIR

Takes default

DIR<SPACE>DDn:

where n = 0 or 1

0 is the external TU58 and 1 in the internal TU58.

## **HALT Command**

SYNTAX: H<CR>

Causes Halt PC to be printed, but the machine must already be halted to execute this command.

RESPONSE:

?nn<SPACE>PC=xxxxxxxxx<CR>

<LF><INPUT-PROMPT>

#### **INITIALIZE Command**

I<CR> SYNTAX:

This command performs the following functions:

- Starts the microcode at microaddress 0

- Initializes the TU58 controller

- Initializes the internal machine constants

- Initializes the processor

- Causes a deposit to SP with the address of (the start of 64 Kbytes of good memory) + †X200

RESPONSE: <CR><LF><INPUT-PROMPT>

## **LOAD Command**

SYNTAX:

L[<QUALIFIER-LIST>]<SP><FILE-SPECIFICATION><CR>

The Load command is used to read file data from the console's load device to main memory, or to the WCS. If no qualifier is given with the Load Command, physical main memory is loaded.

## Table 2-4 LOAD QUALIFIERS

/S:<ADDRESS>

The START qualifier is used to specify a starting address for the load. If no START qualifier is given, the console will start loading at Address 0.

/C

The C qualifier is used to specify that the WCS is to be loaded,

/P

The Physical qualifier is used to force Physical main memory as the destination of the load.

#### MICROSTEP Command

SYNTAX: M[<SPACE><COUNT>]<CR>

The CPU is allowed to execute the number of microinstructions indicated by <COUNT>. If no <COUNT> is specified, one instruction is performed, and the console enters SPACE-BAR-STEP mode.

The program may be restarted by typing C<CR>, and will continue executing from the current instruction. Typing an N<CR> will cause the program to finish the current instruction and then halt.

### NOTE

Stepping through instructions that access the console will not work.

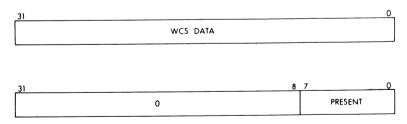

RESPONSE: <CR><LF><TAB> UPC= <CONTENTS OF MI-CRO PC>

## **NEXT Command**

SYNTAX: N[<SP><COUNT>]<CR>

The CPU is allowed to execute the number of MACRO-instructions indicated by <COUNT>. If no <COUNT> is specified, one instruction is performed, and the console enters SPACE-BAR-STEP mode.

The console enters program mode immediately after issuing the Step, and reenters console mode as soon as the Step completes.

## NOTE

Interrupts are blocked while executing the NEXT command from the console.

RESPONSE: <CR><If>

?02<SPACE><SPACE>PC=<CONTENTS OF PC>

## **REPEAT Command**

SYNTAX: R<SP><CONSOLE COMMAND><CR>

R <CONSOLE COMMAND> causes the console to repeatedly execute the <CONSOLE COMMAND> specified until execution is terminated by a CTRL-C, CTRL-P, or a BREAK. The console commands that may be specified are DEPOSIT, EXAMINE, and INIT.

RESPONSE: <dependent on command specified>

## **START Command**

SYNTAX: S[<SP><ADDRESS>]<CR>

or

S/C<SP><ADDRESS><CR>

The START command is normally used to start execution of programs that run without the operating system and without the diagnostic supervisor. START performs the equivalent of the following console commands:

- 1. Initialize the CPU.

- Deposit <address> into the Program Counter (PC). If no address is specified, the current value of the PC is used.

- 3. Perform the Continue function to begin program CPU execution.

Programs which may be started this way must be loaded into main memory before the START command is given. (See LOAD command.) For example:

>>>S 1000

Start the program that begins at address 1000.

## **TEST Command**

SYNTAX: T<CR>

This command attempts to find the program ENKAA.EXE on Drive 0 or 1. If found, it is loaded and control is transferred to it. If it is not found,

the system reloads itself and returns to console mode. The T command, whether it finds ENKAA.EXE or not, destroys the state of the machine.

Once the MIC> prompt is reached, microdiagnostics can be performed.

# **BINARY LOAD/UNLOAD Command**

SYNTAX:

X<SP><ADDRESS><SP><COUNT><CR><CHECKSUM>

<ADDRESS> Starting address of load

<COUNT> Number of bytes to be trans-

ferred

<CHECKSUM> 2's complement checksum of

command string or binary data

The BINARY LOAD/UNLOAD command instructs the console to load binary data into or unload binary data from physical memory, starting from the location specified by <ADDRESS>. A <COUNT> with bit <31> set indicates BINARY UNLOAD. If bit <31> is clear, it is a BINARY LOAD. The remaining bits in <COUNT> indicate the number of bytes to Load or Unload. After a correct 2's complement checksum calculation, the console issues an <INPUT-PROMPT>, but remains in binary mode and either sends data to the user or prepares to receive data. If the checksum shows an error, a message and an <INPUT-PROMPT> are issued.

In UNLOAD, a binary string of data, of length <COUNT> + 1, will be sent once the <INPUT-PROMPT> indicates that the console has accepted the command. When <COUNT> is exhausted, the final byte is a console-calculated block checksum of all the data.

For LOAD, the console processes the command and <CHECKSUM>. Then, if the checksum is correct, the console responds with <INPUT-PROMPT>, followed by a string of bytes which is the binary data requested. A second checksum is calculated and processed as for the LOAD sequence.

## **Console Command Errors**

When a command is given that the console cannot properly process, it responds by typing ?nn. nn is an error code that describes the nature of the problem.

# **INTEGRAL TU58 CARTRIDGE TAPE DRIVES**

The dual TU58 tape cartridge drives are an important part of the console subsystem. The fundamental function of the TU58 is to load the CPU microcode. If one of the TU58s fails, the second TU58 may be used as backup. Additionally, because the TU58 is connected directly to the console subsystem, it retains the ability to run micro and macro level diagnostics even with some system components inoperative. This feature significantly increases system maintainability. The TU58 can be used to boot the system, to load files into physical memory, and to store files which describe and execute site-specific bootstrap procedures (see BOOTING THE VAX-11/730 SYSTEM later in this chapter).

The tape cartridge is preformatted and contains 256 KB, normally formatted in 512-byte records. The controller provides random access to any record. The TU58 searches at 60 inches per second (i/s) to find the file requested, then reads at 30 i/s. Data read from the tape are verified through checksums at the end of each record or header.

From the system operator's standpoint, the booting process is quite simple. For a typical system boot:

- 1. Turn on power to the console terminal.

- 2. Set the Auto Restart switch to the On position.

- 3. Set the Six-Position Keylock Switch to the Local or Local Disable position. The terminal will then print:

CONSOLE VERSION XX.XX

At power-up, the console subsystem bootstraps itself from the TU58, finds 64 KB of good memory, determines what CPU options are installed, and loads the appropriate CPU microcode. It then samples the Auto Restart switch. If it is in the OFF position, the console awaits further commands. If it is in the ON position, a bootstrap program is loaded and begins to execute.

## **Console Subsystem Action on Boot**

There are five distinct ways a boot sequence may be initiated on the VAX-11/730:

- A power-up sequence (Boot Switch or initial power application) with switch set to ON.

- 2. By typing the B command while in console mode.

- 3. Execution of a HALT instruction when the processor is in kernel mode and the Auto Restart switch is in the ON position.

- 4. Execution of an MTPR to the console register that invokes a boot.

- 5. Failure of a restart while the Auto Restart switch is in the ON position.

All five of the above mechanisms will initiate the following sequence of actions. Numbers 1 and 2 clear the bootstrap flag. Numbers 3, 4, and 5 will not.

- Clearing of the bootstrap flag.

- Checking of the bootstrap flag. If it is set, in most instances the machine halts. However, there are certain cases where it will attempt to reload all the control stores by starting the console program at its power-on startup point. If it is clear, then it sets the flag. This prevents bootstrap looping.

- Initialization of the CPU (This places the first address +200 of a 64 KB good block of memory into the SP.)

- Execution of the command file DEFBOO.CMD which loads the operating system from the specified mass storage device.

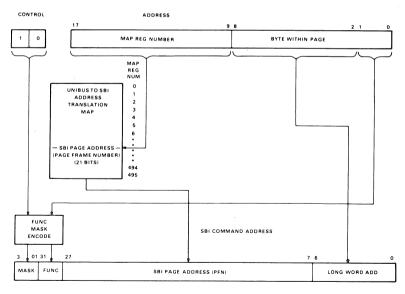

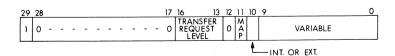

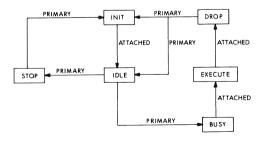

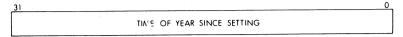

# **Console Subsystem Action on a Restart**