# VAXmate<sup>®</sup> Technical Description

digital

# VAXmate<sup>™</sup> Technical Description

#### © Digital Equipment Corporation 1987. All Rights Reserved.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies.

Hayes is a registered trademark of Hayes Microcomputer Products Inc. IBM-PC/AT is a trademark of International Business Machines Corp. MS and MS-DOS are registered trademarks of Microsoft Corporation.

The following are trademarks of Digital Equipment Corporation:

| digital      | DELNI        | VAX            |

|--------------|--------------|----------------|

| DEC          | DIBOL        | VAXmate        |

| DECconnect   | MASSBUS      | VMS            |

| DECmate      | PDP          | VT             |

| DECsystem-10 | P/OS         | VT220          |

| DECSYSTEM-20 | Professional | VT240          |

| DECUS        | Rainbow      | Work Processor |

| DECwriter    | RSTS         |                |

| DEMPR        | RSX          |                |

| DESTA        | UNIBUS       |                |

Printed in U.S.A.

### Contents

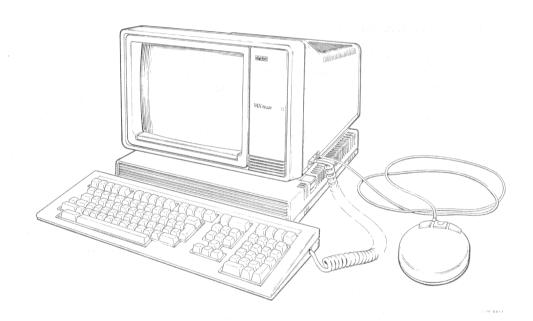

| Chapter | 1 | General | $\mathbf{D}$ | escri | ip | tion | 0 |

|---------|---|---------|--------------|-------|----|------|---|

|---------|---|---------|--------------|-------|----|------|---|

| 1.1 muoduction                          |     |

|-----------------------------------------|-----|

| 1.2 Hardware                            | 1-3 |

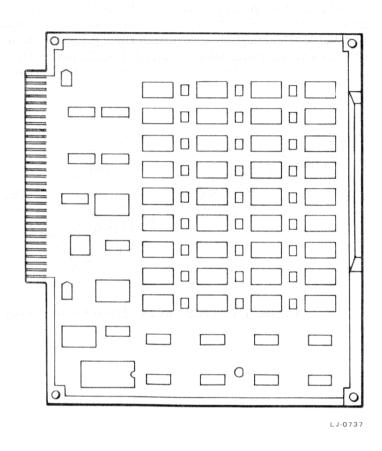

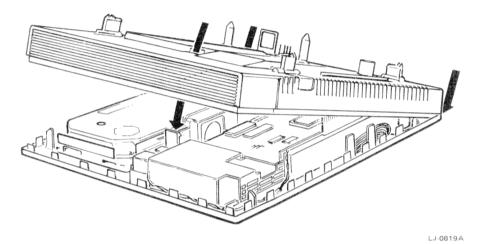

| 1.2.1 CPU/Memory Module                 | 1-4 |

| 1.2.2 I/O-Video Module                  |     |

| 1.2.2.1 Video Controller                | 1-4 |

| 1.2.2.2 Monitor - Amber or Green Screen | 1-6 |

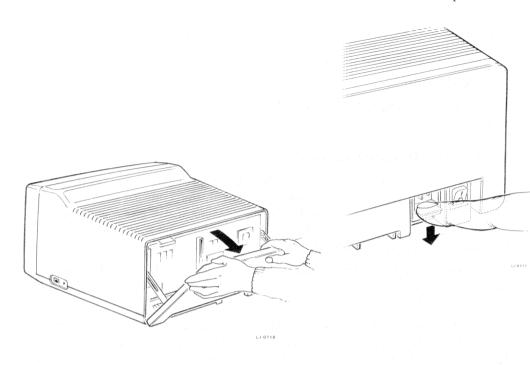

| 1.2.3 RX33 1.2 Mbyte Diskette Drive     | 1-7 |

| 1.2.4 ThinWire Ethernet                 |     |

| 1.2.5 Communications                    |     |

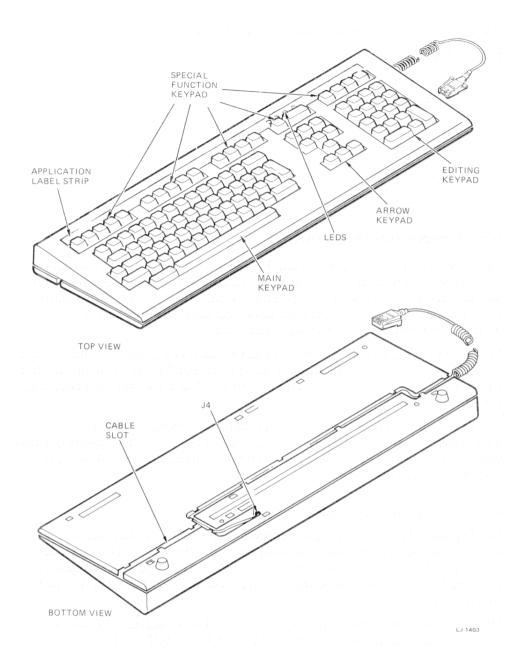

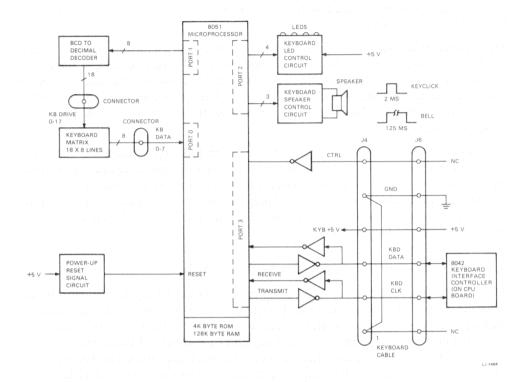

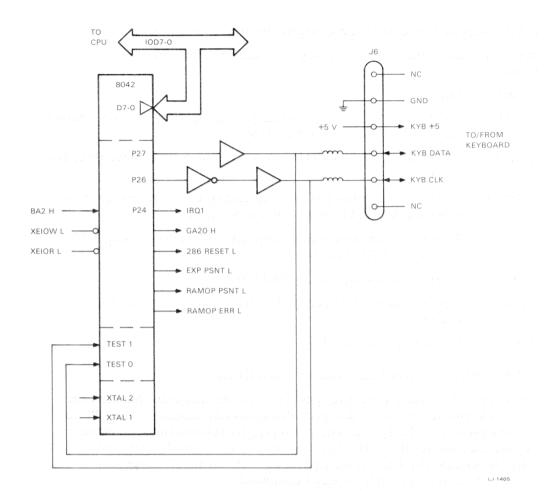

| 1.2.6 LK250 Keyboard                    |     |

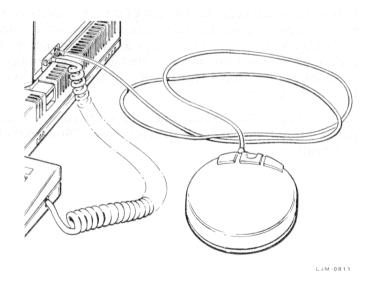

| 1.2.7 Mouse                             |     |

| 1.2.8 Power Supply                      |     |

| 1.2.9 Hardware Options                  |     |

| 1.3 Country Specific Configurations     |     |

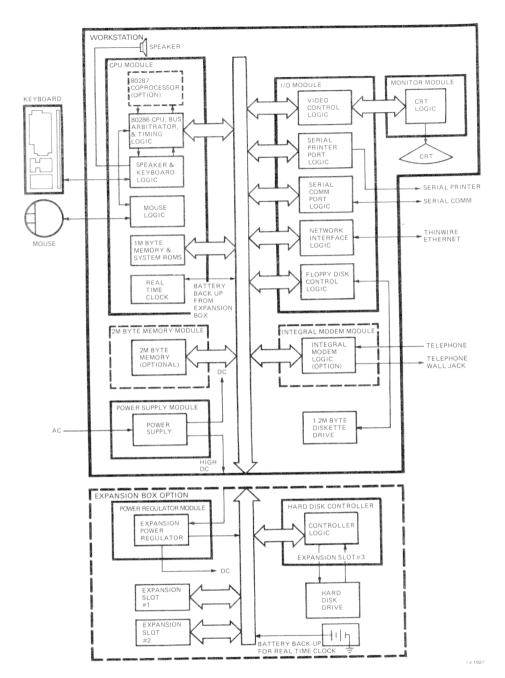

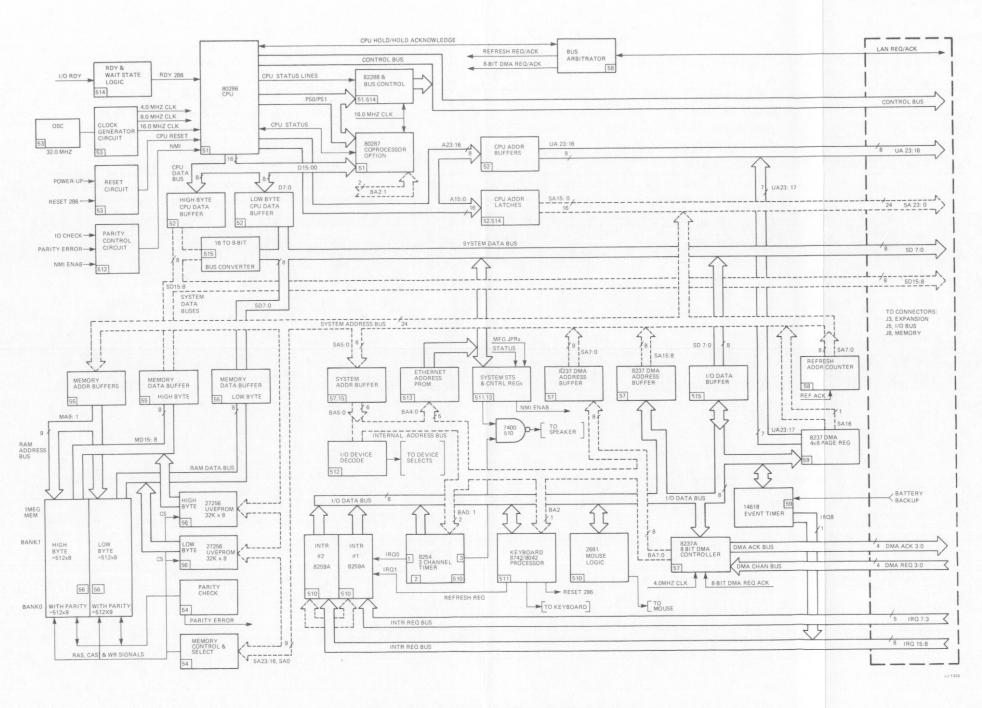

| 1.4 Technical Block Diagram             |     |

| S .                                     |     |

| Chapter 2 VAXmate CPU Module            |     |

| 2.1 Introduction                        | 2-1 |

| 2.2 Clock System                        |     |

| 2.3 Microprocessor                      | 2-2 |

| 2.4 Coprocessor                         | 2-3 |

| 2.5 Memory                              |     |

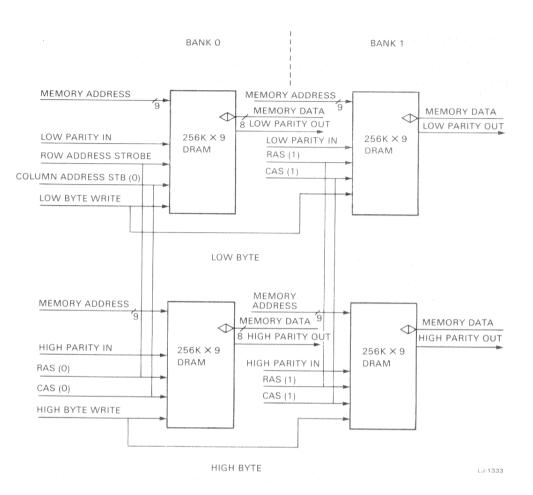

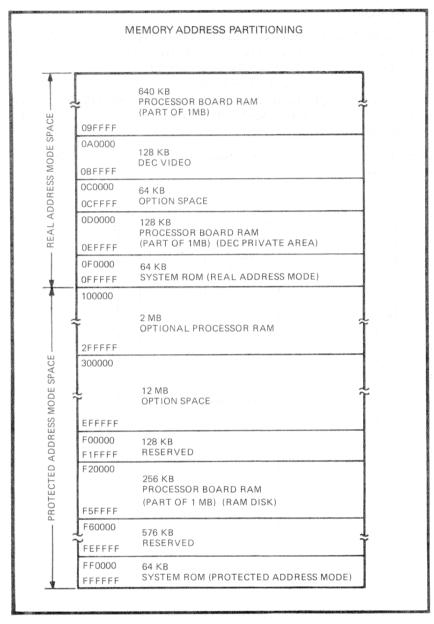

| 2.5.1 1 Mbyte RAM Memory                |     |

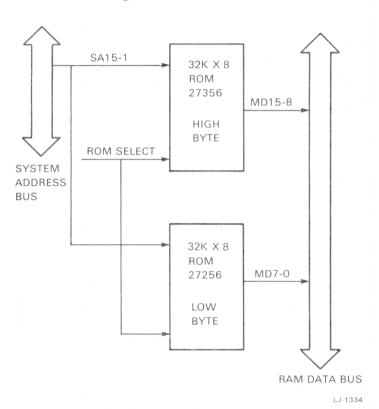

| 2.5.2 System ROM                        |     |

| 2.5.3 2 Mbyte Memory Option             | 2-7 |

| 2.5.3.1 Timing Modes                    |     |

| 2.5.3.2 Memory Option Module Interface  |     |

|                                         |     |

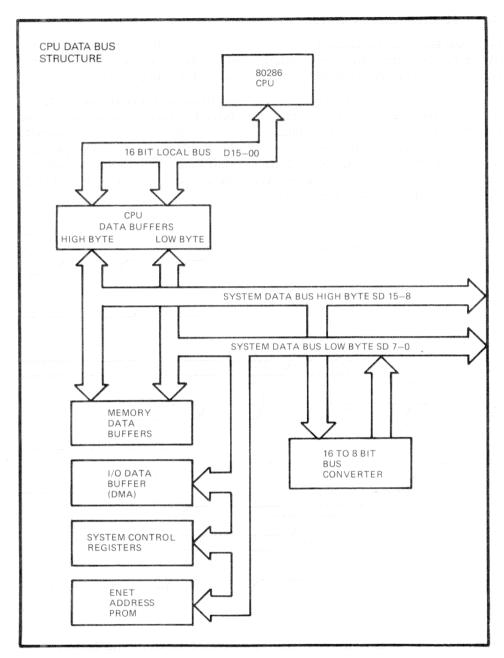

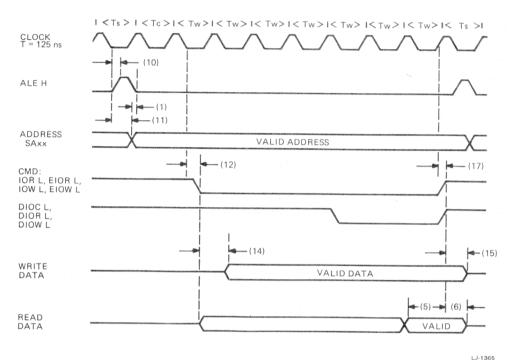

| 2.0  | Bus   |      | icture                              |      |

|------|-------|------|-------------------------------------|------|

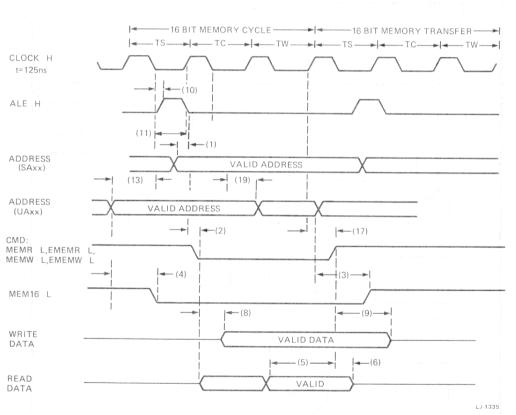

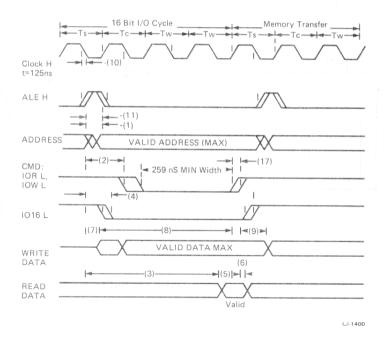

|      | .6.1  | 16-  | Bit Memory Cycle                    | 2-10 |

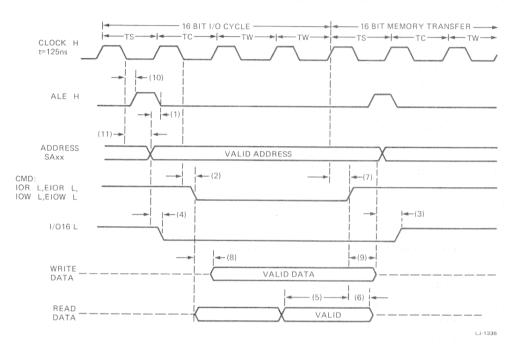

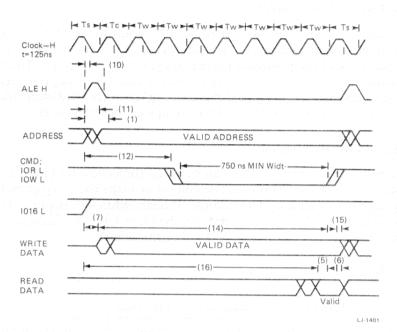

| 2    | .6.2  | 16-  | Bit I/O Cycle                       | 2-12 |

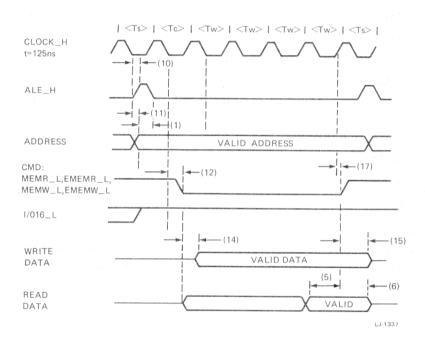

| 2    | .6.3  | 8-B  | it Memory Byte Transfer             | 2-14 |

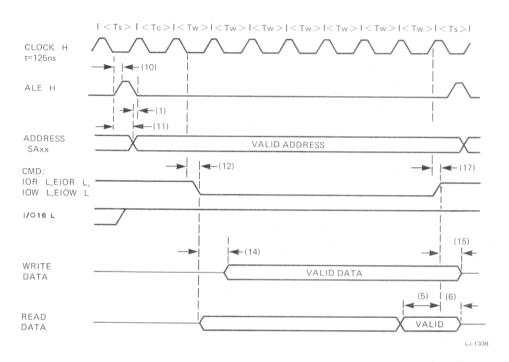

| 2    | .6.4  |      | it I/O Byte Transfer                |      |

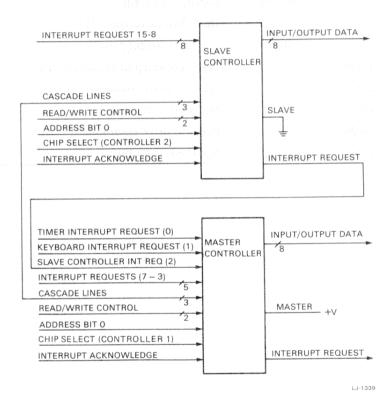

| 2.7  | Inte  | rrup | ot Controllers                      | 2-18 |

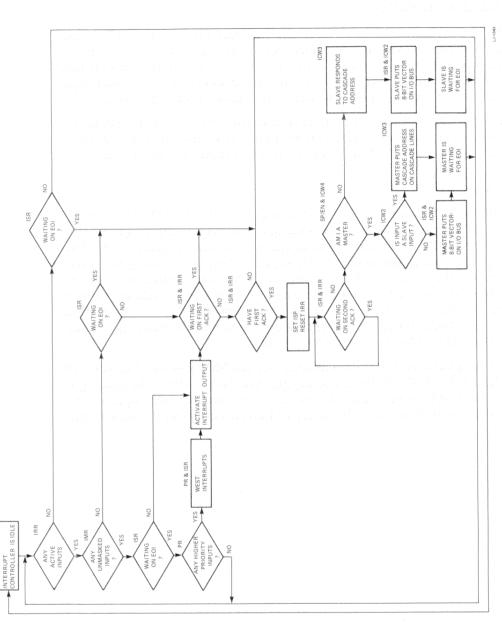

| 2    | .7.1  | Inte | errupt Processing                   | 2-18 |

|      | .7.2  | Rea  | d/Write Control                     | 2-21 |

| 2    | .7.3  |      | eration Command Words               |      |

| 2    | .7.4  | Inte | errupt Registers                    | 2-26 |

| 2    |       |      | errupt Sequence                     |      |

| 2    |       |      | errupt Processing                   |      |

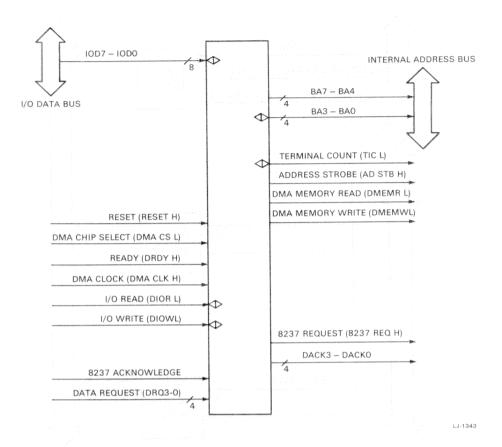

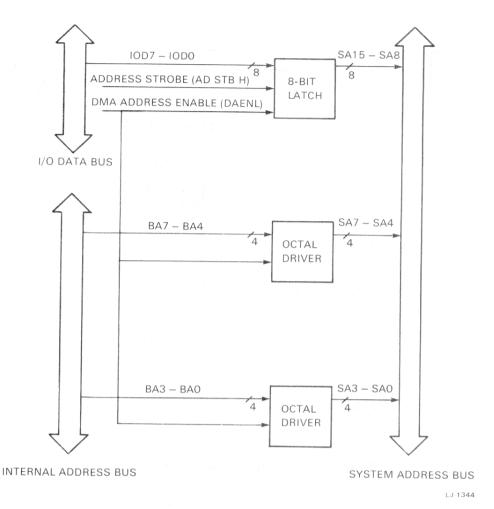

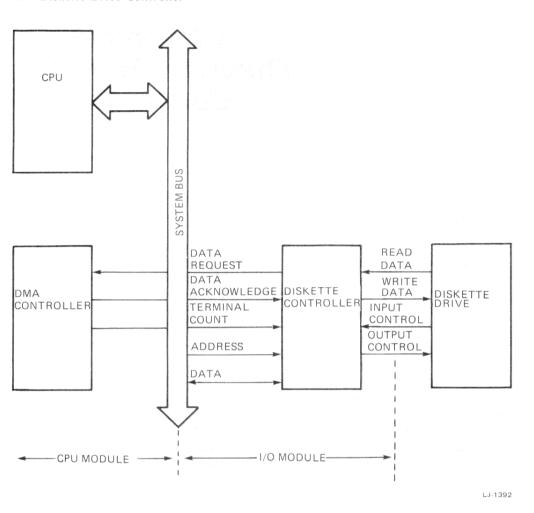

| 2.8  | DMA   | Co   | ntroller                            | 2-30 |

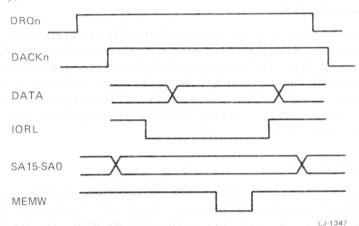

| . 2  | .8.1  | Оре  | eration                             | 2-30 |

|      | 2.8.1 | 1.1  | Device Cycles                       | 2-33 |

|      | 2.8.3 | 1.2  | Data Transfers                      | 2-34 |

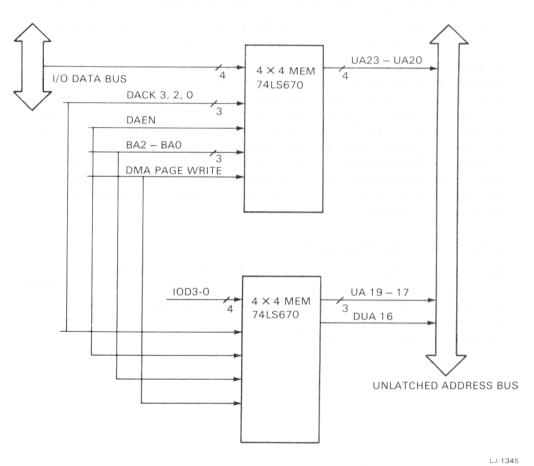

| 2    |       |      | A Page Registers                    |      |

| 2    |       |      | Mastership                          |      |

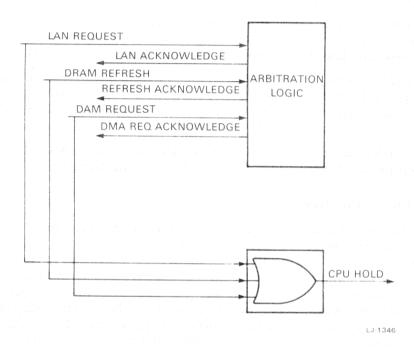

| - 2  | .8.4  | Bus  | Arbitrator                          | 2-37 |

| 2    |       |      | A Read Cycle                        |      |

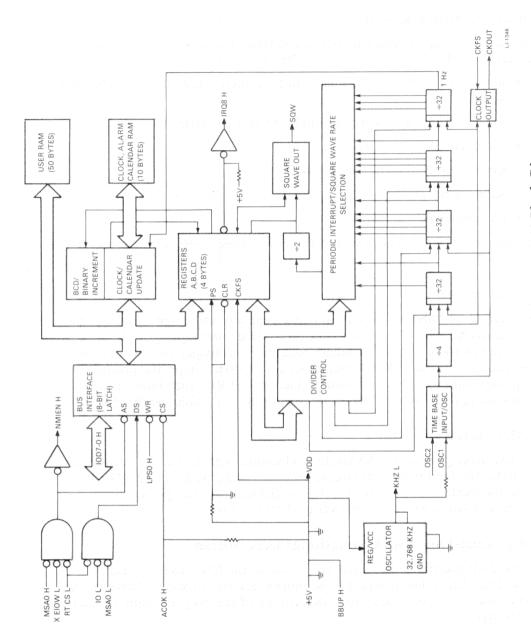

| 2.9  | Real  | Tim  | ne Clock and CMOS RAM               | 2-39 |

|      |       |      | erview                              |      |

|      | 2.9.1 |      | Input/Output                        |      |

|      | 2.9.1 | .2   | Address Map                         |      |

|      | 2.9.1 | .3   | Control and Status                  |      |

|      | 2.9.1 | .4   | Clocking                            |      |

|      | 2.9.1 | .5   | Battery Backup                      |      |

| 2    | .9.2  | Real | 1-Time Clock Functional Description |      |

|      | 2.9.2 |      | Power                               |      |

|      | 2.9.2 | 2.2  | Bus Interface                       |      |

|      | 2.9.2 | 2.3  | Registers A through D               |      |

|      | 2.9.2 | 2.4  | Clock, Alarm, and Calendar RAM      |      |

|      | 2.9.2 | 2.5  | BCD/Binary Increment                |      |

|      | 2.9.2 |      | Clock/Calendar Update               |      |

|      | 2.9.2 | 7    | Internal Time Base and Oscillator   |      |

|      | 2.9.2 | 2.8  | Divider Control                     |      |

|      | 2.9.2 | 2.9  | Square-Wave Output Selection        |      |

|      | 2.9.2 | .10  | Interrupt Selection                 |      |

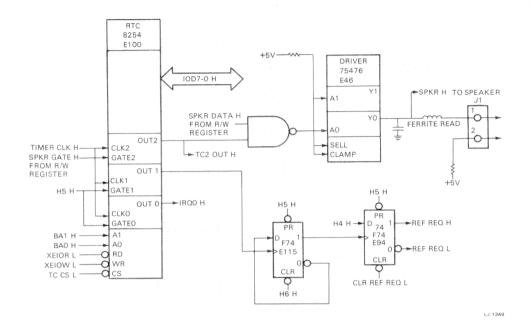

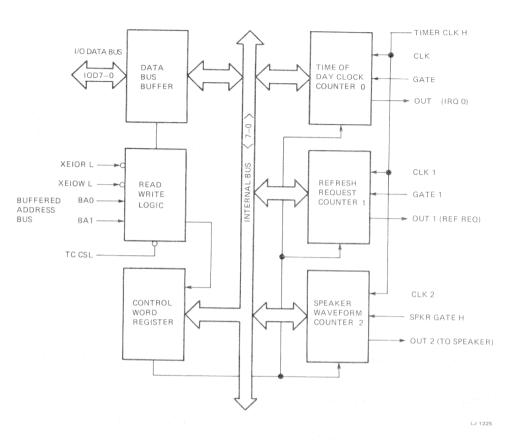

| 2.10 |       |      | Channel Programmable Counter/timer  |      |

|      |       |      | verview                             |      |

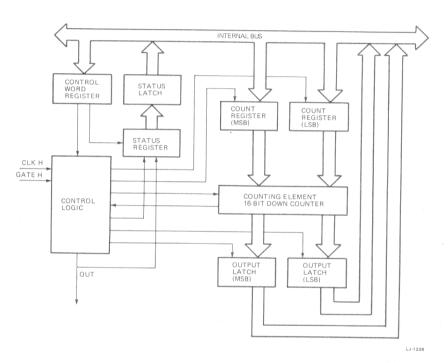

| 2    |       |      | nctional Description                |      |

| 2.10.2.1 Read/Write Logic                               | 2-49 |

|---------------------------------------------------------|------|

| 2.10.2.2 Control Word (CW) Register and Data Bus Buffer |      |

| 2.10.2.3 Counters 0, 1, and 2                           | 2-51 |

| 2.10.3 Mode Definitions                                 | 2-52 |

| 2.10.3.1 Mode 0 (Interrupt on Terminal Count)           | 2-53 |

| 2.10.3.2 Mode 1 (Hardware Retriggerable One-Shot)       | 2-53 |

| 2.10.3.3 Mode 2 (Rate Generator)                        | 2-53 |

| 2.10.3.4 Mode 3 (Square Wave)                           | 2-53 |

| 2.10.3.5 Mode 4 (Software Triggered Strobe)             | 2-54 |

| 2.10.3.6 Mode 5 (Hardware Triggered Strobe)             | 2-54 |

| 2.11 Mouse Information                                  |      |

| 2.11.1 Operation                                        |      |

| 2.11.1.1 Communication Interface                        |      |

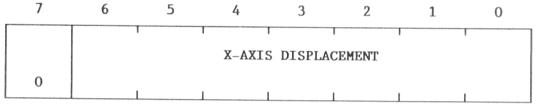

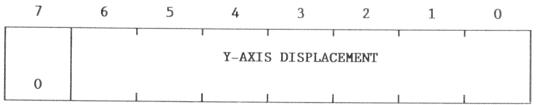

| 2.11.1.2 Data Format                                    | 2-57 |

| 2.11.1.3 Position Reports                               |      |

| 2.11.2 Operating Modes                                  | 2-59 |

| 2.11.2.1 Mouse Commands                                 |      |

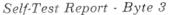

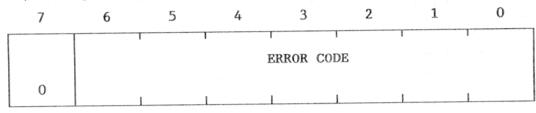

| 2.11.2.2 Power-Up Self Test and Identification          |      |

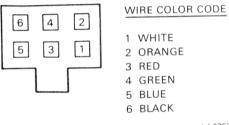

| 2.11.3 Mouse Connectors                                 |      |

| 2.11.3.1 VAXmate Connector                              | 2-62 |

| 2.11.3.2 Module Connector                               | 2-63 |

|                                                         |      |

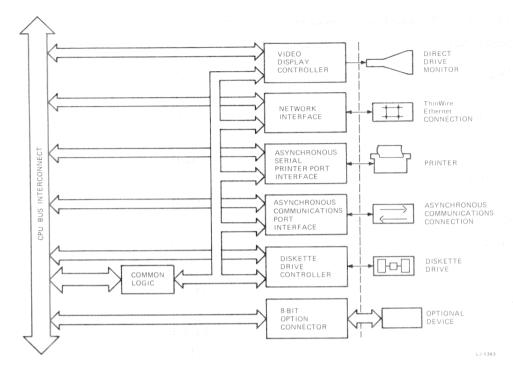

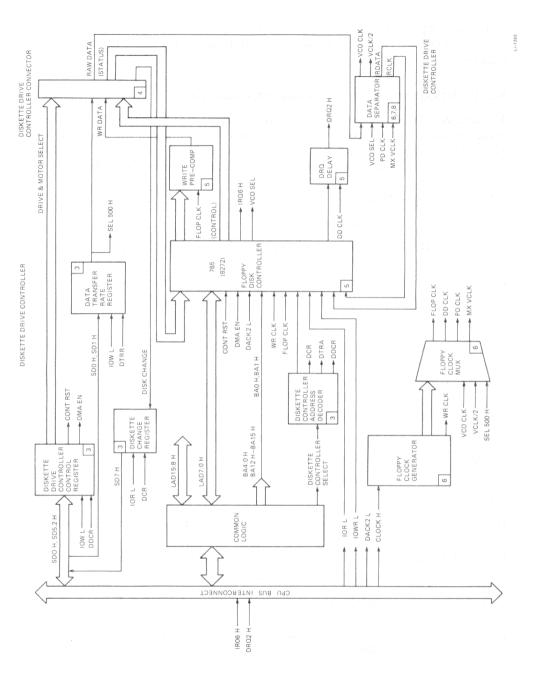

| Chapter 3 VAXmate I/O-Video Module                      |      |

| 3.1 Introduction                                        | 3-1  |

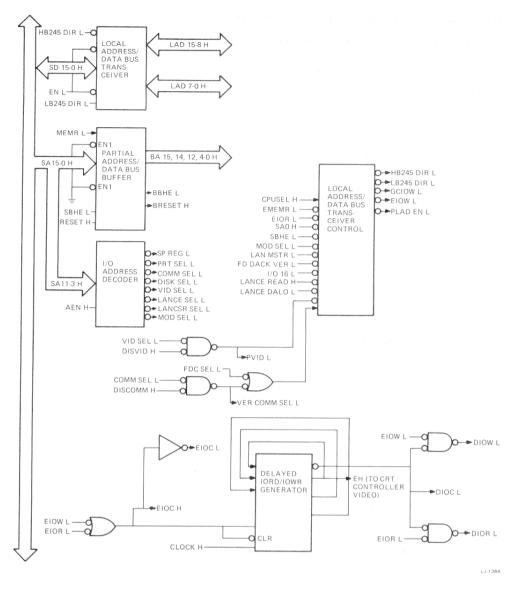

| 3.2 CPU BUS Interconnect                                | 3-3  |

| 3.3 8-Bit Option Interconnect                           | 3-6  |

| 3.4 Common Logic                                        | 3-7  |

| 3.4.1 Overview                                          | 3-9  |

| 3.4.2 Local Address/Data Bus Transceiver                | 3-9  |

| 3.4.3 Partial Address Bus Buffer                        |      |

| 3.4.4 I/O Address Decoder                               | 3-11 |

| 3.4.5 Local Address/Data Bus Transceiver Control        | 3-13 |

| 3.4.6 Delayed IORD/IOWR Generator                       |      |

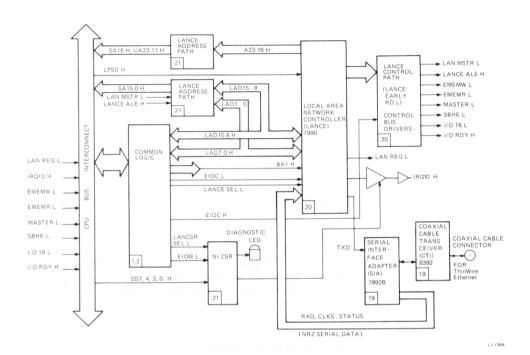

| 3.5 Network Interface                                   | 3-16 |

| 3.5.1 Overview                                          | 3-18 |

| 3.5.1.1 Physical Interconnect                           |      |

| 3.5.1.2 Data Transmission From/To Network               | 3-18 |

| 3.5.1.3 Encoding/Decoding                               | 3-19 |

| 3.5.1.4 Data Transmission From/To CPU and System Memory |      |

| 3.5.1.5 Internal and External Loopback Modes            |      |

| 3.5                                                                                                                                                  | .1.6 I/O-Video Module Diagnostic LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-20                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 3.5.2                                                                                                                                                | Coaxial Transceiver Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-21                                                                         |

| 3.5.3                                                                                                                                                | Serial Interface Adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

| 3.5.4                                                                                                                                                | Local Area Network Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-21                                                                         |

| 3.5.5                                                                                                                                                | LANCE Control Path and Control Bus Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              |

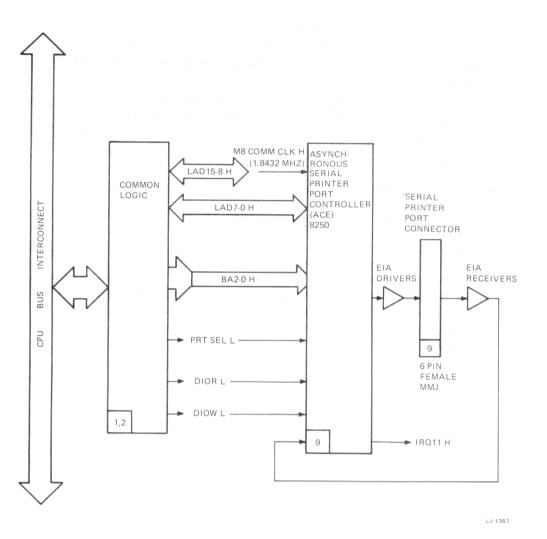

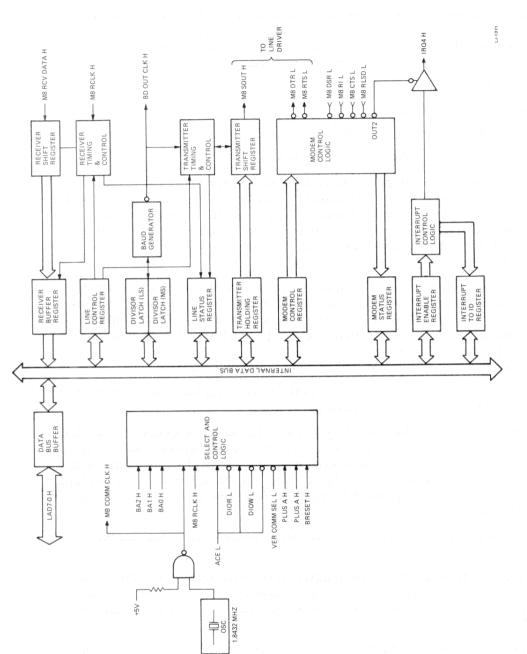

| 3.6 Asy                                                                                                                                              | nchronous Serial Printer Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

| 3.6.1                                                                                                                                                | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

| 3.6.2                                                                                                                                                | Data Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |

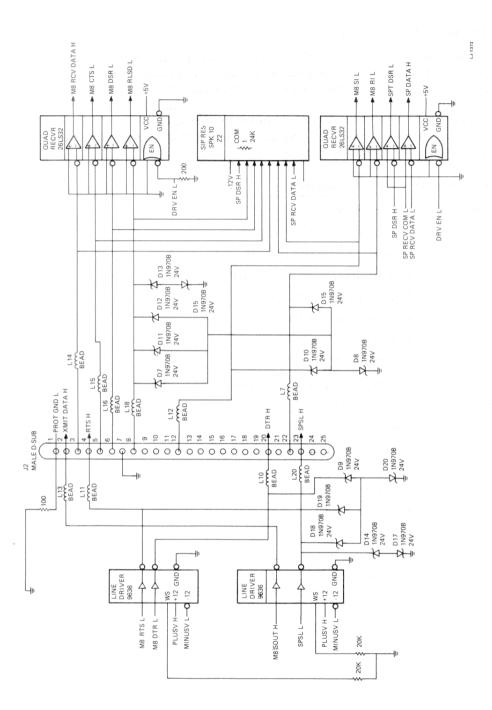

| 3.6.3                                                                                                                                                | EIA Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

| 3.6.4                                                                                                                                                | Physical Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |

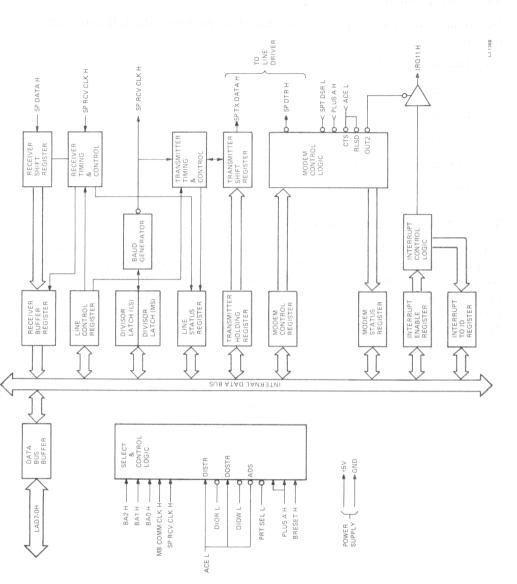

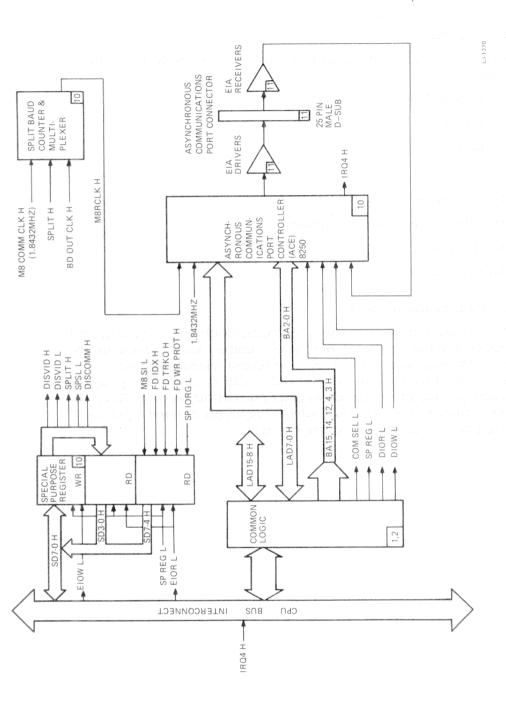

| 3.7 Asy                                                                                                                                              | nchronous Communications Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

| 3.7.1                                                                                                                                                | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

| 3.7.2                                                                                                                                                | Data Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |

| 3.7.3                                                                                                                                                | Modem Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                            |

| 3.7.4                                                                                                                                                | Split Baud Counter and Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |

| 3.7.5                                                                                                                                                | Special Purpose Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

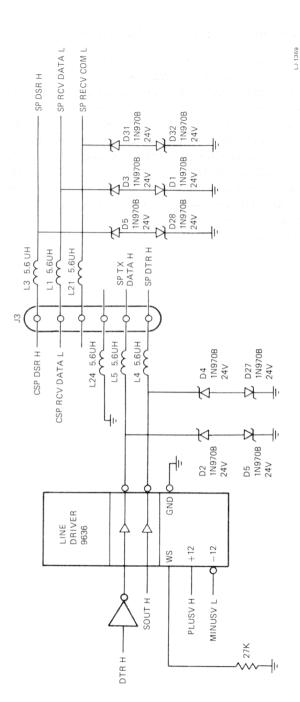

| 3.7.6                                                                                                                                                | EIA Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

| 3.7.7                                                                                                                                                | Physical Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-46                                                                         |

| Chanto                                                                                                                                               | to the Wilder of Court of the c |                                                                              |

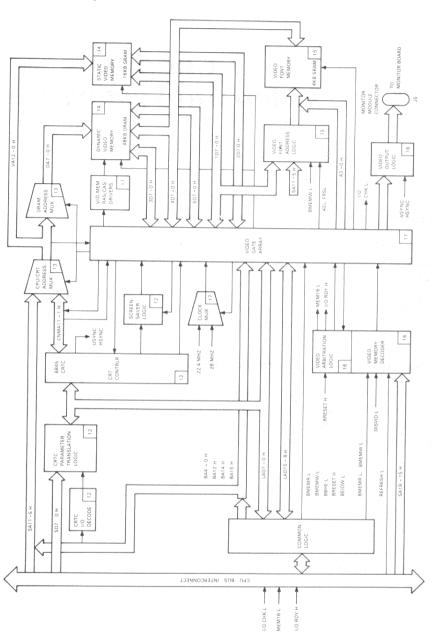

| _                                                                                                                                                    | er 4 Video Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-1                                                                          |

| 4.1 Intr                                                                                                                                             | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

| 4.1 Intr<br>4.2 Vide                                                                                                                                 | roductioneo Controller Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-1                                                                          |

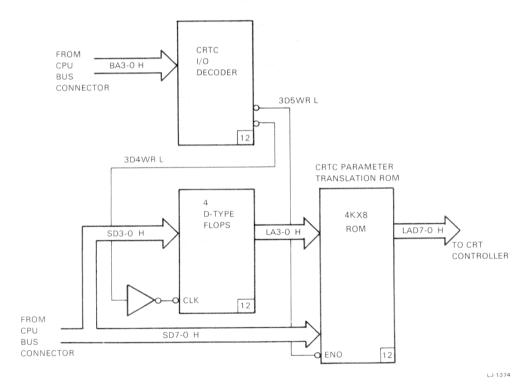

| 4.1 Intr<br>4.2 Vide<br>4.2.1                                                                                                                        | roductioneo Controller Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-1                                                                          |

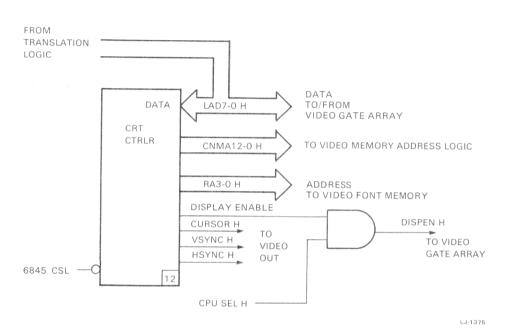

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2                                                                                                               | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1<br>4-3<br>4-4                                                            |

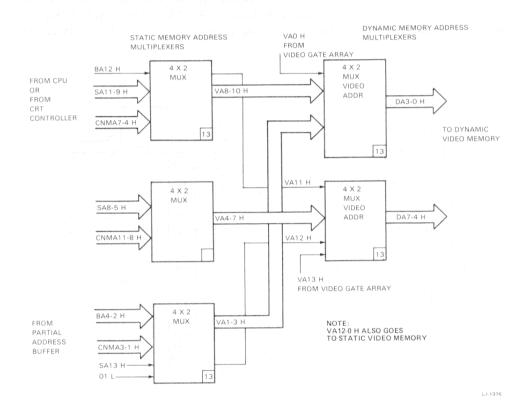

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                      | roduction eo Controller Functional Description Translation Logic CRT Controller Video Memory Address Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-1<br>4-3<br>4-4                                                            |

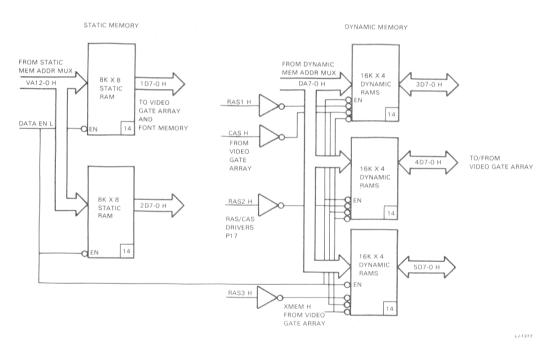

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                                                             | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1<br>4-3<br>4-4<br>4-5                                                     |

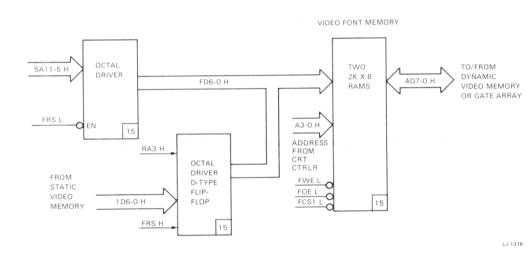

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                      | roduction eo Controller Functional Description Translation Logic CRT Controller Video Memory Address Logic Video Display Memory Video Font RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-1<br>4-3<br>4-4<br>4-5<br>4-6                                              |

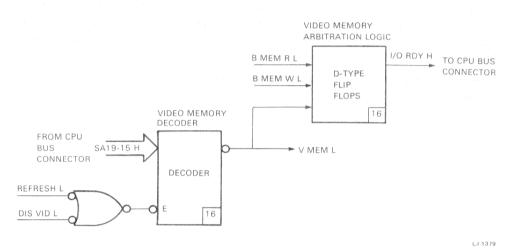

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                                    | roduction eo Controller Functional Description Translation Logic CRT Controller Video Memory Address Logic Video Display Memory Video Font RAM Video Decoder and Arbitration Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-1<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7                                       |

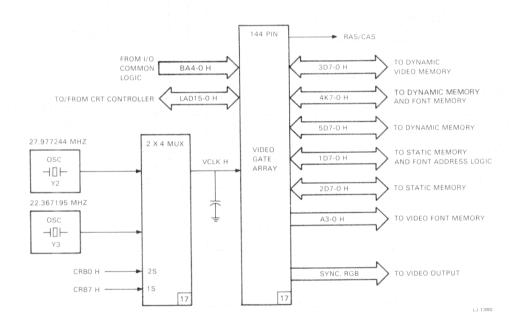

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                                                                           | roduction eo Controller Functional Description Translation Logic CRT Controller Video Memory Address Logic Video Display Memory Video Font RAM Video Decoder and Arbitration Logic Video Gate Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8                                |

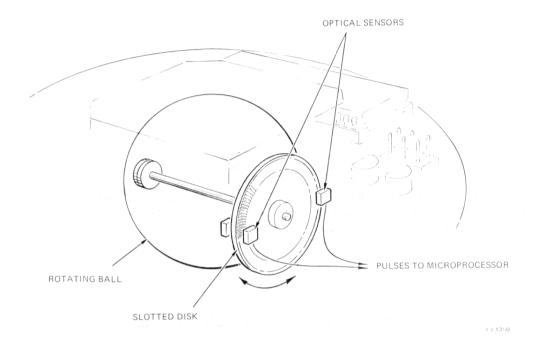

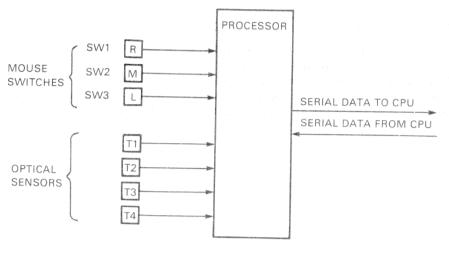

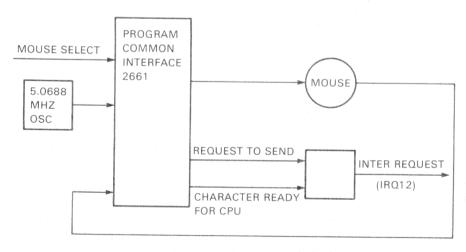

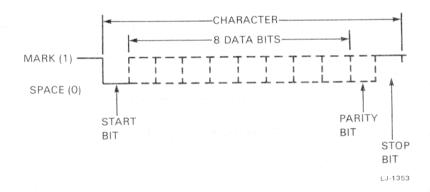

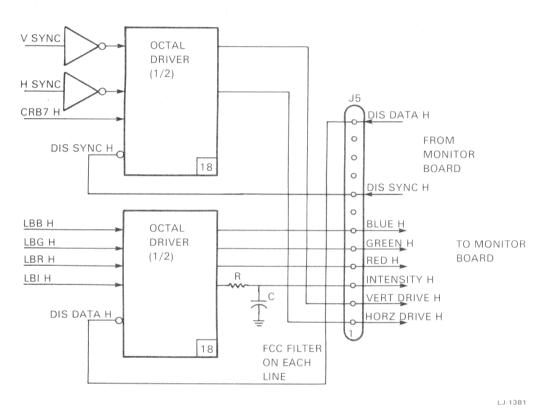

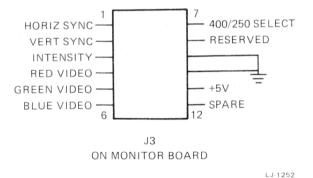

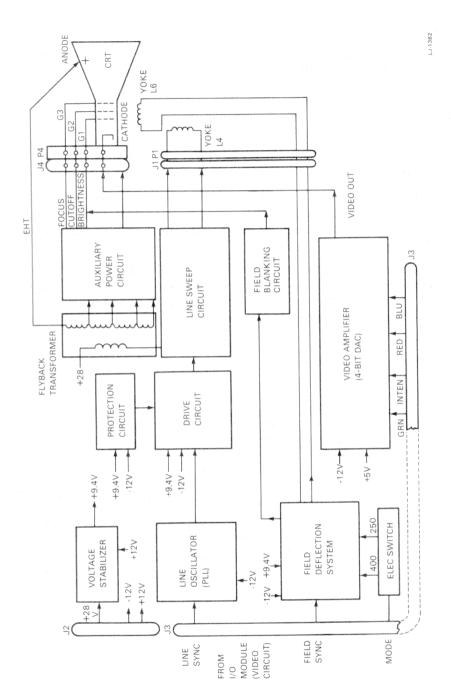

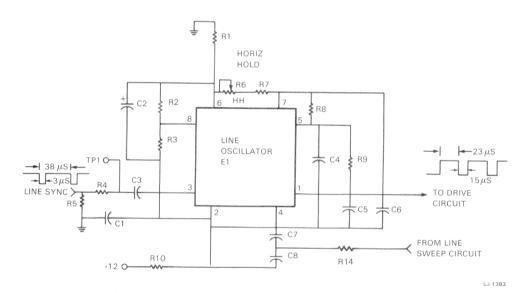

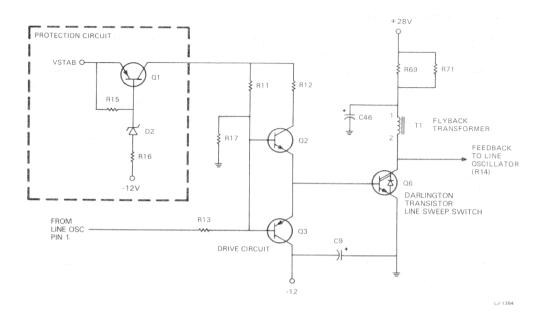

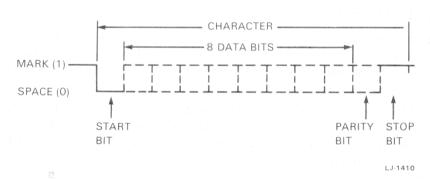

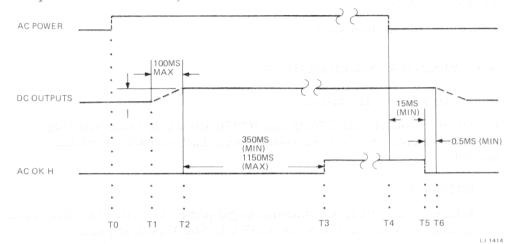

| 4.1 Intr<br>4.2 Vide<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8                                                         | roduction eo Controller Functional Description Translation Logic CRT Controller Video Memory Address Logic Video Display Memory Video Font RAM Video Decoder and Arbitration Logic Video Gate Array Video Output Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-1<br>4-3<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9                                |