# KMV1A Programmable Communications Controller User Guide

## KMV1A Programmable Communications Controller User Guide

Prepared by Educational Services of Digital Equipment Corporation The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

#### Copyright © 1986 by Digital Equipment Corporation

#### All Rights Reserved

#### Printed in U.S.A

The following are trademarks of Digital Equipment Corporation:

| <b>d</b> igital '''' | MASSBUS      | RT             |

|----------------------|--------------|----------------|

|                      | PDP          | UNIBUS         |

| DEC                  | P/OS         | VAX            |

| <b>DECmate</b>       | Professional | VAXBI          |

| DECUS                | Rainbow      | VMS            |

| <b>DECwriter</b>     | RSTS         | VT             |

| DIBOL                | RSX          | Work Processor |

Using Digital's networked computer systems, this book was produced electronically by the Media, Publishing and Design Services department in Reading, England.

### **CONTENTS**

| PREFACE                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 1                                                                                                                                                                                  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                         |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                                                                                            | SCOPE KMVIA GENERAL DESCRIPTION SYSTEM OPERATION CSR LAYOUT BSELI DEFINITIONS KMVIA - HOST INTERACTION                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |

| CHAPTER 2                                                                                                                                                                                  | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.5<br>2.5.1<br>2.5.2<br>2.5.2.1<br>2.5.2.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.6<br>2.7<br>2.7.1<br>2.7.1.1<br>2.7.1.2<br>2.7.2<br>2.8 | UNPACKING AND CHECKOUT INSTALLATION PHASES PREINSTALLATION CONSIDERATIONS Mounting Space Power Requirements Modem Cable Assembly Requirements M7500 INSTALLATION Voltage Check Switch Settings Address Switches Vector Switches Jumper Configurations Standard Switch Setting and Jumper Configuration for KMV1A M7500 Insertion MODEM CABLE ASSEMBLY INSTALLATION KMV1A SYSTEM TESTING Diagnostics MicroPDP-11 Family Diagnostics MicroVAX Family Diagnostics Final Cable Connections KMV1A INSTALLATION CHECK LIST | 2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-3<br>2-3<br>2-4<br>2-5<br>2-6<br>2-9<br>2-10<br>2-10<br>2-10<br>2-10 |

| CHAPTER 3                                                                                                                                                                                  | APPLICATION MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                         |

| 3.1<br>3.2<br>3.3                                                                                                                                                                          | CSR DESCRIPTION  BSEL1 DEFINITIONS  LOADING AND STARTING APPLICATION FIRMWARE                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-1                                                                                                                     |

#### CHAPTER 4 APPLICATION FIRMWARE DEVELOPMENT

| 4.1       | KMV1A I/O PROGRAMMING                                 | 4-1  |

|-----------|-------------------------------------------------------|------|

| 4.1.1     | Front-end Processor Address Space                     | 4-2  |

| 4.1.2     | I/O Register Assignment                               | 4-2  |

| 4.1.3     | Front-end Processor Interrupt System                  | 4-5  |

| 4.2       | CSR AND DMA INTERFACE                                 | 4-6  |

| 4.2.1     | CSR and DMA Address Register Description              | 4-6  |

| 4.2.2     | CSR and DMA Programming                               | 4-7  |

| 4.2.2.1   | Programming Sequence for DMA OUT                      | 4-9  |

| 4.2.2.2   | Programming Sequence for DMA IN                       | 4-9  |

| 4.3       | LINE CONTROLLER INTERFACE                             | 4-10 |

| 4.3.1     | Line Controller Register Description                  | 4-18 |

| 4.3.1.1   | Channel A Receive Buffer (Address 110 000)            | 4-18 |

| 4.3.1.2   | Channel A Transmit Buffer (Address 110 002)           | 4-18 |

| 4.3.1.3   | Channel B Receive Buffer (Address 110 010)            | 4-18 |

| 4.3.1.4   | Channel B Transmit Buffer (Address 110 012)           | 4-18 |

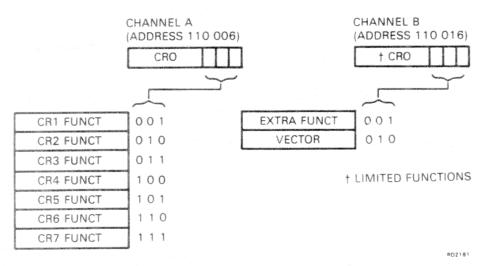

| 4.3.1.5   | Channel A Command Registers (Address 110 006)         | 4-18 |

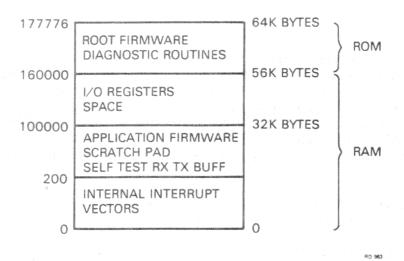

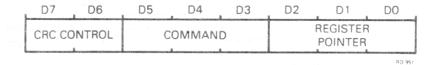

| 4.3.1.5.1 | Control Register 0                                    | 4-18 |

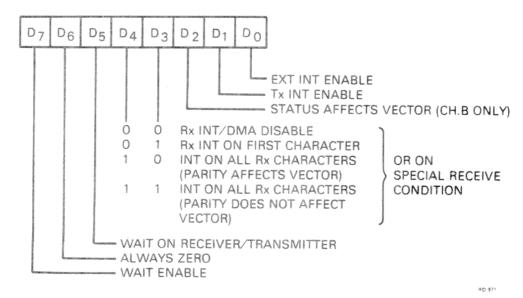

| 4.3.1.5.2 | Control Register 1                                    | 4-21 |

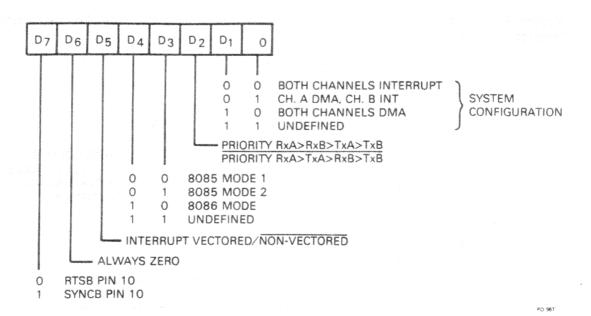

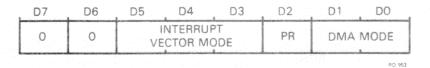

| 4.3.1.5.3 | Control Register 2 (Channel A)                        | 4-23 |

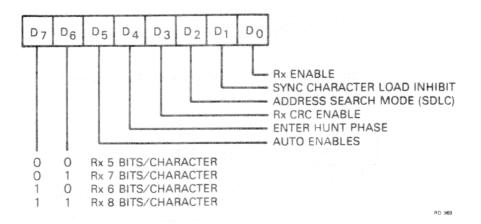

| 4.3.1.5.4 | Control Register 3                                    | 4-24 |

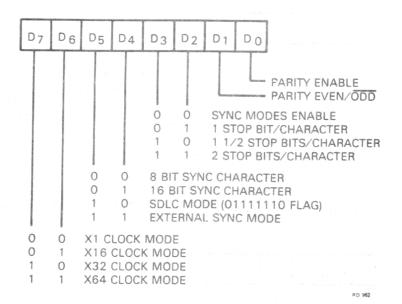

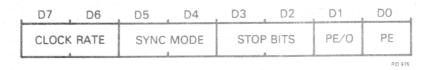

| 4.3.1.5.5 | Control Register 4                                    | 4-26 |

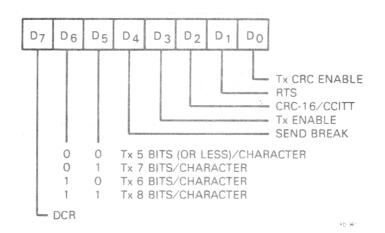

| 4.3.1.5.6 | Control Register 5                                    | 4-27 |

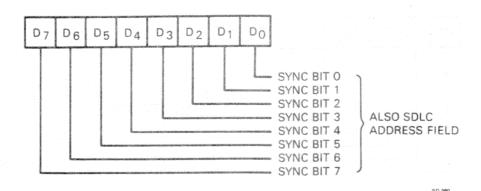

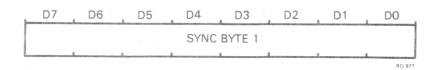

| 4.3.1.5.7 | Control Register 6                                    | 4-30 |

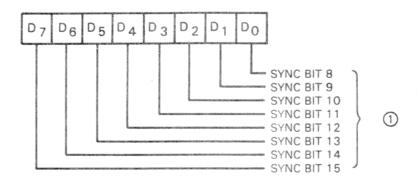

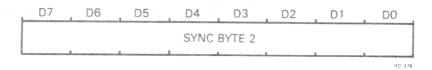

| 4.3.1.5.8 | Control Register 7                                    | 4-30 |

| 4.3.1.6   | Channel B Command Register                            | 4-31 |

| 4.3.1.6.1 | Control Register 0                                    | 4-31 |

| 4.3.1.6.2 | Control Register 1                                    | 4-32 |

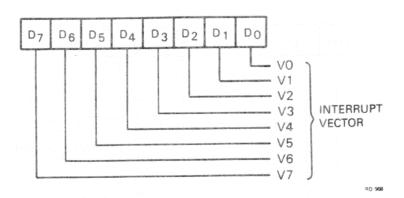

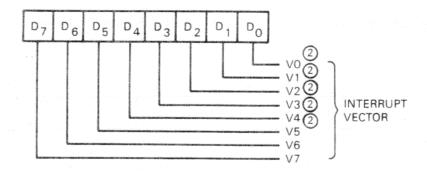

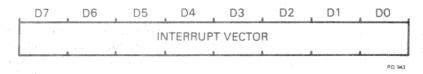

| 4.3.1.6.3 | Control Register 2 (Channel B)                        | 4-32 |

| 4.3.1.7   | Channel A Status Registers                            | 4-32 |

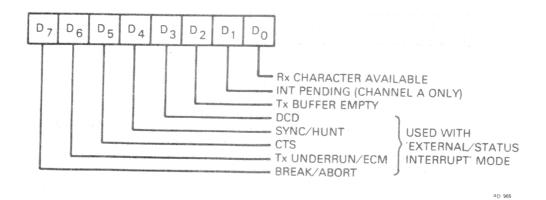

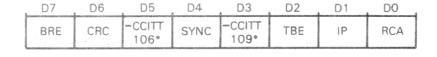

| 4.3.1.7.1 | Status Register 0                                     | 4-32 |

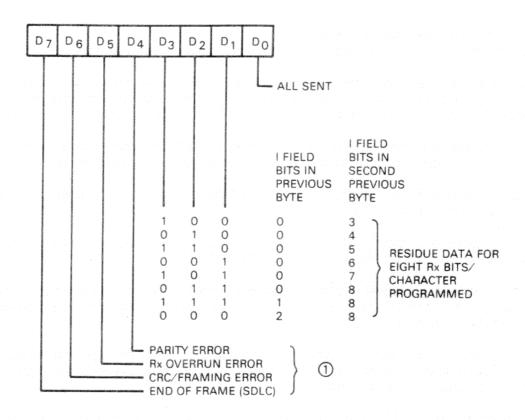

| 4.3.1.7.2 | Status Register 1                                     | 4-35 |

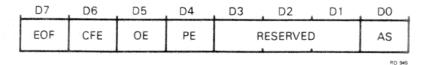

| 4.3.1.8   | Channel B Status Registers                            | 4-37 |

| 4.3.1.8.1 | Status Register 0                                     | 4-37 |

| 4.3.1.8.2 | Status Register 2                                     | 4-37 |

| 4.3.2     | Line Controller Interrupt System and Mode Selection   | 4-38 |

| 4.3.3     | HDLC Operation Example                                | 4-40 |

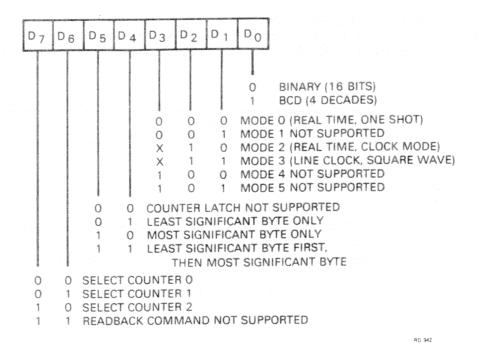

| 4.4       | LINE CLOCK - REAL TIME CLOCK INTERFACE                | 4-42 |

| 4.4.1     | Line Clock - Real Time Clock Register Description     | 4-42 |

| 4.4.2     | Line Clock Programming                                | 4-42 |

| 4.4.3     | Real Time Clock Programming                           | 4-44 |

| 4.4.4     | Line Clock - Real Time Clock Parameter Setting        | 4-44 |

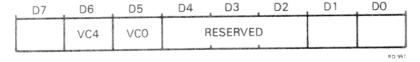

| 4.5       | PERIPHERAL PORT INTERFACE                             | 4-46 |

| 4.5.1     | Peripheral Port Register Description                  | 4-46 |

| 4.5.2     | Modem Monitoring and Control                          | 4-49 |

| 4.6       | HOST INTERRUPT AND Q-BUS CONTROL INTERFACE            | 4-53 |

| 4.6.1     | Host Interrupt and Q-bus Control Register Description | 4-53 |

| 4.6.2     | Host Interrupt and Q-bus Control Programming          | 4-54 |

|           |                                                       |      |

| CHAPTER 5                                                                                                                                                                                               | SERVICE                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.3.1<br>5.3.3.2<br>5.3.3.3<br>5.4<br>5.4.1<br>5.4.1.1<br>6.4.1.1<br>6.4.1.1<br>6.4.1.1<br>6.4.1.2<br>6.4.1.3<br>6.4.2<br>6.4.2<br>6.4.2.1<br>6.5.5.6 | SCOPE  MAINTENANCE PHILOSOPHY  MAINTENANCE TOOLS AND FEATURES  LED Indicators  Self-Test  Line Clock and Loopback Connectors  Line Clock  Real Time Clock  Loopback Connectors/Tests  DIAGNOSTICS  PDP-11 Diagnostics  VKMA Logic Diagnostic  VKMB Line Controller Diagnostic  XKMD DECX-11 Exerciser Module  MicroVAX Diagnostics  MDM Package  PREVENTIVE MAINTENANCE  CORRECTIVE MAINTENANCE | 5-1<br>5-3<br>5-5<br>5-5<br>5-6<br>5-7<br>5-10<br>5-11<br>5-12<br>5-12<br>5-13<br>5-13 |

| APPENDIX A                                                                                                                                                                                              | ORDERING NUMBER AND CABINET INSTALLATION KIT                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| A.1<br>A.2<br>A.3                                                                                                                                                                                       | SCOPE ORDERING NUMBERS CABINET KITS                                                                                                                                                                                                                                                                                                                                                             | A-1<br>A-1<br>A-1                                                                      |

| APPENDIX B                                                                                                                                                                                              | INSTALLATION FOR RS-232-C VERSIONS                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| B.1<br>B.2<br>B.3<br>B.3.1<br>3.2<br>3.2.1<br>B.3.2.2<br>B.3.3<br>B.4                                                                                                                                   | SCOPE COMPONENTS OF THE PACKAGE ASSEMBLY CONSIDERATIONS Before Installation Distribution Panel Installation BA11-M, BA123, BA23 And H9642 BA11-S Installation Checklist TEST CONNECTORS                                                                                                                                                                                                         | B-1<br>B-2<br>B-2<br>B-3<br>B-3<br>B-5<br>B-5                                          |

| APPENDIX C                                                                                                                                                                                              | INSTALLATION FOR RS-422-A VERSIONS                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| C.1<br>C.2<br>C.3<br>C.3.1<br>C.3.1.1                                                                                                                                                                   | SCOPE COMPONENTS OF THE PACKAGE ASSEMBLY CONSIDERATIONS Distribution Panel Installation PDP-11/23S, MicroPDP-11, PDP-11/73, Or MicroVAX II (CK-KMV1A-EA, CK-KMV1A-EB) PDP-11/23 + (CK-KMV1A-EC) Installation Checklist                                                                                                                                                                          | C-1<br>C-1<br>C-2<br>C-2<br>C-2<br>C-3<br>C-5<br>C-5                                   |

| C.4                                                                                                                        | TEST CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C-6                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| APPENDIX D                                                                                                                 | INSTALLATION FOR RS-423-A VERSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |

| D.1<br>D.2<br>D.3<br>D.3.1<br>D.3.1.1                                                                                      | SCOPE COMPONENTS OF THE PACKAGE ASSEMBLY CONSIDERATIONS Distribution Panel Installation PDP-11/23S, MicroPDP-11, PDP11/73, Or MicroVAXII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D-1<br>D-1<br>D-2<br>D-2                                                                                           |

| D.3.1.2<br>D.3.2<br>D.3.3<br>D.4                                                                                           | (CK-KMV1A-FA, CK-KMV1A-FB) PDP-11/23 + (CK-KMV1A-FC) Installation Checklist Unused Items TEST CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D-2<br>D-4<br>D-4<br>D-5<br>D-5                                                                                    |

|                                                                                                                            | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                    |

| Figure No.                                                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                               |

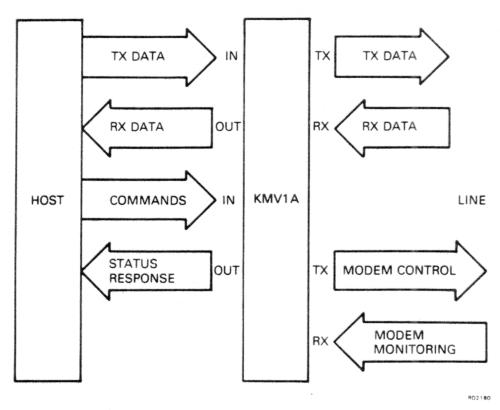

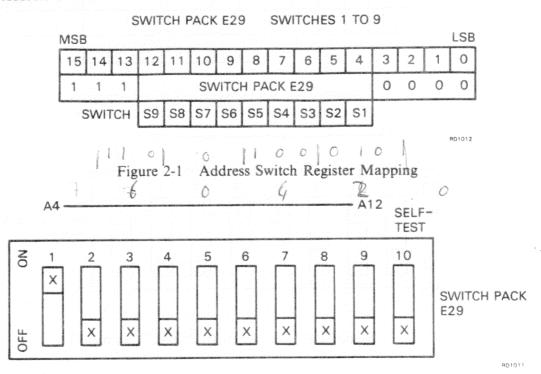

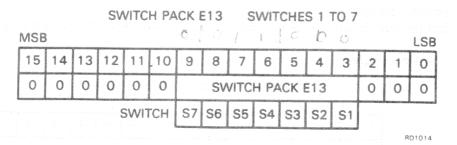

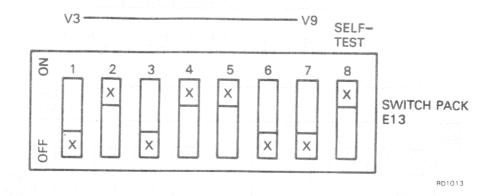

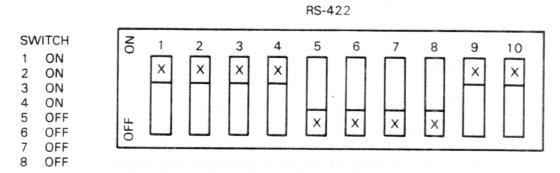

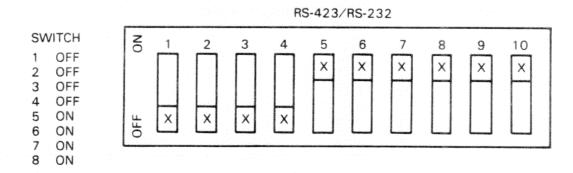

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>3-1<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9 | CSR Definitions BSEL1 Definitions HOST - KMV1A Interaction Address Switch Register Mapping Address Switch Setting Example: 760020 <sub>8</sub> Vector Switch Register Mapping Vector Switch Setting Example: 320 RS-422-A Versus RS-423 (RS-232) on Switch Pack E85 BSEL1 Bit Layout in Application Mode KMV1A Memory Map Control Register 0, Bit Functions Control Register 1, Bit Functions Control Register 2 (Channel A), Bit Functions Control Register 2 (Channel B), Bit Functions Control Register 3, Bit Functions Control Register 4, Bit Functions Control Register 5, Bit Functions Control Register 5, Bit Functions Control Register 6, Bit Functions | 1-3<br>1-3<br>1-5<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>3-1<br>4-2<br>4-11<br>4-12<br>4-13<br>4-14<br>4-14<br>4-15 |

| 4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-16<br>4-17<br>4-18<br>4-19<br>4-20<br>4-21                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-15<br>4-15<br>4-16<br>4-17<br>4-18<br>4-21<br>4-23<br>4-24<br>4-26<br>4-27<br>4-30<br>4-30                       |

| 4-22                                                                                                                       | Control Registers in the KMV1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-31                                                                                                               |

| 4-43                                             | Control Register 2(b) Layout                                      | 4-52 |

|--------------------------------------------------|-------------------------------------------------------------------|------|

| 4-24                                             | Status Register 0(A) Layout                                       | 4-32 |

| 4-25                                             | Status Register 1 Layout                                          | 4-35 |

| 4-26                                             | Status Register 0 (B) Layout in KMV1A                             | 4-37 |

| 4-27                                             | Status Register 2(B) Layout                                       | 4-37 |

| 4-28                                             | Clock Control Register Bit Functions                              | 4-45 |

| 4-29                                             | KMV1A Port A Register Layout                                      | 4-46 |

|                                                  |                                                                   | 4-46 |

| 4-30                                             | Port C Register Layout                                            | 4-47 |

| 4-31                                             | KMV1A Port B Register Layout                                      | 4-53 |

| 4-32                                             | Q-bus Control Register Layout                                     |      |

| 5-1                                              | LED Indicator Location                                            | 5-2  |

| 5-2                                              | Self-Test Switch Locations                                        | 5-4  |

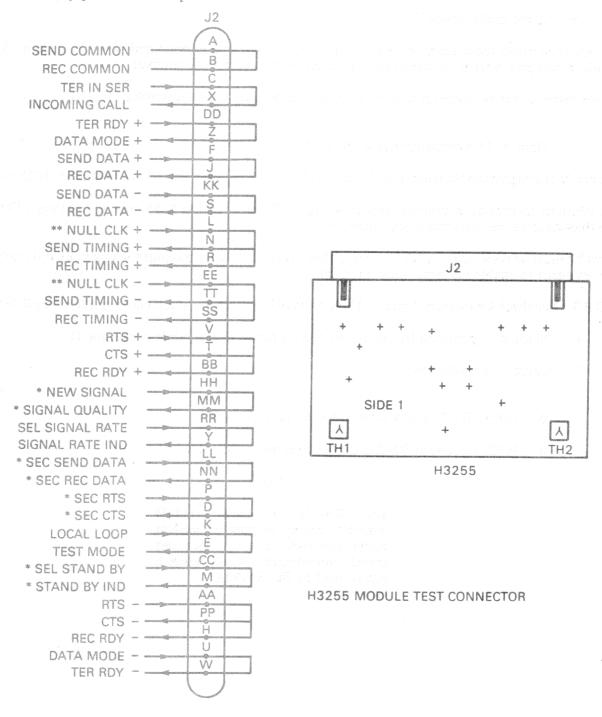

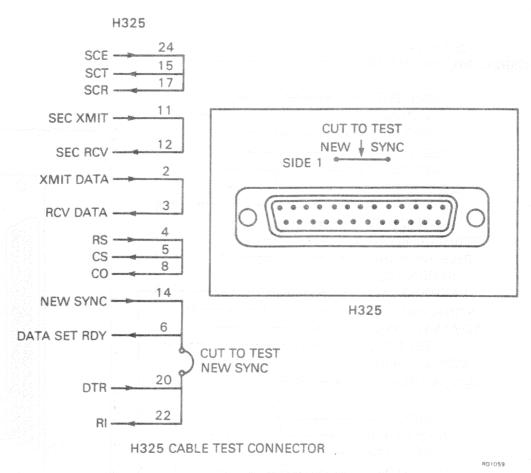

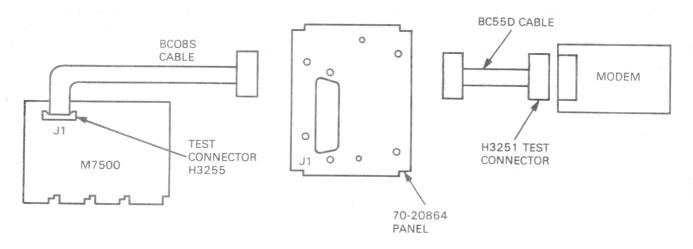

| 5-3                                              | KMV1A Loopback Connector H3255                                    | 5-8  |

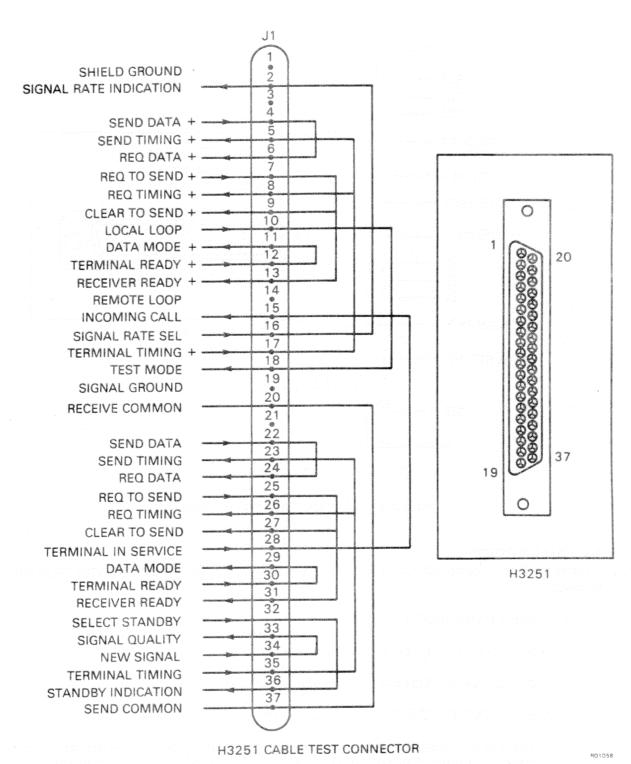

| 5-4                                              | KMV1A Loopback Connector H3251                                    | 5-9  |

| 5-5                                              | KMV1A Turnaround Connector H325                                   | 5-10 |

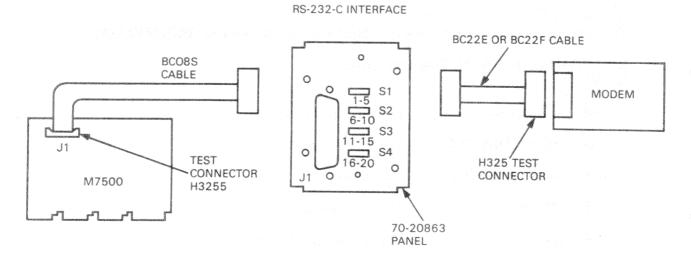

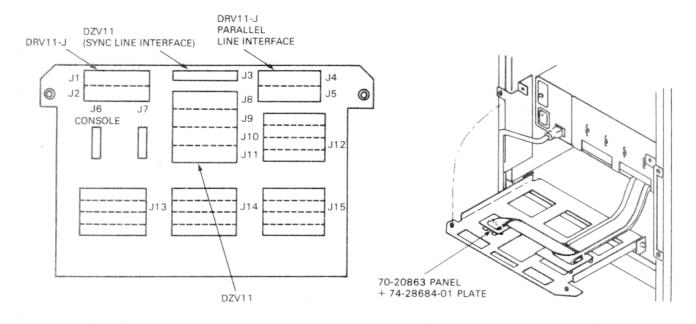

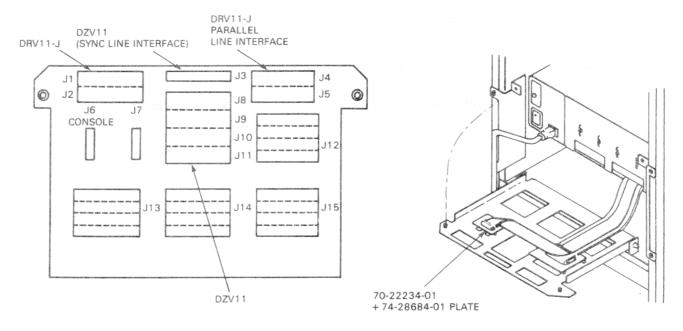

| B-1                                              | General Cabinet Kit Diagram                                       | B-2  |

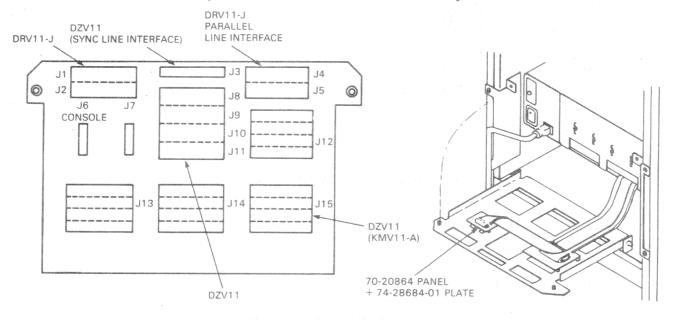

| B-2                                              | Distribution Panel Installation                                   | B-3  |

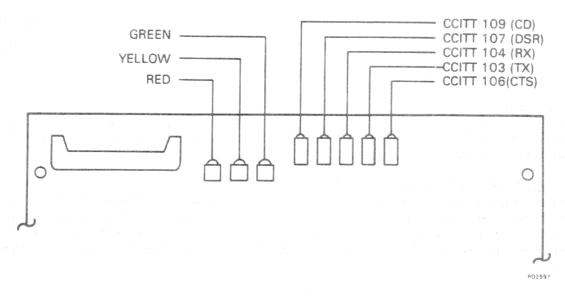

| B-3                                              | BC08S Internal Cable                                              | B-4  |

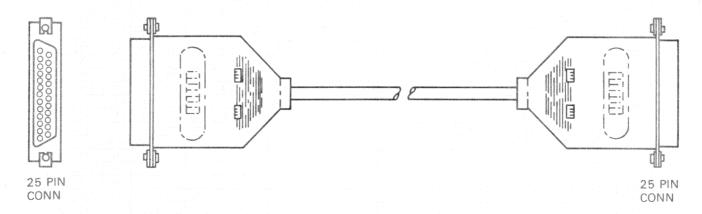

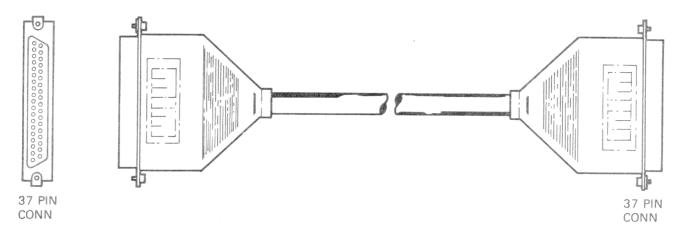

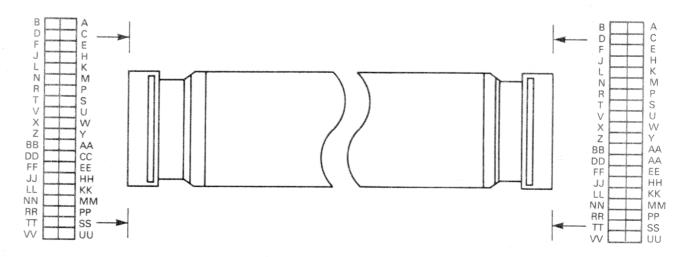

| B-4                                              | BC22F-10 Modem Cable                                              | B-4  |

| B-5                                              | Distribution Panel Installation in BA11-S                         | B-5  |

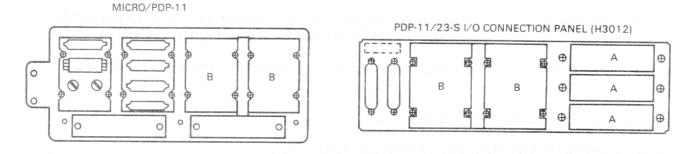

| C-1                                              | General Cabinet Kit Diagram                                       | C-2  |

| C-1<br>C-2                                       | Distribution Panel Installation                                   | C-2  |

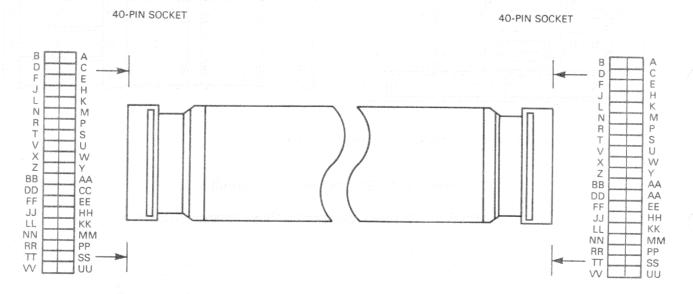

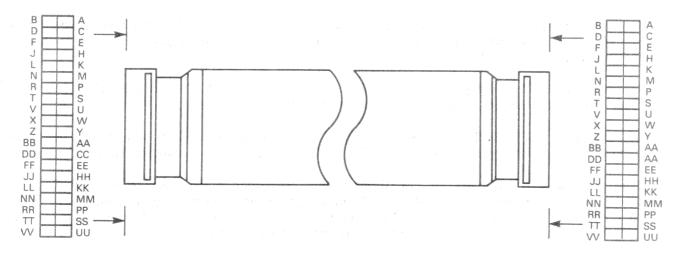

| C-2<br>C-3                                       | BC08S Internal Cable                                              | C-4  |

|                                                  |                                                                   | C-4  |

| C-4                                              | BC55D Modem Cable                                                 |      |

| C-5                                              | Distribution Panel Installation on the PDP-11/23 +                | C-5  |

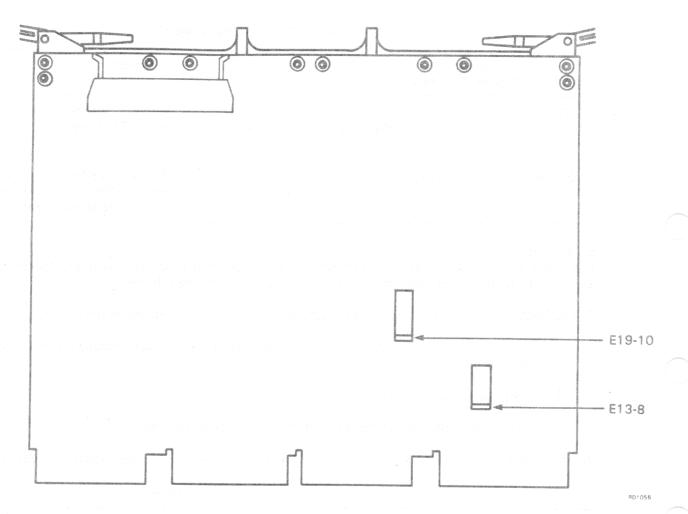

| D-1                                              | General Cabinet Kit Diagram                                       | D-2  |

| D-2                                              | Distribution Panel Installation                                   | D-2  |

| D-3                                              | BC08S Internal Cable                                              | D-3  |

| D-4                                              | BC55D Modem Cable                                                 | D-3  |

| D-5                                              | Distribution Panel Installation on the PDP-11/23 +                | D-4  |

|                                                  | TABLES                                                            |      |

| Table No.                                        | Title                                                             | Page |

| 3. 30 N/40 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                                                   |      |

| 2-1                                              | Self-Test Switch Configuration                                    |      |

| 2-2                                              | KMV1A Switch Register and Jumper Settings                         | 2-6  |

| 2-3                                              | KMV1A Additional Switch and Jumper Settings for RS-232-C and      |      |

|                                                  | RS-423-A Versions                                                 | 2-8  |

| 2-4                                              | KMVIA Additional Switch and Jumper Settings for RS-422-A Versions | 2-8  |

| 3-1                                              | BSEL1 Bit Definitions                                             | 3-2  |

| 4-1                                              | Control Register 0 Description                                    | 4-19 |

| 4-2                                              | Control Register 1 Description                                    | 4-21 |

| 4-3                                              | Control Register 2 (A) Description                                | 4-23 |

| 4-4                                              | Control Register 3 Description                                    | 4-24 |

|                                                  |                                                                   |      |

| 4-5                                              | Control Register 4 Description                                    | 4-26 |

| 4-6                                              | Control Register 5 Description                                    | 4-28 |

| 4-7                                              | Status Register 0 Description                                     | 4-33 |

| 4-8                                              | Status Register 1 Description                                     | 4-35 |

| 1.0                                              | KMV1A Port A Register Rit Description                             | 4-46 |

| 4-10 | Port C Register Bit Description             | 1.1" |

|------|---------------------------------------------|------|

| 4-11 | KMV1A Port B Register Bit Description       | 4-45 |

| 4-12 | List of Supported Modem Signals             | 4-40 |

| 4-13 | Q-bus Register Function Description         | 4-54 |

| 5-1  | LED Meaning                                 | 5.2  |

| 5-2  | Self-Test Switch Configuration              | 5.2  |

| 5-3  | Self-Test List                              | 5.5  |

| A-1  | Definition of KMV1A Cabinet Kits            | A 7  |

| B-1  | 70-20863 Distribution Panel Jumper Settings | R-3  |

|      |                                             |      |

#### **PREFACE**

This user's guide describes how to use the KMV1A programmable communications controller. It describes all the functional elements of the controller and the way user-developed firmware can control these elements.

Other documents which support the KMV1A programmable communications controller are:

- KMV1A Technical Manual (EK-KMV1A-TM-002)

- DCT11-AA Microprocessor User Guide (EK-DCT11-UG-001)

- NEC μPD7201 Multi-Protocol Serial Controller Technical Manual (NEC Electronics (Europe) GmbH)

- Microcomputer Processor Handbook (DIGITAL)

- Microcomputer Interface Handbook (DIGITAL)

Tyse ever en 34 de adition heve es escentification de la presentificie en montantique de la composition de la Escolory de la designada de de la mine de segue de la escolor en especial de la production de la production de Presse de montes

Man polini inili ga kinometriko entrakti, keng in Minili eti ungga, epita seperaki menil

- 等缺陷。因此是是是CVE或是是EBBC的信息,是是是为为是要是CVE。 由

- eren duciji. 1964. jeografi Pojgelus II. Heru, og Depond Edderen Francischer (1907-1908). 1904. p debud 2 decembe

- CONTRACTOR CONTRACTOR OF THE PROPERTY OF THE P

- n (A. P. Park York of Says for been control or the expression of the con-

#### CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This chapter contains a short introduction to the operation of the KMV1A. It is a programmable communications controller, providing single line full modem support interface for the Q-bus.

In this manual the term firmware used in relation to the KMV1A means any set of instructions which is contained in the KMV1A's memory space, and is to be interpreted and executed by the DCT11 microprocessor.

Root Firmware resides within the ROM space of the KMV1A and is a permanent component of the KMV1A.

Application Firmware is to be loaded into the RAM space of the KMV1A at system startup time or after power failure.

#### 1.2 KMV1A GENERAL DESCRIPTION

The KMV1A is designed to be used in a communication link by Q-bus-based systems. The KMV1A is microprocessor based and able to perform functions for bit-oriented synchronous protocols (like HDLC), byte-oriented synchronous protocols (like BSC), or asynchronous protocols. The application firmware defines the computer instructions that are needed to execute the protocol-related activities.

#### Features of the KMV1A include:

- Direct Memory Access (DMA) across the Q-bus for medium-speed transmission and reception.

- A DCT11 microprocessor with the PDP-11 base-level instruction set.

- A 7201 PUSART (Programmable Universal Synchronous Asynchronous Receiver/Transmitter) line controller chip.

- EPROM of 8K bytes, with root firmware and power-up self-test diagnostics.

- Customer-developed application firmware uses the PDP-11 instruction set.

- RAM space of 32K bytes, for implementation of data-link protocols.

- Synchronous (bit-oriented or byte-oriented) as well as asynchronous capabilities for the application firmware.

- Extensive support of modem signals.

- Versions available with interfaces for :

RS-232-C (CCITT V.28)

RS-422-A (CCITT V.11)

RS-423-A (CCITT V.10)

An on-board null modem clock.

By using a microprocessor with a PDP-11 instruction set the KMV1A makes the development of the application firmware more easy.

#### 1.3 SYSTEM OPERATION

Communication of control and status information between the host and the KMV1A uses eight words (16 bytes) of control and status registers (CSRs).

For 18-bit addressing machines the address range will be 76xx00 to 76xx17.

For 22-bit addressing machines the address range will be 1776xx00 to 1776xx17.

These device addresses will be referred to as 'byte select 0 to 17' (BSEL0 to BSEL17) for indicating individual bytes, and as 'select 0 to 16' (SEL0 to SEL16) for indicating individual words.

BSEL1 is defined by the KMV1A's root firmware routines for the following functions:

- Diagnostic firmware self-test execution

- Application mode control

- Special maintenance functions

In application mode, function bits are defined to load, unload, and run application firmware.

Before the application firmware can be executed, it must be loaded into the RAM of the KMV1A.

In order to recover the contents of the RAM, an unload function is provided by the root firmware.

To start the execution of the application firmware, the host can pass to the KMV1A root firmware the start address of the firmware.

#### 1.4 CSR LAYOUT

Figure 1-1 shows the layout of the CSRs in the host processor I/O

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14     | 13 | 12 | 11   | 10  | 9 | 8             | П | 7 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                   | 4   | 3   | 2                            | 1         | 0                      |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|----|------|-----|---|---------------|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|------------------------------|-----------|------------------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |    | BS | EL1  | y41 |   |               |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | BSE | LO  |                              |           |                        | SELO  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BSEL3  |    |    |      |     |   |               |   |   | CONTRACTOR OF THE PARTY OF THE |                     | BSE | L2  |                              |           |                        | SEL2  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BSEL5  |    |    |      |     |   |               |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | BSE | L4  |                              |           |                        | SEL4  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |    | BS | EL7  |     |   |               |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | *************       | BSE | L6  |                              |           |                        | SEL6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |    | BS | EL1  | ı   |   | 31,1 <u>1</u> |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | BSE | L10 |                              |           | recognistic reduction  | SEL10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BSEL13 |    |    |      |     |   |               |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | BSE | L12 |                              |           |                        | SEL12 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BSEL15 |    |    |      |     |   |               |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | COMPA S IN SOMESTIC | BSE | L14 | W. of the 20 colonial little | - 1 Table | en vertigen de l'event | SEL14 |

| L. Committee Com |        |    | BS | EL17 | 7   |   |               |   |   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | BSE | L16 |                              |           | egentari saringan d    | SEL16 |

Figure 1-1 CSR Definitions

#### 1.5 BSEL1 DEFINITIONS

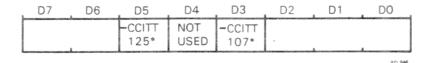

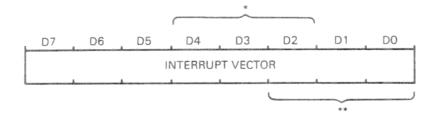

Figure 1-2 shows the BSEL1 layout.

| - | 15  | 14   | 13    | 12 | 11  | 10   | 9                                                                                                              | 8     |

|---|-----|------|-------|----|-----|------|----------------------------------------------------------------------------------------------------------------|-------|

|   | RUN | MCLR | WRITE | MC | DDE | READ | aguard de construire de co | ERROR |

Figure 1-2 BSEL1 Definitions

| Bit | Name  | Function                                                                                                                                                                                        |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | Error | This bit will be set when an illegal address is specified during reading or writing in the KMV1A RAM memory. It will also be set when the address specified with the run command is illegal.    |

| 10  | Read  | When set, this bit directs the root firmware to the memory read routine. The contents of SEL4 will be used as the memory address. The contents of the memory location will be returned in SEL6. |