|  |  |          | : 寶                                   |

|--|--|----------|---------------------------------------|

|  |  |          | · · · · · · · · · · · · · · · · · · · |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  | )        |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  | <i>)</i> |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          | Salas                                 |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

|  |  |          |                                       |

# December 1977

This manual provides the information required to develop, assemble, load, and debug microprograms for the KMC11 auxiliary microprocessor. It includes descriptions of the KMC11 architecture, microinstruction repertoire, macro syntax and expansion, loader utility, KMCDA debugging aid, and special programming techniques.

# KMC11 Programmer's Manual

Order No. AA-5244B-TC

SUPERSESSION/UPDATE INFORMATION:

This document completely supersedes the document

of the same name, Order No. AA-5244A-TC,

published November 1977.

OPERATING SYSTEM AND VERSION:

RSX-11M V3.0

RSX-11D V6.2

IAS V2.0

SOFTWARE VERSION:

KMC11 MACRO V01

KMC11 LOADER V01 KMC11 DEBUGGER V01

To order additional copies of this document, contact the Software Distribution Center, Digital Equipment Corporation, Maynard, Massachusetts 01754

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies.

Copyright © 1977 by Digital Equipment Corporation

The postage-prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| DIGITAL       | DECsystem-10 | MASSBUS    |

|---------------|--------------|------------|

| DEC           | DECtape      | OMNIBUS    |

| PDP           | DIBOL        | OS/8       |

| DECUS         | EDUSYSTEM    | PHA        |

| UNIBUS        | FLIP CHIP    | RSTS       |

| COMPUTER LABS | FOCAL        | RSX        |

| COMTEX        | INDAC        | TYPESET-8  |

| DDT           | LAB-8        | TYPESET-11 |

| DECCOMM       | DECSYSTEM-20 | TMS-11     |

| ASSIST-11     | RTS-8        | ITPS-10    |

# CONTENTS

|         |               |                                                               | Page         |

|---------|---------------|---------------------------------------------------------------|--------------|

| PREFACE |               |                                                               | vii          |

| FREFACE |               |                                                               | V ala ala    |

| CHAPTER | 1             | INTRODUCTION                                                  | 1-1          |

|         | 7 7           | PURPOSE OF MANUAL                                             | 1-1          |

|         | 1.1           | KMC11 GENERAL DESCRIPTION                                     | 1-1          |

|         | 1.2.1         | Controlling Peripherals over the UNIBUS                       | 1-2          |

|         | 1.2.2         | Controlling Peripherals Attached to the                       |              |

|         |               | External Connector                                            | 1-2          |

|         | 1.3           | OPERATING ENVIRONMENT                                         | 1-2          |

|         | 1.3.1         | KMCll Microprogramming Tools Minimum                          |              |

|         |               | Hardware Requirements                                         | 1-2          |

|         | 1.3.2         | KMC11 Software Tools                                          | 1-3          |

|         | 1.3.3         | Prerequisite Software MICROPROGRAM DEVELOPMENT CONSIDERATIONS | 1-3<br>1-3   |

|         | 1.4           | REFERENCE DOCUMENTS                                           | 1-4          |

|         | 1.6           | NOTATIONS                                                     | 1-4          |

|         | 1.0           |                                                               |              |

| CHAPTER | 2             | KMC11 MICROPROCESSOR ARCHITECTURE                             | 2-1          |

|         | 2.1           | CPU STRUCTURES                                                | 2-1          |

|         | 2.1.1         | INBUS/OUTBUS and INBUS*/OUTBUS* Accessed                      |              |

|         |               | Registers                                                     | 2-2          |

|         | 2.1.1.1       | Multiport RAM                                                 | 2-2          |

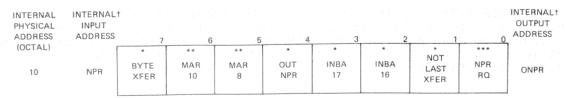

|         | 2.1.1.2       | NPR Control Register                                          | 2-2          |

|         | 2.1.1.3       | Microprocessor Miscellaneous Control                          | 2-4          |

|         | 2.1.1.4       | Register<br>External Connector                                | 2-4          |

|         | 2.1.2         | Components Accessed Through Direct                            | 2 - 4        |

|         | & s .h. s &   | Microinstruction Execution                                    | 2-4          |

|         | 2.1.2.1       | Branch Register                                               | 2-4          |

|         | 2.1.2.2       | Data Memory and Memory Address Register                       | 2-4          |

|         | 2.1.2.3       | Program Counter                                               | 2-5          |

|         | 2.1.2.4       | Scratch Pad Memory                                            | 2-5          |

|         | 2.1.3         | Components Accessed from the UNIBUS                           | 2-5          |

|         | 2.1.3.1       | Control RAM                                                   | 2-5<br>2-6   |

|         | 2.1.3.2 2.1.4 | Maintenance Registers<br>Arithmetic/Logic Unit                | 2-6          |

|         | 2.2           | DATA PATHS                                                    | 2-7          |

|         | 2.2.1         | Source Destination Data Transfer                              | 2-7          |

|         | 2.2.2         | Source Bus                                                    | 2-8          |

|         | 2.2.3         | Destination Bus                                               | 2-8          |

|         | 2.2.4         | UNIBUS Interface                                              | 2-9          |

|         | 2.2.5         | Microprogram Read/Write Bus                                   | 2-10         |

|         | 2.3           | REGISTER AND MEMORY FORMATS                                   | 2-10<br>2-10 |

|         | 2.3.1 2.3.2   | KMCll CSR Format NPR Address and Data and NPR Control         | 2-10         |

|         | tu e ~ e tu   | Register Formats                                              | 2-14         |

|         | 2.3.3         | μPMISC Register Format                                        | 2-17         |

|         | 2.3.4         | Branch Register Format                                        | 2-18         |

# CONTENTS (Cont.)

|         |                       |                                                                                      | P  | age        |

|---------|-----------------------|--------------------------------------------------------------------------------------|----|------------|

| CHAPTER | 3                     | KMC11 MICROINSTRUCTION REPERTOIRE                                                    | 3  | -1         |

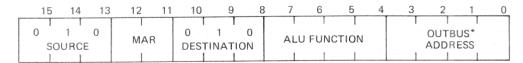

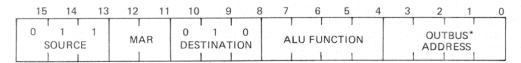

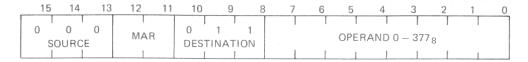

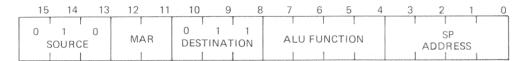

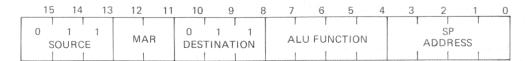

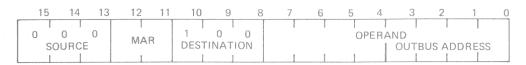

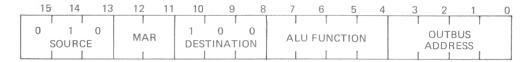

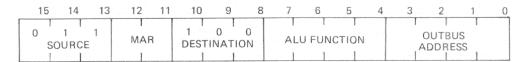

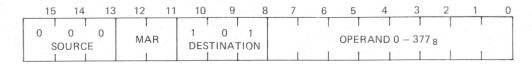

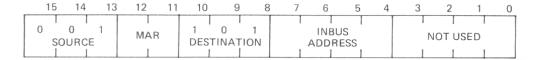

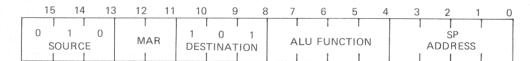

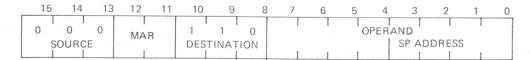

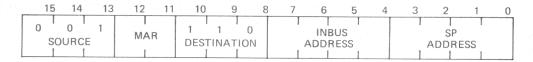

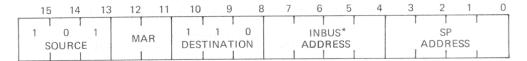

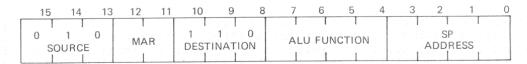

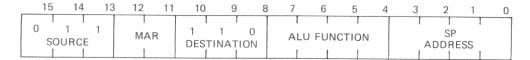

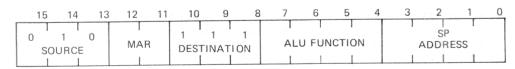

|         | 3.1<br>3.1.1<br>3.1.2 | MOVE CLASS MICROINSTRUCTIONS MAR Control Field Move Class Microinstructions: Formats |    | -1<br>-1   |

|         | 3.1.2.1               | and Functions<br>Destination NODST                                                   | 3  | -2<br>-5   |

|         | 3.1.2.2<br>3.1.2.3    | Destination BRG Destination OUTBUS*                                                  |    | -9<br>-11  |

|         | 3.1.2.4               | Destination BRG Right-Shifted                                                        |    | -14        |

|         | 3.1.2.5<br>3.1.2.6    |                                                                                      | 3- | -16        |

|         | 3.1.2.7               | Destination Data Memory Destination Scratch Pad                                      |    | -19<br>-22 |

|         | 3.1.2.8               | Destination Scratch Pad and BRG                                                      |    | -24        |

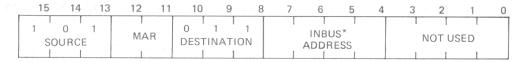

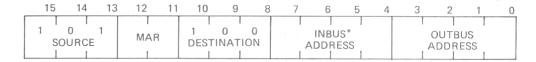

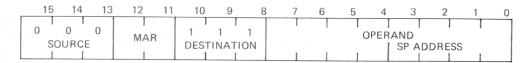

|         | 3.2                   | BRANCH CLASS MICROINSTRUCTIONS                                                       | 3  | -26        |

|         | 3.2.1 3.2.2           | Branch Address Field<br>Branch Class Microinstructions: Formats                      | 3  | -26        |

|         |                       | and Functions                                                                        | 3. | -29        |

|         | 3.2.2.1               | Source Immediate                                                                     |    | -29        |

|         | 3.2.2.2               | Source Data Memory Source BRG                                                        |    | -32        |

|         | J. L. L. J            | Source BRG                                                                           | 3. | -36        |

| CHAPTER | 4                     | KMC11 MACRO INSTRUCTIONS                                                             | 4. | -1         |

|         | 4.1                   | MICROPROCESSOR REGISTER DEFINITIONS                                                  |    |            |

|         | 4.1.1                 | NPR Control Register                                                                 |    | -1<br>-1   |

|         | 4.2                   | MACRO INSTRUCTION SYNTAX                                                             |    | -2         |

|         | 4.2.1                 | Macro Arguments                                                                      |    | -2         |

|         | 4.2.2                 | Source Field Mnemonics                                                               | 4. | -2         |

|         | 4.2.3                 | INBUS* and INBUS Register Symbolic Addresses                                         | 4  | 2          |

|         | 4.2.4                 | Arithmetic/Logic Unit (ALU) Functions                                                |    | -3<br>-3   |

|         | 4.2.5                 | OUTBUS* and OUTBUS Register Symbolic                                                 | -  | _          |

|         | 4.2.6                 | Addresses                                                                            |    | - 3        |

|         |                       | Scratch Pad Locations<br>Memory Address Register (MAR) Field                         | 4- | - 3        |

|         |                       | Definitions                                                                          | 4- | -3         |

|         | 4.2.8                 | Data Memory Page Definitions                                                         | 4- | -4         |

|         | 4.3                   | MICROINSTRUCTION SYNTAX                                                              | 4- | -4         |

|         | 7 . 7                 | EXAMPLES OF KMC11 INSTRUCTION MACRO EXPANSIONS                                       | 1- | -35        |

|         | 4.5                   | RESERVED SYMBOLS                                                                     |    | -37        |

|         | 4.6                   | OPERATING INSTRUCTIONS                                                               | 4- | -38        |

| CHAPTER | 5                     | KMC11 LOADER                                                                         | 5- | -1         |

|         | pos og                |                                                                                      |    |            |

|         |                       | INTRODUCTION KMCll BASIC LOADER SUBROUTINE                                           |    | -1         |

|         | 5.3                   | KMC11 LOADER UTILITY PROGRAM                                                         |    | -2<br>-3   |

|         | 5.3.1                 | Loader Assembly                                                                      |    | - 4        |

|         | 5.3.2                 | Loader and Microcode Task Building                                                   | 5- | - 4        |

| CHAPTER | 6                     | KMC11 DEBUGGING AID                                                                  | 6- | -1         |

|         |                       |                                                                                      | 0- | ola        |

|         |                       | COMMAND CATEGORIES                                                                   |    | -2         |

|         | 6.1.1                 | Examine and Modify CRAM Execution Control Commands                                   |    | -2         |

|         |                       |                                                                                      |    |            |

# CONTENTS (Cont.)

|                                  |         |                                                               |   | Page         |

|----------------------------------|---------|---------------------------------------------------------------|---|--------------|

|                                  | 6 1 0 1 | Cot Propknoints                                               |   | 6-4          |

|                                  | 6.1.2.1 | Set Breakpoints Clear Breakpoints                             |   | 6-5          |

|                                  | 6.1.2.3 | Begin Execution of Microprogram                               |   | 6-5          |

|                                  | 6.1.2.4 | Proceed from Breakpoint                                       |   | 6-6          |

|                                  | 6.1.2.5 | Single Step                                                   |   | 6-6          |

|                                  | 6.1.3   | Examine and Modify CSRs                                       |   | 6-7          |

|                                  | 6.1.4   | Examine Internal Registers and Data                           |   |              |

|                                  |         | Memory                                                        |   | 6-7          |

|                                  | 6.1.4.1 | Examine BRG and Scratch Pad                                   |   | 6-7          |

|                                  | 6.1.4.2 | Examine INBUS and INBUS*                                      |   | 6-8          |

|                                  | 6.1.4.3 | Examine Data Memory                                           |   | 6-8          |

|                                  | 6.1.5   | Utility Commands                                              |   | 6-9          |

|                                  | 6.1.5.1 | Display a Breakpoint                                          |   | 6-10         |

|                                  | 6.1.5.2 | Execute a Microinstruction                                    |   | 6-10         |

|                                  | 6.1.5.3 | Load Data Memory                                              |   | 6-11         |

|                                  | 6.1.5.4 | Load or Display the Memory Address                            |   |              |

|                                  | 26      | Register (MAR)                                                |   | 6-12         |

|                                  | 6.1.5.5 | Load Scratch Pad or BRG                                       |   | 6-12         |

|                                  | 6.1.5.6 | Zero Data Memory                                              |   | 6-13         |

|                                  | 6.1.5.7 | Calculate Offset                                              |   | 6-13<br>6-13 |

|                                  | 6.2     | BREAKPOINT HANDLING                                           |   | 6-14         |

|                                  | 6.2.1   | Reserved CRAM Requirements<br>Breakpoint Location Constraints |   | 6-14         |

|                                  | 6.2.3   | Proceed Counter                                               |   | 6-14         |

|                                  | 6.3     | EXAMPLE OF A KMCDA CONVERSATION                               |   | 6-17         |

|                                  | 0.0     | Infilial of the infoliation of the infiliation                |   |              |

| CHAPTER                          | 7       | SPECIAL PROGRAMMING CHARACTERISTICS                           |   | 7-1          |

|                                  |         |                                                               |   |              |

|                                  | 7.1     | CSR DISCIPLINE                                                |   | 7-1          |

|                                  | 7.1.1   | Initializing the CSRs                                         |   | 7-1          |

|                                  | 7.1.2   | Microprogram Modification of CSRs                             |   | 7-2          |

|                                  | 7.1.3   | UNIBUS Modification of the CSRs                               |   | 7-2<br>7-3   |

|                                  | 7.2     | MULTIPORT RAM LOCKOUT                                         |   |              |

|                                  |         | CSR BIT SETTLING TIME                                         |   | 7-3<br>7-4   |

|                                  | 7.4     | µPMISC AND NPR REGISTER CONSTRAINTS                           |   | /-4          |

| APPENDIX                         | A       | SPECIAL PROGRAMMING TECHNIQUES                                |   | A-1          |

|                                  |         |                                                               |   |              |

|                                  | A.1     | PREVENTING LOSS OF DATA BY OVERWRITING                        | ž |              |

|                                  |         | WHEN THE MICROPROGRAM OR THE PDP-11                           |   |              |

|                                  |         | MODIFIES THE CSRs                                             |   | A-1          |

|                                  | A.2     | ENSURING THAT CSR BITS HAVE SETTLED                           |   | A-3          |

|                                  |         |                                                               |   | T = 3 = 1    |

| INDEX                            |         |                                                               |   | Index-1      |

|                                  |         |                                                               |   |              |

|                                  |         |                                                               |   |              |

|                                  |         | FIGURES                                                       |   |              |

|                                  |         |                                                               |   |              |

| FIGURE                           | 2-1     | KMCll Register and Data Path Structure                        | 3 | 2-3          |

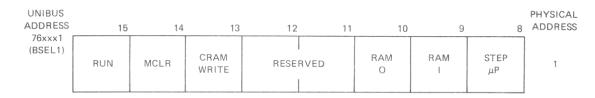

| and the first top of the bridged | 2-2     | KMC11 CSR Format                                              |   | 2-11         |

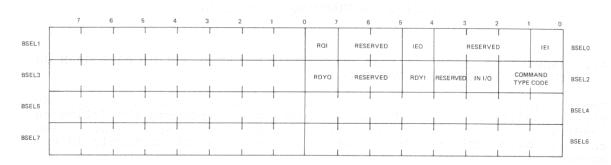

|                                  | 2-3     | NPR Data and Address Register                                 |   | 2-14         |

|                                  | 2-4     | NPR Control Register                                          |   | 2-15         |

|                                  | 2-5     | Microprocessor Miscellaneous (μPMISC)                         |   |              |

|                                  |         | Register                                                      |   | 2-17         |

|                                  | 2-6     | Branch Register                                               |   | 2-18         |

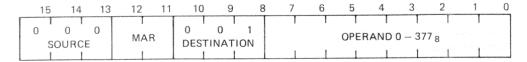

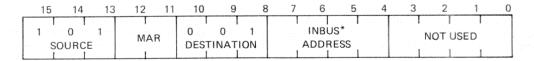

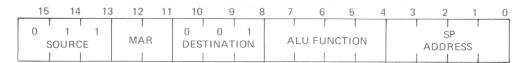

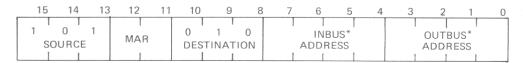

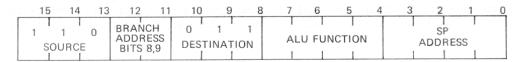

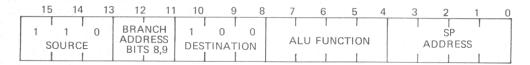

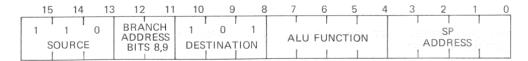

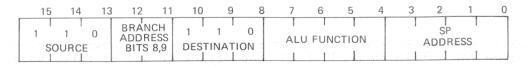

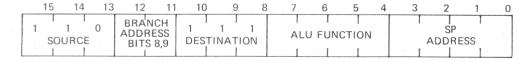

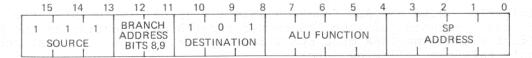

|                                  | 3-1     | Move Class Microinstructions                                  |   | 3-3          |

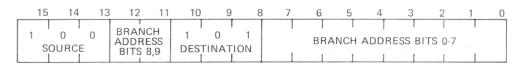

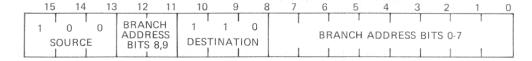

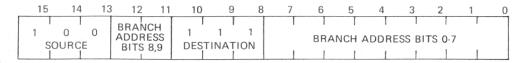

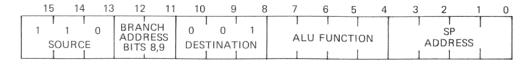

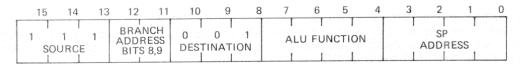

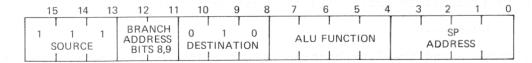

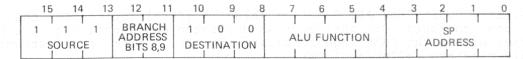

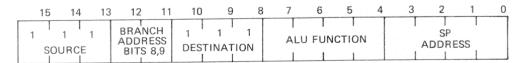

|                                  | 3-2     | Branch Class Microinstructions                                |   | 3-28         |

|        |            |                                                                       | Page       |

|--------|------------|-----------------------------------------------------------------------|------------|

|        |            | FIGURES (Cont.)                                                       |            |

|        |            | (conc.)                                                               |            |

|        |            |                                                                       |            |

| FIGURE | 4-1        | Summary of KMCll Instruction Macros                                   | 4-35       |

|        | 4-2        | Examples of KMCll Macro Expansions                                    | 4-36       |

|        | 5-1        | Control and Status Registers CSR1 Bit Map                             | 5-2        |

|        | 5-2        | KMCll Basic Loader Subroutines                                        | 5-2        |

|        | 5-3        | KMC-11 Loader Printout Example                                        | 5-3        |

|        | 5-4<br>A-1 | KMC-11 Loader Error Printout Example                                  | 5-3        |

|        | H-T        | Suggested Format for UNIBUS CSRs                                      | A-2        |

|        |            |                                                                       |            |

|        |            |                                                                       |            |

|        |            | TABLES                                                                |            |

|        |            |                                                                       |            |

|        |            |                                                                       |            |

| TABLE  | 3-1        | Arithmetic/Logic Unit Functions                                       | 3-4        |

|        | 3-2        | INBUS Register Symbolic Addresses                                     | 3-7        |

|        | 3-3        | INBUS* Register Symbolic Addresses                                    | 3-7        |

|        | 3-4        | OUTBUS* Register Symbolic Addresses                                   | 3-12       |

|        | 3-5        | OUTBUS Register Symbolic Addresses                                    | 3-17       |

|        | 3-6        | Symbolic Values of the Argument OPARG1                                | 3-27       |

|        | 4-1        | Legal Separating and Delimiting Characters                            |            |

|        | 4 2        | Used in Macro Definitions                                             | 4-5        |

|        | 4-2<br>4-3 | INBUS* Register Symbolic Addresses                                    | 4-5        |

|        | 4-4        | INBUS Register Symbolic Addresses Arithmetic/Logic Unit Functions     | 4-6        |

|        | 4-5        | OUTBUS* Register Symbolic Addresses                                   | 4-7<br>4-8 |

|        | 4-6        | OUTBUS Symbolic Addresses                                             | 4-8        |

|        | 4-7        | Move Instruction Destination: Branch                                  | 4-0        |

|        |            | Address Register                                                      | 4-9        |

|        | 4-8        | Move Instruction Destination: OUTBUS*                                 | 4-10       |

|        | 4-9        | Move Instruction Destination: Branch                                  |            |

|        |            | Address Register Right-Shifted                                        | 4-13       |

|        | 4-10       | Move Instruction Destination: OUTBUS                                  | 4-14       |

|        | 4-11       | Move Instruction Destination: Data                                    |            |

|        | 4 70       | Memory                                                                | 4-17       |

|        | 4-12       | Move Instruction Destination: Scratch                                 |            |

|        | 4-13       | Pad Move Instruction Destination: Scratch                             | 4-18       |

|        | 4-10       | Move Instruction Destination: Scratch Pad and Branch Address Register | 4 20       |

|        | 4-14       | Move Instruction Destination: NODST (No                               | 4-20       |

|        |            | Destination)                                                          | 4-22       |

|        | 4-15       | Move Instruction: Increment and Load MAR                              | 4-24       |

|        | 4-16       | Branch Instruction Source: Immediate                                  | 4-25       |

|        | 4-17       | Branch Instruction Source: Data Memory                                | 4-27       |

|        | 4-18       | Branch Instruction Source: Branch Address                             | - App F    |

|        |            | Register                                                              | 4-29       |

|        | 4-19       | Compare Values and Subroutine Calls and                               | -          |

|        |            | Returns                                                               | 4-31       |

#### PREFACE

# MANUAL OBJECTIVES AND READER CLASS ASSUMPTIONS

The objective of this manual is to provide experienced programmers with the information needed to develop, assemble, load, and debug microprograms for the KMCll-A auxiliary microprocessor.

The level of technical detail presented in this manual assumes that the reader is proficient in developing MACRO-11 assembly language programs and using the RSX-11 Task Builder to create an executable task image. In addition, the reader is assumed to be familiar with PDP-11 processor architecture and UNIBUS interfacing and have an in-depth knowledge of PDP-11 programming techniques.

#### STRUCTURE OF THIS MANUAL

This manual consists of seven chapters and an appendix.

Chapter 1 is a concise overview of the KMC11 and a summary of its operating environment. This chapter also contains microprogram development criteria, a list of reference documents, and an explanation of the notations used in this manual.

Chapter 2 describes the KMCll microprocessor architecture with emphasis on the internal registers and data paths.

Chapter 3 provides detailed descriptions of the KMCll microinstruction repertorie; a bit map precedes the description of each microinstruction. This chapter is subdivided into two major parts corresponding to the two classes of microinstructions: Move class and Branch class.

Chapter 4 defines the KMCll macro syntax, the macros, and expansion of the macros. This chapter also lists the reserved symbols and outlines the general procedures to operate the KMC-ll MACRO assembler.

Chapter 5 describes the KMCll loader utility. The basic KMCll loader subroutine in this chapter provides the basis for the user to develop his own operating system specific loader. The KMCll Loader (KMCLDR) running on RSX-11M is also described in this chapter for users who utilize this DIGITAL-developed component.

Chapter 6 provides the programmer with the detailed information necessary to use the KMCll Debugging Aid (KMCDA); this chapter also includes details on task building KMCDA.

Chapter 7 considers special programming characteristics and techniques; some are unique to the KMCll microprocessor and some are unique to KMCll microprocessors operating in the multiprocessor environment.

Appendix A provides information ancillary to that contained in Chapter 7 on preventing overwriting data in the KMCll Control and Status Registers and on ensuring data bit settling.

0.049049

where the property of the state of the second sections of the second section  $f_{ij}$  and  $f_{ij}$  are second sections and the second section  $f_{ij}$  and  $f_{ij}$  are second sections.

ded to toward found and it has been dealed found to be a section of the period of the

。这种即将是"是证据的"的"以"的特别的包含的对

·罗尔萨内尔曼雷尔 如此 中心的 不同的过程数据的 医根根皮肤 压力 电抗光流电极的 (Jacobing) 医电力管

ndi to yammaro o ber ilizar entri le vela estre entropos e el respectore entropos e el el estrenciado de el est mangrader talta trata de estrenciado el estrencia el estrencia entropos entropos entropos el estrencia entropo pa trata como como estrencia entropos ent

getrongulgeterritt fille een hom en tijerronne held for in set vekkungs i onnonne Kone In nostarabeel een eekboonge gen jorte nij set nostalingspro Enter enjan ven ofti beint betrivjusse vi sovenis vat in en cook men op selegies Om narub eent sovetigerongsprong is skeepele ovd net on selegiesede

Odencer v medoculuk bed Alfoli ladanda ettela ikunalik 1880) kallulopeon v goden de kolonik kallulopeon v goden golovok et tekstori di taki kallulopeon perileng protesta indi bita oden ettela (NMP) kallulopeon kallulopeon golovok ettela ettela kallulopeon ettela kallulopeon ettela ettela ettela ettela ettela ettela ettela ettela e ettela ettel

iinappere a provide the programer with the dentited introductions of the antifed antifered of the consequent construction of the consequent along the construction of the consequent along the construction of the construction of the construction of the consequence of the consequen

Ron zairolandonaedo poloreannog Pelonge, brahlenon V podged. Nas embo Poe roneocoagoable Plato odd ol mepenn rac embo greoplodaed Praforengidisa odd di poutoargo encarporagiapie. (1965 od composition

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 PURPOSE OF MANUAL

This manual provides the information needed by an experienced programmer to assemble, load, and debug microprograms for the KMCll-A auxiliary microprocessor. It therefore describes the KMCll software tools that aid the programmer in developing, loading, and debugging a KMCll microprogram.

#### 1.2 KMC11 GENERAL DESCRIPTION

The KMCll is an auxiliary processor designed for use on PDP-ll computer systems. It operates in parallel with the main CPU and has an architecture specifically suited to data movement, character processing, address arithmetic, and other functions necessary for controlling I/O devices, formatting data, and processing communications protocols. The KMCll can be used in conjunction with all UNIBUS-based PDP-ll processors, from the PDP-ll/04 to the PDP-ll/70.

The functions performed by the KMCll are determined primarily by the microprogram in the KMCll control memory. This control memory is writable and may be changed whenever desired by the PDP-ll processor. In normal operation, the PDP-ll operating system would load the microprogram into the KMCll control memory as part of system initialization; it would remain in the control memory until the system is subsequently reinitialized.

Software support of the KMCll by a PDP-ll operating system consists of two parts:

- 1. the PDP-11 operating system driver, and

- 2. the KMCll microprogram.

The microprogram must be tailored to the specific processing to be performed by the KMCll. The operating system driver interfaces the microprogram to the rest of the PDP-ll software. Communication between the microprogram and the operating system uses the KMCll control status registers and is entirely defined by the software. Different applications may require different types of microcode/software interfaces. Operating system support for the KMCll should always be considered in terms of the specific KMCll microprogram employed.

#### INTRODUCTION

# 1.2.1 Controlling Peripherals over the UNIBUS

A typical application of the KMC11 is the control of several peripheral devices attached to the UNIBUS. These devices, for example the DZ11 8-line asynchronous multiplexer, typically operate by programmed I/O, interrupting the PDP-11 processor for each character input or output. However, with the addition of a KMC11, this processor overhead can be substantially reduced and I/O throughput increased.

The PDP-11 processor communicates with the KMC11 on a message basis, with the KMC11 interrupting the processor at the end of each message. The KMC11 has direct memory access to message buffers in PDP-11 memory by means of NPR transfers. Data is transferred between the KMC11 and associated peripherals on a character-by-character basis through NPR transfers that address the peripheral's control, status, and data registers (CSRs). NPR transfers are conducted over the UNIBUS with no direct connection between the KMC11 and associated peripherals. The peripherals are operated with their interrupts disabled. The KMC11 periodically scans the peripheral status registers to determine when characters may be transferred. As single KMC11 can simultaneously control many transfers between peripherals and memory, keeping track of their status by using its 1024-byte data memory.

In addition to assembling and disassembling messages, the KMCll microprogram can perform formatting, special character recognition, error checking, and other protocol functions.

# 1.2.2 Controlling Peripherals Attached to the External Connector

For high-speed operation, the KMCll can be connected directly to a specially designed peripheral device, such as a DMCll synchronous line unit.

In this mode of operation, the KMCll communicates with the PDP-ll processor and memory as described above, but has a direct path to the high-speed peripheral via the KMCll's external connector. The external connector implements a simple bidirectional data port. Transfers are entirely under microprogram control.

# 1.3 OPERATING ENVIRONMENT

The KMCll microcode can operate on any UNIBUS-based system (PDP-11/04 to PDP-11/70) with whatever hardware the user program requires so long as the means exist to load the previously developed microprogram.

To develop the KMCll microprogram, the hardware, software, and software tools listed in Sections 1.3.1 to 1.3.3 are required.

# 1.3.1 KMC11 Microprogramming Tools Minimum Hardware Requirements

Any valid RSX-llM, RSX-llD, or IAS hardware configuration and one KMCll auxiliary microprocessor comprise the minimum hardware requirements.

#### INTRODUCTION

# 1.3.2 KMCll Software Tools

The KMCll microprogramming tools are used to aid a programmer in developing and debugging a KMCll microprogram; the tools enable the programmer to assemble, load and debug the new microprogram.

The KMCll software tools consist of three parts:

- A MACRO-11 prefix file consisting of macro definitions of KMC11 instructions. The prefix file is assembled using MACRO-11 together with a file containing customer written microinstructions in the form of macro calls.

- 2. A utility program to load the writable control memory of a KMCll-A from a file containing an image of a KMCll microprogram. The utility program runs as a privileged task under the supporting operating system. The input to the program is a file created by the Operating System Task Builder from the output of the MACRO-Il assembly.

- 3. A utility program to enable a programmer to debug interactively a microprogram running on a KMCll. The utility program runs as a privileged task under the supporting operating system and utilizes the maintenance features of the KMCll hardware. The user may examine and modify the contents of the microprocessor internal registers, data memory and control memory. The user may start, stop, or single step the microprogram; or he may direct the KMCll to execute a single microinstruction from the console. The user may optionally set up to eight breakpoints in the microprogram. Breakpoints are user-selected locations at which microprogram execution is to be halted temporarily to permit interaction between the microprogram and the user. If breakpoint support is to be used, the 16 highest locations in the KMCll control memory must be reserved for the utility program. All addresses and data input and output to the user are in octal.

## 1.3.3 Prerequisite Software

The KMCll microprogramming tools operate with one of the following PDP-11 systems:

RSX-11M, Version 3.0 RSX-11D, Version 6.2 IAS, Version 1.1

# 1.4 MICROPROGRAM DEVELOPMENT CONSIDERATIONS

Software support of a KMCll by a PDP-11 operating system consists of two parts: the KMCll microprogram and the PDP-11 operating system. The operating system driver interfaces the microprogram with the rest of the PDP-11 software. The microprogram must be tailored to the specific processing to be performed by the KMCll.

Development or acquisition of the microprogram can be through one of the following ways:

Users can use DIGITAL-developed microprograms and drivers supplied with DIGITAL's PDP-11 operating systems.

#### INTRODUCTION

- 2. Users can use DIGITAL-developed microprograms in their own software environment. These users will develop their own operating system drivers.

- 3. Users can develop their own microprograms tailored to specific applications. These users can also develop their own operating system drivers. They may utilize the DIGITAL software tools described in Section 1.3.2.

- 4. Users can use DIGITAL's Computer Special Systems (CSS) to design and develop custom microprograms. CSS services avoid the need to develop in-house expertise and experience in the details of KMCll microprogramming, yet provide the benefits of custom-microcode.

If KMCll microcode is to be developed by the user, personnel should be senior-level and should have experience in programming I/O routines in several different minicomputer or microprocessor assembly languages. In addition, the personnel should be familiar with the problems of correctly synchronizing multiple processors.

# 1.5 REFERENCE DOCUMENTS

The following documents supplement the information in this manual. Some will aid in understanding the use and programming of the peripheral devices mentioned in this manual; others provide installation, operational and maintenance information for the KMCll.

|                                                                                 | Document                                                                         |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| ods nobeced uniscussed <mark>Title</mark> ye offensymmet megg <sub>e</sub> r ye | Number                                                                           |

|                                                                                 | WASHINGTON SHOW WASHINGTON AND WASHINGTON AND AND AND AND AND AND AND AND AND AN |

| KMCll General Purpose Microprocessor User's Manual                              | EK-KMC11-OP                                                                      |

| KMCll General Purpose Microprocessor Maintenance Manual                         | EK-KMC11-MM                                                                      |

| COMM IOP-DUP Programming Manual                                                 | AA-5670A-TC                                                                      |

| COMM IOP-DZ Programming Manual                                                  | AA-5127A-TC                                                                      |

| DMC11-DA Network Link Synchronous Line Unit                                     |                                                                                  |

| Maintenance Manual                                                              | EK-DMCLU-MM                                                                      |

| PDP-11 Peripherals Handbook                                                     | EB05961                                                                          |

| RSX-11M MACRO-11 Reference Manual                                               | DEC-11-OMMAA                                                                     |

| RSX-11M Task Builder Reference Manual                                           | DEC-11-OMTBA                                                                     |

# 1.6 NOTATIONS

The following notations are used throughout this manual. These notations represent actions or processes that express Boolean functions, programming conventions, and line printer or I/O terminal actions.

| V | Boolean  | OR              | CR        | Car | riage I | Return   |        |       |

|---|----------|-----------------|-----------|-----|---------|----------|--------|-------|

| ₩ | Boolean  | Exclusiv        | re OR LF  | Lir | ne Feed |          |        |       |

| ~ | Negation | <b>n</b> 68 868 | arapod[e] | Bra | acketed | Argument | is Opt | ional |

|   |          |                 |           |     |         |          |        |       |

→ Becomes

#### CHAPTER 2

#### KMC11 MICROPROCESSOR ARCHITECTURE

# 2.1 CPU STRUCTURES

The KMCll microprocessor is a parallel 16-bit general-purpose microcomputer. Its architecture and instruction set are optimized for the character processing environment specific to network communications and other I/O-oriented systems. The KMCll instruction cycle has a period ranging from 300 to 330 ns, and microinstructions are executed from a lK x 16-bit writeable control store referred to as the control RAM or CRAM. Microinstructions executed from the CRAM can access all KMCll internal registers as well as data memory.

Within the instruction cycle period, the KMCll can (1) execute internal register-to-register transfers; (2) initiate bus requests (interrupt the main CPU); (3) initiate NPR transactions; and (4) perform transfers between an internal register and data memory. In addition, the KMCll can perform a wide range of arithmetic and logical functions on internally transferred data. (The main CPU is defined as the resident PDP-11 processor and its associated memory.)

All internal registers and data paths are 8 bits wide. In addition, the Control and Status Registers (CSRs) are both word and byte addressable from the UNIBUS, but byte addressable only from the KMCll.

The microprogram can read from or write into all internal registers and memories, except the microinstruction memory (CRAM), the memory address register (MAR), and the program counter (PC). The CRAM can be addressed for microinstruction execution only through the PC, and the MAR and PC can only be written into.

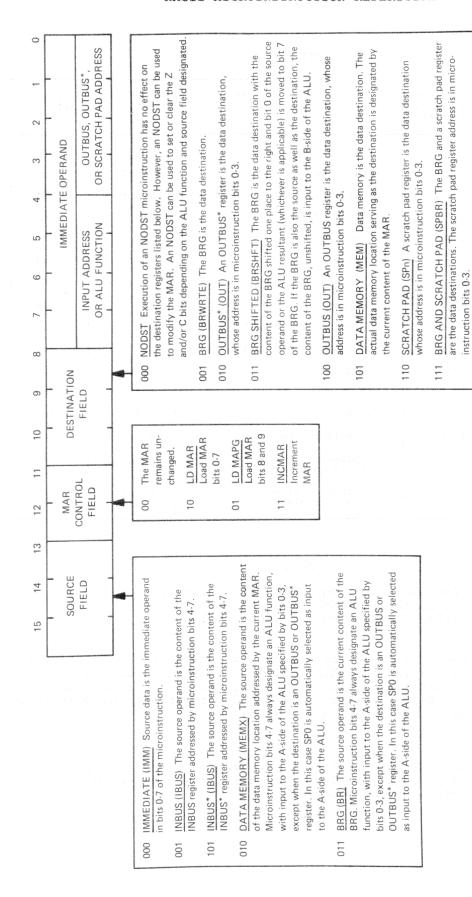

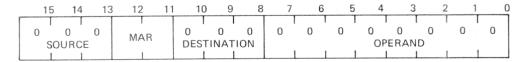

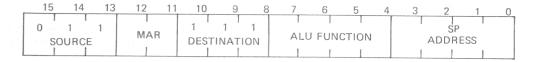

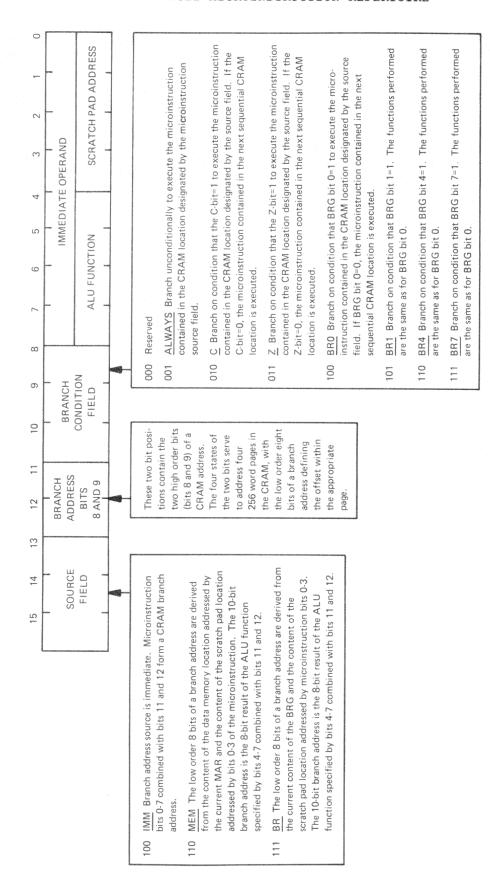

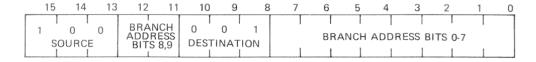

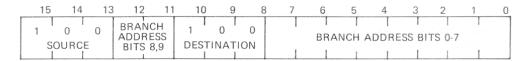

The KMCll microprocessor executes two major classes of microinstructions: the Branch class and the Move class. Branch class microinstructions implement conditional and unconditional program jumps as well as subroutine entry and return. Move class instructions provide for interregister and intermemory data transfers and for logical and arithmetic operations on the transferred data.

Various configurations of each microinstruction class are used to construct the macroinstruction set described in Chapter 4. The detailed descriptions of each microinstruction class are presented in Chapter 3.

A major characteristic of the KMCll is that the CRAM is separate from the data memory. A microprogram executed from the CRAM has free access to the data memory and all internal registers through microinstruction execution. However, a CRAM location cannot be modified through microinstruction execution.

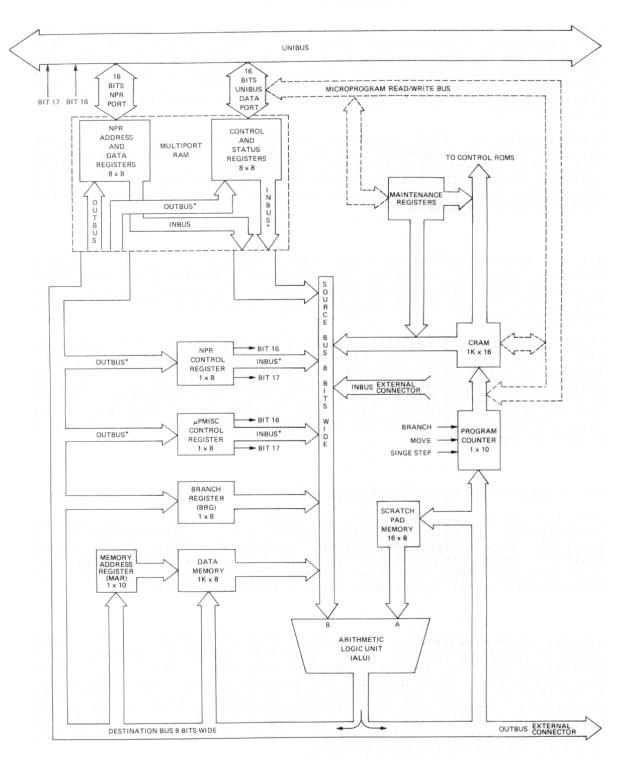

Figure 2-1 is an overall block diagram of the KMCll. It shows the structure of the processor and the data paths connecting that

structure. This section summarizes the structural components accessed through internal buses, through direct microinstruction execution, and over the UNIBUS, as well as the Arithmetic Logic Unit (ALU), which is accessible to all internal registers.

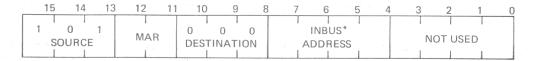

# 2.1.1 INBUS/OUTBUS and INBUS\*/OUTBUS\* Accessed Registers

The INBUS/OUTBUS and the INBUS\*/OUTBUS\* (extended) serve as the data and address link between the KMC11 and its external environment. These busses link a group of internal registers and serve as the interface between the KMC11 and the UNIBUS as well as the KMC11 and an external device. They are accessed through assigned fields in the microinstruction. The registers addressed over these busses include the 16 bytes of the multiport RAM, the NPR control register, the µPMISC register, and registers associated with an external device. These registers are described in detail in Sections 2.1.1.1 through 2.1.1.4.

- 2.1.1.1 Multiport RAM The multiport RAM is a 16-byte random-access memory divided into two 8-byte sections that are addressed through the INBUS\*/OUTBUS\* and the INBUS/OUTBUS. One section contains the CSRs for the KMCll microprocessor, and the other serves as an address and data port for NPR transfers. As shown in Figure 2-1, the multiport RAM interfaces directly with the UNIBUS for the transfer of data words or bytes and the 16 low-order bits of a UNIBUS address. This memory is byte addressable from the microprocessor; the two 8-byte sections can be accessed by the microprogram for both read and write operations. The UNIBUS CSRs are accessed through the INBUS\*/OUTBUS\* and NPR interface through the INBUS/OUTBUS. From the UNIBUS, the CSRs are both word and byte addressable and can be read from and written into by the main CPU or another NPR device.

- 2.1.1.2 NPR Control Register The NPR control register is an 8-bit formatted register that enables the microprogram to control input and output NPR transactions. This register also contains the two high-order bits of the UNIBUS address for an input NPR transaction. Note that an input NPR transaction involves the transfer of data from main CPU memory to the microprocessor. Conversely, an output NPR transaction involves transfer of data from the multiport RAM to main CPU memory.

The NPR register also stores the state of MAR bits 8 and 10, which can be read by the microprogram for detection of page and memory overflow. This register is addressed as a register in the INBUS\*/OUTBUS\* category.

Figure 2-1 KMCll Register and Data Path Structure

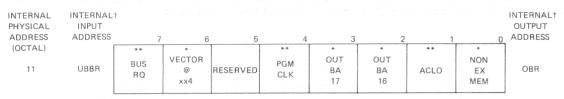

2.1.1.3 Microprocessor Miscellaneous Control Register - The microprocessor miscellaneous control ( $\mu PMISC$ ) register is an 8-bit register that contains various control and function bits necessary for operation of the KMCll. For example, this register contains (1) an internal timing bit that times 50- $\mu$ s intervals, and (2) a bit that flags the addressing of a nonexistent main CPU memory location by the microprocessor.

Specific bits are also available to the microprogram to control initiation of bus requests over the UNIBUS and to specify one of two vectors for appropriate interrupt processing. In addition, this register contains the two high-order UNIBUS address bits for an output NPR transaction. This register is addressed as a register in the INBUS\*/OUTBUS\* category.

2.1.1.4 External Connector - The KMCll microprocessor is equipped with an external connector that supports eight parallel data input lines and eight parallel data output lines. These lines provide the KMCll with direct access to a high-speed peripheral device such as a DMCll line unit.

Eight internal 8-bit register addresses are assigned to the supported line unit. As shown in Figure 2-1, these registers (physically located in the external line unit) are read from the input bus and written from the output bus through the external connector. A typical line unit capable of being used with the KMC11 microprocessor is the Network Link Synchronous Line Unit (DMC11-DA). (The title and document number identifying the maintenance manual for this device are listed in Section 1.5.)

# 2.1.2 Components Accessed Through Direct Microinstruction Execution

Specific KMCll registers are addressed as either sources or destinations of data or loaded through uniquely coded fields in the pertinent microinstruction. These registers include the branch register (BRG), data memory, the memory address register (MAR), the program counter (PC), and the scratch pad. These components are described in detail in Sections 2.1.2.1 through 2.1.2.4.

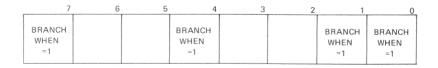

- 2.1.2.1 Branch Register The branch register (BRG) is an 8-bit register used by Branch class microinstructions to specify branch conditions and to derive a branch address. The Move class microinstruction also uses the BRG as a data source and destination. A specific Move class microinstruction can perform a 1-bit right shift on the BRG. Through this Move microinstruction, the BRG can be set up to implement a subsequent conditional branch based on the state of certain BRG bits. The BRG also can be used as a general-purpose storage register by the microprogram.

- 2.1.2.2 Data Memory and Memory Address Register As previously indicated, a major feature of the KMC11 architecture is the use of a separate instruction and data memory. The KMC11 data memory is a 1K  $\times$  8-bit RAM that is read/write accessible to the microprogram. The memory is addressed by a 10-bit memory address register (MAR) that is write-accessible only to the microprogram and cannot be read directly.

Through specific Move class instructions, the MAR can be loaded with an 8-bit address for page offsets (256-byte page) and the two high-order bits to designate one of four pages. A full 10-bit address is loaded in two steps: the eight low-order bits and the two high-order bits. This loading of the MAR can be performed in any sequence desired. In addition, the full 10-bit contents can be incremented to address the next data memory location.

Since the microprogram cannot read the MAR, a page overflow bit and a memory overflow bit are stored in the NPR register. The microprogram uses the page overflow bit (bit 8 of the MAR) to detect page overflow and the memory overflow bit to detect total data memory overflow. In addition, the MAR can be incremented across page boundaries.

2.1.2.3 Program Counter - The KMCll PC has two modes of operation, determined by the class of microinstruction currently being executed. When a Move class instruction is executed, the content of the PC is incremented by one at the conclusion of current microinstruction execution to address the next sequential microinstruction.

If a Branch class instruction is executed and designated branch conditions are satisfied, the result of ALU operation on the two microinstruction-specified operands or the value of a single operand is written into the PC to address the next microinstruction to be executed. Figure 2-1 shows that the microprogram can write into the PC only through the ALU, as a consequence of a Branch class microinstruction execution.

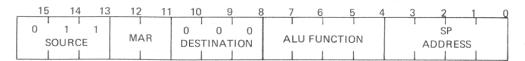

2.1.2.4 Scratch Pad Memory - The KMCll scratch pad memory is a high-speed, read-write, random-access memory made up of sixteen 8-bit bytes, and addressed by the microprogram over the destination bus (Figure 2-1). Scratch pad memory output provides the sole input to the A-side of the ALU.

With Branch class microinstructions, the contents of a scratch pad location can serve as an operand for an arithmetic or logic operation with a second operand such as a data memory location or the BRG to derive a jump address. By using Move class microinstructions, data can be transferred between all internal registers and memories except for the CRAM, the PC, and the MAR. A single Move class instruction cannot be used to exchange the contents of two scratch pad locations. Rather, the contents of one location must first be moved to an internal register that inputs to the B-side of the ALU (such as the BRG). A second Move transfers it to the desired scratch pad location.

# 2.1.3 Components Accessed from the UNIBUS

The KMCll structural components that are accessed only from the UNIBUS include the Control RAM (CRAM) and the two maintenance registers. The functions of these components are described in detail in this section.

2.1.3.1 Control RAM - The KMCll control RAM (CRAM) is a lK  $\,$  x  $\,$  16-bit random-access memory characterized by an extremely high speed access cycle resulting in a microinstruction execution time ranging from 300 ns for most microinstructions to 330 ns for microinstructions accessing the multiport RAM. As previously stated, the microprogram

which controls the functioning of the microprocessor, is stored in and executed from the CRAM.

A loader residing in the main CPU loads the microprogram into the CRAM. A loader that operates as a task under RSX-ll/IAS is described in detail in Chapter 5. Techniques for interfacing this loader with other operating systems are also presented in Chapter 5.

A loader transfers a microprogram stored in main CPU memory over the UNIBUS one microinstruction at a time for storage in the KMCll CSRs. Each instruction is accompanied by the CRAM address for that instruction. For each microinstruction transferred, the loader sets two control bits in the CSR maintenance register: one to load the microinstruction address and another to store the instruction in the CRAM address designated.

Conversely, a given CRAM location can be read over the UNIBUS from the main CPU through use of the KMCll CSRs. In this case only a PC address is stored in the CSRs and specific control bits configured. A main CPU program can then read the addressed CRAM location from the CSRs.

As shown in Figure 2-1, these transfers are accomplished from the CSRs over the microprogram read/write bus. This bus, although internal to the KMC11, cannot be accessed by the microprogram; rather, it is a facility employed by the main CPU for loading, debugging, and maintaining the KMC11 microprogram. Details on the structure and use of the microprogram read/write bus are covered in Section 2.2.2.

2.1.3.2 Maintenance Registers - One maintenance register is used to store a test microinstruction for subsequent execution, and the second serves to address a CRAM location for microinstruction loading. For this discussion, the first is referred to as the maintenance register and the second, the maintenance address register.

The microprogramming debugging function is performed through the maintenance register. During debugging, the KMCll debugging aid (Chapter 6) must be able to read the registers and data memory internal to the KMCll. The debugging aid primarily resides in and is executed from main CPU memory with breakpoint support code in the KMCll.

In actual practice, the debugging aid, through use of specific CSR control bits, can store a microinstruction in the maintenance register, and then execute it as though it came from the CRAM. For example, a series of instructions could move the content of a data memory location addressed by the MAR to the CSRs (INBUS\*/OUTBUS\*) for retrieval and examination by the debugging aid.

During CRAM load time, the maintenance address register is loaded from the UNIBUS to address the CRAM location, which stores an associated microinstruction. This register is also used by the KMCll debugger when a CRAM location is examined or modified. (See Section 6.1.1.)

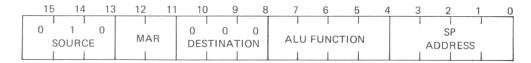

# 2.1.4 Arithmetic/Logic Unit

The KMCll arithmetic/logic unit (ALU) has two sets of 8-bit data input lines and one set of 8-bit data output lines (Figure 2-1). The two sets of input lines are referred to as the A-input and the B-input. The output lines are extended to form a destination bus to all

internal registers and memories in the microprocessor. The A-input accepts data from the scratchpad memory only; the B-input accepts data from the data, CRAM, and multiport memories as well as the NPR, BRG, and  $\mu PMISC$  registers.

For Branch class instructions, the KMCll ALU implements jump address derivations, indexed jumps, and conditional jumps based on an arithmetic or logical condition. For Move class instructions, the ALU performs logical and arithmetic operations on registers and the contents of memory locations; the results are stored in a specified register or memory over the destination bus. As shown in Figure 2-1, the CRAM cannot be accessed through the ALU.

The ALU also asserts the Carry (C) bit and the Zero (Z) bit in response to the various arithmetic and logic operations implemented by Move class microinstructions. The C-bit is asserted as a binary one when a given addition produces a carry term, and as a zero when a given subtraction produces a borrow term. Similarly, when a given arithmetic or logic operation produces a result of all ones (377 octal), the Z-bit is asserted as a binary one.

## 2.2 DATA PATHS

Within the structure of the KMCll, there are four defined data paths:

- 1. the source bus,

- 2. the destination bus,

- 3. the UNIBUS interface, and

- 4. the microprogram read/write bus.

The first two paths in this list are concerned with the transfer of data between KMCll internal registers and memories. The third provides for transfer of data over the UNIBUS between the KMCll and the main CPU. Finally, the fourth data path listed, the microprogram read/write bus, facilitates the loading of microinstructions from the UNIBUS to the CRAM or to the maintenance registers. The functional descriptions of these buses (Sections 2.2.2 through 2.2.5) are preceded by a discussion of the concept of source destination data transfers as implemented by the KMCll microprocessor (Section 2.2.1).

# 2.2.1 Source Destination Data Transfer

Data transfer between internal registers and memories is conducted exclusively over the source bus and destination bus (Figure 2-1). A data source is always an input to the B-side of the ALU, and a destination is always the internal register or memory designated as the recipient of ALU output.

In general, the data source specified in the microinstruction is one of two operands to be operated on by the ALU in a manner designated by the instruction; the second operand is the contents of a scratch pad location. For data memory, the location containing the source operand is the location addressed by the current contents of the MAR. When the INBUS/OUTBUS or INBUS\*/OUTBUS\* is designated as the source of an operand for input into the B-side of the ALU, the operand is addressed by a field in the microinstruction. Where relevant, a scratch pad address is also specified by a microinstruction field.

For certain configurations of Branch class instructions, the source operand and the scratch pad location addressed by the pertinent microinstruction are operated upon by the ALU to derive a jump address. This derived address would point to a page offset in the CRAM containing the next microinstruction to be executed if the branch conditions are satisfied. Note that page address bits 8 and 9 are also contained in the microinstruction to form the full 10-bit address.

For Move class instructions, the source operand and the scratch pad location addressed by the pertinent microinstruction can be operated upon by the ALU with the result transferred to the destination designated by the microinstruction. Alternatively, the source operand can be transferred directly to the designated destination without change. Note that the use of internal registers and memories as destinations of data has relevance only to Move class instructions since the PC is the only possible destination for the results of Branch instruction execution.

Specific internal registers such as the scratch pads, the NPR control register, the  $\mu PMISC$  register, the CSRs, and the NPR data and address registers require a subaddress field in the microinstruction for proper referencing. Therefore, when any of these registers is used as a data source or destination, a field in the microinstruction is reserved for the specific address. When data memory is designated as a data destination, the memory location to contain the transferred data is addressed by the current content of the MAR. Since the MAR can be a data destination, it can be set to address a desired data memory location by a Move instruction (Figure 2-1).

# 2.2.2 Source Bus

Figure 2-1 shows that the KMCll internal source bus is a parallel 8-bit data path that accepts data from one of eight separate sources as designated by the currently executed microinstruction. These sources include the BRG, the registers addressed through the INBUS and INBUS\*, the external connector, the data memory, and the low-order byte of the current microinstruction. This bus connects to the B-side of the ALU providing for input of a source operand from the selected source register or memory location.

At microinstruction execution time, the state of the instruction source field specifies the source operand, thereby selecting the specific register or memory as the source of data input to the B-side of the ALU.

# 2.2.3 Destination Bus

Figure 2-1 shows that the destination bus is also a parallel 8-bit data path that conveys the output of the ALU to all internal registers and memories. The output bus routes data to six separate destinations: (1) BRG, (2) MAR, (3) data memory, (4) OUTBUS and OUTBUS\* registers including the NPR and  $\mu PMISC$  registers, the external connector, the CSRs and the NPR data and address registers, (5) scratch pad, and (6) PC.

Move class microinstructions can designate any of these registers and memories, with the exception of the PC, as a data destination. As previously noted, the PC serves as a data destination only for the results of a Branch class microinstruction execution.

# 2.2.4 UNIBUS Interface

As shown in Figure 2-1, the destination bus, in conjunction with the source bus, provides the path not only for internal data transfers, but also for transfer of data between internal registers and memories and the main CPU. The interface between the KMC11 microprocessor and the UNIBUS is the multiport RAM. Through the multiport RAM, data is transferred over the UNIBUS between the KMC11 and the main CPU by way of the CSRs or under NPR control.

I/O data routed through the CSRs is controlled by the KMCll and the main CPU through the use of a microprogram-defined scheme. In a typical microprogram implementation such as COMM I/OP, data received and transmitted through the CSRs takes the form of structured commands.

Note that the programmer must design his CSR-accessing algorithms in a manner that implements the orderly discipline necessary to the parallel operation of a KMCll and an associated PDP-11. This discipline must take into account all the detailed programming considerations described in Chapter 7.

#### CAUTION

Failure to implement a properly disciplined KMCll CSR accessing algorithm can lead to timing problems and cause unreliable system operation.

In COMM I/OP, one set of these commands permits a user program in the main CPU to configure and initialize a KMC11 microprogram as well as assign and deassign main CPU buffer space accessed by that program. Similarly, a second command set permits a KMC11 microprogram to transfer certain control information and communicate normal and error completions to the main CPU. These commands are described in detail in the COMM IOP-DUP and -DZ programming manuals. (Refer to Section 1.5 for document numbers.)

All data transfers between the KMCll and the main CPU, with the exception of user-designated control information normally passed through the CSRs, are typically performed by NPRs. An NPR transaction can access any UNIBUS address including main CPU memory and any I/O control register in the I/O page. These NPR transfers are conducted under the control of the KMCll. As indicated in Figure 2-1, NPR transfers occur over the UNIBUS from the KMCll to a UNIBUS address and from a UNIBUS address to the KMCll. An NPR that transfers data from the KMCll to a UNIBUS address is designated an output NPR, and the converse, an input NPR. The INBUS/OUTBUS section of the multiport RAM is partitioned to store the 16 low-order bits of a UNIBUS address and the associated 16 data bits for both input and output NPRs. Actual control of an NPR transfer, which is performed asynchronously with respect to the microprogram, is exercised by the NPR control register. As previously indicated, the extended bus address bits (bits 16 and 17) for an output NPR are contained in the µPMISC register and for an input NPR these bits are contained in the NPR register.

# 2.2.5 Microprogram Read/Write Bus

Unlike the source bus, the destination bus, and the UNIBUS interface, the microprogram Read/Write bus is accessible only to the main CPU over the UNIBUS and cannot be accessed in any manner by the KMCll microprogram. The purpose of this data path is to provide for loading the microprogram into the CRAM from the main CPU. In addition, a user program in the main CPU (for example, a debugger) can use this path to write into and read from the maintenance registers as well as read from a CRAM location addressed by the PC.

Figure 2-1 shows that this data path originates at the KMC11 UNIBUS data interface connecting to the INBUS/OUTBUS section of the multiport RAM. In the process of loading microinstructions into the CRAM or maintenance registers or reading from these sources, the data is stored in the INBUS\*/OUTBUS\* section of the multiport RAM. Data is also routed onto or off the microprogram read/write bus directly onto or from the UNIBUS. Note that data is moved over this path by the user program through programmmed data transfers involving 16-bit address and data words only. As previously stated, control of this data path is maintained by a user program through specifically assigned bits in the high byte of CSRO.

# 2.3 REGISTER AND MEMORY FORMATS

The operational components of the KMCll microprocessor that are assigned a fixed format for control purposes include the following: (1) the KMCll CSRs, (2) the NPR data and address registers, (3) the NPR control register, (4) the  $\mu PMISC$  register, and (5) the BRG.

The functions performed by the remaining KMCll components, for example, the CRAM, the scratch pad, the data memory, and the maintenance instruction register, do not require assigned formats. An illustration of each format along with a detailed description of the function performed by each field within a register or memory is presented for each pertinent KMCll component in Sections 2.3.1 through 2.3.4.

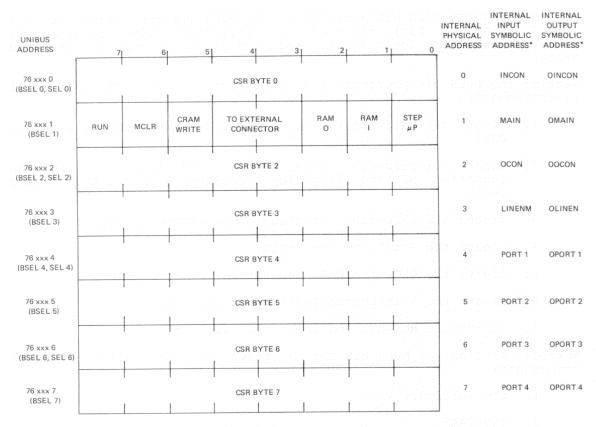

# 2.3.1 KMCll CSR Format

As shown in Figure 2-2, the 8-byte partition of the multiport RAM, which is addressed through the INBUS\*/OUTBUS\*, contains the UNIBUS CSRs for the KMC11 microprocessor. These registers are assigned the following UNIBUS addresses in the floating I/O page: 76XXXO, 76XXX1, 76XXX2, 76XXX3, 76XXX4, 76XXX5, 76XXX6, and 76XXX7, with the even addresses forming the word boundaries. These CSRs are both word and byte addressable from the UNIBUS. For purposes of identity (Figure 2-2), the CSR bytes are referred to by the names BSELO through BSEL7, and on word boundaries by the names SELO, SEL2, SEL4, and SEL6. However, from the KMC11, the CSRs are byte addressable only.

<sup>\*</sup>Symbols used by KMC11 Macroassembler; see Chapter 4.

Figure 2-2 KMCll CSR Format

Figure 2-2 shows that the only CSR having a fixed or hardware-defined format is CSR 1. CSR 1, like the remaining CSRs, exist as read/write locations in the multiport RAM. In addition, the CSR 1 control bits have associated hardware logic elements that implement the functions performed by these bits. The user program can set and clear these bits and the associated logic elements over the UNIBUS through programmed data transfers. The microprogram can also access the multiport RAM through the internal data paths to set and clear CSR 1 control bits. However, the states of the associated logic elements are not altered when the microprogram changes the state of a corresponding bit. Therefore, the microprogram can never assume that the state of a CSR 1 control bit reflects the state of the associated logic element.

Formats for the remaining CSRs are a function of the specific application microprogram; therefore, the descriptions that follow are concerned only with CSR  ${\tt l.}$

#### NOTE

The symbolic addresses assigned the CSR registers shown in Figure 2-2 are those defined by the KMCll Macroassembler described in Chapter 4.

The user program sets bit 6 of CSR 1, the MCLR (master clear) bit, and bit 7 (the RUN bit) at KMCll initialization time to clear all condition-sensitive logic and to place the microprocessor in the run state.

Setting the MCLR bit performs the following actions on the KMCll microprocessor:

- clears all hardware logic related to the maintenance bits in CSRl,

- 2. clears all flip-flops related to the NPR register with the exception of the flip-flop associated with NPR REQ (Figure 2-4),

- 3. clears all flip-flops related to the  $\mu PMISC$  register,

- 4. clears the Z-bit and the C-bit,

- 5. clears the BRG, the MAR, and the PC,

- 6. clears the maintenance instruction register, and

- 7. clears the RUN bit and zeros all timing signals.

However, setting the MCLR bit has no effect on the following KMCll components:

- 1. the multiport RAM,

- 2. the CRAM,

- 3. data memory,

- 4. the scratch pad, and

- 5. the flip-flop associated with the NPR REQ bit.

The NPR REQ bit is cleared independently due to its function in the NPR process by the UNIBUS control signal DATA BUS INIT asserted by the main CPU. Delays implemented through ACLO and PGM CLK (Section 2.3.3) are not cleared but expire at the end of the delay associated with these signals.

With MCLR set, a PDP-11 program can then immediately set the RUN bit through execution of an instruction. The specific conventions concerning the setting and clearing of the RUN bit are detailed in Chapter 7. Detailed examples of the use of the MCLR and RUN bits at initialization time are contained in the COMM IOP-DUP and COMM IOP-DZ programming manuals. (Refer to Section 1.5 for document numbers.)

Bits 2 and 5, RAM O and CRAM WRITE (Figure 2-2), are used together to load a CRAM address and a microinstruction over the microinstruction read/write bus into the maintenance address register and CRAM, respectively. These bits provide the mechanism for loading a complete microprogram into the KMCll CRAM and for changing unique microinstructions.

In this process, the user sets RAM O to one, and loads (1) the address of the CRAM location to which the microinstruction is to be written into SEL4 (this action loads the maintenance address register but does not change the PC content) and (2) the actual instruction into SEL6. The user then sets CRAM WRITE to one, and the instruction is loaded

into the CRAM location addressed by the new value of the maintenance address register.

At this point, both the RAM O and CRAM WRITE bits may be cleared by the PDP-11 program prior to performing the next microinstruction write. However, instead of clearing both RAM O and CRAM WRITE, CRAM WRITE alone can be cleared, and the SEL6 read to verify that the microinstruction was correctly written into the proper location. In this case, the CSR SEL6 contains the contents of the CRAM location addressed by the maintenance address register. SEL4 also contains the contents of the CRAM location written into. However, after RAM O is cleared, SEL4 contains the address of the last CRAM location written. Similarly, the user can read a selected CRAM location by loading the desired PC address into SEL4, setting RAM O, and then reading SEL6.

As an example of this CRAM write/read process, consider the storing of a microinstruction that transfers the contents of the INBUS\* byte 7 to location 4 of the scratch pad into CRAM location 1754 and then verifies the write:

| MOVB | #4,BSEL1     | ;Set RAM O to one                  |

|------|--------------|------------------------------------|

| MOV  | #1754,SEL4   | ;Load address                      |

| MOV  | #123146,SEL6 | ;Load microinstruction             |

| BISB | #40,BSELl    | ;Set CRAM WRITE                    |

| BICB | #40,BSEL1    | ;Clear CRAM WRITE                  |

| CMP  | #123146,SEL6 | ;Verify that instruction is loaded |

After clearing CRAM WRITE, the user can examine the contents of SEL4 and SEL6 directly from the main CPU console. This method of single instruction writing and reading is useful during the microprogram debugging process for changing the contents of specific CRAM locations and verifying that the change is correct. RAM O must be cleared prior to writing the next instruction.

For example, when loading a complete microprogram, the first location in that program could be the base address to be incremented for each microinstruction stored in the CRAM. The microprogram could be stored in a main CPU buffer to be accessed for loading by programmed data transfers in the autoincrement mode. Note that RAM O and CRAM WRITE should be cleared after each microinstruction is loaded (Chapter 6).

Combinations of bits 0 and 1 of BSELl, RAM I and STEP  $\mu P$  are used to write a microinstruction from the main CPU into the KMCll maintenance instruction register. As described in Section 2.1.10, a debugging aid resident in the main CPU can store a microinstruction in this register from the UNIBUS and then execute that instruction in place of a specific instruction in the CRAM.

The first step in loading a microinstruction into the maintenance instruction register involves clearing the RUN bit (Bit 7 of BSEL1). Next, the microinstruction is loaded into SEL6, and RAM I is set to load the microinstruction into the maintenance instruction register. Finally, setting STEP  $\mu P$  causes the instruction to be executed from the maintenance instruction register rather than the CRAM. The PC is also incremented each time STEP  $\mu P$  bit is set. With RAM I cleared, setting STEP  $\mu P$  causes the microinstruction in the next CRAM location to be executed. In addition, the contents of the maintenance instruction register can be read from either SEL4 or SEL6. The user must first clear the STEP P bit, and then set RAM I along with RAM O and read the contents of SEL4 or SEL6 or SEL6.

As shown in Figure 2-2, bits 3 and 4 of BSELl are labeled "to external connector." These bits can serve as status/control bits for an external device.

# 2.3.2 NPR Address and Data and NPR Control Register Formats

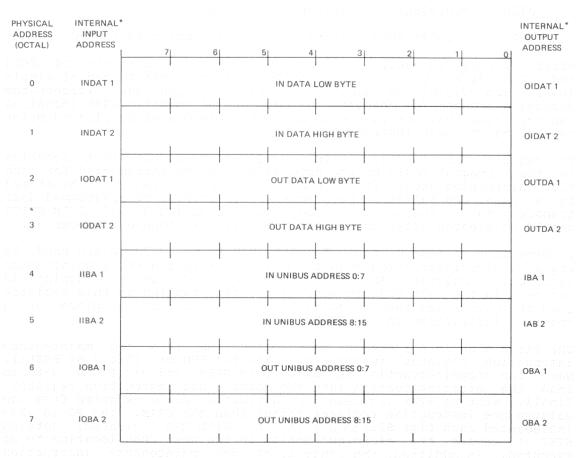

The NPR transactions performed by the KMCll directly involve the NPR address and data registers, which are addressed through the INBUS/OUTBUS and the NPR control register. Note that the NPR register is addressed through the INBUS\*/OUTBUS\*. As shown in Figure 2-3, the NPR address and data registers serve as the buffer for the 16 low-order UNIBUS address bits and the 16-bit data words for both in-NPR and out-NPR transactions. The NPR transactions performed by the KMCll microprocessor are controlled by the NPR control register (Figure 2-4).

Before executing an NPR transaction, the KMCll microprogram must store the 16 low-order bits of the UNIBUS address and the associated 16-bit data word (if the transaction is an out-NPR) in the NPR address and data registers. For an in-NPR, the source of UNIBUS address bits 16 and 17 is the NPR register, and for an out-NPR, the source of these bits is the  $\mu PMISC$  register. (See Figures 2-4 and 2-5.) The microprogram accesses the NPR address and data registers by referencing the NPR register and using the internal symbolic or physical addresses shown in Figure 2-3.