# PDP-8/E OPTIONS

| SECTION 1 MECHANICAL EXPANSION OPTIONS SYSTEM EXPANDER BOXES PANEL OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page<br>7-2                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| SECTION 2 COMPUTER INTERNAL OPTIONS  EXTENDED ARITHMETIC ELEMENT  MEMORY EQUIPMENT  REAL TIME CLOCKS  POWER FAIL DETECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-4<br>7-4<br>7-14<br>7-25<br>7-26                                                                                          |

| SECTION 3 OMNIBUS INPUT/OUTPUT EQUIPMENT OPTIONS CONSOLE TELEPRINTERS PAPER TAPE READERS AND PUNCH CRT DISPLAYS XY PLOTTERS LINE PRINTERS DATA COMMUNICATIONS EQUIPMENT CARD READERS OMNIBUS MAGNETIC TAPE OPTIONS DECTAPES DECMAGTAPES LABORATORY PERIPHERALS A-TO-D CONVERTERS ANALOG MULTIPLEXERS BUFFERED DIGITAL I/O INTERPROCESSOR BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-35<br>7-35<br>7-41<br>7-44<br>7-54<br>7-62<br>7-68<br>7-94<br>7-101<br>7-103<br>7-117<br>7-117<br>7-122<br>7-124<br>7-131 |

| SECTION 4 EXTERNAL BUS INPUT/OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-131                                                                                                                       |

| EQUIPMENT OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-134                                                                                                                       |

| EXTERNAL BUS INTERFACE CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-134                                                                                                                       |

| POSITIVE I/O BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-134                                                                                                                       |

| GENERAL PURPOSE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-135                                                                                                                       |

| DATA BREAK INTERFACE RANDOM ACCESS DISK DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-137                                                                                                                       |

| MAGNETIC TAPE EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-138                                                                                                                       |

| DECTAPES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-160                                                                                                                       |

| DECMAGTAPES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-160<br>7-180                                                                                                              |

| DATA ACQUISITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-160                                                                                                                       |

| A-TO-D CONVERTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-192                                                                                                                       |

| ANALOG MULTIPLEXERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-195                                                                                                                       |

| INTEGRATING DIGITAL VOLTMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-198                                                                                                                       |

| D-10-A CONVERTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-204                                                                                                                       |

| UNIVERSAL DIGITAL CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-207                                                                                                                       |

| MOTERIA TO THE TOTAL TOT | 7-207                                                                                                                       |

| WRITING TABLET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-207                                                                                                                       |

| POSITIVE I/O BUS DATA COMMUNICATIONS FOLIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-211<br>7-219                                                                                                              |

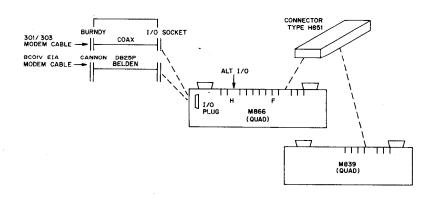

| POSITIVE I/O BUS DATA COMMUNICATIONS EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-211                                                                                                                       |

| POSITIVE I/O BUS DATA COMMUNICATIONS FOLIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-211<br>7-219                                                                                                              |

# CHAPTER 7

# PDP-8/E OPTIONS

### GENERAL

Chapter 7 contains descriptions of all the standard peripheral devices that are optionally available for the PDP-8/E computer. Section 1 deals with the mechanical expansion options. Section 2 covers the computer internal options. Section 3 describes the OMNIBUS input/output equipment options. Section 4 is concerned with the external bus input/output equipment options.

# SECTION 1 MECHANICAL EXPANSION OPTIONS

Included in this section are those options which affect the external physical properties of the PDP-8/E computer, such as cabinets and panels. Further details regarding installation of these options appear in Chapter 11 of this handbook.

### SYSTEM EXPANDER BOXES

# Type BA8-AA System Expander Box

The BA8-AA includes a power chassis assembly and OMNIBUS assembly, capable of accommodating up to 20 PDP-8/E modules, and a BC08H-3F Cable Set (three and a half feet in length) with rack-mountable slides included, as well as a Type KC8-EB blank front panel.

# Type BA8-AB System Expander Box

The BA8-AB includes a power chassis assembly and OMNIBUS assembly, capable of accommodating up to 20 PDP-8/E modules, and a BC08H-3F Cable set (three and a half feet in length) with table-top cover included, as well as a Type KC8-EB blank front panel.

# Type BE8-A OMNIBUS Expander

The BE8-A includes an additional OMNIBUS assembly, capable of accommodating up to 20 PDP-8/E modules, together with M935 Bus Connectors for expanding either the PDP-8/E, the BA8-AA, or the BA8-AB to 38 slots.

### PANEL OPTIONS

## Type KC8-EC Turn-Key Front Panel

The KC8-EC panel contains a key-lock ON/OFF switch for controlling the application of power to the PDP-8/E system. The KP8-E Power Fail option is a prerequisite for using this panel. It is used as an alternate panel to the PDP-8/E.

# Type KC8-EB Blank Front Panel

This panel can be used in place of the KC8-EA panel or the KC8-EC panel on the PDP-8/E, and is supplied with the BA8-AA or BA8-BA Expander Box option. It is used on the PDP-8/E when the system is equipped with a KP8-E, and the user wishes to switch power externally.

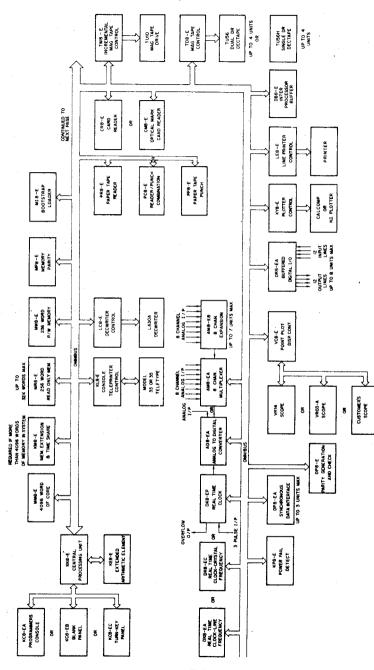

PDP-8/E System Block Diagram

7-2

PDP-8/E System Block Diagram (Continued)

## SECTION 2 COMPUTER INTERNAL OPTIONS

This section deals with internal options for the PDP-8/E computer, including those concerned with the extended arithmetic facility, memory equipment, real-time measurement, and power fail detection and restart.

Many of these are covered in greater detail in Chapters 3 and 4 of this handbook.

The execution time for IOT instructions in this section is 1.2  $\mu$ s, except where otherwise specified in the instructions for extended arithmetic.

# TYPE KE8-E EXTENDED ARITHMETIC ELEMENT (EAE)

The KE8-E option plugs into the PDP8-E OMNIBUS to enable the central processor to perform arithmetic operations at high speeds by incorporating the EAE components with the existing central processor logic so that they operate asynchronously. This two-module option consists of circuits that perform parallel arithmetic operations on positive binary numbers, and includes:

- a. A 5-bit Step Counter (SC) Register. This register is used to record the number of steps performed, and stops many EAE instructions after the correct number of operations. For these instructions, the SC is automatically loaded, and the instruction is terminated when the SC becomes a fixed number. There is one instance, the normalize (NMI) instruction, when the SC is of interest to the programmer. For this reason, instructions allow the programmer to load the SC from memory or the AC, depending upon the mode of operation; and to transfer the contents of the SC to the AC for storage upon interrupt or for program analysis.

- b. A 4-bit instruction register (EAE IR)—This register consists of flip-flops set to MB (6,8-10) during the Fetch cycle of an EAE instruction.

- c. The EAE timing and control logic—all EAE logic is contained in two modules which plug into the OMNIBUS. The KE8-E EAE logic circuits are used in conjunction with the accumulator (AC), link (L), multiplier quotient (MQ), and memory buffer (MB), though asynchronously with them to perform arithmetic operations. When this option is added to a PDP-8/E system, a class of instructions is added to the Group 3 Operate instruction list.

- d. A mode flip-flop which controls the instruction set of the EAE. The mode flip-flop is set to mode A when power is applied to the machine, when the CLEAR key on the panel is operated, and when the CAF instruction is issued.

### **PROGRAMMING**

The Extended Arithmetic Element (EAE) microinstructions are specified by an operate instruction (operation code 7) in which MB(3) and MB(11) always contain binary 1's. The instruction set is arranged so that programs written for the PDP-8/I EAE can be run on the PDP-8/E without modification. A greatly expanded instruction set is also available for new programming.

Two modes of operation, hereafter designated Mode A and Mode B, are available. Mode A, which is the mode in which the computer starts, is the PDP-8/I compatible mode.

### COMMON OPERATIONS

Several EAE operations may be executed in either mode of operation. The common features of these operations are described below.

### Two-word instructions

Many EAE instructions require more than 12 bits. For these instructions, a second 12-bit word is obtained from the next location in memory. The second word is interpreted by the EAE hardware, and used either as an argument or the address of an argument. Program resumes at the location following the second word.

### Multiplication

The Multiply instruction is a two-word instruction. The multiplier is either the second word or is located in the address specified by the second word, depending upon the mode. The contents of the MQ are multiplied by the multiplier and the 24-bit result is left in the AC (most significant bits), and MQ. The multiplication is an unsigned integer multiply, i.e. the multiplier and multiplicand are treated as 12-bit positive numbers with binary point at the right-hand end of the word. The binary point of the product is at the right-hand end of the MQ. If the AC is non-zero at the start of the multiply, its contents are added to the product. The Link is cleared. The SC is used in the execution of this instruction.

### Division

The Divide Instruction is a two-word instruction. The division is either the second word or is located in the address specified by the second word. The contents of the AC (most significant bits) and MQ are divided by the divisor, and the quotient and remainder are left in the MQ and AC respectively. The division is an unsigned integer divide. The Link is cleared if the first subtraction produces a negative result, indicating that divide overflow has not taken place. If the first subtraction produces a positive result, the Link is set (indicating overflow) and the division is terminated. The contents of the AC and MQ are modified if divide overflow occurs. Ordinarily, the divide instruction is followed by a test of the Link to check for overflow before more computation occurs. The SC is used in the execution of this instruction.

### Left Shift

The Link, AC and MQ are treated as one long register. The previous content of the Link is lost, ACO is shifted into the Link, MQO is shifted into AC11, and zero enters the vacated MQ11 position. The second word of the two-word shift left instruction is loaded into the SC and thus defines the number of shifts to be performed.

### Logical Right Shift

The Link is first cleared, then the AC and MQ, but not the Link are treated as one long register. MQ11 is either lost or shifted into the GT flag (depending on the mode). AC11 is shifted into MQ0, and the state of the Link is loaded into AC0. This instruction effectively divides the number of the AC and MQ by two for each place shifted. As in Left Shift, the number of positions shifted is defined by the last five bits of the second word of the two-word instruction.

### Arithmetic Right Shift

This operation is identical to Logical Right Shift, except that the Link is initially loaded with the content of ACO, maintaining the sign of the number in the vacated bits. Because a right shift means shifting the contents of the AC and MQ one place to the right for each place shifted, the value of the 24 bits is effectively divided by two in signed arithmetic.

### Normalization

The Normalize instruction is typically used to cast out and to account for leading zeroes when performing floating-point arithmetic. The Step Counter is initially cleared; then the contents of the L, AC and MQ are shifted left, as described above under Left Shift, until ACO and AC1 are different or until the 24 bits contained in AC and MQ contains the number (6000 0000). The Step Counter is incremented once for each shift. Normalize instruction must not be "ORed" with other EAE operations. At the conclusion of the Normalize instruction, the Step Counter contains a number equal to the number of shifts that were required to perform the normalization and is the EXPONENT (the binary power of 2) the 24-bit number. Thus the normalize instruction converts the number in the AC and MQ into the format. M\*2n; where M is the new result in AC and MQ and n is the contents of the step Counter. (The asterisk is a commonly-used symbol for multiplication)

MODE CHANGING INSTRUCTIONS (All instructions take place in 1.2  $\mu$ sec.) Switch from A to B (SWAB)

Octal Code: 7431

Operation: If the mode flip-flop is "A", it is changed to "B".

If the mode flip-flop is already B, no operation occurs.

Switch from B to A (SWBA) Octal Code: 7447

Operation: If the mode flip-flop is "B", it is changed to "A".

If the mode is already A, no operation occurs.

### Mode A Instructions

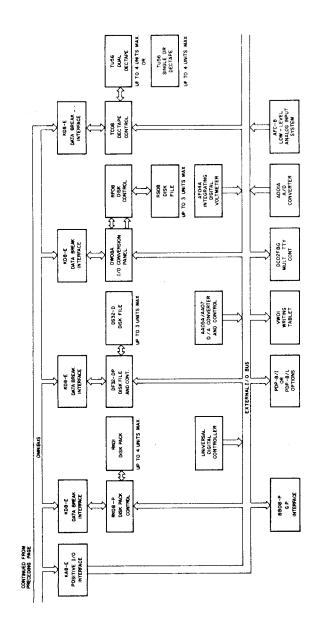

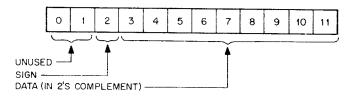

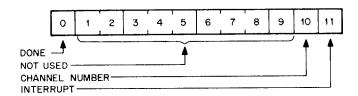

EAE instructions are augmented instructions, and can be combined to perform non-conflicting logical operations, as indicated in Figure 7-1.

Figure 7-1 EAE Mode "A" Bit Assignments

The GT flag, explained in more detail under Mode B, is always zero for Mode A instructions. The instructions involving only bits 4, 5 and 7 have already been defined under Group 3 operate instructions in Chapter 3. For convenience, a summary of these instructions is given below. All execution times are  $1.2~\mu s$ .

Mnemonic Octal Description CAM 7621  $0 \rightarrow AC, O \rightarrow MQ$

MQA 7501 MQ "OR" ed with AC $\rightarrow$ AC

MQA CLA 7701 MQ $\rightarrow$ AC MQ. 7421 AC $\rightarrow$  MQ. Q

The following Mode A instructions are added by the KE8-E hardware:

Step Counter "OR" with AC (SCA)

Octal Code: 7441 Execution time:  $1.2 \mu s$ .

Operation: The contents of the Step Counter are "OR" ed with

the five least-significant bits of the AC, and the result

loaded into the AC.

Step Counter to AC (SCA CLA)

Octal Code: 7641 Execution time:  $1.2 \mu s$ .

Operation: The contents of the Step Counter are loaded into

AC 7-11. AC 0-6 are cleared.

Step Counter Load from Memory (SCL)

Octal Code: 7403 Execution time: 2.6 us.

Operation: The next word in memory is treated as an operand.

The one's complement of the last five bits of this operand are loaded into the Step Counter, and program resumes at the instruction word following the operand. The SCL instruction is most commonly used in interrupt servicing for restoration of the Step

Counter.

Multiply (MUY)

Octal Code: 7405 Execution time: 7.4  $\mu$ s.

Operation: The second word of this two-word instruction is the

multiplier. Multiplication takes place as described

above under "Common Operations"

Divide (DVI)

Operation:

Octal Code: 7407

Execution time: 7.4  $\mu$ s. if no divide overflow, 2.6  $\mu$ s. if divide overflow.

The second word of this two-word instruction. Division takes place as described above under "Common Operations." Program resumes at the location following the divisor. If the Link  $\equiv 1$ , at the conclusion of the division, divide overflow occurred; other-

wise, the divide was legal.

Normalize (NMI)

Octal Code: 7411

Execution time:  $1.5 + 0.3*N \mu s$ , where N is the number of shifts

necessary to normalize.

Operation: The contents of AC and MQ are normalized, as de-

scribed above under "Common Operations". This

command must not be combined with any other EAE commands. NMI "OR"ed with MQL is the SWAB instruction described under Mode Changing.

Shift Left (SHL)

Octal Code: 7413

Execution time: 2.6 + 0.3\*N  $\mu s.$ , where N is the number of shifts.

Operation: The number of shifts performed is equal to one more than the number in the last five bits of the second word. See "Common Operations" above for a descrip-

tion of Left Shift.

Arithmetic Shift Right (ASR)

Octal Code: 7415

Execution time:  $2.6 + 0.3*N \mu s$ , where N is the number of shifts. Operation: The number of shifts performed is equal to one more

ation: The number of shifts performed is equal to one more than the number in the last five bits of the second word. The old content of MQ11 is lost. See "Common Operations" above for a description of Arithmetic

Right Shift.

Logical Shift Right (LSR)

Octal Code: 7417

Execution time: 2.6 + 0.3\*N  $\mu s.$ , where N is the number of shifts. Operation: The number of shifts performed is equal to one more

than the number in the last five bits of the second word. The old content of MQ11 is lost. See "Common Operations" above for a description of Logical Right

Shift.

### Mode B Instructions

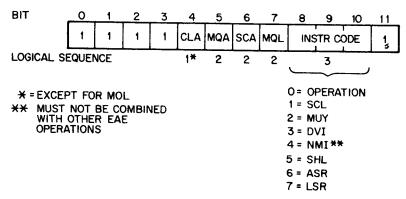

Mode B differs from Mode A in the use of bit 6 of the instruction word, in the location of operands and in greatly increased double-precision arithmetic capability. As in Mode A instructions, these EAE instructions are able to be combined to form non-conflicting logical operations. See Figure 7-2 for Mode B bit assignments.

Figure 7-2 EAE Mode "B" Bit Assignments

In Mode B the GT flag, a flip-flop in the KE8-E, is activated. The GT flag may be manipulated by IOT instructions described in Chapter 3. It is loaded by the SAM instructions, and receives the contents of MQ11 on right shifts.

The instructions involving only bits 4, 5 and 7 have already been defined under Group 3 operate instructions in Chapter 3. For convenience, a summary of these instructions is given below. All execution times are 1.2 μs.

| Mnemonic | Octal | Description                            |

|----------|-------|----------------------------------------|

| CAM      | 7621  | $0 \rightarrow AC, 0 \rightarrow MQ$   |

| MQA      | 7501  | MQ "OR"ed with AC → AC                 |

| MQA CLA  | 7701  | $MQ \rightarrow AC$                    |

| MQL      | 7421  | $AC \rightarrow MQ, 0 \rightarrow AC$  |

| SWP      | 7521  | $AC \rightarrow MQ, MQ \rightarrow AC$ |

The following Mode B instructions are added by the KE8-E hardware:

### Accumulator to Step Count (ACS)

Octal Code: 7403 Execution time: 1.2 μs.

Operation: Bits 7-11 of the AC are loaded into the Step Counter,

and the AC is then cleared.

Multiply (MUY)

Octal Code: 7405 Execution time: 8.6 μs.

Operation: The second word is the address of the multiplier.

If extended memory is being used, the multiplier is obtained from the Data field. Multiplication takes place as described above under "Common Opera-

tions".

Divide (DVI)

Octal Code: 7407 Execution time: 8.6 µs.

The second word is the address of the divisor. If Operation:

extended memory is being used, the divisor is obtained from the Data field. Division takes place as described above under "Common Operations." Program resumes at the location following the address of the divisor. If the Link = 1 at the conclusion of the division, divide overflow occurred: otherwise, the

divide was legal.

Normalize (NMI)

Octal Code: 7411

1.5 + 0.3\*N  $\mu$ s., where N is the number of shifts Execution time:

necessary to normalize.

The contents of AC and MQ are normalized as de-Operation: scribed above under "Common Operations". If the contents of AC and MQ equals 40000000, the AC is

cleared. This command must not be combined with any other EAE commands. NMI "OR"ed with MQL is the SWAB instruction and has no effect if the mode

is already B.

Shift Left (SHL)

Octal Code: 7413

Execution time:  $2.9 + 0.3*N \mu s.$ , where N is the number of shifts. The number of shifts performed is equal to the num-Operation:

> ber in the last five bits of the second word. A shift of zero is a legal command, and does not modify the L, AC or MQ. See "Common Operations" above

for a description of Left Shift.

Arithmetic Shift Right (ASR)

Octal Code:

7415

Execution time: Operation:

$2.9 + 0.3*N \mu s.$ , where N is the number of shifts. The Link is made equal to ACO, and remains in this state for the remainder of the instruction. The num-

ber of shifts performed is equal to the number in the last five bits of the second word. A shift of zero is a legal command which makes the Link equal to ACO, but does not modify the AC or MQ. Bits shifted out of MO11 are shifted into the GT flag, to facilitate round-off operations. See "Common Operations" above for a description of Arithmetic Right Shift.

Logical Shift Right (LSR)

Octal Code: 7417

Execution time: Operation:

$2.9 + 0.3*N \mu s.$ , where N is the number of shifts. The Link is cleared and remains cleared for the re-

mainder of the instruction. The number of shifts performed is equal to the number in the last five bits of the second word. A shift of zero is a legal command which clears the Link, but does not modify the AC or MO. Bits shifted out of MO11 are shifted into the GT flag to facilitate round-off operations. See "Common Operations" above for a description of

Logical Right Shift.

Step Counter "OR" with AC (SCA)

Octal Code: 7441

Execution time: 1.2 μs.

Operation: The contents of the Step Counter are "OR"ed with

the five least-significant bits of the AC, and the result loaded into the AC.

Step Counter to AC (SCA CLA)

Octal Code: 7641 Execution time:

1.2 μs.

Operation: The contents of the Step Counter are loaded into AC

7-11. AC 0-6 are cleared.

Subtract AC from MQ (SAM)

Octal Code: 7457

Execution time: 1.2 μs.

The contents of the AC are subtracted from the MQ Operation: in 2's complement arithmetic. The result is loaded

into the AC. The MQ remains unchanged. If a borrow is propagated from the most significant bit, the Link is set. Otherwise, the Link is cleared. Hence, the Link is set if the original AC was greater than the equal to the MQ. If one wishes to compare signed numbers, the GT flag is helpful. This flag is set if the signed number in the MQ is greater than or equal to the original signed number in the AC; and is cleared otherwise. The SC is not modified. If MQ0  $\pm$  original AC0, complement of MO0  $\rightarrow$  GT

If MQ0 = original AC0, new AC0  $\rightarrow$  GT

THUS:

$1 \rightarrow L$  if AC > MQ \ When AC and MQ are considered  $0 \rightarrow L$  if AC  $\leq$  MQ \ to be positive 12-bit numbers

$1 \rightarrow$  GT if AC  $\leq$  MQ \ When the AC and MQ are con-0 → GT if AC > MQ \ sidered to be signed 2's complement 12-bit numbers.

### **Double-Precision Operations**

These instructions are available only in Mode B. The AC and MQ are treated as a single 24-bit register, with the most significant half of the word in the AC. For operations involving addition or incrementation, the Link is set if a carry occurs from the most significant bit; if no carry occurs, the Link is cleared. The Link is not modified by the DST and DPSZ instructions. The SC is not modified by any of the double-precision instructions.

Two of the double-precision instructions (DAD and DST) are two-word instructions. For these instructions, the contents of the second word (augmented by the Data field bits, if extended memory is used) define the address of the least-significant half of a double-precision word. The most significant half of the word is located in the memory location following the least significant half-word. This format must be adhered to in order for the instruction to work as defined below.

### Double-Precision Add (DAD)

Octal Code: 7443

Execution time:  $5.2 \mu s$ . Operation: The do

The double-precision word specified by the second word is added to the previous contents of the AC and MQ; The result is left in the AC and MQ. If there is a carry from the most significant bit, the Link is set; if there is no carry, the Link is cleared. This instruction can be micro-programmed with the CAM instruction to produce a Double-Precision Load (DLD,

octal 7763).

# Double-Precision Store (DST)

Octal Code: 7445 Execution time: 5.2 us.

Operation: The contents of the MQ and AC are stored at the double-precision location (two consecutive memory

double-precision location (two consecutive memory locations) defined by the (address) second word. The AC, MQ and Link are not changed by this instruction. This instruction can be micro-programmed with the CAM instruction to produce a Double-Precision De-

posit Zero instruction (DDZ, octal 7765).

Double-Precision Increment (DPIC)

Octal Code:

7573

Execution time:

1.8 us.

Operation:

The constant "one" is added to the double-precision number in the AC, MQ in 2's complement arithmetic; the result is left in the AC and MQ. The carry (or lack thereof) is propagated to the Link. This instruction requires the MQL and MQA bits be "1" to work as defined. It may be microprogrammed with the CLA bit to load the AC, MQ with the constant "1".

Double-Precision Complement (DCM)

Octal Code: Execution time: 7575 1.8 us.

Operation:

The number in the AC and MO is complemented and incremented to form the 2's complement of the original number; the result is left in the AC and MQ. The carry (or lack thereof) from the most significant bit is propagated to the Link. This instruction requires the MOL and MOA bits be "1" to work as defined.

Double-Precision Skip if Zero (DPSZ)

Octal:

7451

Execution time:

1.2 us.

Operation:

The 24-bit number in the AC, MQ is tested. If all bits are zero, the next instruction is skipped. If any bit is a one, the next instruction is executed. This instruction, when combined with the CAM instruction, is used to test mode by clearing the AC and MQ and then attempting the DPSZ instruction.

### SUMMARY

The chart below (Figure 7-3) indicates the difference in operation of instructions found in both modes.

| INSTRUCTION         | MODE A                                  | MODE B                                                                                                                              |

|---------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| MUY                 | The next location holds the multiplier. | The next location holds the address of the multiplier.                                                                              |

| DVI                 | The next location holds the divisor.    | The next location holds the address of the divisor.                                                                                 |

| SHL,<br>LSR,<br>ASR | less than the number of shifts.         | The next location holds the number of shifts. (A shift of zero places is legal). On Right Shifts, MQ11 is shifted into the GT flag. |

Figure 7-3 Instruction Differences

Figure 7-4 summarizes cycle times and indicates the longest practical machine cycle. Note that the longest cycle time plus 0.3  $\mu$ s. is the maximum time to enter a DMA cycle, provided the Break Device synchronizes at Int. Strobe time as recommended in Chapter 9. It is possible, by a small amount of programming, to reduce the longest cycle to 6.2 us. This programming consists of pretesting the AC on a normalize, and limiting long shifts to 15 places. Note, for example, that MQL /AC MQ, O AC LSR /Mode B Shift, 6 places 6

is equivalent to an 18-bit logical right shift and has a longest cycle of 3.5  $\mu$ s., rather than 7.1  $\mu$ s. Also, the total execution time for a straight 18-bit shift is 8.3  $\mu$ s., as opposed to 5.9  $\mu$ s. for the above sequence.

|      | MODE A        |               | MODE B           |               |           |                  |           |       |

|------|---------------|---------------|------------------|---------------|-----------|------------------|-----------|-------|

|      | MEM<br>CYCLES | INSTR<br>TIME | LONGEST<br>CYCLE | MEM<br>CYCLES | INSTR I   | LONGEST<br>CYCLE | NOTES     |       |

| SWAB | 1             | 1.2μs         | 1.2μs            | 1             | 1.2       | 1.2              |           |       |

| SWBA | 1             | 1.2           | 1.2              | 1             | 1.2       | 1.2              |           |       |

| SCL  | 2             | 2.6           | 1.4              | N             | ot Availa | ble              |           |       |

| ACS  | 1             | Not Availab   | ole              | 1             | 1.2       | 1.2              |           |       |

| MUY  | 2             | 7.4           | 6.2              | 3             | 8.6       | 6.2              |           |       |

| DVI  | 2             | 7.4           | 6.2              | 3             | 8.6       | 6.2              | No overfl | ow    |

| NMI  | 1             | 1.5+.3N       | 8.1              | 1             | 1.5 + .3N |                  |           |       |

| SHL  | 2             | 2.6+.3N       | 8.9*             | 2             | 2.9+.3N   | 9.2**            | 25-place  | shift |

| ASR  | 2             | 2.6+.3N       | 8.9*             | 2             | 2.9+.3N   | 9.2**            | 25-place  | shift |

| LSR  | 2             | 2.6+.3N       | 8.9*             | 2             | 2.9+.3N   | 9.2**            | 25-place  | shift |

| SCA  | 1             | 1.2           | 1.2              | 1             | 1.2       | 1.2              |           |       |

| DAD  |               | Not Availal   | ole              | 4             | 5.2       | 1.4              |           |       |

| DST  | Not Available |               | 4                | 5.2           | 1.4       |                  |           |       |

| DPSZ | Not Available |               | 1                | 1.2           | 1.2       |                  |           |       |

| DPIC | Not Available |               | 1                | 1.6           | 1.6       |                  |           |       |

| DCM  | ı             | Not Availal   | ole              | 1             | 1.6       | 1.6              |           |       |

| SAM  | 1             | Not Availab   | ole              | 1             | 1.2       | 1.2              |           |       |

<sup>\*</sup>Computed from 1.4+.3N \*\*Computed from 1.7+.3N

Figure 7-4 EAE Mode A/Mode B Instruction Times

## MEMORY EQUIPMENT OPTIONS

The basic memory (MM8-E) is a 4096-word, random-access core memory that performs all the functions of data storage and retrieval. The MM8-E is packaged on three PDP-8/E modules that plug into the OMNIBUS. These modules, when used with the KM8-E Memory Extension and Time Share option, can extend memory capacity up to 32,768 words in increments of 4096 words. In addition, this option enables the PDP-8/E to operate in a time-sharing environment. With the addition of the MP8-E Memory Parity option, all transfers to and from memory can be checked for parity. Other memory options include the MR8-EA 256-Word Read-Only Memory, the MR8-EB 1024-word Read-Only Memory, the MW8-E 256-word Read/Write Memory, and the MI8-E Bootstrap Loader.

# KM8-E Memory Extension and Time-Share Option

This option provides the user with two primary capabilities. The memory extension portion extends the addressing capabilities of the machine from 4069 words up to 32,768 words. The time-share portion enables the computer to operate in either the normal manner (Executive Mode) or the User Mode. User Mode enables the machine to function in a time-sharing environment in which a user program is prevented from disturbing or interfering with another user program. The KM8-E option is packaged on one PDP-8/E module that plugs into the OMNIBUS. This option is required whenever memory capacity is extended beyond 4096 words.

### Memory Extension Description

The functional circuit elements which make up the memory extension control perform as follows: