# CHAPTER 4 PDP-8/E PROGRAMMING SYSTEMS

## **GENERAL**

This chapter deals with the concepts required to program the PDP-8/E and identifies the system programs available to the user. Two handbooks, INTRODUCTION TO PROGRAMMING and PROGRAMMING LANGUAGES, provide a more detailed treatment and description of the commonly used programming languages and programming systems. The chapter is divided into 2 sections. Section 1 provides basic pro-

The chapter is divided into 2 sections. Section 1 provides basic programming guidelines and section 2 identifies the various programming systems and commonly used languages available to the user.

# SECTION 1

# PDP-8/E PROGRAMMING FUNDAMENTALS

Organization of the standard core memory or any 4096-word field of extended memory is summarized as follows:

| Total locations (decimal) Total addresses (octal)   | 0.4095 or 4096<br>0.7777 or 10,000 |

|-----------------------------------------------------|------------------------------------|

| Number of pages (decimal) Page designations (octal) | 0.31 or 32<br>0.37 or 40           |

Number of locations per page (decimal) 0-127 or 128 Addresses within a page (octal) 0-177 or 200

Routines using 128 instructions or less can be written in one page using direct addresses for looping and indirect addresses for data stored in other pages. When planning the location of instructions and data in core memory, the following locations are reserved for special purposes:

|         | Durmana |

|---------|---------|

| Address | Purpose |

0 (octal) Stores the contents of the program counter following a program interrupt.

Stores the first instruction to be executed following

a program interrupt.

10 (octal) --- 17 (octal) Auto-indexing.

#### MEMORY ADDRESSING

1 (octal)

The programmer has 4096 (decimal) locations which he may address. However, as illustrated in Figure 3-2 of Chapter 3, when an instruction is fetched from memory, only bits 5 through 11 contain the address of the data. Addressing is accomplished using octal notation. Therefore the 4096 possible locations require addresses in octal from 0000 to 7777. This means that a total of 12 bits is required to specify an absolute address. So that all locations may be addressed as efficiently as possible, memory is addressed in terms of pages with a coding scheme that allows easy access to any one of the 10,000 octal locations. The page addressing scheme is illustrated in Figure 4-1 which shows the relationship of the 40 octal pages with the 10,000 octal locations. The programmer is interested in only three pages in memory at any one time:

- a. The current page

- b. Page 0

- c. A location on other than the current page or page 0.

Page 0 is used to store commonly used operands and off-page pointers. 'For instance, the location of an indirect address used by instructions is usually on Page 0.

| ABSOLUTE ADD | R. CORE MEMORY PAGE<br>(OCTAL) | PAGE ADDR.<br>(OCTAL) |

|--------------|--------------------------------|-----------------------|

| 7777         | 37                             | 177                   |

| 7600         |                                | 177                   |

| 7400         | 36                             | 000                   |

| 7377         | 35                             | 177                   |

| 7200         |                                | 177                   |

| 7000         | 34                             | 000                   |

| 6777         | 33                             | 177                   |

| 6600<br>6577 |                                | 177                   |

| 6400         | 32                             | 000                   |

| 6377         | 31                             | 177                   |

| 6200         | 31                             | 000                   |

| 6177         | 30                             | 177<br>000            |

| 5777         |                                | 177                   |

| 5600         | 27                             | 000                   |

| 5577         | 26                             | 177                   |

| 5400         |                                | 177                   |

| 5200         | 25                             | 000                   |

| 5177         | 24                             | 177                   |

| 4777         |                                | 000                   |

| 4600         | 23                             | 177                   |

| 4577         | 20                             | 177                   |

| 4400         | 22                             | 000                   |

| 4377         | 21                             | 177                   |

| 4200         |                                | 177                   |

| 4000         | 20                             | 000                   |

| 3777         | 17                             | 177                   |

| 3600         |                                | 000                   |

| 3400         | 16                             | 177                   |

| 3377         | 15                             | 177                   |

| 3200         | 15                             | 000                   |

| 3177<br>3000 | 14                             | 177<br>000            |

| 2777         |                                | 177                   |

| 2600         | 13                             | 000                   |

| 2577         | 12                             | 177                   |

| 2400         |                                | 177                   |

| 2200         | 11                             | 000                   |

| 2177         | 10                             | 177.                  |

| 1777         |                                | 177                   |

| 1600         | 7                              | 000                   |

| 1577         | 6                              | 177                   |

| 1400         |                                | 000                   |

| 1377         | 5                              | 177<br>000            |

| 1177         |                                | 177                   |

| 1000         | 4                              | 000                   |

| 0777         | 3                              | 177                   |

| 0600         |                                | 177                   |

| 0400         | 2                              | 000                   |

| 0377         | 1                              | 177                   |

| 0200         | r .                            | 000                   |

| 0177<br>0000 | 0                              | 177<br>000            |

| - 2000       |                                | 1000                  |

Figure 4-1 Memory Addressing Scheme

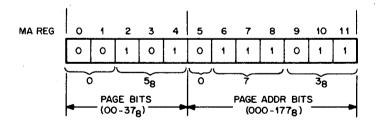

The format of the Central Processor (CPMA) Memory Address Register establishing the memory page must first be considered. The MA register is an unequally divided 12-bit register in which the least significant bits of the MA (bits 5.11) are called the page address bits and the most significant bits (bits 0.4) are called the page bits. The 12 bits of the Memory Address are established by the program counter (PC) and are re-established each time the PC loads an absolute address for the next instruction. Bits 0-4 are used to establish the memory page as shown in Figure 4-2. Because the pages to be addressed include pages 0-37 (octal), only five bits are required. The first two bits represent numbers from 0 to 3 and the next three represent numbers from 0 to 7. Because the locations to be addressed on any given page include locations 0-177 (octal), only seven bits are required to specify any one location. Bit 5 represents an octal 1 or 0; bits 6, 7, and 8 represent the second octal digit from 0 to 7; bits 9, 10, and 11 represent the last octal digit from 0 to 7. Thus, on the example shown in Figure 4-2, the MA register is addressing page 5, location 73 (absolute address 1273).

When the user first receives his PDP-8/E, he should assume that it has no information content in its memory. Before he can load instructions into memory, he must first perform the initializing and loading procedures described in Chapter 2. The following discussion assumes that the preliminary procedures have been completed and that the programmer now wants to load into core those instructions which will be called upon after a program has been written. His main concern is to decide in which memory locations he desires to place his instructions and in which locations he wishes to place the corresponding data.

Figure 4-2 Format Establishing Memory Page

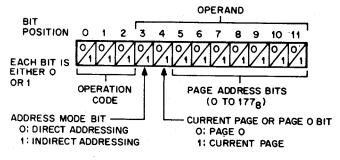

Initially, the programmer must load the Central Processor Memory Address Register with an address and then deposit a 12-bit instruction word in the format shown in Figure 4-3.

Figure 4-3 Format of a Memory Reference Instruction

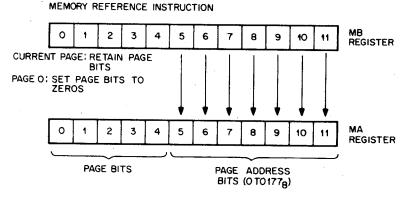

The first three bits contain the instruction operation code and have nothing to do with addressing. The last seven bits address the location (from 0 to 177 octal), which will contain either data or a 12-bit address. Those address bits are located in the Memory Buffer Register, and are ineffective until bits 3 and 4 are decoded, at which time the address bits are transferred from the Memory Buffer to the Central Processor Memory Address Register. The page address (the first five bits of the MA register) is determined by whether bit 4 is a 0 or 1 (see Figure 4-4).

Where to place the instruction word or Data word is a very important consideration. At this point, the programmer has three choices in the location of the data:

- a. the current page (that page containing the Instruction)

- b. page 0

- c. a page other than page 0 or the current page.

Figure 4-4 Transfer of Address Portion of MRI into MA Register

Current Page—If the programmer desires the data to be located in the current page, he must make bit 4 a 1 in the original instruction word. The logic within the processor causes the first five bits of the MA to remain, and transfers the last seven bits of the MB (the new address within a page) to the last seven bits of the MA Register. This method of updating the MA Register is illustrated in Figure 4-4.

Page 0—Page 0 is commonly used to store operands or address of operands or routines. The programmer must set bit 4 word to 0. The logic within the processor then places all zeros in MA bits 0 through 4 and transfers the content of the last 7 bits of the MB register to the last 7 bits of the MA Register. Thus, the page address is now page 0 and the address within page 0 is some address between 0 and 177 octal. This is illustrated in Figure 4-4.

Addressing A Page Other Than the Current Page or Page 0—The programmer may address a page other than the current page or page 0 by placing a 1 in bit 3 of the original instruction word. As before, the computer then goes to an address on the current page or on page 0, depending on the state of bit 4. The logic within the processor responds to bit 3 being a 1 by going into a defer state for a new address. This procedure is called "Indirect Addressing."

## INDIRECT ADDRESSING

In the preceding section, the method of directly addressing 400(octal) memory locations by an MRI was described—namely those on page 0 and those on the current page. This section describes the method for addressing the other 7400(octal) memory locations. Bit 3 of an MRI designates the address mode. When bit 3 is a 0, the operand is a direct address. When bit 3 is a 1, the operand is an indirect address. An indirect address (pointer address) identifies the location that contains the desired address (effective address). To address a location that is not directly addressable, the absolute address of the desired location is stored in one of the 400(octal) directly addressable locations (pointer address); the pointer address is written as the operand of the MRI; and the letter I is written between the mnemonic and the operand. (During assembly, the presence of the I results in bit 3 of the MRI being set to 1.) Upon execution, the MRI will operate on the contents of the location identified by the address contained in the pointer location.

The two examples in Figure 4-5 illustrate the difference between direct addressing and indirect addressing. The first example shows a TAD instruction that uses direct addressing to get data stored on page 0 in location 50; the second is a TAD instruction that uses indirect addressing, with a pointer on page 0 in location 50, to obtain data stored in location 1275. (When references are made to them from various pages, constants and pointer addresses can be stored on page 0 to avoid the necessity of storing them on each applicable page.) The octal value 1050, in the first example, represents direct addressing (bit 3=0); the octal value 1450, in the second example, represents indirect addressing (bit 3=1). Both examples assume that the accumulator has previously been cleared.

| Location | Content  |                                                                                             |

|----------|----------|---------------------------------------------------------------------------------------------|

| 200      | TAD 50   | (TAD 50 = 1050₅)<br>Instruction                                                             |

| 50       | 1275     | Data (Number) To Be Acted Upon By Instruction Address                                       |

| 1275     | 20       | (Content of location 1275 is not used in the execution of the instruction in location 200.) |

| NOTE: AC | = 1275 a | fter executing the instruction in location 200                                              |

| Location | Content  |                                                                                             |

| 200      | TAD I 50 | (TAD I 50 = 1450 <sub>€</sub> )                                                             |

| 50       | 1275     | Designates Indirect Addressing Instruction                                                  |

|          | 12/5     | Pointer Address                                                                             |

| 1275     | 20       | Data (Number) To Be Acted Upon By<br>Instruction<br>Effective Address                       |

NOTE: AC = 20 after executing the instruction in location 200.

Figure 4-5 Comparison of Direct and Indirect Addressing

The following three examples illustrate some additional ways in which indirect addressing can be used. As shown in example 1, indirect addressing makes it possible to transfer program control from off page 0 (or any other page) to any desired memory location. (Similarly, indirect addressing makes it possible for other memory reference instructions to address any of the 4,096(10) memory locations.) Example 2 shows a DCA instruction that uses indirect addressing with a pointer on the current page. The pointer in this case designates a location off the current page (location 227) in which the data is to be stored. (A pointer address is normally stored on the current page when all references to the designated location are from the current page.) Indirect addressing provides the means for returning to a main program from a subroutine, as shown in example 3. Indirect addressing is also effectively used in manipulating tables of data.

#### EXAMPLE 1

| Location | Content   |                                               |

|----------|-----------|-----------------------------------------------|

| 75       | JMP I 100 | $(JMP \ I \ 100 = 5500(octal))$               |

| •        | •         |                                               |

| •        | •         | Designates Indirect Addressing<br>Instruction |

| 100  | 6000     | Pointer Address                 |

|------|----------|---------------------------------|

|      | •        |                                 |

| •    |          |                                 |

| •    | •        |                                 |

| 6000 | DCA 6100 | Next Instruction To Be Executed |

| •    | •        |                                 |

NOTE: Execution of the instruction in location 75 causes program control to be transferred to location 6000, and the next instruction to be executed is the DCA 6100 instruction.

# EXAMPLE 2

| Location | Content   |                                                                      |

|----------|-----------|----------------------------------------------------------------------|

| 450      | DCA 1 577 | (DCA I 577 = 3777(octal)) Designates Indirect Addressing Instruction |

| 577      | 277       | Pointer Address                                                      |

| •        | •         |                                                                      |

| •        | •         |                                                                      |

| 227      | nnnn      | Data (Number) Stored By Instruction (Effective Address)              |

NOTES: 1. Memory Location 577 is location 177 of current page.

Execution of the instruction in location 450 causes the contents of the accumulator to be stored in location 227.

# EXAMPLE 3

| Location   | Content             | *                                                                                                            |

|------------|---------------------|--------------------------------------------------------------------------------------------------------------|

| 207<br>210 | JMS I 70<br>TAD 250 | (JMS I $70 = 4470(\text{octal})$ )<br>(The next instruction to be executed upon return from the subroutine.) |

| 70         | 2000                | (Starting address of the subroutine stored here.)                                                            |

| 2000       | aaaa                | (Return address stored here by JMS instruction.)                                                             |

| 2001       | iii                 | (First instruction of subroutine.)                                                                           |

| 2077       | JMP I 2000          | (Last instruction of subroutine.)                                                                            |

NOTES: 1. Execution of the instruction in location 207 causes the address 210 to be stored in location 2000 and the instruction in location 2001 to be executed next. Execution of the subroutine proceeds until the last instruction (JMP I 2000) causes control to be transferred back to the main program, continuing with the execution of the instruction stored in location 210.

- A JMS instruction that uses indirect addressing is useful when the subroutine is too large to store on the current page.

- 3. Storing the pointer address on page 0 enables instructions on various pages to have access to the subroutine.

## PROGRAMMING OPERATIONS

The programmer can make use of any combination of instructions. The following sections describe the more common programming operations.

## STORING AND LOADING

Data is stored in any core memory location by use of the DCA (Deposit & Clear AC) instruction. This instruction clears the AC to simplify loading of the next data. If the data deposited is required in the AC for the next program operation, the DCA must be followed by a TAD for the same address. All loading of core memory information into the AC is accomplished by means of the TAD instruction.

The DCA instruction stores the contents of the AC in the referenced location, destroying the original contents of the location. The AC is then set to all zeroes. The following example shows the contents of the accumulator, link, and location 225 before and after executing the instruction DCA 225.

#### DCA 225

|                  | AC   | Link | Loc. 225 |

|------------------|------|------|----------|

| Before Execution | 1234 | 1    | 7654     |

| After Execution  | 0000 | 1    | 1234     |

The following facts should be kept in mind when using the DCA instruction:

- a. The state of the link bit is not altered.

- b. The AC is cleared

- The original contents of the addressed location are replaced by the contents of the AC.

#### PROGRAM CONTROL

The Program Counter is used to direct the processor to the next address of the next instruction to be fetched. Therefore, the content of the PC Register is always one more than the content of the Central Processor Memory Address (CPMA) Register. When an instruction has been completed and the processor is ready to go into a new fetch, the content of the Program Counter is transferred into the CPMA Register and the Program Counter with its original address is incremented by +1, thereby pointing to the next sequential address. This procedure is called Program Control because it directs the processor to the next instruction. Because this rigid sequence of instructions is not always desirable for practical programming, the PDP-8/E provides a means of jumping out of this sequence to transfer Program Control from one sequence of instructions to another or to allow the processor to enter a subroutine which is itself a sequence of instructions and re-enter the main program when the subroutine has been completed.

Transfer of program control to any core memory location uses the JMP or JMS instructions. The JMP I and JMS I (indirect address, bit  $3 \equiv 1$ ) are used to transfer program control to any location in core memory which is not in the current page or page 0.

The JMS Y is used to enter a subroutine which starts at location Y +1 in the current page or page 0. The contents of the PC are stored in the specified address Y, and address Y +1 is transferred into the PC. Subroutines or other pages may be entered via an indirect JMS. To exit a subroutine, the last instruction is a JMP 1 Y, which returns program control to the location stored in Y.

The JMP instruction loads the effective address of the instruction into the program counter, thereby changing the program sequence since the PC specifies the next instruction to be performed. In the following example, execution of the instruction in location 250 (JMP 300) causes the program to jump over the instructions in locations 251 through 277 and immediately transfer control to the instruction in location 300.

| Location | Content |                                                               |

|----------|---------|---------------------------------------------------------------|

| 250<br>• | JMP 300 | (This instruction transfers program control to location 300.) |

| 300      | DCA 300 |                                                               |

NOTE: The JMP instruction does not affect the contents of the AC or link.

A program written to perform a specific operation often includes sets of instructions which perform intermediate tasks. These intermediate tasks may be finding a square root, or typing a character on a keyboard. Such operations are often performed many times in the running of one program and may be coded as subroutines. To eliminate the need of writing the complete set of instructions each time the operation must be performed, the JMS (jump to subroutine) instruction is used. The JMS instruction stores a pointer address in the first location of the subroutine and transfers control to the second location of the subroutine. After the subroutine is executed, the pointer address identifies the next instruction to be executed. Thus, the programmer has at his disposal a simple means of exiting from the normal flow of his program to perform an intermediate task and a means of returning to the correct location upon completion of the task. (This return is accomplished using indirect addressing, which is discussed elsewhere in this chapter.)

The following example illustrates the action of the JMS instruction:

| Location       | Content |                                                                                               |

|----------------|---------|-----------------------------------------------------------------------------------------------|

| PROGRAM<br>200 | JMS 350 | (This instruction stores 0201 in location 350 and transfers program control to location 351.) |

| 201        | DCA 270   | (This instruction stores the contents of the AC in location 270 upon return from the subroutine.)   |

|------------|-----------|-----------------------------------------------------------------------------------------------------|

| •          | •         |                                                                                                     |

| •          | •         | •                                                                                                   |

| •          | •         |                                                                                                     |

| SUBROUTINE |           |                                                                                                     |

| 350        | 0000      | (This location is assumed to have an initial value of 0000; after JMS 350 is executed, it is 0201.) |

| 351        | iii       | (First instruction of subroutine)                                                                   |

| •          |           | ( or morrantion of Jubioutile)                                                                      |

| •          | •         |                                                                                                     |

| 375        | JMP I 350 | (Last instruction of subroutine)                                                                    |

The following should be kept in mind when using the JMS:

- 1. The value of the PC (the address of the JMS instruction +1) is always stored in the first location of the subroutine, replacing the original contents.

- 2. Program control is always transferred to the location designated by the operand  $+\ 1$  (second location of the subroutine).

- 3. The normal return from a subroutine is made by using an indirect JMP to the first location of the subroutine (JMP I 350 in the above example); (Indirect addressing, as discussed in this chapter effectively transfers control to location 201).

- 4. When the results of the subroutine processing are contained in the AC and are to be used in the main program, they must be stored upon return from the subroutine before further calculations are performed. (In the above example, the results of the subroutine processing are stored in location 270.)

#### ARITHMETIC OPERATIONS

One arithmetic instruction is included in the order code, the two's complement add (TAD). Using this instruction, routines can easily be written to perform addition, subtraction, multiplication, and division in two's complement arithmetic.

# Two's Complement Arithmetic

In two's complement arithmetic, addition, subtraction, multiplication, and division of binary numbers are performed in accordance with the common rules of binary arithmetic. In the PDP-8/E, as in other machines utilizing complementation techniques, negative numbers are represented as the complements of positive numbers, and subtraction is achieved by complement addition. Representation of negative values in one's complement arithmetic is slightly different from that in two's complement arithmetic.

The one's complement of a number is the complement of the absolute positive value; that is, all 1s are replaced by 0s and all 0s are replaced by 1s. The two's complement of a number is equal to one plus the one's complement of the number.

In one's complement arithmetic a carry from the sign bit (most significant bit) is added to the least significant bit in an end-around carry. In two's complement arithmetic a carry from the sign bit complements the link (a carry would set the link to 1 if it were properly cleared before the operation), and there is no end-around carry.

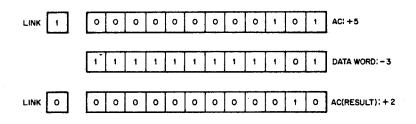

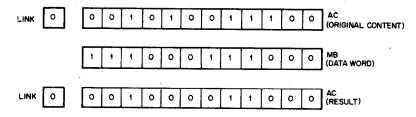

The TAD instruction (see Figure 4-6) performs a binary addition between the specified data word and the contents of the accumulator, leaving the result of the addition in the accumulator. If a carry out of the most significant bit of the accumulator should occur, the state of the link bit is complemented. The add instruction is called a Two's Complement Add to remind the programmer that negative numbers must be expressed as the two's complement of the positive value.

Figure 4-6 Operation of the TAD Instruction

The following points should be remembered when using the TAD instruction:

- a. Negative numbers must be expressed as a two's complement of the positive value of the number.

- b. A carry out of the accumulator will complement the link.

- c. The data word in the referenced location is not affected.

#### LOGIC OPERATIONS

The PDP-8/E instruction list includes the logic instruction AND. A short routine can be written from this instruction to perform the exclusive OR operation.

#### Logical AND

The logical AND operation between the contents of the accumulator and the contents of a core memory location Y is performed directly by means of the AND Y instruction. The logical AND performs an AND operation with ACO and MBO, AC1 and MB1, etc. The result remains in the AC, the original contents of the AC are lost, and the contents of location Y are unaffected.

The AND instruction causes a bit-by-bit Boolean AND operation between the contents of the accumulator and the data word specified by the instruction. The result is left in the accumulator as shown in Figure 4-7.

Figure 4-7 Operation of the AND Instruction

The following points should be noted with respect to the AND instruction:

- a. A 1 appears in the AC only when a 1 is present in both the AC and the data word (The data word is often referred to as a mask).

- b. The state of the link bit is not affected by the AND instruction.

- c. The data word in the referenced location is not altered.

# Inclusive OR

The Inclusive OR instruction makes use of the MQ register, which is a permanent part of the PDP-8/E. Assuming that value A is in the AC and value B is stored in a known core memory address, the following sequence performs the inclusive OR. The sequence is stated as a utility subroutine called IOR.

```

/CALLING SEQUENCE

JMS IOR

(ADDRESS OF B)

/ENTER WITH ARGUMENT IN AC; EXIT WITH

/LOGICAL RESULT IN AC

/ADDRESS LABELINSTRUCTION

REMARKS

IOR.

MOL

/AC TO MO. CLEAR AC

TAD I IOR

/GET ADDRESS OF SECOND

DCA TEM1

ARGUMENT

TAD | TEM1

MQA

/IOR MQ TO AC

ISZ IOR

JMP I IOR

TEM1,

```

#### **Exclusive OR**

The exclusive OR operation for two numbers, A and B, can be performed by a subroutine called by the mnemonic code XOR. In the following general purpose XOR subroutine, the value A is assumed to be in the AC, and the address of the value B is assumed to be stored in a known core memory location.

```

/CALLING SEQUENCE JMS XOR

/ (ADDRESS OF B)

/ (RETURN)

/ENTER WITH ARGUMENT IN AC; EXIT WITH

/LOGICAL RESULT IN AC

```

XOR,

DCA TEM1

TAD I XOR

DCA TEM2

TAD TEM1

AND I TEM2

CMA IAC

CLL RAL

TAD TEM1

TAD I TEM2

ISZ XOR

JMP I XOR

TEM1,

TEM2,

0

An XOR subroutine can be written using fewer core memory locations by making use of the IOR subroutine; however, such a subroutine takes more time to execute. A faster XOR subroutine can be written by storing the value B instead of the address of B, in the second instruction of the calling sequence; however, the resulting subroutine is not as useful as the subroutine given here.

## INDEXING OPERATIONS

External events can be counted by the program, and the count can be stored in core memory. The core memory location used to store the event count can be initialized (cleared) by a CLA command followed by a DCA instruction. Each time the event occurs, the event count can be advanced by a sequence of commands such as CLA, TAD, IAC, and DCA.

The ISZ instruction is used to count repetitive program operations or external events without disturbing the contents of the accumulator. Counting a specified number of operations is performed by storing a two's complement negative number equivalent to the number of operations to be counted. Each time the operation is performed, the ISZ instruction is used to increment the contents of this stored number and to check the result. When the stored number becomes zero, the specified number of operations have occurred and the program skips out of the loop and back to the main sequence.

This instruction is also used for other routines in which the contents of a memory location are incremented without disturbing the contents of the accumulator, such as storing information from an I/O device in sequential memory locations, or using core memory locations to count I/O device events.

The ISZ instruction adds a 1 to the referenced data word and then examines the result of the addition. If a zero result occurs, the instruction following the ISZ is skipped. If the result is not zero, the instruction following the ISZ is performed. In either case, the result of the addition replaces the original data word in memory. The example below illustrates one method of adding the contents of a given location to the AC a specified number of times (multiplying) by using an ISZ instruction to increment a tally. The effect of this example is to multiply the contents of location 275 by 2. (To add the contents of a given location to the AC

twice, using the ISZ loop, as shown below, requires more instructions than merely repeating the TAD instruction or using a rotate instruction. However, when adding the contents four or more times, use of the ISZ loop requires fewer instructions.) In the first pass of the example, execution of ISZ 250 increments the contents of location 250 from 7776 to 7777 and then transfers control to the following instruction (JMP 200). In the second pass, execution of ISZ 250 increments the contents of location 250 from 7777 to 0000 and transfers control to the instruction in location 203, skipping over location 202.

# CODING FOR ISZ LOOP

| Location<br>200<br>201<br>202<br>203 | Content<br>TAD 275<br>ISZ 250<br>JMP 200<br>DCA 276 |

|--------------------------------------|-----------------------------------------------------|

| •                                    | 20/1 2/0                                            |

| •                                    |                                                     |

| 250                                  | 7776                                                |

| •                                    | •                                                   |

| •                                    | •                                                   |

| 275<br>276                           | 0100<br>0000                                        |

## SEQUENCE OF EXECUTION FOR ISZ LOOP

| Location<br>FIRST PASS                  | Cont                     | ent                      | Content A<br>AC                  | after Instru<br>250            | uction Exe<br>275              | ecution<br>276                |

|-----------------------------------------|--------------------------|--------------------------|----------------------------------|--------------------------------|--------------------------------|-------------------------------|

| 200<br>201<br>202                       | TAD<br>ISZ<br>JMP        | 275<br>250<br>200        | 0100<br>0100<br>0100             | 7776<br>7777<br>7777           | 0100<br>0100<br>0100           | 0000<br>0000<br>0000          |

| SECOND PASS<br>200<br>201<br>202<br>203 | TAD<br>ISZ<br>JMP<br>DCA | 275<br>250<br>200<br>276 | 0200<br>0200<br>(Skipped<br>0000 | 7777<br>0000<br>during<br>0000 | 0100<br>0100<br>second<br>0100 | 0000<br>0000<br>pass)<br>0200 |

ISZ Instruction Incrementing a Tally

The following points should be kept in mind when using the ISZ instruction:

- a. The contents of the AC and link are not disturbed.

- b. The original word is replaced in main memory by the incremented value.

- c. When using the ISZ for looping a specified number of times, the tally must be set to the negative of the desired number.

- d. The ISZ performs the incrementation first and then checks for a zero result.

## CODING A PROGRAM

The introduction of an assembler in Chapter 2 enabled the programmer to write a symbolic program using meaningful mnemonic codes rather than the octal representation of the instructions. The programmer could now write mnemonic programs such as the following example, which multiplies 18(10) by 36(10) using successive addition.

| 200 | CLA CLL | Initialize                 |

|-----|---------|----------------------------|

| 201 | TAD 210 | Set up a Tally             |

| 202 | CIA     | equal to $-18(10)$ to      |

| 203 | DCA 212 | count the additions of 36  |

| 204 | TAD 211 | Add 36                     |

| 205 | ISZ 212 | Skip if Tally is 0         |

| 206 | JMP 204 | Add another 36 if not done |

| 207 | HLT     | Stop after 18 times        |

| 210 | 0022    | Equal to 18(10)            |

| 211 | 0044    | Equal to 36(10)            |

| 212 | 0000    | Holds the tally            |

|     |         |                            |

Writing the above program was greatly simplified because mnemonic codes were used for the octal instructions. However, writing down the absolute address of each instruction is clearly an inconvenience. If the programmer later adds or deletes instructions, thus altering the location assignments of his program, he has to rewrite those instructions whose operands refer to the altered assignments. If the programmer wishes to move the program to a different section of memory, he must rewrite the program. Since such changes must be made often, especially in large programs, a better means of assigning locations is needed. The assembler provides this better means.

# **Location Assignment**

As in the previous program example, most programs are written in successive memory locations. If the programmer assigned an absolute location to the first instruction, the assembler could be told to assign the next instructions to the following locations in order. In programming the PDP-8/E the initial location is denoted by a precedent asterisk (\*). The assembler maintains a current location counter by which it assigns successive locations to instructions. The asterisk causes the current location counter to be set to the value following the asterisk. With this improvement incorporated, and with the use of symbolic addresses, the previous example appears as shown in the following example.

| *200   |      |          |                                         |

|--------|------|----------|-----------------------------------------|

| START, | CLA  | CLL      | ·                                       |

| ,      | TAD  | Α        |                                         |

|        | CIA  |          | •                                       |

|        | DCA  | TALLY    |                                         |

|        | TAD  | В        |                                         |

|        | ISZ  | TALLY    | NOTE: In this example, CLA CLL is       |

|        | JMP  | START +4 | stored in location 200 and the suc-     |

|        | HLT  |          | cessive instructions are stored in 201, |

| Α,     | 0022 |          | 202, etc.                               |

| В,     | 0044 |          | 202, 666.                               |

| TALLY, | 0000 |          |                                         |

# WRITING SUBROUTINES

Included in the memory reference instructions, given in Chapter 3, was the instruction JMS (jump to subroutine). This instruction is a modified JMP command which makes possible a later return to the point of departure from the main program. The JMS instruction automatically stores the location of the next instruction after the JMS in the location to which the program is instructed to jump, thereby enabling a return.

The programmer need only terminate the subroutine with an indirect JMP to the first location of the subroutine in order to return to the next instruction following the JMS instruction. The following simple program illustrates the use of a subroutine to double a number contained in the accumulator.

# (Main Program)

START.

CLA CLL TAD N

JMS DOUBLE DCA TWON Get the number in the AC

Jump to subroutine to double N

First instruction after the subroutine

N, TWON. nnnn nnnn

Any number, N

Did overflow occur?

2N will be stored here

#### Subroutine

DOUBLE.

0000

CLL RAL

Rotate left, multiplying by 2

SNL

JMP I DOUBLE

RAR

If overflow occurs, display the num-

ber to be doubled in the AC and

HLT

then stop the computer.

Notice that the first instruction of the subroutine is located in the second location of the subroutine. Any instruction stored in location DOUBLE would be lost when the return address is stored. Also note that the subroutine as it is written must be located on page 0 or current page, because it is directly addressed. (A subroutine is often located on another page and addressed indirectly as the next example demonstrates.)

The following program multiplies a number in the accumulator by a number stored in the location immediately following the JMS instruction.

# Main Program

| *200<br>START,             |            | TAD A DCA .+3 TAD B JMS I 30 0000                             |

|----------------------------|------------|---------------------------------------------------------------|

|                            |            | DCA PRDUCT                                                    |

|                            |            | •                                                             |

| PRDUCT,<br>A,<br>B,<br>*30 |            | 0000<br>0051<br>0027                                          |

|                            |            | MULT                                                          |

|                            | Subroutine |                                                               |

| ~ *6000<br>MULT,           |            | 0000<br>CIA<br>DCA MTALLY<br>TAD I MULT<br>ISZ MTALLY<br>JMP2 |

| MTALLY.                    |            | ISZ MULT<br>JMP I MULT<br>0000                                |

The preceding example illustrates the following important points.

a. The JMS I 30 instruction could be used anywhere in core memory to jump to this subroutine because the pointer word (stored in location 30) is located on page 0, and all pages of memory can reference page 0.

The period was used to denote the current location in the in-

structions DCA .+3 and JMP .-2.

Since the result of the subroutine is left in the AC when jumping back to the main program, the next instruction should store the result for future use.

The first instruction of the subroutine is in location MULT  $+\ 1$ since the next address in the main program is stored in MULT

by the JMS instruction.

e. The first two instructions of the subroutine set the tally with

the negative of the number in the AC.

f. The second number to be multiplied is brought into the subroutine by the TAD I MULT instruction, as it is stored in the location specified by the address that the JMS instruction automatically stores in the first location of the subroutine. This is a common technique for transferring information into a subroutine.

- g. The ISZ MTALLY instruction is used in the subroutine to count the number of additions. The ISZ MULT instruction is used to increment the contents of MULT by one, thereby making the return jump (JMP I MULT) proceed to the next instruction after the location that held the number to be multiplied.

- h. An interesting modification of the previous program is achieved through defining a "new operation" MLTPLY by including in the coding the statement MLTPLY = JMS I 30. The assembler would make a replacement in such a way that any time the programmer writes MLTPLY the computer would perform a jump to the subroutine and return to the program with the product in the AC.

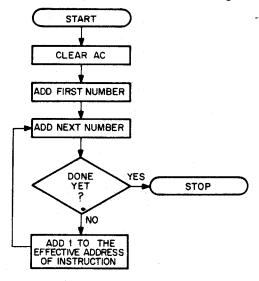

# ADDRESS MODIFICATION

A very powerful tool often used by the programmer is address modification, meaning the inclusion of instructions in a program to modify the operand portion of a memory reference instruction. It is a particularly useful technique when working with large blocks of stored data as illustrated by the two programs that follow (see Figure 4-8).

Figure 4-8 Address Modification

\*200 START,

CLA CLL TAD K200 CIA DCA TALLY TAD K4000 DCA NUM TAD K4200 DCA RESULT

| AGAIN,      | TAD I NUM     |

|-------------|---------------|

|             | JMS- SQUARE   |

|             | DCA I RESULT  |

|             | ISZ RESULT    |

|             | ISZ NUM       |

|             | ISZ TALLY     |

|             | JMP AGAIN     |

|             | HLT           |

| K200.       | 0200          |

| TALLY,      | 0000          |

| K4000.      | 4000          |

| NUM.        | 0000          |

| K4200, 4200 | <b>0000</b> , |

| RESULT.     | 0000          |

| *300        | 3000          |

| SQUARE,     | 0000 -        |

| oquinc,     | DCA STORE     |

|             | TAD STORE     |

|             | CIA           |

|             | DCA COUNT     |

|             | TAD STORE     |

|             | ISZ COUNT     |

|             | JMP .—2       |

|             | JMP I SQUARE  |

| STORE,      | 0000          |

| COUNT.      | 0000          |

| ¢           | 0000          |

It will be noted that the first eight instructions are concerned with initializing the program. This initializing enables the stored program to be restarted several times and still operate on the correct locations. If the program had merely incremented locations K4000 and K4200 and utilized those locations for indirect addressing, it would only operate on the correct locations on the first running. On successive runnings, the program would be operating on successively higher locations in memory. With the program written as shown, however, the pointer words are automatically reset. This procedure is often referred to as "house-keeping."

#### LOOPING A PROGRAM

As many examples have already shown, the use of a program loop, in which a set of instructions is performed repeatedly, is common programming practice. Looping a program is one of the most powerful tools at the programmer's disposal. It enables him to perform similar operations many times using the same instructions, thus saving memory location because he need not store the same instructions many times. Looping also makes a program more flexible because it is relatively easy to change the number of loops required for varying conditions by resetting a counter. It should be remembered that looping is little more than a jump to an earlier part of the program; however, the jump is usually controlled by changing program conditions.

There are two basic methods of creating a program loop. The first me-

thod is using an ISZ (2nnn(octal)) instruction to count the number of passes made through the loop. The ISZ is usually followed by a JMP instruction to the beginning of the loop. This technique is very efficient when the required number of passes through the loop can be readily determined.

The second technique is to use the Group 2 Operate Microinstructions to test conditions other than the number of passes which have been made. Using this second technique, the program is required to loop until a specific condition is present in the accumulator or link bit, rather than until a predetermined number of passes are made.

To illustrate the use of an ISZ instruction in a program loop situation, consider the following program which simply sets the contents of all addresses from 2000 to 2777 to zero.

| *200    |              |                         |

|---------|--------------|-------------------------|

| CLEAR,  | CLA          |                         |

|         | TAD CONST    |                         |

| ,       | DCA COUNT    | /SET COUNT TO -1000.    |

|         | . TAD TTABLE |                         |

|         | DCA STABLE   | /SET STABLE TO 2000.    |

|         | DCA I STABLE | /CLEAR ONE LOCATION.    |

|         | ISZ STABLE   | /SELECT NEXT LOCATION.  |

|         | ISZ COUNT    | /IS OPERATION COMPLETE? |

|         | JMP .—3      | /NO: REPEAT.            |

|         | HLT          | /YES: HALT.             |

| CONST,  | 7000         | /2'S COMP OF 1000.      |

| COUNT,  | 0            |                         |

| TTABLE, | TABLE        |                         |

| STABLE, | 0            | /POINTER TO TABLE.      |

| *2000   |              |                         |

| TABLE,  | 0            |                         |

| \$.     | •            |                         |

Several points should be carefully noted.

- a. The first five instructions initialize the loop, but are not in it. The location COUNT is set to -1000 at the beginning, and 1 is added to it during each passage of the loop. After the 1000th (octal) passage, COUNT goes to zero, and the program skips the JMP instruction, and executes the HLT instruction. On each previous occasion, it executed the JMP instruction.

- b. In the list of constants following the HLT instruction, TTABLE contains TABLE, which is defined below as having the value 2000, and containing 0. Therefore, STABLE contains 2000 initially. In order to understand this point, it must be remembered that an asterisk character causes the first location after the asterisk to be set to the value after the asterisk. Therefore, in the previous example CLEAR equals 200 and TABLE equals 2000.

- c. ISZ STABLE adds 1 to the contents of location STABLE, forming 2001 on the first pass, 2002 on the second pass, and so on. Since it never reaches zero, it will never skip. This is a very

common use. It is said to be indexing the addresses from 2000 to 2777. (When using an ISZ instruction in this way, the programmer must be certain that it does not reach 0. Follow the ISZ instruction with a NOP if it does reach 0 so that the resulting skip will not modify the program sequence.)

d. For every tSZ instruction used in a program, there must be two initializing instructions before the loop, and there must be a constant and a counting location in a table of constants. This procedure allows the program to be rerun with the counting locations reset to the correct values.

The following program utilizes a Group 2 skip instruction to create a loop. The program will search all of core memory to find the first occurrence of the octal number 1234.

\*Λ NUMBER. 1234 \*200 BEGIN. CLA CLL TAD NUMBER CIA DCA COMPARE /STORES MINUS NUMBER. /SETS ENTRY TO 0. DCA ENTRY ISZ ENTRY /INCREASES ENTRY. REPEAT. NOP TAD I ENTRY /COMPARISON IS TAD COMPARE /DONE HERE. SZA CLA JMP REPEAT TAD ENTRY HLT /ENTRY IS IN AC. COMPARE. 0 \_ ENTRY, 0

This example shows that the program searches itself as well as all other core memory locations, and points up the following points:

- a. The ISZ entry instruction is used to index the locations to be tested. The next instruction (NOP) is unnecessary; thus, if ENTRY becomes zero during the course of the program, the program will not be affected. It is important to protect against an ISZ instruction going to zero and skipping a necessary part of a program, if the ISZ is being used simply to index.

- b. The number to be searched for is stored in location 0, and the search starts in location 1. Therefore, the program will find at least one occurrence of the number, and will halt after one complete pass through memory, if not before.

- c. The program could be modified to bound the area of the search. If the contents of ENTRY are set equal to one less than the desired start location and the number being searched for is put in the location following the last location to be searched, the program will search only the designated area of memory.

d. The program could be restarted at location REPEAT in order to find a second occurrence of 1234 after being halted by the first occurrence.

#### **AUTO-INDEXING**

The PDP-8/E computer has eight special registers in page 0; locations 0010 through 0017. Whenever these locations are addressed indirectly by a memory reference instruction, the content of the register is incremented before it is used as the operand of the instruction. These locations can, therefore, be used in place of an ISZ instruction in an indexing application. Because of this, these eight locations are called autoindex registers. Autoindex registers act as any other location when addressed directly. The autoindexing feature is performed only when the location is addressed indirectly.

The following examples below are a modification of the first program example in the preceding section with an autoindex register used in place of the ISZ instruction. (The purpose of the program is to clear memory locations 2000 through 2777.)

Carefully notice the difference between the two examples, especially that TABLE now has to be set to TABLE-1 since this is incremented by the autoindexing register before being used for the first time. This point must be remembered when using an autoindex register. The register increments before the operation takes place; therefore, it must always be set to one less than the first value of the addresses to be indexed.

```

*10

0

INDEX,

*200

CLA

CLEAR.

TAD CONST

DCA COUNT

TAD TTABLE

DCA INDEX

DCA | INDEX

ISZ COUNT

JMP .-2

HLT

CONST.

7000

COUNT.

0

TTABLE.

TABLE 1

*2000

TABLE.

0

```

The memory search example of the preceding section could also be simplified using an autoindex register as shown below.

| *0      |            |                                        |

|---------|------------|----------------------------------------|

| NUMBER. | 1234       |                                        |

| *10     |            |                                        |

| ENTRY,  | 0          | Notice that in this case ENTRY orig-   |

| *200    | •          | inally equals 0 because its content is |

| BEGIN,  | CLA CLL    | incremented before being used to ob-   |

| •       | TAD NUMBER | tain data for the comparison.          |

CIA DCA COMPARE DCA ENTRY REPEAT. TAD I ENTRY TAD COMPARE SZA CLA JMP REPEAT TAD ENTRY HLT COMPARE.

\$

#### PROGRAM DELAYS

Because computer development has been primarily sparked by a desire for speed in performing calculations, it seems inconsistent and selfdefeating to slow the computer down with program delays. However, there are many occasions when a computer must be told to slow down or to wait for further information. This is because most peripheral equipment, and certainly the human operator, is very much slower than the computer program. A temporary delay may be introduced into the execution of a program when needed by causing the computer to enter one or more futile loops, which it must traverse a fixed number of times before jumping out. It is often necessary to have a computer perform a temporary delay while a peripheral device is processing data to be submitted to the computer. The delays can be accurately timed so as not to waste any more computer time than necessary.

The following is a simple delay routine using the ISZ instruction for an inner loop and an outer loop. When analyzing the example it should be remembered that the PDP-8/E represents only positive numbers up to 3777(octal) or 2047(10). Therefore, the computer counts up to 2047 (10) and then continues to count starting at the next octal number 4000(octal), which the computer interprets as -2048(10). Successive increments of this number will finally bring the count to zero. Thus, a location could be used to count from 1 up to 0 by using an ISZ instruction.

(main program)

TAD CONST **ISTART OF DELAY ROUTINE** DCA COUNT ISZ COUNT 1 /INNER JMP .-1 /LOOP

ISZ COUNT

JMP .-3 6030 /SETS DELAY

COUNT. 0 COUNT 1 O

CONST.

#### PROGRAM BRANCHING

Very few meaningful programs are written which do not take advantage

of the computer's ability to determine the future course the program should follow, based upon intermediate results. The procedure of testing a condition and providing alternative paths for the program to travel for each of the different results possible is called branching a program. The Group 2 microinstructions presented previously are most often used for this purpose. The ISZ instruction often referred to as a conditional skip instruction, also provides a branch in a program. This instruction operates upon the contents of a memory location, while the Group 2 microinstructions test the contents of the AC and L.

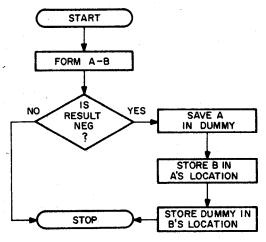

A typical example of a conditional skip would be a program to compare A and B and to reverse their order if B is larger than A (see Figure 4-9).

Figure 4-9 Conditional Skip

| *200   |           |                            |

|--------|-----------|----------------------------|

| TEST,  | CLA CLL   | -                          |

|        | TAD B     | /SUBTRACT B                |

|        | CIA       | /FROM A                    |

|        | TAD A     | /HERE.                     |

|        | SMA CLA   |                            |

|        | HLT       | /STOP HERE IF A IS GREATER |

|        |           | /OR EQUAL                  |

|        | TAD A     | /THE REMAINDER OF          |

|        | DCA DUMMY | /THE PROGRAM               |

|        | TAD B     | /DOES THE SWITCH.          |

|        | DCA A     | -                          |

|        | TAD DUMMY | · ·                        |

|        | DCA B     |                            |

|        | HLT       |                            |

| Α,     | 1234      | SUBSTITUTE ANY POSITIVE    |

| В,     | 2460      | /VALUES FOR A AND B.       |

| DUMMY, | 0         |                            |

| \$     |           |                            |

If A is less than B, their difference will be negative and the HALT will be skipped. The program will proceed to reverse the order of A and B. If A is greater than or equal to B, the program will halt.

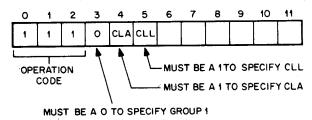

#### MICROPROGRAMMING

Because PDP-8/E instructions of Group 1, Group 2, and Group 3 are determined by bit assignment, these instructions may be combined, or microprogrammed, to form new instructions enabling the computer to do more operations in less time.

# **Combining Microinstructions**

The programmer should make certain that the program clears the accumulator and link before any arithmetic operations are performed. To perform this task, the program might include the following instructions (given in both octal and mnemonic form).

CLA 7200 (octal) CLL 7100 (octal)

However, when the Group 1 instruction format is analyzed, Figure 4-10 illustrates the result.

Figure 4-10 Group 1 Bit Assignments

Since the CLA and the CLL instructions occupy separate bit positions, they may be expressed in the same instruction, thus combining the two operations into one instruction. This instruction would be written as follows.

#### CLA CLL 7300 (octal)

In this manner, many operate microinstructions can be combined, making the execution of the program much more efficient. The assembler for the PDP-8/E will combine the instructions properly when they are written as above; that is, on the same coding line, separated by a space.

# Illegal Combinations

Microprogramming, although very efficient, can also be troublesome for the new programmer. There are many violations of coding which the assembler will not accept.

One rule to remember is: "If you can't code it, the computer can't do it." In other words, the programmer could write a string of mnemonic microinstructions, but unless these microinstructions can be coded

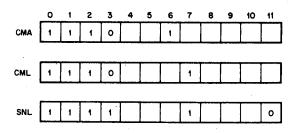

correctly in octal representation, they cannot be performed. To illustrate this fact, suppose the programmer would like to complement the accumulator (CMA), complement the link (CML), and then skip on a non-zero link (SNL). He could write the following.

CMA CML SNL

These instructions require the bit assignments shown in Figure 4-11.

Figure 4-11 Example of Illegal Combinations

The three microinstructions cannot be combined in one instruction because bit 3 is required to be a 0 and a 1 simultaneously. Therefore, no instructions may be used which combine Group 1 and Group 2 microinstructions because bit 3 usage is not compatible. The CMA and CML can, however, be combined because their bit assignments are compatible. The combination would be as follows.

CMA CML 7060 (octal)

To perform the original set of three operations, two instructions are needed.

CMA CML 7060 (octal) SNL 7420 (octal)

Because Group 1 and Group 2 microinstructions cannot be combined, the commonly used microinstruction CLA is a member of both groups. Clearing the AC is often required in a program and it is very convenient to be able to microprogram the CLA with the members of both groups.

RAR RTR 7010 (octal) 7012 (octal) Although he can write the instruction "RAR RTR," it cannot be correctly converted to octal by the assembler because of the conflict in bit 10; therefore, it is illegal.

## **Combining Skip Microinstructions**

Group 2 operate microinstructions use bit 8 to determine the instruction specified by bits 5, 6, and 7 as previously described. If bit 8 is a 0, the instructions SMA, SZA, and SNL are specified. If bit 8 is a 1, the instructions SPA, SNA, and SZL are specified. Thus, SMA cannot be combined with SZL because of the opposite values of bit 8.

## OR GROUP-SMA OR SZA OR SNL

If bit 8 is a 0, the instruction skips on the logical OR of the conditions specified by the separate microinstructions. The next instruction is skipped if any of the stated conditions exist. For example, the combined microinstruction SMA SNL will skip under the following conditions:

- a. The accumulator is negative, the link is zero.

- b. The link is nonzero, the accumulator is not negative.

- c. The accumulator is negative and the link is nonzero.

(It will not skip if all conditions fail.) This manner of combining the test conditions is described as the logical OR of the conditions.

# AND GROUP-SPA AND SNA AND SZL

A value of bit 8=1 specifies the group of microinstructions SPA, SNA, and SZL, which combine to form instructions that act according to the logical AND of the conditions. In other words, the next instruction is skipped only if all conditions are satisfied. For example, the instruction SPA SZL will cause a skip of the next instruction only if the accumulator is positive and the link is zero. (It will not skip if either of the conditions fail.)

- NOTES: 1. The programmer is not able to specify the manner of combination. The SMA, SZA, SNL conditions are always combined by the logical OR, and the SPA, SNA, SZL conditions are always joined by a logical AND.

- Since the SPA microinstruction will skip on either a positive or a zero accumulator, to skip on a strictly positive (positive, nonzero) accumulator the combined microinstruction SPA SNA is used.

## Order of Execution of Combined Microinstructions

The combined microinstructions are performed by the computer in a very definite sequence. When written separately, the order of execution of the instructions is the order in which they are encountered in the program. In writing a combined instruction of Group 1 or Group 2 microinstructions, the order written has no bearing upon the order of execution. This should be clear, because the combined instruction is a 12-bit binary number with certain bits set to a value of 1. The order in which the bits are set to 1 has no bearing on the final execution of the whole binary word.

#### **GROUP 1**

CLA, CLL—Clear the accumulator and/or clear the link are the first actions performed. They are effectively performed simultaneously and yet independently.

CMA, CML—Complement the accumulator and/or complement the link. These operations are also effectively performed simul-

taneously and independently.

IAC—Increment the accumulator. This operation is performed third, allowing a number in the AC to be complemented and then incremented by 1, thereby forming the two's complement, or negative, of the number.

RAR, RAL, RTR, RTL, BSW—The rotate instructions are performed last in sequence. Because of the bit assignment previously discussed, only one of the five operations may be

performed in each combined instruction.

## **GROUP 2**

Either SMA or SZA or SNL when bit 8 is a 0. Both SPA and SNA and SZL when bit 8 is a 1. Combined microinstructions specifying a skip are performed first. The microinstructions are combined to form one specific test; therefore, skip instructions are effectively performed simultaneously.

Because of bit 8, only members of one skip group may be com-

bined in an instruction.

CLA—Clear the accumulator. This instruction is performed second in sequence, allowing different arithmetic operations to be performed after testing (see Event 1) without the necessity of clearing the accumulator with a separate instruction before some subsequent arithmetic operation.

OSR—Inclusive OR between the switch register and the AC. This

instruction is performed third in sequence, allowing the AC to

be cleared first, and then loaded from the switch register.

4. HLT-The HLT is performed last to allow any other operations

to be concluded before the program stops.

This is the order in which all combined instructions are performed. In order to perform operations in a different order, the instructions must be written separately, as shown in the following example. The following combined microinstruction looks as if it might clear the accumulator, perform an inclusive OR between the SR and the AC, and then skip on a nonzero accumulator.

#### CLA OSR SNA

However, the instruction would not perform in that manner, because the SNA would be executed first. In order to perform the skip last, the instructions must be separated, as follows:

## CLA OSR SNA

Microprogramming requires that the programmer carefully code mnemonics legally so that the instruction actually does what he desires it to do. The sequence in which the operations are performed and the legality of combinations are crucial to PDP-8/E programming.

The following is a list of commonly used combined microinstructions, some of which have been assigned a separate mnemonic.

|     | INST | RUCTIO | N EXPLANATION                                                                                  |

|-----|------|--------|------------------------------------------------------------------------------------------------|

|     | CLA  | CLL    | Clear the accumulator and link.                                                                |

| CIA | СМА  | IAC    | Compliment and increment the accumulator. (Sets the accumulator equal to its own negative.)    |

| LAS | CLA  | OSR    | Load accumulator from switches. (Loads the accumulator with the value of the switch register.) |

| STL | CLL  | CML    | Set the link (to a 1).                                                                         |

| -   | CLA  | IAC    | Sets the accumulator to a 1.                                                                   |

| STA | CLA  | CMA    | Sets the accumulator to a $-1$ .                                                               |

|     |      |        |                                                                                                |

In summary, the basic rules for combining operate microinstructions are as follows:

- a. Group 1 and Group 2 microinstructions cannot be combined.

- b. Rotate microinstructions (Group 1) cannot be combined with each other.

- OR Group (SMA, SZA, or SNL) microinstructions cannot be combined with AND Group (SPA, SNA, or SZL) microinstructions.

- d. OR Group microinstructions are combined as the logical OR of their respective skip conditions. AND Group microinstructions are combined as the logical AND of their respective skip conditions.

- e. Order of execution for combined instructions is listed below.

|    | Group 1                 |    | Group 2                   |

|----|-------------------------|----|---------------------------|

| 1. | CLA, CLL                | 1. | SMA/SZA/SNL (OR group) or |

|    |                         |    | SPA/SNA/SZL (AND group)   |

| 2. | CMA, CML                | 2. | CLA                       |

| 3. | IAC                     | 3. | OSR                       |

| 4. | RAR, RAL, RTR, RTL, BSW | 4. | HLT                       |

For the modern business manager, DEC offers complete data processing capability with on-line input/output devices such as a line printer, DEC-writer, card reader, high-speed reader/punch; for mass storage, the DECtape and/or Disk systems are provided with complete file handling programs.

# SECTION 2

# PDP-8/E SYSTEM PROGRAMS

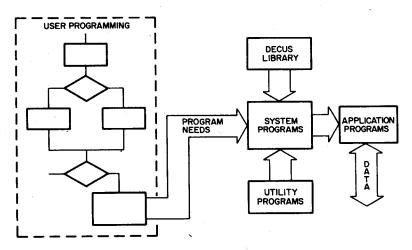

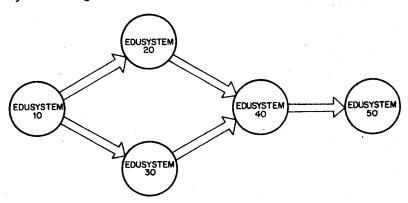

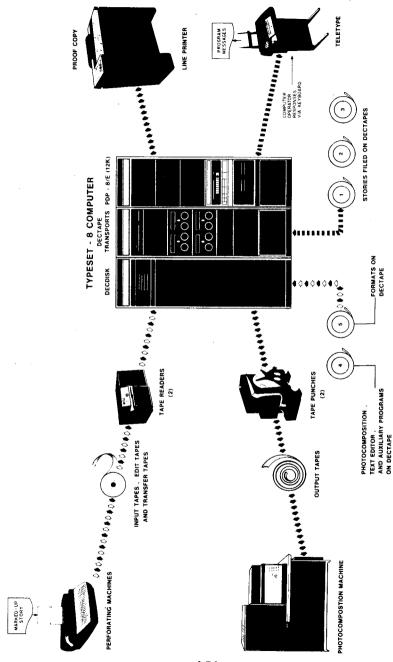

The Programming System for the PDP-8/E consists of SYSTEM PROGRAMS, UTILITY PROGRAMS, and APPLICATION PROGRAMS, and is complemented with the DECUS LIBRARY (see Figure 4-12).

More than 1000 PDP-8 programs are available to the user. Digital Equipment Corporation's Program Library, for instance, offers more than 700 programs from which to choose. In addition, a library containing programs developed by PDP-8 users, called the "DECUS LIBRARY," is available to all PDP-8 users. These programs cover a wide variety of applications in addition to the application programs developed by DEC. The programming system was designed to simplify and accelerate the process of learning to program. At the same time, experienced programmers will find that it incorporates many advanced features. The system is intended to make immediately available to each user the full, general-purpose data processing capability of the computer and to serve as the operating nucleus for a growing library of programs and routines available to all installations.

Figure 4-12 PDP-8/E Programming System

#### PDP-8/E Software Kit

A basic Family-of-8 software kit for the PDP-8/E computer is provided with each basic PDP-8/E system. The user receives one or more paper tapes and the necessary documentation for each program. Those programs provided in the basic software kit are identified by an asterisk (\*) in the following program descriptions.

The following material is included in the basic PDP-8/E software kit:

PDP-8/E Small Computer Handbook Introduction to Programming Handbook, 1970 Programming Languages Manual, 1970 Logic Handbook PDP-8/E Instruction Cards (2 Cards) FOCAL-69 Binary Tape and Utility Overlay Tape PAL-III Symbolic Assembler **DDT Symbolic Debugging Program** ODT Octal Debugging Program (2 Tapes) Symbolic Editor Program RIM Punch (ASR-33 version) Binary Punch (ASR-33 version) Octal Memory Dump Program Floating Point Subroutines (4 Tapes) Software Performance Summary A Complete Set of Maintenance (Diagnostic) Software

#### System Programs

The system programs are used, combined with the utility programs and/ or the DECUS Library Program, to translate the user's ideas into desired application programs. System Programs include: Monitors, Editors, Assemblers, Compilers, Interpretive Languages, Debuggers, and Loaders,

## **Monitor Programs**

Monitor programs used with the PDP-8/E include PS/8, Disk Monitor, and TSE.

PS/8 PROGRAMMING SYSTEM—PS/8, an 8K programming system, represents a significant advance in software development for small computers with capabilities which were formerly available only on such powerful machines as the PDP-10.

The PS/8 is a program development system for the PDP-8/E with minimum 8K of core and one or more of the following mass storage devices:

- a. TC08/TU56 DECtape

- b. RF08 Disk

- c. RK8 Disk Pack

- d. DF32 Disk (64K minimum)

- e. TD8-E DECtape (with 12K Core)

The 8K programming system has the following features:

- a. It allows the user device-independent access to up to 15 I/O devices, including up to eight DECtapes, up to four Disk units, Teletype, high speed paper tape reader and punch, card reader, line printer, and any other device for which it is possible to write a device handler in one, or in some cases two, pages.

- b. The user program may call upon the monitor for several services, including loading device handlers for devices to which the user may assign a name, looking up input files on these devices, creating and closing variable and fixed-length output files on these devices, and getting and decoding a line of input from the console Teletype that identifies input and output files and options.

PS/8 gives the user, in addition to the language processor (8K FOCAL, 8K FORTRAN, PAL-8, and SABR), absolute and relocatable loaders, a symbolic editor, CONVERT (a program to provide file compatibility with the present Disk Monitor System), PIP (Peripheral Interchange Program), and an invisible ODT (Octal Debugging Technique), which allows the programmer to debug programs without giving up valuable core space.

# Advantages offered by the PS/8 System include:

- Dévice Independence—

- 1. Programs can be run using the most effective I/O devices available at a given installation.

- 2. As an installation grows, programs need not be rewritten for increased I/O capability.

- 3. A user device handler may easily be added.

- b. User Interfacing-

- User may use any standard I/O device without having to directly program the device.

- 2. User may use the system command decoder to vary the I/O used in the programs.

- c. Performance—Increased, due to efficient use of storage devices (especially noticeable on DECtape).

- d. Expandability—As the system grows, so does the capability of the PS/8 system.

- e. The PS/8 Library of Programs.

- f. Increased power, derived from the addition of 4K of core to an existing 4K disk monitor system.

- g. A program to convert all 4K monitor files to PS/8 files.

- h. The capability of accommodating any amount of core storage from 8K to 32K.

## **Disk Monitor System**

A keyboard monitor is available to Disk System users that allows them to save core images on the Disk and restore them to memory. The extensive software package available consists of: FORTRAN Compiler, Program Assembly Language (PAL-D), Editor Program (Editor), Peripheral Interchange Program (PIP), and Dynamic Debugging Technique (DDT-D) Program.

In addition, the user may save and restore his own core images and use the remainder of the available device storage for temporary storage of source or binary data. The monitor system may also be used with DECtape.

## **Time-Sharing Monitor**

TSE (Time-Sharing PDP-8/E) is a general purpose, stand-alone monitor time-sharing system. The TSE can accommodate up to 16 users simultaneously. A minimum of 12K of core memory and an RF08-type disk is required for a comprehensive library of system programs, which provide facilities for compiling, assembling, editing, loading, saving, calling, debugging, and running user programs on line.

The center of a TSE system is a complex of programs called Monitor. Monitor coordinates the operations of the various units, allocates the time and services of the computer to users, and controls their access to the system. The computer works on user programs simultaneously by segregating the central processor operations from the time-consuming interactions of the human users. Execution of various programs are interspersed without interfering with one another and without detectable delays in the responses to the individual user.

Consult the DECUS Library for additional monitor programs.

#### **EDITOR PROGRAM**

# Symbolic Paper Tape Editor\*

The Symbolic Paper Tape Editor program is used to edit, correct, and update symbolic program tapes using the PDP-8/E, the Teletype unit, and/or the high-speed reader. With Editor in core memory, the user reads in portions of his symbolic tape, removes, changes, or adds instructions, and gets back a complete new symbolic tape with errors removed. He can work through the program instruction, spot check it, or concentrate on new sections. A character string search is available. The user can move one or more lines of text from one place to another. The program requires 4K core and a Teletype. Consult the DECUS Library for additional editor programs.

#### ASSEMBLER PROGRAMS