| 1.  | IDENTIFICATION            |

|-----|---------------------------|

| 1.1 | Maindec 803               |

| 1.2 | PDP-8 Memory Address Test |

٠

•

i I

\_

1.3 May 11, 1965

\*

а, <sup>р</sup>а

÷  $\sim$ × •  $\hat{\checkmark}$

## 2. ABSTRACT

Maindec 803 provides a rough inspection of the performance of the memory address register and the decoder network which selects a given memory cell. Primarily, Maindec 803 detects errors that arise from open or shorted selection lines.

3. REQUIREMENTS

3.1 Storage

The program occupies memory cells 0001–0033. It is designed for use with the RIM Loader in locations 7756–7776. If it is used with a RIM Loader in 7700, change the contents of memory cell 0032 from 0023 to 0101 before starting the test.

- 3.2 Subprograms and/or Subroutines (Not Applicable)

- 3.3 Equipment Standard PDP-8

- 4. USAGE

- 4.1 Loading

- 4.1.1 Turn off the Teletype reader.

4.1.2 Set the SWITCH REGISTER to 7756; press LOAD ADDRESS, the START.

4.1.3 Place the Maindec 803 RIM program tape in the Teletype reader, and turn on the reader.

4.1.4 When the program has been loaded, stop the computer, turn off the reader, and remove the program tape.

- 4.2 Calling Sequence (Not Applicable)

- 4.3 Switch Settings

- 4.3.1 Starting address = 0001

- 4.3.2 Other settings: none

4.4 Start up and/or Entry

With the program in memory, set the SWITCH REGISTER to 0001, press LOAD ADDRESS, then START.

#### 4.5 Errors in Usage

For any error, the following two stops occur:

| Error | C(MA) | Cause of Error                                                                                       |

|-------|-------|------------------------------------------------------------------------------------------------------|

| El    | 0017  | Contents of the memory cell just inspected were in-<br>correct. The AC displays the actual contents. |

| EIA   | 0022  | The AC displays the address of the cell causing the pre-<br>vious error.                             |

## Maindec 803 Page 2

#### 4.6 Recovery from such Errors

In general, the Memory Address Test detects two types of difficulty in the selection network. If a selection line is open at any point, the memory registers selectable by that line are effectively isolated from the central processor. The program is unable to write information into those cells, or read information out. Conversely, if two lines are shorted together, information entering or leaving the registers selectable by one line also enters or leaves those selectable by the other. Thus, the same information appears in two different registers.

Errors seldom occur singly. Usually, a pattern of errors appears throughout the tested portion of memory which allows the operator to isolate the possible source of trouble. The pattern usually consists of alternating blocks of erroneous and error-free memory cells. The following can be used as a guide to isolate the source of trouble.

4.6.1 If the errors occur in blocks of 100<sub>g</sub> registers or more, the trouble lies in the X-axis selection, and the following modules should be checked:

| Module Type | Module Position | Drawing Number |

|-------------|-----------------|----------------|

| G203        | MC6             | D8012          |

| G203        | MC7             | D8012          |

| G203        | MC8             | D8012          |

| G203        | MC9             | D8012          |

| G203        | MD6             | D8012          |

| G203        | MD7             | D8012          |

| G203        | MD8             | D8012          |

| G203        | MD9             | D8012          |

| G603        | MP1             | D8012          |

| G603        | MP2             | D8012          |

| G603        | MP3             | D8012          |

| G603        | MP4             | D8012          |

4.6.2 If the errors occur in blocks of 77<sub>8</sub> registers or less, the trouble lies in the Y-axis selection, and the following modules should be checked.

| Module Type | Module Position | Drawing Number |  |

|-------------|-----------------|----------------|--|

| G203        | MC12            | D8013          |  |

| G203        | MC13            | D8013          |  |

| G203        | MC14            | D8013          |  |

| G203        | MC15            | D8013          |  |

| G203        | MD12            | D8013          |  |

| G203        | MD13            | D8013          |  |

| G203        | MD14            | D8013          |  |

| G203        | MD15            | D8013          |  |

| G603        | MP5             | D8013          |  |

| G603        | MP6             | D8013          |  |

| G603        | MP7             | D8013          |  |

| G603        | MP8             | D8013          |  |

#### 4.6.3

After an error halt, the test is resumed by following these procedures:

| Error | Recovery                                              |  |

|-------|-------------------------------------------------------|--|

| El    | Record the C(AC). Press CONTINUE to reach the next ha |  |

| EIA   | A Record the C(AC). Press CONTINUE to resume the test |  |

5. RESTRICTIONS (Not Applicable)

6. DESCRIPTION

#### 6.1 Discussion

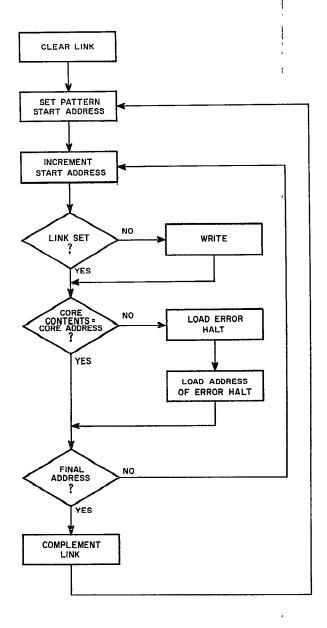

The program deposits in each memory register a quantity equal to the address of that register, and then reads the contents of the same register. If the deposit and read operations were successful, it continues to the next cell in sequence. After all the testable area of memory has been checked in this manner, the program returns to the beginning of that area and attempts to read the contents of each cell. If this is successful, it returns to the first procedure, depositing information and immediately reading it. The test continues to alternate these operations, first making one pass through the tested area performing the write-then-read check, then making a second, read-only pass.

If an error occurs during a write-then-read pass, the writing is suppressed for the remainder of the pass, to insure that errors further along are not obliterated.

#### 6.2 Examples and/or Applications

Maindec 803 is useful as a rough check of the memory selection networks when performing routine maintenance tests. It can also be used to confirm an operator's suspicions if trouble occurs during the normal operation of the computer. Generally, however, troubles arising from failures in the address selection of memory read-write circuits are likely to require the attention of a field service engineer.

7. METHODS (Not Applicable)

8. FORMAT (Not Applicable)

## 9. EXECUTION TIME

The program will run indefinitely, taking approximately 1.3 seconds for each pass until an error is encountered or until the operator stops the computer manually.

10. PROGRAM

- 10.1 Core Map (None)

- 10.2 Dimension List(s) (None)

- 10.3 Macro, Parameter, and Variable Lists (None)

Maindec 803 Page 4

10.4 Program Listing

/MAINDEC 803: PDP-8 MEMORY ADDRESS TEST:

¢

$\sum$

|              |               | *1        | 011 01 A                | /INITIALIZE                     |

|--------------|---------------|-----------|-------------------------|---------------------------------|

| <b>999</b> 1 | 7300          | BGIN,     | CLL CLA<br>TAD C+1      | CLEVER DODGE TO INITIALIZE ADRS |

| 0002         | 1024          |           | DCA ADRS                |                                 |

| 0003         | 3033          | ۵         | ISZ ADRS                | ,                               |

|              | 2033          | Α,        | SZL CLA                 | /WRITING THIS PASS?             |

| <b>9</b> 995 | 7630          |           | JMP B                   | /NO. GO READ                    |

| 0006         | 5011          |           | TAD ADRS                | /YES.                           |

|              | 1033          |           | DCA I ADRS              | 71E5 •                          |

|              | 3433          | <b>D</b>  | TAD I ADRS              | /READ &COMPARE                  |

|              | 1433          | в,        | CIA                     |                                 |

|              | 7041          |           | TAD ADRS                | /C(ADRS)-C(C(ADRS))             |

| <b>9913</b>  | 1033<br>7650  |           | SNA CLA                 | /IS RESULT=0?                   |

|              |               |           | JMP C                   | YES. GO ON                      |

| 0015         | 5023          |           | JHF C                   | 71E5. do on                     |

| aa 1 c       | 1 477         | GION      | TAD I ADRS              | /NO                             |

| <b>99</b> 16 | 1433          |           | HLT                     | /ERROR: AC SHOWS INCORRECT WORD |

| 0017         | 7492          | El,       | CLA STL                 | /ERROR: NO DROWD INCOMPLOI WORD |

| 0020<br>6721 | 7329          |           | TAD ADRS                |                                 |

| 0021         | 1933          | <b>F1</b> |                         | AC SHOWS CORRECT ADDRESS.       |

| 0022         | 7492          | EIA,      | HLT                     | THE SHOWS CONNECT HUDNESD       |

| <b>99</b> 23 | 7269          | C.        | CLA CMA CML             | /IMPLEMENTATION OF              |

| 0024         | 0033          | υ,        | AND ADRS                | THE CLEVER DODGE                |

|              | 1932          |           | TAD CTAB                | /END OF PASS TEST.              |

| <b>0</b> 026 | 7640          |           | SZA CLA                 | /IS IT?                         |

|              | 5004          |           | JMP A                   | /NO. NEXT WORD                  |

|              | 7929          |           | CML                     | YES. NEXT PASS                  |

| 0031         | 5002          |           | JMP BGIN+1              | TED, WEAT THOD                  |

| MBO I        | <b>/#</b> 964 |           |                         |                                 |

| 0032         | 0023          | CTAB,     | <b>G</b> ( <b>G</b> )23 |                                 |

| 0033         | 0000          | ADRS.     |                         |                                 |

|              |               | HDIG 9    | . 0                     |                                 |

| A            | 000           | 4         |                         |                                 |

| ADRS         | 003           | -         |                         |                                 |

| В            | 001           |           |                         |                                 |

| BGIN         | ãão           |           |                         |                                 |

| С            | 002           |           |                         |                                 |

| CTAB         | 003           |           |                         |                                 |

| Ēl           | 001           |           |                         |                                 |

| EIA          | 002           |           |                         |                                 |

| SIGH         | 001           |           |                         |                                 |

|              |               | -         |                         | •                               |

1 ¥ í

# 11. DIAGRAMS

ز جو

11.1 Flow Chart

ş

ł

.