# VAX 6000 Series Vector Processor Owner's Manual

Order Number EK-60VAA-OM-001

This manual is for the system manager or system operator of a VAX 6000 system with a vector processor. The manual expands upon information found in the  $V\!A\!X$  6000–400 Owner's Manual and the MiniReference.

digital equipment corporation maynard, massachusetts

#### First Printing, May 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1990 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEMNA PDP VAXcluster

DEC ULTRIX VAXELN

DEC LANcontroller UNIBUS VMS

DECnet VAX XMI

DECUS VAXBI digital

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# **Contents**

| Preface                                    | vii  |  |

|--------------------------------------------|------|--|

| Chapter 1 VAX Vector Processing System     |      |  |

| 1.1 VAX 6000 System Architecture           | 1-2  |  |

| Chapter 2 Vector Console Commands          |      |  |

| 2.1 Console Commands                       | 2-3  |  |

| 2.2 DEPOSIT Command                        | 2-6  |  |

| 2.2.1 Syntax and Qualifiers                | 2-6  |  |

| 2.2.2 Examples                             | 2-8  |  |

| 2.3 EXAMINE                                |      |  |

| 2.3.1 Syntax and Qualifiers                | 2-10 |  |

| 2.3.2 Examples                             | 2-12 |  |

| 2.4 SET CPU Command                        | 2-14 |  |

| 2.4.1 Syntax and Qualifiers                | 2-14 |  |

| 2.4.2 Examples                             | 2-16 |  |

| 2.5 Sample Console Session                 | 2–18 |  |

| Appendix A Self-Test                       |      |  |

| Appendix B Vector Processor Error Messages |      |  |

| Appe   | endix C Vector Module Registers                                            |      |

|--------|----------------------------------------------------------------------------|------|

| C.1    | Console Commands to Access Registers                                       | C-1  |

| C.2    | <REFERENCE $>$ (XRP) IPRs Related to the Vector Module                     | C-8  |

| C.3    | <reference>(xrv) Internal Processor Registers</reference>                  | C-9  |

| C.4    | $<\!\!REFERENCE\!\!>\!\!(xrv)\ Registers - Vector\ Indirect\ Registers\ .$ | C-12 |

| la da. |                                                                            |      |

| Index  | X .                                                                        |      |

| Exan   | nples                                                                      |      |

| A-1    | Sample Self-Test Results, Scalar Processors Only                           | A-2  |

| A-2    | Sample Self-Test Results with Vector Processors                            | A-4  |

| Figur  | res                                                                        |      |

| 1-1    | VAX 6000 Model 400 Vector Processing System                                | 1-2  |

| A-1    | <reference>(XRP) LEDs After Self-Test</reference>                          | A-5  |

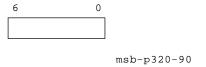

| C-1    | Vector Length (VLR) and Vector Count (VCR) Registers                       | C-2  |

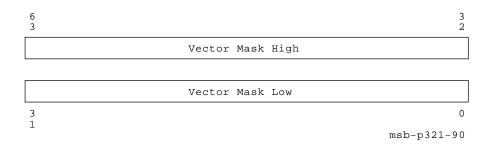

| C-2    | Vector Mask Register (VMR)                                                 | C-2  |

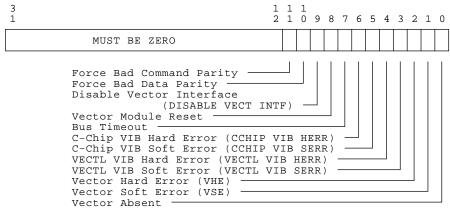

| C-3    | Vector Interface Error Status Register (VINTSR) IPR123 (7B hex)            | C-8  |

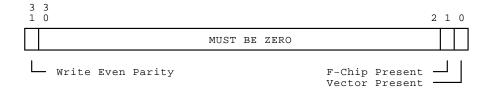

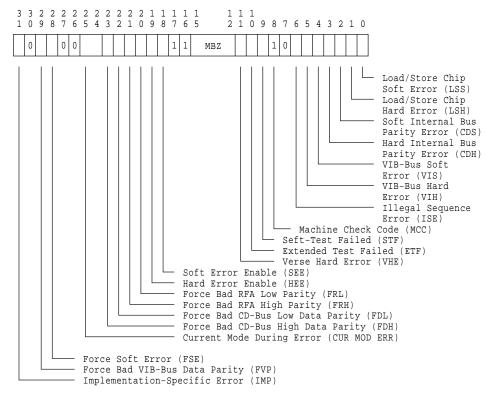

| C-4    | Accelerator Control and Status Register (ACCS) IPR40 (28 hex)              | C-8  |

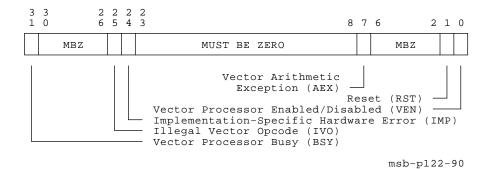

| C-5    | Vector Processor Status Register (VPSR)                                    |      |

| C-6    | IPR144 (90 hex)                                                            | C-9  |

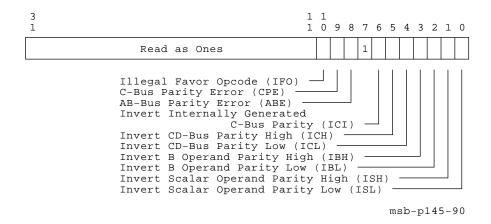

| C-0    | IPR145 (91 hex)                                                            | C-9  |

| C-7    | Vector Memory Activity Check Register (VMAC) IPR146 (92 hex)               | C-10 |

| C-8    | Vector Translation Buffer Invalidate All Register (VTBIA) IPR147 (93 hex)  | C-10 |

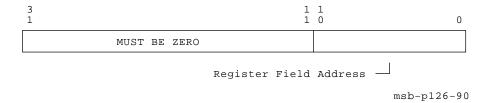

| C-9    | Vector Indirect Address Register (VIADR) IPR157 (9D hex)                   |      |

| C-10   | Vector Indirect Data Low Register (VIDLO) IPR158 (9E hex)                  |      |

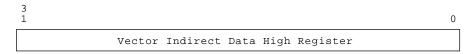

| C-11   | Vector Indirect Data High Register (VIDHI) IPR159 (9F hex)                 |      |

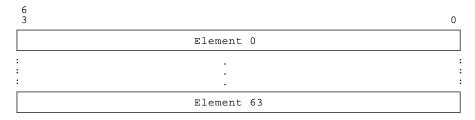

| C-12   | Vector Register n (VREGn)                                                  |      |

|      | 000—3FF, 16 registers                                    | C-12 |

|------|----------------------------------------------------------|------|

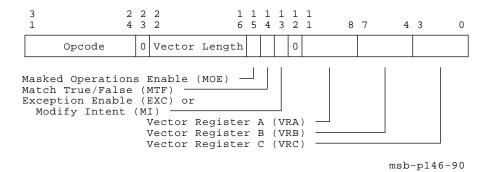

| C-13 | Arithmetic Exception Register (ALU_OP) 440 hex           | C-12 |

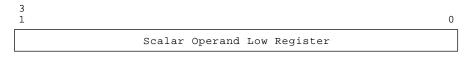

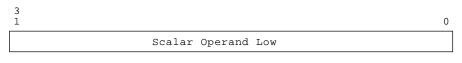

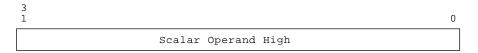

| C-14 | Scalar Operand Low Register (ALU_SCOP_LO) 448 hex        | C-13 |

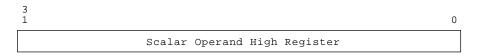

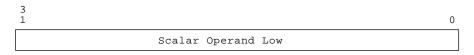

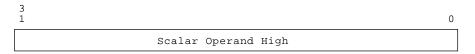

| C-15 | Scalar Operand High Register (ALU_SCOP_HI) 44C hex       | C-13 |

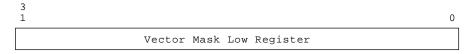

| C-16 | Vector Mask Low Register (ALU_MASK_LO) 450 hex           |      |

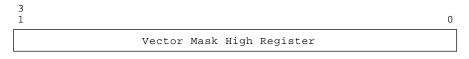

| C-17 | Vector Mask High Register (ALU_MASK_HI) 451 hex          |      |

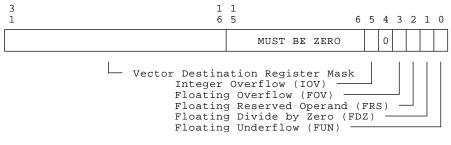

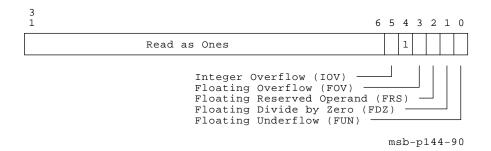

| C-18 | Exception Summary Register (ALU_EXC) 454 hex             |      |

| C-19 | Diagnostic Control Register (ALU_DIAG_CTL) 45C hex       |      |

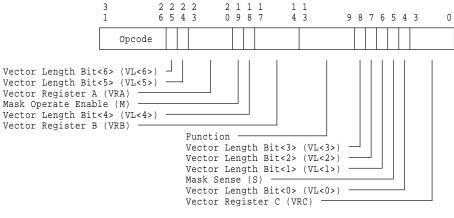

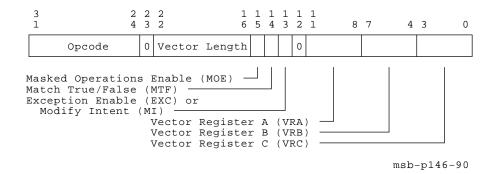

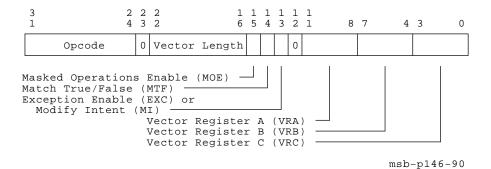

| C-20 | Current ALU Instruction Register (VCTL_CALU) 480 hex     |      |

| C-21 | Deferred ALU Instruction Register (VCTL_DALU) 481 hex    |      |

| C-22 | Current ALU Operand Low Register (VCTL_COP_LO) 482 hex   |      |

| C-23 | Current ALU Operand High Register (VCTL_COP_HI) 483 hex  |      |

| C-24 | Deferred ALU Operand Low Register (VCTL_DOP_LO) 484 hex  |      |

| C-25 | Deferred ALU Operand High Register (VCTL_DOP_HI) 485 hex |      |

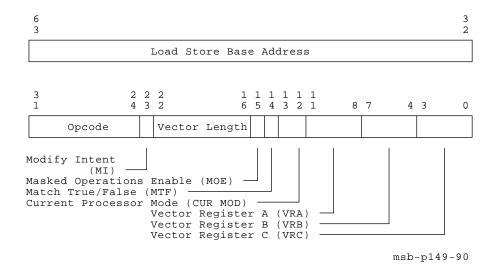

| C-26 | Load/Store Instruction Register (VCTL_LDST) 486 hex      |      |

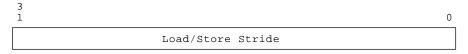

| C-27 | Load/Store Stride Register (VCTL_STRIDE) 487 hex         |      |

| C-28 | Illegal Instruction (VCTL_ILL) 488 hex                   |      |

|      | Vector Controller Status (VCTL_CSR) 489 hex              |      |

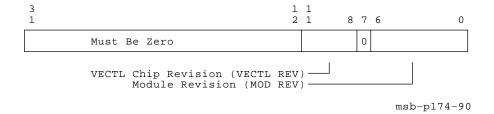

| C-30 | Module Revision (MOD_REV) 48A hex                        |      |

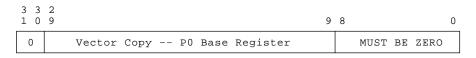

| C-31 | P0 Base Register (LSX_P0BR) 500 hex                      |      |

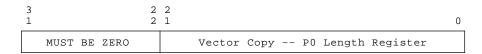

| C-32 | P0 Length Register (LSX P0LR)                            | ~ W1 |

|      | 501 hex                                                         | C-21 |

|------|-----------------------------------------------------------------|------|

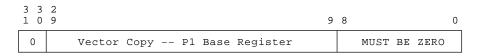

| C-33 | P1 Base Register (LSX_P1BR) 502 hex                             | C-22 |

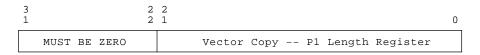

| C-34 | P1 Length Register (LSX_P1LR) 503 hex                           | C-22 |

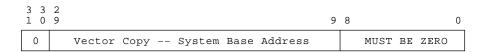

| C-35 | System Base Register (LSX_SBR) 504 hex                          | C-22 |

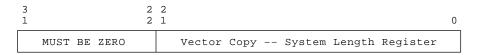

|      | System Length Register (LSX_SLR) 505 hex                        | C-23 |

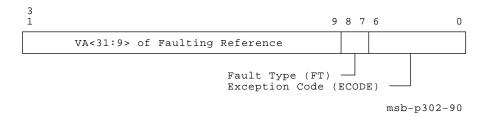

| C-37 | Load/Store Exception Register (LSX_EXC) 508 hex                 | C-23 |

| C-38 | Translation Buffer Control Register (LSX_TBCSR) 509 hex         | C-23 |

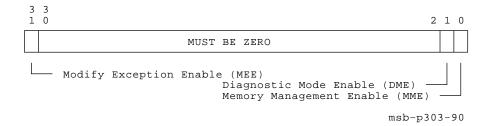

| C-39 | Memory Management Enable (LSX_MAPEN) 50A hex                    | C-24 |

| C-40 | Translation Buffer Invalidate All Register (LSX_TBIA) 50B hex   | C-24 |

| C-41 | Translation Buffer Invalidate Single Register (LSX_TBIS) 5C hex | C-24 |

| C-42 | Vector Mask Low Register (LSX_MASKLO) 510 hex                   | C-25 |

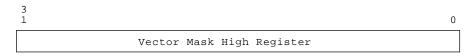

| C-43 | Vector Mask High Register (LSX_MASKHI) 511 hex                  | C-25 |

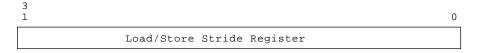

| C-44 | Load/Store Stride Register (LSX_STRIDE) 512 hex                 | C-25 |

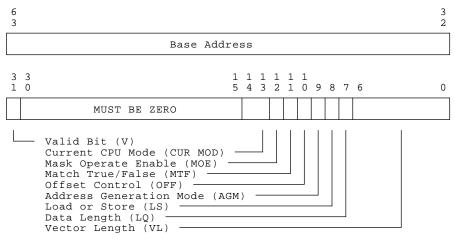

| C-45 | Load/Store Instruction Register (LSX_INST) 513 hex              | C-26 |

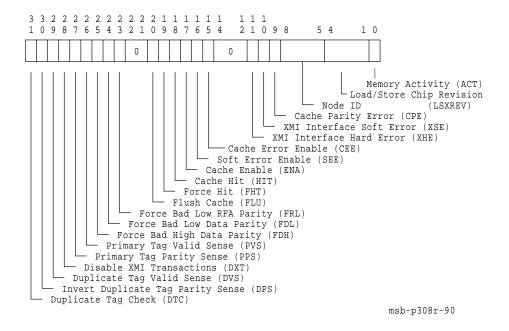

| C-46 | Cache Control Register (LSX_CCSR) 520 hex                       | C-27 |

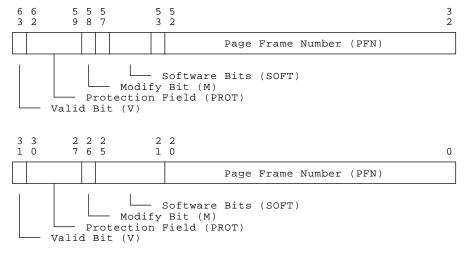

| C-47 | Translation Buffer Tag Register (LSX_TBTAG) 530 hex             | C-27 |

| C-48 | Translation Buffer PTE Register (LSX_PTE) 531 hex               | C-28 |

# Tables

| 1-1 | Processor Module Combinations                             | 1-3  |

|-----|-----------------------------------------------------------|------|

| 2-1 | Console Commands and Qualifiers                           | 2-3  |

| 2-2 | DEPOSIT Command Qualifiers                                | 2-6  |

| 2-3 | EXAMINE Command Qualifiers                                | 2-10 |

| 2-4 | SET CPU Command Qualifiers                                | 2-14 |

| 2-5 | SET CPU Command Qualifiers' Effect After a System Reset . | 2-17 |

| B-1 | Vector Error Messages                                     | B-1  |

| C-1 | Internal Processor Registers                              | C-3  |

| C-2 | FV64A Registers—Vector Indirect Registers                 | C-5  |

#### **Intended Audience**

This manual is for the system manager or system operator of a VAX 6000 system with a vector processor. The day-to-day operations of the system are detailed in the *Owner's Manual* that ships with the system; this manual focuses on information pertaining to systems with vector processors.

### **Document Structure**

The manuals in the VAX 6000 series documentation set are designed using structured documentation theory. Each topic has a boldface indented abstract, to help you use the manual as a reference tool. Other typical components of a topic include an illustration or example, a chart or list, and descriptive text.

This manual has two chapters and three appendixes:

- **Chapter 1, VAX Vector Processing System,** gives an overview of VAX 6000 systems with vector processors.

- Chapter 2, Vector Console Commands, describes the console commands used with vector processors.

- Appendix A, Self-Test, describes how to interpret the console display for self-test and the LEDs on processor modules.

- Appendix B, Vector Processor Error Messages, lists error messages associated with the vector module.

- **Appendix C, Vector Module Registers,** gives the registers associated with the vector module.

# <REFERENCE>(VAX\_XXXX) Documents

Documents in the <REFERENCE>(VAX\_XXXX) documentation set include:

| Title                                                           | Order Number |

|-----------------------------------------------------------------|--------------|

| <reference>(VAX_XXXX) Installation Guide</reference>            | EK-640EA-IN  |

| <reference>(VAX_XXXX) Owner's Manual</reference>                | EK-640EA-OM  |

| <reference>(VAX_XXXX) Mini-Reference</reference>                | EK-640EA-HR  |

| <reference>(VAX_XXXX) System Technical User's Guide</reference> | EK-640EB-TM  |

| <reference>(VAX_XXXX) Options and Maintenance</reference>       | EK-640EB-MG  |

| VAX 6000 Series Upgrade Manual                                  | EK-600EB-UP  |

| VAX 6000 Series Vector Processor Owner's Manual                 | EK-60VAA-OM  |

| VAX 6000 Series Vector Processor Programmer's Guide             | EK-60VAA-PG  |

## **Associated Documents**

Other documents that you may find useful include:

| Title                                                     | Order Number |

|-----------------------------------------------------------|--------------|

| CIBCA User Guide                                          | EK-CIBCA-UG  |

| DEBNI Installation Guide                                  | EK-DEBNI-IN  |

| Guide to Maintaining a VMS System                         | AA-LA34A-TE  |

| Guide to Setting Up a VMS System                          | AA-LA25A-TE  |

| HSC Installation Manual                                   | EK-HSCMN-IN  |

| H4000 DIGITAL Ethernet Transceiver Installation<br>Manual | EK-H4000-IN  |

| H7231 Battery Backup Unit User's Guide                    | EK-H7231-UG  |

| Installing and Using the VT320 Video Terminal             | EK-VT320-UG  |

| Introduction to VMS System Management                     | AA-LA24A-TE  |

| KDB50 Disk Controller User's Guide                        | EK-KDB50-UG  |

| RA90 Disk Drive User Guide                                | EK-ORA90-UG  |

| Title                                              | Order Number |

|----------------------------------------------------|--------------|

| RV20 Optical Disk Owner's Manual                   | EK-ORV20-OM  |

| SC008 Star Coupler User's Guide                    | EK-SC008-UG  |

| TK70 Streaming Tape Drive Owner's Manual           | EK-OTK70-OM  |

| TU81/TA81 and TU81 PLUS Subsystem User's Guide     | EK-TUA81-UG  |

| ULTRIX-32 Guide to System Exercisers               | AA-KS95B-TE  |

| VAX Architecture Reference Manual                  | EY-3459E-DP  |

| VAX Systems Hardware Handbook — VAXBI Systems      | EB-31692-46  |

| VAX Vector Processing Handbook                     | EC-H0419-46  |

| VAXBI Expander Cabinet Installation Guide          | EK-VBIEA-IN  |

| VAXBI Options Handbook                             | EB-32255-46  |

| VMS Installation and Operations: VAX 6000 Series   | AA-LB36B-TE  |

| VMS Networking Manual                              | AA-LA48A-TE  |

| VMS System Manager's Manual                        | AA-LA00A-TE  |

| VMS VAXcluster Manual                              | AA-LA27A-TE  |

| VMS Version 5.4 New and Changed Features<br>Manual | AA-MG29C-TE  |

# Chapter 1

# **VAX Vector Processing System**

This chapter describes the architecture for the VAX 6000 Model 400 systems that support attached vector processors. Earlier models of the 6000 series do not support vector processing.

## 1.1 VAX 6000 System Architecture

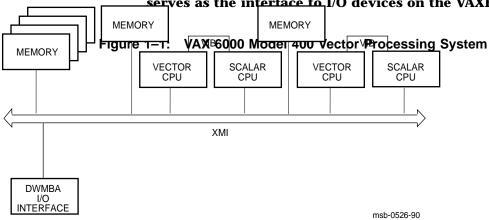

The VAX 6000 computer systems use the high-speed system bus, the XMI, to interconnect processors and memory modules. The VAX 6000 Model 400 series supports multiprocessing with up to six scalar processors or one or two scalar/vector pairs. In Figure 1-1 the DWMBA adapter serves as the interface to I/O devices on the VAXBI bus.

VAX 6000 Model 400 systems support vector processing. The FV64A vector processor is an integrated vector processor; that is, the vector processor module performs as a coprocessor that is tightly coupled with a host scalar processor. To an executing program, the scalar/vector pair of modules appear as one processor.

The two processor modules are physically connected by an intermodule cable, the VIB. The scalar processor is specifically designed to support its vector coprocessor, and the VAX vector instruction set is implemented as part of the host native instruction set. Both the scalar and vector processors are on the XMI bus, and they both access a common memory.

A VAX 6000 Model 400 system can have one or two scalar/vector pairs. If the system has only one pair, it can also have up to three additional scalar processors. Table 1–1 lists the maximum number of scalar and vector processor modules allowed.

Table 1–1: Processor Module Combinations

| Maximum<br>CPUs | Maximum<br>Vectors | Configuration<br>(Slot 1 at Right) |  |

|-----------------|--------------------|------------------------------------|--|

| 6               | 0                  | PPPPP                              |  |

| 4               | 1                  | MVPPPP                             |  |

| 2               | 2                  | MVPMVP                             |  |

For performance reasons, the scalar processor of a scalar/vector pair should not be made the primary processor when other scalar processors are in the system. For optimal performance, two memory modules are required for one scalar/vector pair, and four memory modules are required for two scalar/ vector pairs.

**NOTE:** Installation of an <REFERENCE>(xrv) vector processor requires that the attached <REFERENCE>(xrp) module (T2015) be at a minimum revision of K. In addition, the ROMs on any additional <REFERENCE>(xrp) modules must be at a minimum revision of V2.0 (ROM 0 and ROM 1).

## Chapter 2

# **Vector Console Commands**

This chapter describes the console commands that allow communication with a vector processor module.

## Individual sections include:

- Console commands

- **DEPOSIT** command

- **EXAMINE** command

- **SET CPU command**

- Sample console session

A sample console session (see Section 2.5) shows the system response to the SHOW CPU and SHOW CONFIGURATION console commands.

## 2.1 Console Commands

Using the console program, you can examine and modify the system memory and registers, boot or restart an operating system, designate a primary processor, disable a vector processor, and return to program mode.

Section 2.2 through Section 2.4 give details on the console commands that are used with a vector processor; these are the DEPOSIT, EXAMINE, and SET CPU commands. For details on all console commands in Table 2-1, see your system Owner's Manual.

Table 2-1: Console Commands and Qualifiers

| Command and Qualifiers                        | Function                                                                                                 |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|

| BOOT /R3:n /R5:n /XMI:n /BI:m /NODE:n         | Initializes the system, causing a self-test, and begins the boot program.                                |

| CLEAR EXCEPTION                               | Cleans up error state in XBER and RCSR registers.                                                        |

| CONTINUE                                      | Begins processing at the address where processing was interrupted by a CTRL/P console command.           |

| DEPOSIT  /B /G /I /L /M /  N  /P /Q /V /VE /W | Stores data in a specified address.                                                                      |

| EXAMINE                                       | Displays the contents of a specified address.                                                            |

| FIND<br>/MEMORY<br>/RPB                       | Searches main memory for a page-aligned 256-Kbyte block of good memory or for a restart parameter block. |

| HALT                                          | Null command; no action is taken since the processor has already halted in order to enter console mode.  |

| HELP                                          | Prints explanation of console commands.                                                                  |

Table 2–1 (Cont.): Console Commands and Qualifiers

| Command and Qualifiers                                                             | Function                                                                                                                                  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| INITIALIZE [n] /BI:n                                                               | Performs a system reset, including self-test.                                                                                             |

| REPEAT                                                                             | Executes the command passed as its argument.                                                                                              |

| RESTORE EEPROM                                                                     | Copies the TK tape's EEPROM contents to the EEP-ROM of the processor executing the command.                                               |

| SAVE EEPROM                                                                        | Copies to the TK tape the contents of the EEP-ROM of the processor executing the command.                                                 |

| SET BOOT                                                                           | Stores a boot command by a nickname.                                                                                                      |

| SET CPU [n] /ENABLED /ALL /NOENABLED /NEXT_PRIMARY /PRIMARY /ALL /NOPRIMARY        | Specifies eligibility of processors to become the boot processor.                                                                         |

| /VECTOR_ENABLED<br>/NOVECTOR_ENABLED                                               | Specifies whether the vector processor is to be included in the system configuration.                                                     |

| SET LANGUAGE<br>ENGLISH<br>INTERNATIONAL                                           | Changes the output of the console error messages between numeric code only (international mode) and code plus explanation (English mode). |

| SET MEMORY /CONSOLE_LIMIT:n /INTERLEAVE:(n+n) /INTERLEAVE:DEFAULT /INTERLEAVE:NONE | Designates the method of interleaving the memory modules; supersedes the console program's default interleaving.                          |

| SET TERMINAL /BREAK /NOBREAK /HARDCOPY /NOHARDCOPY /SCOPE /NOSCOPE /SPEED:n        | Sets console terminal characteristics.                                                                                                    |

| SHOW ALL                                                                           | Displays the current value of parameters set.                                                                                             |

| SHOW BOOT                                                                          | Displays all boot commands and nicknames that have been saved using SET BOOT.                                                             |

Table 2–1 (Cont.): Console Commands and Qualifiers

| Command and<br>Qualifiers | Function                                                                                                         |

|---------------------------|------------------------------------------------------------------------------------------------------------------|

| SHOW CONFIGURATION        | Displays the hardware device type and revision level for each XMI and VAXBI node and indicates self-test status. |

| SHOW CPU                  | Identifies the primary processor and the status of other processors. $ \\$                                       |

| SHOW ETHERNET             | Locates all Ethernet adapters on the system and displays their addresses.                                        |

| SHOW LANGUAGE             | Displays the mode currently set for console error messages, international or English.                            |

| SHOW MEMORY               | Displays the memory lines from the system self-test, showing interleave and memory size.                         |

| SHOW TERMINAL             | Displays the baud rate and terminal characteristics functioning on the console terminal.                         |

| START                     | Begins execution of an instruction at the address specified in the command string.                               |

| STOP<br>/BI:n             | Halts the specified node.                                                                                        |

| TEST<br>/RBD              | Passes control to the self-test diagnostics.                                                                     |

| UPDATE                    | Copies contents of the EEPROM on the processor executing the command to the EEPROM of another processor.         |

| Z<br>/BI:n                | Logically connects the console terminal to another processor on the XMI bus or to a VAXBI node.                  |

| !                         | Introduces a comment.                                                                                            |

## 2.2 DEPOSIT Command

The DEPOSIT command stores data in a specified address. Various qualifiers provide access to the vector data registers (/VE), IPRs (/I), and vector indirect registers (/M). No qualifier is needed to deposit to VMR, VCR, and VLR.

## 2.2.1 Syntax and Qualifiers

Table 2-2: DEPOSIT Command Qualifiers

| Qualifier           | Meaning                                                                                                                                                           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /B                  | Defines data size as a byte.                                                                                                                                      |

| /G                  | Defines the address space as the general register set, R0 through R15.                                                                                            |

| /I                  | Defines the address space as the internal processor registers, accessed through MTPR and MFPR instructions.                                                       |

| /L                  | Defines data size as a longword; initial default.                                                                                                                 |

| /M                  | Defines the address space as a vector indirect register; accesses addresses $400$ and higher.                                                                     |

| /N: <count></count> | Defines the address space as the first of a range. $^{1}  \text{}$ is a required value with $\slash\!N.$                                                          |

| /P                  | Defines the address space as physical memory; initial default.                                                                                                    |

| /Q                  | Defines data size as a quadword; initial default for vector registers (except for VCR and VLR).                                                                   |

| /V                  | Defines the address space as virtual memory. All access and protection checking occur. Use when your operating system has been running prior to system halt. $^2$ |

| /VE                 | Defines the address space as the vector register set.                                                                                                             |

| /W                  | Defines data size as a word.                                                                                                                                      |

$<sup>^1</sup>$ The console deposits to the first address, then to the specified number of succeeding addresses. Even if the address is '-', the succeeding addresses are at higher addresses (that is, the symbol specifies only the starting address, not the direction).

$<sup>^2</sup>$ If memory management has not been enabled, virtual addresses are equal to physical addresses. If access is not allowed to a program running with the current processor status longword (PSL), the console issues an error message. Virtual space deposits cause the PTE<M> bit to be set in the mapping PTE and force the processor write buffer to be flushed.

#### The DEPOSIT command syntax is:

```

D[EPOSIT] [/qualifier] <address> <data>

```

where /qualifier is a value from Table 2-2, and the variable <data> is a hexadecimal value to be stored. The value must fit in the data size to be deposited. The variable <address> is a 1- to 8-digit hexadecimal value or one of the following:

- PSL, the processor status longword. You cannot use any address space qualifier with PSL.

- PC, the program counter. The address space is set to /G.

- SP, the stack pointer. The address space is set to /G.

- Rn, the general purpose register *n*. The register number is in decimal. The address space is set to /G.

- VCR, 7-bit Vector Count Register. No address qualifier is permitted.

- VLR, 7-bit Vector Length Register. No address qualifier is permitted.

- VMR, 64-bit Vector Mask Register. No address qualifier is permitted.

- V0-V15, vector registers. Elements of a vector register are specified Vn:mm, where n is a decimal number 0–15 specifying the vector register, and mm is a hex number 0–3F specifying the element within the vector register. The address qualifier must be set to /VE.

- +, the location immediately following the last location you referenced in an EXAMINE or DEPOSIT command. For physical and virtual memory, the referenced location is the last location plus the size of the reference (1 for byte, 2 for word, 4 for longword). For other address spaces, the address is the last referenced address plus one.

- -, the location immediately preceding the last location you referenced in an EXAMINE or DEPOSIT command. For physical and virtual memory, the referenced location is the last location minus the size of the reference (1 for byte, 2 for word, 4 for longword). For other address spaces, the address is the last referenced address minus one.

- \*, the last location you referenced in an EXAMINE or DEPOSIT command.

- @, the location addressed by the last location you referenced in an EXAMINE or DEPOSIT command.

If no qualifiers are given with subsequent commands, the system uses the qualifiers from the preceding command as the defaults. With the / M qualifier, the address is a 3-digit hex number (400 or above).

## 2.2.2 Examples

## **Examples**

```

>>> DEPOSIT/VE V12 0 ! Deposits zero into all 64 elements ! of vector register V12.

>>> DEPOSIT V6:2C/n:2 0 ! Deposits zero into V6 beginning at ! element 2C (hex) and also in the next ! two elements.

>>> DEPOSIT VLR 1 ! Deposits one in the Vector Length ! Register.

>>> DEPOSIT/Q/P 200 FFFFFFFF45370201 ! Deposits FFFFFFF45370201, a quadword ! of data into physical memory at address ! 200.

>>> DEPOSIT/M 440 0 ! Deposits zeros to vector indirect ! register with address 440 (hex).

```

The DEPOSIT command directs data into the specified address. If you do not specify any address space or data size qualifiers, the defaults are the last address space or data size specified in a DEPOSIT or EXAMINE command. After processor initialization, the default address space is physical memory, the default data size is longword, and the default address is zero.

If the specified value is too large to fit in the data size, the console program ignores the command and issues an error message. If the specified value is smaller than the data size to be deposited, the console program fills the high order data positions with zeros. If you specify conflicting data sizes or address spaces, the console program ignores the command and issues an error message.

## 2.3 EXAMINE

The EXAMINE command displays the contents of a specified address. Various qualifiers provide access to the vector data registers (/VE), IPRs (/I), and vector indirect registers (/M). No qualifier is needed to examine VMR, VCR, and VLR.

## 2.3.1 Syntax and Qualifiers

Table 2-3: EXAMINE Command Qualifiers

| Qualifier           | Meaning                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| /B                  | Defines data size as a byte.                                                                                                |

| /G                  | Defines the address space as the general register set, R0 through R15.                                                      |

| /I                  | Defines the address space as the internal processor registers, accessed through MTPR and MFPR instructions.                 |

| /L                  | Defines data size as a longword; initial default.                                                                           |

| /M                  | Defines the address space as a vector indirect register; accesses addresses 400 and higher.                                 |

| /N: <count></count> | Defines the address space as the first of a range. $^{1}\  \  $<br>$\  \  $<br>$\  \  $ count> is a required value with /N. |

| /P                  | Defines the address space as physical memory; initial default.                                                              |

| /Q                  | Defines data size as a quadword; initial default for vector registers (except for VCR and VLR).                             |

| /V                  | Defines the address space as virtual memory. All access and protection checking occur. $^{\!2}$                             |

| /VE                 | Defines the address space as the vector register set.                                                                       |

| /W                  | Defines data size as a word.                                                                                                |

$<sup>\</sup>overline{\ }^1$ The console examines the first address, then the specified number of succeeding addresses. Even if the address is '-', the succeeding addresses are at higher addresses; that is, the symbol specifies only the starting address, not the direction.

$<sup>^2</sup>$ If memory management has not been enabled, virtual addresses are equal to physical addresses. If access is not allowed to a program running with the current processor status longword (PSL), the console issues an error message. Virtual space deposits cause the PTE<M> bit to be set in the mapping PTE and force the processor write buffer to be flushed.

#### The EXAMINE command syntax is:

```

E[XAMINE] [/qualifier] [<address>]

```

where /qualifier is a value from Table 2–3, and <address> is a 1- to 8-digit hexadecimal value or one of the following:

- PSL, the processor status longword. You cannot use any address space qualifier with PSL.

- PC, the program counter. The address space is set to /G.

- SP, the stack pointer. The address space is set to /G.

- Rn, the general purpose register n. The register number is in decimal.

The address space is set to /G.

- VCR, 7-bit Vector Count Register. No address qualifier is permitted.

- VLR, 7-bit Vector Length Register. No address qualifier is permitted.

- VMR, 64-bit Vector Mask Register. No address qualifier is permitted.

- V0–V15, vector registers. Elements of a vector register are specified V*n:mm*, where *n* is a decimal number 0–15 specifying the vector register, and *mm* is a hex number 0–3F specifying the element within the vector register. The address qualifier must be set to /VE.

- +, the location immediately following the last location you referenced in an EXAMINE or DEPOSIT command. For physical and virtual memory, the referenced location is the last location plus the size of the reference (1 for byte, 2 for word, 4 for longword). For other address spaces, the address is the last referenced address plus one.

- -, the location immediately preceding the last location you referenced in an EXAMINE or DEPOSIT command. For physical and virtual memory, the referenced location is the last location minus the size of the reference (1 for byte, 2 for word, 4 for longword). For other address spaces, the address is the last referenced address minus one.

- \*, the last location you referenced in an EXAMINE or DEPOSIT command.

- @, the location addressed by the last location you referenced in an EXAMINE or DEPOSIT command.

If no qualifiers are given with subsequent commands, the system uses the qualifiers from the preceding command as the defaults. With the / M qualifier, the address is a 3-digit hex number (400 or above).

## 2.3.2 Examples

#### **Examples**

```

1. >>> EXAMINE VLR

! Examines the Vector Length

! Register.

M 00000001 0E

! Examines vector register V0; system

! displays all 64 elements of register V0.

2. >>> EXAMINE/VE VO

VE V00:00 00000000 00000002

VE V00:01 00000000 00000002

VE V00:02 00000000 00000002

VE V00:03 00000000 00000002

VE

V00:04

00000000

00000002

VE

V00:05

00000000

00000002

VE

V00:06

00000000

00000002

VE

V00:07

00000000

00000002

VE

V00:08

00000000

00000002

VE

V00:09

00000000

00000002

VE

V00:00

00000000

00000002

VE

V00:00

00000000

00000002

VE

V00:02

00000000

00000002

VE

V00:01

00000000

00000002

VE

V00:12

00000000

00000002

VE

V00:11

00000000

00000002

VE

V00:12

00000000

00000002

VE

V00:13

00000000

00000002

VE

V00:16

00000000

00000002

VE

V00:17

00000000

00000002

VE

V00:18

00000000

00000002

VE

V00:19

00000000

00000002

VE

V00:12

00000000

00000002

VE

V00:18<

VE V00:04 00000000 00000002

VE V00:05 00000000 00000002

VE V00:06 00000000 00000002

VE V00:07 00000000 00000002

! Examines the quadword in ! physical memory at address 200.

3. >>> EXAMINE/Q/P 200

```

```

4. >>> EXAMINE/VE V12:2E ! Examines element 2E (hex)

! (which is 41 decimal) of vector

! data register V12.

5. >>> EXAMINE/M 440 \,! Examines the vector indirect

! register at hex address 440.

M 440 FFFFFFFF 00000000 ! /M is used to access vector

! indirect registers.

```

The system response to the EXAMINE command is in hexadecimal notation:

```

<address space identifier> <address> <data>

```

where <address space identifier> can be one of these values:

- P Physical memory. When virtual memory is examined, the <address space identifier> is P and <address> is the translated physical address.

- G General register.

- I Internal processor register.

- M Vector indirect register. This identifier is also returned when the PSL is examined.

- VE Vector data register.

## 2.4 SET CPU Command

The SET CPU command allows you to specify a particular processor as the primary processor or designate its eligibility to become the primary processor. You can also disable a vector processor module.

## 2.4.1 Syntax and Qualifiers

Table 2-4: SET CPU Command Qualifiers

| Qualifier           | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| /E[NABLED]<br>/ALL  | Processor is included in the system configuration and is eligible to become the boot processor. With the /ALL qualifier all processors are eligible to become the boot processor; initial default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| /NOE[NABLED]        | Processor is immediately excluded from the system configuration; START, BOOT, and CONTINUE commands are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| /NEX[T_PRIMARY]     | Processor will be the primary (boot) processor at the next system reset. $% \left( \frac{1}{2}\right) =\left( \frac{1}{2}\right) \left( $ |  |  |  |  |  |  |  |

| /P[RIMARY]<br>/ALL  | Processor will be eligible to be selected as the primary (boot) processor at the next system reset. With the /ALL qualifier all processors are eligible to become the boot processor; initial default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| /NOP[RIMARY]        | Processor will not be eligible to be selected as the primary (boot) processor at the next system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| /V[ECTOR_ENABLED]   | Vector processor attached to the specified scalar processor is included in the system configuration and can be sent vector instructions; initial default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| /NOV[ECTOR_ENABLED] | Vector processor attached to the specified scalar processor is excluded from the system configuration. $ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| None                | Processor immediately becomes the new primary processor; the next system prompt comes from the new primary processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

#### The SET CPU command syntax is:

```

SE[T] C[PU] [/qualifier] [<XMI-node>]

```

where <XMI-node> is the <REFERENCE>(XMI) node number of the processor to be affected. If you omit <XMI-node>, the system uses the current processor.

If you omit all qualifiers, the SET CPU command immediately causes the specified processor to become the primary processor. The console terminal is then connected to the new primary processor, and the next console prompt is generated by the designated processor.

If you use qualifiers, the SET CPU command changes the processor parameters that take effect at the next system reset. These qualifiers modify the EEPROM (if the lower key switch is set to Update) and take effect immediately:

- /ENABLE

- /NOENABLED

- /VECTOR\_ENABLED

- /NOVECTOR\_ENABLED

The /NEXT\_PRIMARY qualifier acts the same as if you had issued a SET CPU/NOPRIMARY command for all other nodes. To undo /NEXT\_ PRIMARY, you can issue the SET CPU/PRIMARY/ALL command.

The /NOVECTOR\_ENABLED qualifier removes the vector processor from the system configuration. The scalar processor is not affected. The /VECTOR\_ENABLED qualifier restores the vector processor to the configuration.

The effect of the SET CPU command qualifiers is shown on the BPD lines of the system self-test display (see Section 2.5).

NOTE: For performance reasons, the scalar processor of a scalar/vector pair should not be made the primary processor when other scalar processors are in the system.

## 2.4.2 Examples

## **Examples**

```

>>> SET CPU/NOVECTOR_ENABLED 4 ! The vector processor attached ! to the scalar processor at node 4 ! is disabled.

>>> SET CPU/VECTOR_ENABLED 4 ! The vector processor attached ! to the scalar processor at node 4 ! is included in the system configure ! ation.

```

Table 2-5: SET CPU Command Qualifiers' Effect After a System Reset

| Qualifier           | BPD Value at Next Reset <sup>1</sup>                                                                        |  |  |  |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| /NEX[T_PRIMARY]     | B for boot processor; must be chosen the boot processor at the next system reset. All other CPUs show as D. |  |  |  |  |  |  |  |

| /NOE[NABLED]        | D for disable; processor is not included in the configuration.                                              |  |  |  |  |  |  |  |