# pelpt bus henelbook

digital

The material in this document is for informational purposes only and is subject to change without notice. Digital Equipment Corporation assumes no liability or responsibility for any errors which appear in this document or for any use made as a result thereof. By publication of this document, no licenses or other rights are granted by Digital Equipment Corporation by implication, estoppel or otherwise, under any patent, trademark or copyright.

Copyright © 1979, Digital Equipment Corporation

The following are trademarks of Digital Equipment Corporation:

DIGITAL PDP UNIBUS

DEC DECUS MASSBUS

DECtape DDT FLIP CHIP

DECdataway

## **CONTENTS**

#### PART 1, UNIBUS SPECIFICATION 1 INTRODUCTION ..... Scope ........... Content ..... 1 1 UNIBUS DESCRIPTION ..... 2 Architecture ......................... 2 Unibus Transmission Medium ..... 2 Bus Terminator ..... 3 Bus Segment ..... 3 Bus Repeater ..... 3 Bus Master ..... Bus Slave ......... 3 Bus Arbitrator ..... Bus Request ..... Bus Grant ...... Processor ...... Interrupt Fielding Processor ..... UNIBUS SYSTEMS ..... 4 Priority Structure ..... Address Space ....... 7 Latency ...... Arrangement of Devices on the Unibus ...... 8 Expanding the Unibus System ..... 9 PROTOCOL ..... Types of Transactions ...... 9 Priority Arbitration Transactions ..... 9 Data Transfers ....... 11 12 UNIBUS SIGNAL DETAILS ..... 12 Unibus Sections and Signal Lines ...... 13 Signal Transmission ...... 14 Bus Transmission Delay ..... 14 Skew .............. 15 Deskew ...... 15

Types of Unibus Signal Lines ......

Priority Arbitration Section .....

Non-Processor Request (NPR) .....

Non-Processor Grant (NPG) .....

Bus Request (BR4, BR5, BR6, BR7) .....

16

18

19

19

20

20

| Selection Acknowledged (SACK)                    | 21       |

|--------------------------------------------------|----------|

| Bus Busy (BBSY)                                  | 21       |

| Data Transfer Section                            | 21       |

| Data Lines, D<15:00>                             | 21<br>21 |

| Address Lines, A<17:00>                          | 21       |

| Control Lines, C0, C1                            | 24<br>24 |

| Master Sync (MSYN)                               | 24<br>24 |

| Slave Sync (SSYN)                                | 24<br>25 |

| Interrupt Request (INTR)                         | 25<br>25 |

| Initialization Section                           | 25       |

| Initialize (INIT)                                | 25       |

| AC Low (AC LO)                                   | 26       |

| DC LOW (DC LO)                                   | 20       |

| UNIBUS PROTOCOLS                                 | 26       |

| Definitions and Concepts                         | 26       |

| Arbitration                                      | 26       |

| Centralized Arbitration                          | 26       |

| Priority Arbitration                             | 26       |

| Data Transfer (Bus Cycle)                        | 26       |

| Transaction                                      | 27       |

| Protocol                                         | 27       |

| Unibus Operation Concepts                        | 28       |

| Priority Protocol                                | 28       |

| Bus Device Priority Levels                       | 28       |

| Interrupt Fielding Processor CPU Priority Levels | 29       |

| Grant                                            | 29       |

| Assertion                                        | 30       |

| Negation                                         | 31       |

| Priority Arbitration Example                     | 32       |

| Priority Arbitration Transactions                | 33       |

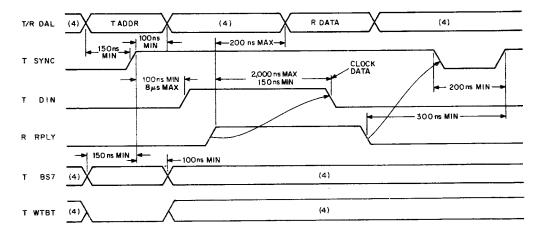

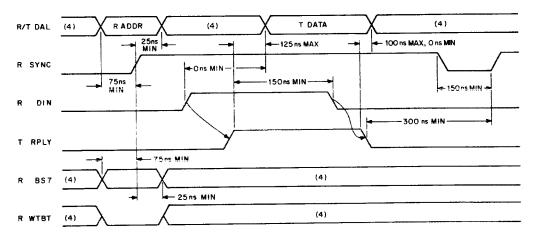

| Notes on the Timing Diagrams                     | 34       |

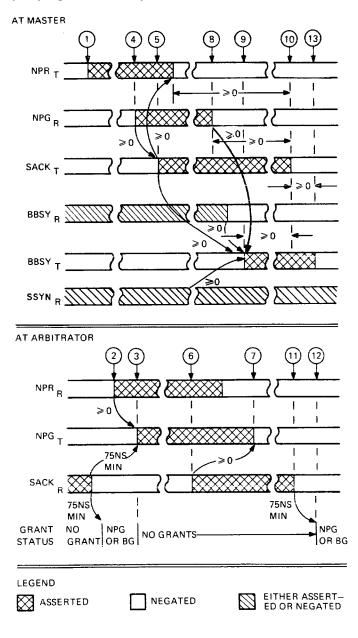

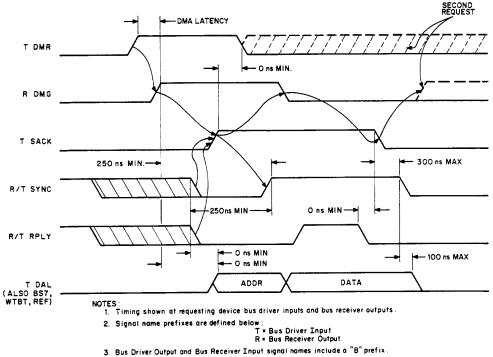

| NPR Arbitration Sequence                         | 36       |

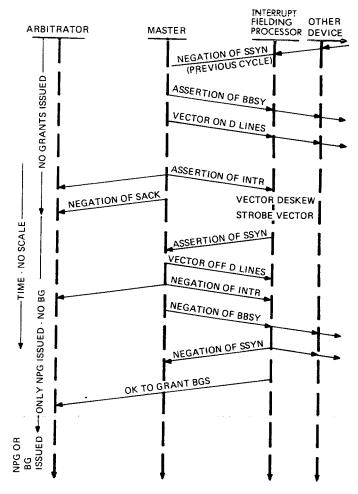

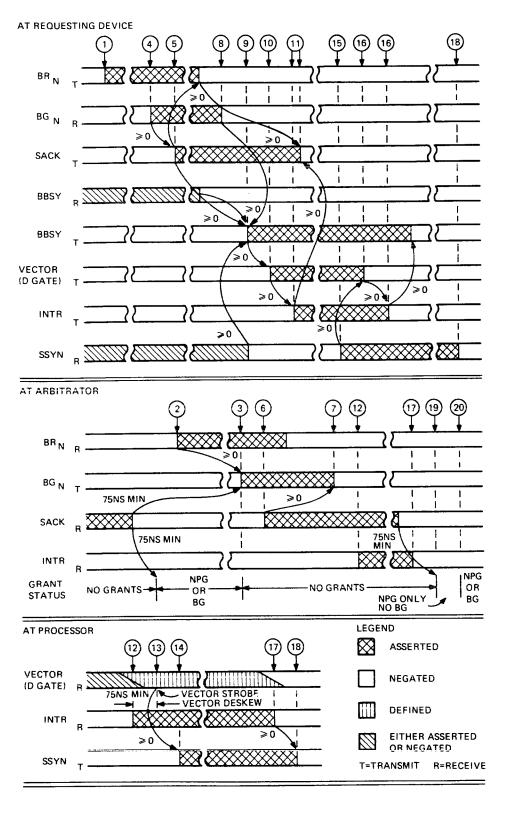

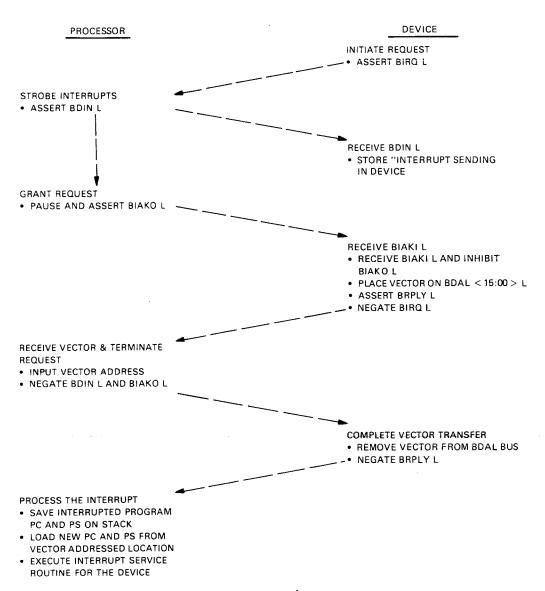

| BR Interrupt Arbitration Sequence                | 39       |

| Data Transfer Protocol                           | 43       |

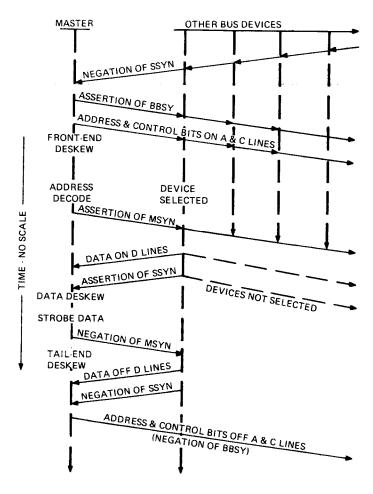

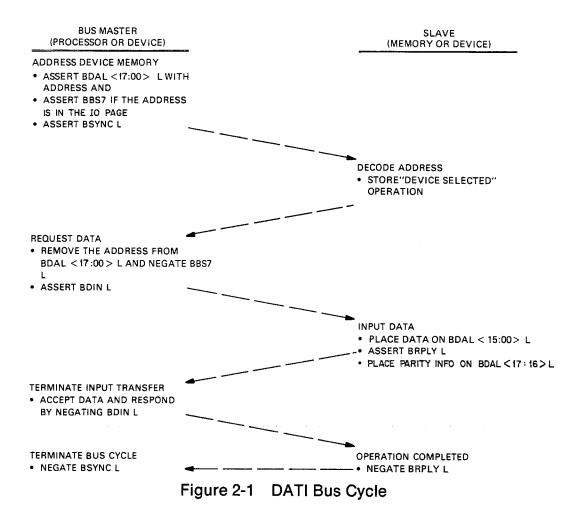

| Data-In Transaction (DATI or DATIP)              | 43       |

| Detailed Description, DATI and DATIP             | 44       |

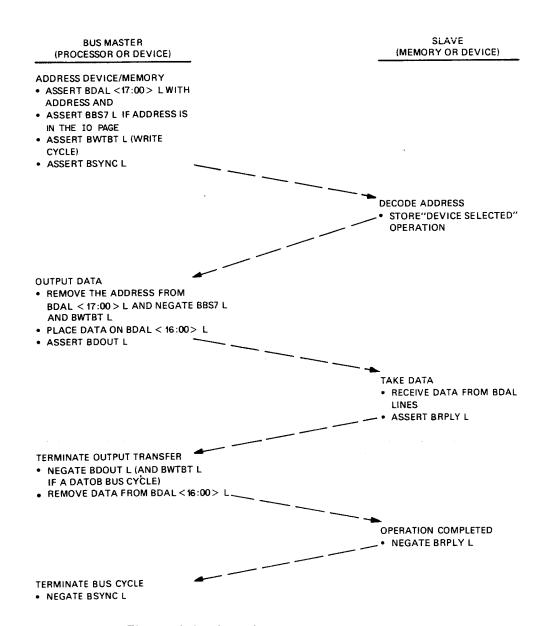

| Data-Out Transaction (DATO or DATOB)             | 47       |

| Detailed Description, DATO and DATOB             | 48       |

| Read/Modify/Write Transaction (DATIP-DATO/B)     | 51<br>50 |

| Multiple Word Transfers                          | 52       |

| INITIALIZATION SECTION                           | 52       |

| Initialization (INIT)                            | 52       |

| Processor Requirements                           | 52       |

| Arhitrator Poenoneo                              | 50       |

| Master/Slave Response                                                                                                                                                                                                                                                                                                                                                                                                        | 53<br>53                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

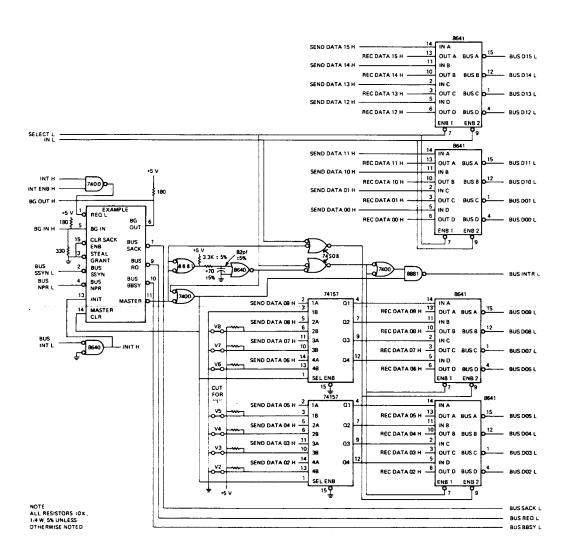

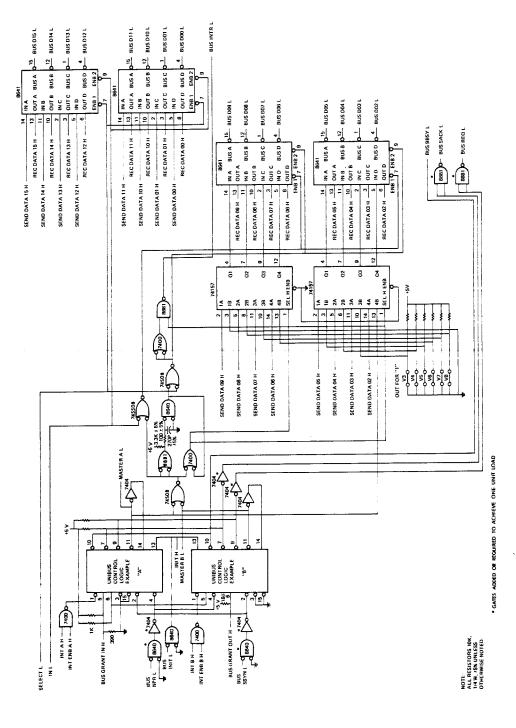

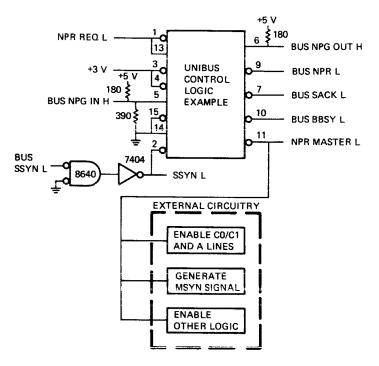

| UNIBUS INTERFACE DESIGN GUIDELINES Preferred Interface Integrated Circuit (IC) Chips Unibus Transmitter (Driver) Unibus Receiver Bus Receiver and Transmitter Equivalent Circuits DC Bus Load Module Layout Backplanes Grounding Logic Design Guidelines for Unibus Interfaces Master Devices Unibus Control Logic Bus Request (BR) Device—One Vector Bus Request (BR) Device—Two Vectors Non-Processor Request (NPR) Device | 57<br>57<br>58<br>59<br>59<br>61<br>61<br>62<br>64<br>64<br>67<br>70<br>72<br>74 |

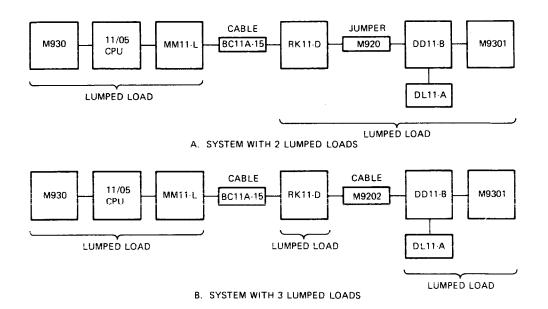

| UNIBUS CONFIGURATION Definitions Unibus Segment Unibus Cable                                                                                                                                                                                                                                                                                                                                                                 | 75<br>76<br>76<br>77                                                             |

| Unibus Element                                                                                                                                                                                                                                                                                                                                                                                                               | 77<br>77<br>77<br>77                                                             |

| Bus Terminator                                                                                                                                                                                                                                                                                                                                                                                                               | 78<br>79<br>79                                                                   |

| DATIP Transactions  Data-Out Transactions  Parity Error Indicators (PA, PB)  Master Sync (MSYN)                                                                                                                                                                                                                                                                                                                              | 80<br>80<br>81<br>81                                                             |

| Slave Sync (SSYN) Interrupt Request (INTR) AC Bus Load DC Bus Load                                                                                                                                                                                                                                                                                                                                                           | 81<br>82<br>82                                                                   |

| Maximum Cable Length (Rule 1)                                                                                                                                                                                                                                                                                                                                                                                                | 82<br>82<br>83<br>83                                                             |

| Maximum AC Loading (Rule 3)                                                                                                                                                                                                                                                                                                                                                                                                  | 83<br>85<br>87                                                                   |

| UNIBUS HARDWARE Unibus Cable (BC11A) M920 Unibus Jumper Module                                                                                                                                                                                                                                                                                                                                                               | 88<br>88                                                                         |

| M9202 Unibus Jumper with Cable                                                                                                                                                                                                                                                                                                                                                                                               | 89<br>89                                                                         |

.

| M930 Unibus Terminator Module                                                                                                                                                                                                   | 89<br>91<br>91<br>93                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| PART 2, LSI-11 BUS SPECIFICATION                                                                                                                                                                                                |                                                      |

| INTRODUCTION                                                                                                                                                                                                                    | 97<br>97                                             |

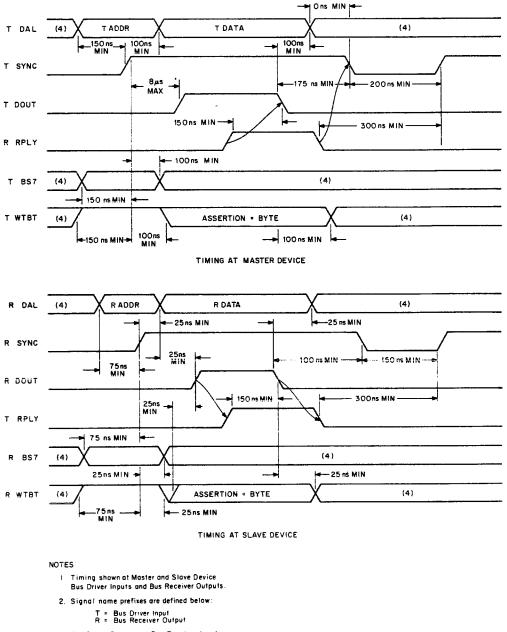

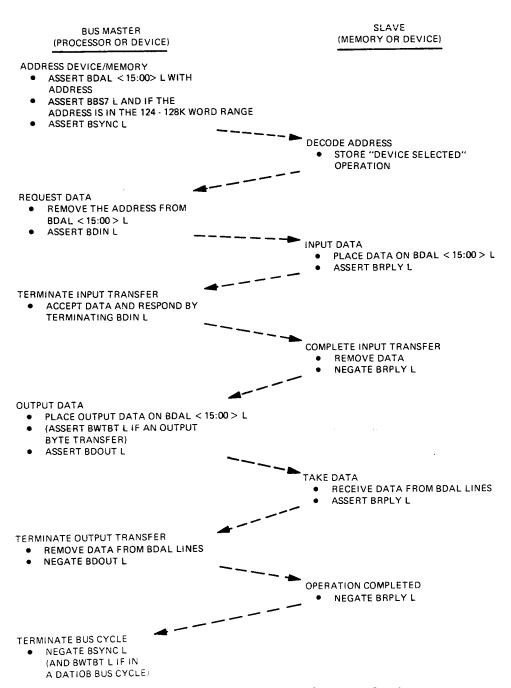

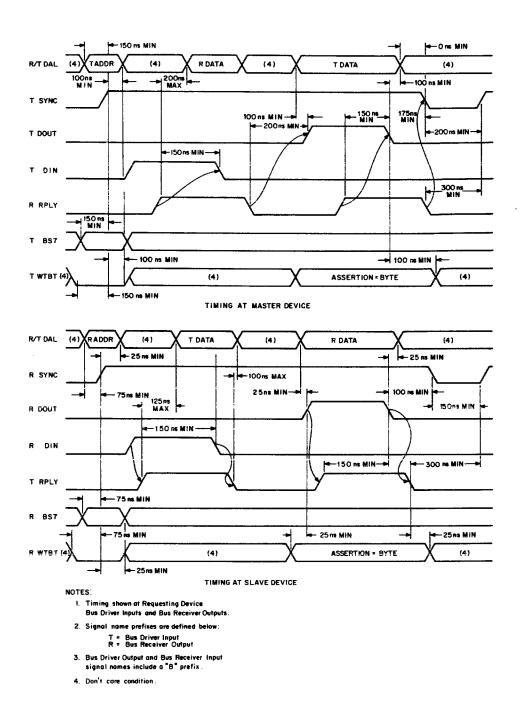

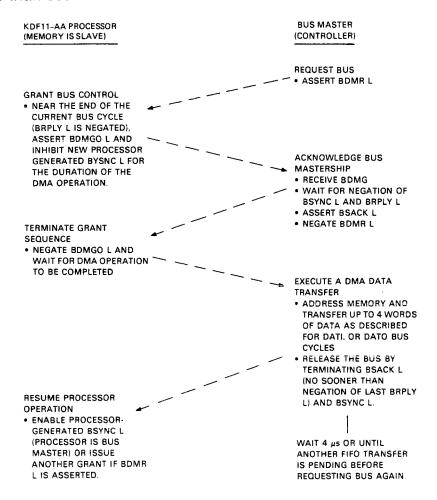

| DATA TRANSFER BUS CYCLES  Bus Cycle Protocol                                                                                                                                                                                    | 106<br>107<br>107<br>108<br>109<br>112<br>113<br>115 |

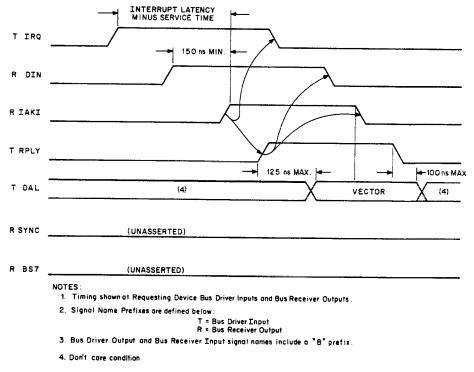

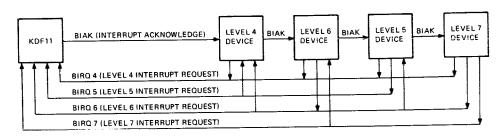

| INTERRUPTS Device Priority Interrupt Protocol 4-Level Interrupt Configurations (LSI-11/23)                                                                                                                                      | 117<br>118<br>118<br>121                             |

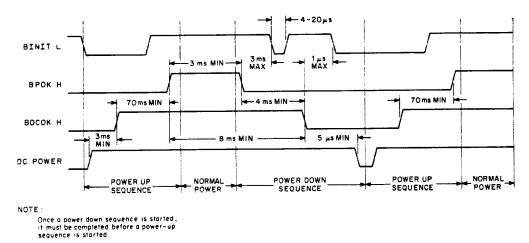

| CONTROL FUNCTIONS  Memory Refresh  Halt  Initialization  Power Status  BDCOK H  BPOK H  Power-Up/Down Protocol                                                                                                                  | 123<br>123<br>123<br>123<br>123<br>123<br>124        |

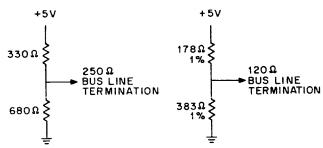

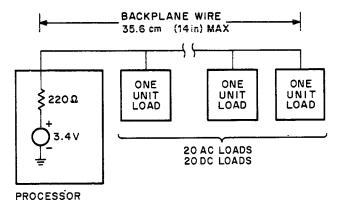

| BUS ELECTRICAL CHARACTERISTICS  AC Load Definition  DC Load Definition  120 Ohm LSI-11 Bus  Bus Drivers  Bus Receivers  Bus Termination  Bus Interconnecting Wiring  Backplane Wiring  Intra-Backplane Wiring  Power and Ground | 124<br>124<br>125<br>125<br>125<br>126<br>126<br>127 |

| SYSTEM CONFIGURATIONS                                                                                                                                                                                                           | 128<br>128<br>128<br>129                             |

# **APPENDICES**

| APPENDIX A, MASSBUS    | 135 |

|------------------------|-----|

| APPENDIX B, DECDATAWAY | 141 |

| APPENDIX C. PCL-11     | 147 |

## **PREFACE**

Since the introduction of the PDP-11 in 1970, engineers have found PDP-11 bus structures easy to understand and easy to interface. This book describes the technical specifications of the PDP-11 UNIBUS and LSI-11 bus in a convenient reference document. We hope the book will assist users in configuring large, complex PDP-11 systems and aid in the design of interfaces for PDP-11's.

The reader is expected to be familiar with PDP-11 architecture. For further information on the PDP-11 architecture and instruction set, see the various processor and other handbooks available from Digital.

The UNIBUS and LSI-11 bus are protected by Digital patents. However, licenses are available under these patents for peripheral and memory devices to be connected to these buses. The PDP-11 family of computers includes other buses whose specifications are not available to customers. These include the high speed Massbus, the multidrop DECdataway, and the network interconnecting PCL-11 bus. Each of these is briefly characterized in an appendix to this book.

An excellent discussion of buses in general, and the UNIBUS and LSI-11 bus in particular, can be found in the book **COMPUTER ENGINEERING**, **A DEC View of Hardware Systems Design**, written by C. Gordon Bell, J. Craig Mudge, and John E. McNamara, and published by Digital Press; Bedford, Massachusetts; copyright 1978.

part 1

unibus

specification

# UNIBUS SPECIFICATION

#### INTRODUCTION

Part 1 of this handbook defines the terminology and specifies the minimum requirements of the PDP-11 Unibus. All products designed at DIGITAL for use on the Unibus must conform to the Unibus Specification before being considered for production release. Users are advised to follow the technical specifications carefully in designing custom interfaces.

## Scope

This specification applies to the PDP-11 family of central processor units that use a single high-speed bus, known as the Unibus. Address, data, and control information are sent along the 56 lines of this bus. Each processor with a Unibus uses the same set of signals for communication on the bus.

This specification applies to PDP-11 Unibus central processor units (CPU) and options which use the Unibus.

#### Content

The Unibus specification is divided into the following sections.

- 1. Introduction—scope and contents.

- 2. Unibus Description—system architecture, definitions, priority structure, protocol introduction, and types of data transfers.

- Unibus Signal Details—types of Unibus lines and interrelationship among signals.

- 4. Unibus Protocol—priority arbitration, data transfers, and initialization.

- 5. Unibus Interface Design Guidelines—bus drivers and receivers, placement of these on an interface, wiring backplanes, deskewing signals, and a discussion of the master device.

- Unibus Configuration—definitions, rules, and guidelines to configure a system; bus elements, bus loads, and bus length.

- 7. Unibus Hardware—cables, jumpers, terminators, and backplane pin assignments.

## UNIBUS DESCRIPTION

This section defines the Unibus components in general terms, the arrangement of these components into a system, and the various types of operations that are transacted in a system. Greater technical detail follows in later sections.

A bus is an electrical conductor that carries current or signals to several other electronic circuits. The Unibus is a set of electrical circuits defined for the PDP-11 family of central processors. The Unibus is defined by its architecture, its protocol, and its electrical characteristics. The word "bus" when used in Part 1 of this book is synonymous with the word "Unibus."

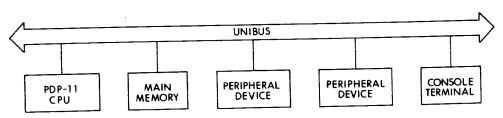

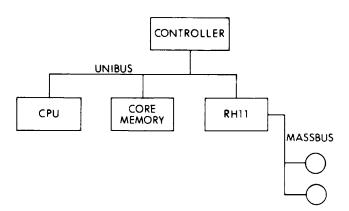

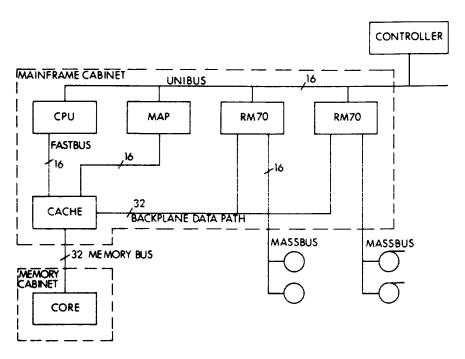

**Architecture**—The Unibus is a linear bus. It consists of a multiconductor transmission medium to which the components of a system are attached at various points, as shown in Figure 1-1.

Figure 1-1 Unibus System Simplified Block Diagram

Unibus Transmission Medium—The Unibus transmission medium interconnects the component "bus devices" of a system. The transmission medium consists of the following elements.

- A flat flexible cable containing 56 signal lines and 64 corresponding ground lines.

- 2. Drivers and receivers for the signals transmitted on the 56 signal lines. A "driver" (or bus driver) is a circuit used by a device to transmit signals to the Unibus; a "receiver" (or bus receiver) is a circuit used by a device to receive signals from the Unibus. These drivers and receivers are physically located in the devices but are electrically part of the Unibus. A device contains drivers and/or receivers only for the bus signals that it uses.

- 3. The interconnect between the flat cable and the output of the drivers or the input to the receivers.

The 56 signal lines are grouped logically into three types.

- 1. Initialization (3 lines): Signals on these lines control power-up, power-down, or initialization sequences of the bus devices;

- Data (38 lines): These lines are used for data transfer between devices; and

- 3. Priority Arbitration (15 lines): Signals on these lines decide which device will next be allowed to control the data section.

Bus Terminator—The Unibus, as a transmission medium or transmission line, has a characteristic impedance and must be properly

terminated. A Unibus is terminated at both ends by a bus terminator.

**Bus Segment**—A bus segment is that portion of a Unibus system between two terminators. A system may consist of one or more segments. The number of devices that may be connected to a segment is limited, as is the length of its cable.

**Bus Repeater**—A bus repeater is a device used to interconnect two segments of a multi-segment Unibus system. A repeater receives the signals from one segment and retransmits them onto the other segment. Its purpose is twofold:

- 1. It prevents signal levels from becoming degraded due to the connection of too many devices to a bus.

- 2. By receiving and then retransmitting all signals going between one segment and the next, it ensures that the proper timing relationship between signals is maintained.

Bus Master—The bus master is the device or processor that is currently permitted to use the data section of the Unibus. Only one device may be master at a given time. Typically, a master uses the data section of the bus to transfer data between itself and another device which is called "slave." A typical example of this relationship is the processor, as master, fetching an instruction from memory (which is always a slave).

**Bus Slave**—The bus slave is the device that communicates with the bus master. Only one device may be the bus slave at a given time.

Some devices may become both master and slave (at different times), while other devices may become only master or only slave.

Bus Arbitrator—The bus arbitrator is a logic circuit that compares priorities from devices requesting the use of the data section of the bus in order to determine which device is to be granted control next (i.e., become next bus master). The processor, as bus arbitrator, may pass bus control to a Direct Memory Access (DMA) device. The DMA device, as bus master, could then communicate with memory (always a slave) without processor intervention.

The arbitrator may or may not be part of a processor. There must be one and only one arbitrator on a Unibus. A system may have more than one Unibus, each with its own arbitrator.

**Bus Request**—A request by a master device to use the data section of the bus. The request is sent to the arbitrator on one of five signal lines: BR4, BR5, BR6, BR7, and NPR.

Bus Grant—A grant is a signal to the requesting device that it may

become next bus master. The grant is sent by the arbitrator on one of five signal lines: BG4, BG5, BG6, BG7, and NPG.

**Processor**—A processor is a bus device that includes the circuits that control the interpretation and execution of instructions. A processor does not include the Unibus, main memory, or peripheral devices. A processor may become master or slave.

Interrupt Fielding Processor—There may be more than one processor connected to a Unibus; however, there is normally only one "interrupt fielding processor." An interrupt fielding processor is a processor that has special connections to the arbitrator.

These special connections permit the interrupt fielding processor to service interrupt transactions on the Unibus.

## **UNIBUS SYSTEMS**

The elements of the Unibus are interconnected to constitute a computing system. The function of the Unibus in the system is to allow data to be exchanged between devices as directed by the program. A program is a sequence of instructions as interpreted by a processor.

Data is transmitted on the bus either as 16-bit words or as 8-bit bytes. The data is exchanged between a master and a slave.

There can be only one master and one slave on the bus at any given time. The master determines which device will become slave by putting the address of the desired slave device on the bus. In order to become bus master, a device must request and obtain the use of the data section. This request may be made at any time the device is ready for a data transfer. Any number of devices may be asserting a request at the same time. The priority scheme implemented by the arbitrator determines which of these requests is honored (i.e., which device will obtain the use of the data section when it becomes free).

Several devices may be ready to transfer data at the same time. Since only one of these devices can obtain the use of the data section, the other requesting devices have to wait before being allowed to transfer data. If the wait is too long, some devices may lose data. This wait period is known as latency.

The concepts of signal lines, priority structure, address space, and latency are discussed in the following paragraphs. These concepts must all be taken into consideration when arranging devices on a Unibus.

#### Signal Lines

Previous literature has defined Unibus signal lines as being either "bidirectional" or "unidirectional." These terms are ambiguous

and are not used in this description. They are only mentioned in this paragraph because of the previous usage.

Unibus signals may be divided into two general categories with respect to the manner in which they are transmitted. The majority of signals use lines that are, in effect, wired-OR circuits to which the inputs to the bus receivers and the outputs of the bus drivers are connected. These lines are thus available along the length of the Unibus to any device which needs to receive or to assert/negate the signals transmitted on the lines. These lines were in the past called "bidirectional lines" because a signal asserted or negated at any point on the line may be received at any other point on the bus. It should be noted, however, that some of the signals transmitted on lines of this type are logically, if not electrically, "unidirectional," For example: requests for permission to use the data section of the bus are asserted on a line of this type by devices that need to become bus master, but are received only by the arbitrator. This request signal is thus in effect "unidirectional," although transmitted on a "bidirectional" line.

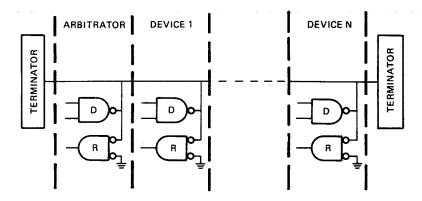

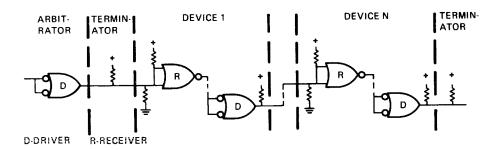

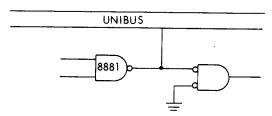

The drawing in Figure 1-2 shows these wired-OR lines schematically.

Figure 1-2 Illustration of Unidirectional Lines

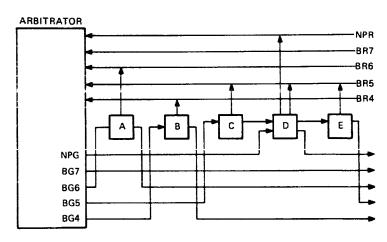

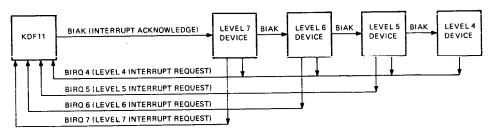

Five Unibus signals use lines where the signal is received only by the device that is closest on that line to the origin of the signal; this receiving device, in turn, either retransmits the signal to the next device on the line ("passes" the signal) or does not retransmit it ("blocks" the signal). The transmission process continues until either a device blocks the signal or the end of the line is reached. These lines have been called "unidirectional lines." They are used only by the arbitrator to grant bus access permission to devices requesting the use of the data section of the bus. Figure 1-3 shows this type of line schematically.

Figure 1-3 Requesting Bus Access

#### **Priority Structure**

A priority structure determines which requesting device will use the data section of the bus. The priority of a device is a function of (1) the priority level assigned to the device and (2) its position on the bus with respect to other devices of the same priority level.

All devices, with the exception of the interrupt fielding processor, may be assigned to one (or more) of five hardware priority levels. A signal line is dedicated to each of these levels. Each signal line is driven by all bus devices assigned to the priority level. These five lines are referred to as "request lines" and are monitored by the arbitrator. A device that requires the use of the data section of the bus asserts a request on one of these lines. This request is received by the arbitrator.

The arbitrator also monitors the priority level of the interrupt fielding processor. The arbitrator issues a grant to the highest priority request active if the interrupt fielding processor is not at a higher priority level.

A grant signal informs the requesting device that it may become next bus master. This signal is sent on a separate line than the request, either: NPG, BG7, BG6, BG5, or BG4. The level of the grant is the same as that of the request.

The arbitrator issues a grant to the first device on the bus assigned to the same priority level as the grant. If this device is requesting the use of the data section of the bus, it accepts and acknowledges receipt of the grant. It also blocks further transmission on the grant line. If the device is not requesting the use of the data section, it passes the grant to the next device on the same grant line. This procedure is repeated until a device accepts the grant or until the end of the bus is reached. In this last case, the grant is cancelled by the arbitrator and the arbitration process is restarted. Each device on a Unibus is assigned a discrete position in the priority structure. This position is determined by:

1. the priority level assigned to the device, and

2. the position of the device on the grant line with respect to the other devices of the same priority level.

All devices assigned to a given priority level have higher priority than any device at a lower level. Within a given priority level, the device closest to the arbitrator (origin of the grant signal) has the highest effective priority.

## **Address Space**

An address is the name of a location in memory of a register. A number specifies the location. A Unibus device may contain one or more locations. A simple device such as a line clock may contain only one; a memory device may contain thousands. A device may be able to store many words and yet have only three or four address locations. An example of this is a disk or tape controller. An address location may be used for storage of data (i.e., data register) or for control of a device (i.e., peripheral address).

A PDP-11 16-bit word is divided into a low byte (bits 0-7) and a high byte (bits 8-15). A 16-bit word used for byte addressing can address a maximum of 32K words (or 64K bytes). However, the top 4,096 word locations are reserved for peripheral register addresses, and the user therefore has 28K words for programs. Systems with Memory Management options provide an 18-bit effective memory address which permit addressing up to 124K words of memory for programs.

A device must be bus master to use the address lines. An address put on the address lines by a master is received by all bus devices that are capable of becoming slaves: one of these devices recognizes its address and becomes the slave; the slave does not know which device is master, nor where the master is physically located on the bus. The master does not know the physical location of its slave, nor does it need to know.

Each external I/O device in a computing system has an external page address assigned to it. The use of this address on the Unibus is defined as part of the PDP-11 I/O page.

#### Latency

Latency is the delay between the time that a device initiates a request and the time that it receives a response. Nonprocessor request (NPR) or Bus request (BR) latency is the total time consumed by all the operations that occur between the instant a device makes a request and the moment it becomes bus master. (NPR and BR device requests are further defined in later sections.) The delay encountered is a function of current bus activity, the types of other devices in the system, and the arrangement or configuration of the equipment along the bus.

Maximum tolerable latency is the longest time that a device can wait for service before losing data. The service time is measured from the assertion of a request by the device to the time that the requested data transfer is complete.

# Arrangement of Devices on the Unibus

The arrangement of devices on the Unibus is a function of the following four factors.

- Any device can communicate with any other device on the data section of the bus. Physical position of the device is not important to its ability to communicate on the Unibus.

- 2. Grants are issued by the arbitrator and received and reissued by each device of the same level. All devices capable of becoming bus master must be on the same side of the arbitrator. In reality, the arbitration is on the CPU module. Most bus devices are located on one side of the CPU module.

- 3. The maximum tolerable latency for each device must not be exceeded. This depends on:

- a. the priority level assigned to the device,

- b. its position on its grant signal line relative to other devices of same priority level,

- c. the effect on the bus of all other devices at their priority levels, and

- d. the length of the bus.

- 4. The maximum length of the Unibus cable should not exceed 15.24 m (50 ft). A bus repeater can drive an additional 50 ft. More information on determining bus length is found in the section on Unibus Configuration.

#### NOTE

The interrupt fielding processor is typically next to the arbitrator on the bus. An arbitrator is built into each PDP-11 processor module.

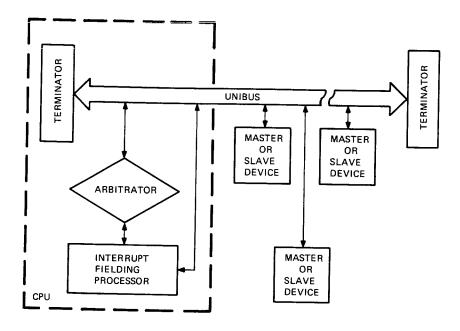

A typical Unibus configuration is shown in Figure 1-4. The bus is terminated at both ends. The processor module terminates one end of the bus; a terminator module terminates the other end. Various devices (such as memories, peripheral controllers, and input/output devices) are placed between these modules.

# **Expanding the Unibus System**

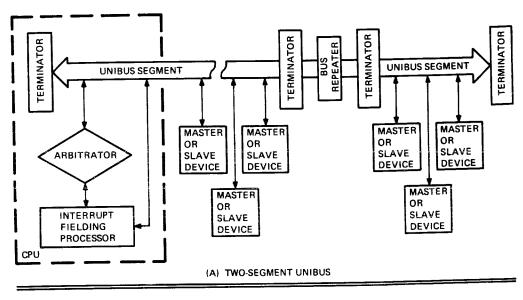

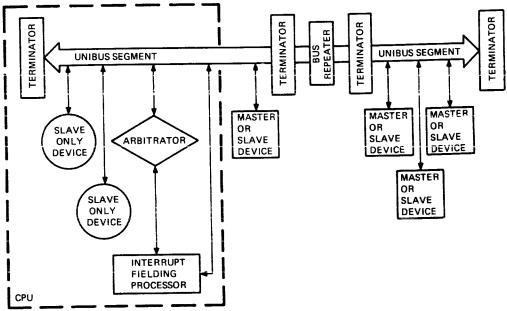

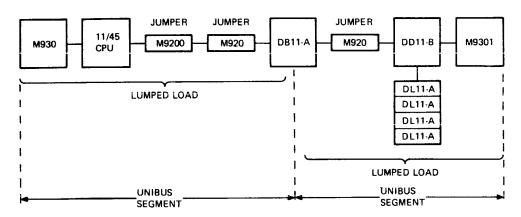

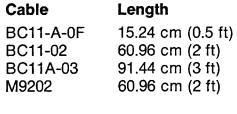

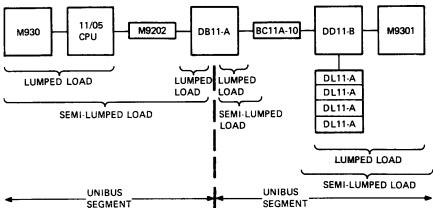

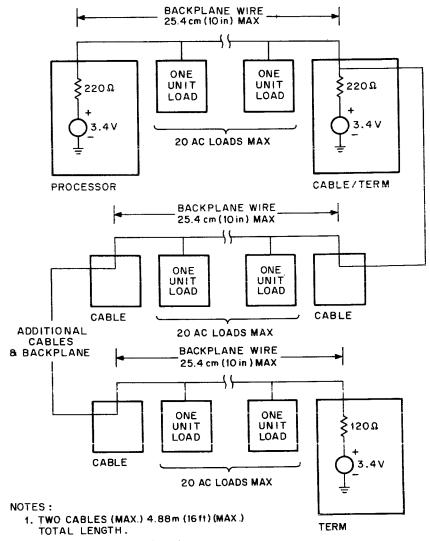

If a system exceeds the limitations set forth in this document, the bus must be divided into bus segments that are connected by a bus repeater. The limitations apply to the maximum number of devices on a segment (bus loading) and to the length of the bus cable. Figure 1-5 shows a two-segment Unibus configuration.

Figure 1-4 Typical Unibus Configuration

A device that can only be a slave, never a master, (such as a memory built into the CPU module) never requests nor receives grants. It may be physically located on either side of the arbitrator, as shown in Figure 1-5b.

#### **PROTOCOL**

The Unibus protocol defines the procedures that are used for communication on the bus. Communication between devices is in the form of transactions. A transaction is a sequence of signals that complete a logical unit of activity on the Unibus.

## Types of Transactions

There are three types of Unibus transactions.

- 1. priority arbitration,

- 2. data transfer, and

- 3. initialization.

Each of these occurs on a separate section of the Unibus. This allows simultaneous priority arbitration and data transfer transactions. For example, the next master can be selected while the current master executes its data transfer.

# **Priority Arbitration Transactions**

Priority arbitration determines which device will obtain control of the bus. In order to transfer data on the data section of the bus, a device must become bus master. No change of bus master occurs during the priority arbitration sequence. The sequence selects the device to become the next master when the current

(B) TWO-SEGMENT UNIBUS WITH SLAVE DEVICES ON BOTH SIDES OF ARBITRATOR

Figure 1-5 Two-Segment Unibus System

master releases the data section of the bus. Any number of devices may request the use of the data section at one time. The one device that is selected to be bus master is the one with the highest effective priority.

The highest priority device grant is called a non-processor grant (NPG). It is used by a device that does not require processor time. It may be used by devices **only** for data transfers that do not require interrupts. When requested, an NPG grant is issued on this level.

#### NOTE

An NPG is issued by the arbitrator for an NPR request. NPR is the highest level request; NPG is the highest level grant.

More than one device may be connected to the Unibus at the NPR level of priority. In the case of a tie for an NPR request, the device closest to the arbitrator is granted the NPG (on the NPG line).

When no request or grant is active at the NPG priority level and if there is no BG issued, the interrupt fielding processor may become bus master. The priority arbitration is affected by the priority state of the CPU.

The CPU program execution priority (PRI) varies from 0 to 7. The Unibus arbitrator grants use of the bus to non-CPU devices by the following rules:

- 1. At any time when an NPR is received, assert NPG. (A controller may do direct memory access data transfers at any time.)

- 2. When the CPU is between instructions, then:

- a. If PRI <7 and BR7 is received, assert BG7;

- b. If PRI <6 and BR6 is received, assert BG6;</li>

- c. If PRI <5 and BR5 is received, assert BG5;

- d. If PRI <4 and BR4 is received, assert BG4.

(The CPU will accept interruptions from a controller whose priority is greater than the current program execution priority of the CPU.)

#### **Data Transfers**

A data transfer is defined as the transmission of data between a master and a slave. This transfer can occur without processor intervention or supervision.

The device that has been granted next bus master waits for the Unibus to be released by the current bus master. When a device becomes bus master, it causes one or more words of data to be transferred between itself and a slave device. The particular slave and the direction of transfer are determined by the information issued by the bus master onto the Unibus. When the transfer is complete, the master releases the bus, at which time a new device may assume mastership. A device in control of the bus can transfer data at the maximum rate allowed by the combination of the master, the slave, and the bus.

An interrupt is a special type of data transaction to which only the interrupt fielding processor can respond as slave.

There are four types of data transfer transactions on the Unibus: data-in, data-out, read/modify/write, and interrupt.

- 1. Data-in is the transfer of one word from a slave to a master.

- 2. Data-out is the transfer of one word of data from a master to a slave; data-out, byte is the transfer of one byte of data from a master to a slave.

- 3. Read/modify/write is a transaction in which data is transferred from a slave location to a master, modified by the master, and transferred back to the same slave location. A read/modify/write consists of a data-in, pause followed by a data-out or by a dataout byte. The data-in, pause is identical to the data-in; however, it informs the slave that a data-out transaction to the same location will follow the data-in. If the slave is a destructive readout device (e.g., a core memory), it automatically restores the data after a data-in. After a data-in, pause, the slave might not restore the data but may wait for the modified data from the following data-out.

- 4. An interrupt transaction is the transfer of one word, the "interrupt vector," from the master to the interrupt fielding processor (CPU).

The fact that data transfers may be executed without processor intervention or supervision permits operations such as a disk directly refreshing a CRT display or transfers between the memory and a mass storage device.

Processors may use data transfers for instruction fetch and for control of other devices by modification of their control registers, as well as for the manipulation of information.

#### Initialization

The initialization section of the Unibus continuously monitors the AC power input to the bus power supplies. It also controls the orderly power-up and power-down of all bus devices.

Individual devices may be initialized under program control. Bus initialization stops all bus operations and puts all bus devices in a known well defined state.

## UNIBUS SIGNAL DETAILS

The Unibus consists of 56 signals. Standardized control logic makes it possible to use separate dedicated lines for all signals. For example, a bus master provides the address of a location it wishes to access. The slave device responds. Control and timing signals are provided. Address, control, data, and timing functions each use a distinct set of bus lines.

All bus activity is asynchronous and depends on interlocked control signals. In every case, a control signal transmitted is acknowledged by the receiver of that signal.

# **Unibus Sections and Signal Lines**

Although the Unibus is a single communication path for all devices in a PDP-11 computer system, the bus actually consists of three interrelated sections:

the priority arbitration section, the data transfer section, and the initialization section.

These sections and their signal lines are shown in Table 1-1.

Table 1-1

Unibus Sections and Signal Lines

|                          |                        |           | _        | olgilai Ellics                              |                         |

|--------------------------|------------------------|-----------|----------|---------------------------------------------|-------------------------|

| Name                     | Mnemonic               | No<br>Lin |          | f<br>Function                               | Asser-<br>tion<br>Level |

| Data Transfer            | Section                |           |          |                                             |                         |

| Address                  | A <17:00>              | 18        |          | Selects slave device and/or memory address  | Low                     |

| Data                     | <d 15:00=""></d>       | 16        |          | Information transfer                        | Low                     |

| Control                  | C0, C1                 | 2         |          | Type of data transfer                       | Low                     |

| Master Sync              | MSYN                   | 1         |          | Timing control for                          | Low                     |

| Slave Sync               | SSYN                   | 1         | ſ        | data transfer                               | Low                     |

| Parity                   | PA, PB                 | 2         |          | Device parity error                         | Low                     |

| Interrupt                | INTR                   | 1         |          | Interrupt                                   | Low                     |

| Priority Arbitrat        | ion Section            |           |          | •                                           | 2011                    |

| Bus Request              | BR4, BR5,<br>BR6, BR7* | 4         |          | Requests use of bus (usually for interrupt) | Low                     |

| Bus Grant                | BG4, BG5,<br>BG6, BG7* | 4         |          | Grants use of bus (usually for interrupt)   | High                    |

| Non-Processor<br>Request | NPR                    | 1         |          | Requests use of bus for data transfer       | Low                     |

| Non-Processor<br>Grant   | NPG                    | 1         |          | Grants use of bus for data transfers        | High                    |

| Selection<br>Acknowledge | SACK                   | 1         |          | Acknowledges grant                          | Low                     |

| Bus Busy                 | BBSY                   | 1         |          | Indicates that the data section is in use   | Low                     |

| Initialize Section       |                        |           |          |                                             |                         |

| Initialize               | INIT                   | 1         |          | System reset                                | Low                     |

| AC Low                   | AC LO                  | 1         |          |                                             | Low                     |

| DC Low                   | DC LO                  | <b>1</b>  | <b>}</b> | Power monitoring                            | Low                     |

<sup>\* &</sup>quot;BRn" and "BGn" are abbreviations used to designate that one pair of Bus Request (BR) and Bus Grant (BG) lines is used.

All transactions on the priority arbitration section and on the data transfer section are interlocked dialogs between devices. The requesting devices and the arbitrator communicate on the priority arbitration section. The bus master and the bus slave communicate on the data transfer section.

The signals that delimit or establish the boundaries for data operations are:

Data Transfer: MSYN, SSYN

Interrupt: INTR, SSYN

The signals that delimit priority arbitration are:

Priority Arbitration: [NPR, NPG] or [BRn, BGn], SACK, BBSY

In all bus transactions, the assertion and the negation of a signal used in the interlocking dialog have different meanings. A device may assert a signal to indicate the initiation of a process and negate the same signal to note the completion of the same process. The important event is the transition from one state to the other. For example, in a data-in operation, the bus master asserts MSYN to request data from the slave, and negates MSYN to acknowledge receipt of the data from the slave. The assertion and the negation of MSYN can be considered two different signals issued by a bus master on a single line. The following definitions apply to this specification.

"The assertion of ..." or "at the assertion of ..." signifies the transition of a signal from the negated state to the asserted state.

"While . . . is asserted" refers to the interval between the assertion and the negation of a signal. While asserted, a signal is in the logically true state.

"The negation of ..." or "at the negation of ..." signifies the transition from the asserted state to the negated state.

"While . . . is negated" refers to the interval between the negation and the assertion of the signal. While negated, a signal is in the logically false state.

In tables and diagrams, a 0 may be used in place of "while negated" and a 1 in place of "while asserted."

# Signal Transmission

Bus transmission delay and skew affect signal transmission on the Unibus.

Bus Transmission Delay-Bus transmission delay is the length of time taken by a signal to travel from one device on the bus to another. The delay is measured from the time of the assertion or negation of the signal at the input to the driver of the sending device to the time at which the assertion or negation arrives at the output of the receiver of the receiving device.

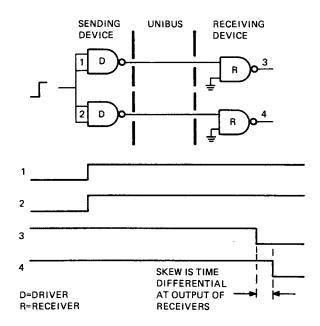

**Skew**—Skew is the propagation delay due to variations in electronic circuits. Two signals starting at the same time, from one device to another, experience a time difference on arriving at the second device, even if similar circuitry and transmission media are used. This time difference (or time uncertainty) is called skew. It is caused mainly by the variation in the transmission delay time through the Unibus drivers and receivers, and by different loading of the bus by devices connected to the Unibus. Figure 1-6 illustrates this time differential.

Figure 1-6 Example of Skew Time Differential

Maximum skew is the greatest difference in arrival time of two signals on the Unibus. This is measured from the inputs of two bus drivers in the first device to the output of receivers in the second device. Maximum skew on the Unibus is 75 ns. This includes the effects of drivers, receivers, and cables.

**Deskew**—To deskew is to introduce a delay in a circuit to compensate for skew.

A master is responsible for deskewing on all data transfer transactions with the exception of interrupt. The arbitrator and interrupt fielding processor are responsible for deskewing on interrupt transactions. The arbitrator is responsible for deskewing on priority arbitration transactions. By assigning these responsibilities.

the amount of logic elements required throughout the system is minimized. The number of master devices on a system are generally fewer than slave devices. Also, there is only one arbitrator and one interrupt fielding processor on a bus.

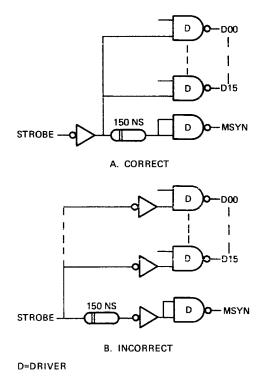

All delays in this Unibus specification refer to assertions or negations at the input to the Unibus drivers. Figure 1-7a shows an example of correct gating of data lines and a delayed control signal (MSYN); Figure 1-7b is an example of incorrect gating because the inverters do not all have the same propagation delay, thus introducing additional skew.

Figure 1-7 Example of Deskewing

#### **Types of Unibus Signal Lines**

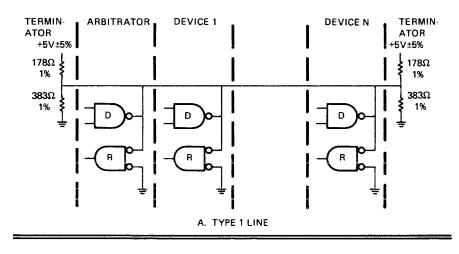

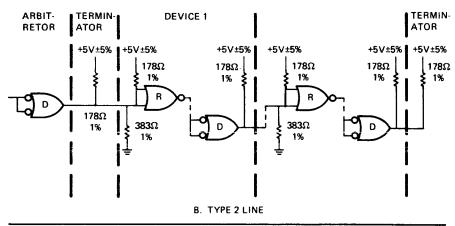

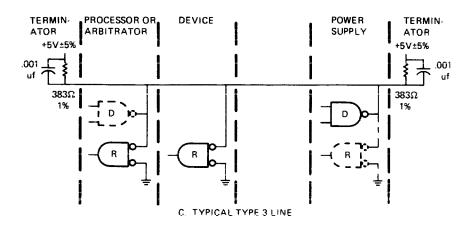

Three types of signal lines are used on the Unibus. These are defined in the following paragraphs and illustrated in Figure 1-8.

#### NOTE

The drivers and receivers are considered part of the Unibus and NOT part of the device or processor in which they are physically located.

Type 1 Line—A type 1 line is a transmission line that has drivers or receivers connected in a logic OR configuration. If one device asserts a signal on this type line, all other devices receive the sig-

Figure 1-8 Types of Unibus Lines

nal, for example: bus busy. A line of this type is terminated at both ends of the Unibus by:

- 1. a resistor to + 5 Vdc and

- 2. a resistor to ground.

A device or processor may have drivers or receivers (or both drivers and receivers) connected to a type 1 line. Type 1 lines are used by all Unibus signals with the *exception* of NPG, BG7, BG6, BG5, BG4, AC LO and DC LO.

Type 2 Line—A type 2 line is a transmission line in which a signal is received only by the device electrically closest to it on that line. This device either transmits or does not transmit the signal to the next device on the same line. Each segment of a type 2 line is terminated at the receiver end by resistors to ground and to +5 Vdc and at the driver end by a resistor to +5V. Type 2 lines are used by Unibus grant signals: NPG, BG7, BG6, BG5, and BG4.

Type 3 Line—A type 3 line is a transmission line used for monitoring purposes. These lines are constantly at one state unless a failure occurs. These lines are terminated at both ends of the Unibus by a resistor and a capacitor in parallel to +5 Vdc. Type 3 lines are used for power monitor signals: AC LO and DC LO.

#### **Priority Arbitration Section**

Twelve signal lines are used on the priority arbitration section of the Unibus.

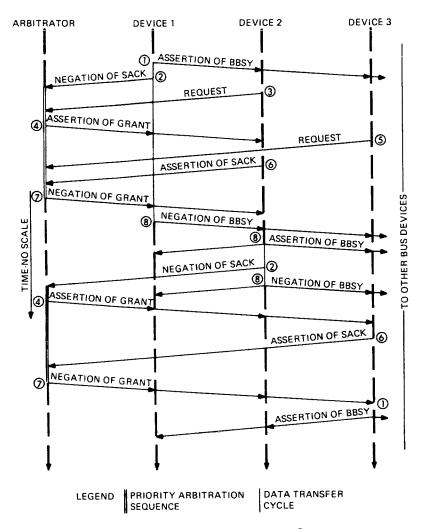

Transactions on this section of the bus occur between the priority arbitration network and devices that need to become bus master. A request (NPR or BRn) is asserted by one or more of these devices. The arbitrator issues a grant (NPG or BGn) for the highest priority device requesting the bus, and the requesting device electrically closest to the arbitrator at this priority level accepts and acknowledges the grant by asserting SACK. When the current data transaction is ended, the master releases the bus by negating BBSY, the new master asserts BBSY and starts its data cycle(s).

Requests are transmitted on type 1 lines and grants on type 2 lines.

A device that receives a grant and does not require the use of the data section of the bus retransmits the grant to the next device on the same grant line. This is known as "passing the grant."

#### NOTE

Lines used to pass a grant are also used to negate the grant.

A device that receives a grant and does require the use of the data section of the bus accepts the grant and does not retransmit it. This is called "blocking the grant."

If a grant is not acknowledged by any device on the bus, the grant is cancelled. This is done either by the arbitrator after a time out delay, or by a terminator at the opposite end of the bus from the

arbitrator. This terminator asserts SACK if it receives a grant. Upon receipt of SACK, the arbitrator negates the grant. SACK is negated by the terminator upon receipt of this negation. In both cases, a new arbitration cycle is started. If a grant is cancelled due to the assertion of INIT (as part of a bus initialization procedure), arbitration is not resumed until receipt of the negation of INIT.

Non-Processor Request (NPR)—NPR is an asynchronous signal requesting the use of the data section of the bus. A device that requires the use of the bus to execute data transfers sends NPR to the arbitrator. The data transfers are made without active participation by the processor. The NPR signal may be asserted any time the device is ready to start a data transfer. An NPR has the highest priority. (A controller may do DMA transfers at any time.)

NPR is transmitted on a type 1 line.

#### NOTE

PDP-11/15 and PDP-11/20 data transfers are completed prior to NPR or BR service.

Non-Processor Grant (NPG)—The arbitrator generates the non-processor grant signal. Each device capable of asserting a non-processor request (NPR) receives and optionally retransmits this grant.

NPG is transmitted on a type 2 line.

One or more data transfers (commonly called "NPR transfers") may be executed while the device is bus master.

#### NOTE

An interrupt must not be attempted while doing NPR transfers by the device that became bus master under the authority of an NPG.

Assertion—The assertion of NPG by the arbitrator informs the first device on the NPG line (that has NPR active) that it may become next bus master. This occurs after the new master determines the current user of the data section of the bus is done. (The next master monitors BBSY • SSYN • NPG to determine when to assert BBSY.

If a device intends to assert Selection Acknowledge (SACK), it blocks the grant. If a device does not intend to assert SACK, it passes the grant.

#### NOTE

Priority arbitration is disabled while NPG is asserted.

Negation—The following rules apply to negate NPG.

- The arbitrator acknowledges receipt of the assertion of SACK by negating NPG.

- 2. A device that is asserting SACK may not negate SACK before it has received the negation of NPG.

- 3. A device that is not asserting SACK passes the negation of NPG to the next device on the NPG line.

Bus Request (BR4, BR5, BR6, BR7)—A Bus Request is a signal requesting use of the data section of the bus. A device that requires use of the bus for the purposes of executing data transfers, executing an interrupt transaction, or both of these, sends a Bus Request to the arbitrator. The request is an interrupt. The request, the grant, and the data transfer together represent an interrupt transaction. Only one interrupt transaction may be executed under a single grant.

BR4, BR5, BR6, and BR7 are transmitted on type 1 lines.

Bus Grant (BG4, BG5, BG6, BG7)—A Bus Grant is a signal by the arbitrator. Each device capable of asserting the corresponding BR line (BRn) receives and optionally retransmits this bus grant. The arbitrator guarantees that a BG is never asserted unless the processor that receives interrupts is ready to accept an interrupt vector at that level.

BG4, BG5, BG6, and BG7 are transmitted on type 2 lines.

Assertion—The assertion of BGn by the arbitrator informs the first device on the BGn line (that has BRn active) that it may become next bus master. This occurs after the device determines the current user of the data section of the bus is done. (The next master monitors BBSY·SSYN·BGn to determine when to assert BBSY.)

If a device intends to assert Selection Acknowledge (SACK), it blocks the grant. If a device does not intend to assert SACK, it passes the grant.

#### NOTE

Priority arbitration is disabled while BGn is asserted.

Negation—The following rules apply to negate Bus Grant.

- 1. The arbitrator acknowledges receipt of the assertion of SACK by negating BGn.

- 2. A device that is asserting SACK may not negate SACK until it has received the negation of BGn.

- 3. A device that is not asserting SACK passes the negation of BGn to the next device on the BGn line.

**Selection Acknowledged (SACK)**—SACK is a signal sent to the arbitrator by a device that has received a grant.

SACK is transmitted on a type 1 line.

Assertion—The assertion of SACK is the acknowledgement by a device that it has accepted a grant. Priority arbitration is disabled while SACK is asserted.

Negation—The negation of SACK allows the start of a new priority arbitration cycle. The negation of SACK signifies that the master has almost finished using the data section of the bus. SACK is negated before the last data transfer by the current master. This allows the next bus master to be determined and ready when the current master is finished.

Bus Busy (BBSY)—BBSY is a signal sent by a bus master to all other bus devices.

BBSY is transmitted on a type 1 line.

Assertion—While asserted, BBSY informs all devices on the Unibus that a master exists. During this time no device other than the master may assert BBSY, MSYN, INTR, or use the address or control lines. The data lines may be used only by the master or by the slave designated by the address lines. SSYN may be asserted only by the slave; although it may or may not be negated before the master negates BBSY. Other devices may use signal lines in the priority arbitration section of the bus.

Negation—While negated, BBSY means there is currently no bus master.

#### **Data Transfer Section**

Forty-one signal lines are used for data transfer. In a data transfer, one device is a bus master and controls the transfer of data to or from a slave device.

All signals in the Data Transfer Section are transmitted on type 1 lines.

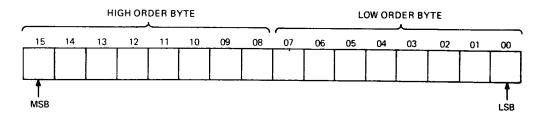

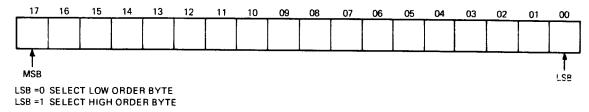

Data Lines, D<15:00>—The 16 data lines contain the word of information that is being transferred between the master and the slave devices. A word consists of two eight-bit bytes as shown in Figure 1-9. The low order byte contains bits 00 through 07; the high order byte, bits 08 through 15.

Address Lines, A<17:00>—The 18 address lines carry the 18 address bits from the master during a data transfer transaction. These bits specify a location. The device contains the specified location responds as the slave for this data transaction.

Figure 1-9 High and Low Byte Format

The address format is shown in Figure 1-10. The 17 address lines A<17:01> specify a unique location. All locations contain a 16-bit word which is at an even address. A byte is half a word. In byte operations, bit A00 specifies which byte is being addressed. All words are located at an even address X (i.e., its A00=0), the low order byte is addressed at X and the high order byte at X plus 1.

Figure 1-10 Address Format

Control Lines, C0, C1—The control lines are used by the master to indicate one of four possible data transfer operations. The operations are listed in Table 1-2 and defined in the following paragraghs.

#### NOTE

The direction of data transfer is always specified with reference to the master device; data-in is from slave to master, and data-out is from master to slave.

Data-In Transactions—The DATI and DATIP transactions request transfer of data from a slave to a master. Both transactions use the D lines to carry the data. These transactions are always a full word transfer; i.e., the slave places the data on D<15:00>. If the master wants only one byte, it must retrieve the data from the proper lines. For a low-order byte use D<07:00>; for a high-order byte use D<15:08>. For byte operations, the master can not assert bit A00 and the slave must ignore this bit.

DATIP Transaction—The DATIP operation is identical to the DATI, except DATIP informs the slave device that the present transfer is the first part of a read/modify, write cycle.

Table 1-2

Control Operations (C Lines)

|                   |           | Valu | ie |                                                                                                                                  |

|-------------------|-----------|------|----|----------------------------------------------------------------------------------------------------------------------------------|

| Name              | Mnemonic* | C1   | CO | Function                                                                                                                         |

| Data In           | DATI      | 0    | 0  | One word of data from slave to master                                                                                            |

| Data In,<br>Pause | DATIP     | 0    | 1  | Same as DATI, but inhibits restore cycle in destructive read-out device. Must be followed by DATO or DATOB to the same location. |

| Data Out          | DATO      | 1    | 0  | One word of data from master to slave.                                                                                           |

| Data Out,<br>Byte | DATOB     | 1    | 1  | One byte of data from master to slave.                                                                                           |

|                   |           |      |    | Data is transferred on:                                                                                                          |

|                   |           |      |    | D <15:08> for A00 = 1<br>D <07:00> for A00 = 0                                                                                   |

<sup>\*</sup> The notations DATI/P and DATO/B are equivalent to DATI (or DATIP) and DATO (or DATOB).

## Example:

A pause flag is set in a destructive read-out device (e.g., core memory) that inhibits the restore cycle. The DATIP must be followed by a data-out cycle (DATO or DATO/B) to the same word address.

Since address bit A00 may change between a DATIP and a DATO/B, the slave must check the bus address at the beginning of the DATO/B. The master must retain bus control until this DATO/B is completed; i.e., it must remain bus master (assert BBSY) without interruption from the start of the DATIP cycle to the end of the DATOB cycle. No other data transfer may be executed between the DATIP and the DATO/B cycles.

In nondestructive readout devices (i.e., flip-flops), the DATI and DATIP are treated identically by the slave.

#### NOTE

In the case of locations which can be accessed by more than one Unibus or other bus (e.g., the PDP-11/45 semiconductor memory) a DATIP on one bus must prevent

the slave from responding on any other bus until the DATO/B cycle has been completed. This is necessary to avoid problems in multiple processor systems.

If a DATIP is followed by a DATO/B, and the device performs a destructive readout, then the device takes the responsibility for restoring the other byte.

Data-Out Transactions—The DATO and DATOB operations transfer data from the master to the slave. A DATO is used to transfer a word to the address specified by A<17:01>. The slave ignores A00 and the master places data on D<15:00>.

A DATOB is used to transfer a byte of data to the address specified by A<17:00>. Line A00 = 0 indicates the low-order byte. The master places the data on lines D<07:00>. A00 = 1 indicates the high order byte. The master now places the data on lines D<15:08>.

Parity Error Indicators (PA, PB)—PA and PB are generated by a slave and received by a master. They indicate parity error internal to a device as follows.

| PA | PB | Condition                     |

|----|----|-------------------------------|

| 0  | 0  | No error in a slave in DATI/P |

| 0  | 1  | Error in slave in DATI/P      |

| 1  | Х  | Reserved for future expansion |

The protocol for PA and PB is the same as that for D<15:00>.

PA and PB are not defined in a DATO transaction. PA and PB may be used by the bus master's parity error logic.

Master Sync (MSYN)—MSYN is a signal issued by a bus master and received by a slave. MSYN has two functions depending on whether it is being asserted or negated.

Assertion—The assertion of MSYN requests the slave, defined by the A lines, to perform the function required by the C Lines.

Negation—The negation of MSYN indicates to the slave that the master considers the data transfer concluded.

**Slave Sync (SSYN)**—SSYN is a signal issued by a slave and received by a master. SSYN has two functions depending on whether it is being asserted or negated.

#### NOTE

In an interrupt transaction, the interrupt fielding processor is the slave and the interrupting device is the master.

Assertion—In a master-slave data transfer, the assertion of SSYN informs the bus master that the slave has concluded its part of the data transfer. For a DATI or DATIP, the requested data is placed on the D lines; for a DATO or DATOB, the data on the D lines is accepted.

In an interrupt operation, SSYN is asserted by the interrupt fielding processor. In this case, SSYN signifies that the interrupt vector is accepted by the interrupt fielding processor.

Negation—The negation of SSYN informs all bus devices that the slave has concluded the data transfer. For data-in (DATI/P), the negation of SSYN signifies the negation of Master Sync (MSYN) is received and the data removed from the D lines. For data-out (DATO/B), the negation of SSYN means that the negation of Master Sync (MSYN) is received. For an interrupt, the negation of SSYN signifies that the negation of the Interrupt Request (INTR) is received by the processor.

## **Interrupt Request (INTR)**

Assertion—INTR is a signal asserted by an interrupting device, after it becomes bus master. The signal informs the interrupt fielding processor that an interrupt is to be performed and that the interrupt vector is present on the D lines. INTR may only be asserted by a device that obtains bus mastership under the authority of BG4, BG5, BG6, or BG7.

Negation—INTR is negated upon receipt of the assertion of the Slave Sync (SSYN) from the interrupt fielding processor at the end of the transaction.

#### **Initialization Section**

Three signals are used in the initialization section of the Unibus: INIT, AC LO, and DC LO.

Initialize (INIT)—INIT may be generated by processors or arbitrators. A console operation may cause a processor to assert INIT. INIT may be received by any UNIBUS device. The purpose of INIT is to stop all bus operations and initialize the bus devices by placing each in a well defined state.

INIT is transmitted on a type 1 line.

**AC Low (AC LO)**— AC LO is a signal generated by all power supplies whose failure may affect Unibus transactions. This signal is received by processors, arbitrators and bootstrap devices.

AC LO is transmitted on a type 3 line.

Assertion—The assertion of AC LO informs Unibus devices that the AC power input to a power supply is not within specifications. This failure may make the bus inoperable.

Negation—The negation of AC LO informs Unibus devices that all power supplies can maintain DC power within specifications long enough for a complete power-down and power-up sequence.

**DC Low (DC LO)**—DC LO informs bus devices that dc power is about to fail.

DC LO may be received by any bus device. It is typically received by core memories that use it to disable their internal operations so as not to lose data. DDC LO may also be used to initialize devices.

DC LO is transmitted on a type 3 line.

Assertion—The assertion of DC LO informs the bus devices that DC power is about to fail.

DC LO may be generated by any Unibus device or power supply. It is generally issued by a processor, or by a power supply, or by both of these. No device should issue DC LO except in correct sequence with AC LO.

Negation—The negation of DC LO informs the bus devices that DC power is within specifications and bus operations can therefore resume.

#### **UNIBUS PROTOCOLS**

### **Definitions and Concepts**

**Arbitration**—The goal of arbitration is to decide which device is to have the use of the bus. Data transfers can originate from more than one source in the Unibus. Arbitration is the process of deciding which source is to use the bus next.

Centralized Arbitration—A signal must pass from a requesting device to a common arbitration point, and a response signal must return to the requesting device before it may transfer data. The Unibus uses centralized arbitration.

**Priority Arbitration**—In case of an apparent tie to request use of the data bus, rules are established to let one device go ahead of another. A priority arbitration sequence is a transaction during which a device is selected as next bus master. No actual bus transfer is performed. Priority arbitration is controlled by the arbitrator.

Data Transfer (Bus Cycle)—A data transfer, or bus cycle, is the transfer of one word between a master and a slave. The cycle starts when the master puts the address and control bits on the A and C lines; it ends when the master removes these bits from the lines.

**Transaction**—A transaction is a sequence of signals which completes a logical unit of activity on the Unibus. A transaction may consist of one or more bus cycles. For example: A data-in (DATI) is a single cycle transaction; a read/modify/write sequence (DATIP-DATO/B) is a two bus cycle transaction.

**Protocol**—The Unibus protocol is a set of procedures that must be used for a bus transaction.

# **Unibus Operation Concepts**

Three concepts must be understood about the operation of the Unibus.

- A device that has been designated as next bus master can turn the arbitrator on or off. The bus master asserts SACK to turn the arbitrator off; no further arbitration takes place. The master negates SACK to turn the arbitrator back on.

- A bus master controls the data section of the bus. No other device may control this section until the master releases it. The master asserts BBSY to prohibit any other device (with the exception of the designated slave) from using the data section of the bus.

- 3. Priority arbitration and data transfer may be executed simultaneously on the Unibus. This is shown in Figure 1-11. Device N requests the use of the data section of the bus. A device may do this at any time. No action is taken on this request until device N-1, the current bus master, releases the arbitrator. When this is done, if no requests of a priority level higher than that of device N are pending, device N is selected as next master. At this time, device N controls the arbitrator and device N-1 still controls the data section of the bus.

The arbitration sequence begins at the release of the arbitrator by device N-1 and ends with the selection of device N as next bus master. The arbitration sequence can take place while the data transfer by device N-1 is being executed.

Device N-1 releases the data section of the bus when its data transfer is complete. Device N then becomes bus master and starts its own data transfer. Device N now controls both the arbitrator and the data section of the bus.

### NOTE

To ensure optimal operation of the Unibus, the next master should be selected before the current master releases the data section. The current master should release the arbitrator before it releases the data section. Typically the bus master releases the arbitrator just before its last data transfer. The

DATA SECTION DEVICE ARBITRATOR DEVICE DEVICE N OF UNIBUS N - 1 N+1 **DEVICE N-1 USING DATA** SECTION REQUEST USE OF DATA SECTION RELEASE OF ARBITRATOR AND SELECT N RELEASE OF AS NEXT DATA SECTION MASTER AND TIME-NO SCALE DEVICE N USING DATA SECTION REQUEST OF DATA SECTION RELEASE OF ARBITRATOR AND SELECT N+1 BELEASE OF AS NEXT DATA SECTION MASTER DEVICE N+1 USING DATA SECTION

arbitrator waits 75 ns then resumes arbitration.

Figure 1-11 Arbitrator Request Sequence

# **Priority Protocol**

The use of the data section of the bus is granted to requesting devices in accordance with the priority assigned to each one. The priority of a device on the Unibus is determined by two factors: (1) the priority level assigned to the device, and (2) its electrical position on the bus with respect to other devices of the same priority level.

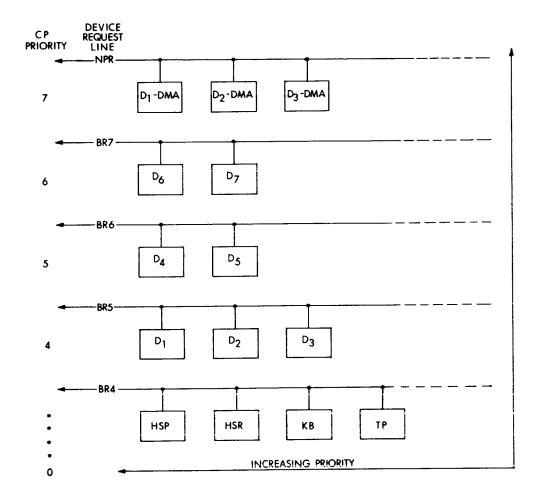

Bus Device Priority Levels—Five priority levels are available for assignment to all bus devices capable of becoming bus master, with the exception of the interrupt fielding processor. These levels in descending order are:

NPR Level 7 Level 6 Level 5 Level 4

The PDP-11/15 processor has only two priority levels: NPR and BR. An option (KF11) allows this processor to use all four BR priority levels.

Five bus request lines correspond to these priority levels: NPR, BR7, BR6, BR5, and BR4. These are type 1 signal lines. A device that requires the use of the data section of the bus asserts a request on one of these lines. This request is received by the arbitrator.

A device may be assigned to more than one priority level. A typical combination is a device which uses NPR to transfer data and a BR to interrupt the processor at the end of a data block.

Interrupt Fielding Processor CPU Priority Levels—The arbitrator monitors the priority state of the CPU. The CPU program execution priority (PRI) varies from 0 to 7. Five of these levels are relevant to the arbitration process.

```

PRI 7 (highest CPU priority level)

PRI 6

PRI 5

PRI 4

PRI <4 (below 4)

```

**Grant**—A grant signal informs a requesting device that it may become bus master after the current master releases the data section of the bus. The following two rules apply.

- An NPR has the highest priority, assert NPG (non-processor grant). (A controller may do DMA transfers at any time.)

- 2. Whenever the CPU is between instructions (interruptable), the arbitrator may issue a grant at the level of the highest bus request if the CPU PRI level is not equal to or higher. The order of priorities is as follows and is shown in Figure 1-12.

| Bus Request<br>Priority Level | CPU<br>Priority Level | Bus<br>Grant |

|-------------------------------|-----------------------|--------------|

| NPR (Highest)                 |                       | NPG          |

| BR7                           | PRI 7                 | BG7          |

| BR6                           | PRI 6                 | BG6          |

| BR5                           | PRI 5                 | BG5          |

| BR4                           | PRI 4                 | BG4          |

|                               | PRI <4 (lowest)       |              |

|                               |                       |              |

Figure 1-12 Priority Structure for Issuing Grants

### Example 1:

If the CPU is operating under its highest program execution priority (PRI 7) the only grant that can be issued is an NPG in response to an NPR. A controller may do DMA transfers at any time.

### Example 2:

If the CPU is operating at PRI 6 and a BR6 bus request is received, ignore that request. The processor is operating at an equal to or higher priority level.

#### NOTES

No other grant (BG or NPG) may be issued by the arbitrator while a BG is asserted.

PDP-11/15 and PDP-11/20 data transfers occur prior to NPR or BR service.

Assertion—The arbitrator asserts the grant. The first device on the bus assigned to the same priority level as the grant receives this grant. If this device is requesting the use of the data section of

the bus at that level, it acknowledges receipt of the grant by asserting SACK and blocks the grant. If the device is not requesting the use of the data section, it passes the grant on to the next device of the same priority level. This procedure is repeated until a device accepts the grant or until the end of the bus is reached. In this last case, the grant is cancelled. This cancellation is affected by either a "NO SACK TIMEOUT" circuit in the arbitrator or by a "SACK TURNAROUND" bus terminator at the far end of the bus.

**Negation**—A grant is cancelled when it reaches the end of the bus without being acknowledged.

If a device asserts a request then negates it before receiving a grant, the grant is cancelled by the arbitrator. This is only possible if no other device at the same priority level accepts the grant.

A program may enable and then disable a request, thus cancelling the grant. A hardware interface that does not latch a request may lose the request and unintentionally cancel the grant. These two methods of cancelling a grant are not recommended as they slow down the Unibus operation.

Priority Structure Rules—The following rules define the Unibus priority structure.

- 1. The priority of a device on the Unibus is determined by two factors: (1) the priority level assigned to the device, and (2) its electrical position relative to the other devices of same priority level on the bus.

- The priority level assigned to a device is the primary factor in determining whether or not this device obtains the use of the bus.

- 3. No device may use the bus until it has received a grant issued by the arbitrator.

- 4. A grant is issued only to the highest priority level request line that is asserting a request for the use of the bus. Only the devices at the priority level of this grant may obtain the use of the bus.

- 5. The requesting device electrically closest to the arbitrator on the specific grant line (NPG, BG7, BG6, BG5, or BG4) accepts, acknowledges, and blocks the grant, thus preventing the other devices on the grant line from using the grant signal. Electrical position is the secondary factor in determining the priority of a device.

- The arbitrator does not know which devices are requesting grants, nor their physical position on the bus. The five request lines may be asserted by more than one device on each line at the same time.

- 7. The arbitrator does not know which of the devices at the level at which a grant is issued is using this grant, nor the physical position of this device on the bus.

- 8. In order to receive grants, all devices capable of becoming bus master must be physically located on the same side of the arbitrator on the bus. These devices must be able to receive and retransmit grants at their priority level.

**Priority Arbitration Example**—In Figure 1-13, devices A through E are assigned to priority levels as follows.

| Device | Priority Level        |

|--------|-----------------------|

| Α      | Level 6               |

| В      | Level 4               |

| С      | Level 5               |

| D      | Level NPR and Level 5 |

| E      | Level 5               |

Their physical position on the bus is as shown in Figure 1-13. Device A is closest to the arbitrator. The effective priority order of devices A through E is as follows.

| Priority Order by Device | Priority Level |

|--------------------------|----------------|

| D (highest)              | NPR            |

| A                        | 6              |

| C                        | 5, 1st in line |

| D                        | 5, 2nd in line |

| E                        | 5, 3rd in line |

| B (lowest)               | 4              |

| ,                        | NOTE           |

Device D has the highest priority at its NPR level, but it is fourth at its level 5. Device B is in the second physical position on the bus, but it has the lowest priority.

Figure 1-13 Priority Arbitration Example

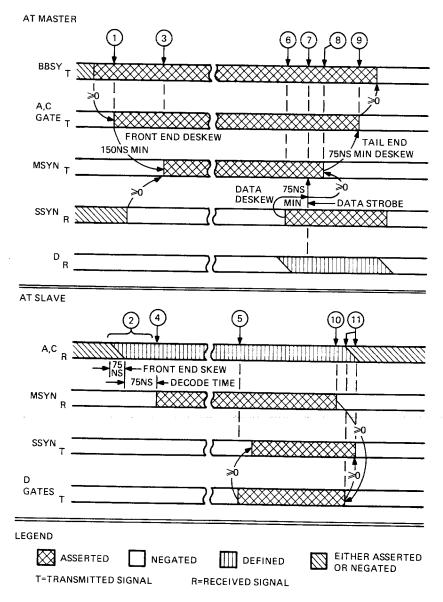

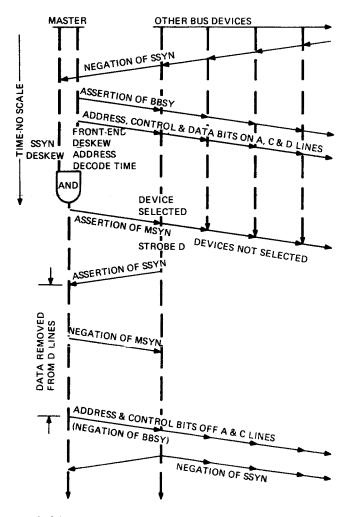

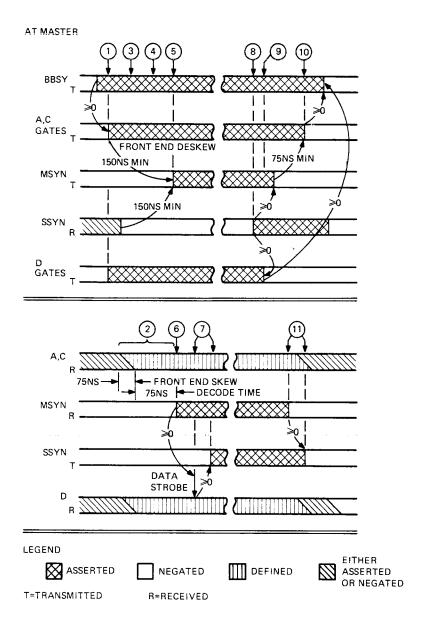

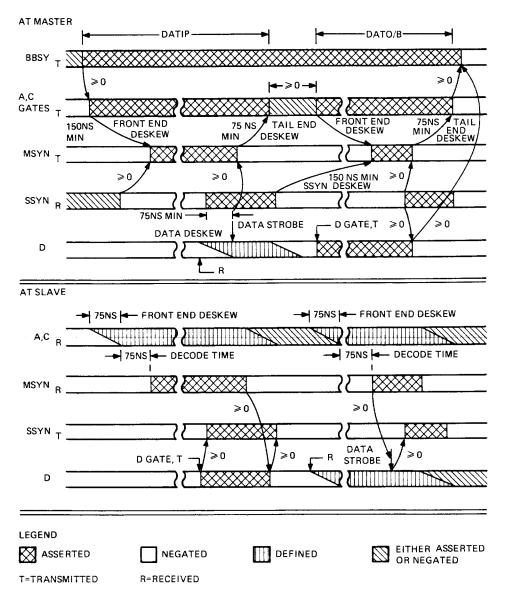

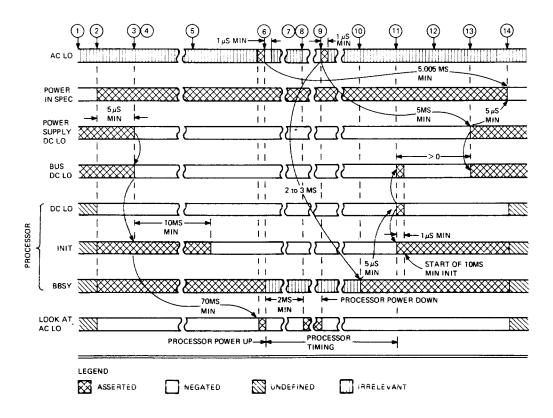

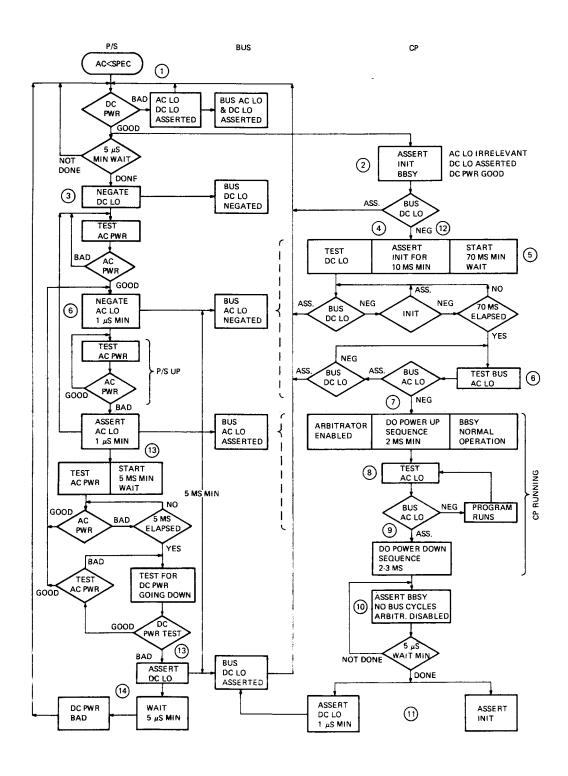

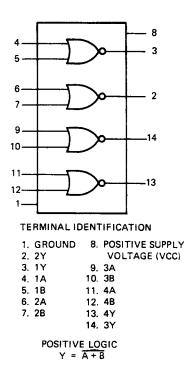

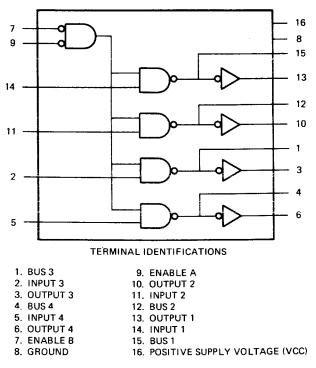

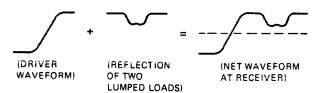

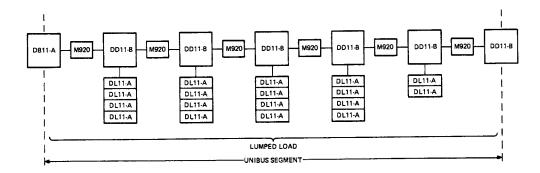

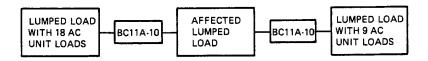

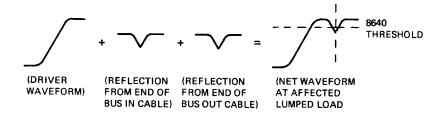

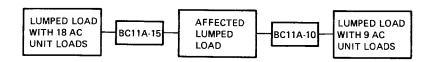

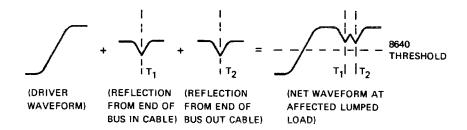

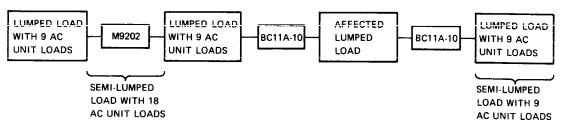

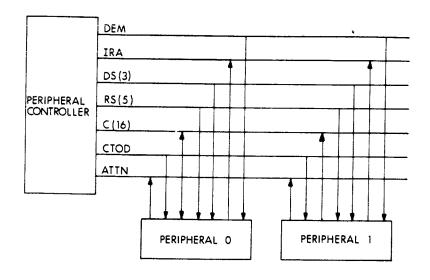

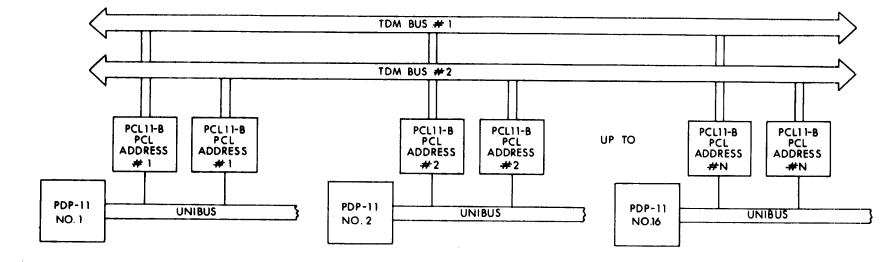

**Priority Arbitration Transactions**—The priority arbitration of the Unibus is directly affected by the priority state of the CPU. The CPU priority (PRI) can range from 0 to 7. The arbitrator grants use of the bus to non-CPU devices by the following rules.