| +  |   | -+- |   | -+- |   | -+- |   | -+- |   | -+             |   | -+- |   | -+ | TM |

|----|---|-----|---|-----|---|-----|---|-----|---|----------------|---|-----|---|----|----|

|    |   | 1   |   | 1   |   |     |   |     |   |                |   | -   |   | 1  |    |

|    | d | -   | i |     | g |     | i | 1   | t | 1              | a | 1   | 1 | l  |    |

| İ  |   | 1   |   | 1   | - | 1   |   | Ì   |   | į              |   | Ĺ   |   | İ. |    |

| +- |   | •+• |   | -+- |   | -+- |   | -+- |   | - <del>.</del> |   | -+- |   | -+ |    |

TO: APECS Spec. distribution

INTEROFFICE MEMORANDUM INTERNAL USE ONLY

FROM: Sam Nadkarni DATE: 5 November 1993

DEPT: SEG/HPC LOC: HLO2-3/C12 DTN: 225-7162

ENET: RICKS::Nadkarni

SUBJECT: APECS Datasheets are available.

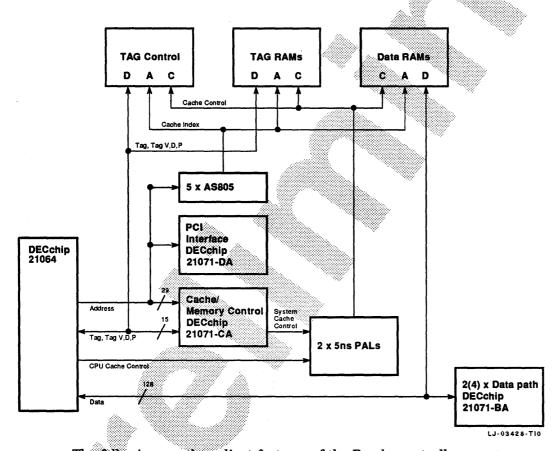

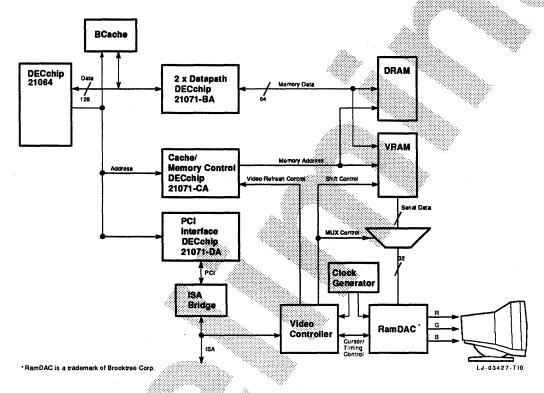

The latest APECS specification is available and will be mailed to all of you by interoffice mail. The specification represents functionality corresponding to the second pass of the chip set. This document is different from the previous revision of the APECS specification (rev 1.1) in that it is a data sheet for the chip set which will be used for internal and external customers. The names of the chip set (APECS) and the chips (COmanche, Decade, Epic) are not used in this document, instead the respective external DECchip numbers. The correspondence between the internal names and the numbers is given below:

APECS chip set, 64-bit memory - DECchip 21071-AA

APECS chip set, 128-bit memory - DECchip 21072-AA

Decade chip - DECchip 21071-BA

Comanche chip - DECchip 21071-CA

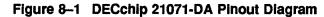

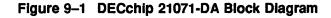

Epic chip - DECchip 21071-DA

Along with the data sheet you will be receiving the following documents:

- 1. Major software and Hardware differences between pass1 and pass2.

- List of pass1 bugs and their workarounds.

- Pass2 specification erata or additions.

- 4. Two clock specification sheets showing internal skew requirements on a per-chip basis.

List of Major Differences between pass1 and pass2

Rev 0.0

11/5/93

Because the Data Sheet was written for pass2 of the 21071-AA and 21072-AA, the following list has been compiled to point out the most important differences between pass2 and pass1 for those customers using pass1 parts.

### 21071-BA response to itself on PCI

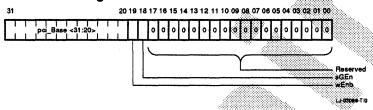

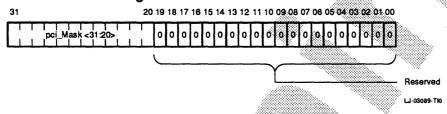

In pass1, the 21071-BA PCI Base Register has the requirement that the PCI Window Address MUST NOT be programmed such that a CPU initiated transaction from the 21071-BA gets mapped back into system memory by hitting in the PCI\_BASE. In pass2, this restriction has been removed as the 21071-BA chip will never respond to the PCI addresses it drives out on the bus.

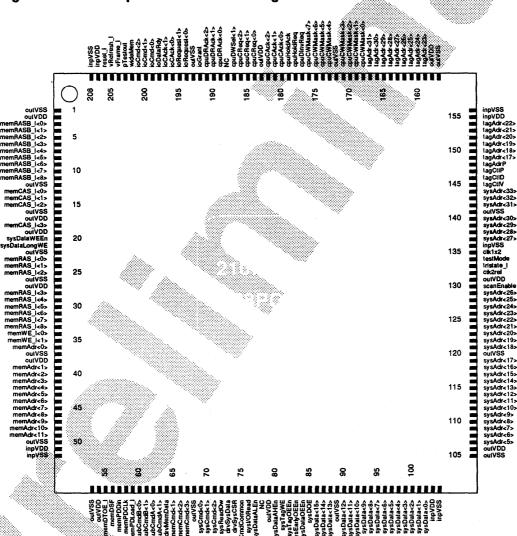

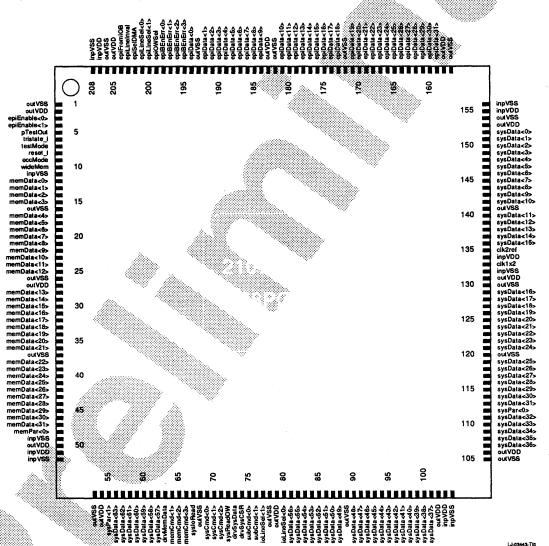

### 2. 21071-CA pinout changes

|     |     | Pass1                | Pass2         |

|-----|-----|----------------------|---------------|

|     |     |                      |               |

|     |     |                      |               |

| PIN | 19  | MEMCASL 4            | OUTVDD        |

| PIN | 20  | MEMCASL 5            | SYSDATAWEEN   |

| PIN | 21  | MEMCASL 6            | SYSDATALONGWE |

| PIN | 22  | MEMCASL <sup>7</sup> | OUTVSS        |

| PIN | 72  | IODATARDY 0          | SYSREADOW     |

| PIN | 77  | SYSDATAAEN 4         | SYSDATAALEN   |

| PIN | 80  | SYSCACWR -           | SYSDATAAHEN   |

| PIN | 81  | SYSWEEN              | SYSTAGWE      |

| PIN | 198 | IODATARDY_1          | IODATARDY     |

To correspond with the IODATARDY\_0 change for the 21071-CA, the 21071-BA changed the name of its IODATARDY pin to SYSREADOW. Note that this is a name change only.

### 3. CSR Differences Between Pass1 and Pass2.

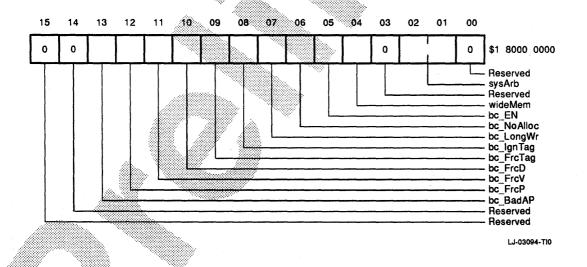

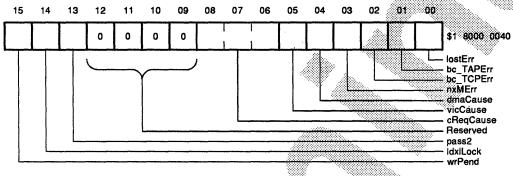

21071-CA Error and Diagnostic Status Register - EDSR<13> specifies which version of the chip you have. In pass1, EDSR<13> reads as a zero and in pass2, EDSR<13> reads as a one.

21071-CA General Control Register - GCR<13> is an unused bit in pass1 and forces bad Tag address parity in pass2.

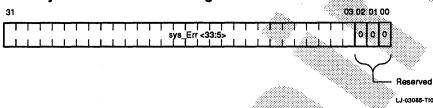

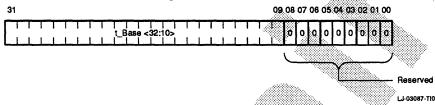

21071-BA Diagnostic Control and Status Register - DCSR<31> specifies which version of the chip you have. In pass1, DCSR<31> reads as a zero and in pass2, DCSR<31> reads as a one.

### 4. 21071-CA Bcache Pal Interface and Equations

In pass2 the Bcache control logic consists of one OEPAL and one WEPAL. Pass1 requires three PALS for Bcache control logic. The three Pals consist of the OEPAL and two WEPALS. The following equations should be used for the three Pass1 Bcache Pal Equations on Pass1 EB64+ modules. (Note that the OEPAL equations are identical between pass1 and pass2.)

```

MODULE

OEPAL

TITLE

'EB64+ Evaluation Board Bcache Output Enable Pal'

**

DATE

AUTH REV

COMMENTS

**

11

2-Feb-93 DDD 0.0 INITIAL IMPLEMENTATION

.1 ADDED WE AND DATAA<4> FUNCTIONS

12-Feb-93 DDD

11

06-May-93 DDD

.2 Change DCOK to SENSE DIS (note polarity)

03-Sep-93 WPS 1.2 Prepared for publication

OEPAL

DEVICE 'P16L8';

DECLARATIONS

"=========

INPUTS -

PIN 1;

sysEarlyOEEn

PIN 2;

sysTaqOEEn

PIN 3;

sysDataOEEn

cpuDataCEOE

PIN 4;

PIN 5;

sysDOE

cpuTagCEOE

PIN 6;

PIN 7;

cpuCReq2

PIN 8;

cpuCReq1

PIN 9;

cpuCReq0

" GND

PIN 10;

PIN 11;

senseDis

" VCC

PIN 20;

OUTPUTS -

!bcTagCEOE

PIN 12 ISTYPE 'Com, Invert';

PIN 13 ISTYPE 'Com, Invert';

!Pin13

PIN 14 ISTYPE 'Com, Invert';

!Pin14

!bcDataCEOE0 PIN 15 ISTYPE 'Com, Invert'; !bcDataCEOE1 PIN 16 ISTYPE 'Com, Invert'; !bcDataCEOE2 PIN 17 ISTYPE 'Com, Invert'; !bcDataCEOE3 PIN 18 ISTYPE 'Com, Invert'; !cpuDOE PIN 19 ISTYPE 'Com, Invert';

" 4 copies

EQUATIONS

Tag and Data Output Enables

bcTagCEOE =

(sysEarlyOEEn & cpuCReq0

# sysEarlyOEEn & cpuCReq1

# sysEarlyOEEn & cpuCReq2

# cpuTagCEOE

# sysTagOEEn );

bcTagCEOE.OE = ((1));

bcDataCEOE0 =

(sysEarlyOEEn & !cpuCReq2 & cpuCReq1

# sysEarlyOEEn & cpuCReq2 & !cpuCReq0

# sysEarlyOEEn & !cpuCReq2 & cpuCReq0

# cpuDataCEOE

# sysDataOEEn );

bcDataCEOE0.OE = ((1));

bcDataCEOE1 =

(sysEarlyOEEn & !cpuCReq2 & cpuCReq1

# sysEarlyOEEn & cpuCReq2 & !cpuCReq0

```

```

# sysmarryomen & :cpuckedz & opuckedo

# cpuDataCEOE

# sysDataOEEn );

bcDataCEOE1.OE = ((1));

bcDataCEOE2 =

(sysEarlyOEEn & !cpuCReq2 & cpuCReq1

# sysEarlyOEEn & cpuCReq2 & !cpuCReq0

# sysEarlyOEEn & !cpuCReq2 & cpuCReq0

# cpuDataCEOE

# sysDataOEEn );

bcDataCEOE2.OE = ((1));

bcDataCEOE3 =

(sysEarlyOEEn & !cpuCReq2 & cpuCReq1

# sysEarlyOEEn & cpuCReq2 & !cpuCReq0

# sysEarlyOEEn & !cpuCReq2 & cpuCReq0

# cpuDataCEOE

# sysDataOEEn );

bcDataCEOE3.OE = ((1));

" CPU Output Enable, must be tristated when 3.3V is not stable.

(sysEarlyOEEn & cpuCReq2 & cpuCReq0

cpuDOE =

# sysDOE );

cpuDOE.OE = !senseDis;

Spares

Pin13 = (0);

Pin13.OE = ((0));

Pin14 = (0);

Pin14.OE = ((0));

END

```

```

MODULE wepalckl

'EB64+ Evaluation Board bcache Write Enable PAL, Uses CLK1'

TITLE

**

DATE

AUTH REV COMMENTS

11

____

___

------

**

2-FEB-93 DDD 0.0 INITIAL IMPLEMENTATION

.1 ADDED WE AND DATAA<4> FUNCTIONS

.2 Change DCOK to SENSE_DIS (note polarity)

**

12-FEB-93 DDD

06-May-93 DDD

**

01-Sep-93 DDD CK1 Created from WEPAL.ABL, but uses clk1 not clk1x2

wepal

DEVICE 'P16L8';

DECLARATIONS

"------

" INPUTS -

clk1

PIN 1;

clk2

PIN 2;

PIN 3;

sysWEEn

cpuTagCtlWE

PIN 4;

PIN 5;

sysCacWr

cpuDataWE1

PIN 6;

PIN 7;

cpuDataWE0

PIN 8;

sysDataAEn4

cpuDataA4

PIN 9;

" GND

PIN 10;

PIN 11;

longWr

PIN 20;

" VCC

OUTPUTS -

A ViewPLD bug requires active high outputs to be inverted in the EQUATIONS

PIN 14 ISTYPE 'Com, Invert';

!bcTagCtlWE

!bcTagAdrWE

PIN 13 ISTYPE 'Com, Invert';

PIN 15 ISTYPE 'Com, Invert';

!bcDataWE1

PIN 16 ISTYPE 'Com, Invert';

!bcDataWE0

bcDataA4 1

PIN 12 ISTYPE 'Com, Invert';

bcDataA4 0

PIN 19 ISTYPE 'Com, Invert';

!palWRLat

PIN 17 ISTYPE 'Com, Invert';

!palRDLat

PIN 18 ISTYPE 'Com, Invert';

" DataA4 Macros, these terms appear in both dataA4's, palWRLat and palRDLat

RdEqn MACRO {

( (palRDLat & clk1)

# (palRDLat & clk2)

# (sysDataAEn4 & !clk1 & !clk2) )

WrEqn MACRO {

( (palWRLat & !clk2)

# (palRDLat & clk2) )

```

<sup>&</sup>quot; WE Macros, this produces a write pulse with proper timing " This is the basis of the 4 other write enables

```

WEEqn MACRO {

( (!clk1 & sysWEEn & clk2 )

# (!clk1 & bcTagAdrWE )

(!clk2 & bcTagAdrWE & longWr) )

EQUATIONS

" Cache Data Write Enables

" The cpu provides four different wires, one per copy

bcDataWE1 =

(WEEqn & sysCacWr )

# cpuDataWE1;

bcDataWE1.OE = ((1));

bcDataWE0 =

(WEEqn & sysCacWr )

# cpuDataWE0;

bcDataWE0.OE = ((1));

" Cache Tag Control and Address Write Enables

" The CPU cannot write the address cache ram

bcTaqAdrWE =

(WEEqn);

bcTagAdrWE.OE = ((1));

bcTagCtlWE =

(WEEqn)

# cpuTagCtlWE;

bcTagCtlWE.OE = ((1));

" Cache Address Bit 4

" These are 4 identical copies

bcDataA4 1 =

(RdEqn & !sysCacWr)

# (WrEqn & sysCacWr)

# cpuDataA4;

bcDataA4 1.OE = ((1));

bcDataA4 0 =

(RdEqn & !sysCacWr)

# (WrEqn & sysCacWr)

# cpuDataA4;

bcDataA4 \ 0.OE = ((1));

" Feedback terms.

" These are internal feedbacks used to generate dataA4

palRDLat = RdEqn;

palRDLat.OE = ((1));

palWRLat =

WrEqn;

palWRLat.OE = ((1));

```

**END**

List of pass1 bugs and their workarounds

Rev 0.1 11/4/93

The following is a list of pass1 21071-AA and 21072-AA chipset bugs that need workarounds for the system to work successfully. The workarounds are described below the issue. Some are Hardware work arounds and some are software workarounds. Some of these bugs will be fixed in pass2 so these workarounds are only temporary.

1. 21071-DA Masked DMA Write Causes Unmasked Write to Memory - Fixed in p2

21071-DA has a bug with DMA Writes where a 7 longword PCI burst that starts on a cache-line boundary will cause the 8th longword to be corrupted in memory. This bug is present because 21071-DA incorrectly does an unmasked DMA Write on the SysBus instead of a masked write.

Software Workaround:

a DMA Write to 21071-DA never ends with a PCI burst of 7 longwords. One method to insure this would be to have software check the ending address of all DMA transfers to memory. If the address ends on anything other than an aligned cacheline boundary, the last longwords of data can be transferred using single longword PCI bursts. This would guarantee that the DMA transfer never ends with a 7 longword PCI burst.

Software must provide a mechanism to guarantee that

2. 21071-DA CSR write followed by a MB could result in DMA

Scatter Gather PTE fetch Data being corrupted. - Fixed in P2

When an 21071-DA CSR Write is followed immediately by an MB instruction, there is a possibility that a DMA Scatter Gather PTE fetch could be transferred from the 21071-BA to the 21071-DA incorrectly

The problem is caused by the internal DMA Read Bypass mux switching incorrectly. This results in 21071-DA using the wrong LW pointer bits to transfer the data from 21071-BA to 21071-DA on the epiData bus.

Software Workaround: During DMA operations, any 21071-DA CSR writes must be followed by a 21071-DA CSR read to the same address to insure 21071-DA CSR writes are never followed immediately by an MB. Since the TBIA register is the only register that software should be writing to in the 21071-DA in the presence of DMA (in the absence of errors), a TBIA write should be followed by a read of that same TBIA CSR address. Data returned from this write-only register is garbage.

3. DCache not invalidated on no-BCache systems - Fixed in P2

On NO-Bcache systems (or systems with the BCache off) the following situation will cause the CPU's internal Dcache to become incoherrent. The EV4 reads a memory location into its cache. The 21071-DA then writes that location. Because the DMA Write does not hit in the BCache, the 21071-CA will not invalidate the CPU's Dcache line. The EV4 now has the stale version of the data, not the new DMA

Hardware Workaround:

If you don't have a Bcache or if you are doing DMA with the Bcache off and Dcache on, tie the 21071-CA's sysDataA4 pin to the 21064's

dInvReq pin.

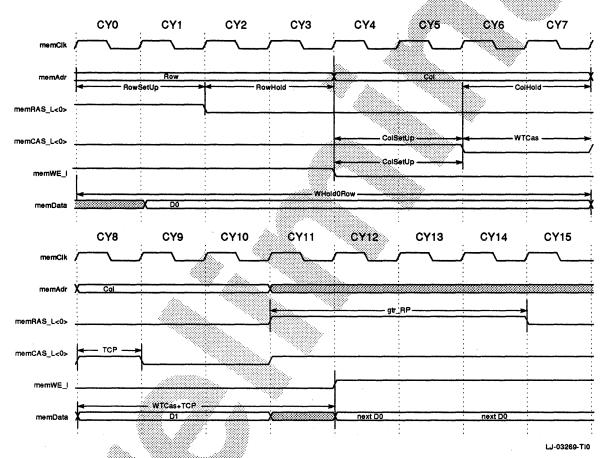

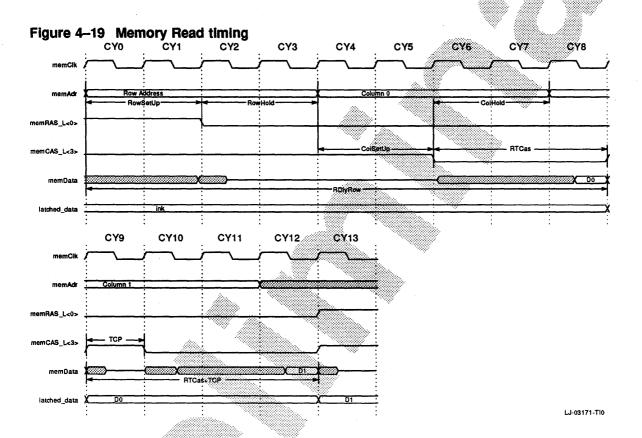

4. 21071-CA spec change for RAS Precharge Bug

- NOT Fixed in P2

With the fastest allowed timing values, an entire octaword write or serial register transfer can fit in a ras precharge interval if the precharge interval is programmed to a large value.

Software Workaround:

Because there is one Ras Precharge counter for all memory banks, the system designer must insure that the RAS precharge time is longer than the minimum possible time between the assertion of RAS and the assertion of a different RAS.

This can be ensured by meeting the following rules for the programmed value of RAS precharge.

(all values in the equation below are programmed values, not desired values)

GTR RP <= ROWHOLD + COLSETUP + WTCAS + 4 GTR RP <= ROWHOLD + COLSETUP + RTCAS + 4

This equation has to be met for all timing bank programmings.

5. Configuration Write Data may get corrupted - Fixed in P2

If the 21071-DA loses its grant on the PCI in the first cycle of the address (21071-DA does address stepping on configuration transactions i.e. address is driven on the bus for one cycle prior to assertion of FRAMEL), the configuration write data gets corrupted.

Old behavior:

cy 1 **cy2** DA gnt DA gnt DA gnt

removed

addr1 bus High Z addr1 addr2 bad data framel

DA Req DA Req DA Req DA Req DA Req

Hardware workaround: In the PCI arbiter.

Solution 1: Make the 21071-DA the highest priority

Solution 2: When the PCI is granted to the 21071-DA, the arbiter should not take away the grant from the 21071-DA if it has a request asserted, even if the 21071-DA has not asserted FRAME1.

e.g. In the example shown above the arbiter would

sample the DA\_keq in cycle  $\sigma$  and decide not to take away the grant from the 21071-DA in cycle 1.

Suggested new behavior

g

cy 0 cy 1 cy 2 cy 3

DA\_gnt DA\_gnt

addr1 addr2 good data

framel

DA\_Req DA\_Req

6. 21071-CA Video Support - Fixed in P2

21071-CA Video functionality was not verified for pass1 and has a number of bugs which will prohibit it from working correctly. Memory read and write accesses to Bank8 are bug free.

7. 21071-DA Error Logging - Fixed in P2

21071-DA Error detection and reporting was not fully verified for passl and has a number of bugs which will prohibit it from working correctly. Software should not depend on 21071-DA Error handling and error handling

code should not be developed with pass1 APECS parts.

Changes/additions to the DECchip 21071-AA /21072-AA Chipset Datasheet

- pg 3-24: Table 3-7, Row and Column Address decode for BankSet 8

10,10 Row ID bits are not supported. Only 9,9 and 9,8 RAMs are supported by the 21071-CA.

- 2. pg 3-26: 3.2.4.2, 3.2.5

Read Decision Pending (RDP) has been removed.

Wait After Read (WAR) condition takes effect after any Read, CPU or DMA.

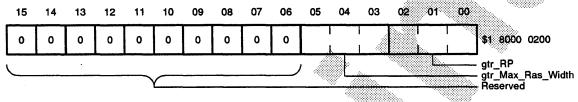

3. pg 4-24: Add New equations for GTR RP.

(all values in the equation below are programmed values, not desired values)

```

GTR_RP <= ROWHOLD + COLSETUP + WTCAS + 4

GTR_RP <= ROWHOLD + COLSETUP + RTCAS + 4

```

This equation has to be met for all timing bank programmings.

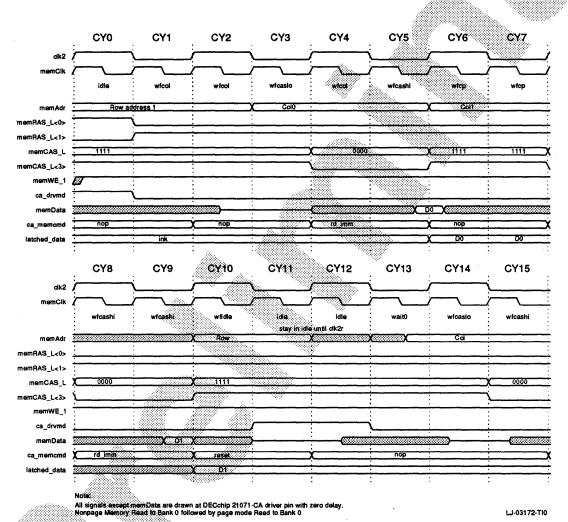

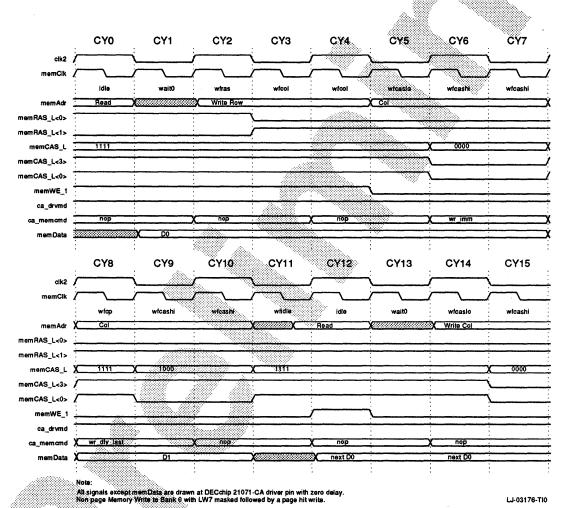

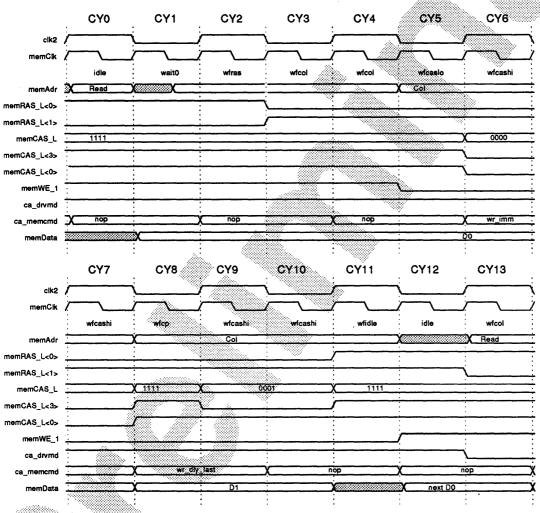

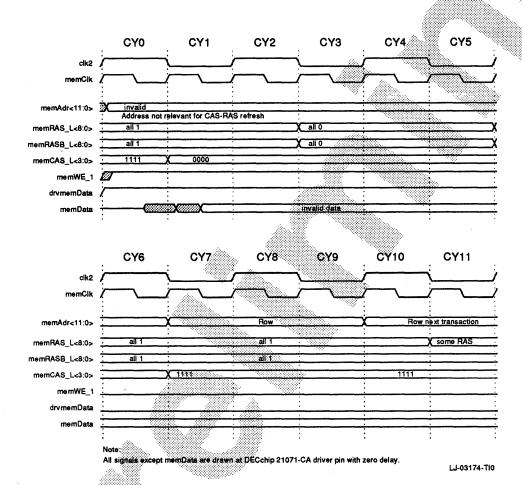

For the example timing shown ion Fig. 4-18 and Fig 4-19,  $GTR\_RP$  cannot be programmed > 7 cycles.

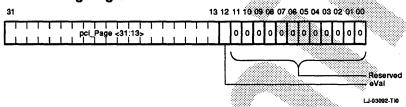

4. pg 10-11: PCI Configuration Space Address Translation changed

The type of the access is determined by two register bits in the host bridge. If these bits are 00, the access is a type 0 access, if these bits are 01, the access is a type 1 access. 10 and 11 are reserved values.

The translation of the rest of the address depends on the access type and is shown below.

### Programmed Address:

|       | 33<br>+                    | 29   | 28           |        | 21       | 20     | 16 | 15                  | 13      | 12                      | 7  | 6                              | 3      |          |

|-------|----------------------------|------|--------------|--------|----------|--------|----|---------------------|---------|-------------------------|----|--------------------------------|--------|----------|

|       | <br> Config<br>  Space<br> |      | <br> Bus<br> | :<br># |          | Device | #  | <br> Funct<br> <br> | ion     | <br> Registe<br>  #<br> | er | used<br> for<br> byte<br> enab | )<br>• |          |

| PCI . | Address                    | :    | /            | , , ,  | /<br>dec | code   | 11 | <br>                | 8       | <br> <br> <br><b>v</b>  | 2  | fr<br>v                        | com 1  | register |

|       | <br>  On:<br>              | ly ( | one '        | 1'     |          |        |    | <br> Funct<br>      | <br>ion | <br> Registe<br>  #<br> | er |                                |        |          |

| Device#<br>[2016]                                                                                                                                                                                                             | decoded value [3111]                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| 00000<br>00001<br>00010<br>00011<br>00100<br>00101<br>00110<br>00111<br>01000<br>01001<br>01011<br>01100<br>01111<br>10000<br>10010<br>10010<br>10011<br>10110<br>10111<br>11000<br>11011<br>11010<br>11011<br>11010<br>11011 | 0 0000 0000 0000 0000 0001<br>0 0000 0000 |  |

| 11110<br>11111                                                                                                                                                                                                                | 0 0000 0000 0000 0000 0000                |  |

## Type 1 Access Translation (access to remote PCI)

Programmed Address:

|     | 33<br>+                     | 29        | 28       | 2                        | 21   | 20<br>                        | 16 | 15                          | 13 | 12                       | 7 6          | 3                         | 3        |

|-----|-----------------------------|-----------|----------|--------------------------|------|-------------------------------|----|-----------------------------|----|--------------------------|--------------|---------------------------|----------|

|     | <br> Config<br>  Space<br>  | <br> <br> | <br> Bus | +                        |      | Device                        | #  | <br> Functi<br> <br>        | on | <br> Register<br>  #<br> | fo<br> by    | sed<br>or<br>vte<br>nable |          |

| PCI | Address:                    | : 24      | 123      | <br> <br> <br> <br> <br> | .61  | <br> <br> <br> <br> <br> <br> | 11 | <br> <br> <br> <br> <br> 10 | 8  | <br> <br> <br> <br>  7   | <br> <br>  v |                           | register |

|     | +<br> <br>  000000<br> <br> |           | <br> Bus |                          | <br> | Device                        |    |                             |    | <br> Register<br>  #     | <br>         | +<br>                     |          |

5. pg 9-8, pg 10-22 Parity Checking Disable added

Bit 3 of DCSR which was reserved will be used to disable parity checking on the PCI (DPEC bit). When the DPEC is set, PCI address and data parity errors are not detected by the 21071-DA. When DPEC is cleared, PCI address and data parity checking will be in effect.

6. pg 6-6, Table 6-4 pg 12-7, table 12-4 pg 17-7, Table 17-4, 17-5

All the AC specification numbers are pass1 numbers, and will change for pass2.

7. pg 6-3 section 6.3.1 pg 12-3 section 12.3.1 pg 17-3 section 17.3.1

All sections replaced with accompanying handouts

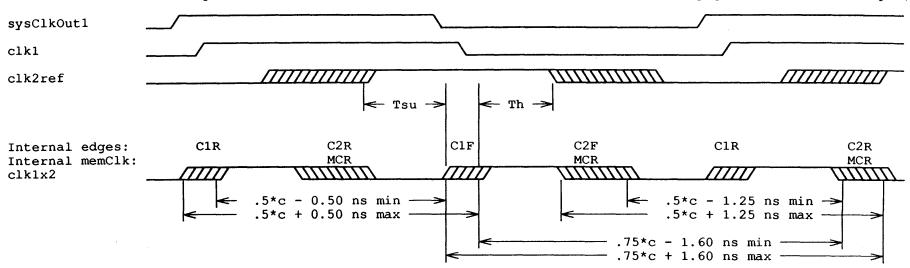

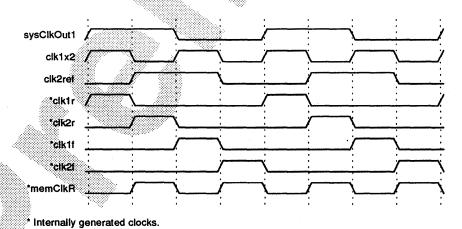

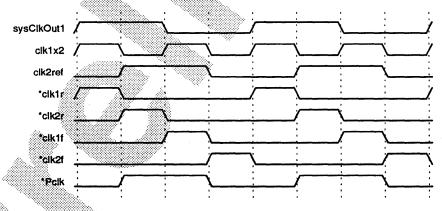

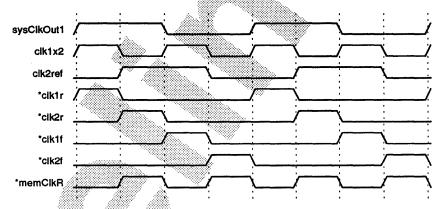

These are only the requirements to make the internal logic on a single chip function. There are no chip requirements specs for clkl or sysClkOutl. clkl is constrained by external paths to/from the PALs. The phase error between sysClkOutl and clklx2 is constrained by external paths to/from the CPU.

These numbers include 0.1 ns of skew due to the different input edge rates at the ASICs. The skew numbers are at 30.0 ns, if a larger cycle time is used these numbers may be increased as long as the minimum time between clocks is not violated.

| Parameter                        | Min Nom Max Uni  |               |          |       | Note   |        |           |  |  |

|----------------------------------|------------------|---------------|----------|-------|--------|--------|-----------|--|--|

| cycle time (c)                   | 30.0             | 30.0          | _        | ns    | -      |        |           |  |  |

| clk1x2 period                    | -                | 15.0          | _        | ns    | _      |        |           |  |  |

| clk1x2 duty cycle                | _                | 50.0          |          | 8     |        |        |           |  |  |

| clk1x2 rise time                 | _                | -             | 1.0      | ns    | _      |        |           |  |  |

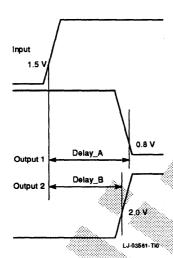

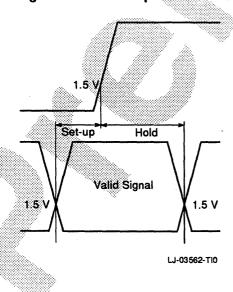

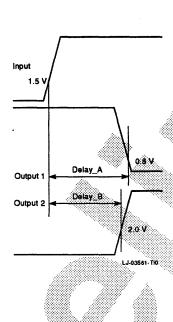

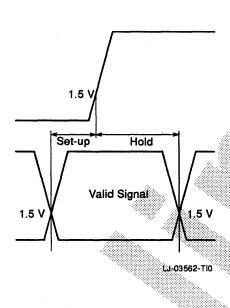

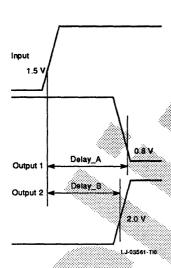

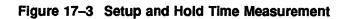

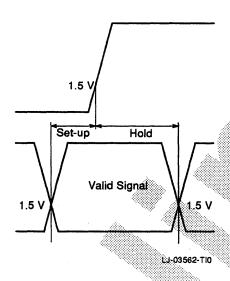

| clk2ref setup to clk1x2 rising   | 0.8              | -             | -        | ns    | Tsu in |        |           |  |  |

| clk2ref hold from clk1x2 rising  | 1.7              |               | _        | ns    | Th in  | Figure |           |  |  |

| •                                |                  |               |          |       |        |        |           |  |  |

| Parameter                        | Exampl           | e Transf      | ers      |       | Max    | Unit   | Note      |  |  |

| Rising to same clock rising      | C1R_C1<br>C1F_C1 | .R, C1R_C     | C1F, C1F | _C1R, | 0.50   | ns     | at c=30ns |  |  |

| Falling to same clock falling    | C2R_C2<br>C2F_C2 | R, C2R_C<br>F | C2F, C2F | _C2R, | 1.25   | ns     | at c=30ns |  |  |

| clk1x2 rising to clk1x2 falling, | C1R C2           | R, Clr C      | C2F,     |       |        |        |           |  |  |

|                                  | C1FC2            | R, C1F        | 2F,      |       | 1.60   | ns     | at c=30ns |  |  |

| clk1x2 falling to clk1x2 rising  |                  | R, $C2R$      |          |       |        |        |           |  |  |

|                                  | C2F C1           | R, $C2F$      | C1F      |       |        |        |           |  |  |

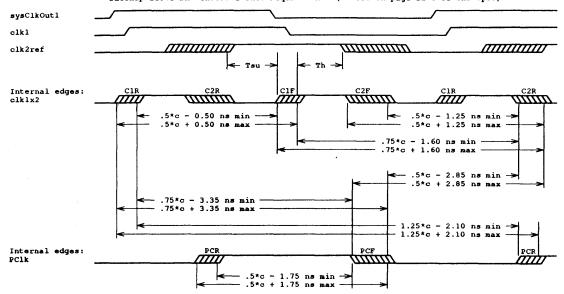

These are only the requirements to make the internal logic on a single chip function. There are no chip requirements specs for clk1 or sysClkOut1. clk1 is constrained by external paths to/from the PALs. The phase error between sysClkOut1 and clk1x2 is constrained by external paths to/from the CPU.

These numbers include 0.1 ns of skew due to the different input edge rates at the ASICs. The skew numbers are at 30.0 ns, if a larger cycle time is used these numbers may be increased as long as the minimum time between clocks is not violated.

| Parameter                        | Min    | Non      | Max     | Unit | Note   |        |           |

|----------------------------------|--------|----------|---------|------|--------|--------|-----------|

| cycle time (c)                   | 30.0   | 30.0     | _       | ns   |        |        |           |

| clk1x2 period                    | -      | 15.0     | -       | ns   | _      |        |           |

| clk1x2 duty cycle                | -      | 50.0     | -       | *    | -      |        |           |

| clklx2 rise time                 | -      | -        | 1.0     | ns   | -      |        |           |

| PClk period                      | -      | 30.0     | -       | ns   | -      |        |           |

| PClk duty cycle                  | -      | 50.0     | -       | *    |        |        |           |

| PClk rise time                   | -      | -        | 1.0     | ns   | -      |        |           |

| clk2ref setup to clk1x2 rising   | 0.8    | -        | -       | ns   | Tsu ir | Figure |           |

| clk2ref hold from clk1x2 rising  | 1.7    | -        | -       | ns   | Th in  | Figure |           |

| Parameter                        | Exampl | e Transf | ers     |      | Max    | Unit   | Note      |

| Rising to same clock rising      |        | R, C1R_C |         | C1R, | 0.50   | ns     | at c=30ns |

|                                  | C1F_C1 | F, PCR_P | CR      |      |        |        |           |

| Falling to same clock falling    | C2R C2 | R, C2R C | 2F, C2F | C2R, | 1.25   | ns     | at c=30ns |

|                                  | C2F_C2 | F, PCF_F | CF      | -    |        |        |           |

| clk1x2 rising to clk1x2 falling, |        | R, CIR_C |         |      |        |        |           |

|                                  |        | R, CIF_C |         |      | 1.60   | ns     | at c=30ns |

| clk1x2 falling to clk1x2 rising  |        | R, C2R C |         |      |        |        |           |

|                                  | C2F_C1 | R, C2F_C | :1F     |      |        |        |           |

| PClk rising to PClk falling,     | PCR_PC |          |         |      | 1.75   | ns     | at c=30ns |

| PClk falling to PClk rising      | PCF_PC | R        |         |      |        |        |           |

| clk1x2 rising to PClk rising,    | C1R PC | R, CIF F | CR,     |      | 2.10   | ns     | at c=30ns |

| PClk rising to clklx2 rising     | PCR_C1 | R, PCR_C | 1F      |      |        |        |           |

| clk1x2 falling to PClk falling,  |        | F, C2F_F |         |      | 2.85   | ns     | at c=30ns |

| PClk falling to clk1x2 falling   | PCF_C2 | R, PCF_C | 2F      |      |        |        |           |

| clk1x2 rising to PClk falling,   |        | F, ClF P |         |      | 3.35   | ns     | at c=30ns |

| clk1x2 falling to PClk rising,   |        | R, C2F P |         |      |        |        |           |

| PClk rising to clklx2 falling,   |        | R, PCR C |         |      |        |        |           |

| PClk falling to clk1x2 rising    | PCF C1 | R, PCF C | 1F      |      |        |        |           |

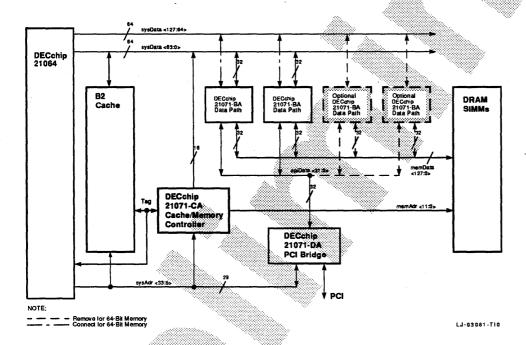

# DECchip 21071-AA and 21072-AA Chipsets

## **Data Sheet**

Order Number: EC-N0648-72

Revision/Update Information: This is a preliminary manual.

Digital Equipment Corporation Maynard, Massachusetts

#### First Edition, November 1993

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

This document is confidential and proprietary and is the property of Digital Equipment Corporation.

© Digital Equipment Corporation 1992, 1993. All Rights Reserved.

The following are trademarks of Digital Equipment Corporation: Alpha AXP, the AXP logo, DEC, DECchip, Digital, the DIGITAL logo, OpenVMS and VAX DOCUMENT.

This document was prepared using VAX DOCUMENT Version 2.1.

## Contents

| P | reface . |                                                | vii |

|---|----------|------------------------------------------------|-----|

| 1 | DECch    | ip 21071-AA and 21072-AA Chipset Overview      |     |

|   | 1.1      | DECchip 21071-AA and 21072-AA Chipset Features | 1–1 |

|   | 1.2      | System Overview                                | 1–3 |

|   | 1.2.1    | DECchip 21064 Microprocessor Chip              | 1-4 |

|   | 1.2.2    | Beache Data and Tag RAMs                       | 1-4 |

|   | 1.2.3    | Bcache Control PALs                            | 1–5 |

|   | 1.2.4    | Cache Address Buffer                           | 1–5 |

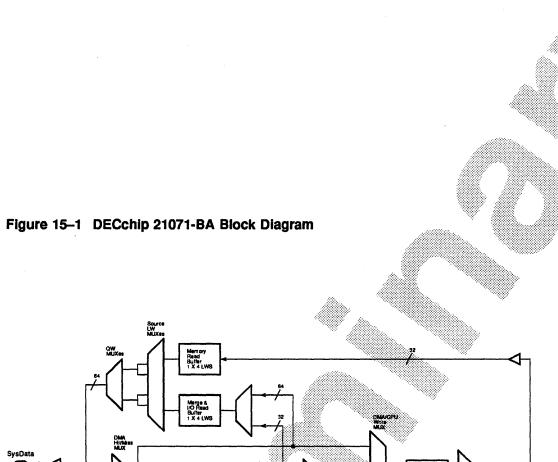

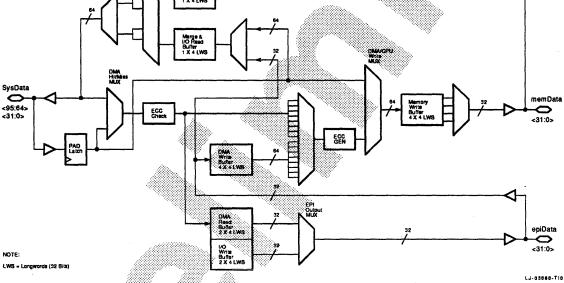

|   | 1.2.5    | DECchip 21071-BA                               | 1–5 |

|   | 1.2.6    | DECchip 21071-CA                               | 1–6 |

|   | 1.2.7    | DECchip 21071-DA                               | 1–6 |

|   | 1.2.8    | System Clock Generator                         | 1–7 |

|   | 1.2.9    | Serial ROM                                     | 1–8 |

|   | 1.2.10   | Interrupt Control/CPU Configuration PAL        | 1–8 |

|   | 1.2.11   | Memory SIMMs                                   | 1-8 |

|   | 1.2.12   | PCI Interrupt Controller                       | 1–8 |

|   | 1.2.13   | PCI Peripherals                                | 1–8 |

|   | 1.2.14   | PCI Arbiter                                    | 1–9 |

|   | 1.2.15   | System ROM                                     | 1_9 |

Part I

#### **DECchip 21071-CA Pin Descriptions** 2–1 2.1 DECchip 21071-CA Pin List...... 2.2 2-5 2.2.1 2-5 2.2.1.1 2-5 2-6 2.2.1.2 2.2.1.3 2-6 2-7 2.2.1.4 sysTagPar ...... sysTagCtlV..... 2-7 2.2.1.5 2.2.1.6 sysTagCtlD..... 2-7 2.2.1.7 2-7 2.2.1.8 2-7 2.2.1.9 2-8 2.2.1.10 2-9 2.2.1.11 2-9 2.2.1.12 2-10 2.2.1.13 cpuDInvReq ..... 2-11 2.2.1.14 2-11 cpuHoldReq ..... 2.2.1.15 cpuHoldAck ...... 2-11 2.2.2 2-11 2.2.2.1 sysEarlyOEEn ...... 2-11 2.2.2.2 sysTagOEEn....... 2-12 2.2.2.3 sysDataOEEn.... 2-12 2.2.2.4 2-13 2.2.2.5 sysDataAHEn ...... 2-13 2.2.2.6 sysTagWE ......... 2-13 2.2.2.7 sysDataWEEn ........ 2-14 2.2.2.8 sysDataLongWE..... 2-14 2.2.2.9 sysDOE ...,.... 2-14 PCI Bridge Interface Signal Descriptions..... 2.2.3 2-14 2.2.3.1 ioRequest<1:0>..... 2-14 2.2.3.2 ioGrant..... 2-15 2.2.3.3 2-16 2.2.3.4 ioCAck<1:0>..... 2-17 2.2.3.5 2-17 2.2.4 2-18 Data Path Control Signal Descriptions ...... 2.2.4.1 drvSysData ...... 2-18 2.2.4.2 2 - 182.2.4.3 drvMemData ...... 2 - 182.2.4.4 sysIORead ...... 2-19 2.2.4.5 sysReadOW ..... 2-19 2.2.4.6 subCmdA<1:0>, subCmdB<1:0>, subCmdCommon ..... 2-19

|          |          | * ** ** ** ** ** ** ** ** ** ** ** ** *           | 0.000,000 |

|----------|----------|---------------------------------------------------|-----------|

|          | 2.2.4.7  | sysCmd<2:0>                                       | 2-20      |

|          | 2.2.4.8  | memCmd<3:1>                                       | 2-22      |

|          | 2.2.5    | Memory Signal Descriptions                        | 2–23      |

|          | 2.2.5.1  | memAdr<11:0>                                      | 2-24      |

|          | 2.2.5.2  | memRAS_l<8:0>                                     | 2-24      |

|          | 2.2.5.3  | memRASB_l<8:0>                                    | 2-24      |

|          | 2.2.5.4  | memCAS_l<3:0>                                     | 2–24      |

|          | 2.2.5.5  | memWE_l<1:0>                                      | 2-25      |

|          | 2.2.5.6  | memPDClk                                          | 2-25      |

|          | 2.2.5.7  | memPDLoad_l                                       | 2-25      |

|          | 2.2.5.8  | memPDDIn                                          | 2-25      |

|          | 2.2.6    | Video Support Signal Descriptions                 | 2-26      |

|          | 2.2.6.1  | vFrame_l                                          | 2–26      |

|          | 2.2.6.2  | vRefresh_l                                        | 2–26      |

|          | 2.2.6.3  | memDTOE_l                                         | 2-26      |

|          | 2.2.6.4  | memDSF                                            | 2–27      |

|          | 2.2.7    | Miscellaneous Signal Descriptions                 | 2–27      |

|          | 2.2.7.1  | wideMem                                           | 2-27      |

|          | 2.2.7.2  | clk1x2                                            | 2–27      |

|          | 2.2.7.3  | clk2ref                                           | 2–27      |

|          | 2.2.7.4  | reset_1                                           | 2-27      |

|          | 2.2.7.5  | testMode testMode                                 | 2-28      |

|          | 2.2.7.6  | scanEnable                                        | 2–28      |

|          | 2.2.7.7  | tristate_l                                        | 2-28      |

|          | 2.2.7.8  | pTestout                                          | 2-28      |

|          | 2.3      | DECchip 21071-CA Pin Assignment                   | 2-28      |

|          | 2.3.1    | Signal Types                                      | 2–28      |

|          | 2.3.2    | DECchip 21071-CA Alphabetical Pin Assignment List | 2-29      |

|          | 2.3.3    | DECchip 21071-CA Numerical Pin Assignment List    | 2-34      |

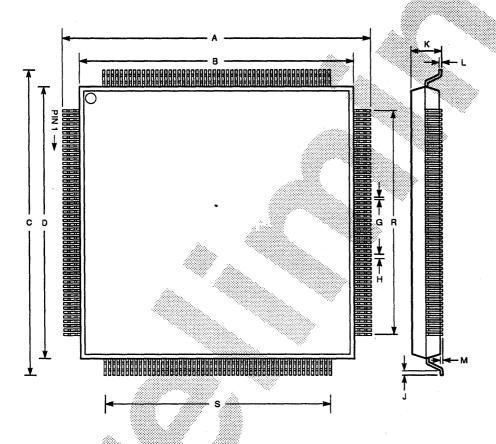

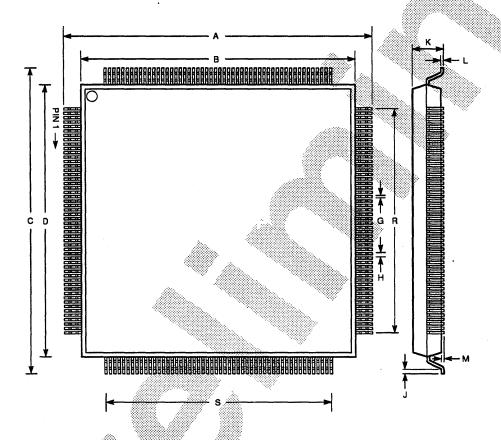

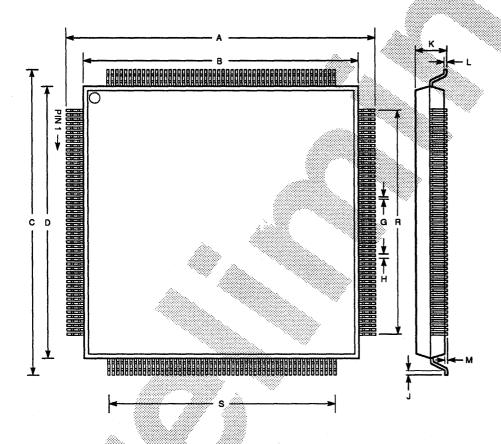

|          | 2.4      | DECchip 21071-CA Mechanical Specification         | 2–37      |

|          |          |                                                   |           |

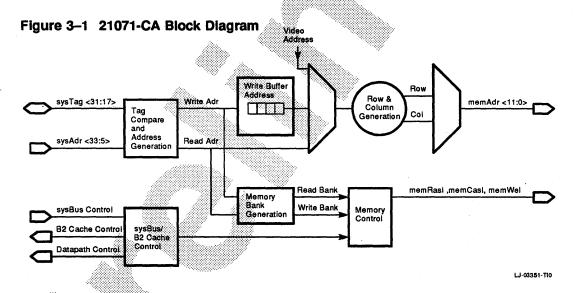

| ı        | )FCch    | ip 21071-CA Architecture Overview                 |           |

|          | 9808000. |                                                   |           |

|          | 3.1      | sysBus Interface Architecture                     | 3–1       |

|          | 3.1.1    | sysBus Arbitration                                | 3–2       |

|          | 3.1.1.1  | Arbitration CSRs                                  | 3–2       |

|          | 3.1.1.2  | DECchip 21071-DA Requests                         | 3–2       |

| 9<br>36. | 3.1.1.3  | Arbitration Cycles                                | 3–4       |

|          | 3.1.1.4  | Grant Mechanism                                   | 3–4       |

|          | 3.1.1.5  | Releases                                          | 3–5       |

|          |          |                                                   |           |

| 3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-17         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.2       Bankset0Bankset7       3-21         3.2.2.3       Bankset8       3-22         3.2.2.4       Supported Memory SIMMs       3-23         3.2.4       Performance Optimizations       3-25         3.2.4.1       Memory Page Mode Support       3-25         3.2.4.2       Read Latency Minimization       3-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.2.1<br>3.1.2.2<br>3.1.2.3<br>3.1.2.4<br>3.1.2.5<br>3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1 | Bcache Width, Size, and Speed Bcache Allocation Policy Bcache Write Granularity CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF | 3+7<br>3-8<br>3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 3.1.2.1   Bcache Width, Size, and Speed   3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.2.1<br>3.1.2.2<br>3.1.2.3<br>3.1.2.4<br>3.1.2.5<br>3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4            | Bcache Width, Size, and Speed Bcache Allocation Policy Bcache Write Granularity CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF | 3-8<br>3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10        |

| 3.1.2.2       Bcache Allocation Policy       3-8         3.1.2.3       Bcache Write Granularity       3-8         3.1.2.4       CPU-Initiated Bcache Operations       3-9         3.1.2.5       DMA-initiated Bcache Operations       3-9         3.1.2.6       External Logic Requirement       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.3       sysBus Controller       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000 0 FFFF       FFFF         FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 0 1 7FFF         FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000 0 1 9FFF FFFF         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Full Condition       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions <td>3.1.2.3<br/>3.1.2.4<br/>3.1.2.5<br/>3.1.2.6<br/>3.1.2.7<br/>3.1.2.8<br/>3.1.3<br/>3.1.3.1<br/>3.1.4<br/>3.1.4.1</td> <td>Bcache Allocation Policy Bcache Write Granularity CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF</td> <td>3-8<br/>3-9<br/>3-9<br/>3-9<br/>3-10<br/>3-10</td> | 3.1.2.3<br>3.1.2.4<br>3.1.2.5<br>3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                       | Bcache Allocation Policy Bcache Write Granularity CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                               | 3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10                       |

| 3.1.2.3       Bcache Write Granularity       3-8         3.1.2.4       CPU-Initiated Bcache Operations       3-8         3.1.2.5       DMA-initiated Bcache Operations       3-9         3.1.2.6       External Logic Requirement       3-9         3.1.2.7       Tag Compare Logic       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000 0 FFFF       FFFF         FFFFF       3-12         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 0 1 7FFF       FFFFF         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 0 1 7FFF       FFFFF         3.1.4.3       21071-CA CSR Space - 1 8000 0000 0 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Full Condition       3-13         3.1.6.2       Write Buffer Fountrol       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       CPU Transactions       3-15         3.1.8.1       CPU Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.1.2.4<br>3.1.2.5<br>3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                  | Bcache Write Granularity CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 . 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                      | 3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10               |

| 3.1.2.4       CPU-Initiated Bcache Operations       3-8         3.1.2.5       DMA-initiated Bcache Operations       3-9         3.1.2.6       External Logic Requirement       3-9         3.1.2.7       Tag Compare Logic       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000 0 FFFF         FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 0 1 7FFF         FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000 0 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Fdddress Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8       DMA Tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.1.2.5<br>3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                             | CPU-Initiated Bcache Operations DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                 | 3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10                      |

| 3.1.2.5       DMA-initiated Bcache Operations       3-9         3.1.2.6       External Logic Requirement       3-9         3.1.2.7       Tag Compare Logic       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.3.1       Wrapping       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000       0 FFFF         FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000       1 7FFF         FFFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000       1 9FFF FFFF         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Full Condition       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.8       DMA Transactions       3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                                        | DMA-initiated Bcache Operations External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                 | 3-9<br>3-9<br>3-10<br>3-10<br>3-10                             |

| 3.1.2.6       External Logic Requirement       3-9         3.1.2.7       Tag Compare Logic       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.3.1       Wrapping       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000       0 FFFF         FFFF       3-12         3.1.4.2       Noncacheable Memory Space - 1 0000 0000       1 7FFF         FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000       1 9FFF FFFF         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.8       sysBus Transactions       3-15         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.1.2.6<br>3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                                        | External Logic Requirement Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                                                 | 3-9<br>3-9<br>3-10<br>3-10<br>3-10                             |

| 3.1.2.7       Tag Compare Logic       3-9         3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000 .0 FFFF FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 .1 7FFF FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000 .1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Full Condition       3-13         3.1.6.2       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.3       Bankset8       3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.1.2.7<br>3.1.2.8<br>3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                                                   | Tag Compare Logic CPU Primary Cache Invalidates sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                                                                            | 3–9<br>3–10<br>3–10<br>3–10                                    |

| 3.1.2.8       CPU Primary Cache Invalidates       3-9         3.1.3       sysBus Controller       3-10         3.1.3.1       Wrapping       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0.0000 0000 .0 FFFF         FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1.0000 0000 .1 9FFF FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1.8000 0000 .1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Full Condition       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.8       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2       Memory Organization       3-19         3.2.1       DRAM a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.1.3<br>3.1.3.1<br>3.1.4<br>3.1.4.1                                                                                         | CPU Primary Cache Invalidates  sysBus Controller  Wrapping  Address Decoding  Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF  Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                                                                                         | 3–10<br>3–10<br>3–10                                           |

| 3.1.3       sysBus Controller       3-10         3.1.3.1       Wrapping       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000       0 FFFF         FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000       1 7FFF         FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000       1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Flushing       3-13         3.1.7       Read/Merge Buffer Control       3-13         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       Memory Bankset Characteristics       3-29         3.2.2.1       Memory Bankset Character                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.1.3.1<br>3.1.4<br>3.1.4.1                                                                                                  | sysBus Controller Wrapping Address Decoding Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                                                                                                                            | 3–10<br>3–10                                                   |

| 3.1.3.1       Wrapping       3-10         3.1.4       Address Decoding       3-10         3.1.4.1       Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF       3-11         3.1.4.2       Noncacheable Memory Space - 1 0000 0000 1 7FFF FFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-13         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Bankset Characteristics       3-20         3.2.2.1       Memory Address Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.1.3.1<br>3.1.4<br>3.1.4.1                                                                                                  | Wrapping                                                                                                                                                                                                                                                                                                                                                               | 3–10                                                           |

| 3.1.4   Address Decoding   3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.1.4.1                                                                                                                      | Address Decoding                                                                                                                                                                                                                                                                                                                                                       |                                                                |

| 3.1.4.1   Cacheable Memory Space - 0 0000 0000 . 0 FFFF FFFF FFFF   3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.1.4.1                                                                                                                      | Cacheable Memory Space - 0 0000 0000 0 FFFF FFFF                                                                                                                                                                                                                                                                                                                       | 3_11                                                           |

| FFFF   3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1.4.2                                                                                                                      | FFFF                                                                                                                                                                                                                                                                                                                                                                   | 3-11                                                           |

| 3.1.4.2       Noncacheable Memory Space - 1 0000 0000 1 7FFF FFFFF       3-12         3.1.4.3       21071-CA CSR Space - 1 8000 0000 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-13         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.2       Bankset8       3-21         3.2.2.3       Memory Address Generation       3-23         3.2.4       Performance Optimizations       3-25         3.2.4.1       Memory Page Mode Support       3-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.1.4.2                                                                                                                      | Noncacheable Memory Space - 1 0000 0000 1 7FFF                                                                                                                                                                                                                                                                                                                         | <b>-</b>                                                       |

| FFFF       3-12         3.1.4.3       21071-CA CSR Space 1 8000 0000 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-15         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.2       Bankset0. Bankset7       3-21         3.2.2.3       Memory Address Generation       3-23         3.2.4       Performance Optimizations       3-25         3.2.4.1       Memory Page Mode Support       3-25         3.2.4.2       Read Latenc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                        |                                                                |

| 3.1.4.3       21071-CA CSR Space 1 8000 0000 1 9FFF FFFF       3-12         3.1.5       Lock Address Register and Lock Bit       3-13         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-17         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.2       Bankset8       3-22         3.2.2.3       Bankset8       3-22         3.2.3       Memory Address Generation       3-23         3.2.4       Performance Optimizations       3-25         3.2.4.1       Memory Page Mode Support       3-25         3.2.4.2       Read Lat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                              | FFFF                                                                                                                                                                                                                                                                                                                                                                   | 3-12                                                           |

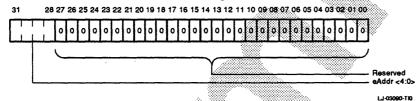

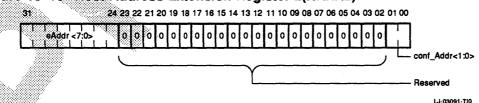

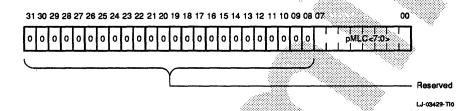

| 3.1.5       Lock Address Register and Lock Bit       3-12         3.1.6       Memory Write Buffer       3-13         3.1.6.1       Write Buffer Address Comparison       3-13         3.1.6.2       Write Buffer Flushing       3-13         3.1.6.3       Write Buffer Full Condition       3-13         3.1.7       Read/Merge Buffer Control       3-14         3.1.8       sysBus Transactions       3-15         3.1.8.1       CPU Transactions       3-15         3.1.8.2       DMA Transactions       3-17         3.1.9       Error Handling       3-18         3.2       Memory Controller       3-19         3.2.1       DRAM and SIMM Requirements       3-19         3.2.2       Memory Organization       3-19         3.2.2.1       Memory Bankset Characteristics       3-20         3.2.2.2       Bankset8       3-22         3.2.2.3       Bankset8       3-22         3.2.2.4       Supported Memory SIMMs       3-23         3.2.4       Performance Optimizations       3-25         3.2.4.1       Memory Page Mode Support       3-25         3.2.4.2       Read Latency Minimization       3-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.1.4.3                                                                                                                      | 21071-CA CSR Space - 1 8000 0000 1 9FFF FFFF                                                                                                                                                                                                                                                                                                                           | 3-12                                                           |