# digital

RP04 device control logic maintenance manual

digital equipment corporation · maynard, massachusetts

# RPO4 device control logic maintenance manual

EK-RP04-MM-001

digital equipment corporation · maynard. massachusetts

Preliminary, June 1974 1st Edition, November 1974 2nd Printing, January 1975

#### Copyright © 1974, 1975 by Digital Equipment Corporation

This material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

#### DISCLAIMER

Removable media involve use, handling and maintenance which are beyond DEC's direct control. DEC disclaims responsibility for performance of the Equipment when operated with media not meeting DEC specifications or with media not maintained in accordance with procedures approved by DEC. DEC shall not be liable for damages to the Equipment or to media resulting from such operation.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

> DEC FLIP CHIP DIGITAL

PDP FOCAL COMPUTER LAB

#### CONTENTS

J

ø,

| CHAPTER 1        | INTRODUCTION                                                  |

|------------------|---------------------------------------------------------------|

| 1.1              | GENERAL                                                       |

| 1.1.1            | System Compatibility                                          |

| 1.2              | PHYSICAL DESCRIPTION 1-2                                      |

| 1.2.1            | Card Nest and Cable Assembly                                  |

| 1.2.1.1          | Hex Printed Circuit Boards                                    |

| 1.2.1.2          | MASSBUS and MDLI Interface PCBs                               |

| 1.2.2            | Power Supply                                                  |

| 1.2.3            | Power Monitor                                                 |

| 1.3              | DCL FUNCTIONAL DESCRIPTION 1-6                                |

| 1.3.1            | Dual Controller Operation                                     |

| 1.3.2            | Read/Write Data Transfers                                     |

| 1.3.2.1          | Disk Pack Formatting 1-6                                      |

| 1.3.2.2          | Other Read/Write Commands 1-9                                 |

| 1.3.3            | Disk Addressing Techniques and Related Commands               |

| 1.3.4            | DCL Interface Registers 1-9                                   |

| 1.3.5            | Error Correction Capability                                   |

| 1.4              | APPLICATION INSTRUCTION MANUALS                               |

| 1.5              | SPECIFICATIONS                                                |

|                  |                                                               |

| <b>CHAPTER 2</b> | THEORY OF OPERATION                                           |

| 2.1              | DEVICE CONTROL LOGIC, SIMPLIFIED BLOCK DIAGRAM DISCUSSION 2-1 |

| 2.1.1            | Asynchronous Transfers and Control Command Execution          |

| 2.1.1.1          | Dual Control Operation                                        |

| 2.1.1.2          | Register Select Decoding and Registers                        |

| 2.1.1.3          | Command Decoding                                              |

| 2.1.2            | Synchronous Data Transfers 2-3                                |

| 2.1.2.1          | Synchronous Data Transfer Commands                            |

| 2.1.2.2          | Synchronous Data Transfer Control Logic                       |

| 2.1.3            | Disk Addressing Logic                                         |

| 2.1.3.1          | Cylinder/Track Addressing (Seek) 2-5                          |

| 2.1.3.2          | Sector Addressing                                             |

| 2.2              | MASSBUS AND MDLI (DRIVE) INTERFACE SIGNALS 2-6                |

| 2.2.1            | Massbus Interface Signals                                     |

| 2.2.2            | MDLI (DRIVE) Interface Signals                                |

| 2.3              | COMMAND REPERTOIRE                                            |

| 2.3.1            | Control Commands                                              |

| 2.3.2            | Data Transfer Commands                                        |

| 2.3.3            | Housekeeping Commands                                         |

| 2.3.4            | Mechanical Movement Commands                                  |

| 2.4              | DETAILED BLOCK DIAGRAM DISCUSSION                             |

| 2.4.1            | Massbus Control Signal Routing and DCL Interface Registers    |

| 2.4.1.1          | Control Line Enabling Signals                                 |

| 2.4.1.2          | Attention Summary Register Access                             |

| 2.4.1.3          | DCL Interface Registers                                       |

| 2.4.2            | Synchronous Data Flow                                         |

| 2.4.2.1          | Write Operation (Massbus-to-Disk Transfer)                    |

#### CONTENTS (Cont)

|           |                                                                | Page   |

|-----------|----------------------------------------------------------------|--------|

| 2.4.2.2   | Read Operation (Disk-to-Massbus Transfers)                     | 2-31   |

| 2.4.3     | Basic Clock and Index Pulse Distribution                       |        |

| 2.4.3.1   | Basic Clock Signals                                            |        |

| 2.4.3.2   | Sync Clock Generator Circuits                                  |        |

| 2.4.3.3   | Ring Counter                                                   |        |

| 2.4.3.4   | Byte Counter and Byte Count Shift Register                     |        |

| 2.4.3.5   | Sync Clock Enable Control and Sync Clock Enable Flip-Flop      |        |

| 2.4.3.6   | Sector Clock Counter and Sector Counter                        |        |

| 2.4.3.7   | Sector Compare Logic and Desired Sector Register               |        |

| 2.4.3.8   | Sector Found Control and Sector Found Flip-Flop                |        |

| 2.4.4     | Sector Format and Related Control/Synchronization Requirements |        |

| 2.4.5     | Disk Addressing Logic, Block Diagram Discussion                |        |

| 2.4.5.1   | Cylinder Addressing                                            |        |

| 2.4.5.2   | Track Addressing                                               |        |

| 2.4.5.3   | Sector Addressing                                              |        |

|           | Error Correction Code Logic Block Diagram Discussion           |        |

| 2.4.6     | Generating and Writing the ECC Field (Write Operation)         |        |

| 2.4.6.1   |                                                                |        |

| 2.4.6.2   | Checkout of the ECC Redundancy Code (Read Operation)           |        |

| 2.4.6.3   | Error Correction Processing                                    | . 2-30 |

| CHAPTER 3 | SERVICE INFORMATION                                            |        |

| 3.1       | GENERAL                                                        | . 3-1  |

| 3.2       | DCL POWER SUPPLY AND POWER MONITOR                             | . 3-1  |

| 3.3       | ASYNCHRONOUS DATA TRANSFER (HANDSHAKE)                         | . 3-2  |

| 3.3.1     | Writing a Register                                             | . 3-2  |

| 3.3.2     | Reading a Register                                             | . 3-3  |

| 3.3.3     | Dual Control                                                   |        |

| 3.3.3.1   | Port Acquisition                                               | . 3-4  |

| 3.3.3.2   | Port Release                                                   | . 3-5  |

| 3.3.3.3   | Simultaneous Controller A and Controller B Demands             | . 3-5  |

| 3.4       | MECHANICAL MOVEMENT                                            | . 3-5  |

| 3.4.1     | Seek                                                           | . 3-5  |

| 3.4.1.1   | Seek Flow                                                      | . 3-5  |

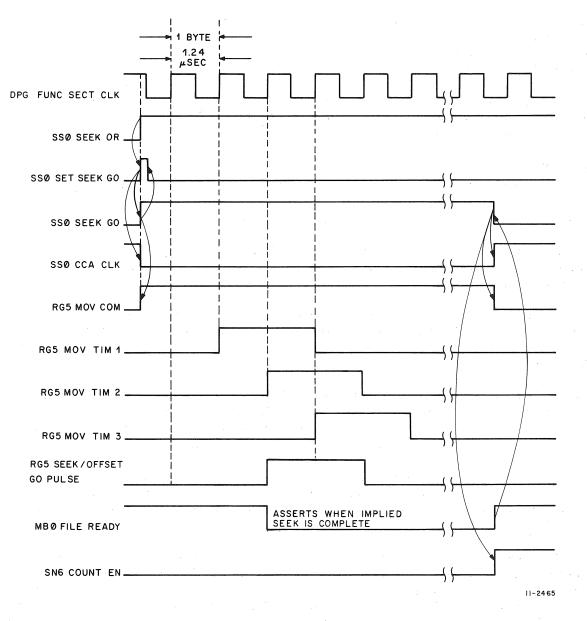

| 3.4.1.2   | Implied Seek                                                   | . 3-6  |

| 3.4.1.3   | Mid-Transfer Seek                                              | . 3-6  |

| 3.4.2     | Offset                                                         | . 3-6  |

| 3.4.2.1   | Offset Flow                                                    | . 3-7  |

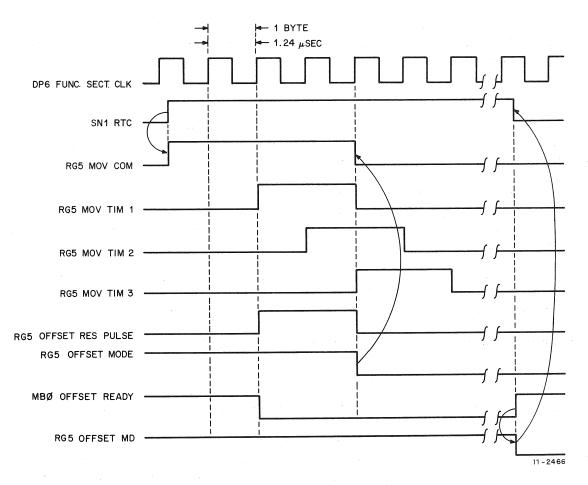

| 3.4.3     | Return-to-Centerline                                           | . 3-8  |

| 3.4.3.1   | Return to Centerline Flow                                      | . 3-8  |

| 3.4.3.2   | Implied Return to Centerline                                   | . 3-8  |

| 3.4.4     | Recalibrate                                                    | . 3-8  |

| 3.4.4.1   | Recalibrate Flow                                               |        |

| 3.4.5     | Unload                                                         |        |

| 3.4.5.1   | Unload Flow                                                    |        |

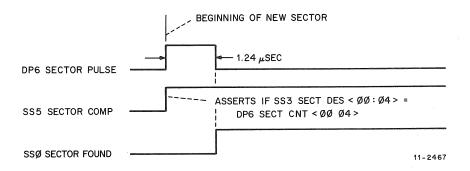

| 3.5       | SECTOR SEARCH                                                  |        |

| 3.5.1     | Sector Timing                                                  |        |

| 3.5.2     | Sector Search Flow                                             |        |

| 3.5.3     | Implied Search                                                 |        |

#### **CONTENTS (Cont)**

Page

| 3.6              | WRITE HEADER AND DATA FLOW DIAGRAM DISCUSSION                 |

|------------------|---------------------------------------------------------------|

| 3.6.1            | Command Setup                                                 |

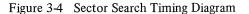

| 3.6.2            | Sector Search/Sector Found                                    |

| 3.6.3            | Pre-Header Field                                              |

| 3.6.3.1          | Writing the Sync Byte                                         |

| 3.6.4            | Header Setup Operation and Writing the Header                 |

| 3.6.5            | Header Gap                                                    |

| 3.6.5.1          | Data Field Sync Byte                                          |

| 3.6.6            | Data Field                                                    |

| 3.6.7            | Error Correction Code (ECC) Field                             |

| 3.6.8            | Data Gap                                                      |

| 3.7              | HEADER COMPARE PROCESS                                        |

| 3.8              | WRITE DATA FLOW DIAGRAM DISCUSSION                            |

| 3.8.1            | Command Setup                                                 |

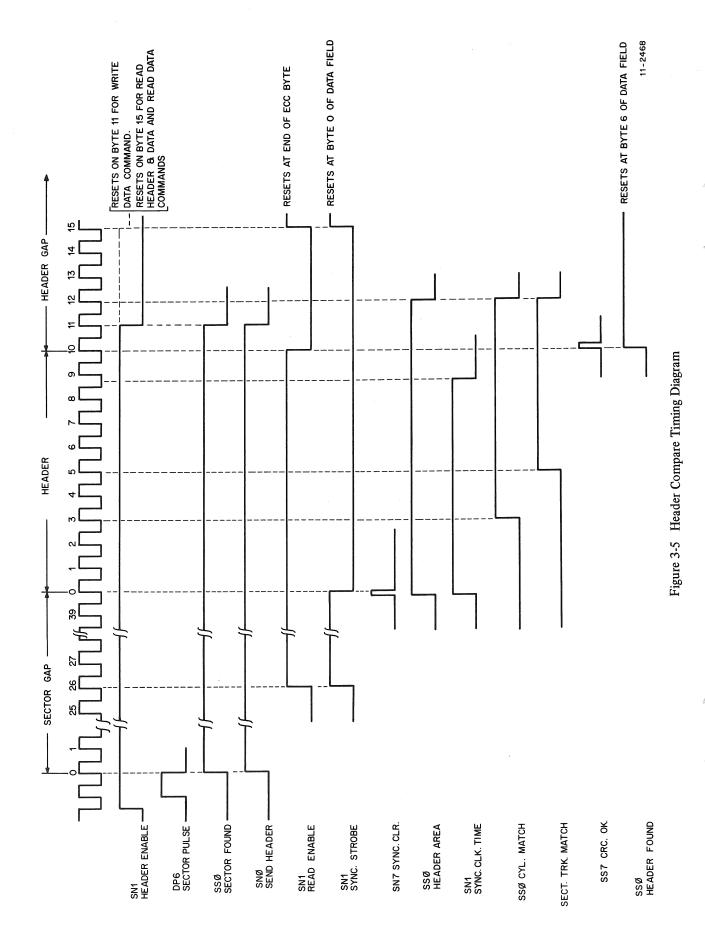

| 3.8.2            | Pre-Header Field and Header Field                             |

| 3.8.3            | Header Gap                                                    |

| 3.8.4            | Data Field Sync Byte and Data Field                           |

| 3.8.5            | ECC Field                                                     |

| 3.8.6            | Data Gap                                                      |

| 3.9              | READ DATA COMMAND/READ HEADER AND DATA                        |

| 5.9              | COMMAND FLOW DIAGRAM DISCUSSION                               |

| 3.10             | HOUSEKEEPING COMMANDS                                         |

| 3.10.1           | No Operation (No-Op)                                          |

| 3.10.2           | Read In                                                       |

| 3.10.3           | Pack Acknowledge                                              |

| 3.10.4           | NG Drive Clear                                                |

| 3.11             | BYTE COUNTER OPERATION                                        |

| 3.11.1           | Shift Clock Select                                            |

| 3.11.2           | Byte Count Development                                        |

| 3.12             | ERROR HANDLING AND ECC HANDLING                               |

| 3.12.1           | Error Handling                                                |

| 3.12.2           | ECC Handling                                                  |

| 5.12.2           | Ece manuning                                                  |

| <b>CHAPTER 4</b> | REPLACEMENT PROCEDURES                                        |

| 4.1              | GENERAL                                                       |

| CHAPTER 5        | MAINTENANCE                                                   |

| 5.1              | GENERAL                                                       |

|                  | INTEGRATED CIRCUIT DESCRIPTION                                |

| APPENDIX A       | INTEGRATED CIRCUIT DESCRIPTION                                |

| A.1              | INTRODUCTION A-1                                              |

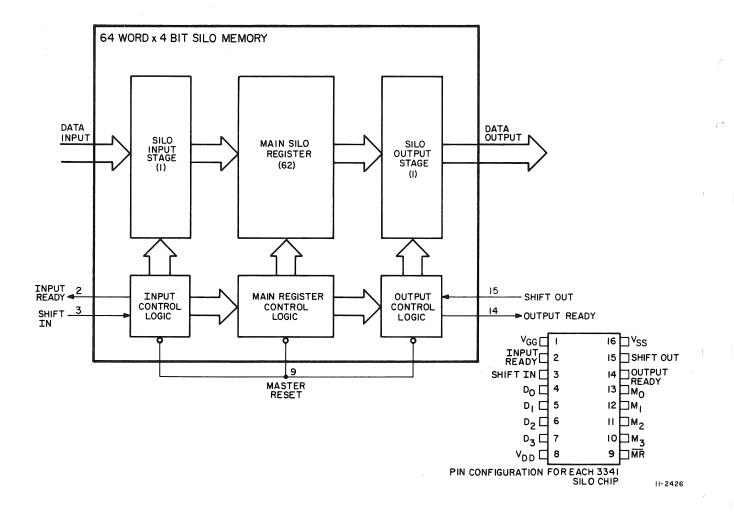

| A.2              | 3341 64-WORD × 4-BIT SERIAL MEMORY (SILO) A-1                 |

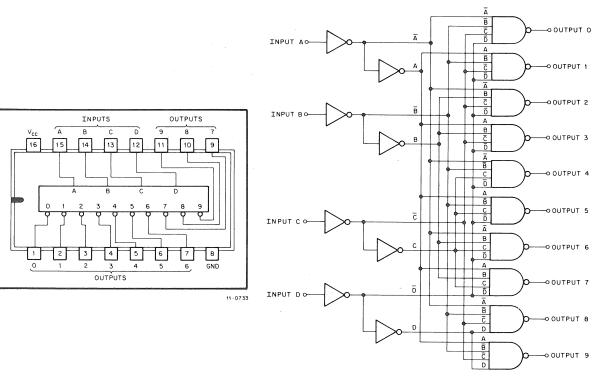

| A.3              | 7442 4-LINE-TO-10-LINE DECODERS A-3                           |

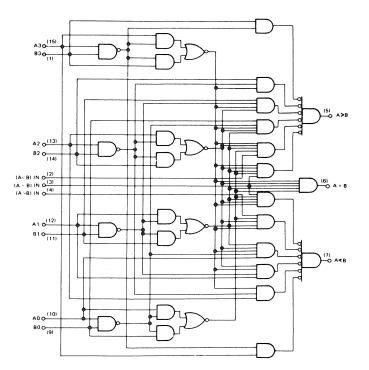

| A.4              | 7485 4-BIT MAGNITUDE COMPARATORS A-4                          |

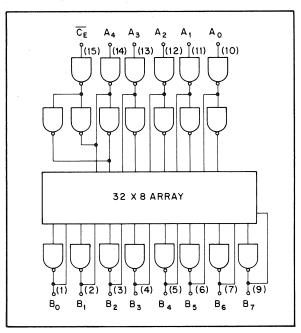

| A.5              | 8223 256-BIT BIPOLAR FIELD-PROGRAMMABLE ROM (32 × 8 PROM) A-5 |

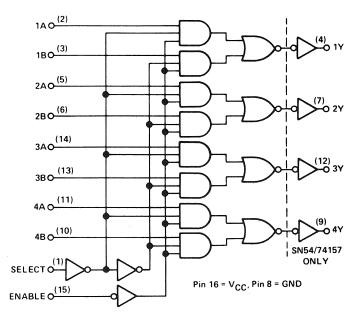

| A.6              | 8234 2-INPUT 4-BIT DIGITAL MULTIPLEXER A-6                    |

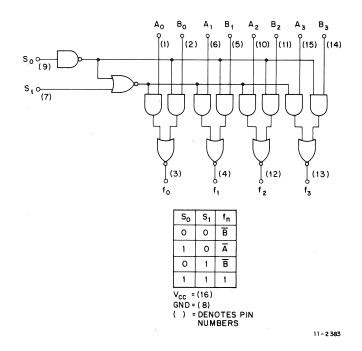

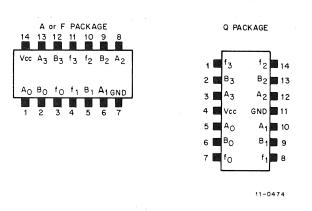

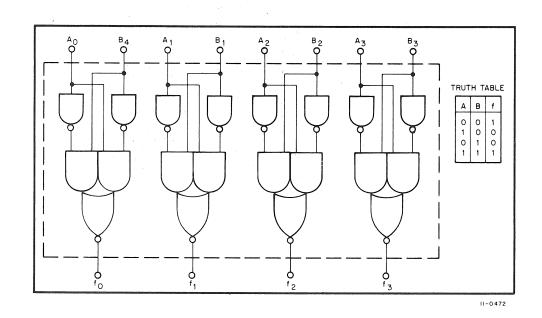

| A.7              | 8242 EXCLUSIVE-NOR 4-BIT DIGITAL COMPARATOR A-7               |

#### **CONTENTS (Cont)**

| A.8  | 74157 QUADRUPLE 2-LINE TO 1-LINE MULTIPLEXER | . A-8 |

|------|----------------------------------------------|-------|

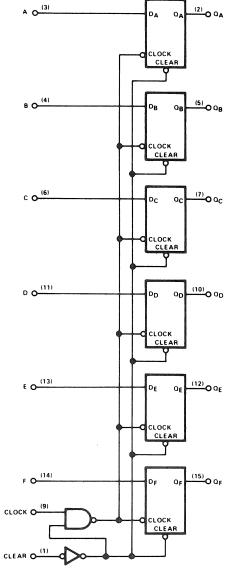

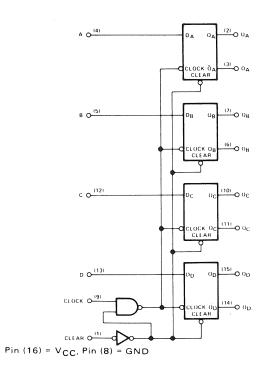

| A.9  | 74174 HEX D-TYPE FLIP-FLOPS                  | . A-9 |

| A.10 | 74175 QUAD D-TYPE FLIP-FLOPS                 | A-10  |

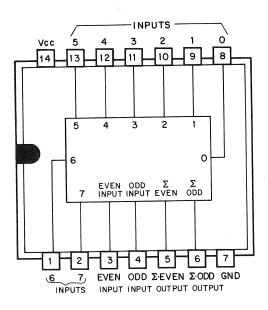

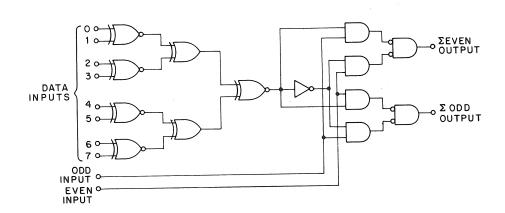

| A.11 | 74180 PARITY CONTROL GENERATOR/CHECKER       | A-11  |

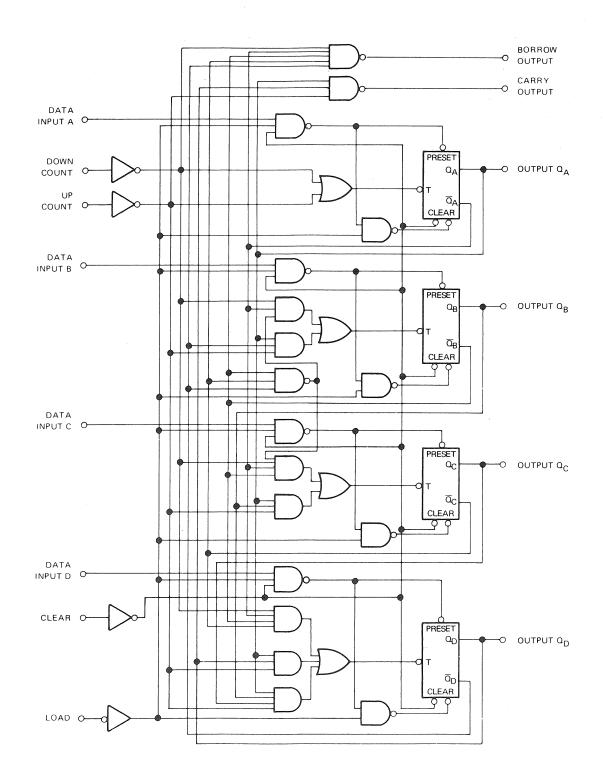

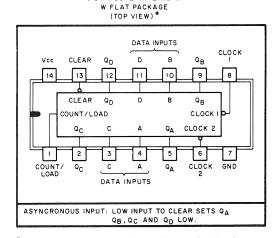

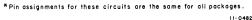

| A.12 | 74193 4-BIT BINARY COUNTER                   | A-12  |

| A.13 | 74197 50 MHz PRESETTABLE DECADE AND          |       |

|      | BINARY COUNTERS/LATCHES                      | A-14  |

#### **ILLUSTRATIONS**

#### Figure No.

#### Title

#### Page

| 1-1 | RP04 Drive and DCL Assemblies                                    |

|-----|------------------------------------------------------------------|

| 1-2 | RP04 Drive and DCL Assemblies Back View, Rear Panels Removed 1-3 |

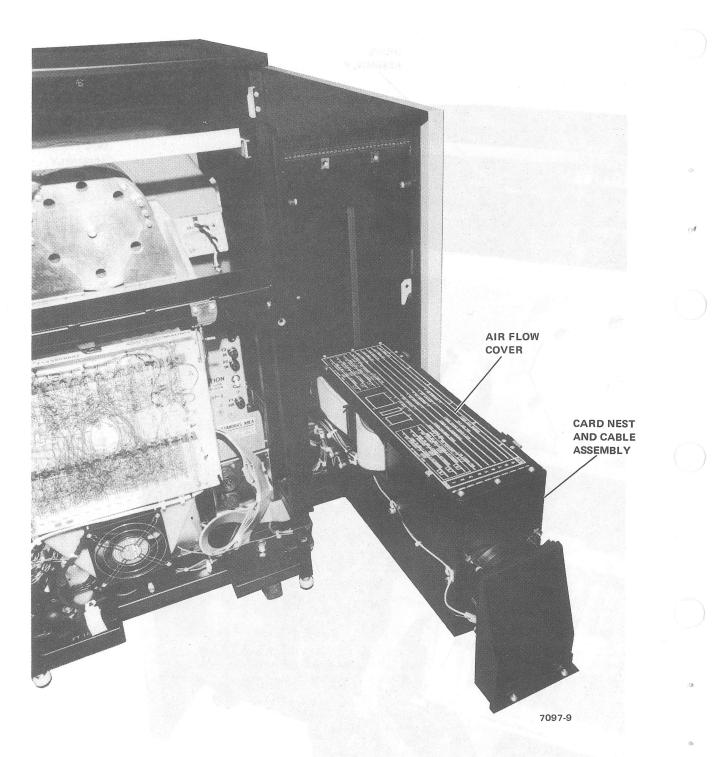

| 1-3 | DCL Rear View, Card Nest and Cable Assembly Extended 14          |

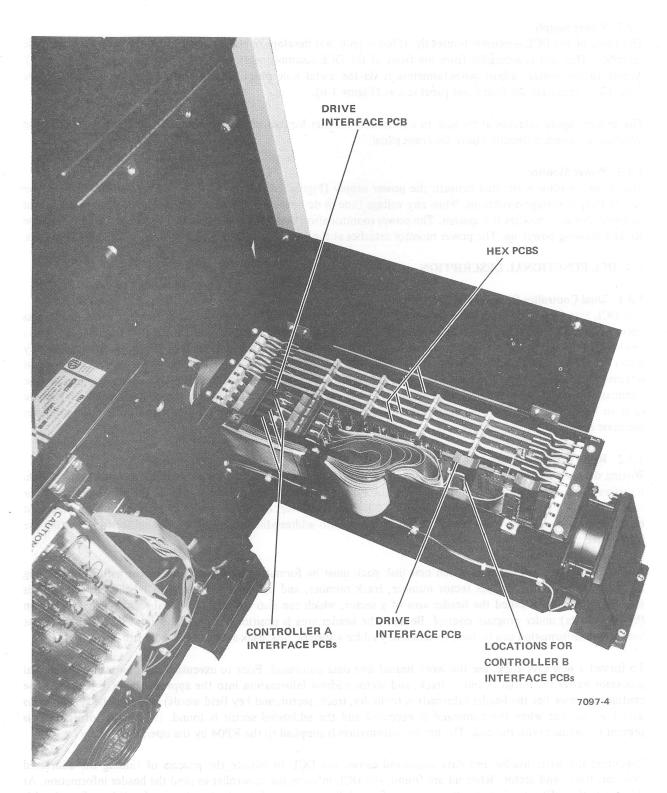

| 1-4 | Card Nest and Cable Assembly PCB Layout 1-5                      |

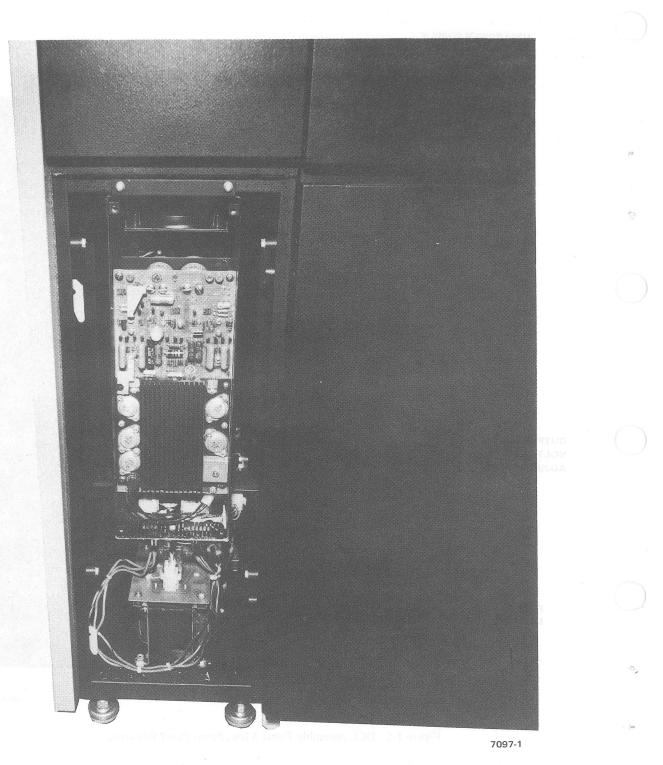

| 1-5 | DCL Assembly Front View, Front Panel Removed 1-7                 |

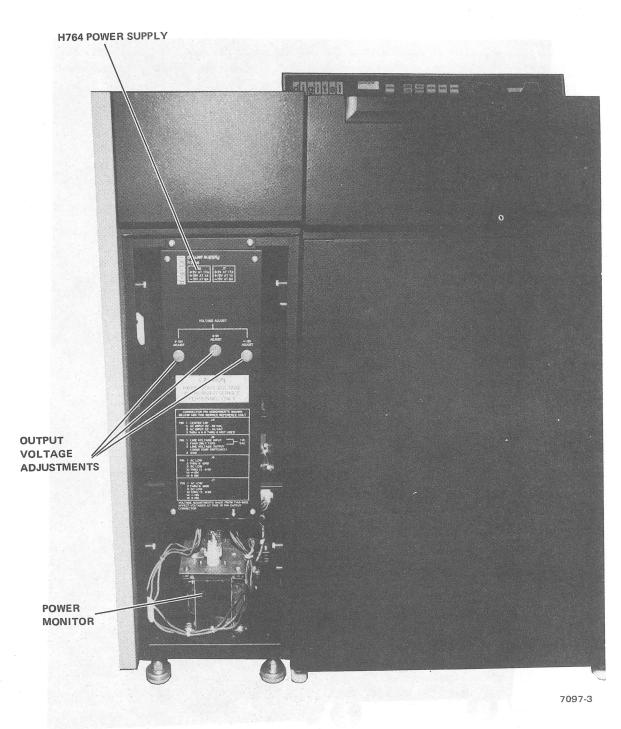

| 1-6 | DCL Assembly Power Supply, Front Panel Removed 1-8               |

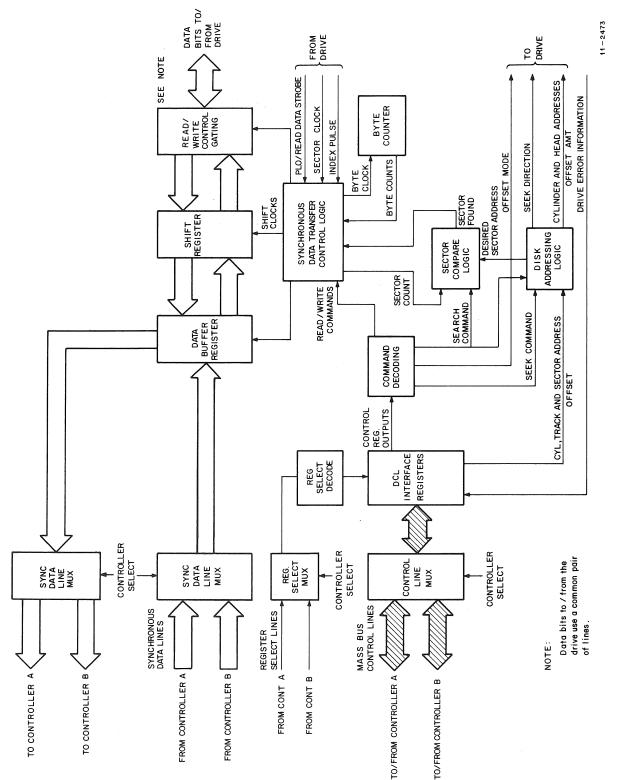

| 2-1 | Device Control Logic, Simplified Block Diagram 2-2               |

| 2-2 | Massbus and MDLI (Drive) Interface Signal 2-7                    |

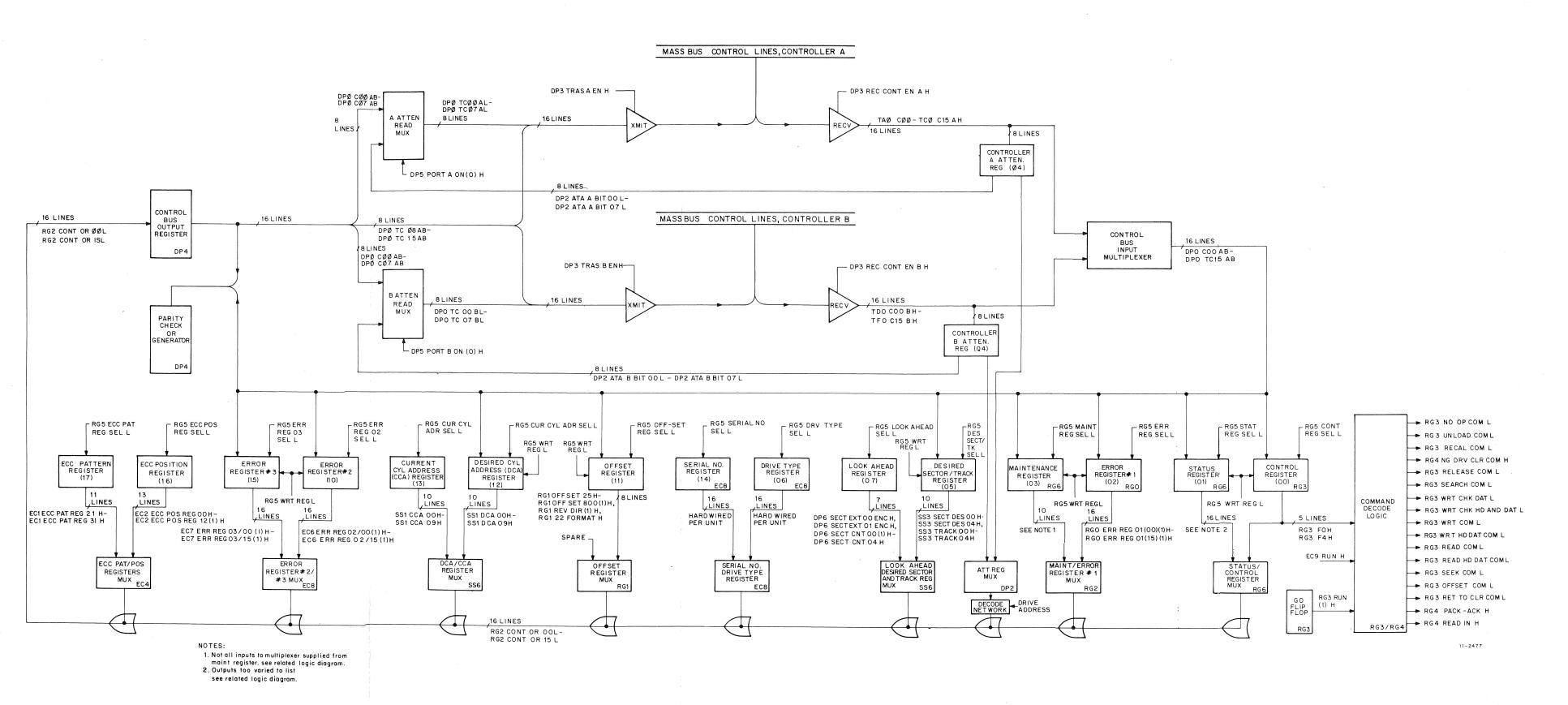

| 2-3 | DCL Interface Registers and Massbus Control Signal Routing       |

|     | Block Diagram                                                    |

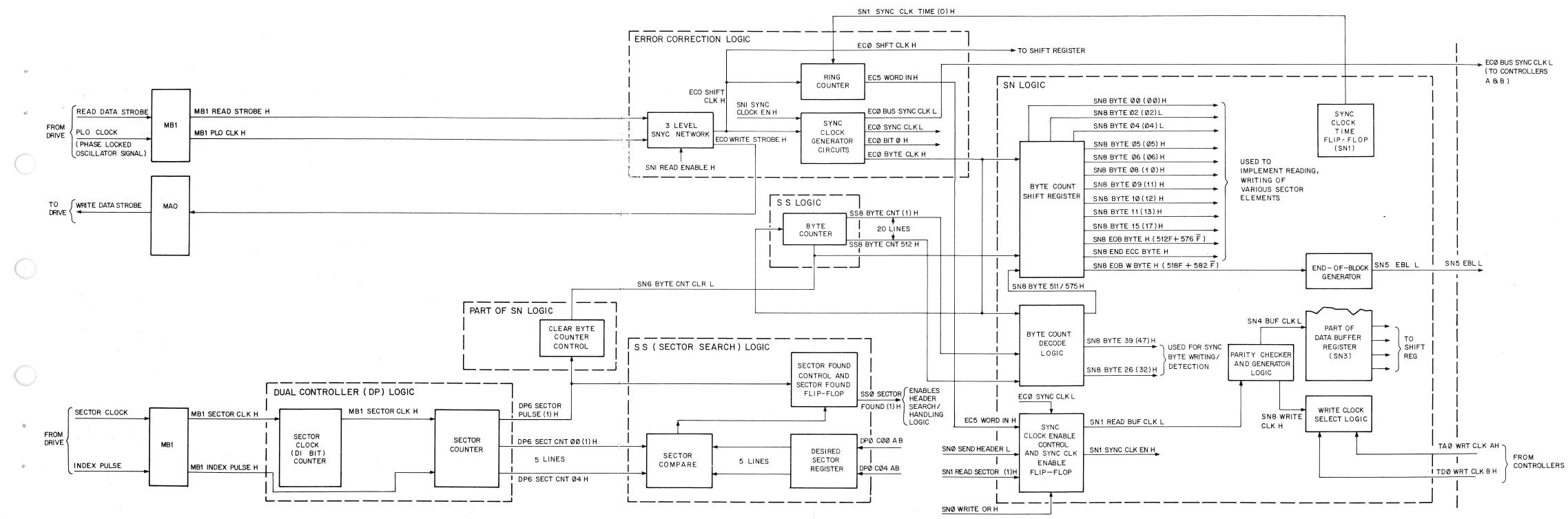

| 2-4 | Synchronous Data Transfer Path Block Diagram 2-29                |

| 2-5 | Basic Clock and Index Pulse Distribution Block Diagram 2-33      |

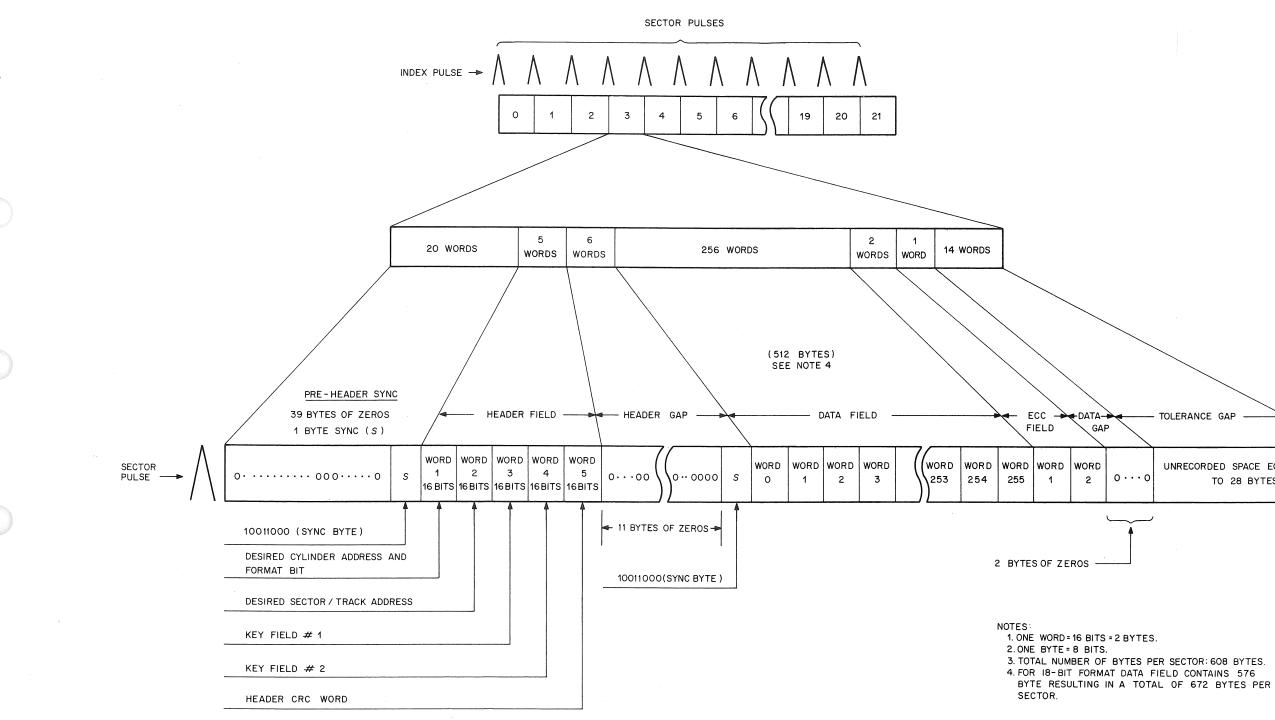

| 2-6 | Sector Format (16 Bit Mode) Diagram 2-37                         |

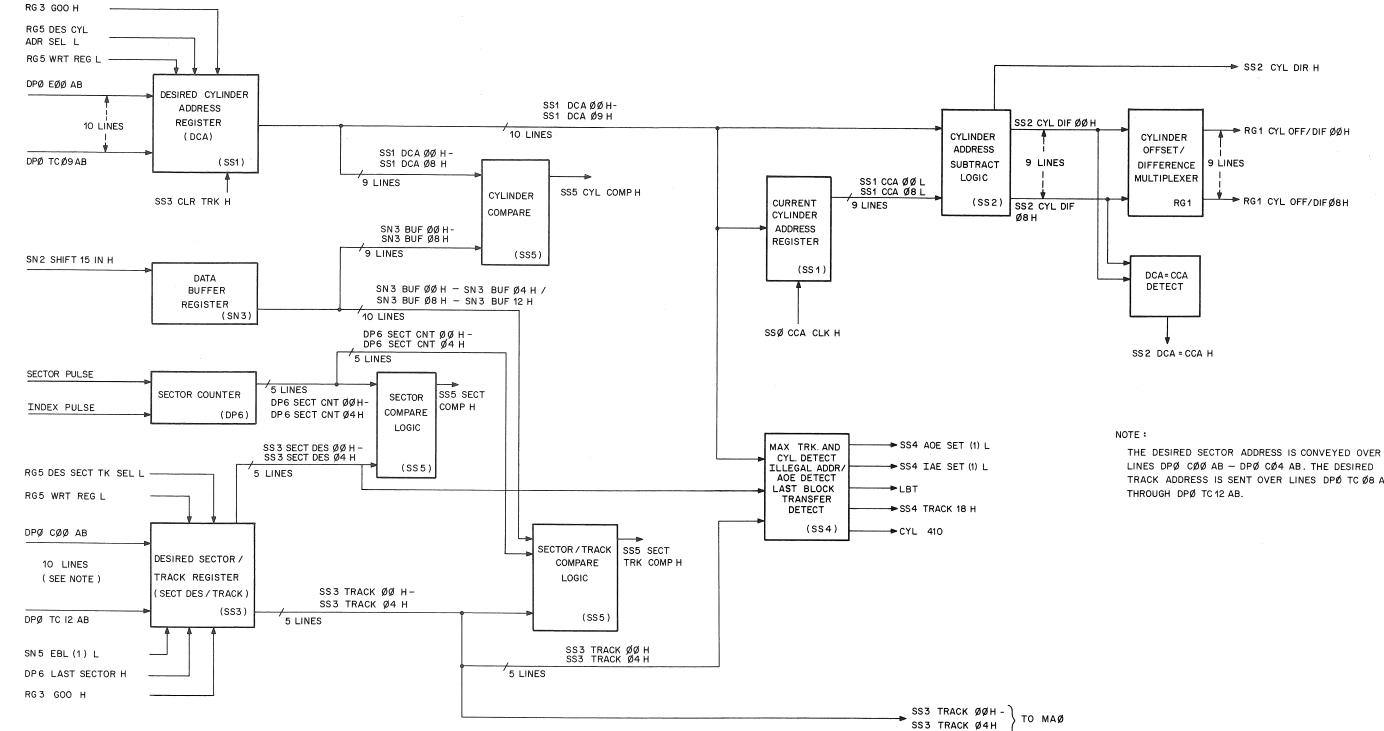

| 2-7 | Disk Addressing Logic Block Diagram 2-45                         |

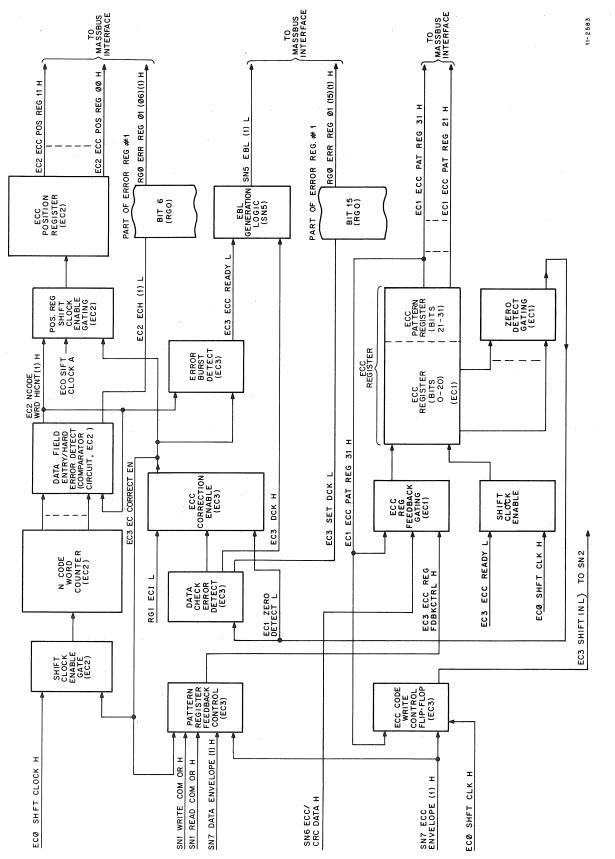

| 2-8 | Error Correction Logic Block Diagram 2-49                        |

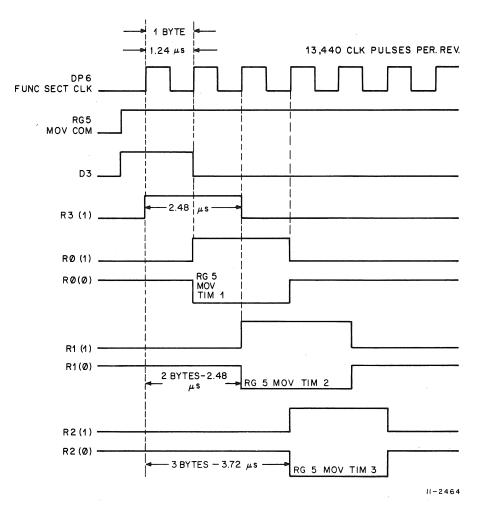

| 3-1 | Move Timing Diagram 3-6                                          |

| 3-2 | Implied Seek Timing Diagram 3-7                                  |

| 3-3 | Implied Return to Centerline Timing Diagram 3-9                  |

| 3-4 | Sector Search Timing Diagram                                     |

| 3-5 | Header Compare Timing Diagram                                    |

| 3-6 | Data Field Timing – Read Data and Read Header and Data           |

#### TABLES

# Table No.TitlePage2-1DRY/PIP/ATA Status During DCL Operation2-182-2Sector Format Processing For Read/Write Commands2-39A-1Control Signal Timing SpecificationsA-1

## CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

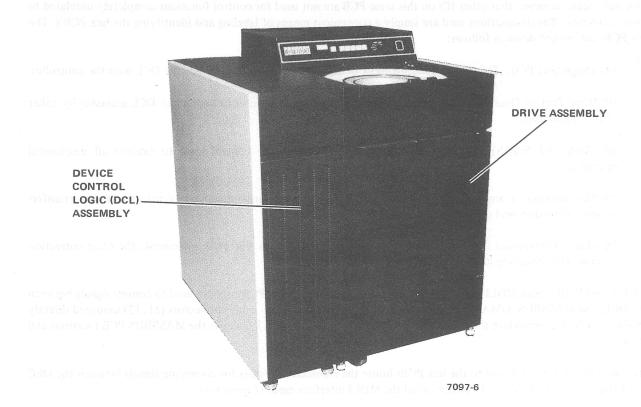

This manual describes the Device Control Logic (DCL) incorporated in the RP04 Disk Drive. The RP04 is divided into two major functional parts (Figure 1-1):

1. The DCL which houses the necessary logic circuits to interpret and implement all commands executable by the RP04 and allows for access by two different controllers.

2. The DEC 733 Disk Storage Drive which houses the circuits for: rotating the disk pack, positioning the read/write heads at the addressed cylinder track and sector; and writing/reading bits on the disk pack surface.

#### 1.1.1 System Compatibility

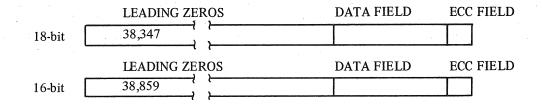

The DCL is capable of handling data transfers in either 16 or 18-bit format making the RP04 compatible with the PDP-11, PDP-15 and DECsystem-10. Each system has its own specialized controller that interfaces the RP04 with the related processor.

Figure 1-1 RP04 Drive and DCL Assemblies

#### 1.2 PHYSICAL DESCRIPTION

The DCL itself is a 9-inch wide by 32-inch deep by 35-inch high unit that attaches at the left of the Drive assembly when the RP04 is viewed from the front (Figure 1-1). The DCL assembly is attached to the drive assembly by four 2-inch long  $1/4 \times 20$  bolts. The DCL assembly also has its own casters for easy roll-away when disconnected from the Drive assembly. Levelers are attached to provide stability when the DCL is permanently installed.

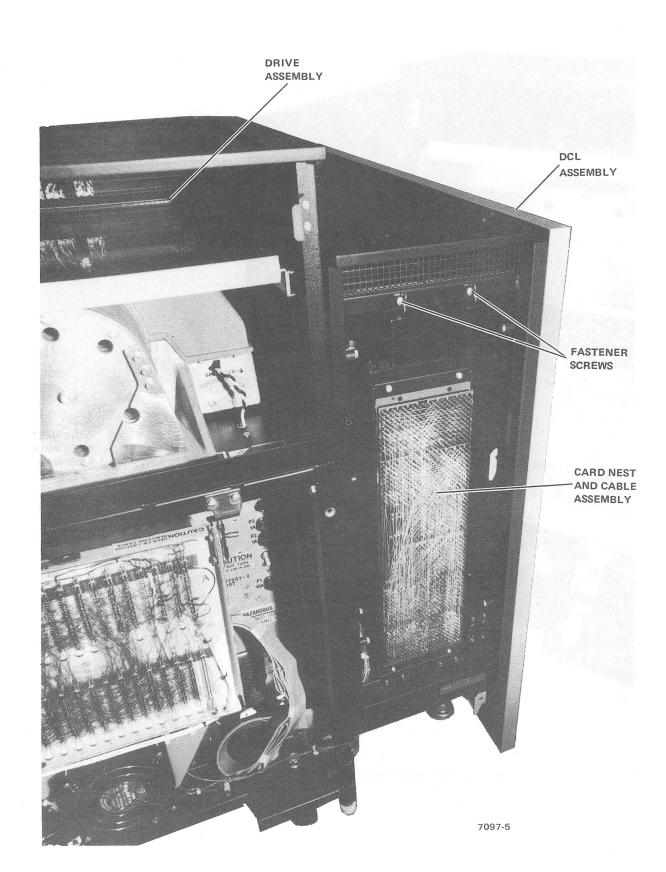

Physically, the DCL is comprised of three main subassemblies: The Card Nest and Cable Assembly, the Power Supply, and the Power Monitor (Figures 1-2 and 1-3).

#### 1.2.1 Card Nest and Cable Assembly

The card nest and cable assembly is accessible through the rear of the unit by lifting the entire rear cover panel and drawing it free of the assembly. This exposes the two fasteners that are used to hold the card nest and cable assembly (Figure 1-2) in an upright position. Then access to the printed circuit cards is gained by:

- 1. Loosening the two fastener screws and carefully swinging the assembly outboard until it rests in a horizontal position.

- 2. Loosening the two fastener screws (Figure 1-3) on the air flow cover and swinging the cover to the vertical position. This exposes the hex and interface printed circuit boards (PCB's).

All control logic circuits are housed on the hex PCBs that extend the full length of the card nest and cable assembly. The PCBs that interface with the drive assembly and the two controllers are the smaller PCBs situated to the left of the assembly when viewed from the top. Figure 1-4 shows the layout of the PCBs within the card nest and cable assembly.

1.2.1.1 Hex Printed Circuit Boards – There are five hex PCBs. Designations for these cards are based on the principal control circuits housed on a particular PCB. For example, the Error Correction (EC) PCB is so designated because there are more ICs used for this function than for any other control function on this particular board. This does not mean, however, that other ICs on this same PCB are not used for control functions completely unrelated to error correction. The designations used are simply a convenient means of labeling and identifying the hex PCB's. The hex PCBs are broken down as follows:

RG (Registers) PCB: This board contains most of the registers used to interface the DCL with the controller.

DP (Dual Port or Dual Controller) PCB: This card contains logic used to implement DCL accessing by either of two controllers.

SS (Seek and Search) PCB: This board primarily includes the control logic to execute all mechanical operations.

SN (Synchronous Transfer) PCB: Much of the logic on this board implements synchronous data transfers between controller and disk pack.

EC (Error Correction) PCB: Approximately half of the logic on this PCB implements the error correction process. The remaining logic is used for error registers and timing.

1.2.1.2 MASSBUS and MDLI Interface PCBs – Of the eight interface PCBs, six are used to convey signals between the DCL and MASSBUS A/MASSBUS B. Each of these six PCBs has two cable connectors (J1, J2) mounted directly on the card to accommodate the appropriate MASSBUS cables. Figure 1-4 shows the MASSBUS PCB locations and designations.

The two interface cards closest to the hex PCBs house the transceiver circuits for conveying signals between the DEC 733 Drive and the DCL. These PCBs are called the MDLI interface cards (Figure 1-4).

Figure 1-2 RP04 Drive and DCL Assemblies Back View, Rear Panels Removed

Figure 1-3 DCL Rear View, Card Nest and Cable Assembly Extended

Figure 1-4 Card Nest and Cable Assembly PCB Layout

ter wittelbesdu and dari communiciatio allow on writing dati weeda beginning at a fixed time following fig eader Theane when data words ise wetten is called the dura field.

#### 1.2.2 Power Supply

The front of the DCL Assembly houses the H764 supply that develops operating voltages for the card nest and cable assembly. This unit is accessible from the front of the DCL assembly when the front panel is removed (Figure 1-5). Access to the voltage adjust potentiometers is via the metal hole plugs. The power supply components can be replaced by removing the four front panel screws (Figure 1-6).

The power supply attaches at its base to a mounting bracket located in the center of the DCL assembly. The top attaches to a bracket directly above the front panel.

#### 1.2.3 Power Monitor

The power monitor is situated beneath the power supply (Figure 1-5) and provides a constant check of the power supply output voltage conditions. When any voltage (line or dc output) strays from the required tolerance (ac low or dc low), this unit notifies the system. The power monitor also provides the "power OK" signal used to initialize the RP04 following power up. The power monitor attaches at the base of the DCL assembly with four mounting screws.

#### 1.3 DCL FUNCTIONAL DESCRIPTION

#### 1.3.1 Dual Controller Operation

The DCL interface logic is designed to permit access by two different controllers (i.e., provided that the dual access option is installed). The setting of the CONTROLLER SELECT switch on the control panel determines whether a single or both controllers are allowed to access the RP04. When set to the A/B position, it allows for accessing by either controller on a "first-come, first-serve" basis. Once a controller has gained access in the dual access mode, it retains control until it has completed its operation. Normally, a controller releases the DCL by executing a release command to place the RP04 back in a device available status. However, if the accessing controller fails to execute such an instruction within a one-second time span (i.e., following the last operation), a timeout function produces the same result.

#### 1.3.2 Read/Write Data Transfers

Writing data words onto the RP04 disk pack or reading data words from the disk pack are termed synchronous data transfers since such transfers are effected over the synchronous data bus portion of the MASSBUS interface. Four read/write commands are implemented by the DCL logic. However, the write header and data command must first be used to format a disk pack (divide the disk surface into addressable sectors) as a prerequisite to executing the other three commands.

**1.3.2.1** Disk Pack Formatting – Each new disk pack must be formatted to provide each sector with an identifying indicator or label that defines sector number, track number, and cylinder number. This labeling information is inserted into what is called the header area of a sector, which can also contain additional identifying information (key field data) under program control. Because the header area is positioned before the data field of a sector, the header area information can be used to accurately address specific disk pack sectors for read/write operation.

To format a new disk pack, use the write header and data command. Prior to executing this command, the central processor writes the initial cylinder, track, and sector address information into the appropriate DCL registers. The central processor has the header information (cylinder, track, sector, and key field words) ready on the synchronous data lines so that when the command is executed and the addressed sector is found, the header information is present for writing onto the disk. The header information is supplied to the RP04 by the operating system.

Executing the write header and data command causes the DCL to initiate the process of finding the addressed cylinder, track, and sector. When all are found, the DCL informs the controller to send the header information. At this time, the DCL also initiates the sequence for serially writing each header word onto the disk surface. In this way, header information is introduced onto an addressed sector.

The write header and data command also allows for writing data words beginning at a fixed time following the header. The area where data words are written is called the data field.

Figure 1-5 DCL Assembly Front View, Front Panel Removed

Figure 1-6 DCL Assembly Power Supply, Front Panel Removed

1.3.2.2 Other Read/Write Commands – The DCL interprets and executes three other commands to effect read/write data transfers. For each of these commands, the DCL makes proper identification of the header prior to initiating the transfer process. The technique for header identification is to compare the cylinder, sector, and track addresses of the header against those supplied prior to the read/write command initiation. Failure to detect a matchup in all three addresses results in the DCL setting a header compare error bit that is eventually sampled by the central processor.

A breakdown of the remaining read/write commands and their functions is given below:

Write data command: This command is used to write data words into the data field of an addressed sector. The DCL executes this command by first finding and identifying the addressed sector and then initiating the write transfer into the data field of that sector. The command can be used for an extended (multi-sector) write operation in that the DCL continues to write into the data fields of successive sectors for as long as the RUN line from the controller is asserted.

Read Header and Data Command: This command reads the header and data fields of an addressed sector and sends both to the central processor via the controller. Reading the header information may prove useful in analyzing faults after the DCL has indicated a header compare error on a particular sector. By reading the header information (cylinder, track and sector address) and comparing it against that supplied with the read header and data command, the CPU is able to determine exactly what header (format) information is in error.

Read Command: This command is used to read the data field of an addressed sector. As is the case with all read/write commands, the CPU must load the desired cylinder address and desired sector/track registers prior to executing the command. Once the addressed sector has been found, the DCL reads consecutive sectors for as long as the RUN line from the controller is asserted.

#### 1.3.3 Disk Addressing Techniques and Related Commands

The DCL executes two commands that are used solely to locate addressed areas of the disk pack - seek and search. The functions carried out by these commands are broken down as follows:

Seek Command: This causes the drive read/write heads to be positioned over the addressed cylinder. Cylinder and track information is supplied from the central processor prior to executing the command. When the heads are correctly positioned, the drive informs the DCL which in turn asserts the ATTENTION line to the controller.

Read/Write commands may also require positioning the read/write heads at the addressed cylinder. This activity is referred to as an "implied seek", since the seek command is not used and the ATTENTION line is not asserted.

Search Command: The search command is used as a method of optimizing the pack revolution time. When the DCL detects the addressed sector, it asserts the ATTENTION line to the controller.

#### 1.3.4 DCL Interface Registers

The DCL has 16 interface registers that can be accessed by the controller; they fall into the following general categories:

Control – The control register receives the command (read, write, seek, etc.) codes from the controller. The DCL control logic samples the content of this register and initiates the appropriate execution sequence.

Status – The bits of this register supply the central processor with DCL and Drive status information.

Maintenance – The maintenance register is used by diagnostic programs to initiate various maintenance functions.

Error Information - Three registers are provided to indicate error status within both the DCL and the Drive.

Address Data – These are five registers that are associated with disk addressing:

- Desired Cylinder Address Register

- Current Cylinder Address Register

- Desired Sector/Track Register

- Offset Register, used to offset the disk read/write heads in fixed increments.

- Look Ahead Register, can be used to subdivide the data field of a sector.

System Housekeeping – There are two registers used for system housekeeping, i.e., a drive type register and a serial number register.

Attention Summary Pseudo Register – This is a one bit register used to indicate that the RP04 requires the attention of the system. In one sense it can be considered an interrupt line.

Error Correction – There are two registers used to convey error correction information to the central processor.

#### 1.3.5 Error Correction Capability

The DCL is equipped with error correction logic, which (provided it is not inhibited by the system) becomes operative whenever an error is detected during a read operation. Once activated, the error correction circuits proceed to locate the area in the sector data field where the error occurred. When this area is detected, the DCL makes available the following information to the operating system:

- 1. Error correction code burst pattern.

- 2. Position with the data field where the error occurred.

Given this information, the software can determine the exact bits in error and correct them.

#### 1.4 APPLICABLE INSTRUCTION MANUALS

Instruction manuals bearing upon use of the RP04 depends on whether the device is configured in a PDP-11 or PDP-10 system environment (or both). When used with the PDP-11, applicable instruction manuals are:

- RP04 Disk Drive Installation Manual

- Model 733 DEC Disk Storage Drive Operation, Service and Diagrams Manual

- RJP04 Moving Head Disk Drive Maintenance Manual

- RH11 Controller Instruction Manual

- RP04 DCL Print Set

When the RP04 is used with the PDP-10 system, related handbooks are:

- RP04 Disk Drive Installation Manual

- Model 733 DEC Disk Storage Drive Operation, Service and Diagrams Manual

- RH10 Controller Instruction Manual

- RP04 DCL Print Set

#### 1.5 SPECIFICATIONS

Data Format Option:

20 sectors per data track (256 18-bit words per sector data field). 22 sectors per data track (256 16-bit words per sector data field).

Error Handling:

Error Detection and Correction Capability.

#### Interface Characteristics:

MASSBUS Controller to device interface Dual Controller capability.

#### System Compatibility:

Can be used in PDP-11 or PDP-10 system configuration.

#### Data Transfer Modes:

Single sector or multisector (spiral or extended read/write) transfers.

#### Operating Temp. Ranges:

15° C minimum to 32° C maximum.

#### Humidity Range:

20% minimum to 80% maximum.

#### Dimensions:

9-in. wide by 35-in. high by 32-in. deep.

#### Weight (DCL only):

100 lb (approx).

#### Operating Voltages DCL only:

+5 Vdc -15 Vdc

+15 Vdc

۳.

### CHAPTER 2 THEORY OF OPERATION

#### 2.1 DEVICE CONTROL LOGIC, SIMPLIFIED BLOCK DIAGRAM DISCUSSION

Figure 2-1 is a simplified block diagram of the DCL indicating the major functional areas involved in accessing the RP04 (asynchronous operation) and the implementation of synchronous data transfers. This diagram also shows the duality of the Massbus interface (the DCL can be accessed by either of two controllers).

#### 2.1.1 Asynchronous Transfers and Control Command Execution

2.1.1.1 Dual Control Operation – Asynchronous transfers between DCL and controller take place over the Massbus control lines and occur when the controller writes or reads a register within the DCL. Between controllers, access to the DCL registers is on a first-come-first-serve basis. Once the DCL is selected by a controller, the enabling signals (indicated in Figure 2-1 as CONTROLLER SELECT) permit transfers only to/from that controller.

2.1.1.2 Register Select Decoding and Registers – Register addressing is also an integral part of the asynchronous transfer process. The address of the register to be accessed is sent over the Massbus register select lines and multiplexed in the same manner as the control line signals. The output of the register select multiplexer is applied to register select decode logic which decodes the five bit address and then generates an enabling signal to the proper register for the register read or register write operation.

The DCL has 16 Massbus drive registers, all of which are readable by the controller. About half can also be written into. The DCL registers fall into the following categories:

Control Register – This read/write register receives all command codes from the controller and stores the command for the duration required to execute the command.

Status Register – This read only register provides status information to the controller regarding the state of the drive and regarding conditions within the DCL itself.

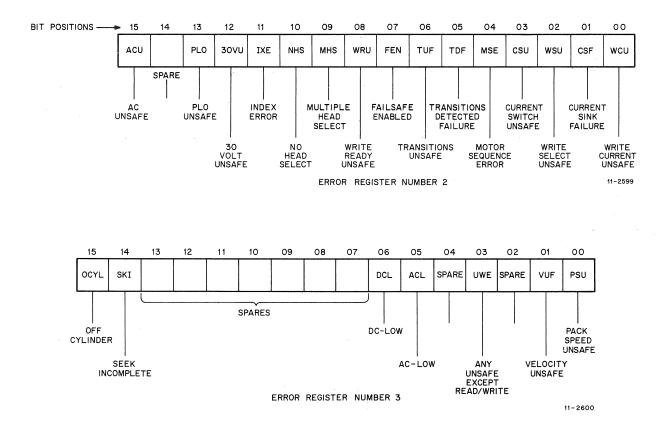

Error Registers – The DCL has three read/write error registers to convey Drive and DCL error information to the controller.

Maintenance Register – A read/write maintenance register that can be used for diagnostic purposes is provided.

Attention Summary Pseudo Register – There are two of these read/write registers (one for each controller) if the dual controller configuration is used.

Disk Addressing Registers – The DCL has five registers that are involved in accessing data from the disk. Three are read/write; two are read only.

Figure 2-1 Device Control Logic, Simplified Block Diagram

Serial No. and Drive Type Registers – These two read only registers are used for system housekeeping.

ECC Position and Pattern Registers – These two read only registers are used for error correction code handling.

2.1.1.3 Command Decoding – The command decoding logic interprets the outputs of the control register to determine which of the 17 possible commands is to be executed. Among these commands are the read/write commands (discussed later) that initiate synchronous data transfers. The seek command (Figure 2-1) is used to move the disk read/write heads between cylinders.

The offset mode is used to offset the read/write heads from the track centerline. The search command can be used to detect a particular sector of a track. A more comprehensive breakdown of the command repertoire is given later in this section.

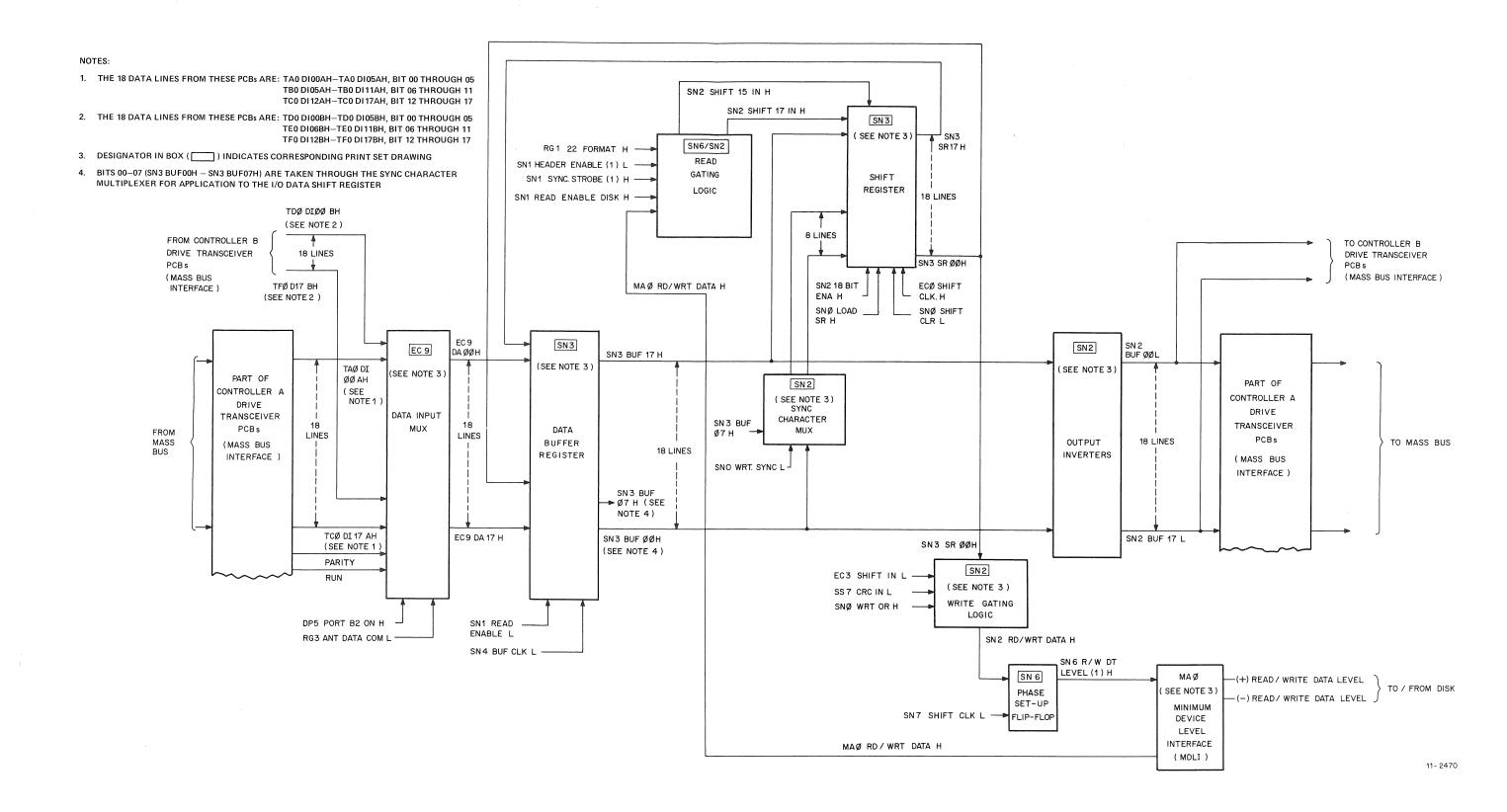

#### 2.1.2 Synchronous Data Transfers

Once the RP04 has been connected to a controller and a read/write command has been decoded, synchronous data transfers are implemented via the four blocks shown at the top of Figure 2-1. Controller A or B (having earlier accessed the DCL and therefore having control) transmits or receives data via the following circuit groups:

Massbus Synchronous Data Line Multiplexer – This logic steers 16/18-bit data words (refer to format bit in offset register) to or from the controller having access to the DCL. Once a controller has gained access, enabling signals (indicated here as CONTROLLER SELECT) are generated that permit transfers to/from only that controller.

Data Buffer Register – This register buffers 16/18-bit data words in one of two ways depending on transfer mode (write/read):

- During write operations this register accepts the data words from the multiplexer and presents them to the shift register.

- During read operations this register accepts data words from the shift register and presents them to the Massbus.

The time at which the data buffer register accepts a word is governed by the synchronous data transfer control logic. This logic takes into account such factors as the number of shift clocks required to empty/load the shift register before loading a new word into the data buffer register.

Shift Register – The shift register fulfills the parallel-to-serial conversion requirement during write operations and the serial-to-parallel conversion requirement during read operations. These conversions are accomplished as follows:

- Write operation: In this case, the shift register accepts 16/18-bit words in parallel from the data buffer register; then transfers the word a-bit-at-a-time (via the least significant bit position) until all 16/18 bits have been emptied from the shift register and written onto the disk. At this point the next data word is parallel loaded into the shift register.

- Read operation: In this case, the shift register accepts data words a-bit-at-a-time from the disk for application at the most significant bit position. When 16/18 shifts have been accomplished on the incoming data, a complete word is contained in the shift register. It is then presented in parallel to the data buffer register.

The shift pulses used to clock bits to/from the shift register are supplied from the synchronous data transfer control logic. The number of shift clocks supplied to fully shift a word depends on whether 16- or 18-bit words are being transferred.

Read/Write Gating Control Logic – This logic simply gates data from/to the disk depending on whether it is a read or a write operation. It also governs the length of the registers for 16- or 18-bit mode operation. If the DCL is in the 18-bit mode, two high order stages of the buffer and shift registers are enabled.

2.1.2.1 Synchronous Data Transfer Commands – The DCL interprets six basic read/write commands for transferring data words via the synchronous data path. These commands, and only these commands, activate the synchronous data transfer control logic to implement the data transfers. The six commands are:

Write Header and Data – Used for formatting each sector on the disk. Formatting consists of dividing each sector into fields to insert gaps of all zeros, control words (header), and data words (data field). This is necessary so that the DCL can address specific sectors of a track when using the other data transfer commands. The makeup and structure of the sector format are discussed in a later paragraph of this chapter.

Write Data – Used to write data into the data field of a sector. The address information is specified prior to executing the write command. The DCL uses this address information to find the correct sector and then initiates the write data transfer.

*Read Header and Data* – Executed to retrieve the header information as well as the contents of the data field of a sector. Address information must be supplied prior to executing the command so that the DCL can locate the proper sector and implement the read transfer.

Read Data Command – Similar to the read header and data command except that only the contents of the data field are sent to the controller. Again, proper header identification must be made prior to reading the data field words from the disk.

Write Check Header and Data.

Write Check Data.

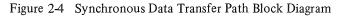

2.1.2.2 Synchronous Data Transfer Control Logic – This logic carries out all control operations inherent in executing the read/write commands for transferring data from/to the disk. The paragraphs that follow describe some of the more salient control operations and the reasons for them.

- Read/Write Command Interpretation The synchronous data transfer control logic must recognize the type of read/write command being executed to initiate the proper control sequence. That is, the control sequence employed when formatting a disk through use of the write header and data command is altogether different from that used when executing a read data command. Also, the clock signal used to develop shift clock pulses differs for the write and read modes. Furthermore, the proper control signals must be sent to the read/write control gating in keeping with the type of operation in progress.

- Clock (PLO/Read Data Strobe) Sector Clock and Index Pulses The DCL synchronous data transfer control logic receives clock, sector, and index pulses from the drive. The clock pulse is derived from one of two source signals depending on read/write mode. When reading, the read data strobe signal is used to develop the shift clock. In write operations, the phase locked oscillator (PLO) signal is used to develop the shift clock.

The sector clock is used to keep track of and to update the sector count as the disk revolves beneath the read/write heads. The sector count is important to the sector addressing technique employed by the DCL. There can be either 20 or 22 sectors per track depending on word length (i.e., 18-bit or 16-bit).

The index pulse is used to signify the beginning of each revolution.

- Shift Clock Pulse Uses Since each shift clock pulse represents a serial bit transfer time, it is used for counting as well as shifting data bits. The four uses of the shift clock pulse are listed below.

- 1. Clocks bit serially to/from the shift register for DCL to disk transfers.

- 2. Counts the number of bits shifted to determine when the shift register has been emptied or filled. This is necessary to inform the controller when to take or send a word.

- 3. Generates a byte clock so that the DCL is aware of what byte and word of a sector is passing beneath the disk read/write heads.

- 4. Serves as a clocking source in cyclic redundancy checking.

- Byte Count Development The synchronous data transfer control logic employs a byte counter to keep track of what part of a sector is being accessed. As stated earlier, each sector is broken up into fields during the formatting process. Each field must contain the same number of bytes when comparing one sector against another. Also, each field must begin at the proper byte count with respect to the sector pulse which defines the start of a sector. The synchronous data transfer control logic uses the count from the byte counter to determine when to read/write sync bytes, header words, and the data words that make up the data field of a sector.

- Sync Clock Generation The synchronous data transfer control logic also generates the sync clock signals to the controller that must be issued to effect each word transfer. During a write operation, the DCL issues the sync clock (telling the controller to send another word) after the shift register has been emptied and a word is parallel loaded into the shift register. During read operations, the DCL issues the sync clock (telling the controller to take another word) after the shift register has been filled and the word is loaded into the data buffer register.

#### 2.1.3 Disk Addressing Logic

The disk addressing logic actually includes a number of the registers within the register block on Figure 2-1. However, the disk addressing logic and sector compare logic are shown as separate blocks on the diagram to distinguish them as functions and to indicate their relationship to the seek and search commands respectively.

2.1.3.1 Cylinder/Track Addressing (Seek) – To select an addressed cylinder, the DCL and Drive must execute a seek, which means that the disk read/write heads must be mechanically moved to the desired cylinder address. The DCL employs a desired cylinder register (9 bits) to store the new cylinder address and a current cylinder address register (9 bits) to store the current position of the read/write heads. When the contents of both these registers is the same, no positioning of the read/write head (seek action) is required. Any change in the contents of the desired cylinder address register initiates a subtraction process that results in the DCL sending direction and magnitude information to the Drive. This information is, in turn, used by the Drive to carry out a seek operation. At the conclusion of a seek (meaning that the heads have been positioned at the desired cylinder), the desired cylinder address (now the current address) is entered into the current cylinder address register. At this time, both registers contain the same address. Following this, any updating or change of the contents of the desired cylinder address register results in the DCL and Drive executing a new seek. Updating the contents of desired cylinder address register can occur in any of the following ways:

• The controller executes a seek command. In this case, the desired cylinder address is loaded with the new desired cylinder address before the seek command code is loaded into the control register.

- The controller executes a read/write command having previously loaded a new cylinder address into the desired cylinder address register. This type of seek is called an "implied seek", because a seek command is not being executed, yet a seek operation must take place before the data transfer can start.

- The desired cylinder address is incremented following the last track of a cylinder when the DCL is executing an extended read/write operation. This is called a "mid-transfer" seek.

- A search command is executed and the previously loaded desired cylinder address differs from the current cylinder address.

The DCL disk addressing circuits employ subtraction logic using the outputs of both the desired cylinder address (DCA) register and current cylinder address (CCA) register to develop difference for the Drive. The cylinder difference (magnitude) of seek is generated by subtracting the contents of the CCA from the contents of the DCA. The disk addressing logic also supplies a seek direction signal to the Drive, informing it as to which way the read/write heads must be moved for the new cylinder address.

Track addressing is effective via a five bit portion of the desired sector/track address register and selects the desired read/write head of the drive.

2.1.3.2 Sector Addressing – New sector addresses accompanying operating system commands are inserted into a five bit portion of the desired sector/track register. This may be done when the operating system executes a search or any read/write command.

The DCL employs a sector counter (part of the synchronous data transfer control logic) to maintain synchronization between the DCL sector timing and the actual disk revolution in relation to the read/write heads. When the sector count matches the contents of the five bit sector address (in the desired sector/track register), the sector found condition occurs.

All read/write commands have desired sector addresses accompanying them. When the sector found condition occurs, it means that the synchronous data transfer control logic can initiate the control sequence for the read/write transfer.

Clearing the sector counter occurs once each revolution on assertion of the index signal from the Drive.

#### 2.2 MASSBUS AND MDLI (DRIVE) INTERFACE SIGNALS

The interface signals conveying control signals and data words from the DCL to the Massbus and from the DCL to the Drive are shown on Figure 2-2. These signals and their purposes are described in subsequent paragraphs.

#### 2.2.1 Massbus Interface Signals

Individual Massbus signal lines and signal group lines connecting the controller and DCL are described below:

- 1. SYNCHRONOUS DATA AND PARITY (19) LINES These lines convey 16-bit or 18-bit data and an associated parity bit. The synchronous data lines are bidirectional and employ odd parity. Data is transmitted synchronously using the sync clock signal supplied from the DCL and the write clock signal generated by the controller.

- 2. SYNC CLOCK Developed by the DCL during read/write data transfers to inform the controller to:

- Accept the data on the synchronous data lines during read operations. The controller accepts the data on the negation of the SYNC CLOCK signal and the DCL changes the data on the assertion of the SYNC CLOCK signal.

11-2474

Figure 2-2 Massbus and MDLI (Drive) Interface Signal

DEC 733 DRIVE

- Send the WRITE CLOCK during write operations. This informs the DCL to take the data word on the synchronous data bus lines.

- 3. WRITE CLOCK This signal is echoed by the controller in response to the SYNC CLOCK during write operations. On the assertion of the WRITE CLOCK the DCL accepts the data word. On the negation of this signal, the controller changes the data on the data bus lines.

- 4. RUN LINE After a data transfer command has been written into the control register of the DCL, the DCL connects to the synchronous data bus. The controller then asserts the RUN line to initiate the function. At the end of each sector, on the trailing edge of the EBL (end-of-block) pulse, RUN is sampled by the DCL. If it is still asserted, the function continues for the next sector; if it is negated, the function is terminated.

- 5. END-OF-BLOCK (EBL) This signal is asserted by the DCL at the end of each sector (after the last sync clock/pulse and the two ECC words). For certain error conditions where it is necessary to terminate operations immediately, EBL is asserted prior to the normal time for the last SYNC CLOCK. The data transfer is terminated prior to the end of the sector in this case.

- 6. EXCEPTION (EXC) This signal is asserted when an abnormal condition occurs in the DCL. The DCL asserts this signal to indicate an error during a data transfer command. EXCEPTION is asserted at or prior to assertion of EBL and is negated at the negation of EBL.

- 7. CONTROL BUS The parallel control and status path consists of a 16-bit parallel data path and an associated parity bit. The control and status lines are bidirectional and employ odd parity.

- 8. DRIVE SELECT These four lines transmit a 4-bit binary code from the controller to select a particular DCL/Drive. The DCL responds when the (unit) select number in the DCL corresponds to the transmitted binary code.

- 9. CONTROLLER-TO-DRIVE This signal is generated by the controller and indicates the direction in which control and status information is to be transferred. For a controller-to-Drive transfer, the controller asserts this signal. For a Drive-to-controller transfer, this signal is negated by the controller.

- 10. REGISTER SELECT These five lines transmit a 5-bit binary code from the controller to the DCL. The binary code selects one of the DCL registers.

- 11. DEMAND This signal is asserted by the controller to indicate that a transfer is to take place on the control bus. For a controller-to-DCL transfer, DEMAND is asserted by the controller when control line information is present and settled on the control bus. For a DCL-to-controller transfer, DEMAND is asserted by the controller to request data and is negated when the data has been strobed off the control bus.

- 12. TRANSFER This signal is asserted by the DCL in response to DEMAND. For a controller-to-DCL transfer, TRANSFER is asserted when the data is strobed off of the control lines and is negated when DEMAND is negated. For a DCL-to-controller transfer, TRANSFER is asserted after the data is asserted on the control bus and negated when the negation of DEMAND is received.

- 13. ATTENTION This line is shared by all eight DCL's attached to a controller; it may be asserted by any DCL as a result of an abnormal condition or status change in the DCL. An ATA status bit in each DCL is set whenever that Drive is asserting the ATTN line.

This signal may be asserted for any of these reasons:

- An error, while no command is being executed (asserted immediately).

- At the completion of a command if an error occurred during execution of the command.

- Completion of a non-data transfer command (such as SEARCH).

The ATTENTION bit in a DCL may be cleared by the following actions:

- Asserting INITIALIZE on the Massbus (affects all eight Drives).

- Writing a 1 into the Attention Summary register (in the bit position corresponding to the address of the asserting Drive). This clears the ATTENTION bit; however, it does not clear the error.

- Writing a valid command (with the GO bit set) into the DCL Control register when no composite error is preset. Note that clearing the ATTENTION bit of one DCL does not always cause the ATTN line to be negated because other DCLs may also be asserting the line.

- 14. INITIALIZE This signal is asserted by the controller to perform a system reset of all DCLs. When a DCL receives the INITIALIZE pulse, it immediately aborts the execution of any current command.

- 15. MASS FAIL When asserted, this signal indicates that a power-fail condition has occurred in the controller.

#### 2.2.2 MDLI (DRIVE) Interface Signals

Control and data lines used to transfer signals between the DCL and Drive are also on Figure 2-2. These signals are described in the handbook for the Drive. Some of the more fundamental signals are shown on Figure 2-1 and described in the paragraphs covering this illustration.

#### 2.3 COMMAND REPERTOIRE

The subsequent paragraphs describe the reaction of the DCL to control commands, as well as the range and type of commands executable within the DCL itself.

#### 2.3.1 Control Commands

Execution of a control command by the controller causes transfer of control/status information over the 17 control bus lines (Figure 2-2).

Execution of a control command by the controller always results in the reading or writing of an addressed DCL register. Consequently, a register select code, supplied over the five register select lines, must always be present when the controller executes a command code. Further, the DCL device code must also be supplied over the drive select lines. When the register selected is the control register and the controller writes into this register (i.e., with the low order bit, called the GO bit, set), one of the 17 commands executable by the DCL is initiated.

A summary of the 16 registers that can be sampled and written into by the controller is listed as follows.

| Register Name                 | Register Select Code<br>(Octal) | Unibus Address**<br>(Octal) |

|-------------------------------|---------------------------------|-----------------------------|

| Control*                      | 00                              | 776700                      |

| Status*                       | 01                              | 776720                      |

| Error Register No. 1*         | 02                              | 776714                      |

| Maintenance*                  | 03                              | 776724                      |

| Attention Summary*            | 04                              | 776716                      |

| Desired Sector/Track Address* | 05                              | 776706                      |

| Look Ahead                    | 07                              | 776720                      |

| Drive Type                    | 06                              | 776726                      |

| Serial No.                    | 14                              | 776730                      |

| Offset*                       | 11                              | 776732                      |

| Desired Cylinder Address*     | 12                              | 776734                      |

| Current Cylinder Address      | 13                              | 776736                      |

| Error Register No. 2*         | 10                              | 776740                      |

| Error Register No. 3*         | 15                              | 776742                      |

| ECC Position                  | 16                              | 776744                      |

| ECC Pattern                   | 17                              | 776746                      |

\*Indicates register can also be written.

\*\*Code conversion of two low order octal digits is accomplished by related controller.

#### 2.3.2 Data Transfer Commands

The DCL executes the following data transfer commands when the related command code is written into the control register:

- 1. Write header and data (formatting), 638

- 2. Write data, 618

- 3. Read header and data, 738

- 4. Read data, 718

- 5. Write check header and data,  $53_8$ . The decode of this command is ORed with that of the read header and data. As such the DCL executes the same control sequence.

- 6. Write check data  $51_8$ . The decode of this command is ORed with that of the read command. Hence, the DCL treats it as a read command.

- 7. Search. The search command does not actually transfer data. However, it does inform the controller that the desired sector has been found, and consequently, the software can go ahead and initiate a data transfer. Its principal uses are in disk use optimization and rotational position sensing.

A brief description of the activities carried out by the DCL for each of these commands is given below:

- When formatting (write header and data command), the DCL writes all fields of a sector (including header field and data field) onto the disk and inserts each field in its proper position with respect to the sector pulse. (The sector pulse defines the start of a sector.)

- Write data. This command is used to write the 256-word data field of a sector. The DCL makes proper identification of the addressed cylinder track and sector by reading and verifying the header before beginning the write operation.

- Read Header and Data. When executing this command, both the header and data fields of a sector are sent to the controller. Proper identification of the sector only is required before the transfer is initiated.

- Read Data. In this case, the DCL sends only the data field of a sector. Again, proper header identification is made before beginning the transfer.

Data transfer commands may include an implied seek if the desired cylinder address (accompanying the command) does not match the current cylinder address. When there is a difference between the desired cylinder address and the current cylinder address on execution of a data transfer command, the DCL executes a seek to position the disk read/write heads at the addressed cylinder. The DCL then searches the disk (on the addressed track) for the desired sector and when found, initiates the data transfer.

#### 2.3.3 Housekeeping Commands

The housekeeping commands used by the DCL and their individual purposes are as follows:

- 1. NO-OP. This command does nothing and is used as a filler command by the software.

- 2. DRIVE CLEAR. The following registers and conditions within the DCL are cleared by this command.

- Status Register (ATA and ERR status bits)

- All three Error Registers

- Attention Summary Register

- ECC Position and Pattern Registers

- The Diagnostic Mode Bit

- 3. INITIALIZE SIGNAL. This MASSBUS interface signal performs the same functions as the DRIVE CLEAR command, but does not require that the Drive be ready (i.e., it bypasses the control register).

- 4. PACK ACKNOWLEDGE. This command sets the volume valid bit for the commanding controller. This command must be issued before any data transfer or positioning commands can be given if the drive has gone off-line and then on-line. It is primarily intended to avoid unknown disk pack changes.

- 5. READ-IN PRESET. This command sets the VV (volume valid) bit, clears the desired sector/track address register, clears the desired cylinder address register, and clears the FMT, HCI, and ECI bits in the offset register. It is used to bootstrap the device.

- 6. RELEASE. This command performs a drive clear function and releases the Drive for use by the other controller.

#### 2.3.4 Mechanical Movement Commands

All of the below commands require movement of the Drive read/write heads as part of their execution sequence.

- 1. SEEK. This command causes the heads to be moved over the desired cylinder. Once the heads are positioned, the desired cylinder address becomes the current cylinder address since they are now the same.

- 2. OFFSET. This command is executed as a "micro" seek. It allows the read/write heads to be moved off the track center line. This command is used as part of the error recovery process and requires 10 ms to execute, regardless of the offset value.

- 3. RETURN TO CENTER LINE. This command is used to return the read/write heads to the track center line after an offset operation.

- 4. RECALIBRATE. This command positions the read/write heads over cylinder zero, and resets the current cylinder address register to zero. This command takes a maximum of 500 ms to complete.

- 5. UNLOAD. This command is used to place the drive in the STANDBY state. The heads are retracted, the spindle powered down, and the STANDBY light lit. This command completes when the Drive is brought back on-line (up to speed and heads loaded).

#### 2.4 DETAILED BLOCK DIAGRAM DISCUSSION

#### 2.4.1 Massbus Control Signal Routing and DCL Interface Registers

A block diagram showing the circuits used to route control line data from/to the controller and all interface control registers within the DCL is illustrated in Figure 2-3. The command decoding logic used to interpret the contents of the control register is also shown on this illustration.

Since the DCL can be accessed by either of two controllers, enabling signals that permit transfer to/from one particular controller at any given time must be generated. A controller gains access to the DCL when it asserts its DEMAND line at a time when the DCL is free (i.e., at a time when the other controller has not pre-empted the DCL through an earlier access).

**2.4.1.1 Control Line Enabling Signals** – The enabling signals (allowing transfer over the control lines) generated following access by a controller are defined below:

1. Controller A has access and is writing a DCL register. Signal DP3 REC CONT EN A H enables the related receivers to apply the 16-bit control line information to the control bus input multiplexer. Only the receivers are enabled since the Control-to-Drive (CTOD) signal is asserted when transferring to the DCL (Figure 2-3).

Figure 2-3 DCL Interface Registers and Massbus Control Signal Routing Block Diagram

2. Controller A has access and is reading one of the DCL registers. In this case, signal DP3 TRAS A EN H is asserted to enable the transmitters to send the outputs of the control bus output register/A attention read multiplexer to the controller.

#### NOTE

The eight low order bits from the control bus output register are taken through a multiplexer that also receives the outputs of the controller A attention register. This arrangement permits controller A to sample the status of the attention register at times when it does not have control of the DCL. This feature is discussed in a later paragraph.

Because controller A has access in this instance, signal DP5 PORT A ON (0) H is not asserted. This allows the multiplexer to pass on the low order byte from the control bus output register and not the output of the controller A Attention Register.

- 3. Controller B has access and is sending 16-bit information over the control bus. In this case, signal DP3 REC CONT EN B H is asserted in the same way as described for Controller A.

- 4. Controller B has access and is sampling the contents of the DCL register. In this case, signal DP3 TRAS B EN H is asserted in the same way as described for Controller A.

When a controller is sending information over the control bus, it is to write the control information into one of the DCL registers. The transfer path in this situation involves the receivers, control bus input multiplexer, and the addressed (selected) register.

To write control data into any register, signal RG5 WRT REG L must be asserted (this signal is generated only when the control-to-drive, CTOD, signal is asserted to indicate that the direction of transfer is to the DCL).

When a register is being sampled by a controller, the routing path is through an associated multiplexer. (In all but one case, one multiplexer serves two registers.) The signals are then applied to the control bus output register for transfer to the controller via the related read multiplexer and transmitter circuits.

All multiplexer circuits feeding the control bus output register have their outputs wire ORed. The multiplexer enabling signals that select the outputs of one register rather than another are the same as the signals used to select a particular register. The register selection signals are listed in the following table:

| Register Name               | Selection Signal      |

|-----------------------------|-----------------------|

| Control                     | RG5 CONT REG SEL L    |

| Status                      | RG5 STAT REG SEL L    |

| Error Reg No. 1             | RG5 ERR REG 01 SEL L  |

| Maintenance                 | RG5 MAINT REG SEL L   |

| Attention Summary           | DP2 ATA REG SEL A/B H |

| Desired Cylinder<br>Address | RG5 DES CYL ADR SEL L |

| Register Name               | Selection Signal      |

|-----------------------------|-----------------------|

| Current Cylinder<br>Address | RG5 CUR CYL ADR SEL L |

| Error Reg 02                | RG5 ERR REG 02 SEL L  |

| Error Reg 03                | RG5 ERR REG 03 SEL L  |

| ECC Position                | RG5 ECC POS REG SEL L |

| ECC Pattern                 | RG5 ECC PAT REG SEL L |

2.4.1.2 Attention Summary Register Access – The manner and path in which an attention summary register is sampled by a controller depends on whether the DCL is free for access or currently engaged by one of the two controllers. For example, assume that the DCL is not currently engaged and it raises the ATTENTION interface line. Assume further that controller A is the first of the two controllers to sample the attention summary register to determine which Drive unit raised the ATTENTION line. In such a situation, controller A gains access to the DCL and samples the attention register via the following path: attention register multiplexer, Drive address decode network, control bus output register, A attention register read multiplexer, and the controller A transmitter circuits. If it is further assumed in this example that controller B attempts to read the attention summary register (after controller A has already gained access), it too can sample the register but the transfer now takes place over a different path. The transfer path to controller B is directly through the B attention read multiplexer. From Figure 2-7, it can be seen that this in no way affects paths to controller A which currently has access to the DCL. When controller B attempts to access the status register after accessing the attention summary register, it is supplied with an all zeros status, meaning that controller A has control.

2.4.1.3 DCL Interface Registers – The subsequent paragraphs describe the interface registers within the DCL.

• Control Register (00) and Command Decoding – The control register is addressed (selected) by the controller when the five Register Select lines convey all zeros. The control register is used to store the command code as shown below.

| 15 | 14 | 13 | 12 | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|----|----|----|----|-----|----|---|---|---|---|---|---|---|---|---|----|

|    | _  |    |    | DVA | -  | _ |   |   | _ |   |   |   |   |   | GO |

- DVA Device Available (For status sampling)

- F1-F5 Function Code

- GO GO bit

**Control Register Format**

The GO bit can be considered an extension of the function code since it must be set (and also the RUN line must be high) for the DCL to execute the specified command. The five bit function (F1-F5) specifies the type of command to be executed. The Function Code and related commands are listed below.

|     | Fun | ction | Code |     | Command                       |

|-----|-----|-------|------|-----|-------------------------------|

| F5  | F4  | F3    | F2   | F1  |                               |

| 0   | 0   | 0     | 0    | 0   | No operation                  |

| 0   | 0   | 0     | 0    | 1   | Unload (stand-by)             |

| 0   | 0   | 0     | 1    | 1   | Recalibrate                   |

| 0 " | 0   | 1     | 0    | 0   | Drive Clear                   |

| 0   | . 0 | 1     | 0    | 1   | Release (dual-port operation) |

| 0   | 1   | 1     | 0    | 0 0 | Search Command                |

| 1   | 0   | 1     | 0    | 0   | Write Check Data              |

| 1   | 0   | 1     | 0    | 1   | Write Check Header and Data   |

| 1   | 1   | 0     | 0    | 0   | Write Data                    |

| . 1 | 1   | 0     | 0    | 1   | Write Header and Data         |

| 1   | 1   | 1     | 0    | 0   | Read Data                     |

| 1   | 1   | 1     | 0    | 1   | Read Header and Data          |

| 0   | 0   | 0     | 1    | 0   | Seek Command                  |

| 0   | 0   | 1     | 1    | 0   | Offset Command                |

| 0   | 0   | 1     | 1    | 1   | Return to Centerline          |

| 0   | 1   | 0     | 0    | 1   | Pack Acknowledge              |

| 0   | 1   | 0     | 0    | 0   | Read-In Preset                |

| 1   | 1   | 0     | 1    | 0)  |                               |

|     | Т   | hroug | h    | , } | Illegal Functions             |

| 1   | 1   | 1     | 1    | 1   |                               |

The device available (DVA) bit is used for controller status sampling. This bit is set if sampled by the controller that has gained control of the DCL. It is reset (meaning that the device is not available) to the controller that does not have control.

• Status Register – The status register informs the controller of various conditions within the DCL and the Drive. The format and the meaning for each bit position are shown below.

|      |       |                            |           |                   |               | 10                  | <u> </u> | )9 | 08             | 0          | 7 C        | 6   | 05  | 04                         | 03   | 02                       | 01                   | 0                     |     |

|------|-------|----------------------------|-----------|-------------------|---------------|---------------------|----------|----|----------------|------------|------------|-----|-----|----------------------------|------|--------------------------|----------------------|-----------------------|-----|

| AT/  | A EF  | R P                        | IP        | MOL               | WRL           | LS                  | TP       | GМ | DPR            | DR         | Y V        | v   | DE1 | DL64                       | GRV  | DIGB                     | DF2                  | D DF5                 |     |

|      | COMPO |                            |           | MEDIUM<br>DN-LINE |               | LAS<br>SECT<br>TXFI | OR       |    | DRIVE<br>PRESE |            | VOL<br>VAI | UME |     | IFFEREN<br>LESS<br>THAN 64 |      | DRIV<br>TO INN<br>ARD BC | IER                  | DIF<br>FORWA<br>5" SI | ARD |

| ACTI |       | POSIT<br>OPER<br>I<br>PROC | ATIO<br>N | N                 | WRITE<br>LOCK |                     | OGRA     |    |                | DRI<br>REA |            |     |     |                            | REVE | RSE                      | DIF<br>FORW<br>20" : | ARD                   |     |

Bits 0-5 are used to monitor the drive read/write head loading sequence. Following a successful head loading sequence, these bits are always cleared. On an unsuccessful head loading, the particular bits that are set inform the operating/diagnostic system of the type of fault. A detailed breakdown of all bit meanings is given below:

- 1. Bit 0: Drive Forward 5 in./sec (DF5) The DCL has detected the drive forward 5 in./sec signal while in the head load mode after a start pulse was recognized. This bit is reset by the File Ready signal at the completion of a head load sequence.

- 2. Bit 1: Drive Forward 20 in./sec (DF20) The DCL has detected the drive forward 20 in./sec signal during a head load sequence. This bit is reset by File Ready at the completion of a head load sequence.

- 3. Bit 2: Drive to Inner Guard Band (DIGB) The DCL has detected the drive to inner guard band signal during a head load sequence. This bit is reset by a File Ready at the completion of the head load sequence.

- 4. Bit 3: Go Reverse (GRV) The DCL has detected the GO Reverse signal during a head load sequence. This bit is reset by File Ready at the completion of a head load sequence.

- 5. Bit 4: Difference Less than 64 (DL64) The DCL has detected a value less than 64 in the difference counter during the reverse seek of the head load sequence. This bit is reset by a File Ready at the completion of a head load sequence.

- 6. Bit 5: Difference Equals 1 (DE1) The DCL has detected a value equal to 1 in the difference counter during a head load sequence. The bit is reset by a File Ready at the completion of a head load sequence.

- 7. Bit 6: Volume Valid (VV) The "Volume Valid" status bit indicates when a disk pack may have been changed, and therefore the program should not assume anything about the identity of the pack. Even though only one VV bit exists in the dual-controller application, VV-A is accessible only to controller A and VV-B is accessible only to controller B. The VV status bit is reset by the DCL whenever the drive cycles up (from the off state). The "Pack Acknowledge" command or "Read in Preset" command, when received from either controller, causes the VV bit to set for that controller.

- 8. Bit 7: Drive Ready (DRY) At the completion of every command, data handling or mechanical motion, the DCL sets this bit. The controller should not attempt to issue another command if this bit is reset. This bit indicates the readiness of the RP04 DCL to accept a new command. The (DRY) bit is associated with the following conditions:

- If the command is read or write type, the setting of the DRY bit indicates normal termination. If an error was made during data transfer, the appropriate error bits are set as well.

- If the command is mechanical movement command, both the ATA bit and the DRY bit are set at the completion of the command. If an error was committed during the command, the appropriate error bits are also set.

The DRY bit status during the various stages of the DCL operation is shown in Table 2-1. The ATA bit associated with the DRY bit functions is shown in the table only if no error conditions exist (normal termination). At the completion of the operation, the DRY bit is set.

| Operation             | DRY | PIP | ATA at End?<br>(No Error) |

|-----------------------|-----|-----|---------------------------|

| No Operation          | 1   | 0   | No                        |

| Unload (Stand-by)     | 0   | 1   | Yes                       |

| Recalibrate           | 0   | 1   | Yes                       |

| Drive Clear           | 1   | 0   | No                        |

| Release               | 0   | 0   | No                        |

| Search Command        | 0   | 1   | Yes                       |

| Implied Search        | 0   | 0   | No                        |

| Seek                  | 0   | 1   | Yes                       |

| Offset                | 0   | 1   | Yes                       |

| Write Check           | 0   | 0   | No                        |

| Write Data            | Ó   | 0   | No                        |

| Write Header and Data | 0   | 0   | No                        |

| Read Data             | 0   | 0   | No                        |

| Read Header and Data  | 0   | 0   | No                        |

| Implied Seek          | 0   | 0   | No                        |

| Mid-Transfer Seek     | 0   | 0   | No                        |

| Return to Centerline  | 0   | 1   | Yes                       |

| Pack Acknowledge      | 1   | 0   | No                        |

| Read-In Preset        | 1   | 0   | No                        |

Table 2-1 DRY/PIP/ATA Status During DCL Operation

9. Bit 8: Drive Preset (DPR) – On a single-controller type operation this bit is always set. On dual-controller type operation, this bit will be reset if the DCL is busy from the other controller.

The DPR bit is set again when the RP04 switches from the other controller to this one.

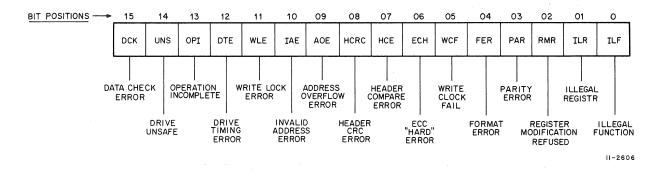

In general, setting the DPR bit indicates that the DCL is connected to the asynchronous control bus of this controller.