SPDG.

÷.,

EK-MXV1B-UG-001

# MXV11-B Multi-Function Option Module

User Guide

# CONTENTS

### CHAPTER 1 GENERAL DESCRIPTION

į

| 1.1   | General                                  | 1 |

|-------|------------------------------------------|---|

| 1.2   | Read/Write Memory                        | 1 |

| 1.3   | MOS RAM Battery Backup                   | 1 |

| 1.4   | Read Only Memory                         | 2 |

| 1.4.1 | Direct Addressing Mode                   | З |

| 1.4.2 | ROM Window Map                           | З |

| 1.5   | Serial Line Units                        | 5 |

| 1.6   | Line Time Clock                          | 5 |

| 1.7   | LED Diagnostic Display Register          | 6 |

| 1.8 , | MXV11-B2 Bootstrap/Diagnostic ROM Option | 6 |

| 1.9   | Specifications                           | 7 |

| 1.9.1 | Physical Specifications                  | 7 |

| 1.9.2 | Environmental Specifictions              | 7 |

| 1.9.3 | Random Access Memory Specifictions       | 7 |

| 1.9.4 | Electrical Specifictions                 | 8 |

|       |                                          |   |

### CHAPTER 2 FUNCTIONAL DESCRIPTION

| 2.1   | General                           |

|-------|-----------------------------------|

| 2.2   | PROM Addressing 9                 |

| 2.2.1 | Direct Addressing 9               |

| 2.2.2 | I/O Page Addressing 10            |

| 2.3   | RAM Memory Functional Description |

| 2.3.1 | Read/Write Access 12              |

| 2.3.2 | Refresh Access 14                 |

| 2.3.3 | Arbitration Logic 14              |

| 2.4   | Crystal Oscillator 15             |

| 2.5   | Line Time Clock 16                |

| 2.6   | Diagnostic Display Register 16    |

| 2.7   | Serial Line Units 17              |

| 2.7.1 | Address Selection 17              |

| 2.7.2 | Interrupt Vector Selection 18     |

| 2.7.3 | SLU Register Addressing 18        |

| 2.7.4 | Baud Rate Selection 24            |

| 2.8   | Cables                            |

| 2.8.1 | Interface Connector Pins 29       |

| 2.8.2 | Current Loop 30                   |

|       |                                   |

iii

### CONTENTS

# HAPTER 3 JUMPER CONFIGURATIONS

| 1    | General                          |

|------|----------------------------------|

| 2    | Jumper Configurations 53         |

| 3    | ROM Configurations 54            |

| .3.1 | User Mode (Direct Addressing) 55 |

| .3.2 | Boot Mode (Page Addressing) 55   |

| .3.3 | Boot Mode (Direct Addressing) 57 |

| .4   | SLU Configurations 57            |

| .5   | Line Time Clock Control 58       |

| .6   | LTC Frequency 58                 |

化油油合金

# CHAPTER 4 MAINTENANCE AND DIAGNOSTICS

| General 59                               |

|------------------------------------------|

| Data Testing 59                          |

| Serial Line Unit Testing 59              |

| Program Options and Defaults 60          |

| Execution Times 63                       |

| Power Fail 63                            |

| Error Handling                           |

| Device Registers 64                      |

| Summary of Tests and Special Subroutines |

| System Requirements 69                   |

| Operating Instructions                   |

| Loading and Starting Procedures          |

| Operational Switch Settings 71           |

|                                          |

## APPENDIX A PROGRAMMING SUMMARY

### FIGURES

| 1-1  | MXV11-B Simplified Block Diagram 2          |

|------|---------------------------------------------|

| 1-2  | ROM Window Map Addresses 3                  |

| 1-3  | Page Control Register 4                     |

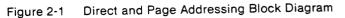

| 2-1  | Direct and Page Addressing Block Diagram 10 |

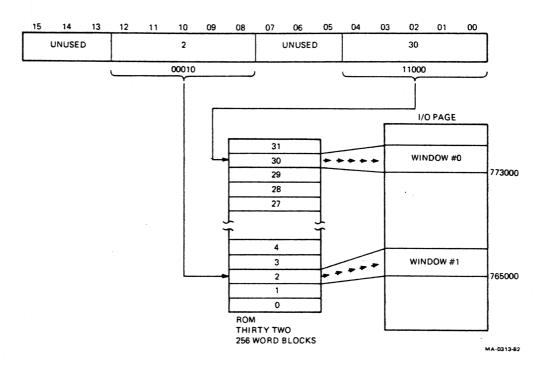

| 2-2  | Page Mode Addressing 11                     |

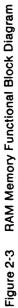

| 2-3  | RAM Memory Functional Block Diagram         |

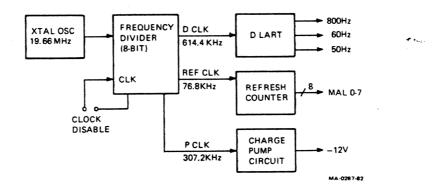

| 2-4  | XTAL Oscillator Block Diagram 15            |

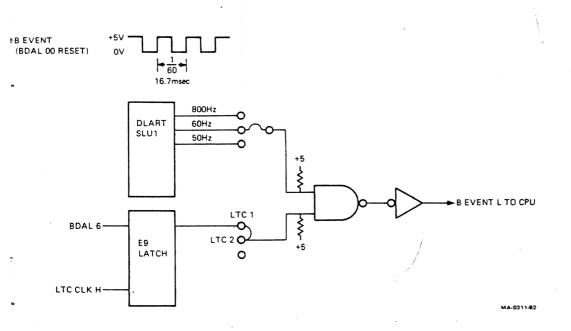

| 2-5  | Line Time Clock Diagram 16                  |

| 2-6  | MXV11-B Diagnostic Register 17              |

| 2-7  | SLU Vector Address Bit Format 18            |

| 2-8  | SLU Register Addressing 23                  |

| 2-9  | MXV11-B EIA Cable Configurations            |

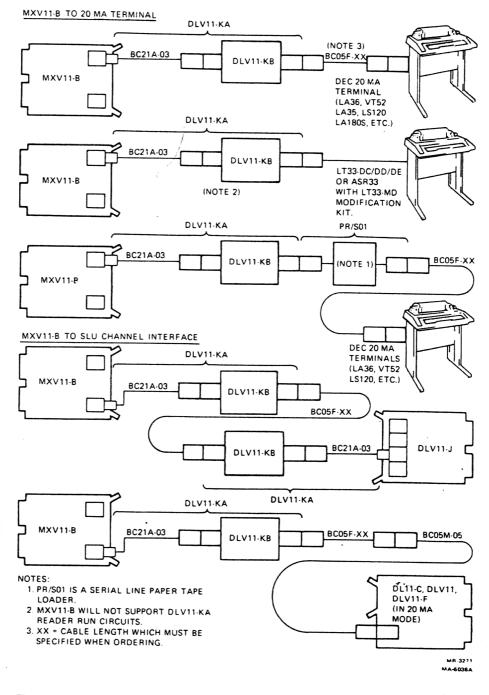

| 2-10 | MXV11-B 20 mA Cable Configurations 27       |

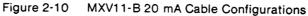

| 2-11 | BC21 B-05 Modem Cable 28                    |

| 2-12 | BC20 N-05 Null Modem Cable 28               |

| 2-13 | MXV11-B Connector Pins 30                   |

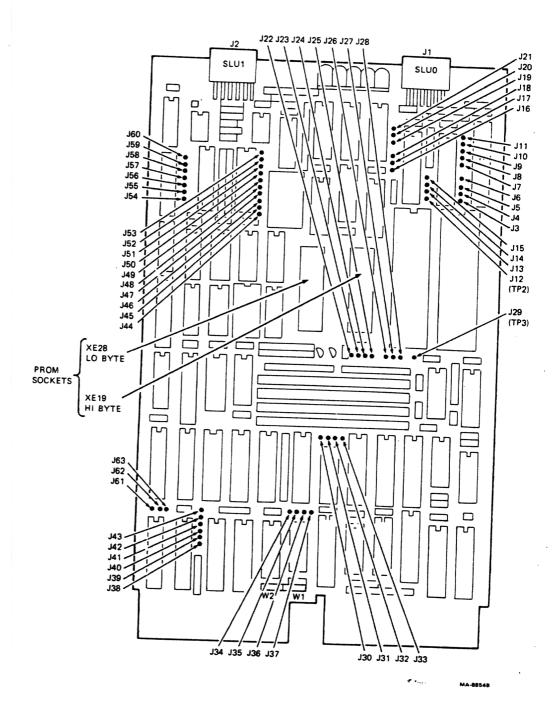

| 3-1 | Default Configuration of Push-On Connectors | 32 |

|-----|---------------------------------------------|----|

| 3-2 | MXV11-B Jumper Locations                    |    |

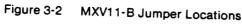

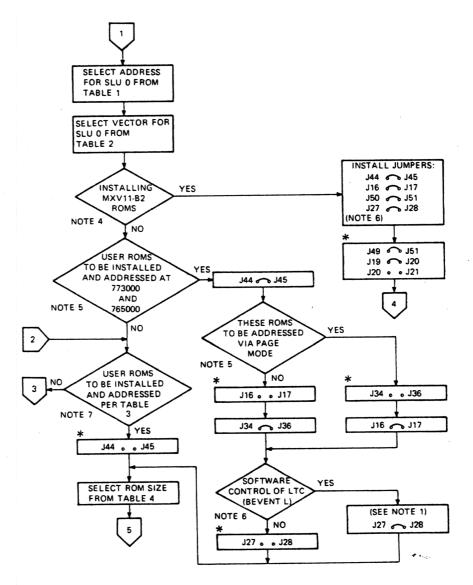

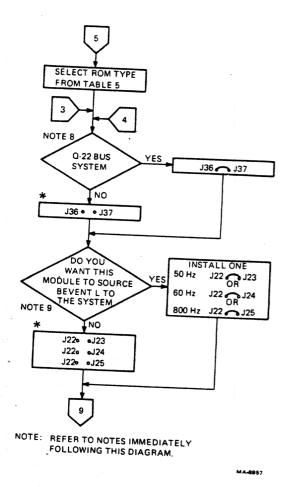

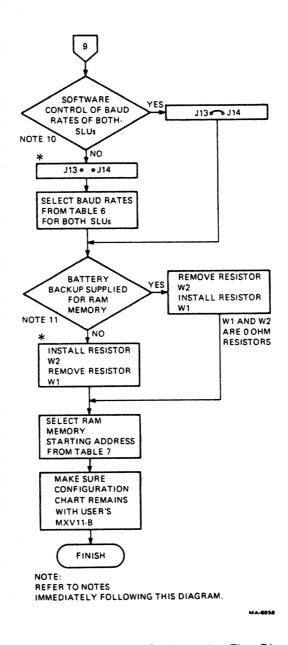

| 3-3 | Jumper Configuration Flow Diagram           |    |

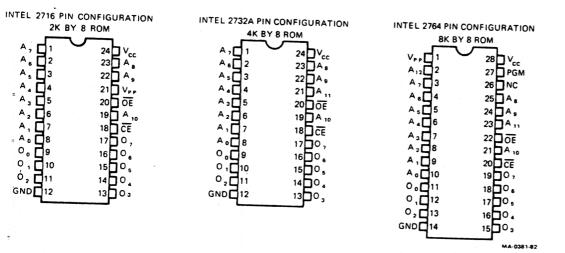

| 3-4 | PROM Chips                                  |    |

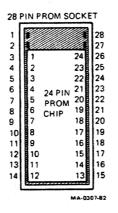

| 3-5 | Insertion of 24-Pin PROM Chips              | 55 |

### TABLES

| 1-1   | ROM Window Addresses for 16-, 18-, and 22-bit Q-bus | 4  |

|-------|-----------------------------------------------------|----|

| 2-1   | ROM Window Map                                      | 12 |

| 2-2   | Receiver Status Register Bit Assignments (RCSR)     | 18 |

| 2-3   | Receiver Data Buffer Bit Assignments (RBUF)         | 20 |

| 2-4   | Transmitter Status Register Bit Assignments (XCSR)  | 21 |

| 2-5   | Transmitter Data Buffer Bit Assignments (XBUF)      | 22 |

| 2-6   | Definition of Cables                                | 25 |

| 2-7   | MXV11-B I/O Connector Pin Functions                 | 29 |

| 3-1   | Jumper Connections for MXV11-B                      | 41 |

| 3-2 🕜 | Miscellaneous Jumper Configurations                 | 43 |

| 3-3   | Jumpers for PROM Starting Address                   | 47 |

| 3-4   | Serial Line Unit Baud Rates                         | 48 |

| 3-5   | Serial Line Unit Starting Address Jumpers           | 48 |

| 3-6   | Jumpers for SLU Vector Addresses                    | 49 |

| 3-7   | RAM Starting Address Jumpers                        | 50 |

| 3-8   | PROM Jumpers                                        | 52 |

| 3-9   | Jumpers to Configure PROM Size                      |    |

| 3-10  | Jumper Connections for PROM Sizes in User Mode      | 56 |

| 3-11  | Jumper Connections for PROM Sizes in Boot Mode      |    |

|       | (Page Addressing)                                   | 56 |

| 3-12  | Jumper Connections for PROM Sizes in Boot Mode      |    |

|       | (Direct Addressing)                                 | 57 |

|       |                                                     |    |

### GENERAL DESCRIPTION

### 1.1 GENERAL

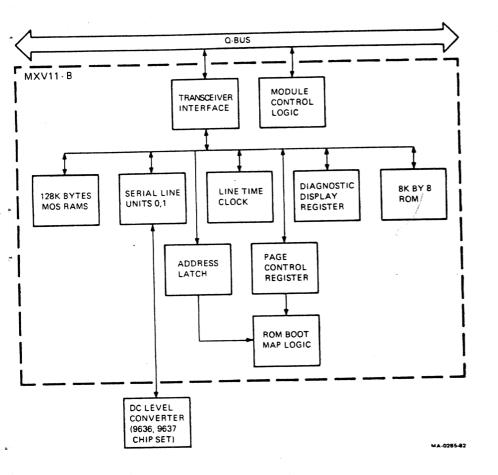

The M7195 module, designated MXV11-B, is a dual-height, multi-function option module compatible with LSI-11, LSI-11/2 and LSI-11/23 processors. The module can operate on the 22-bit Q-bus (up to 316K words), the 18-bit Q-bus, and the 16-bit Q-bus. MXV11-B features include:

- Read/write memory capability (MOS RAM)

- 5 V battery backup for MOS RAMs

- Read only memory (ROM)

- ROM window map logic (page control register)

- Two asynchronous serial line ports (SLU0, SLU1)

- Multiple line time clock frequencies

- LED diagnostic display register.

NOTE: The page control register, line time clock register, and diagnostic display register are user options and can only be selected if the MXV11-B is strapped for console port and bootstrap mode. Also, the Halt or Boot functions may be optionally selected in this configuration.

The following paragraphs describe these features. Figure 1-1 is a simplified block diagram of the module.

### 1.2 READ/WRITE MEMORY

The MXV11-B read/write memory consists of 128K bytes of dynamic MOS RAM without parity. The MOS RAMs operate off the system's +5 V supply or from the +5 V battery backup via a jumper consisting of a 0 ohm resistor. On-board memory refresh is included and is transparent to the user.

The read/write memory is configured from 64K SIPs (single in-line package). Four SIPs provide 64K 16-bit words or 128K bytes. RAM starting addresses are from 0 to 252K words on 4K word boundaries. This memory does not respond to addresses in the I/O page.

#### **1.3 MOS RAM BATTERY BACKUP**

The MXV11-B provides battery backup for the MOS RAMs. The battery backup must be jumpered to be functional, and battery backup power must be supplied by the system. A green light emitting diode connects across the MOS RAM power supply and ground to show that power is on to the RAMs.

1

### 1.4 READ ONLY MEMORY

Two 28-pin sockets on the +5 V read only memories (ROMs) contain bootstrap code, diagnostic code, or user routines. Wire-wrap posts allow the insertion of 2K by 8, 4K by 8, or 8K by 8 PROMs/ROMs in these sockets.

The PROM/ROM devices used may be ultra-violet Eraseable Programmable Read Only Memories, fusible link Programmable Read Only Memories, or masked Read Only Memories.

The 28-pin sockets can house user PROMs or the MXV11-B2 ROM set. If user PROMs are installed and are located in the user area (00000 through 077776 octal), the PROMs may only be directly addressed. If the user PROMs are located in the boot area, 773000<sub>8</sub>, 765000<sub>8</sub> (18-bit address) they may be directly or indirectly addressed by a window mapping technique. (Refer to Paragraphs 1.4.1 and 1.4.2.)

If the MXV11-B2 ROM set is installed in the sockets, it can only reside in the boot area and may only be addressed by the window mapping technique.

Any size PROM (2K by 8, 4K by 8, or 8K by 8) can be addressed directly or indirectly via window mapping. One exception to this is the 2K by 8 UV (ultra violet) PROM which may be addressed only through direct addressing.

*NOTE:* To prevent wraparound, the PROM 1 and PROM 2 jumpers must be set to the correct PROM size.

### 1.4.1 Direct Addressing Mode

In direct addressing, ROM will reside in main memory, with starting addresses on any 4K word boundaries under 16K words (000000-777776 if 18-bit addressing is used). If that word bank is selected, only the space containing ROM is enabled, preventing "wraparound." Any read request made to ROM, where no ROM exists, results in no response from the module.

NOTE: All addresses specified in this manual are 18-bit.

Direct addressing can be used to access ROM in the I/O page when the ROM is used for bootstrapping. The bootstrap area consists of a 256 word block in the address range from 773000 to 773776. If an access is made to the ROM outside the bootstrap area, there is no response unless it is the address of an actual device in the system.

### 1.4.2 ROM Window Map

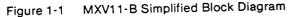

The ROM in the MXV11-B uses two windows in the I/O page. Each window points to 32 256-word blocks in ROM. This method of pointing prevents the whole I/O page from containing ROM code. Through this technique, any 256 word block of ROM can be transferred to the appropriate window area in the I/O page (Figure 1-2).

Figure 1-2 ROM Window Map Addresses (18 Bit Q-bus)

The ROM window addresses in Figure 1-2 are the addresses used by the 18-bit Q-bus. If the 16- or 22-bit Q-bus is used, the addresses are shown in Table 1-1. The window map is used when the MXV11-B is configured for bootstrap mode.

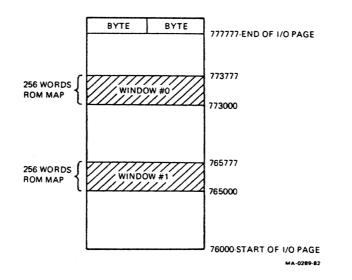

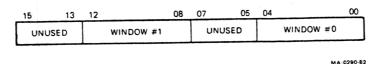

A page control register (PCR) in the MXV11-B, is used for the mapping feature. The PCR is a read/write register which supports DATIOB and DATOB operations. It resides at location 177520 in the I/O page and is two bytes in length.

The PCR which holds the window address fields points to one of the 256 word blocks to be accessed. The CPU reads the ROM via one of the two ROM window maps.

Each of these window maps (bootstrap areas) is pointed to by a five-bit address in the PCR. PCR format and bit assignments are shown in Figure 1-3. Bits 0 through 4 point to 1 of 32 256-word blocks in ROM (8K word space). The 256word block pointed to by bits 0 through 4 is read through bootstrap address 773000<sub>8</sub>. Bits 8 through 12 point to 1 of 32 256-word blocks in ROM. The 256word block pointed to by bits 8 through 12 is read through bootstrap address 765000<sub>8</sub>.

Table 1-1 ROM Window Addresses for 16-, 18-, and 22-bit Q-bus

| Q-bus  | Window 1<br>Start Addr<br>(octal) | End Addr<br>(octal) | Window 0<br>Start Addr<br>(octal) | End Addr<br>(octal) |

|--------|-----------------------------------|---------------------|-----------------------------------|---------------------|

| 16-bit | 165000                            | 165777              | 173000                            | 173377              |

| 18-bit | 765000                            | 765777              | 773000                            | 773377              |

| 22-bit | 17765000                          | 17765777            | 17773000                          | 17773377            |

|   | 15  | 13  | 12 |           | 08 | 07  | 05  | 04 | 0         | 0 |

|---|-----|-----|----|-----------|----|-----|-----|----|-----------|---|

| ſ | UNU | SED |    | WINDOW #1 |    | UNU | SED |    | WINDOW #0 |   |

|   |     |     | 1  |           |    |     |     |    |           |   |

Figure 1-3 Page Control Register

+ 1.

### 1.5 SERIAL LINE UNITS

Data between the CPU and a peripheral device is serialized by an asynchronous serial line unit. The MXV11-B uses two of these lines, SLU 0 and SLU 1.

Each SLU contains a DLART which is a Universal Asynchronous Receiver/ Transmitter (UART) that has been modified by Digital Equipment Corporation. SLU 1 can be used as a console terminal port but SLU 0 cannot.

The serial line interfaces are configured so that SLU 0 is electrically closer than SLU 1 and therefore, has the higher interrupt priority.

The MXV11-B module also configures the SLUs so that SLU 1 tracks SLU 0. That is, SLU 1 is assigned to the next higher starting address over SLU 0. This is also true for the vector address assignments. An exception to this is when SLU 1 is assigned as the console port.

If SLU 1 is selected for console, the Halt and Boot options are normally enabled. These functions may be enabled under other conditions also. Either function is invoked when SLU 1 detects a break character. If the Halt option is selected, a break character halts program execution and the processor enters console ODT microcode. If the Boot option is selected, a break character initializes the system, then restarts the processor with the selected power up mode.

The baud rates for each serial line can be software programmable or can be strapped to 300, 1200, 9600, or 38,400.

The SLUs transmit and receive EIA-423 or RS 232 signal levels at 300, 1200, 9600, or 38,400 baud. A 20 mA active or passive current loop operation may be obtained with the DLV11-KA EIA to 20 mA converter option. The MXV11-B does not support the reader run portion of the DLV11-KA and does not contain modem control lines.

Break generation and error indicator bits the DLARTs provide overrun parity and framing errors. These errors can be read via the status registers. No parity bit or external baud rate clock logic is provided.

#### 1.6 LINE TIME CLOCK

The line time clock (LTC) is a one-bit register (bit 06). When bit 06 is set, the clamp is removed from BEVENT thereby enabling the LTC. The address of the LTC is 777546. The LTC is derived from a 20 MHz crystal oscillator on the MXV11-B board. The crystal oscillator is also used for memory refresh.

NOTE: If a customer uses the LTC feature of the MXV11-B module, the module and the processor should be mounted in the same backplane.

A frequency divider connected to the oscillator provides a frequency of 617.4 KHz which is applied to the DLARTs of SLU1 and SLU0. The SLU1 DLART provides selectable line time clock frequencies of 50, 60, or 800 Hz. The desired frequency is selected by wire-wrapping the frequency to a common wire-wrap

post. The LTC can be enabled or disabled from driving the BEVENT line on the Q-bus by appropriate wire-wrap. The BEVENT line is used by the system for the eal time clock (50 Hz, 60 Hz, or 800 Hz). The MXV11-B also provides a BEVENT clamp which holds BEVENT low at power-up to aid system diagnostics.

CAUTION: There should be only one source driver on the BEVENT line in any system. In most systems, the system power supply supplies the BEVENT signal. This source must be disabled if the MXV11-B is used to drive the line clock.

### 1.7 LED DIAGNOSTIC DISPLAY REGISTER

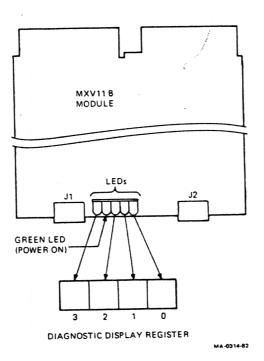

The MXV11-B contains a four-bit LED diagnostic display register (DDR) used for system diagnostics. The register is write-only but generates a reply on DATIO and DATIOB accesses. The DDR resides at location 777524 on the I/O page, and is enabled when the MXV11-B has its boot and console functions enabled.

### 1.8 MXV11-B2 BOOTSTRAP/DIAGNOSTIC ROM OPTION

The MXV11-B2 bootstrap/diagnostic ROM is a plug-in option for the MXV11-B. It performs bootstrap loading of programs (operating systems, for example) from mass storage devices and also performs diagnostic tests on the memory during power-up or when manually invoked. To install this option and configure the module and system it will be used in, refer to Chapter 3.

The bootstrap function is automatic on power-up if the CPU is configured for this feature. But an operator can intervene with a console terminal and boot devices at nonstandard I/O page addresses, select a secondary system device, or invoke a diagnostic utility.

Turnkey operation can be supported so that operator intervention is not needed to start the bootstrap function.

Some of the MXV11-B2 ROM features are listed below:

- Special standalone RT-11 volumes can be loaded and run.

- A system can be configured to down-line load via a DECnet link without operator intervention.

- All system devices currently available on the Q-bus are supported.

- Full 22-bit mapping support is included.

To use this option properly refer to the separate MXV11-B2 ROM Set User Guide (EK-MXVB2-UG) supplied with it.

NOTE: In order to use this ROM's examine/deposit command, the MXV11-B module must be contained in a 22-bit Q-bus system and must be configured to large systems (J37 jumpered to J36).

### 1.9 SPECIFICATIONS

The following paragraphs describe the physical, electrical, and environmental specifications for the MXV11-B module. The module is designed to the Q-bus specification.

### 1.9.1 Physical Specifications

| Module: | Double height                                             |

|---------|-----------------------------------------------------------|

| Height: | 5.187 inches                                              |

| Width:  | 0.5 inch single layer                                     |

| Length: | 8.94 inches (bottom of fingers to top of handle extended) |

| Weight: | 7.5 oz                                                    |

#### 1.9.2 Environmental Specifications

#### Temperature

Storage Temperature Range: -40° C to 66° C

Before using a module with a temperature beyond the operating range, bring the module to an environment within the operating range and then allow it to stabilize for a reasonable length of time (five or more minutes, depending on air circulation).

Operating Temperature Range: 5° C to 60° C

Derate the maximum operating temperature by 1.8° C for each 1000 meters of altitude above sea level.

#### **Relative Humidity**

Storage: 10% to 90%, noncondensing Operating: 10% to 90%, noncondensing

#### Altitude

Storage: The module will not be mechanically or electrically damaged at altitudes up to 9 km. Operating: Up to 3 km.

Airflow, Operating, Sea Level - Provide adequate airflow to limit the outlet temperature rise across the module to 5° C when the inlet temperature is 60° C. For operation below 55° C, provide airflow to limit the inlet to outlet temperature rise across the module to 10° C.

### 1.9.3 Random Access Memory Specification

Address Selection – RAM may be positioned on any 4K word boundary in the 0 to 252K word memory area. If bank select seven (BBS7) or bus refresh (BREF) is asserted, the memory will not respond.

### 8 GENERAL DESCRIPTION

### 1.9.4 Electrical Specifications

Power Requirements - The following voltages are used by this module.

| Voltage | Tolerance | Pins          |

|---------|-----------|---------------|

| +5 V    | ±5%       | AA2, BA2, BV1 |

| +12 V   | ±5%       | AD2, BD2      |

| +5 VB   | ±5%       | AV1           |

Power dissipated in each power supply configuration is as follows.

### No battery backup

| +5 V |         |  |

|------|---------|--|

| Тур  | 17.25 W |  |

| Max  | 24.57 W |  |

| +12 V |        |

|-------|--------|

| Тур   | 0.67 W |

| Max   | 0.71 W |

### Battery backup configuration

| +5 V |         |

|------|---------|

| Тур  | 12.90 W |

| Max  | 15.95 W |

### +5 VB

•Typ 4.35 W Max 8.60 W

# +12 V

Typ 0.67 W Max 0.71 W

### Data retention mode

VCC = 0 V, +12 V supply = 0

### +5 VB

|   | Тур | 4.35 | W   |

|---|-----|------|-----|

| 5 | May | 5 54 | ۱۸/ |

2

### FUNCTIONAL DESCRIPTION

### 2.1 GENERAL

This chapter describes the following functional areas of the MXV11-B.

ROM addressing (direct mode and page mode) RAM memory Line time clock Crystal oscillator Serial line units

The registers and bit formats are described in this chapter and are summarized in Appendix A.

### 2.2 PROM ADDRESSING

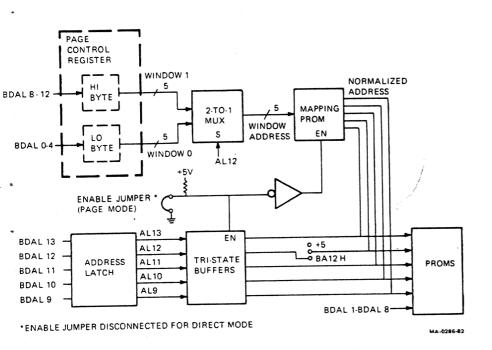

The PROM memory in the MXV11-B can be directly addressed (direct mode) via the Q-bus or indirectly addressed (page mode) via the two windows in the I/O page. Each window can specify 1 of 32 blocks (256 words per block). In direct mode or page mode, bits 14–15 (16-bit bus), 14–17 (18-bit bus) or 14–21 (22-bit bus), are used for address selection and are not used by the PROM.

### 2.2.1 Direct Addressing

Bits 9–13 (BDAL 9–BDAL 13) of the Q-bus are applied to the PROMs via tristate drivers, bits 1–8 (BDAL 1–BDAL 8) are applied directly to the PROMs and bit 0 (BDAL 0) serves as a byte pointer. Figure 2-1 is a simplified block diagram showing how direct addressing and page addressing are implemented.

To directly address the PROMs you must leave the PG L/DIR H jumper disconnected. This turns the tri-state drivers on and address bits 9–13 are directly applied to the PROMs. As previously mentioned, bits 1–8 are wired directly to the PROMs.

When the page control register (PCR) is initialized both windows of this register point to the first location in window 0 which is 773000. This is the PCR default and allows all PROMs (whether 2K by 8, 4K by 8, or 8K by 8) to point to the same location. The PCR is primarily used in I/O page address mapping and is described in more detail in the next paragraph.

9

10 FUNCTIONAL DESCRIPTION

### 2.2.2 I/O Page Addressing

To use page addressing you must connect the PG L/DIR H to GND jumper (J17 to J16), and BOOT L/PROM H to GND jumper (J44 to J45). Also, the boot ROM used must reside on the MXV11-B module. Then specify 1 of 32 256-word blocks of boot address space. The address space is selected by the read/write page control register (PCR). The PCR holds two window address fields, designated window 0 (773000–773776) and window 1 (765000–765776).

The CPU reads the 256 word ROM through one of two windows in the I/O page. The windows are pointed to by a 5-bit address field in the PCR. Bits 8–12 of the PCR point to window 1 and bits 0–4 point to window 0. The address of the PCR is 777520.

• Figure 2-2 shows an example of how the page mode addressing is used. The window 0 field of the PCR is set to 30. As a result, the 256-word block addressed as 30 is read into the window 0 field (773000-773777) of the I/O \*page.

The window 1 field of the PCR is set to 2. The 256-word block addressed as 2 is read into the window 1 field (765000-765777) the I/O page.

The window 1 and window 0 address are applied to a 2-to-1 multiplexer which multiplexes the window 1 or window 0 address to the output depending on the state of address line 12 (BDAL 12). The 5-bit window address is applied to a mapping PROM which is enabled by the PG L/DIR H jumper (J17) being connected. This jumper turns off the tri-state drivers causing the output of the tri-state lines to be high impedance. Note that the tri-state drivers are turned on during direct mode addressing and are turned off during window mapping.

The mapping PROM normalizes the window address – the normalized address is derived from the true address via a mapping matrix. Table 2-1 shows the true addresses (window block) and the corresponding normalized (ROM) addresses.

The 5-bit normalized address is connected to the tri-state output lines which are now high impedance. As a result, the normalized address is applied to the PROMs.

The 32 blocks of memory may not be contiguous. The mapping function takes care of this and its operation is transparent to the user.

### 12 FUNCTIONAL DESCRIPTION

| Table 2-1       | ROM Window N                   | Лар                                 |

|-----------------|--------------------------------|-------------------------------------|

| Window<br>Field | Normalized<br>0 ROM<br>Address |                                     |

| 0               | 00000                          |                                     |

| 1               | 01000                          |                                     |

| 2               | 02000                          |                                     |

| 3 .             | 03000                          |                                     |

| 4               | 04000                          |                                     |

| 5               | 05000                          |                                     |

| 6               | 06000                          |                                     |

| 7               | 07000                          | Maximum address for 2K by 8 PROM    |

| 10              | 10000                          |                                     |

| 11              | 11000                          | · · ·                               |

| 12              | 12000                          |                                     |

| 13              | 13000                          |                                     |

| 14              | 14000                          |                                     |

| 15              | 15000                          |                                     |

| 16              | 16000                          | Martin and design for Alf by 8 DDOM |

| 17              | 17000                          | Maximum address for 4K by 8 PROM    |

| 20              | 20000                          |                                     |

| 21              | 21000                          |                                     |

| 22              | 22000                          |                                     |

| 23              | 23000                          |                                     |

| 24              | 24000                          |                                     |

| 25              | 25000                          |                                     |

| 26              | 26000                          |                                     |

| 27              | 27000                          |                                     |

| 30              | 30000                          |                                     |

| 31              | 31000                          |                                     |

| 32              | 32000                          |                                     |

| 33              | 33000                          |                                     |

| 34 -            | 34000                          |                                     |

| 35              | 35000                          |                                     |

| 36              | 36000                          | Maximum address for 8K by 8 PROM    |

| 37              | 37000                          | Maximum address for on by o PROM    |

### 2.3 RAM MEMORY FUNCTIONAL DESCRIPTION

Figure 2-3 shows a simplified block diagram of the RAM memory. The memory consists of 64K by 4 Single In-line Packages (SIPs). The following paragraphs describe read/write memory access, refresh access, and the arbitration logic for memory access.

### 2.3.1 Read/Write Access

The address from the Q-bus is saved in an address latch through a set of Q-bus transceiver interfaces. The address is then separated into high and low bytes by a 16-to-8 line multiplexer. These bytes are then applied to the RAM address lines via a second multiplexer which selects between the bus address or a refresh address. The second multiplexer is formed by the tri-state outputs of the refresh counter and the 16-to-8 multiplexer. Refresh has priority over RAM read/write request and peripheral I/O (PIO) requests.

However, if a read or write memory cycle is in progress, that cycle completes - before a refresh cycle starts. On a read cycle, the read data from memory is applied to a data buffer and then to the transceiver interface for transfer to the Q-bus. On a write cycle, the data from the Q-bus is applied to the transceiver interface and then directly to the memory.

### 2.3.2 Refresh Access

The RAM memory is refreshed at a 76.8 KHz rate. This rate is obtained from a 19.660 MHz crystal oscillator which has been applied to a frequency divider. The divider divides the frequency by 256 to yield 76.8 KHz. This frequency is applied to a refresh counter which refreshes each row of the MOS RAMs at the 76.8 KHz rate.

#### 2.3.3 Arbitration Logic

Bits 13–15 of the 16-bit Q-bus address are applied to the decode logic. For the 18-bit Q-bus, bits 13–17 are applied to the decode logic, and for the 22-bit Q-bus bits 13–21 are applied to the decode logic. This address is the address the CPU wants to access.

The SLU start address, the PROM start address, and the RAM start address are selected by wire-wrap pins on the MXV11-B module. These addresses are also applied to the decode logic.

Finally, BWTBT (Bus Write Byte), BBS7 (Bus Bank Select 7), and BREF (Bus Refresh) are applied to the decoder via bus receivers. The decode logic decodes all these inputs and outputs a RD REQ, WR REQ, or PIO REQ.

If the BBS7 signal is asserted at the input to the decode logic, memory will not respond and the system can only access the I/O page. If the BREF signal is asserted, memory will not respond. If the BWTBT signal is asserted, it indicates a DATO(B) operation will occur. If BWTBT is negated, a DATI or DATI(B) operation will occur. In order for the DATO or DATI operation to occur, BREF must be negated.

If the CPU is doing a write operation to memory, BWTBT is asserted and the decode logic asserts WR REQ. If the write operation is to the I/O page, BBS7 is also asserted. Conversely, if the CPU is doing a read operation, BWTBT is negated, and the decode logic outputs RD REQ.

PIO REQ is asserted when access is made to a boot ROM, SLU, or I/O page register (LTC, PCR, or DDR).

The RD REQ, WR REQ, and PIO REQ signals are mutually exclusive in that only one of the signals can be asserted at any given time. These signals, along with the REF REQ signal are applied to the arbitration logic which arbitrates between REF REQ and one of the other requests (RD REQ, WR REQ, or PIO REQ). The first request is the one that is serviced first. But, when a REF REQ and RD REQ, WR REQ, or PIO REQ occur almost simultaneously, the arbitration logic decides which request gets serviced first.

When this decision is made, the output of the arbitration logic starts the clock to initiate the memory access via the memory control logic. If the memory access is a write word, the WRITE HI BYTE, WRITE LO BYTE, RAS and CAS signals are all asserted by the memory control logic. If the memory access is a write byte, the appropriate byte signal (WRITE HIGH BYTE or WRITE LO BYTE), and the RAS and CAS signals are asserted. Data from the Q-bus is fed to the RAM via the transceiver interface.

If the memory access is a read request, the WRITE HI BYTE and WRITE LO BYTE signals are negated and the RAS amd CAS signals are asserted. Data from memory is applied to a data buffer, the transceiver interface, and then to the CPU via the Q-bus.

The memory control logic also provides control signals for the MXV11-B registers, PROMs, serial line units, refresh circuit, transceivers, and the data buffer.

#### 2.4 CRYSTAL OSCILLATOR

The crystal oscillator (Figure 2-4) in the MXV11-B oscillates at 19.66 MHz. The oscillator's output is applied to an 8-bit frequency divider. The divider divides the oscillator frequency for the various system functions described below.

The DCLK signal is derived from the oscillator and clocks the DLARTs. The DCLK signal is 614.4 KHz (19.66 MHz divided by 32). There is a DLART for each SLU. The line time clock for the MXV11-B is obtained from one of three selectable frequency outputs of the DLART. The DLART has outputs of 800 Hz, 60 Hz, and 50 Hz. One of these frequencies is chosen by wire-wrapping the appropriate pins.

The PCLK signal of 307.2 KHz (19.66 MHz divided by 64) clocks the -12 V charge pump circuit. The REF CLK of 76.8 KHz (19.66 MHz divided by 256) clocks the refresh counter. Each row of RAM memory chips is refreshed at the 76.8 KHz rate.

### 16 FUNCTIONAL DESCRIPTION

### 2.5 LINE TIME CLOCK

Figure 2-5 is a simplified block diagram of the line time clock logic. The DLART associated with SLU 1 has selectable frequency outputs of 800 Hz, 60 Hz, and 50 Hz. To use one of these frequencies as the line time clock, the appropriate post must be wire-wrapped. Figure 2-5 shows the 60 Hz frequency selected. In addition, bit 6 of the LTC latch must be set and the LTC 1 to LTC 2 jumper must be connected. This allows BEVENT L to be driven at a 60 Hz rate by the MXV11-B. In most Digital systems, the power supply drives BEVENT.

CAUTION: There can only be one source of BEVENT in a system.

### 2.6 DIAGNOSTIC DISPLAY REGISTER

The diagnostic display register (DDR) resides at location 777524 in the I/O page. It is a write-only register but generates a reply on DATIOB and DATOB accesses. DDR is only enabled when the MXV11-B has its Boot and Console functions enabled.

Only bits 0-3 of the 16-bit word are used. These bits correspond to four red LEDs on the board (bit 3 is the MSB and bit 0 is the LSB). Figure 2-6 shows five LEDs – the four red LEDs comprise the DDR and the green LED indicates power-on.

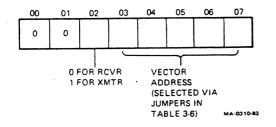

### 2.7.2 Interrupt Vector Selection

Vector address selection covers the vector address space from 010-376.

- NOTE: Be careful - some addresses are reserved.

Bits 3–7 of the vector address can be programmed (via wire-wrap) to select independent vector addresses for each of the serial line units. Bits 0, 1, and 8 are always 0 for the MXV11-B (Figure 2-7).

The vector assignment for SLU 1 is the next higher vector location over SLU 0. The exception is if SLU 1 is selected as the console port. In this case, serial line unit 1 has a vector address of 060 for the transmitter and 064 for the receiver.

Each of the DLART transmit and receive registers track each other. Bit 2 of the vector address automatically selects a zero for the receiver and a one for the transmitter of each serial line interface.

Figure 2-7 SLU Vector Address Bit Format

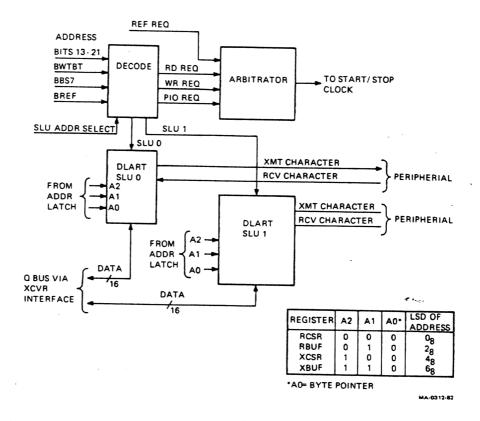

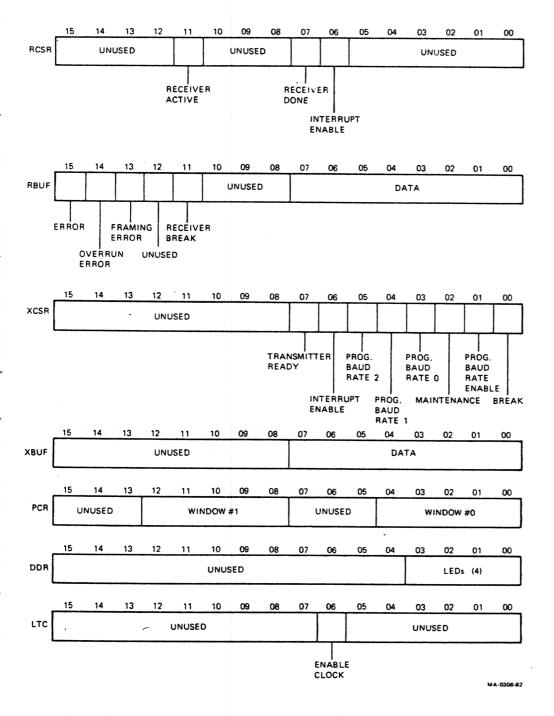

### 2.7.3 SLU Register Addressing

The MXV11-B has four registers associated with each of the two SLUs. The registers for SLU 0 are:

| Receiver control/status register    | (RCSR 0) – Table 2-2  |

|-------------------------------------|-----------------------|

| Receiver data buffer                | (RBUF 0) – Table 2-3  |

| Transmitter control/status register | (XCSR 0) - Table 2-4  |

| Transmitter data buffer             | (XBUF 0) – Table 2-5. |

The registers for SLU 1 are:

| Receiver control/status register    | (RCSR 1) – Table 2-2  |

|-------------------------------------|-----------------------|

| Receiver data buffer                | (RBUF 1) – Table 2-3  |

| Transmitter control/status register | (XCSR 1) - Table 2-4  |

| Transmitter data buffer             | (XBUF 1) – Table 2-5. |

Both SLUs have the same bit assignments and are located in the I/O page. BBS7, when asserted, specifies the I/O page and bits A3–A12 specify the peripheral device in the I/O page. SLU 0 can be assigned one of eight addresses (Table 3-5). SLU 1 can be assigned one of eight addresses and may be assigned as the console port (777560).

| 15    | 14 13                        | 12 11                              | 10 | 09               | 08                                                                                                                                                                                                                                                                               | 07                                | 06                        | 05                              | 04                                        | 03                         | 02                      | 01        | 00        |  |  |

|-------|------------------------------|------------------------------------|----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|---------------------------------|-------------------------------------------|----------------------------|-------------------------|-----------|-----------|--|--|

| RCSR  | CSR UNUSED                   |                                    |    | UNUSED UNUSED    |                                                                                                                                                                                                                                                                                  |                                   |                           |                                 |                                           |                            | UNUSED                  |           |           |  |  |

|       |                              | RECEIN                             |    |                  |                                                                                                                                                                                                                                                                                  |                                   |                           | IPT                             |                                           |                            |                         | Mź        | -0306A-82 |  |  |

| Bit   |                              | 6.<br>16                           |    | I                | Desc                                                                                                                                                                                                                                                                             | riptic                            | on .                      |                                 |                                           |                            |                         |           |           |  |  |

| 15-12 |                              |                                    |    | j l              | Jnus                                                                                                                                                                                                                                                                             | ed                                |                           |                                 |                                           | A                          |                         |           |           |  |  |

| 11    |                              | RA<br>Receiver active<br>read only |    |                  | A logic one indicates that the receiver is<br>active. Set at the center of the start bit o<br>the input serial data. Cleared at the<br>expected center of the stop bit at the end<br>of the time prior to the leading edge of<br>RCV DONE. Also cleared by power up<br>sequence. |                                   |                           |                                 |                                           |                            | end<br>of               |           |           |  |  |

| 10–8  |                              |                                    |    | ι                | Jnuse                                                                                                                                                                                                                                                                            | ed                                |                           |                                 |                                           |                            |                         |           |           |  |  |

| 7     | RD<br>Receiver<br>only       | done rea                           | ad | i<br>e<br>a<br>r | nterfa<br>enable<br>in inte<br>eadir                                                                                                                                                                                                                                             | ace h<br>ed by<br>errup<br>ig the | as re<br>bit 6,<br>t. Rec | ceive<br>rece<br>eiver<br>eiver | that<br>d a c<br>iver d<br>done<br>data i | harac<br>one r<br>e is cle | ter. I<br>eque<br>eared | sts<br>by |           |  |  |

| 6     | IE<br>Interrupt<br>read/writ |                                    |    | a                |                                                                                                                                                                                                                                                                                  | disa                              | bles                      |                                 | eceiv<br>upts.                            |                            |                         |           |           |  |  |

| 5-0   |                              |                                    |    | ι                | Inuse                                                                                                                                                                                                                                                                            | d                                 |                           | •                               |                                           |                            |                         |           |           |  |  |

# Table 2-2 Receiver Status Register Bit Assignments (RCSR)

+ 1.....

#### 00 07 05 04 03 02 01 08 06 10 09 13 12 11 DATA UNUSED RBUF ERROR FRAMING RECEIVER FRROR BREAK OVERRUN UNUSED ERROR MA-03068-82 Description Bit A logic one indicates that bit 13 and/or ER 15 bit 14 is a one. Cleared when the bit is Error read only read or cleared by power-up sequence. A logic one indicates a word in the OE 14 receiver buffer had not been read when Overrun error read another word was received and placed only in the receiver buffer. Cleared when read

or by power-up sequence. A logic one indicates that a start bit was FE 13 detected but there was no corresponding Framing error read stop bit. A framing error is generated only when a break is received. Cleared when read or by power-up sequence. Unused 12 This bit is set when serial-in (SI) signal 11 RB goes from a mark to a space and stays in Receiver break read the space condition for 11 bit times after only serial reception starts. This bit is cleared when the SI signal returns to the Mark condition, or by power-up sequence. Unused 10-8 These eight bits hold the most recent Data read only 7-0 byte received. When a new byte is transferred to the data buffer, the RCV DONE

sequence.

in the RCSR is set. Bit0 is the LSB and bit 7 is the MSB. Cleared by power-up

### Table 2-3 Receiver Data Buffer Bit Assignments (RBUF)

| 15   | 14                                                                                                             | 13 12             | 11   | 10 | 09                       | 08                                                                                                                                                                                                                                                                                              | 07                                                      | 06                                                    | 05                                                    | 04                                          | 03                                           | 02                        | 01                  | 00 |

|------|----------------------------------------------------------------------------------------------------------------|-------------------|------|----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|----------------------------------------------|---------------------------|---------------------|----|

| XCSR |                                                                                                                | UNI               | USED |    |                          |                                                                                                                                                                                                                                                                                                 |                                                         |                                                       |                                                       |                                             |                                              |                           |                     |    |

| •    |                                                                                                                |                   |      |    |                          | TRAI<br>REAI                                                                                                                                                                                                                                                                                    |                                                         |                                                       |                                                       | 2<br>PROG.<br>BAUD<br>RATE                  |                                              | 0<br>NTENA                |                     |    |

| Bit  |                                                                                                                |                   | 1    |    | C                        | escri                                                                                                                                                                                                                                                                                           | ptio                                                    | n                                                     | -                                                     |                                             |                                              |                           | unun etti vara meni |    |

| 15-8 |                                                                                                                |                   |      |    | L                        | Inuse                                                                                                                                                                                                                                                                                           | d                                                       |                                                       |                                                       |                                             |                                              |                           |                     |    |

| 7    | TR<br>Transr<br>read o                                                                                         | nitter re<br>nly  | ady  |    | ir<br>C<br>re<br>re<br>t | logic<br>hterfa<br>harac<br>egiste<br>eady i<br>eady i<br>ne tra<br>ower-                                                                                                                                                                                                                       | ce is<br>iter ir<br>er. If e<br>reque<br>s clea<br>nsmi | read<br>nto th<br>enabl<br>ests a<br>ared v<br>tter d | y to a<br>e trar<br>ed by<br>n inte<br>vhen<br>ata re | nsmit<br>hsmit<br>bit 6<br>errupt<br>data i | t a<br>ter da<br>, tran<br>t Tran<br>is writ | smitt<br>Ismitt<br>ten in | er<br>ito           |    |

| 6    | IE<br>Interru<br>read/w                                                                                        | ipt enab<br>vrite | ole  |    | ir                       | logic<br>nterru<br>nterru                                                                                                                                                                                                                                                                       | pts. A                                                  | logi                                                  | c zer                                                 | o disa                                      | ables                                        | on.                       |                     |    |

| 5–3  | BR2-BR0*<br>Programmable baud<br>rate select<br>read/write                                                     |                   |      |    |                          | When PBR-bit 1 in XCSR is set, these<br>bits determine the baud rate (set by<br>software if SOFT jumper connected to<br>GND). If SOFT jumper is connected to<br>OPEN, baud rate is obtained via wire-<br>wrap. Bits BR2-BR0 are cleared by PBR<br>Inhibit (SOFT EN) or by power-up<br>sequence. |                                                         |                                                       |                                                       |                                             |                                              |                           |                     |    |

| 2    | MAINT<br>Mainte<br>read/w                                                                                      | enance            |      |    | te<br>s<br>is            | his bi<br>est. W<br>erial c<br>erial i<br>disco<br>nitializ                                                                                                                                                                                                                                     | hen foutpu<br>nput<br>onne                              | t is co<br>and t<br>cted.                             | it is so<br>onnec<br>he ex                            | et, th<br>ted to<br>terna                   | e tran<br>o the r<br>al seri                 | smitt<br>eceiv<br>al inp  | er<br>er<br>out     |    |

|      | BAADANNY TANANA MANANA MAN |                   |      |    |                          |                                                                                                                                                                                                                                                                                                 |                                                         |                                                       |                                                       |                                             |                                              |                           |                     |    |

### Table 2-4 Transmitter Status Register Bit Assignments (XCSR)

\* Read only as a zero when PBRI (programmable baud rate inhibit) is asserted low. PBRI is asserted low by connecting the SOFT EN to OPEN jumpers (J14 to J15). In this case, the baud rate is determined by the wire-wrap jumpers (J7–J11). Otherwise, with SOFT EN to GND (J14–J13), the bit is read/write. This bit is cleared by power-up sequence or PBRI (SOFT EN to OPEN jumper–J14–J15).

| Bit |                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PBR*<br>Programmable<br>baud rate enable<br>Read/write<br>when software<br>programmable baud<br>rates enabled (SOFT<br>to GND jumper); else<br>read only as 0 | This bit selects between internal and<br>external baud rate selection. When set<br>(enable), the baud rate is determined by<br>the PBR2-0 bits in this register. When<br>clear (inhibit), the baud rate is determined<br>by the J1, J0 wire-wrap pins. This bit is<br>cleared by power-up sequence or SOFT<br>to OPEN Jumper connected (program-<br>mable baud rate inhibit (J14 to J15). |

| 0   | BK<br>Break<br>read/write                                                                                                                                     | When this bit is set, it causes the serial<br>output signal to go to a space condition.<br>A space condition longer than a char-<br>acter time causes a framing error when it<br>is received and is regarded as a break.<br>Cleared by bus initialization.                                                                                                                                |

### Table 2-4 Transmitter Status Register Bit Assignments (XCSR) (Cont)

Read only as a zero when PBRI (programmable baud rate inhibit) is asserted low. PBRI is asserted low by connecting the SOFT EN to OPEN jumpers (J14 to J15). In this case, the baud rate is determined by the wire-wrap jumpers (J7–J11). Otherwise, with SOFT EN to GND (J14–J13), the bit is read/write. This bit is cleared by power-up sequence or PBRI (SOFT EN to OPEN jumper–J14–J15).

### Table 2-5 Transmitter Data Buffer Bit Assignments (XBUF)

|      | 15        | 14 | 13   | 12 | 11   | 10 | 09         | 08                                                                                                                                   | 07                                                                                             | 06                                                                                                 | 05                                                                                            | 04                                                                                                      | 03                                                                                    | 02                                                                                             | 01                                                          | 00       |

|------|-----------|----|------|----|------|----|------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|

| XBUF | IF UNUSED |    |      |    |      |    |            |                                                                                                                                      |                                                                                                | DA                                                                                                 | TA                                                                                            |                                                                                                         |                                                                                       |                                                                                                |                                                             |          |

|      |           |    |      |    |      |    |            |                                                                                                                                      | <b></b>                                                                                        |                                                                                                    |                                                                                               |                                                                                                         |                                                                                       |                                                                                                | м.                                                          | A-0306D- |

|      |           |    |      |    |      |    |            |                                                                                                                                      |                                                                                                |                                                                                                    | -                                                                                             |                                                                                                         |                                                                                       |                                                                                                |                                                             |          |

| Bit  |           |    |      |    |      |    | <b>.</b> . | Descr                                                                                                                                | iptio                                                                                          | n                                                                                                  |                                                                                               |                                                                                                         |                                                                                       |                                                                                                |                                                             |          |

| 15-8 |           |    |      |    |      |    |            | Unuse                                                                                                                                | d                                                                                              |                                                                                                    |                                                                                               |                                                                                                         |                                                                                       |                                                                                                |                                                             |          |

| 7–0  |           | ,  | T DA |    | UFFE | R  |            | Transr<br>registe<br>byte w<br>into th<br>bit in t<br>byte is<br>output<br>empty<br>set wh<br>mitter<br>registe<br>registe<br>by poo | er hol<br>ritter<br>is reg<br>he X<br>copi<br>t regi<br>and<br>en a<br>data<br>er. Re<br>er ca | Ids a of<br>into<br>gister<br>CSR<br>ied in<br>ster w<br>the b<br>byte i<br>buffe<br>eadin<br>uses | copy<br>it. Wh<br>the t<br>regis<br>to the<br>vhene<br>it is cop<br>er into<br>g the<br>no ot | of the<br>enal<br>transi-<br>ter is<br>e tran-<br>ever t<br>clear.<br>bied fr<br>o the<br>cont<br>her e | e mos<br>byte is<br>mit re<br>clear<br>smitt<br>hat re<br>The<br>The<br>seria<br>ents | t rece<br>s writh<br>ady (<br>red. T<br>er se<br>egiste<br>TR bi<br>ne tra<br>I outp<br>of thi | ten<br>TR)<br>his<br>rial<br>ris<br>t is<br>ns-<br>put<br>s |          |

#### \* •••

The SLU registers for both SLUs are addressed via address lines A2, A1, and A0 from the address latch (Figure 2-8). The address latch and decoder are the same as shown in Figure 2-3. A2, A1, and A0 are applied to both SLUs. The SLU selected is determined by the chip select (CS) input to the DLART and is a function of the decode logic.

The chart in Figure 2-8 shows how A2, A1, and A0 select one of the four DLART registers by determining the least significant octal digit of the address.

NOTE: All bits in the SLU registers are reset by a power-down/power-up sequence which causes signals BDC OK H and BINIT L to go low and then go high.

These bits are also reset if the operator presses a restart switch contained in certain systems. There are certain bits (Interrupt Enable, Break, and Maint) in the SLU registers which may be cleared by bus initialization and by the power-up sequence (refer to Tables 2-2 through 2-5).

### 2.7.4 Baud Rate Selection

The baud rates are the same for transmit and receive functions of the same DLART. The baud rates can be set via strapping or by software programming.

Strapped Baud Rates – Each of the SLUs can be strapped to one of four baud rates (300, 1200, 9600, and 38.4K) when the SOFT EN to OPEN jumper is connected. This disables the software programmed baud rates in both SLUs.

Each SLU has a set of two wire-wrap posts strapped in various combinations to select the desired baud rate (Table 3-4).

Software Programmed Baud Rates – The software programmed baud rates are enabled if the SOFT EN wire-wrap post is strapped to GND (J14 to J13). Software then has to write the XCSR (Paragraph 2.7.3) of each DLART to set up the baud rates.

In order to enable software controlled baud rates, SOFT EN must be jumpered to GND (J14 to J13) and the programmable baud rate enable (PBRE) bit (bit 1 of XCSR) must be set. If this bit is not set, the strapped (hardware controlled) pins (Table 3-4) determine the baud rate. With PBRE set, the programmable baud rate bits (PBR 2, 1, and 0 in XCSR) select the baud rate in accordance with this chart.

| PBI | R |   |      | Octal | Baud  |

|-----|---|---|------|-------|-------|

| 2   | 1 | 0 | PBRE | Data  | Rate  |

| Q   | 0 | 0 | 1    | 002   | 300   |

| 0   | 0 | 1 | 1    | 012   | 600   |

| 0   | 1 | 0 | 1    | 022   | 1200  |

| 0   | 1 | 1 | 1    | 032   | 2400  |

| 1   | 0 | 0 | 1    | 042   | 4800  |

| 1   | 0 | 1 | 1    | 052   | 9600  |

| 1   | 1 | 0 | 1    | 062   | 19200 |

| 1   | 1 | 1 | 1    | 072   | 38400 |

At power up, if SOFT EN is connected to GND (J14 to J13), the software baud rates are enabled. PBR 2, 1, and 0 are reset to 0 which defaults to 300 baud. If the PBRE bit is set to 0, the DLARTs monitor the hardware selectable baud rates (jumpers J7–J11).

If the operator sets PBRE to 1, the DLART disregards the jumpers and uses the baud rates determined by PBR 2, 1, and 0. Those bits must be set to their proper baud rates.

If the SOFT EN jumper is not connected to GND at power up, the baud rate is determined by hardware selectable baud rate jumpers J7–J11.

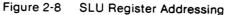

### 2.8 CABLES

Table 2-6 lists part numbers, options, applications, and cabling lengths available for the MXV11-B module. Digital offers the BC20M-50 cable for MXV11-B to DLV11-J operation. Because longer cables usually require routing without connectors attached, the user should make cables for lengths greater than 15 meters (50 feet). Cable material must adhere to EIA RS-423 specifications. The connectors on the MXV11-B module are AMP-87272-8 (2 pin  $\times$  5 pin on 0.1 inch centers). These connectors can mate with a wide variety of low cost cables including 10-conductor flat cable. Note that a pin 1 baud rate clock is not used on this module.

Pin 10 carries +12 Vdc to supply power for the DLV11-KA option. Therefore, pins 1 and 10 should be unterminated if the DLV11-KA option is not used. Cable retention in the module is provided by locking clip contacts (AMP PN87124-1).

The locking clips hold the receptacle (AMP PN87133-5) in the module connector when the cable is pulled. To remove the cable from the connector, pull back the cable receptacle to disengage the locking clips.

| Cable     | Application                                                                                                                          | Length        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|---------------|

| BC21 B-05 | EIA RS-232C modem cable to interface with<br>modems and acoustic couplers (2 × 5 pin AMP<br>female to RS-232C male)                  | 1.5 m (5 ft)  |

| BC20N-05  | EIA RS-232C null modem cable to directly interface with a local EIA RS-232C terminal (2 $\times$ 5 pin AMP female to RS-232C female) | 1.5 m (5 ft)  |

| BC20M-50  | EIA RS-422 or RS-423 cable for high-speed transmission (19,200 baud) (2 $\times$ 5 pin AMP female to 2 $\times$ 5 AMP female)        | 15 m (50 ft)  |

| BC05D-10  | Extension cable used in conjunction with BC21 B-05                                                                                   | 3 m (10 ft)   |

| BC05D-25  | Extension cable used in conjunction with BC21B-05                                                                                    | 7.6 m (25 ft) |

| BC03M-25  | "Null modem" extension cable used in conjunction with BC21B-05                                                                       | 7.6 m (25 ft) |

|           |                                                                                                                                      |               |

Table 2-6 Definition of Cables

Note: "Strapped" logic levels are provided on data terminal ready (DTR) and request to send (RTS) to all operation of modems with manual provisions (such as Bell 103A data set with 804B auxiliary set).

The MXV11-B may operate with several peripheral device cables and options for flexibility when configuring systems. Figures 2-9 and 2-10 show the variety of cables and options used with the MXV11B the primary application of each.

!,

28 FUNCTIONAL DESCRIPTION

When designing a cable for the MXV11-B, consider these several points:

1. To connect directly to a local EIA RS-232C terminal, you must use a null modem. To design the null modem into the cable, switch Received Data (pin 2) with Transmitted Data (pin 3) on the RS-232C male connector as shown (Figure 2-11).

4

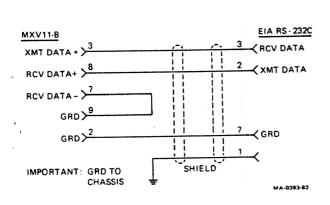

2. The receivers on the MXV11-B have differential inputs. Therefore, when designing an RS-232C or RS-423 cable, you must tie Receive Data (pin 7 on the 2 × 5 pin AMP connector) to signal ground (pins 2, 5, or 9) in order to maintain proper EIA levels (Figure 2-12).

To mate to the  $2 \times 5$  pin connector block, you need the following parts.

| Cable receptacle (1)      | AMP PN 87133-5<br>DEC PN 12-14268-02 |

|---------------------------|--------------------------------------|

| Locking clip contacts (9) | AMP PN 87124-1<br>DEC PN 12-14267-00 |

| Key pin (pin 6) (1)       | AMP PN 87179-1<br>DEC PN 12-15418-00 |

### 2.8.1 Interface Connector Pins

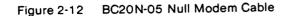

Two 10-pin connectors (one for each serial line) are provided on the MXV11-B module. Connector pins and signal functions are described in Table 2-7 and shown in Figure 2-13.

| Pin | Signal | Function                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BRCLK  | Baud rate clock. This output provides a clock signal at a frequency of 16 times the selected aud rate. This pin is used as an output from the MXV11-B and does not accept external clock inputs. |

| 2   | Ground |                                                                                                                                                                                                  |

| 3   | ХМІТ   | Transmitter output                                                                                                                                                                               |

| 4   | Ground |                                                                                                                                                                                                  |

| 5   | Ground |                                                                                                                                                                                                  |

| 6   | NC     | Key, pin not provided                                                                                                                                                                            |

| 7   | RCV-   | Receiver input most negative                                                                                                                                                                     |

| 8   | RCV+   | Receiver input most positive                                                                                                                                                                     |

| 9   | Ground | <ul> <li>A set</li> </ul>                                                                                                                                                                        |

| 10  | +12 V  | Power for the DLV11-KA option                                                                                                                                                                    |

Table 2-7 MXV11-B I/O Connector Pin Functions

### 2.8.2 Current Loop

The MXV11-B module can interface with 20 mA active or passive current loop devices when used with the DLV11-KA option. This option consists of a DLV11-KB (EIA-to-20 mA current loop converter) and a BC21A-03 interface cable. The MXV11-B cannot support the reader run portion of the DLV11-KA option. The DLV11-KA option is placed between the MXV11-B serial line output and the 20 mA current loop peripheral device. Figure 2-10 shows the cables and devices which may be used with the DLV11-KA option.

3

### JUMPER CONFIGURATIONS

### 3.1 GENERAL

This chapter describes how the user can configure the MXV11-B module to function properly in his system. The jumpers used with this module are of two types – push-on connectors and wire-wrap. However, sometimes the user has to wire-wrap certain jumpers (for example, line time clock jumpers). The push-on connectors are associated with grouping of pins where one of the pins is open. These connectors allow two adjacent pins to be jumpered. If the jumper relating to a function is to remain disconnected, one pin of the push-on connector is placed on the pin associated with that function. The other pin of the push-on connector. If a push-on connector is missing, a wire-wrap jumper may be substituted. When installing jumpers, arrange the wire runs so that no more than two wires are on each post and there is no level jumping between posts.

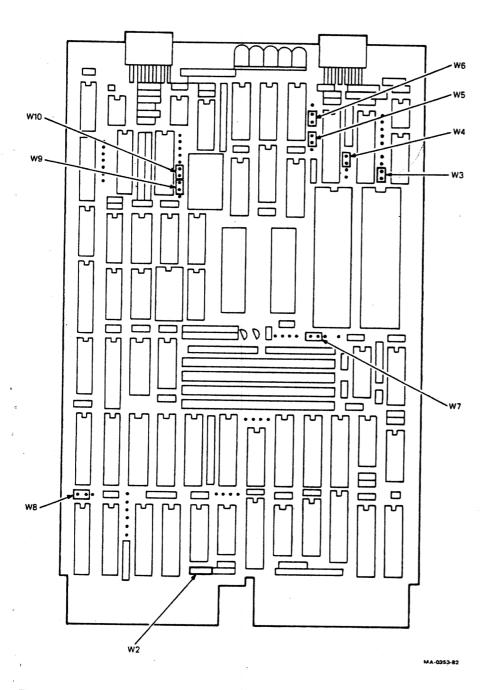

MXV11-B modules shipped from the factory have a 0 ohm resistor supplying the MOS RAMs with nonbattery backup power of +5 V; 8 push-on connectors; and no wire-wrap jumpers connected. Figure 3-1 shows the default configuration for the push-on connectors designated W3–W10. There are two 0 ohm resistors used for battery backup connections: W1 and W2. Only one of them may be inserted at a time. For nonbattery backup applications, W2 is inserted. Paragraph 3-2 summarizes these default conditions and the defaults for the wire-wrap jumpers. 32 JUMPER CONFIGURATIONS

Figure 3-1 Default Configuration of Push-On Connectors

### JUMPER CONFIGURATIONS 33

Before trying to configure the MXV11-B module, complete the following checklist. The checklist, jumper locations in Figure 3-2, the flow diagram in Figure 3-3, and the tables in this chapter should be used when configuring a system.

|     |                                                                                                                                                                                      | User's<br>Configuration | Shipped<br>Configuration |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|

| 1)  | Do you wish to connect the<br>system console to this<br>MXV11-B? If no, disregard<br>following questions marked<br>with an *. If yes, the<br>console must be connected<br>to SLU #1. |                         | Yes                      |

| 2)* | Do you wish system to halt<br>on break from console?                                                                                                                                 |                         | Yes                      |

| 3)* | Do you wish system to<br>reboot on break from<br>console?                                                                                                                            |                         | No                       |

| 4)  | What is desired address/<br>vector for SLU 0?                                                                                                                                        | /                       | 776500/300               |

| 5)  | What is desired address/<br>vector for SLU 1?                                                                                                                                        | //                      | 777560/60                |

| 6)* | Will this MXV11-B contain<br>MXV11-B2 ROM?                                                                                                                                           |                         | No                       |

| 7)  | Will this MXV11-B contain user ROM?                                                                                                                                                  |                         | No                       |