# MS11-L MOS memory technical manual

MS11-L MOS memory technical manual

digital equipment corporation • maynard, massachusetts

1st Edition, June 1979

Copyright © 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

| 0111200 | VMS          | IAS          |

# CONTENTS

# CHAPTER 1 CHARACTERISTICS AND SPECIFICATIONS

| 1.1   | INTRODUCTION 1.1                          |

|-------|-------------------------------------------|

| 1.2   | GENERAL DESCRIPTION 1-1                   |

| 1.3   | SPECIFICATIONS 1-2                        |

| 1.3.1 | Functional Specifications 1-2             |

| 1.3.2 | Electrical Specifications 1-3             |

| 1.3.3 | Physical and Environmental Specifications |

| 1.4   | RELATED DOCUMENTS 1-5                     |

# CHAPTER 2 INSTALLATION AND PROGRAMMING

| 2.1     | GENERAL                                     | . 2-1 |

|---------|---------------------------------------------|-------|

| 2.2     | INSTALLATION                                | . 2-1 |

| 2.2.1   | Switch and Jumper Configurations            | . 2-1 |

| 2.2.1.1 | Memory Addressing.                          |       |

| 2.2.1.2 | I/O Peripheral Page Size Selection.         |       |

| 2.2.1.3 | CSR Address Selection                       |       |

| 2.2.1.4 | Power Voltages                              | . 2-7 |

| 2.2.2   | Backplane Placement (Unibus Operation Only) |       |

| 2.2.3   | Power Voltage Check                         |       |

| 2.2.4   | MAINDEC Testing                             |       |

| 2.3     | CSR BIT ASSIGNMENTS                         |       |

# CHAPTER 3 THEORY OF OPERATION

r

| GENERAL                            | -1                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOS STORAGE ARRAY 3-               | -1                                                                                                                                                                                                                                                                                                                    |

| 16K MOS RAM Chip Description       | -1                                                                                                                                                                                                                                                                                                                    |

| Storage Array Organization         | -3                                                                                                                                                                                                                                                                                                                    |

| FUNCTIONAL DESCRIPTION             | -4                                                                                                                                                                                                                                                                                                                    |

| TIMING LOGIC 3                     | -7                                                                                                                                                                                                                                                                                                                    |

| Memory Data Cycle Execution        | -9                                                                                                                                                                                                                                                                                                                    |

| Refresh Cycle Execution            |                                                                                                                                                                                                                                                                                                                       |

| REFRESH LOGIC 3-1                  | 13                                                                                                                                                                                                                                                                                                                    |

| ADDRESS DECODE LOGIC 3-1           | 13                                                                                                                                                                                                                                                                                                                    |

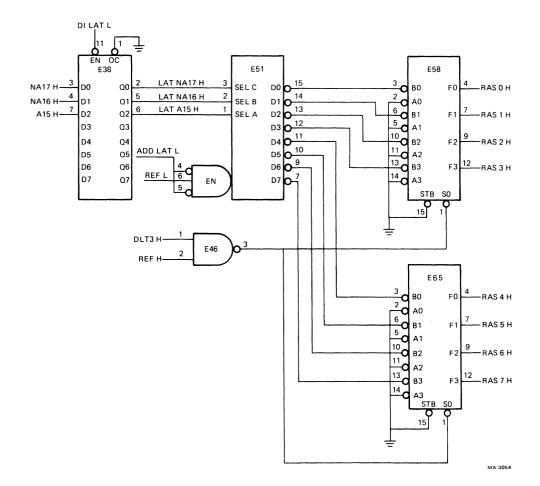

| RAS GENERATION LOGIC 3-1           | 15                                                                                                                                                                                                                                                                                                                    |

| ADDRESS MUX 3-1                    | 17                                                                                                                                                                                                                                                                                                                    |

| DATA PATH CONTROL LOGIC 3-1        | 17                                                                                                                                                                                                                                                                                                                    |

| DATA PATH                          | 22                                                                                                                                                                                                                                                                                                                    |

| PARITY GEN/CHECK LOGIC AND CSR 3-2 | 22                                                                                                                                                                                                                                                                                                                    |

| Parity Generation                  | 22                                                                                                                                                                                                                                                                                                                    |

|                                    | MOS STORAGE ARRAY3-16K MOS RAM Chip Description.3-Storage Array Organization3-FUNCTIONAL DESCRIPTION3-TIMING LOGIC3-Memory Data Cycle Execution.3-Refresh Cycle Execution.3-REFRESH LOGIC3-1ADDRESS DECODE LOGIC3-1RAS GENERATION LOGIC.3-1ADDRESS MUX3-1DATA PATH CONTROL LOGIC3-2PARITY GEN/CHECK LOGIC AND CSR.3-2 |

# **CONTENTS** (Cont)

| 3.11.2 | Parity Check          | 3-26 |

|--------|-----------------------|------|

| 3.11.3 | Parity Error Reaction | 3-26 |

| 3.11.4 | CSR Access            | 3-26 |

# CHAPTER 4 MAINTENANCE

| 4.1   | GENERAL                          | 4-1 |

|-------|----------------------------------|-----|

| 4.2   | PREVENTIVE MAINTENANCE           | 4-1 |

| 4.2.1 | Visual Inspection                | 4-1 |

| 4.2.2 | Voltage Measurements             |     |

| 4.2.3 | MAINDEC Testing                  |     |

| 4.3   | CORRECTIVE MAINTENANCE           | 4-2 |

| 4.3.1 | Initial Check                    | 4-2 |

| 4.3.2 | Address Decode Check             | 4-2 |

| 4.3.3 | Timing Logic Check.              | 4-2 |

| 4.3.4 | Refresh Logic Check              | 4-3 |

| 4.3.5 | Data Shorts Check                | 4-3 |

| 4.3.6 | Address Circuits Check (A14-A01) | 4-3 |

| 4.3.7 | Toggle in Memory Test.           | 4-3 |

# APPENDIX A IC DESCRIPTIONS

# FIGURES

# Figure No.

# Title

4

| 2-1  | 16K MOS RAM Chip 3-                    | 1  |

|------|----------------------------------------|----|

| 3-2  | Chip Read Timing                       | 2  |

| 3-3  | Chip Write Timing 3-                   | 2  |

| 3-4  | MS11-L Block Diagram 3-                | 5  |

| 3-5  | Timing Logic                           |    |

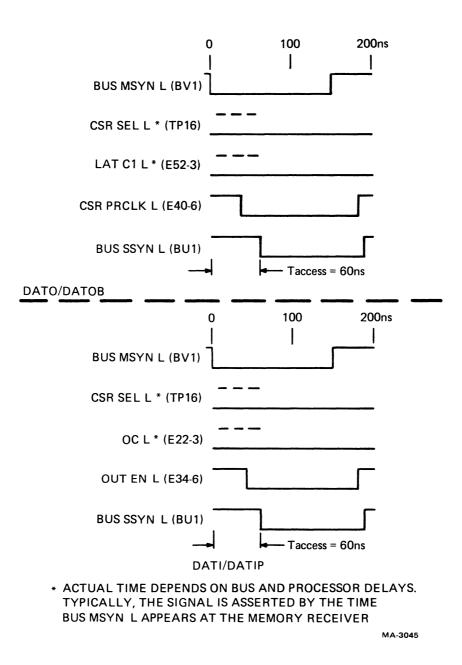

| 3-6  | DATO/DATOB Memory Timing (Typical)     |    |

| 3-7  | DATI/DATIP Memory Timing (Typical) 3-1 |    |

| 3-8  | Refresh Timing (Typical) 3-1           |    |

| 3-9  | Address Decode Logic                   |    |

| 3-10 | RAS Generation Logic 3-1               | 6  |

| 3-11 | Data Path Control Logic 3-1            | 8  |

| 3-12 | CSR Timing (Typical) 3-1               | 9  |

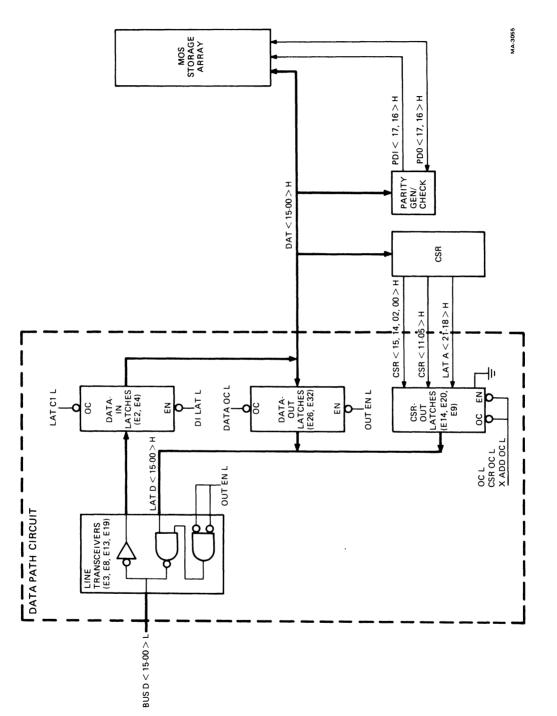

| 3-13 | Data Path                              | 3  |

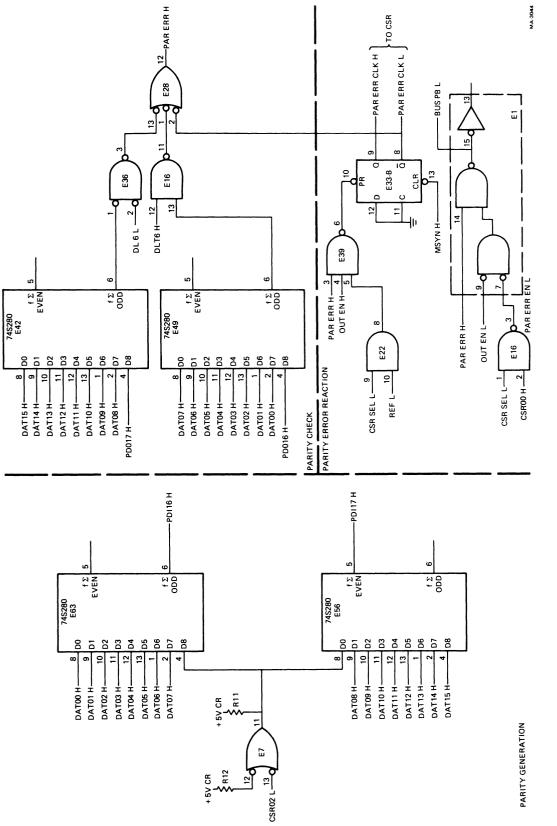

| 3-14 | Parity Gen/Check Logic 3-2             |    |

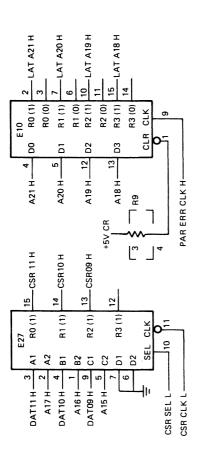

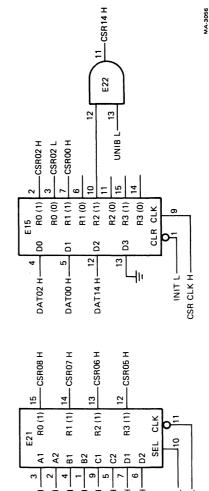

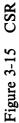

| 3-15 | CSR                                    | ,5 |

# **TABLES**

~

.

r

# Title

| 2-1  | Switch and Jumper Locations        | 2-2 |

|------|------------------------------------|-----|

| 2-2  | Bus Accessible Data Locations      |     |

| 2-3  | Power Voltages                     |     |

| 2-4  | CSR Bit Assignments                |     |

| 3-1  | 16K MOS RAM Chip                   |     |

| 3-2  | Chip Read Timing                   |     |

| 3-3  | Chip Write Timing                  |     |

| 3-4  | MS11-L Block Diagram               |     |

| 3-5  | Timing Logic                       |     |

| 3-6  | DATO/DATOB Memory Timing (Typical) |     |

| 3-7  | DATI/DATIP Memory Timing (Typical) |     |

| 3-8  | Refresh Timing (Typical)           |     |

| 3-9  | Address Decode Logic               |     |

| 3-10 | RAS Generation Logic               |     |

| 3-11 | Data Path Control Logic            |     |

| 3-12 | CSR Timing (Typical)               |     |

| 3-13 | Data Path                          |     |

| 3-14 | Parity Gen/Check Logic             |     |

| 3-15 | CSR                                |     |

|      |                                    |     |

.

--

.

-

# CHAPTER 1 CHARACTERISTICS AND SPECIFICATIONS

### **1.1 INTRODUCTION**

This manual describes the MS11-L which is a metal oxide semiconductor (MOS), random access memory (RAM) designed to be used with the PDP-11 Unibus or special buses with reserve addressing capability. The memory assumes the role of a slave device to the PDP-11 processor or to any peripheral device that is designated bus master. The MS11-L provides storage for 18-bit words (16 data bits and 2 parity bits) and also contains parity control circuitry and a control and status register (CSR). There are four versions of the MS11-L that are differentiated by the total memory capacity available on the module (Table 1-1). Note that the maximum configuration is 128K (131,072 words).

| Option<br>Designation | Module<br>Designation | Storage<br>Capacity   |  |

|-----------------------|-----------------------|-----------------------|--|

| MS11-LA               | M7891-AA              | $32K \times 18$ -bit  |  |

| MS11-LB               | M7891-BA              | $64K \times 18$ -bit  |  |

| MS11-LC               | M7891-CA              | $96K \times 18$ -bit  |  |

| MS11-LD               | M7891-DA              | $128K \times 18$ -bit |  |

Table 1-1MS11-L Versions

## **1.2 GENERAL DESCRIPTION**

The MS11-L consists of a single, hex-height module (M7891) that contains the Unibus/special bus interface, timing and control logic, refresh circuitry and a MOS storage array. The module also contains circuitry to generate and check parity, and a control and status register (CSR).

The memory starting address can be set at any 4K boundary within the 128K Unibus address space or 2048K special bus address space. (Special buses compatible with the MS11-L contain 22 address lines as opposed to 18 Unibus address lines.) The MS11-L allows the top 2K, 4K or 8K of the Unibus or special bus address space to be reserved for the I/O peripheral page. Note that there is no address interleaving with the MS11-L.

The memory storage elements are  $16384 \times 1$ -bit, MOS dynamic RAM devices. The MOS storage array contains 18 of these devices for each 16K bank of memory; e.g., a 128K memory contains 144 storage devices, a 64K memory contains 72 storage devices. Unlike core memory, the read operation for MOS storage devices is nondestructive; consequently, the write-after-read operation associated with core memory is eliminated. The MOS storage devices must be periodically refreshed so that the data remains valid.

The MS11-L memory uses +5 V and either  $\pm 15$  V or  $\pm 12$  V power. Since the MOS storage devices are volatile (data is not retained when power is lost), a battery backup unit is available which supports the MOS power supply regulator(s). Therefore, dc power is available to MOS memory only, for a limited time during an ac power failure. In the battery support mode, power is used only to refresh the MOS storage array so that battery backup time, and therefore, data retention time, are maximized. A green LED on the module stays on as long as +5 V power is supplied to the logic required for memory refresh.

The control and status register (CSR) in the MS11-L contains 11 bits which are used to store information in case of a parity error and control certain parity functions. The CSR has its own address in the top 2K of the Unibus or special bus address space and can be read or written into by any device designated as bus master, even during a memory refresh cycle.

The parity control circuitry in the MS11-L generates parity bits based on data being written into memory during a DATO or DATOB bus cycle. One parity bit is assigned to each data byte and is stored with the data in the MOS storage array. When data is retrieved from memory during a DATI or DA-TIP bus cycle, the parity of the data is recalculated and compared to the stored bits. If the parity bits correspond, the data is assumed to be correct; if the parity bits do not correspond, the data is assumed to be unreliable and the memory initiates the following action:

- 1. The parity error bit (bit 15) of the CSR is set to a logical 1.

- 2. A red LED on the module turns on, providing a visual indication of a parity error.

- 3. If bit 0 in the CSR is set, the memory asserts BUS PB L which warns the processor that a parity error has occurred.

- 4. Part of the address of the faulty data is recorded in the CSR (Paragraph 2.3).

# **1.3 SPECIFICATIONS**

## 1.3.1 Functional Specifications

Capacity

| MŠ11-LA | 32,768 (32K) words   |

|---------|----------------------|

| MS11-LB | 65,536 (64K) words   |

| MS11-LC | 98,304 (96K) words   |

| MS11-LD | 131,072 (128K) words |

18-bit words (2 data bytes with 2 parity bits)

Refresh Timing Cycle time

570 ns (typical), 610 ns (maximum)

Repetition rate

One cycle every 14.5 µs (typical), 13.5 µs (maximum)

## NOTE

Refresh cycle time is defined as the time interval between the assertion of REF REQ L and the negation of BUSY L. These signals are internal to the memory module. Access and Cycle Times (Table 1-2)

|                     | Access Time (ns) |         | Cycle   | Cycle Time (ns) |  |

|---------------------|------------------|---------|---------|-----------------|--|

| Bus Mode            | Typical          | Maximum | Typical | Maximum         |  |

| DATI/DATIP (Memory) | 385              | 415     | 510     | 540             |  |

| DATO/DATOB (Memory) | 125              | 150     | 510     | 540             |  |

| DATI/DATIP (CSR)    | 60               | 80      |         |                 |  |

| DATO/DATOB (CSR)    | 60               | 80      |         |                 |  |

| Table | 1-2 | Access | and | Cycle | Times |

|-------|-----|--------|-----|-------|-------|

|-------|-----|--------|-----|-------|-------|

#### NOTES

1. Access time - The time interval between memory reception of BUS MSYN L (at the input of the receiver) and the assertion of BUS SSYN L on the Unibus or special bus.

Cycle time – The time interval between the assertion of MEM REQ L and the negation of BUSY L. These signals are internal to the memory module.

- 2. If the memory is accessed by a bus master during a refresh cycle (causing a refresh conflict), the data transfer is delayed until the refresh cycle is completed. In the worst case, memory access and cycle times are increased by the entire refresh time; 570 ns (typical), 610 ns (maximum). Access to the CSR is not affected by a refresh cycle.

- 3. If the memory is accessed by a bus master momentarily before the start of a refresh cycle, memory cycle and access times are increased by the refresh arbitration time; 60 ns (typical), 90 ns (maximum). Access to the CSR is not affected by refresh arbitration.

#### **1.3.2 Electrical Specifications**

Humidity

| Voltage Requirements | $+5 V \pm 5\%$ , max ripple = 0.2 V p-p                                                                         |

|----------------------|-----------------------------------------------------------------------------------------------------------------|

|                      | $+15 V + 10\%$ , $-3.3\%$ or $+12 V \pm 5\%$ , max ripple = 1 V p-p                                             |

|                      | $-15 \text{ V} \pm 10\% \text{ or } -12 \text{ V} \pm 10\%, \text{ max ripple} = \hat{1} \text{ V} \text{ p-p}$ |

Current and Power Requirements Tables 1-3 and 1-4

#### 1.3.3 Physical and Environmental Specifications

| MS11-LA<br>MS11-LB<br>MS11-LC<br>MS11-LD | M7891-AA<br>M7891-BA<br>M7891-CA<br>M7891-DA | All versions are hex-height multilayer, 21.6 $\times$ 38.1 cm (8.5 $\times$ 15 inch) |

|------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| Operating Temperature                    |                                              | 5° to 50° C (41° to 122° F)                                                          |

10 to 95 percent (noncondensing)

| Monon                                                     |                  | 754                                                                                 |                  |                  | AC                        |                                                 |                         | +12 V/+15 V             | 15 V                    |                          |

|-----------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|------------------|------------------|---------------------------|-------------------------------------------------|-------------------------|-------------------------|-------------------------|--------------------------|

| Option                                                    | F                |                                                                                     |                  |                  | A CI-/A 71-               | A CI-                                           | Sta                     | Standby                 | Active                  | è                        |

|                                                           | Тур              | Мах                                                                                 | Typ              | Max              | Тур                       | Max                                             | Typ                     | Max                     | Typ                     | Max                      |

| MS11-LA 1.5 1.8 1.0 A (32K × 18) (7.5 W) (9.5 W) (5.0 W)  | 1.5 A<br>(7.5 W) | 1.8 A<br>(9.5 W)                                                                    | 1.0 A<br>(5.0 W) | 1.3 A<br>(6.8 W) | 9 m.A<br>(0.108/0.135 W)  | 11 mA<br>(0.145/0.182 W) 85 mA<br>(1.02/1.28 W) | 85 mA<br>(1.02/1.28 W)  | 105 mA<br>(1.32/1.73 W) | 485 mA<br>(5.82/7.28 W) | 540 mA<br>(6.8/8.91 W)   |

| MS11-LB<br>(64K × 18)                                     | 1.5 A<br>(7.5 W) | 1.5A 1.8A 1.0A (5.0W)                                                               | 1.0 A<br>(5.0 W) | 1.3 A<br>(6.8 W) | 12 mA<br>(0. 144/0. 18 W) | 14 mA<br>(0. 185/0.231 W)                       | 140 mA<br>(1.68/2.1 W)  | 160 mA<br>(2.02/2.64 W) | 535 mA<br>(6.42/8.03 W) | 595 mA<br>(7.5/9.82 W)   |

| MS11-LC<br>(96K × 18)                                     | 1.5 A<br>(7.5 W) | 1.5 A         1.8 A         1.0 A           (7.5 W)         (9.5 W)         (5.0 W) | 1.0 A<br>(5.0 W) | 1.3 A<br>(6.8 W) | 15 mA<br>(0.180/0.225 W)  | 17 mA<br>(0.224/0.281 W)                        | 190 mA<br>(2.28/2.85 W) | 215 mA<br>(2.71/3.55 W) | 590 mA<br>(7.08/8.85 W) | 650 mA<br>(8.19/10.73 W) |

| MS11-LD 1.5A 1.8A 1.0A (5.0W) (128K × 18) (7.5 W) (9.5 W) | 1.5 A<br>(7.5 W) | 1.8 A<br>(9.5 W)                                                                    | 1.0A<br>(5.0W)   | 1.3 A<br>(6.8 W) | 18 mA<br>(0.216/0.27 W)   | 20 mA<br>(0.264/0.33 W)                         | 240 mA<br>(2.88/3.6 W)  | 265 mA<br>(3.34/4.73 W) | 640 mA<br>(7.68/9.6 W)  | 700 mA<br>(8.82/11.55 W) |

| Requireme |  |

|-----------|--|

| Power     |  |

| and       |  |

| Current   |  |

| 1-3       |  |

| Table     |  |

NOTES

- The module has inputs for two sources of +5 V power designated +5 VBBU (optionally battery supported) and +5 V (not battery supported). The voltage tolerances required for the +5 V and +5 VBBU inputs are the same. The total module consumption of +5 V power during normal operation is equal to the sum of the +5 V and +5 VBBU ratings (Paragraph 2.2.1.4).

- The standby and active ratings for +5 V, +5 VBBU and -12 V/-15 V are the same. ų

- The maximum power ratings have been calculated using the worst case voltage tolerances. ÷

| Memory                 | Standby     |             | Active      |             | <b>Battery Backup Mode</b> |             |

|------------------------|-------------|-------------|-------------|-------------|----------------------------|-------------|

| Option                 | Тур         | Max         | Тур         | Max         | Тур                        | Max         |

| MS11-LA<br>(32K × 18)  | 13.6/13.9 W | 17.8/18.2 W | 18.4/19.9 W | 23.3/25.4 W | 6.1/6.4 W                  | 8.3/8.7 W   |

| MS11-LB<br>(64K × 18)  | 14.3/14.8 W | 18.5/19.2 W | 19.1/20.7 W | 24/26.4 W   | 6.8/7.3 W                  | 9/9.7 W     |

| MS11-LC<br>(96K × 18)  | 15/15.6 W   | 19.2/20.1 W | 19.8/21.6 W | 24.7/27.3 W | 7.5/8.1 W                  | 9.7/10.6 W  |

| MS11-LD<br>(128K × 18) | 15.6/16.4 W | 19.9/21 W   | 20.4/22.4 W | 25.4/28.2 W | 8.1/8.9 W                  | 10.4/11.5 W |

# Table 1-4 Total Module Power Requirements

# NOTES

## 1. $XX/YY = rating when \pm 12 V/ \pm 15 V$ power is used.

# 2. The maximum power ratings have been calculated using the worst case voltage tolerances.

#### **1.4 RELATED DOCUMENTS**

Additional reference information can be found in the documents listed below.

| Title                                                                | Document No. | Availability            |

|----------------------------------------------------------------------|--------------|-------------------------|

| PDP-11 Family Field Installation<br>and Acceptance Procedures Manual | EK-FS003-IN  | Hardcopy and Microfiche |

| PDP-11 Peripherals Handbook                                          | EB-05961     | Hardcopy only           |

| PDP-11/04/34/45/55/60<br>Processor Handbook                          | EB-09340     | Hardcopy only           |

These documents can be ordered from:

Digital Equipment Corporation Supplies and Accessories Group Cotton Road Nashua, New Hampshire 03060

For information concerning Microfiche Libraries, contact:

Digital Equipment Corporation Micropublishing Group

BU/F Bedford, MA. ~

# CHAPTER 2 INSTALLATION AND PROGRAMMING

## 2.1 GENERAL

This chapter presents the information necessary for installation and programming of the MS11-L and applies to all versions of the memory. Installation procedures include: switch/jumper settings, back-plane placement, power voltage checks and MAINDEC testing. Programming information includes a discussion of bit assignments in the control and status register (CSR). Power voltage regulation on the module is also discussed in this chapter.

#### 2.2 INSTALLATION

#### 2.2.1 Switch and Jumper Configurations

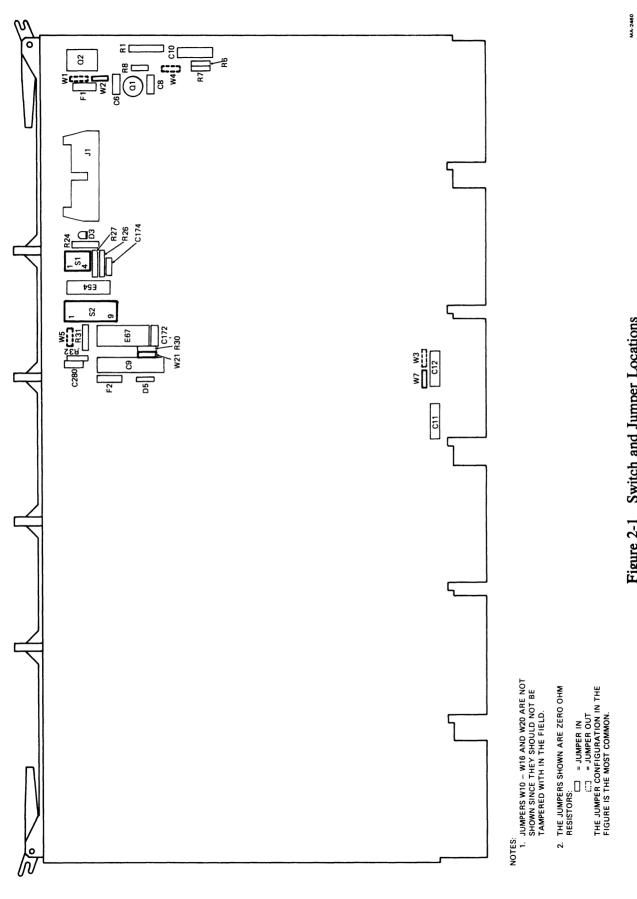

The MS11-L contains 15 jumpers and two switchpacks; one switchpack contains four switches (S1-1 to S1-4) and the other contains nine switches (S2-1 to S2-9). The location of the jumpers and switches is shown in Figure 2-1. In normal operation, jumpers W10-W16 and W20 should be IN. The other jumpers are used to specify Unibus or special bus operation, I/O peripheral page size, and the dc power inputs available to the module. The memory starting address and CSR address are specified by the switches.

#### 2.2.1.1 Memory Addressing

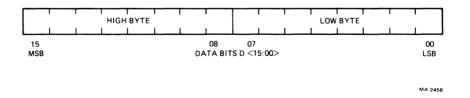

**PDP-11 Memory Conventions** – The MS11-L can be used with the PDP-11 Unibus or special buses with reserve addressing capability. Memory in these computer systems is organized into 16-bit data words, each containing two 8-bit bytes. These bytes are identified as low or high, as shown below.

Each byte is addressable and has its own address location; low bytes are even-numbered and high bytes are odd-numbered. Words are addressed by even numbered locations only, and the high (odd) byte for each word is automatically included.

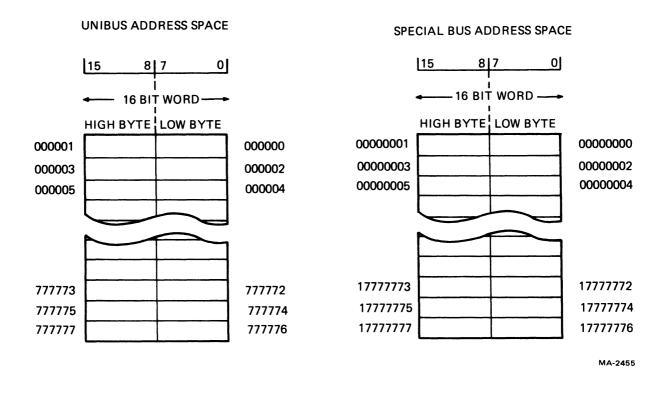

Via the Unibus, 131,072 (128K) words or 262,144 (256K) bytes can be addressed; 2,097,152 (2048K) words or 4,194,034 (4096K) bytes can be addressed via a special bus. Each byte location in Unibus memory is specified by a 6-digit octal number, but with a special bus, 8-digit octal numbers are used. The address range is 000000 through 777777 on the Unibus and 000000000 through 17777777 on a special bus (Figure 2 through 2).

Figure 2-1 Switch and Jumper Locations

Figure 2-2 Bus Accessible Data Locations

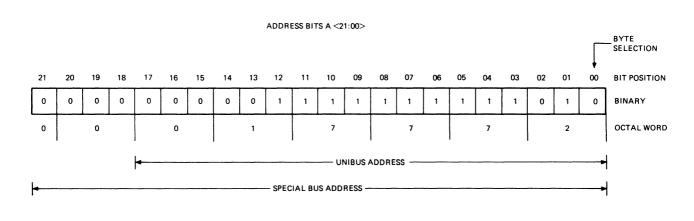

The memory address decoding logic responds to the binary equivalent of the octal address. The binary equivalent of 00017772 is shown below. The MS11-L decodes an 18-bit address (A17-A00) on the Unibus or a 22-bit address (A21-A00) on a special bus.

MA-2459

The address space on a bus occupied by a memory module is determined by the memory starting address and address range. A unique starting address is selected by switches on the MS11-L which correspond to address bits A17-A13 on the Unibus or A21-A13 on a special bus. Table 2-1 lists the octal address ranges of the MS11-L versions and the associated address bits which determine the word location within the module. Address bit A00 is used to select a data byte during a DATOB bus cycle.

| Memory      | Storage Capacity              | Octal Address     | Associated   |

|-------------|-------------------------------|-------------------|--------------|

| Designation |                               | Range             | Address Bits |

| MS11-LA     | 32,768 words (65,536 bytes)   | 00000000-00177777 | A15-A00      |

| MS11-LB     | 65,536 words (131,072 bytes)  | 00000000-00377777 | A16-A00      |

| MS11-LC     | 98,304 words (196,608 bytes)  | 00000000-00577777 | A17-A00      |

| MS11-LD     | 131,072 words (262,144 bytes) | 00000000-00777777 | A17-A00      |

Table 2-1 MS11-L Address Ranges

**Memory Starting Address Selection** – The lowest bus address which the MS11-L responds to is the memory starting address. The starting address must be assigned to a 4K boundary within the 128K Unibus address space or 2048K special bus address space. The starting address is assigned by manually setting nine switches, S2-1 through S2-9, to the appropriate positions for the desired location (Tables 2-2 and 2-3).

| Partial Starti | ing Address |            | Switch Positions |            |            |  |  |

|----------------|-------------|------------|------------------|------------|------------|--|--|

| Decimal        | Octal       | S2-1 (A21) | S2-2 (A20)       | S2-3 (A19) | S2-4 (A18) |  |  |

| 0K             | 00RR0000    | ON         | ON               | ON         | ON         |  |  |

| 128K           | 01RR0000    | ON         | ON               | ON         | OFF        |  |  |

| 256K           | 02RR0000    | ON         | ON               | OFF        | ON         |  |  |

| 384K           | 03RR0000    | ON         | ON               | OFF        | OFF        |  |  |

| 512K           | 04RR0000    | ON         | OFF              | ON         | ON         |  |  |

| 640K           | 05RR0000    | ON         | OFF              | ON         | OFF        |  |  |

| 768K           | 06RR0000    | ON         | OFF              | OFF        | ON         |  |  |

| 896K           | 07RR0000    | ON         | OFF              | OFF        | OFF        |  |  |

| 1024K          | 10RR0000    | OFF        | ON               | ON         | ON         |  |  |

| 1152K          | 11RR0000    | OFF        | ON               | ON         | OFF        |  |  |

| 1280K          | 12RR0000    | OFF        | ON               | OFF        | ON         |  |  |

| 1408K          | 13RR0000    | OFF        | ON               | OFF        | OFF        |  |  |

| 1536K          | 14RR0000    | OFF        | OFF              | ON         | ON         |  |  |

| 1664K          | 15RR0000    | OFF        | OFF              | ON         | OFF        |  |  |

| 1792K          | 16RR0000    | OFF        | OFF              | OFF        | ON         |  |  |

| 1920K          | 17RR0000    | OFF        | OFF              | OFF        | OFF        |  |  |

Table 2-2

Starting Address Configurations (Part 1)

#### NOTES

- 1. RR = octal digits determined by switches S2-5 to S2-9

- 2. The decimal addresses listed are equivalent to the associated octal addresses if RR = 00

| Partial Starting Address |          | Switch Positions |            |            |            |            |  |

|--------------------------|----------|------------------|------------|------------|------------|------------|--|

| Decimal                  | Octal    | S2-5 (A17)       | S2-6 (A16) | S2-7 (A15) | S2-8 (A14) | S2-9 (A13) |  |

| 0K                       | SS000000 | ON               | ON         | ON         | ON         | ON         |  |

| 4K                       | SS020000 | ON               | ON         | ON         | ON         | OFF        |  |

| 8K                       | SS040000 | ON               | ON         | ON         | OFF        | ON         |  |

| 12K                      | SS060000 | ON               | ON         | ON         | OFF        | OFF        |  |

| 16K                      | SS100000 | ON               | ON         | OFF        | ON         | ON         |  |

| 20K                      | SS120000 | ON               | ON         | OFF        | ON         | OFF        |  |

| 24K                      | SS140000 | ON               | ON         | OFF        | OFF        | ON         |  |

| 28K                      | SS160000 | ON               | ON         | OFF        | OFF        | OFF        |  |

| 32K                      | SS200000 | ON               | OFF        | ON         | ON         | ON         |  |

| 36K                      | SS220000 | ON               | OFF        | ON         | ON         | OFF        |  |

| 40K                      | SS240000 | ON               | OFF        | ON         | OFF        | ON         |  |

| 44K                      | SS260000 | ON               | OFF        | ON         | OFF        | OFF        |  |

| 48K                      | SS300000 | ON               | OFF        | OFF        | ON         | ON         |  |

| 52K                      | SS320000 | ON               | OFF        | OFF        | ON         | OFF        |  |

| 56K                      | SS340000 | ON               | OFF        | OFF        | OFF        | ON         |  |

| 60K                      | SS360000 | ON               | OFF        | OFF        | OFF        | OFF        |  |

| 64K                      | SS400000 | OFF              | ON         | ON         | ON         | ON         |  |

| 68K                      | SS420000 | OFF              | ON         | ON         | ON         | OFF        |  |

| 72K                      | SS440000 | OFF              | ON         | ON         | OFF        | ON         |  |

| 76K                      | SS460000 | OFF              | ON         | ON         | OFF        | OFF        |  |

| 80K                      | SS500000 | OFF              | ON         | OFF        | ON         | ON         |  |

| 84K                      | SS520000 | OFF              | ON         | OFF        | ON         | OFF        |  |

| 88K                      | SS540000 | OFF              | ON         | OFF        | OFF        | ON         |  |

| 92K                      | SS560000 | OFF              | ON         | OFF        | OFF        | OFF        |  |

| 96K                      | SS600000 | OFF              | OFF        | ON         | ON         | ON         |  |

| 100K                     | SS620000 | OFF              | OFF        | ON         | ON         | OFF        |  |

| 104K                     | SS640000 | OFF              | OFF        | ON         | OFF        | ON         |  |

| 108K                     | SS660000 | OFF              | OFF        | ON         | OFF        | OFF        |  |

| 112K                     | SS700000 | OFF              | OFF        | OFF        | ON         | ON         |  |

| 116K                     | SS720000 | OFF              | OFF        | OFF        | ON         | OFF        |  |

| 120K                     | SS740000 | OFF              | OFF        | OFF        | OFF        | ON         |  |

| 124K                     | SS760000 | OFF              | OFF        | OFF        | OFF        | OFF        |  |

# Table 2-3 Starting Address Configurations (Part 2)

# NOTES

1. SS = octal digits determined by switches S2-1 to S2-4

2. The decimal addresses listed are equivalent to the associated octal addresses if SS = 00

Switches S2-1 through S2-9 correspond to address bits A21-A13 respectively on a special bus; a switch in the OFF position corresponds to a logical 1. The positions of S2-1 through S2-4 specify the starting address to a 128K range; S2-5 to S2-9 specify the starting address to a 4K boundary within a 128K range.

#### NOTE

# Switches S2-1 to S2-4 should be set to the ON position if the MS11-L is used with the PDP-11 Unibus.

Unibus or special bus operation of the MS11-L is selected by jumper W4:

W4OUT – Unibus operation W4IN – Special bus operation

**2.2.1.2** I/O Peripheral Page Size Selection – The I/O peripheral page is the address space reserved for CPU and peripheral registers. The MS11-L allows the top 2K, 4K or 8K of the Unibus or special bus address space to be reserved for the I/O peripheral page. The peripheral page size is specified by jumpers W5 and W21 as shown in Table 2-4.

| Peripheral<br>Page Size | Unibus Location | Special Bus Location | Jumpers<br>W5 | W21 |

|-------------------------|-----------------|----------------------|---------------|-----|

| 2K                      | 126K-128K       | 2046K - 2048K        | IN            | IN  |

| 4K                      | 124K-128K       | 2044K - 2048K        | OUT           | IN  |

| 8K                      | 120K-128K       | 2040K - 2048K        | OUT           | OUT |

Table 2-4

Peripheral Page Size Selection

## NOTES

1. The remaining jumper configuration, W5 IN and W21 OUT, should never be used since it results in a peripheral page which is not continuous.

## 2. Memory diagnostics are not compatible with a 2K or 8K peripheral page (Paragraph 2.2.4).

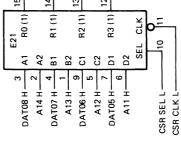

**2.2.1.3** CSR Address Selection – The control and status register (CSR) can be read or written into via the Unibus or special bus, even during a memory refresh cycle. Address decoding logic in the MS11-L specifies the CSR address in the range of 772100–772136 for Unibus operation or 17772100–17772136 for special bus operation. Four switches, S1-1 through S1-4, are used to select the exact CSR address (Table 2-5). Switches S1-1 through S1-4 correspond to address bits A04–A01 respectively; a switch in the OFF position corresponds to a logical 1. The CSR is always accessed as an entire data word since bit A00 is not decoded by the CSR address logic. The Unibus or special bus address of the CSR is in the top 2K of the available address space.

#### NOTE

The CSR address has no relevance to the memory starting address or storage capacity of the MS11-L.

|                   |                        |               | Switch Positions |               |               |  |  |

|-------------------|------------------------|---------------|------------------|---------------|---------------|--|--|

| Unibus<br>Address | Special Bus<br>Address | S1-1<br>(A04) | S1-2<br>(A03)    | S1-3<br>(A02) | S1-4<br>(A01) |  |  |

| 772100            | 17772100               | ON            | ON               | ON            | ON            |  |  |

| 772102            | 17772102               | ON            | ON               | ON            | OFF           |  |  |

| 772104            | 17772104               | ON            | ON               | OFF           | ON            |  |  |

| 772106            | 17772106               | ON            | ON               | OFF           | OFF           |  |  |

| 772110            | 17772110               | ON            | OFF              | ON            | ON            |  |  |

| 772112            | 17772112               | ON            | OFF              | ON            | OFF           |  |  |

| 772114            | 17772114               | ON            | OFF              | OFF           | ON            |  |  |

| 722116            | 17772116               | ON            | OFF              | OFF           | OFF           |  |  |

| 772120            | 17772120               | OFF           | ON               | ON            | ON            |  |  |

| 772122            | 17772122               | OFF           | ON               | ON            | OFF           |  |  |

| 772124            | 17772124               | OFF           | ON               | OFF           | ON            |  |  |

| 772126            | 17772126               | OFF           | ON               | OFF           | OFF           |  |  |

| 772130            | 17772130               | OFF           | OFF              | ON            | ON            |  |  |

| 772132            | 17772132               | OFF           | OFF              | ON            | OFF           |  |  |

| 772134            | 17772134               | OFF           | OFF              | OFF           | ON            |  |  |

| 772136            | 17772136               | OFF           | OFF              | OFF           | OFF           |  |  |

Table 2-5 CSR Address Selection

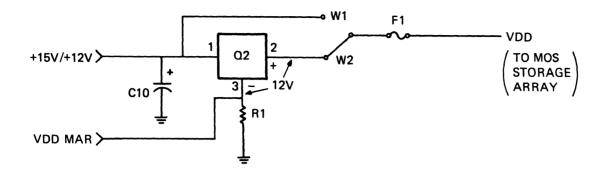

**2.2.1.4** Power Voltages – The MS11-L uses +5 V and either  $\pm 15$  V or  $\pm 12$  V power. Jumpers W1 and W2 are used as listed below to specify  $\pm 15$  V or  $\pm 12$  V operation.

| Power                                            | Jumpers   |           |  |  |

|--------------------------------------------------|-----------|-----------|--|--|

| Voltage                                          | W1        | W2        |  |  |

| $\begin{array}{c} \pm 15V\\ \pm 12V \end{array}$ | OUT<br>IN | IN<br>OUT |  |  |

The circuit shown in Figure 2-3 yields + 12 V and -5 V which are designated VDD and VBB respectively and are routed to the MOS storage array. The major components of the circuit are Q1 and Q2 which are three-terminal voltage regulators. Regulator Q2 produces + 12 V from a + 15 V module input and Q1 produces -5 V from a -15 V or -12 V module input. In normal operation, voltage drops across R1 and R8 are negligible. Fuses F1 and F2 provide current overload protection and zener diode D5 provides overvoltage protection. If an overvoltage condition occurs, D5 conducts so that VBB is clamped to -6.8 V. Note that if the module operates with  $\pm 12$  V inputs, the output of Q2 is not used but current flows from the module input via W1. The  $\pm 15$  V/ $\pm 12$  V module inputs are battery supported during an ac power failure if a battery backup unit is present.

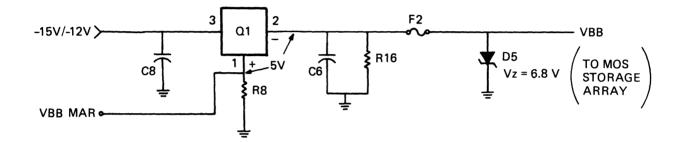

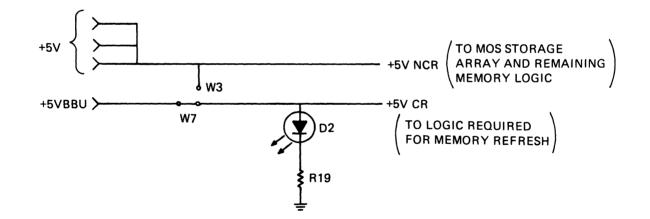

The module has inputs for two sources of +5 V power, designated +5 VBBU and +5 V. Jumpers W3 and W7 are associated with the +5 VBBU and +5 V inputs and are configured as follows.

|                    | Jumpers |     |                                                      |

|--------------------|---------|-----|------------------------------------------------------|

| Power Voltages     | W3      | W7  | Comments                                             |

| +5 V and $+5$ VBBU | OUT     | IN  | Normal configuration                                 |

| +5V only           | IN      | OUT | Used if power is available at the $+5$ V input only. |

#### NOTES:

- 1. AS SHOWN, W1 AND W2 INDICATE ±15V OPERATION AND W3 AND W7 INDICATE MODULE USAGE OF +5V AND +5VBBU. JUMPERS W3 AND W7 SHARE A HOLE ON THE MODULE SO THAT BOTH JUMPERS CAN NOT BE IN AT THE SAME TIME.

- 2. INPUTS VDD MAR AND VBB MAR ARE USED AT THE FACTORY TO MARGIN THE MEMORY (IN  $\pm 15V$  OPERATION ONLY).

MA-2456

Figure 2-3 Power Voltages

With W3 OUT and W7 IN, power is routed from the +5 VBBU input to the logic required for memory refresh; power from the +5 V input is routed to the MOS storage array and the remaining memory logic. The +5 VBBU input is battery supported during an ac power failure if a battery backup unit is present. In the battery support mode, power is used only to refresh the MOS storage array so that battery backup time and therefore data retention time are maximized. (The MOS storage devices do not require +5 V power during a refresh cycle.) Note that in most systems, power is supplied to the +5 V and +5 VBBU inputs even if the battery backup unit is not used. With W3 IN and W7 OUT, the power distribution lines on the module for +5 V and +5 VBBU are jumpered together and the +5VBBU module input is disconnected.

A green LED (D2) stays on as long as the logic required for refresh receives power from either the +5 V or +5 VBBU input. The MS11-L should not be extracted from the backplane when the green LED is ON, even in battery support mode.

#### **2.2.2** Backplane Placement (Unibus Operation Only)

The MS11-L should be inserted into any slot in a backplane which contains modified Unibus connectors in sections A and B. For example:

| DD11-PK | Slots 3–8      |

|---------|----------------|

| DD11-DK | Slots 2–8      |

| DD11-CK | Slots 2 and 3. |

The MS11-L is compatible with all modified Unibus parity or non-parity memories. The MS11-L does not require an M7850 Parity Controller; however, an M7850 is required for other parity memories that may be in the same backplane. The presence of the M7850 does not affect the MS11-L. The backplane connections used by the MS11-L are listed in Table 2-6.

## 2.2.3 Power Voltage Check

Once primary power has been turned on, the dc power voltages listed below should be checked at the backplane.

| Voltage and Tolerance                                                                                 | <b>Backplane Pin(s)</b> |

|-------------------------------------------------------------------------------------------------------|-------------------------|

| $+5 V \pm 5\%$ , max ripple = 0.2 V p-p                                                               | AA2, BA2, CA2           |

| + 5 VBBU $\pm$ 5%, max ripple = 0.2 V p-p<br>(only if jumper W7 is IN and W3 is<br>OUT on the module) | BD1                     |

| $+15 V + 10\%$ , $-3.3\%$ or $+12 V \pm 5\%$ ,<br>max ripple = 1 V p-p                                | AR1                     |

| $-15 V \pm 10\% \text{ or } -12 V \pm 10\%,$<br>max ripple = 1 V p-p                                  | AS1                     |

## 2.2.4 MAINDEC Testing

The following diagnostic program should be used with the MS11-L: 0-128K Memory and Memory Parity Exerciser (MAINDEC-11-CZQMC). To verify proper operation of the memory, run two passes of the diagnostic. No errors are permitted. Also, verify that the program printout agrees with the total memory in the system.

| Table | 2-6 | MS11-L F | 'in Out |

|-------|-----|----------|---------|

|-------|-----|----------|---------|

|   | A                         |       | В                |         | с            |       | D   |                 | E   |          | F   |          |

|---|---------------------------|-------|------------------|---------|--------------|-------|-----|-----------------|-----|----------|-----|----------|

|   | 1                         | 2     | 1                | 2       | 1            | 2     | 1   | 2               | 1   | 2        | 1   | 2        |

| A | INIT L                    | + 5 V | -                | + 5 V   | NPG<br>IN H  | + 5 V | -   | -               | -   | -        | -   | -        |

| B | -                         | -     | -                | -       | NPG<br>OUT H | -     | -   | -<br>GND        | -   | -<br>GND | -   | -<br>GND |

| С | D00 L                     | GND   | -                | GND     | -            | GND   | -   | -               | -   | -        | -   | -        |

| D | D02 L                     | D01 L | + 5 V<br>Battery | -       | -            | -     | -   | -               | -   | -        | -   | -        |

| Е | D04 L                     | D03 L | A19 L            | A18 L   | -            | -     |     | -               | -   | -        | -   | -        |

| F | D06 L                     | D05 L | -                | DC LO L | VDD MAR      | -     | -   | -               | -   | -        | -   | -        |

| Н | D08 L                     | D07 L | A01 L            | A00 L   | -            | -     | -   | -               | -   | -        | -   | -        |

| J | D10 L                     | D09 L | A03 L            | A02 L   | -            | -     | -   | BUS G7<br>SO H  | -   | -        | -   | -        |

| К | D12L                      | DIIL  | A05 L            | A04 L   | -            | -     | -   | BUS G7<br>OUT H | -   | -        | -   | -        |

| L | D14 L                     | DI3L  | A07 L            | A06 L   | -            | -     | -   | BUS G6<br>SO H  | -   | -        | -   | -        |

| М | -                         | D15 L | A09 L            | A08 L   | -            | -     | -   | BUS G6<br>OUT H | -   | -        | -   | -        |

| N | A21 L                     | PB L  | AIIL             | A10 L   | -            | -     | -   | BUS G5<br>SO H  | -   | -        | -   | -        |

| Р | A20 L                     | -     | A13 L            | A12 L   | -            | -     | -   | BUS G5<br>OUT H | -   | -        | -   | -        |

| R | + 15 V/ + 12 V<br>Battery | -     | A15 L            | A14 L   |              | -     | -   | BUS G4<br>SO H  | -   | -        | -   | -        |

| S | -15 V/-12 V<br>Battery    | -     | A17L             | A16 L   | -            | -     | GND | BUS G4<br>OUT H | GND | -        | GND | -        |

| Т | GND                       | -     | GND              | CIL     | GND          | -     | -   | -               | -   | -        | -   | -        |

| U | -                         | -     | SSYN L           | COL     | -            | -     | -   | -               | -   | -        | -   | -        |

| v | -                         | -     | MSYN L           | -       | -            | -     |     |                 |     |          |     |          |

NOTES Pins AN1, AP1, BE1 and BE2 are used for address lines A21 L - A18 L in special bus operation. In Unibus operation, the signals on these pins are ignored by the MS11-L (receivers disabled). In Unibus operation, AN1, AP1, BE1 and BE2 contain the internal bus used by the M7850 Parity Controller. 1.

Pins marked by | are tied together on the module to provide grant continuity. 2.

## NOTE MAINDEC-11-CZQMC diagnostic is compatible with a 4K I/O peripheral page only (Paragraph 2.2.1.2).

# 2.3 CSR BIT ASSIGNMENTS

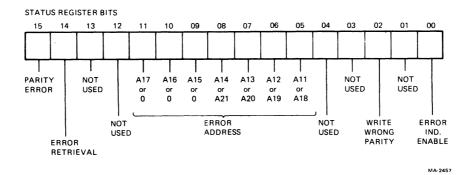

The control and status register (CSR) in the MS11-L allows program control of certain parity functions and contains diagnostic information if a parity error has occurred. The CSR is assigned an address and can be accessed by a bus master via the Unibus or a special bus, even during a memory refresh cycle. Some CSR bits are cleared by the assertion of BUS INIT L. This signal is asserted for a short time by the processor after system power has come up or in response to a reset instruction. The CSR bit assignments are illustrated in Figure 2-4 and are described as follows:

Figure 2-4 CSR Bit Assignments

| Bits 1, 3, 4, 12, and 13 | These bits are not used and are always read as logical 0s. Writing into these bits has no effect on the CSR.                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0                    | Error Indication Enable – This bit, when set (logical 1), allows the MS11-L to assert BUS PB L when data is retrieved from memory if a party error has been detected. This bit can be read or loaded by the program (read/write bit) and is cleared by BUS INIT L.                                                                                                                                                                                                                 |

| Bit 2                    | Write Wrong Parity – This bit, when set, causes the MS11-L to generate<br>the wrong (incorrect) parity when data is written into memory during a<br>DATO or DATOB bus cycle. A parity error should then be detected<br>when this data is read during a DATI or DATIP bus cycle. The bit is<br>usually set for diagnostic purposes and should be cleared (logical 0) for<br>normal operation (correct parity generated). Bit 2 is a read/write bit and<br>is cleared by BUS INIT L. |

| Bits 05-11               | Error Address – Once a parity error has occurred, these bits contain a partial address of the faulty data which caused the parity error. In Unibus operation, address bits A17–A11 are in CSR bits 11–05 respectively, specifying the faulty data location to a 1K segment of memory. In special bus operation, the address bits placed in bits 05–11 are determined by bit 14. Bits 05–11 are read/write bits and are not cleared by BUS INIT L.                                  |

Special Bus Error Retrieval – This bit, when set, causes the MS11-L to place A21-A18 of the faulty data location into CSR bits 08-05; logical 0s are placed in bits 11-09. Address bits A17-A11 are placed in bits 11-05 when bit 14 is cleared. In special bus operation, bit 14 is a read/write bit and is cleared by BUS INIT L. In Unibus operation bit 14 is a read-only bit and is always a logical 0 (clear).

#### NOTE

In normal special bus operation, bit 14 should be a logical 0. If a parity error has occurred, the partial address (A21-A11) of the faulty data can be re-trieved using the following sequence.

- 1. Read the CSR with a DATI bus cycle to obtain A17-A11. Bit 14 should be read as a logical 0.

- 2. Write a logical 1 in bit 14 of the CSR with a DATO bus cycle.

- 3. Read the CSR with a DATI bus cycle to obtain A21-A18. But 14 should be read as a logical 1.

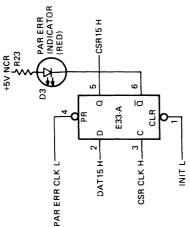

Bit 15

Parity Error Bit - This bit, when set, indicates that a parity error has occurred and also turns on a red LED on the module, providing a visual indication of a parity error. Bit 15 is a flag, but it does not cause a parity error trap in the processor. This bit is a read/write bit and is cleared by BUS INIT L.

# **CHAPTER 3** THEORY OF OPERATION

MA-3053

## 3.1 GENERAL

This chapter contains functional and detailed descriptions of the circuitry in the MS11-L. The descriptions in this chapter are supported by the MS11-L Field Maintenance Print Set (MP00672).

## 3.2 MOS STORAGE ARRAY

## 3.2.1 16K MOS RAM Chip Description

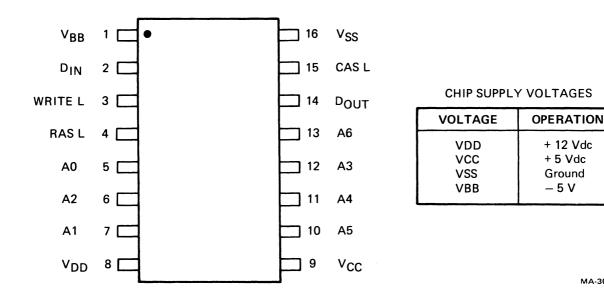

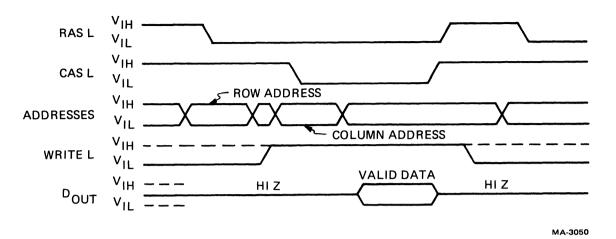

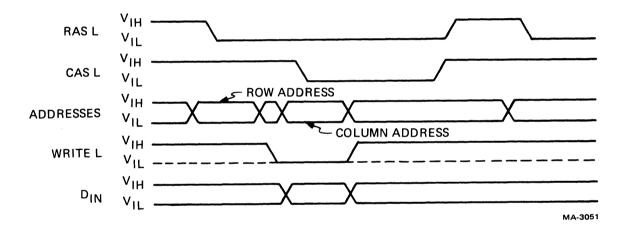

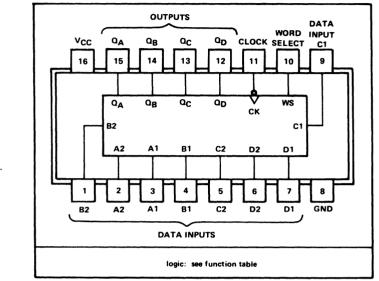

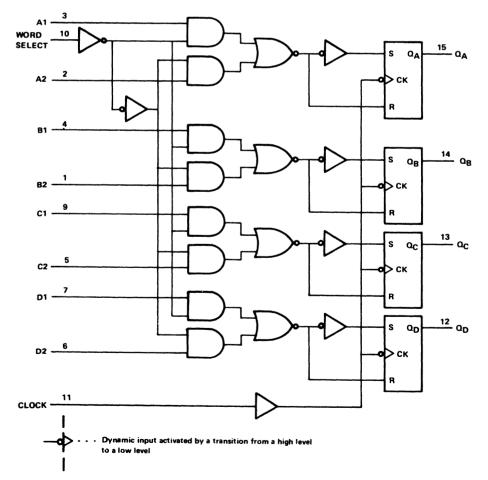

The MOS storage device used in the MS11-L is a  $16384 \times 1$ -bit, dynamic, random-access-memory circuit. The circuit is packaged in a standard 16-pin DIP (Figure 3-1). Timing diagrams for the read cycle and write cycle are shown in Figures 3-2 and 3-3.

To specify a data location within the chip, 14 address bits are required. The 14 address bits are multiplexed, seven at a time, onto the A6-A0 inputs and are latched into on-chip address registers by two signals. The first seven bits comprise the row address and are latched by asserting the RAS L (Row Address Strobe) signal. The other seven bits make up the column address and are latched by asserting the CAS L (Column Address Strobe) signal. The internal timing chain of the chip is started at the negative transition of RAS L.

Figure 3-1 16K MOS RAM Chip

Figure 3-2 Chip Read Timing

Figure 3-3 Chip Write Timing

For a read cycle, the WRITE L signal must be high during the entire time that CAS L is asserted. The data is available on the D OUT line at access time (135 ns max. after CAS L is asserted) and remains valid until CAS L is negated. The D OUT line is driven by a tristate buffer and is in a high impedance (open circuit) state when a valid data output is not present.

A write cycle is specified if the WRITE L signal goes low before CAS L is asserted. The data on the D IN line is strobed into an input buffer by the negative transition of the CAS L signal. Since the D OUT line remains in the high impedance state during a write cycle, the D IN and D OUT lines can be tied together to form a common input/output bus.

The MOS chips must be periodically refreshed so that data remains valid. The data in locations specified by the row address is refreshed during a read or write cycle. Since a data location may be addressed infrequently, if at all, during normal read/write operations, a RAS – only refresh cycle is initiated by the MS11-L approximately every 14.5  $\mu$ s. A different row address is supplied by the MS11-L during each refresh cycle so that data in all 128 row addresses is refreshed in less than 2 ms. The chip does not require a VCC input (+5 V) during a refresh cycle.

## 3.2.2 Storage Array Organization

The storage array in the MS11-L contains up to 144 16K MOS RAM chips, providing storage for up to 128K 18-bit words (2 data bytes and 2 parity bits). The number of chips in the array is different for each version of the MS11-L. The storage array for a 128K memory is shown in sheets 11-14 of the print set. Each sheet shows 32K of memory.

A bank of 18 chips is allocated to each 16K bank of memory; e.g., a 128K memory contains 8 chips for each data and parity bit (Tables 3-1 and 3-2). Parity for the high and low data bytes is written into the array via PD117 H and PD116 H. The two parity bits are retrieved via PD017 H and PD016 H. Data is written into and retrieved from the storage array via the DAT < 15:00 > H lines. The D OUT and D IN lines are tied together for chips that store data.

|                | Data Storage Chips        |                          | Associated Chip Input Lines |                |                |                    |                     |

|----------------|---------------------------|--------------------------|-----------------------------|----------------|----------------|--------------------|---------------------|

| Memory<br>Bank | High Byte<br>(Bits 15-08) | Low Byte<br>(Bits 07-00) | A6-A0<br>Lines              | CAS L<br>Lines | RAS L<br>Lines | Write<br>High Byte | L Lines<br>Low Byte |

| 0-16K          | E87-E94                   | E95-E102                 | AA<7-1>L                    | CAS 0 L        | RAS0L          | WTBT 2 L           | WTBT 0 L            |

| 16-32K         | E103-E110                 | E111-E118                | AA < 7-1 > L                | CAS 1 L        | RAS 1 L        | WTBT 2 L           | WTBT 0 L            |

| 32-48K         | E120-E127                 | E128-E135                | BA < 7-1 > L                | CAS 2 L        | RAS 2 L        | WTBT 2 L           | WTBT 0 L            |

| 48-64K         | E137-E144                 | E145-E152                | BA < 7-1 > L                | CAS 3 L        | RAS 3 L        | WTBT 2 L           | WTBT 0 L            |

| 64-80K         | E153-E160                 | E161-E168                | CA < 7-1 > L                | CAS4L          | RAS4L          | WTBT 3 L           | WTBT 1 L            |

| 80–96K         | E170-E177                 | E178-E185                | CA < 7-1 > L                | CAS 5 L        | RAS 5 L        | WTBT 3 L           | WTBT 1 L            |

| 96-112K        | E187-E194                 | E195-E202                | DA<7-1>L                    | CAS 6 L        | RAS 6 L        | WTBT 3 L           | WTBT 1 L            |

| 112-128K       | E204-E211                 | E212-E219                | DA < 7-1 > L                | CAS7L          | RAS7L          | WTBT 3 L           | WTBT 1 L            |

Table 3-1 Data Storage in Array

|                | Parity Stor           | age Chips |          |          |                |                                       |          |

|----------------|-----------------------|-----------|----------|----------|----------------|---------------------------------------|----------|

| Memory<br>Bank | High Byte<br>(bit 17) |           |          |          | RAS L<br>Lines | Write L Lines<br>High Byte   Low Byte |          |

| 0-16K          | E77                   | E85       | PA<7-1>L | PCAS 0 L | PRAS0L         | WTBT 2 L                              | WTBT 0 L |

| 16-32K         | E76                   | E84       | PA<7-1>L | PCAS 0 L | PRAS 1 L       | WTBT 2 L                              | WTBT 0 L |

| 32-48K         | E75                   | E83       | PA<7-1>L | PCAS 0 L | PRAS 2 L       | WTBT 2 L                              | WTBT 0 L |

| 48-64K         | E74                   | E82       | PA<7-1>L | PCAS 0 L | PRAS 3 L       | WTBT 2 L                              | WTBT 0 L |

| 64-80K         | E73                   | E81       | PA<7-1>L | PCAS 0 L | PRAS 4 L       | WTBT 2 L                              | WTBT 0 L |

| 80-96K         | E72                   | E80       | PA<7-1>L | PCAS 0 L | PRAS 5 L       | WTBT 2 L                              | WTBT 0 L |

| 96-112K        | E71                   | E79       | PA<7-1>L | PCAS 0 L | PRAS6L         | WTBT 2 L                              | WTBT 0 L |

| 112-128K       | E70                   | E78       | PA<7-1>L | PCAS 0 L | PRAS7L         | WTBT 2 L                              | WTBT 0 L |

Table 3-2

Parity Storage in Array

The remaining input signals required by the chips are generated by the MS11-L logic. These signals are distributed to the array via a number of inverting line drivers, due to fanout considerations. The number of drivers is different for each version of the MS11-L. Sheets 9 and 10 in the print set show the 64 drivers used in a 128K memory. The signal distribution to the 128K array is summarized below.

- 1. The multiplexed row address and column address signals are routed to all the chips in the array by five groups of seven lines.

- 2. One Column Address Strobe is routed to all the chips in the array by nine lines.

- 3. One Row Address Strobe is routed to each 18-chip bank by two lines.

- 4. One write byte signal is routed by two lines to the 72 chips which correspond to each byte (data and parity).

During a memory data cycle, the 18-chip bank which contains the desired word location is enabled by asserting the appropriate Row Address Strobe. Chips that do not receive an asserted RAS L signal, do not cycle internally, remaining in a low-power (standby) state.

# 3.3 FUNCTIONAL DESCRIPTION

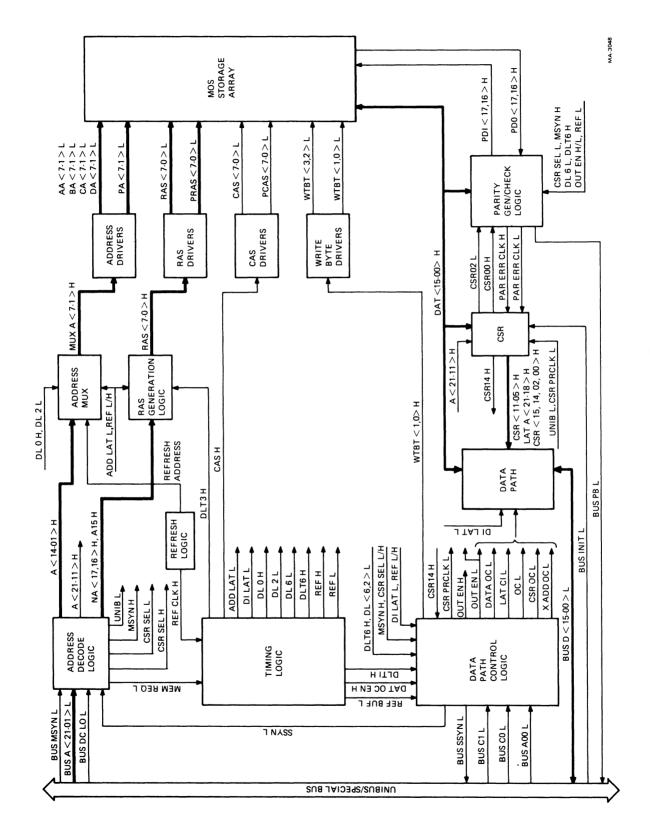

A block diagram of the MS11-L is shown in Figure 3-4. The memory is compatible with the PDP-11 Unibus or special buses that have 22 address bits. Unibus or special bus operation is specified by a jumper on the module. Data cycles are initiated by the bus master; refresh cycles are initiated within the memory.

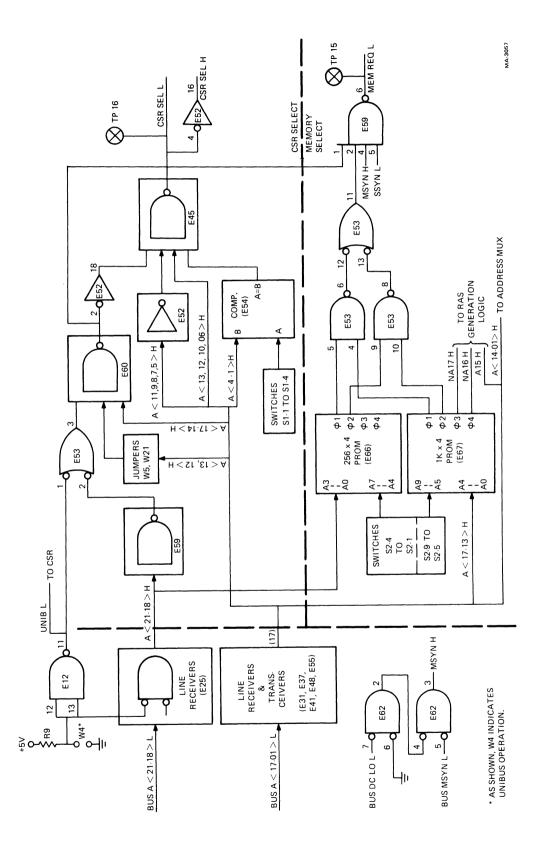

The address decode logic determines if an address on the bus is assigned to the CSR or MOS storage array in the MS11-L. The address decode logic also checks BUS DC LO L (generated by the computer power supply) and SSYN L. Access to the MOS storage array is prevented if BUS DC LO L or SSYN L is asserted or if the bus address is within the I/O peripheral page. Access to the CSR is prevented if BUS DC LO L is asserted. If Unibus operation is specified, the logic associated with address bits A21-A18 is disabled. Therefore, the assigned CSR address and address space reserved for the I/O peripheral page are automatically in the Unibus address space.

With BUS MSYN L asserted, the address decode logic enables bus master access to the storage array by asserting MEM REQ L. The timing logic then initiates a memory data cycle if the memory is not busy. Timing signals and address information are used by the address mux and RAS generation logic to provide the row address, column address and Row Address Strobe to the array. The Column Address Strobe is provided by the timing logic. Address bits A17 and A16 may have been modified by the address decode logic to provide NA17 and NA16. These two lines and A15–A01 are latched in and specify the data location in a 128K MOS storage array as follows:

| Select 1 of 8 RAS signals to be asserted which in<br>turn enables the 18-chip bank that contains the de-<br>sired data location |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Collection be called the desired more different in the                                                                          |  |  |  |

| Collectively select the desired word location within the enabled 18-chip bank.                                                  |  |  |  |

|                                                                                                                                 |  |  |  |

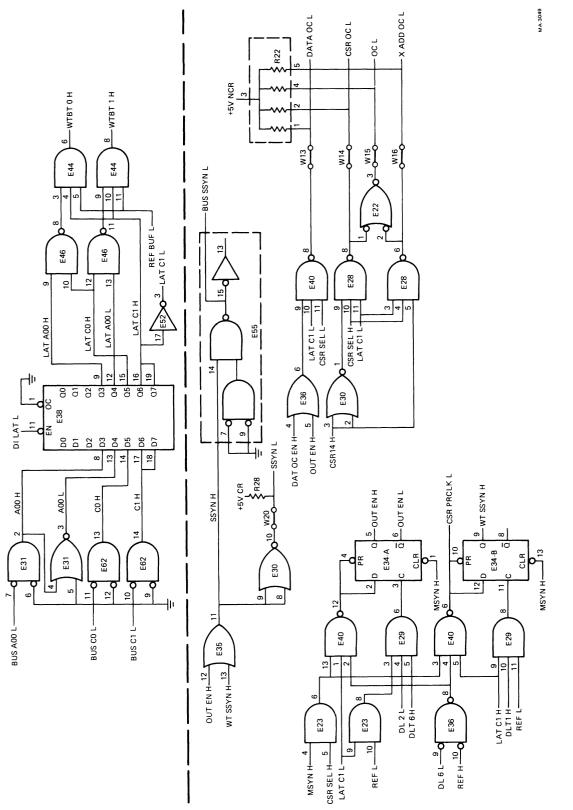

Control signals on the bus (C0 and C1) specify the type of data transfer (DATI, DATIP, DATO or DATOB). If a DATOB cycle is specified, address bit A00 selects the byte to be written. The data path control logic uses bus signals C0, C1 and A00 in conjunction with address decode and timing signals to control the flow of data on the module. Signals BUS SSYN L and SSYN L are also controlled by the data path control logic.

For a memory data cycle, C0, C1 and A00 are latched-in. If a memory write cycle (DATO or DATOB) is specified, data from the bus is channeled to the DAT < 15-00 > H lines and latched. Two parity bits are generated based on the data (one parity bit for each data byte). The appropriate data byte(s) and parity bit(s) are then written into the desired location of the MOS storage array. If a memory read cycle (DATI or DATIP) is specified, the two data bytes and parity bits are retrieved from the desired location in the storage array. The parity of the data is recalculated and compared to the retrieved parity. The data is then placed on the bus and if a parity error is detected, the parity gen/check logic initiates the following steps:

- 1. The parity error bit (bit 15) in the CSR is set to a logical 1.

- 2. A red LED on the module turns on, providing a visual indication of a parity error.

- 3. If bit 0 in the CSR is set, signal BUS PB L is asserted warning the CPU that a parity error has occurred.

- 4. A partial address of the faulty data is stored in the CSR.

The write byte signals specify a read or write operation for the MOS chips in the array that are associated with each byte. The specified operation is carried out by the 18-chip bank for which the Row Address Strobe and Column Address Strobe are asserted. A DATIP bus cycle involving memory data is executed in the same manner as a DATI cycle. The control and status register (CSR) allows program control of certain parity functions and contains diagnostic information if a parity error has occurred. The address decode logic enables bus master access to the CSR by asserting CSR SEL H, CSR SEL L and then MSYN H. The timing logic is not activated for a data transfer involving the CSR. Therefore, the CSR can be accessed during a refresh cycle. If bus signals C0 and C1 specify a write cycle (DATO or DATOB), data from the bus is channeled to the DAT <15-00> H lines and clocked into the CSR. A DATOB bus cycle is executed as a DATO cycle. If a read cycle (DATI or DATIP) is specified, information from the CSR is channeled via the data path circuit to the bus. The information placed on the bus for bits 11-05 is determined by the data path control logic in accordance with CSR bit 14. Error address information (A17-A11) or data previously written into the CSR is retrieved if CSR bit 14 is cleared. Error address bits A21-A18 are retrieved if bit 14 is set. For special bus operation, CSR bit 14 is a read/write bit but for Unibus operation it is a read-only bit which is always cleared. A DATIP bus cycle is executed as a DATI cycle.

All MOS chips in the storage array are periodically refreshed by a specially-timed, RAS-only, refresh cycle. An oscillator in the refresh logic is used to activate the timing logic for a refresh cycle every 14.5  $\mu$  s if the memory is not busy. In accordance with the timing signals, the address mux channels the refresh address to the array, and the RAS generation logic asserts all eight Row Address Strobes. For each chip in the array, the refresh address is interpreted as a row address specifying 128 data cells that are refreshed in a cycle. After each refresh cycle, the address is incremented by one. Therefore, a different address is used during each successive refresh cycle so that all 128 row addresses are refreshed in less than 2 ms. Note that the Column Address Strobe and write byte signals are inhibited.

## 3.4 TIMING LOGIC

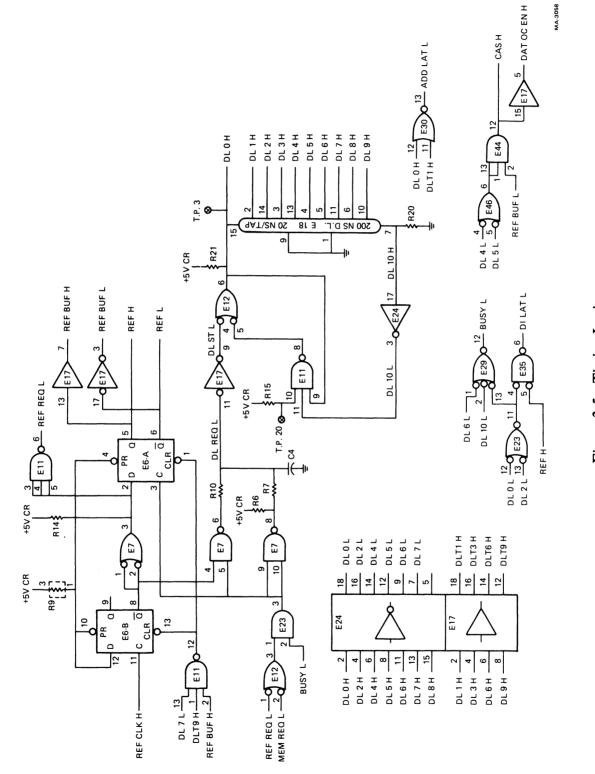

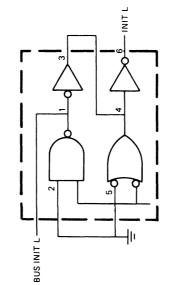

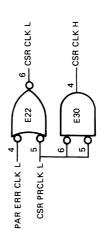

The timing logic, shown in Figure 3-5, generates a sequence of signals that causes the execution of a memory data cycle or refresh cycle. To initiate a memory data cycle, the address decode logic must assert MEM REQ L. To initiate a refresh cycle, REF REQ L must be asserted by clocking a logical 1 into E6-B at the leading (rising) edge of REF CLK H. The timing logic is not used to execute a data cycle involving the CSR.

With BUSY L negated, the assertion of MEM REQ L or REF REQ L causes E23 pin 3 to go high. Capacitor C4 discharges, DL 0 H is asserted triggering the timing chain, and BUSY L is asserted. Signal BUSY L remains asserted until the end of the cycle and therefore, the start of another cycle is prevented until the present cycle is completed. Memory data cycles and refresh cycles are executed on a first-come/first-serve basis.

For a refresh cycle, a logical 1 is clocked into E6-A at the leading (rising) edge of E23 pin 3; a logical 0 is clocked into E6-A for a memory data cycle. Therefore, REF H, REF L, REF BUF H and REF BUF L are asserted for a refresh cycle only. Note that E6-A is cleared at a later time in a refresh cycle and therefore, E6-A always contains a logical 0 at the end of a cycle.

The triggering of the timing chain is delayed from the beginning of a cycle but the delay is longer for a refresh cycle than for a memory data cycle. For a refresh cycle, the Q output of E6-B inhibits E7 pin 6 from going low, when E7 pin 8 goes low. Capacitor C4 discharges through a higher resistance (R7 as opposed to R7/R10) so the discharge time is longer. Therefore, the triggering of the timing chain is delayed an extra 50-60 ns for a refresh cycle.

The timing chain is generated by a 200 ns delay line (E18). The timing chain is triggered by the leading (rising) edge of DL 0 H which is applied to the input of E18. The positive-edged signal travels down the delay line, appearing at the taps along the way. Feedback derived from the DL 10 H tap is used to truncate DL 0 H, resulting in a 230 ns pulse width. Therefore, a positive pulse, 230 ns wide, appears at each delay line tap with the taps spaced at 20 ns intervals along the line.

The timing logic produces 13 signals that are used by other sections of the memory logic; 10 of these signals are timing chain outputs. Signal DL 0 H is considered one output of the timing chain. The other nine are derived from various gates that are controlled by the delay line taps and DL 0 H. Signals REF H, REF L and REF BUF L which are controlled by E6-A determine whether the timing chain causes the execution of a refresh cycle or a memory data cycle.

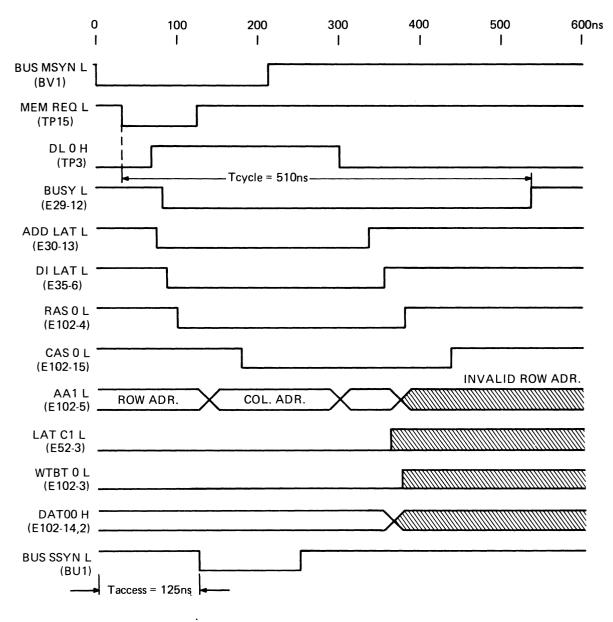

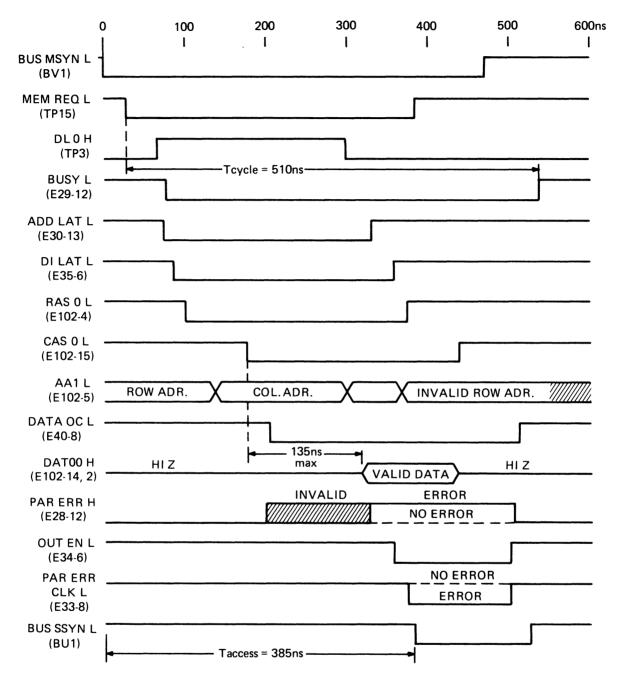

# 3.4.1 Memory Data Cycle Execution

Signals REF H, REF L and REF BUF L are negated so the timing chain executes a memory data cycle. The data path control logic determines if a DATI, DATO or DATOB data transfer is performed. A DATIP data transfer is interpreted as a DATI. The timing for these cycles is shown in Figures 3-6 and 3-7. The timing chain outputs, except DLT3 H, are listed below with a functional description of their effects during a memory data cycle. Signal DLT3 H is used for a refresh cycle only.

- ADD LAT L This signal, when asserted, causes the address mux to latch in the row address and column address, and also enables the RAS generation logic to assert 1 of 8 Row Address Strobe signals.

- DI LAT L This signal, when asserted, is used by the data path control and RAS generation logic to latch in the following address and control signals: C0, C1, A00, NA17, NA16 and A15. If a DATO or DATOB operation is specified, this timing signal is also used by the data path circuit to latch in data from the bus.

- DL 2 L,DL 0 H These signals are used to control the address mux. The row address is placed online until the DL 2 L pulse appears. The column address is then placed on-line from the leading (falling) edge of DL 2 L until the trailing (falling) edge of DL 0 H.

- CAS H This signal is the Column Address Strobe that is routed to all the MOS chips in the array by inverting line drivers. When this timing signal is asserted, the column address is latched into the 18 chips that are enabled by the Row Address Strobe signal.

- DAT OC EN H If a DATI operation is specified, the assertion of this timing signal results in the assertion of DATA OC L by the data path control. The tristate outputs of the data-out latches in the data path are then enabled.

- DLT6 H,DL 6 L If a DATI operation is specified, these signals, when asserted, enable the parity checking circuitry in the parity gen/check logic.

- DLT1 H If a DATO or DATOB operation is specified, the leading (rising) edge of this signal causes the data path control logic to assert BUS SSYN L and SSYN L.

- DL 2 L,DLT6 H If a DATI operation is specified, these signals are used by the data path control logic to gate the following signals: BUS SSYN L, SSYN L, OUT EN L and OUT EN H. These data path control outputs are asserted at the trailing (rising) edge of DL 2 L. Data from the storage array is latched in by the data-out latches, and the line transceivers are enabled placing data on the bus. At this time, the parity gen/check logic initiates certain steps if a parity error has been detected.

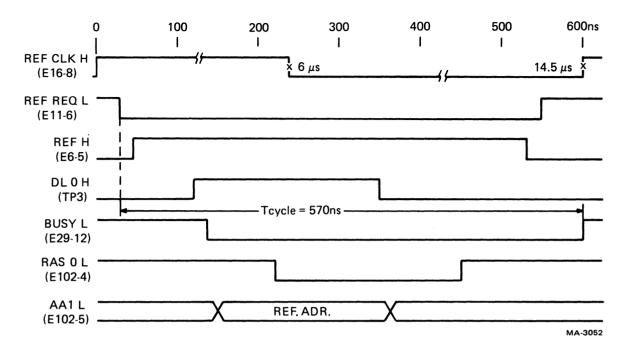

## 3.4.2 Refresh Cycle Execution

Signals REF H, REF L and REF BUF L are asserted so the timing chain executes a refresh cycle (Figure 3-8). These three signals disable the data cycle functions of the timing chain and enable the refresh functions as follows:

#### NOTES

- 1. SIGNALS RAS 0 L, CAS 0 L, AA1 L, WTBT 0 L AND DAT00 H ARE AT THE MOS STORAGE ARRAY (PARAGRAPH 3.2.2).

- 2. FOR A DATO OPERATION, BUS AND PROCESSOR DELAYS DETERMINE WHEN THE FOLLOWING SIGNALS ARE FIRST ASSERTED: LAT C1 L, WTBT 0 L, DATA (i.e. DAT00 H) AND THE MULTIPLEXED ROW ADDRESS (i.e. AA1 L). TYPICALLY, THESE SIGNALS ARE ASSERTED BY THE TIME BUS MSYN L APPEARS AT THE MEMORY RECEIVER. SIGNALS LAT C1 L AND WTBT 0 L ARE LATCHED WHEN DI LAT L IS ASSERTED.

- 3. DATA FROM THE BUS IS CHANNELED TO THE DAT <15-00> H LINES WHEN LAT C1 L IS ASSERTED.

MA-3046

Figure 3-6 DATO/DATOB Memory Timing (Typical)

NOTES

- 1. SIGNALS PAR ERR H, PAR ERR CLK L AND PAR ERR CLK H ARE GENERATED BY THE PARITY GEN/CHECK LOGIC.

- 2. ONCE THE DATA AND PARITY BITS ARE RETRIEVED FROM THE ARRAY, SIGNAL PAR ERR H BECOMES VALID.

MA-3047

Figure 3-7 DATI/DATIP Memory Timing (Typical)

Figure 3-8 Refresh Timing (Typical)

#### **REF L**

- 1. Disables the selection of the row address and column address by the address mux.

- 2. Disables the decoding of NA17, NA16 and A15 by the RAS generation logic.

- 3. Disables the effect of the timing signals on the following data path control outputs: OUT EN H, OUT EN L, SSYN L and BUS SSYN L. However, these outputs can still be asserted in reaction to a data transfer involving the CSR.

- 4. Disables the circuitry which reacts to a parity error.

#### **REF BUF H**

- 1. Inhibits the assertion of the write byte signals by the data path control logic.

- 2. Inhibits the assertion of CAS H and DAT OC EN H by the timing logic.

#### **REF H**

- 1. Inhibits the assertion of DI LAT L by the timing logic.

- 2. Enables the address mux to select the refresh address when DL 0 H is asserted.

- 3. Enables the RAS generation logic to assert all eight Row Address Strobes when DLT 3 H is asserted.

Timing chain signals DL 7 L and DLT9 H are used in conjunction with REF BUF H to produce a clear pulse for E6-A and E6-B (Figure 3-5). Flip-Flop E6-A, in turn controls signals REF H, REF L, REF BUF H and REF BUF L. In preparation for the next memory cycle, these four signals are negated when E6-A and E6-B are cleared at the trailing (rising) edge of DL 7 L. Signal REF REQ L is also negated at this time.

#### 3.5 **REFRESH LOGIC**

The refresh logic, shown in sheet 6 of the print set, generates REF CLK H and the refresh address. Signal REF CLK H is derived from a 555 timer (E5) which is set up as a free running oscillator, powered by the +15 V/+12 V module input (V-555). The REF CLK H signal oscillates with a period of 14.5  $\mu$ s and has a positive pulse width of 6  $\mu$ s during each period. The leading (rising) edge of REF CLK H is used by the timing logic to assert REF REQ L and therefore, REF REQ L is asserted once every 14.5  $\mu$ s. Signal REF REQ L, when asserted, initiates a refresh cycle if the memory is not busy. If the memory is busy, the refresh cycle is delayed until the present cycle is completed (Paragraph 3.4).