## PRELIMINARY

M9301 BOOTSTRAP TERMINATOR

MAINTENANCE MANUAL

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

Copyright © by Digital Equipment Corporation

Written by PDP-11 Engineering

|  |  |   | σ  |

|--|--|---|----|

|  |  |   | 23 |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   | s. |

|  |  |   |    |

|  |  |   |    |

|  |  | · |    |

|  |  |   |    |

|  |  |   |    |

|  |  |   |    |

# M9301 MAINTENANCE MANUAL

# CONTENTS

| 1.0                                       | PREFACE                                                                                                                                                                                                                                    |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>♦ 및</b> ☆                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                      |

| 2,0                                       | INTRODUCTION                                                                                                                                                                                                                               |

| 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5 | General Description Features Physical Description Electrical Specification Power Consumption Electrical Interfaces External Electrical Interfaces Electrical Prerequisites Power and Ground Pinouts Modified UNIBUS Pin Assignments Timing |

|                                           | Operating Environmental Specifications<br>Temperature Range<br>Relative Humidity                                                                                                                                                           |

| 3.0                                       | HARDWARE DESCRIPTION                                                                                                                                                                                                                       |

| 3,7                                       | Introduction Definition of Terms Overview Power Up Booting Logic External Boot Circuit Power Up Transfer Detection = Logic Power Up Clear Address Detection Logic Address Offset Switch Bank Rom Memory M9301 Terminator                   |

## Contents (Con't)

```

4.0

M9301 VARIATIONS

4,1

Overview

4.2

M9301-0

4.3

M9301-YA and M9301-YB

Physical Differences from M9301-0

4.3.1

4.3.2

Program Memory Maps

4.3.2.1

CPU Diagnostics

4.3.2.2

Register Display Routine

4,3,2,3

Memory Diagnostics

4.3.2.4

Bootstrap Programs

RX11 Diskette

TA11 Cassette

PC11 Paper Tape

Disks

Magtape

Console Emulator

4.3.2.5

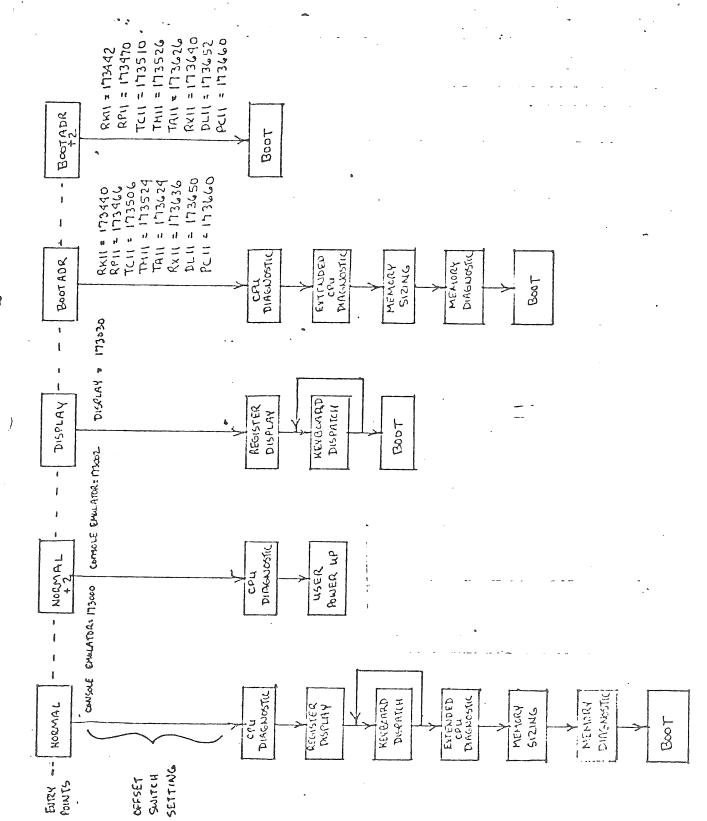

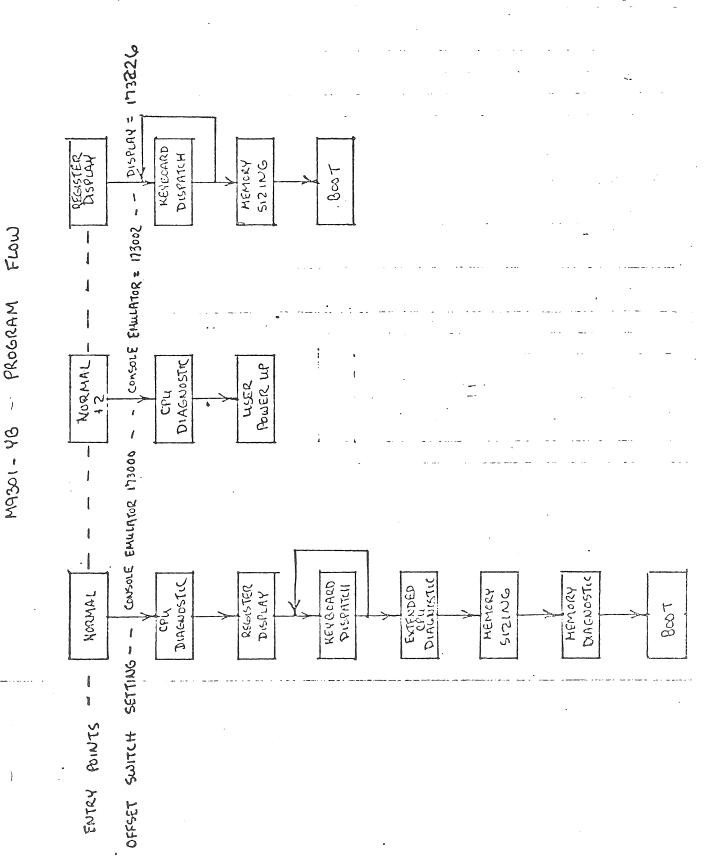

Program Flows

M9301 YA

M9301 YB

4,3,3

Installation

4.3.3.1

Reboot Enable

4.3.3.2

Low Rom Enable

4.3.3.3

Boot Switch Selection

4.3.3.4

External Boot Switch

4,4

M9301-YC

4,4.1

Memory Map

4.4.2

General Description

4.4.3

Diagnostic test Descriptions

4.4.4

11/70 Bootstrap

4.4.5

Installation

4.4.6

Starting Procedure

4.4.7

Errors

5,0

EXTENDED ADDRESSING

5.1

Extended Addressing (Defination)

5,2

Defination of Virtual and Physical addresses

5.3

Address mapping without Memory Management

5,4

Address Mapping with Memory Management

5,5

Creation of a Virtual address

5,6

Memory Management Registers

5.7

Address Assignments

6.0

M9301=YD

6.1

Purpose

6.2

Functionality

6.3

Using the M9301-YD

6.4

Program Listing

7.0

APPENDIX

```

### 1.0 PREFACE

This manual describes the M9301 Bootstrap/Terminator module and its various versions. Complete understanding of its contents requires that the user have a general knowledge of digital circuitry and a basic understanding of PDP=11 computers. The following related documents may be valuable as references.

PDP11 Peripherals Handbook PDP11 Processor Handbooks PDP=11/34, 11/39, USERS MANUAL

### 2.0 INTRODUCTION

### 2.1 General Description

The M9301 Bootstrap/Terminator is a double height extended module which plugs into a terminator slot on most PDP11 computers (see Installation Section 4). It contains a complete set of UNIBUS termination resistors along with 512 words of Read-Only memory which can be used for bootstrap programs. The module also provides circuitry for initiating bootstrap programs either on power ups or from an external or logic level switch closure, See Figure 1 for photo of module,

### 2.2 Features

- Combines UNIBUS termination and bootstrap capability on one double height module.

- . Can be used in all PDP11 machines which can handle an extended length module in the terminator slots.

- Bootstrap programs can be initiated by the following means:

- 1. Direct program jumps to the memory space occupied by the bootstrap.

- 2. Programmer console Load address and start sequence.

- 3. Power restarts (See Section 3.3)

- 4. External Boot switch closure

- Provides capability of enabling or disabling boots on power restarts.

- Provides 512 words of user memory space which can be programmed by the user or purchased with standard patterns provided by DEC. (See sections 3.10 and 4.2).

Module Photo

To Be Supplied

### 2.3 Physical Description

The M9301 is a double height extended (8  $1/2 \times 5$  1/2 inches) FLIP-CHIP module which plugs into the A and B terminator slots on the PDP11 backplane. External connections are made via three FAST ON (TP1,TP2, and TP3) tabs provided at the handle end of the module.

2.4 Electrical Specification

2.4.1 Power Consumption

+5V DC = 2.0 Amperes typical

2.4.2 Electrical Interfaces

The UNIBUS interface is standard using 8837 and 8640 receivers and 8881 drivers.

## 2.4.3 External Electrical Interfaces

The external interface consists of three FAST ON tabs (TP1, TP2 and TP3), each having the following loading and usage constraints.

- TP1 Represents one standard TTL load with a 1K ohm pull-up. Input should be stable during a nower up. Refer to Section 3.3 for TP1 usage.

- TP2 Represents two standard TTL loads with a 1K ohm pull-up resistor. Input signals should be limited to a 100ns minimum pulse width with all switch bounce noise restricted to a 5ms maximum duration. Note that triggering is initiated upon release of an input low (logic "Ø") pulse. On all power-ups, triggering is disabled until approximately 100ms after power returns (See Section 3.7) assuming that +5 VOC will be available from the power supply within 27ms. It is also important to realize that this input has no over voltage protection capability and adequate filtering must be provided when remoting this input outside the standard DEC computer enclosure. Refer to Section 3.5 for TP2 usage.

- TP3 Should be used as a ground return for external switches attached to TP1 and TP2. Note that there is no protection for large voltage spikes on this input so proper filters should be externally installed to guarantee adequate isolation.

2,4,4 Electrical Prerequistes

Refer to Section 4.0 for system constraints on specific version being used.

2.4.5 Power and Ground Pinouts

+5VDC:

pin AAZ, BAZ

GND:

PINS ACZ, AT1, BC2, BT1

2.4.6 M9301 MODIFIED UNIBUS Pin Assignments

See TABLE 1.

2.4.7 Timing

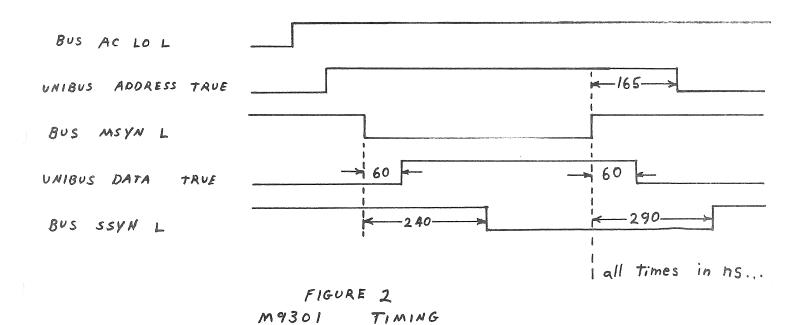

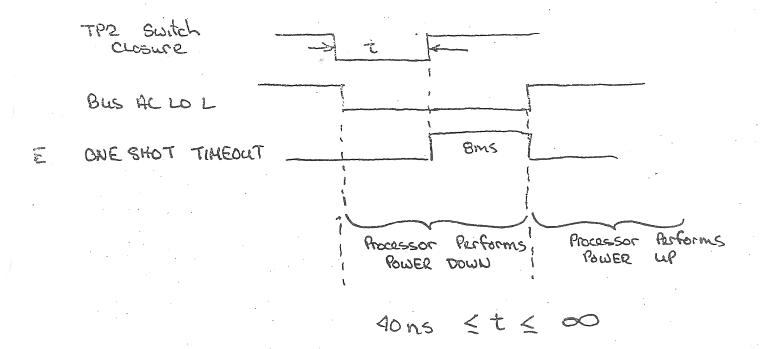

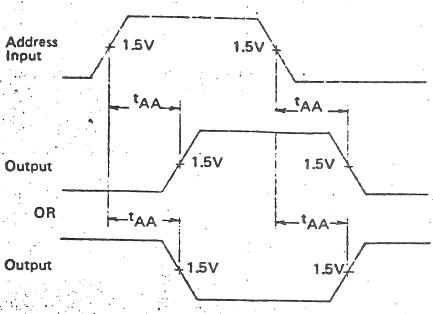

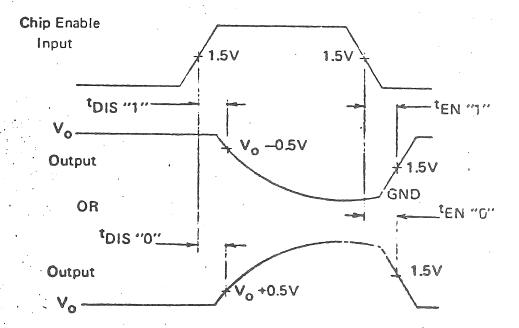

Figure 2 shows important timing constraints for the M9301. Values shown are typical.

FIGURE 2 M9301 TIMING

- 2.5 Operating Environmental Specifications

- 2.5.1 Temperature Range Ø c to 70 c

- 2.5.2 Relative Humidity = 20% to 95% (with out condensation)

TABLE 1

M9301 MODIFIED UNIBUS PIN ASSIGNMENTS

| PIN                      | SIGNAL                                              | PIN        | SIGNAL         |

|--------------------------|-----------------------------------------------------|------------|----------------|

| AA1                      | BUS INIT L                                          | BA1        | SPARE          |

| <b>SAA</b>               | POWER (+5V)                                         | BAZ        | POWER (+5V)    |

| AB1                      | BUS INTR L                                          | 881        | SPARE          |

| ABS                      | TEST POINT                                          | 882        | TEST POINT     |

| AC1                      | BUS DOO L                                           | BC1        | BUS BR 5L      |

| ACS                      | GROUND                                              | BCS        | GROUND         |

| AD1                      | TEST POINT BUS DOO L GROUND BUS DO2 L BUS DO1 L     | BD1        | BAT-BACKUP +5V |

|                          | BUS DO1 L                                           | BDZ        | BR 4L          |

| AE1                      |                                                     |            |                |

| AE2                      |                                                     | BE 5       |                |

| AF1                      | BUS DO6 L                                           | BF1        | BUS ACLO L     |

| AF2                      |                                                     | BFZ        | BUS DCLO L     |

|                          | BUS DO8 L                                           | BH1        | BUS AO1 L      |

| AH2                      |                                                     | BH2        |                |

| AJ1                      |                                                     | <b>BJ1</b> |                |

| AJ2                      | BUS DO9 L                                           | <b>BJ2</b> |                |

| AK1                      | BUS D12 L                                           | BK1        | BUS AØ5 L      |

| VK5                      | BUS D11 L                                           | BK5        | BUS A04 L      |

| AL1<br>AL2<br>AM1<br>AM2 | BUS D14 L                                           | BL1        | BUS A07 L      |

| AL2                      | BUS D13 L                                           | BL2        | BUS AØ6 L      |

| AM1                      | BUS PA L                                            | BM1        | BUS AM9 L      |

|                          |                                                     | BMZ        | BUS A08 L      |

| ANI                      | P 1                                                 | BN1        | BUS A11 L      |

|                          | BUS PB L                                            | BNZ        | BUS A10 L      |

| AP1                      | PØ                                                  | BP1        | BUS A13 L      |

|                          | BUS BBSY L                                          | BP2        | BUS A12 L      |

| AR1                      | BAT BACKUP +15V                                     |            |                |

|                          |                                                     | BR2        |                |

| AS1                      | BAT. BACKUP =15V                                    | B\$1       | BUS A17 L      |

| ASZ                      | BUS NPR L                                           | BSZ        | BUS A16 L      |

| AT1                      | GROUND                                              | BT1        | GROUND         |

| AT2                      | BUS NPR L GROUND BUS BR 7L +20V BUS BR 6L +20V +20V | BT2        | BUS C1 L       |

| AU1                      | +20V                                                | BU1        | BUS SSYN L     |

| SUA                      | BUS BR 6L                                           | BUZ        | BUS CO 1       |

| AV1                      | +20V                                                | BV1        | BUS MSYN L     |

| 2 V A                    | + 2 Ø V                                             | BVZ        | <b>™</b> 5∀    |

## 3.0 HARDWARE DESCRIPTION

## 3.1 Introduction

The following is a detailed circuit description of the M9301 Bootstrap/Terminals module. Various segments of this module will be analyzed separately for clarity. M9301 circuit schematics will be referenced throughtout the description. (CS M9301-0-1).

## 3.2 Definition of Terms

## 3.2.1 Bootstrap Program

A bootstrap program is any program which load another (usually larger) program into computer memory from a peripheral device.

## 3,2,2 Boot

Boot is a verb which means to initiate execution of a hootstrap program.

## 3,2,3 Bootstrap

Bootstrap and bootstrap program are used interchangeably.

### 3.3 Overview

Typically all PDP11 computers perform what is referred to as a power up sequence each time power is applied to their CPU module(s). This sequence is as follows:

## 3.3 Overview continued

+5VDC COMES TRUE

BUS DC LO L RELEASED BY POWER SUPPLY

BUS AC LO L RELEASED BY POWER SUPPLY

PROCESSOR ACCESSES MEMORY LOCATION 24(8) FOR NEW PC

PROCESSOR ACCESSES MEMORY LOCATION 26(8) FOR NEW PSW

PROCESSOR BEGINS RUNNING PROGRAM

AT NEW PC CONTENTS

WITH AN M9301 BOOTSTRAP/TERMINATOR IN THE PDP11 computer system, on power ups the user can optionally (a switch on the M9301 can enable or disable this feature) force the processor to read its new PC from a ROM memory location (unibus Location 773024(8)) and offset switch bank on the M9301, A new PSW will also be read from a location (UNIBUS Location 773026(8)) in the M9301 memory. This new PC and PSW will then direct the processor to a program (typically a bootstrap) in the M9301 ROM (UNIBUS memory locations 773000 thru 773776).

If booting on power ups is disabled an external switch or logic level and be used to force the processor to execute a boot program. Programs in the M9301 can also be initiated by program jumps to their starting addresses or through the START switch feature of a programmer's switch console if one is available in the system.

3.4 Power Up Booting Logic

AC LO and DC LO

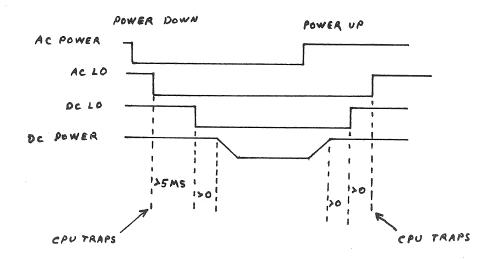

The status of every PDP11 power supply is described by the two UNIBUS control lines BUS AC LO L and BUS DC LO L. The condition of these two lines in relation to the +5 volt output of the power supply is defined by UNIBUS specifications as summarized in Figure 3.

## Figure 3 Power fail Sequence

Power Up or Power DOWN

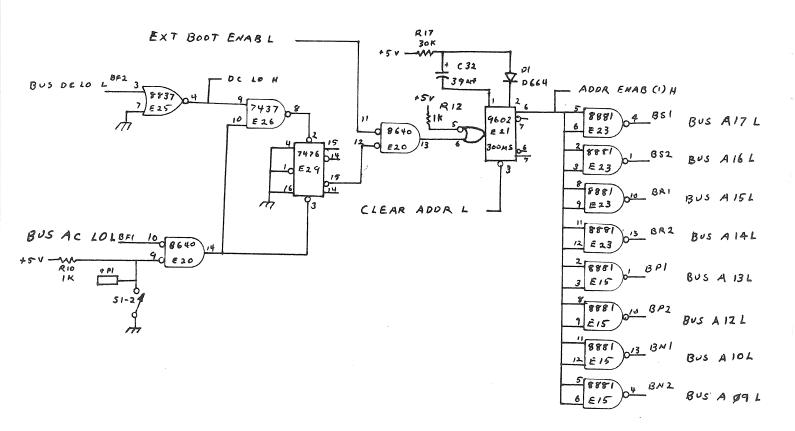

On the M9301, Power up sequences are detected by the circuitry shown in Figure 4. When +5 volts first becomes true, both Bus AC LO, and BUS DC LO are asserted low. Assuming the POWER UP REBOOT ENABLE switch (Si=2) is closed on, flip flop E29 will then be set. When BUS DC LO L goes high followed by BUS AC LO L, this flip=flop is then cleared generating a low=to high transition on the output of E20 (pin 13). This transition triggers the one=shot E21 which asserts UNIBUS address lines BUS A09 L, BUS A10 L, and BUS A12 L thru BUS A17 L for 300 ms.

FIGURE 3 Power Fail Sequence

# FIGURE 4 POWER UP BOOT LOGIC

Processor reads new program counter

During the 300 ms time-out of E21, the central processor will be performing its power up sequence, when the processor attempts to read a new program counter (PC) address from memory location 24(8), the address bits enabled by the one-shot are logically ORed to generate the address 773024(8). This location happens to be an address in the M9301 rom space which contains the starting address of a specific (see Section 3.9) boot routine.

Processor read new status word

Having obtained a new PC from location 773024(8); the processor then attempts to read a new Processor Status Word (PSW) from memory location 26(8). The address bits enabled by one-shot E21 are logically ORed to generate the address 773026(8) which is also in the M9301 ROM address space. Once this transfer is completed the removal of MSYN from the bus will generate a ADDR CLR L signal (See Section 3,6) which clears the one-shot (E21) timeout removing address bits BUS A09, BUS A10, and BUS A12 thru BUS A17. The 300 ms timeout length of E21 was chosen to guarantee enough time for all PDP11 processors to complete the two memory transfers described before releasing the address lines.

POWER UP REBOOT ENABLE

FIGURE 4

POWER UP BOOT LOGIC

The POWER UP REBOOT ENABLE switch (S1-2) can be used to disable the logic shown in Figure 4. With this switch open, the clear input to the flip-flop E29 will always be low, preventing it from ever being set on power restarts. FAST ON tab TP1 is provided to allow switch S1=2 to be remoted external to the module, Note that when an external switch is used, S1=2 must be left in the off position.

### 3.5 External Boot Circuit

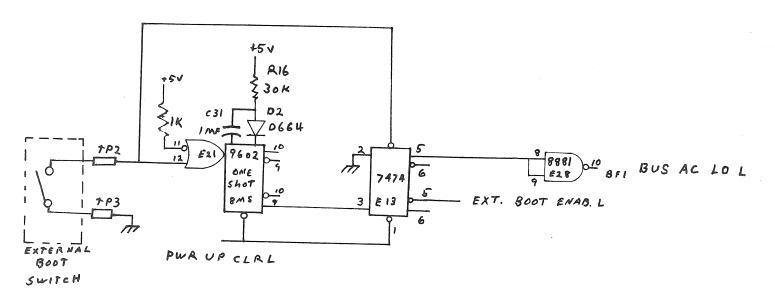

The processor can be externally activated by grounding the FAST ON tab TP2 input, as shown in FIGURE 5, This low input sets flip-flop E13 which then generates a BUS AC LO L signal on the UNIBUS. Upon seeing this

# FIGURE 5 EXTERNAL BOOT CIRCUIT

UNIBUS SIGNAL EVERY PDP11 processor will begin a power down routine anticipating a real power failure. After completing this routine, the processor will then wait for the release of BUS AC LO L at which time it will perform a power up sequence through location 24(8) and 26(8).

When the EXTERNAL BOOT input is released, the oneshot E21, is triggered causing an 8 ms timeout, and the set input to flip-flop E13 removed. At the end of the one-shot timeout, flip-flop E13 is clocked low releasing the BUS AC LO L line and firing the 300 ms one-shot (E21) mentioned in Section 3.4. The processor then is forced to read its new PC and PSW from location 773024 and 773026 respectively as described in Section 3.4.

FIGURE 5

EXTERNAL BOOT CIRCUIT

FIGURE 6

EXTERNAL BOOT TIMING

## 3.6 Power Up Transfer Detection Logic

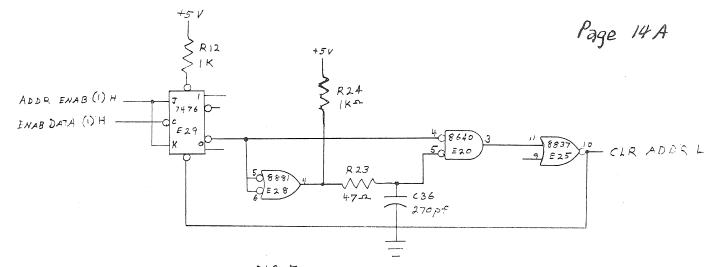

# FIGURE 7 TRANSFER DETECTION LOGIC

After BUS AC LO L and BUS DC LO L have performed their power up sequence as described in Section 3.4, the logic shown in Figure 7 counts the first two DATI transfers on the UNIBUS and generates a 75 ns pulse on the CLR ADDR L line. The two UNIBUS transfers performed will be to obtain a new PC and PSW as previously described. The CLR ADDR L pulse resulting will be used to clear the one shot E21 shown in Figure 4 releasing bus address line BUS A29, BUS A10, and BUS A12 thru BUS A17.

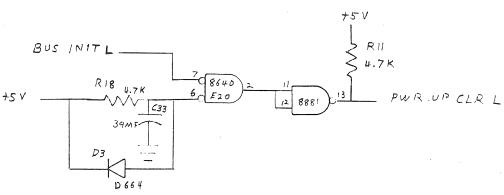

### 3.7 Power Up Clear

The circuit shown in Figure 8 is included on the M9301 to quarantee that specific storage elements on the module are cleared when power is first applied the PWR CLR L signal will be held low for approximately 70 ms after the +5VDC has returned assuming the +5V supply has a rise time of less than 20ms. The exact period of time for holding PWR CLR L is a function of the rise time of the +5VDC power supply.

FIGURE 8

POWER UP CLEAR LOGIC

FIG. 7 TRANSFER DETECTION LOGIC

FIG. 8

POWER UP CLEAR LOGIC

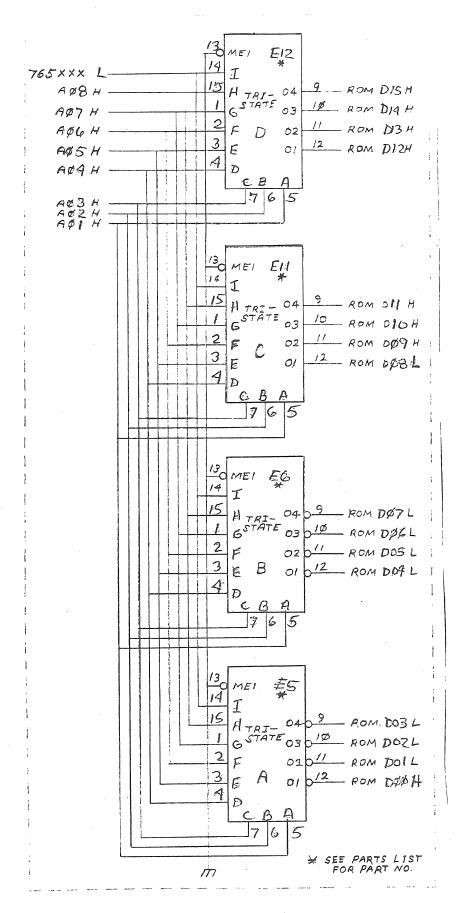

## 3,8 Address Detection Logic

M9301 Address Space

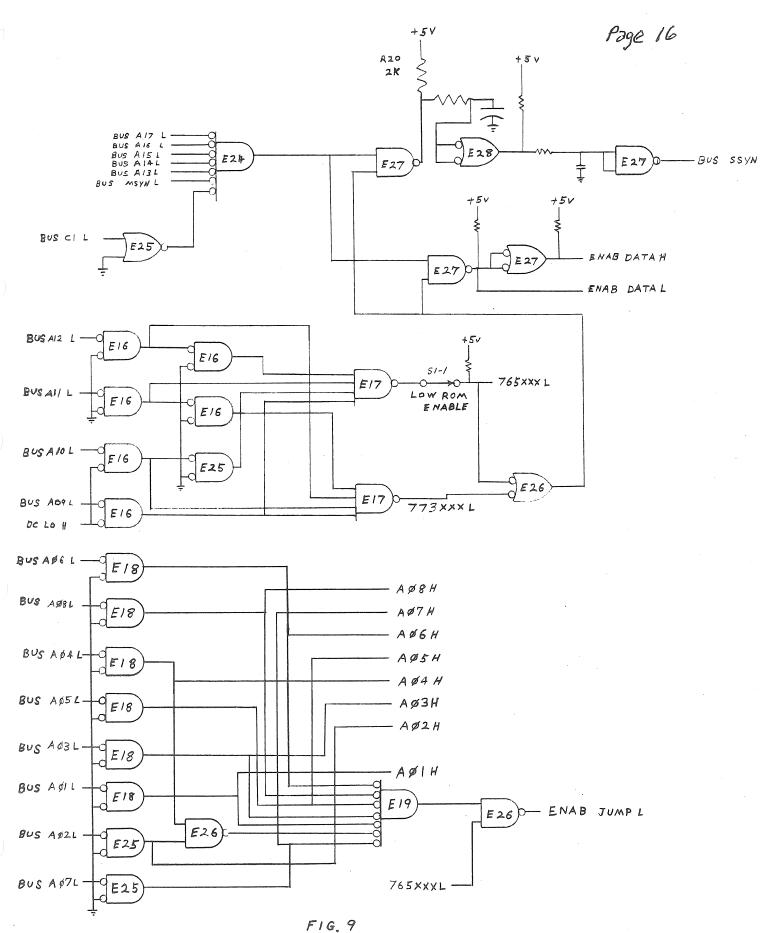

Figure 9 shows the complete UNIBUS address detection logic on the M9301. The purpose of this circuitry is to detect UNIBUS addresses within the address space of the M9301 773000(8) = 773777(8) and 765000(8) = 765777(8)), and recognize the specific addresses 773024(8) and 773026(8) for the power up circuit previously described in Sections 3, 4, and 3.5.

ADDRESS DECODER LOGIC

## M9301 Memory Access Constraints

The circuitry show in Figure 9 determines when the M9301 ROM address space is being accessed. Upon receiving a recognized UNIBUS address, and BUS MSYN, the ROM data outputs are enabled onto the UNIBUS data lines (BUS D00 L = BUS D15 L) and BUS SSYN L is enabled 200 ns later. Conditions which must be met before enabling the ROM data and returning BUS SSYN are as follows:

- 1. Detection of the UNIBUS address 765XXX (dependent on position the of L ROM ENABLE switch S1=1) or 773XXX where XXX is redundant.

- Transfer being performed is a DATI operation where BUS C1 L is not asserted,

- 3. A BUS MSYN L control signal has been obtained.

#### Low ROM Enable Switch

LOW ROM ENABLE switch (s1-1) shown in Figure 9 allows the user to disable the M9301 detection of UNIBUS addresses 765000 tru 765777. These addresses would normally represent the lower 256 words of the M9301 memory space. Disabling the detection of these addresses S1-1 is set to OFF position) becomes essential when that memory space is being used by other peripheral devices in the system. For M9301 modules containing standard DEC programs, users should note what program features will be eliminated by disabling M9301 address locations 765000 thru 765777.

#### ROM Address Generation

Logic shown in the lower half of Figure 9 performs two functions. First it receives the nine address inputs for the M9301 RDM memory (765XXXL and A01H thru A08H). Second it detects the UNIBUS address 773024 and generates the offset switch enable signal (See Section 3.9) ENAB JUMP L.

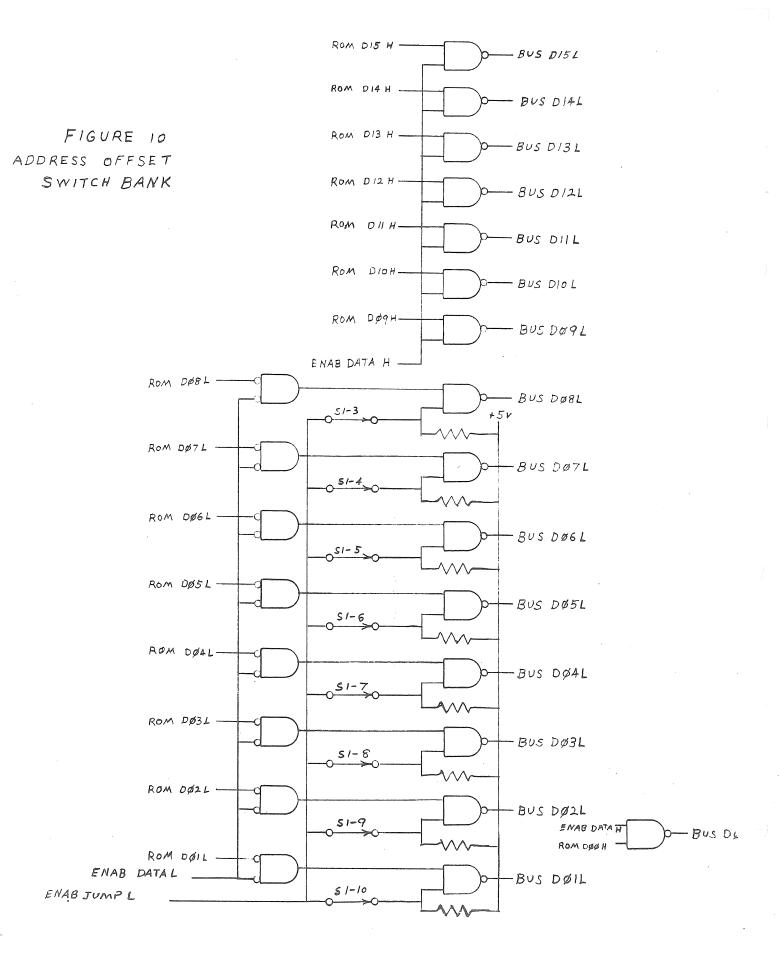

### 3.9 Address Offset Switch Bank

As previously mentioned in Section 3.4, on all boots, the M9301 processor obtains its new PC from location 773024(8) instead of location 24(8), when the M9301 address detection logic (Section 3.8) decodes the address 24(8), it enables (via ENABL JUMP L) the address offset switch bank (Figure 10) shown below. The contents of these switches, combined with the contents of the specified address in M9301 ROM memory, produce a new PC for the CPU. This new Pc will point the processor to the starting address of a specific program (usally a bootstrap routine) in the M9301 memory. Several programs can be included in the M9301 memory with any one being user selectable through the address offset switch selection

## Examples

|        | ROM address 773024 contains |        |

|--------|-----------------------------|--------|

| Offset | Switch Bank contains        | 254    |

| New PC | read by CPU                 | 173254 |

### 3.10 ROM Memory

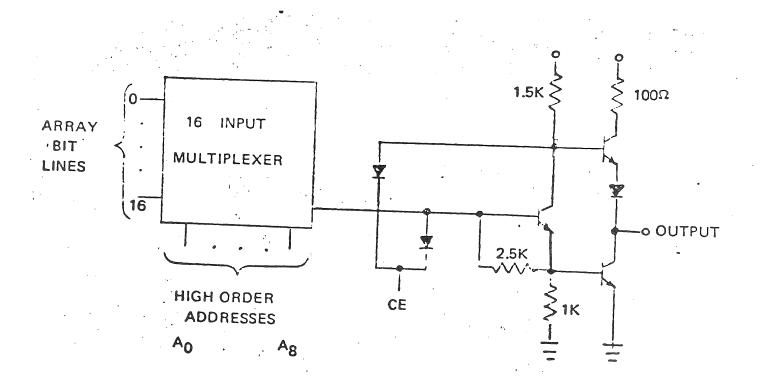

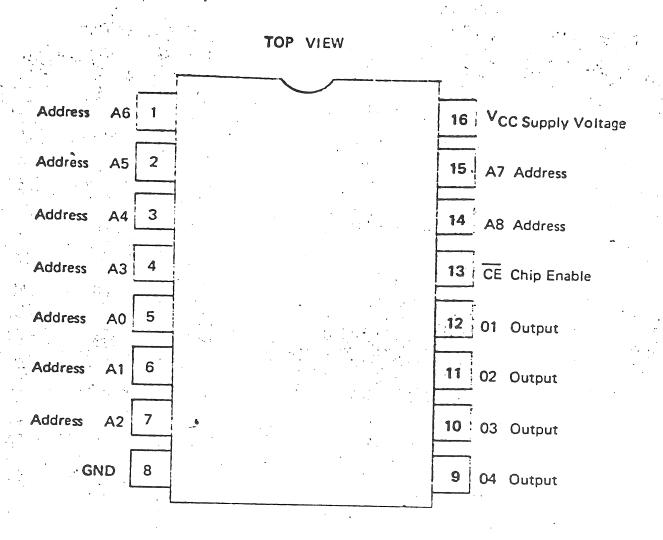

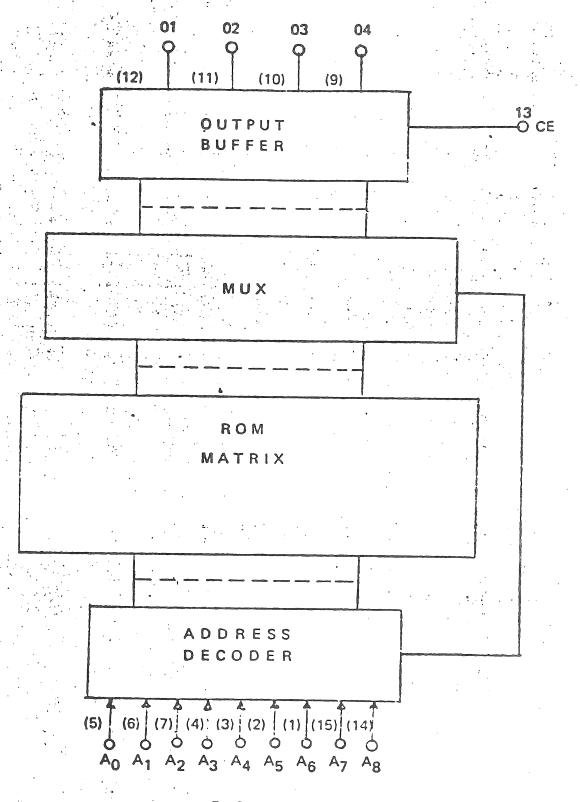

The heart of the M9301 is the 512 word ROM (Read Only Memory) shown in Figure 11. It is composed of four 512 x 4 Bit Triestate ROMS organized in a 512 x 16 bit configuration. All four units share the same address lines and produce 16-bit PDP=11 instructions for execution by the processor.

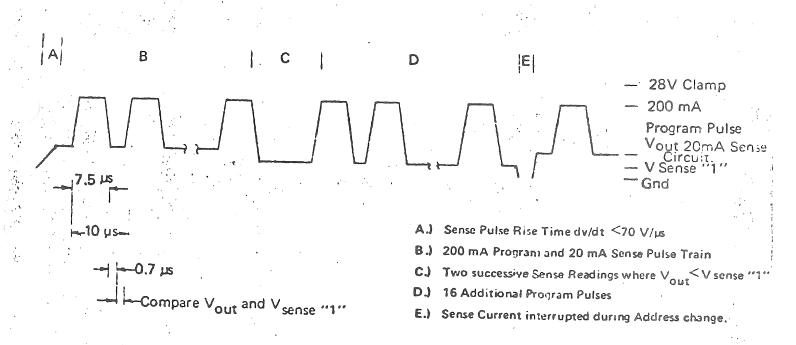

All four ROM outputs are always enabled, so any change in address inputs will result in a change in the UNIBUS data lines when the ENAB DATA signals in Figure 9 are enabled. For further information on M93Ø1 compatible ROMS, CONSULT THE ROM Specifications shown in the Appendix.

M9301 users that program their own PROMS should note the following programming constraints.

- There is no address or data output translation required.

- 2, UNIBUS address locations 773000(8) thru 773776(8) are located in the lower 256 words of PROM word space and UNIBUS address locations 765000(8) thru 765776(8) are resident in the upper 256 words.

- 3. When coding PROM patterns data bits D01 thru D08 must always contain the inverse of the data required to compensate for the extra inversion logic available in the M9301 Offset Switch Circuitry,

FIGURE 11 M9301 ROM MEMORY

## 3.11 M9301 TERMINATOR

The terminator section of the M9301 consists of four resistor pack circuits each containing the required pull-up and pull-down resistors for proper UNIBUS termination. Since PDP11/04 and PDP11/34 computers incorporate BUS GRANT pull-up resistors on the processor modules, space has been left on the M9301 for five Jumpers (W1 thru W5) which allow the user to select whether to include BUS GRANT pull-up resistors. TABLE 2 indicates which versions of the M9301 have BUS GRANT Jumpers installed.

Caution should be taken when inserting M9301 modules in various PDP11 (PDP11/05, 11/10, 11/35, 11/40) computers. If the processor in question, does not have BUS GRANT pull-ups on the CPU, jumpers W1 through W5 on the M9301, should be inserted or the M9301 should be positioned at the end on the UNIBUS furthest from the CPU.

## 4.0 M9301 VARIATION

## 4.1 Overview

The M9301 Bootstrap/Terminator presently comes in five variations as described in the following sections. Table 2 summarizes the differences between each variation.

|                                                    | M93@1 |      |       |     |     |

|----------------------------------------------------|-------|------|-------|-----|-----|

|                                                    | = 0   | - YA | - Y B | -YC | -YD |

| EXTERNAL BOOT SWITCH RESTART                       | *     | YES  | YES   | NO  | YES |

| POWER UP REBOOT ENABLE RESTART                     | *     | YES  | YFS   | NO  | YES |

| PROGRAMMERS CONSOLE STANDARD WITH COMPUTER         | *     | NO   | NO    | YES | YES |

| READ ONLY MEMORY (ROM)                             | NO    | YES  | YES   | YES | YES |

| SOCKETS SUPPLIED FOR PROGRAMMABLE (ROM/PROM)       | YES   | NO   | NŪ    | NO  | NO. |

| BUS GRANT PULL-UP TERMINATOR RESISTER (W1 THRU W5) | YES   | NO   | NO    | YES | NO  |

| SWITCH SELECTABLE BOOTING                          | *     | YES  | NO    | YES | NO  |

| STANDARD DEC BOOTSTRAPS AND MASSBUS DEVICE BOOTS   | МО    | NO   | YES   | NO  | NO  |

| STANDARD DEC BOOTSTRAPS                            | NO    | YES  | NO    | NO  | NO  |

| PDP 11/70 USER PROGRAM                             | NO    | NO   | NO    | YES | NO  |

| DDCMP USER PRGRAM                                  | NO    | NO   | NO    | NO  | YES |

\* INDICATES USER SELECTABLE

TABLE 2

M9301 VARIATION FEATURES

### M9301 Variation Usage

#### General:

None of the following M9301 variations will function in a PDP11 system containing a UNIBUS repeater, unless the M9301 is inserted in a terminator position on the processor side of the repeater.

- M9301 = 0 = Can be used in any PDP11 computer that accepts an extended length terminator. The user defines the bootstrap or program available in M9301 Rom space.

- M9301 = YA = Used in most PDP11/04, and 34 OEM machines but is program compatible with all PDP11 machines that will accept an extended length terminator. Note however, that in other machines having CPUs which do not contain BUS GRANT pull up resistors, the M9301=YA must be placed at the end of the UNIBUS farthest from the CPU.

- M9301 = YB = Same as the M9301=YA except it is intended for end user machines in the PDP11/04, and 34.

- M9301 = YC = For use in only PDP11/70 machines.

- M9301 YD Can be used in any PDP11 machine. Caution should be taken, however, when inserting the M9301 in some PDP11 computers. If the processor in question does not have BUS GRANT pull-up resisters on the CPU, Jumpers 11 thru W5 on M9301 should be inserted or, the M9301 should be placed at the end of the UNIBUS furthest from the processor. (See Section 3.11).

### 4.2 M9301=0

The M9301-0 has been created as a universal bootstrap device which allows the user to program and install customized 512 x 4 hit ROMS. This module version comes with four 16-pin IC (integrated circuit) sockets in place of the Roms normally inserted on other module versions. For pinout and access time constraints on Roms used, consult the Rom Specification shown in the Appendix. When configuring Rom bit patterns for the M9301-0, care should be taken to arrange them to meet the address and data output pinouts on the module. (See section 3.10)

## 4.3 M9301=YA and M9301=YB Versions

Two versions of the M9301 have been created for use in the PDP 11/04, and 34, computers. One version, designated M9301-YA, is for OEM (original equipment manufacturer) use and the other designated M9301-YB is for end users. Both units contain basic CPU and memory GO=NO GO diagnostics along with specific sets of bootstrap programs as shown in Table 3 and Table 4.

4.3.1 Physical Differences from the M9301-0

The only physical difference between the M9301-YA/M9301-YB modules and the M9301-0 previously described, is that specially programmed Tri State 512 x 4 bit ROMs are inserted in the four locations occupied by 16-pin DIP sockets on the M9301-0.

4.3.2 M9301-YA and M9301-YB Program Memory Map

Table 5 is a program memory map of the M9301-YA and M9301-YB modules and briefly lists the nature of each diagnostic test in the ROMS.

4.3.2.1 Basic CPU Diagnostics

TEST 1 = SINGLE OPERAND TEST

This test executes all single operand instructions using destination mode 0. The basic objective is to verify that all single operand instructions operate; it also provides a cursory check on the operation of each instruction, while ensuring that the CPU decodes each instruction in the correct manner.

TEST 1 brings the test destination register through its three possible states: zero, negative, and positive. Each instruction operates on the register contents in one of four ways:

- 1. Data will be changed via a direct operation, i.e., increment, clear, decrement, etc.

- 2. Data will be changed via an indirect operation, i.e., arithmetic shifts, add carry, and subtract carry.

- 3. Data will be unchanged, but operated upon, via a direct operation, i.e., clear a register already containing zeros.

- 4. Data will be unchanged via a non-modifying instruction (TEST).

Note that when operating upon data in am indirect manner, the data is modified by the state of the appropriate condition code. Arithmetic shift will move the "C" bit into or out of the destination. This operation, when performed correctly, inplies that the "C" bit was set correctly by the previous instruction. There are no checks on the data integrity prior to the end of the test. However, a check is made on end the result of the data manipulation. A correct result implies that all instructions manipulated (or, did not manipulate) the data in the correct way. If the data is incorrect, the program will hang in a program loop until the machine is halted.

TEST 2 - DOUBLE OPERAND, ALL SOURCE MODES,

### DESTINATION MODE @

This test verifies all double operand general and logical instruction == each in one of the seven modes (excludes mode 0). Thus, two operations are checked the correct decoding of each double operand instruction, and the correct operation of each addressing mode for the source operand.

Each instruction on the test must operate correctly in order for the next instruction to operate. This inter-dependence is carried through to the last instruction (bit test) where, only through the correct execution of all previous instructions is a data field examined for a specific bit configuration. Thus, each instruction prior to the last serves to set up the pointer to the test data.

Two checks on instruction operation are made in TEST 2. One check, a branch on condition, is made following the compare instruction, while the second is made as the last instruction in the test sequence.

Since the GO=NO GO test resides in a ROM memory, all data manipulation (modification) must be performed in destination mode  $\theta$  (register contains data). The data and addressing constants used by TEST 2, are contained within the ROM.

It is important to note that two different types of operations must execute correctly in order for this test to opeate:

- I. Those instructions that paritcipate in computing the final address of the data mask for the final bit test instruction.

- Those instructions that manipulate the test data within the register to generate the expected bit pattern.

Detection of an error within this test results in a program loop,

TEST 3 - JUMP TEST MODES 1, 2, AND 3

The purpose of this test is to ensure correct operation of the Jump instruction. This test is constructed such that only a Jump to the expected instruction will provide the correct pointer for the next instruction.

There are two possible failure modes that can occur in this test:

- The jump addressing circuitry will malfunction causing a transfer of execution to an incorrect instruction sequence or non-existent memory.

- 2. The Jump addressing circuitry will malfunction in such a way as to cause the CPU to loop.

The latter case is a logical error indicator. The former, however, may manifest itself as an after-the fact error. For example, if the Jump causes control to be given to other routines within the M9301, the inter-dependent instruction sequences would probably cause a

failure to eventually occur. In any case, the failing of the Jump instruction will eventually cause an out of sequence or "illogical event" to occur. This in itself is a meaningful indicator of a malfunctioning CPU.

This test contains a JUMP, MODE 2. This instruction is not compatible across the PDP=11 line. However, it will operate on any PDP=11, within this test, due to the unique programming of the instruction within TEST 3. Before illustrating the operation, it is important to understand the difference of the JUMP MODE 2 between machines.

On the PDP=11/20, 11/05, and 11/10 processor, for the Jump Mode 2 (JMP (R)+) the register (R) is incremented by 2 prior to execution of the Jump. On the PDP=11/40 and 11/35. (R) is used as the Jump address and incremented by 2 after execution of the Jump.

In order to avoid this incompatability, the Jump (R)+ is programmed with (R) pointing back on the Jump itself. On 11/20, 11/05, and 11/10 processors, execution of the instruction would cause (R) to be incremented to point to the following instruction, effectively continuing a normal execution sequence.

On the PDP-11/40 and 11/35 processors, the use of the initial value of (R) will cause the Jump to "loop" back on itself. However, correct operation of the auto-increment will move (R) to point to the next instruction following the initial Jump. The Jump will then be executed again. However, the destination address will be the next instruction in sequence.

TEST 4 - SINGLE OPEAND, NON-MODIFYING, BYTE TEST

This test focuses on then one unique single operand instruction, the TST. TST is a special case in the CPU execution flow since it is a non-modifying operation. TEST 4 also tests the byte operation of this instruction. The TSTB instruction will be executed in Mode 1 (register deferred) and Mode 2 (register deferred, auto increment).

The TSTB is programmed to operate on data which has a negative value most significant byte and a zero (not negative) least significant byte.

In order for this test to operate properly, the TSTB on the LSB must, first, be able to access the even addressed LSB, then set the proper condition codes. The TSTB is then re-executed with the auto-increment facility. After the auto-increment, the addressing register should be pointing to the MSB of the test data. Another TSTB is executed on what should be the MSB. The "N" bit of the condition codes should be set by this operation.

Correct execution of the last TSTB implies that the auto-increment recognized that a byte operation was request, thereby only incrementing the address in the register by one, rather than two. If the correct condition code was not set by the associated TSTB instruction, the program will loop.

TEST 5 - DOUBLE-OPERAND, NON-MODIFYING TEST

These are two non-modifying double-operand instructions - the Compare (CMP) and bit test (BIT). These two instructions operate on test data in source modes 1 and 4, and destination modes 2 and 4.

The BIT and CMP instructions will operate on data consisting of all ones (177777), Two separate fields of ones are used in order to utilize the compare instructions, and to provide a field large enough to handle the automincrementing of the addressing register. Since the compare instruction is executed on two fields containing the same data, the expected result is a true "Z" bit, indicating equality.

The BIT instruction will use a mask argument of all ones against another field of all ones. The expected result is a non-zero condition (Z).

Most failures will result in a one instruction loop.

4.3.2.3 Register Display Routine = The register display routine prints out the octal contents of the CPU registers RO, R4, SP and old PC on the console terminal. This sequence will be followed by a prompt character (\$) on the next line.

Example of a typical printout.

XXXXXXX XXXXXX XXXXXX XXXXXX S

Prompt R0 R4 R6 Old PC Program Counter (Stack Pointer)

- 1. Where X signifies an octal number (0-7).

- 2. Whenever there is a power up routine or the BOOT SMITCH is released on PDP11/04 and PDP11/34 machines, the PC at this time will be stored in R5. The contents of R5 are then printed as the OLD PC shown in the example.

The prompting character string indicates that diagnostics have been run and the processor is operating.

4.3.2.3 Memory Modifying CPU Diagnostics

TEST 6 - DOUBLE OPERAND, MODIFYING, BYTE TEST

The objective of this test is to verify that the double-operand, modifying instructions will operate in the byte mode. TEST 6 contains three sub-tests:

- 1. Test source mode 2, destination mode 1, odd and even bytes,

- 2. Test souce mode 3, destination mode 2.

3. Test source mode 0, destination mode 3, even byte.

The move byte (MOVB), bit clear byte (BICB), and bit set byte (BISB) are used within TEST 6 to verify the opeation of the modifying double-operand functions.

Since modifying instructions are under test, memory must be used as a destination for the test data. TEST 6 uses location  $50\%(^9)$  as a destination address. Later, in TEST 7 and the Memory Test, location 500 is used as the first available storage for the stack.

Note that, since TEST 6 is a byte test, location 500(8) implies that both 500(8) and 501 are used for the bytes test (even and odd, respectively. Thus, in the word of data at 500 add and even bytes are caused to be all zeroes and all ones throughout the test. Each byte is modified independently of the other,

### TEST 7 - JSR TEST

The JSR is the first test in the GO=NO GO sequence that utilizes the stack. The Jump Subroutine command (JSR is executed in modes 1 and 6. After the JSR is executed, the subroutine which was given control, will examine the stack to ensure that the correct data was placed in t correct stack location (500(8)). The routine will also ensure that the line back register points to the correct address. Any errors detected in this test will result in a Halt.

## TEST 8 - MEMORY TEST

Although this test is intended to test both core and MOS memories, the data patterns used are designed to exhibit the most taxing operation for MOS. Before the details of the test are described, it would be appropriate to discuss the assumptions placed upon the failure modes of the MOS technology.

This test is intended to check for two types of problems that may arise in the memory.

- 1. Solid Element or Sense Amp failures.

- 2. Addressing Malfunctions external to the chip.

The simplest failure to detect is a solid read or write problem. If a cell fails to hold the appropriate data, it is expected that the Memory Test will easily detect this problem. In addition, the program attempts to saturate a chip in such a way as to cause marginal sense amp operation to manifest itself as a loss or pick-up of unexpected data. The 4K x 1 chip used in the memory consists of a 64 x 64 matrix of MOS storage elements. Each 64 bit section is tied to a common sense amplifier. The objective of the program is to saturate the section with, at first all zeroes and one "1" bit. This "1" bit is then floated through the chip. At the end, the data is complemented, and the test repeated.

For external addressing failures, it is assumed that if two or more

locations are selected at the same time, and a write occurs, it is likely that both locations will assume the correct state. Thus, prior to writing any test data, the background data is checked to ensure that there was no crosstalk between any two locations. All failures will result in a program halt as do failures in tests 6 and 7. After the halt, it is expected that the operator will depress the BOOT switch causing RO (Expected Data), R4 (Received Data), SP (failing Address), and PC (PC indicating memory failure) to be displayed.

# NOTE

If the expected and received data are the same, it is highly probable that an intermittent failure has been detected (i.e., timing or margin problem). The reason the expected and received data can be identical is that the test program re-reads the failing address after the initial non-compare is detected. Thus, a failure at CPU speed is deteted, and indicated by the reading of the failing address on a single reference (not at speed) operation.

4.3,2.4 Bootstrap Programs Supported by the M9301-YA and M9301-YB - Peripheral devices whose bootstraps are supported by the M9301-YA and M9301-YB are listed in TABLE 3 and TABLE 4. Each of these bootstraps is compatible with standard DEC boots and operate as follows.

4.3.2.4.1 RX11 DISKETTE - Loads the first 64 words (200 bytes) of data from track one, sector one into memory location 0 -177 beginning at location 0. Once loaded the contents of location 0 is checked. If it contains 240, operation is transferred to the routine beginning in location 0. If location 0 does not contain 240, the boot is restarted. Restarts will occur 2000 times before the machine is halted automatically.

4,3,2,4,2 TA11 CASSETTE - This bootstrap is identical to that of the RX11 except that data is loaded from the cassette beginning at the second block.

4.3.2.4.3 PC11 PAPER TAPE READER - Loads an Absolute Loader formatted tape into the upper memory locations XXX746 to XXX777 (XXX is dependent on memory size). Once loading is completed, the boot transfers operation to a routine beginning at location XXX752. In systems containing an M9301-YA which is set up not to run diagnostics

TEST 1 thru TEST 5, XXX will become @17 not the upper part of memory.

4.3.2.4.4 = DISKS (excluding RX11) = Load 1000 words (2000 bytes) of data from the disk into memory locations 0-1776.

4,3,2,4.5 MAGTAPE - TM11 - Loads second record (1000 bytes maximum size) from the magtape into memory location 0-777, TJU16 - Load second record (2000 bytes maximum size) from magtape into memory locations 0-1777,

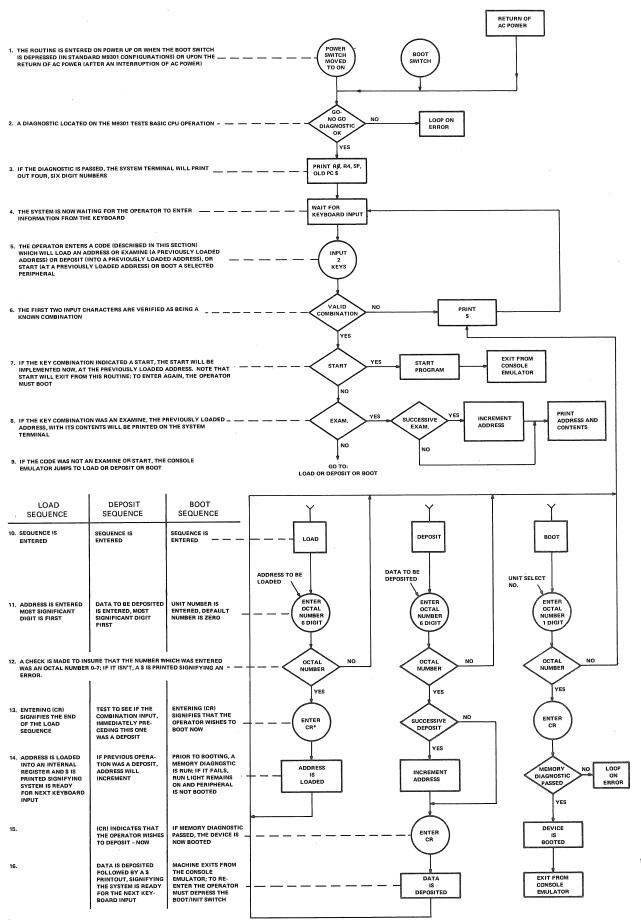

4.3,2.4.6 CONSOLE EMULATOR - when this routine is used in conjunction with the user's terminal, functions quite similar to those found on the programmer's console of traditional PDP11 family computers are generated, as shown in the summary below. The description of the operation that follows assumes that the user's M9301 module is configurated to enter the console emulator routine (DIP switch settings for emulator are shown in TABLE(3) on POWER UP or whenever the BOOT switch is depressed.

### A SUMMARY OF THE CONSOLE EMULATOR FUNCTIONS

- LOAD = This function loads the address to be manipulated into the system

- EXAMINE Allows the operator to examine the contents of the address that was loaded and or deposited.

- DEPOSIT Allows the operator to write into the address that was loaded and/or examined

- START = Initializes the system and starts execution of the program at the address loaded

- BOOT = Allows the booting of a specified device by typing in a two character code and unit number.

# Console Emulator Operation

The console emulator allows the user to perform load, examine, deposit, start, and boot operations by typing in appropriate code on the keyboard. The combination of the console emulator routing and the keyboard will be referred to as "The Console Emulator".

### Introduction

The simplified operator's flow chart of the console emulator routine (which will be referred to as the Operator's Flow Chart) is presented at this point in the text, to give the reader a unified picture of the console emulator routine.

Detailed discussions of each aspect of the chart are presented in Sections in the following paragraphs.

Symbols

Rectangle

Rectangles indicate automatic operations which are performed by the machine. There is only one entrance and one exit on a rectangle.

Diamond

A diamond indicates an automatic operation which can take either of two paths depending on how the question stated within the diamond is answered.

Circle

A circle indicates operator action, and the moving of a switch or the typing of keys.

\*CR = CARRIAGE RETURN KEY

CR

CR is the symbol for the carriage return key.

Using the Console Emulator

After The S =

Once the system has been powered up or booted, and RØ, RA, SP, PC and \$ have been printed, the console emulator routine can be used.

Keyboard Input Symbols

The discussion of keyboard input format uses the following symbols:

Space Bar

: (SB)

Carriage Return Key: (CR)

Any Number 0 - 7

(Octal Number) key : (X)

Keyboard Input Format: Load = Examine deposit start. All character keys shown in the following discussion represent themselves with the exception of those in parenthesis.

| FUNCTION     | KEYBOARD STROKES |      |     |     |     |     |     |     |      |

|--------------|------------------|------|-----|-----|-----|-----|-----|-----|------|

| Load Address | L                | (88) | (X) | (X) | (X) | (X) | (X) | (X) | (CR) |

| Examine      | E (              | (SB) |     |     |     |     |     |     |      |

| Deposit      | D (              | (SB) | (X) | (X) | (X) | (X) | (X) | (X) | (CR) |

| Start        | S                | (SR) |     |     |     |     |     | • . |      |

Order of Significance of Input Keys

The first character that is typed will be the most significant character. Conversely, the last character that is typed is the least significant character.

Leading Zeros

When an address or data word contains leading zeros, these zeros be omitted when loading the address or depositing the data.

Example Using the Load, Examine, Deposit, and Start Functions

Assume that a user wishes to:

- 1. Turn on power

- 2. Load address 700

- 3. Examine location 700

- 4. Deposit 777 into location 700

- 5. Examine location 700

- 6. Start at location 700

|     | USER           | TERMINAL DISPLAY            |

|-----|----------------|-----------------------------|

| 1 . | TURNS ON POWER | XXXXXX XXXXXX XXXXXX XXXXXX |

| 2.  | L(SB) 700 (CR) | \$ L700                     |

| 3,  | E(SB)          | \$ E 000700 XXXXXX          |

| 4.  | D(SB) 777(CR)  | \$ D 777                    |

| 5.  | E(SB)          | \$ E 000700 000777          |

| 6.  | S(CR)          | \$ S                        |

### Even Addresses Only

The console emulator routine will not work with odd addresses. Even numbered addresses must always be used.

Successive Operations

## Examine

Successive examine operations are permitted. The address is loaded for the first examine only. Successive examines cause the address to increment and will display consecutive addresses along with their contents.

Example of Successive Examine Operation

Examine Addresses 500 = 506

| Operator | INPUT | Terminal | DISPLAY  |

|----------|-------|----------|----------|

| L(SB 500 | CR    | L 500    |          |

| F(SB)    |       | SE 00050 | z xxxxxx |

| E(SB) | \$E  | 000502 | XXXXXX |

|-------|------|--------|--------|

| E(SB) | \$ E | 000504 | xxxxxx |

| E(SB) | \$ E | 000506 | ****   |

# Deposit

Successive deposit operations are permitted, The procedure is identical to that used with examine,

Example of Successive Deposit Operations

Deposit 60 into Location 500 2 into Location 502 4 into Location 504

| Operator           | Input | Terminal       | Display |

|--------------------|-------|----------------|---------|

| L(SB 500           | CR    | \$L 500        |         |

| D(SB) 60           | CR    | \$D 60         |         |

| D(SB) 2<br>D(SB) 4 |       | \$0 1<br>\$0 4 |         |

Alternate Deposit - Examine Operations

This mode of operation will not increment the address. The Address will contain the last data which was deposited.

Example of Alternate Deposit - Examine Operations

Load address 500, deposit the following numbers with examines after every deposit 1000, 2000, 5420.

| Operator Input  | Terminal Display  |

|-----------------|-------------------|

| L(SB) 500 (CR)  | \$L 500           |

| D(SB) 1000 (CR) | \$D L000          |

| E(SB)           | SE 000500 001000  |

| D(SB) 2000 (CR) | SD 2000           |

| E(SB)           | \$E 000500 002000 |

| D(SB) 5420 (CR) | \$D 5420          |

| E(SB)           | \$E 000500 005420 |

Alternate Examine - Deposit Operations

If an examine is the first instruction after a load sequence, and is alternately followed by deposits and examines, the address will not be incremented, and the address will contain the last data which was deposited. (The above example applies to this operation, with the exception of the order of examine and deposit, the end result is the same).

## Limits of Operation

The M9301 console emulator routine can directly manipulate the lower 28K of memory and the 4K I/O page. See section 5, for an explanation of techniques required to access addresses above the lower  $28\text{K}_{\odot}$

Booting From The Keyboard

Once the \$ symbol has been displayed in response to system power coming up, or the boot switch being depressed, the system is ready to load a bootstrap from the device which the operator selects.

Console Emulator Boot Procedures

- 1. Find the two character boot command code on either Table 3 or Table 4, that corresponds to the peripheral to be booted.

- Load papertape, magtape, disc, etc. into the peripheral to be booted if required.

- 3. Verify that the peripheral indicators signify that the peripheral is ready (if applicable).

- 4. Type two character code obtained from the table.

- 5. If there is more than one unit of a given peripheral, type the unit number to be booted (0 7) if no number is typed, the default number will be 0.

- 6. Type (CR), this initiates the boot,

Before Booting ...

### Always Remember:

- The medium (Paper tape, disc, magtape, cassette, etc.) must be placed in the peripheral to be booted prior to booting,

- 2. The machine will not be under the control of the console emulator routine after booting.

- 3. The program which is booted in must:

- 1) be self starting or 2) allow the user to load another program by using the CONT function or 3) be prestartable after the console emulator is recalled.

- 3. Actuating the boot switch will always abort the program being run. The contents of the general registers (RØ=R7) will be destroyed. There is no way to continue with the program which was aborted. Some program are designed to be restartable.

Example: Booting the High Speed Reader Using The

### Console Emulator

An operator wishes to load the CPU Diagnostic for an 11/39 computer system. The system has a high speed reader,

Procedure:

- 1. Place the HALT/CONT switch in the CONT position.

- 2. Obtain a Sby:

- a. Turning on system power

- b. Actuating the boot.

(R0, R4, SP, and PC will be printed prior to the \$a)

- 3. Place the absolute loader paper tape (coded leader section) in the high speed reader,

- 4. Type: PR (CR)

The absolute loader tape will be loaded, and the machine will halt.

- 5. Remove the absolute loader and place the leader of the program, in this case a CPU Diagnostic, in the reader.

- 6. Move the HALT/CONT switch to HALT and then return it to CONT. The diagnostic will be loaded and the machine will halt (normal for this programming, non-diagnostic programs could be self starting).

- 7. If program is not self starting activate the 800T/INIT switch, this will restart the console emulator routine.

- 8. Using the console emulator, deposit desired functions into the Software Switch Register (a memory address) location. See the diagnostic for the software switch register's actual location and significance.)

9. Using the console emulator, load the starting address, and start the program as described earlier in this section.

Example of Booting A Disc Using the Console Emulator

A user wishes to boot the system's RK11 Disk, which contains the CPU Diagnostic which the user wants to run.

### Procedure:

- 1. Verify the the HALT/CONT switch is in the CONT position and the write lock switch on the RK11 peripheral is in the ON position.

- 2. The user turns on system power. The system terminal displays RØ, R4, SP and PC which are random binary numbers. Followed by a \$ on the next line.

- 3. The user placed the disk pack into drive zero.

- 4. When the RK05 load light appears, the system is ready to be booted.

- 5. The user type in: DK (CR)

This causes the loading of the bootstrap routine into memory and the execution of that routine.

6. The program should identify itself and initiate a dialogue (which won't be discussed here).

# CONSOLE EMULATOR

The following discussion will describe the effects of entering information incorrectly to the console emulator routine.

### Symbols

Space Bar = (SB)

Carriage Return Key = (CR)

Any Octal Number (0 - 7) Key (X)

Non=Octal Number (8 or 9) keys (9)

#### (Y) - Represents:

1. All Keys (other than numerics which are unknown,

2. Keys which are known but do not consitute a valid code in the context which they are entered.

Refer to previous sections for a discussion of the correct method operating the console emulator routine.

# ESCAPE ROUTE

If an entry has not been completed and the user realizes that an incorrect or unwanted character has been entered, depress the rub out or delete key. This action will void the entire entry and allow the user to try again.

| PLES            | TERMINAL | <b>ப</b><br>செச                                                              | ×<br>×<br>×<br>×<br>×<br>×<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ×<br>×<br>×<br>×<br>я                                                                              | XXX<br>0<br>18                                                                                                         |                    |                 |                                                   | & & & & & & & & & & & & & & & & & & &                                                                       | L 1XXXXX                                                                                      | &L XXXXX<br>&XXX (CP)                                                 | ങ II ക ര<br>റ<br>റ                                                    |

|-----------------|----------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

| USEFUL EXAMPLES | OPERATOR | ۲(۲)                                                                         | L(SB) XXX9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | L(SB) XXXX                                                                                         | S(SB) 6XXXXXX                                                                                                          |                    |                 |                                                   | L(SB) 1XXXXX                                                                                                | L(SB) 1XXXX<br>(CR)                                                                           | L(SB) XXXXX<br>(CR)                                                   | S(X) or                                                               |

|                 | REMEDY   | ° C C C C C C C C C C C C C C C C C C C                                      | . C ↑ B Q G → C ↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ۵ - الم                                                                                            | >                                                                                                                      |                    |                 | Try again,                                        | e<br>- e<br>- o<br>- o<br>- o<br>- o<br>- o<br>- o<br>- o<br>- o<br>- o<br>- o                              | > > = = = = = = = = = = = = = = = = = =                                                       | Type (CR)                                                             | ° C + 000 c > 1.                                                      |

| DEPOSIT ERROR   | RESULT   | Terminal display will the signify return a strong ode, No address is loaded. | COURT | 00 a a a a a a a a a a a a a a a a a a                                                             | An address will be loaded, however, the state of the most sign nificant address bit will be determined by bit 15 only: | 2 1 0 3 1 1 4 11 0 | 5 = 16 = 07 = 1 | Address will be loaded,<br>but unchanged,         | The loaded number will be incorrect. The sysil tem will accept any will accept any six characters typed in. | No errors will result<br>unless a deposit, ex-<br>autempted.                                  | Machine will wait indefinitely for (CR) 8 will not be returned.       | Terminal display will immediately return a 8 to cignify an unknown co |

|                 | ERROR    | L was followed by a key other<br>than (SB)                                   | An filegel (non octel) number (8 or 9) is typed after the correct load entrance, within an otherwise velid number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | An incorrect albha key is extend after the correct load entrance within an otherwise valid aumber. | The most significant octal number in a six bit address is greater than one.                                            |                    |                 | An unwanted byte legal octal<br>number is loaded, | An extra (seventh) octal<br>number is typed <sub>e</sub>                                                    | A memory location higher than the highest memory location available in the machine is loaded. | Load entrance and number were entered correctly, (CR) wasn't entered. | E or S is followed by a key other than space.                         |

| (B % (B % )                                                                                                                          |                                                                                                                                                 |                                                                  | S &                                                                       |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------|

| Debress the E(Sboot switch, S(S                                                                                                      |                                                                                                                                                 | Reload program<br>and try again,                                 | Try again, D)Y)                                                           | Activate the boot switch to reboot the system.                                                                                                            | der consider to content to conten | b, Reboot machine.                             | Depress the boot switch.                          |