EK-OKL10-TM-002

# KL10-Based Technical Manual

# KL10-Based Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, August 1983 2nd Edition, July 1984

© Digital Equipment Corporation 1983, 1984

All Rights Reserved.

Printed in U.S.A.

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital      | MASSBUS      | TOPS-20        |

|--------------|--------------|----------------|

| DEC          | PDP          | UNIBUS         |

| DECmate      | P/OS         | VAX            |

| DECsystem-10 | Professional | VMS            |

| DECSYSTEM-20 | Rainbow      | VT             |

| DECUS        | RSTS         | Work Processor |

| DECwriter    | RSX          |                |

| DIBOL        | TOPS-10      |                |

# CONTENTS

## CHAPTER 1 INTRODUCTION

| 1.1     | DECsystem-10/DECSYSTEM-20 TECHNICAL INTRODUCTION | 1-1 |

|---------|--------------------------------------------------|-----|

|         | Purpose and Use                                  | 1_1 |

| 1.1.2   | General Description                              | 1-7 |

| 1.1.3   | Related Documents                                |     |

| 1.1.3.1 | Hardware Documentation                           |     |

| 1.1.3.2 | Software Documentation                           |     |

| 1.2     | DECsystem-10/DECSYSTEM-20 SITE PREPARATION AND   |     |

|         | PLANNING                                         | 1-6 |

| 1.2.1   | DECsystem-10/DECSYSTEM-20 Installation           | 1-6 |

| 1.2.2   | DECsystem-10/DECSYSTEM-20 Operation/Programming  |     |

| 1.2.3   | DECsystem-10/DECSYSTEM-20 Service                | 1-6 |

| 1.2.4   | DECsystem-10/DECSYSTEM-20 Engineering            |     |

|         | Drawing Sets                                     |     |

# CHAPTER 2 SYSTEM FEATURES

٠

| 2.1    | INTRODUCTION                          | 2-1 |

|--------|---------------------------------------|-----|

| 2.2    | INSTRUCTION SET                       | 2-1 |

| 2.2.1  | Full-Word Data Transmission           | 2-3 |

| 2.2.2  | Half-Word Data Transmission           | 2-4 |

| 2.2.3  | Block-Transfer Instruction            | 2-4 |

| 2.2.4  | Byte Manipulation                     | 2-4 |

| 2.2.5  | Business Instruction Set              | 2-4 |

| 2.2.6  | Logic Instructions                    | 2-4 |

| 2.2.7  | Fixed-Point Arithmetic                | 2-4 |

| 2.2.8  | Floating-Point Arithmetic             | 2-4 |

| 2.2.9  | Arithmetic Operation Modes            | 2-5 |

| 2.2.10 | Fixed/Floating Conversions            | 2-5 |

| 2.2.11 | Compare and Modify                    | 2-5 |

| 2.2.12 | Program Control                       | 2-5 |

| 2.2.13 | Input/Output                          | 2-5 |

| 2.2.14 | Unimplemented User Operations (UUOs)  | 2-5 |

| 2.2.15 | Trap Handling                         | 2-5 |

| 2.3    | INSTRUCTION FORMAT                    | 2-6 |

| 2.4    | NUMBER SYSTEM                         | 2-6 |

| 2.4.1  | Fixed-Point Arithmetic Conventions    | 2-6 |

| 2.4.2  | Floating-Point Arithmetic Conventions | 2-7 |

| 2.5    | EFFECTIVE ADDRESS CALCULATION         | 2-7 |

| 2.6    | GENERAL-PURPOSE REGISTER BLOCKS       | 2-7 |

| 2.7    | MEMORY SYSTEM                         | 2-8 |

| 2.7.1  | MOS Memory                            | 2-8 |

| 2.7.2  | DMA                                   | 2-8 |

| 2.7.3  | Cache Memory                          | 2-8 |

| 2.8    | PROCESSOR MODES                       | 2-8 |

| 2.9    | PROCESS TABLES                        | 2-9 |

| 2.10   | MEMORY ADDRESS MAPPING                | 2-9 |

| 2.11   | DIRECT I/O2                           | -11 |

# Page

| 2.12      | CHANNEL I/O                                  |  |

|-----------|----------------------------------------------|--|

| 2.12.1    | CHANNEL I/O<br>Integrated Massbus Controller |  |

| 2.12.2    | Integrated Channels                          |  |

| 2.13      | PRIORITY INTERRUPT SYSTEM                    |  |

| 2.14      | TRAP FACILITY                                |  |

| 2.15      | ACCOUNTING AND PERFORMANCE METERS            |  |

| 2.16      | FRONT-END PROCESSOR                          |  |

| 2.16.1    | Functions                                    |  |

| 2.16.2    | Components                                   |  |

| 2.16.2.1  | DTE20                                        |  |

| 2.16.2.2  | Console                                      |  |

| 2.16.2.3  | PDP-11                                       |  |

| CHAPTER 3 | THE HARDWARE                                 |  |

| 3.1       | INTRODUCTION                                 |  |

| 3.2       | THE MAIN PROCESSOR SUBSYSTEM                 |  |

| 3.2      | THE MAIN PROCESSOR SUBSYSTEM 3-1      |

|----------|---------------------------------------|

| 3.2.1    | The EBox                              |

| 3.2.1.1  | Hardware                              |

| 3.2.1.2  | Firmware                              |

| 3.2.2    | The MBox                              |

| 3.2.3    | Channel/Cache Interface Description   |

| 3.2.3.1  | Request Dialog                        |

| 3.2.3.2  | Channel Read Operations               |

| 3.2.3.3  | Channel Write Operations              |

| 3.2.4    | Meter Board                           |

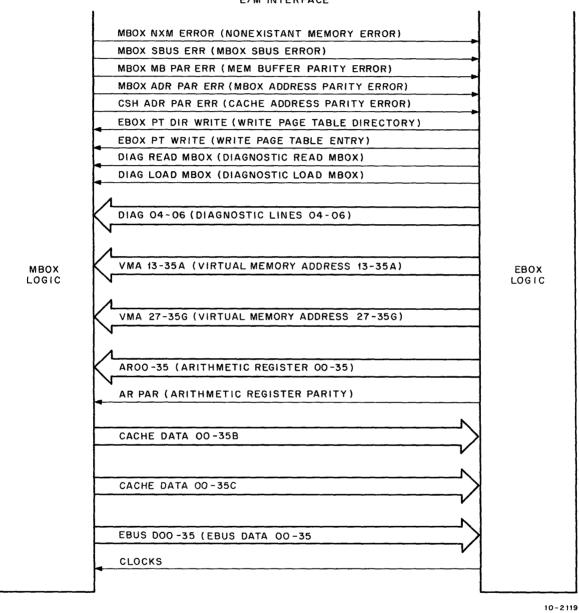

| 3.2.5    | EBox/MBox (E/M) Interface Description |

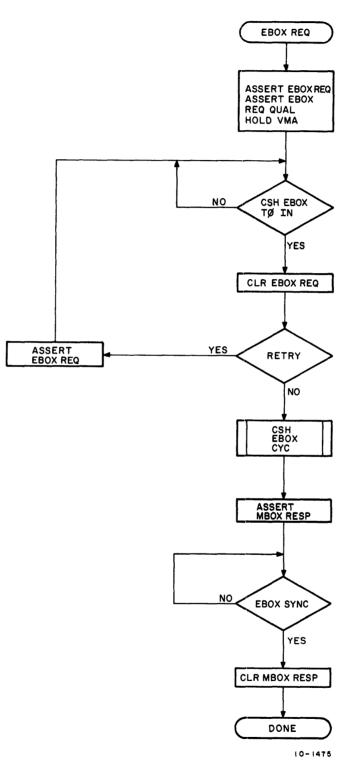

| 3.2.5.1  | Basic Request Dialog                  |

| 3.2.5.2  | Register References                   |

| 3.2.5.3  | Memory Reference                      |

| 3.2.5.4  | Basic Cache Strategy 3-27             |

| 3.2.6    | XBus Description                      |

| 3.2.6.1  | Read Dialog                           |

| 3.2.6.2  | Write Dialog                          |

| 3.2.6.3  | Read-Pause-Write Dialog               |

| 3.2.6.4  | Diagnostic Cycle Dialog               |

| 3.2.6.5  | Diagnostic Function Descriptions      |

| 3.2.7    | The Storage Bus                       |

| 3.2.8    | The EBus                              |

| 3.2.8.1  | CONO/DATAO Operation                  |

| 3.2.8.2  | CONI/DATAI Operation                  |

| 3.2.8.3  | Interrupt Operation                   |

| 3.2.8.4  | Diagnostic Bus                        |

| 3.2.9    | Channel Bus Description               |

| 3.2.9.1  | Controller Selection                  |

| 3.2.9.2  | Transfer Cycle Definitions            |

| 3.2.10   | DTE20                                 |

| 3.2.10.1 | UNIBUS Description                    |

| 3.2.11   | RH20                                  |

.

## Page

| 3.2.11.1 | MASSOUS Description                                  | 2 7 2 |

|----------|------------------------------------------------------|-------|

| 3.2.12   | MASSBUS Description                                  |       |

| 3.2.12   | Interrupt Facility                                   |       |

| 3.2.13   | Trap Facility                                        |       |

| 3.2.14   | Internal Devices                                     |       |

|          | APR                                                  |       |

| 3.2.14.2 | PI                                                   |       |

| 3.2.14.3 | PAG                                                  |       |

| 3.2.14.4 | CCA.                                                 |       |

| 3.2.14.5 | TIM and MTR                                          | 3-79  |

| 3.2.15   | External and Internal I/O Controllers and            |       |

|          | Devices (Typical)                                    | 3-79  |

| 3.3      | FRONT-END PROCESSOR SUBSYSTEM                        |       |

| 3.3.1    | Devices                                              |       |

| 3.3.1.1  | KD11-A Central Processor                             | 3-80  |

| 3.3.1.2  | KY11-D Programmers Console                           | 3-80  |

| 3.3.1.3  | KW11-L Line Clock Option                             | 3-81  |

| 3.3.1.4  | MF11-UP Memory                                       | 3-81  |

| 3.3.1.5  | MM11-UP Memory                                       | 3-81  |

| 3.3.1.6  | BM873-YJ ROM Loader Module                           | 3-81  |

| 3.3.1.7  | DL11-C Asynchronous Line Interface                   | 3-81  |

| 3.3.1.8  | DL11-E Asynchronous Line Interface                   | 3-81  |

| 3.3.1.9  | LA120 Keyboard Terminal                              | 3-81  |

| 3.3.1.10 | DC20F Asynchronous 16-Line Multiplexer               |       |

| 3.3.1.11 | CD20 Card Readers                                    |       |

| 3.3.1.12 | LP26 Line Printer                                    |       |

| 3.3.1.13 | RP06 Disk File System                                |       |

| 3.3.1.14 | RX11 Floppy Disk Subsystem                           |       |

| 3.3.1.15 | BC11-A Unibus                                        | 3-84  |

| 3.3.2    | Interdevice Transfers                                |       |

| 3.3.3    | Functions                                            |       |

| 3.3.3.1  | Examine/Deposit Operations                           |       |

| 3.3.3.2  | TO10/TO11 Byte Transfer Operations                   | 3_85  |

| 3.3.3.3  | System Bootstrap Function                            |       |

| 3.3.3.4  | Interprocessor Interrupts                            |       |

| 3.3.3.5  | Diagnostic and Miscellaneous Console Functions       |       |

| 3.3.4    | Modes                                                |       |

| 3.3.5    | Interprocessor Communication                         |       |

| 3.3.5.1  | Communication Areas                                  |       |

| 3.3.5.2  |                                                      |       |

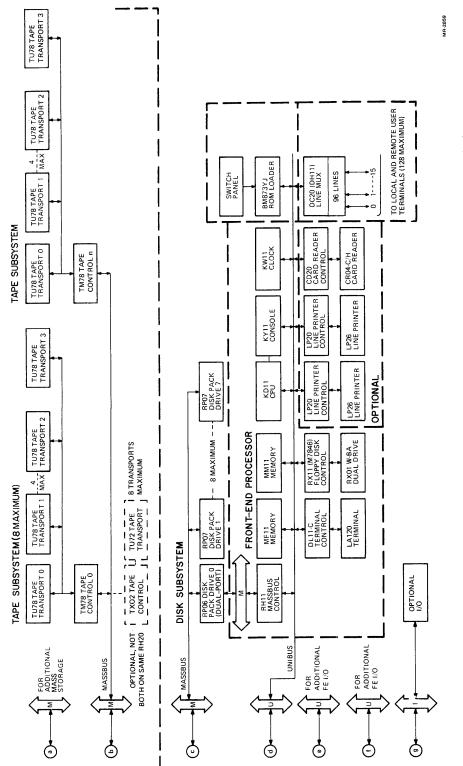

| 3.4      | Queue Processing/Messages<br>MASS STORAGE SUBSYSTEMS |       |

| 3.4.1    |                                                      |       |

| 3.4.1.1  | TX02 Tape Control Unit                               |       |

| 3.4.1.2  | Nine-Track NRZI                                      |       |

| 3.4.1.3  | Seven-Track NRZI                                     |       |

| 3.4.1.3  | Two-Channel Switch – TX03                            |       |

| 3.4.1.4  | $2 \times 8$ Tape Switch – TX05                      |       |

|          | TU72 Tape Units                                      |       |

| 3.4.2.1  | Self-Loading                                         |       |

| 3.4.2.2  | Automatic Reel Hub                                   |       |

| 3.4.2.3  | Capstan                                              | 3-91  |

# Page

| 3.4.2.4 | Dynamic Amplitude Control   |  |

|---------|-----------------------------|--|

| 3.4.2.5 | Backside Tape Cleaner       |  |

| 3.4.2.6 | Tape Storage Pocket         |  |

| 3.4.2.7 | Power Window                |  |

| 3.4.2.8 | Data Density Option         |  |

| 3.4.3   | TU77 Magnetic Tape          |  |

| 3.4.4   | TU78 Magnetic Tape          |  |

| 3.4.5   | RP06 Disk Pack Drive        |  |

| 3.4.6   | RP07 Disk Drive             |  |

| 3.4.7   | RP20 Disk Subsystem         |  |

| 3.4.8   | DX20 MASSBUS-To-IBM Adapter |  |

| 5.1.0   |                             |  |

# CHAPTER 4 THE SOFTWARE

| 4.1     | INTRODUCTION                                | . 4-1 |

|---------|---------------------------------------------|-------|

| 4.2     | TOPS-10/20 OPERATING SYSTEM                 | . 4-1 |

| 4.2.1   | The File System                             | . 4-2 |

| 4.2.1.1 | Files                                       | . 4-2 |

| 4.2.1.2 | PNNs                                        |       |

| 4.2.1.3 | Directory Files for TOPS-10                 |       |

| 4.2.1.4 | Directories for TOPS-20                     |       |

| 4.2.1.5 | Groups on TOPS-20                           | . 4-3 |

| 4.2.1.6 | File Usage                                  | . 4-4 |

| 4.2.2   | The Command Processor                       | . 4-4 |

| 4.2.2.1 | Timesharing                                 | . 4-5 |

| 4.2.2.2 | Batch                                       | . 4-6 |

| 4.2.3   | The Monitor                                 |       |

| 4.2.3.1 | Resident                                    | . 4-7 |

| 4.2.3.2 | Nonresident                                 | . 4-8 |

| 4.2.3.3 | Communication with the Monitor for TOPS-20  |       |

| 4.2.4   | The Front-End Software (RSX20-F)            |       |

| 4.2.4.1 | Introduction                                |       |

| 4.2.4.2 | Console Processor                           |       |

| 4.2.4.3 | Communication Processor                     | . 4-9 |

| 4.2.4.4 | Peripheral Processor                        | . 4-9 |

| 4.2.4.5 | Diagnostic/Maintenance Processor            | . 4-9 |

| 4.2.5   | The System Reporting and Control Facilities | . 4-9 |

| 4.2.5.1 | Accounting                                  | 4-10  |

| 4.2.5.2 | System Control                              | 4-10  |

| 4.2.5.3 | System Generation                           | 4-10  |

| 4.2.5.4 | Error Reporting                             | 4-10  |

| 4.2.5.5 | Backup Facilities                           | 4-10  |

| 4.3     | THE PROCESS                                 | 4-11  |

| 4.3.1   | Structure                                   |       |

| 4.3.2   | Interprocess Communication Facility (IPCF)  |       |

| 4.3.3   | Enqueue/Dequeue (ENQ/DEQ)                   |       |

| 4.3.4   | Software Interrupt System                   |       |

| 4.3.5   | Virtual Memory                              | 4-13  |

#### Page

| 4.3.5.1  | Working Set                           |  |

|----------|---------------------------------------|--|

| 4.3.5.2  | Balance Set                           |  |

| 4.4      | LANGUAGES AND UTILITIES               |  |

| 4.4.1    | ALGOL                                 |  |

| 4.4.2    | APL                                   |  |

| 4.4.3    | BASIC                                 |  |

| 4.4.4    | COBOL                                 |  |

| 4.4.4.1  | Features                              |  |

| 4.4.4.2  | Indexed Sequential Access Mode (ISAM) |  |

| 4.4.5    | EDIT                                  |  |

| 4.4.6    | MACRO                                 |  |

| 4.4.7    | DDT                                   |  |

| 4.4.8    | Dumper/Backup                         |  |

| 4.4.9    | FORTRAN                               |  |

| 4.4.10   | Data Base Management System           |  |

| 4.4.10.1 | Introduction                          |  |

| 4.4.10.2 | DBMS Features                         |  |

| 4.4.11   | LINK                                  |  |

| 4.4.12   | RUNOFF                                |  |

| 4.4.13   | SORT                                  |  |

|          |                                       |  |

Appendix A MCA25 KL Cache/Paging Upgrade

## TABLES

#### Table No.

#### 3-1 3-2 3-3 3-4 3-5 Diagnostic Function 1...... 3-36 3-6 3-7 3-8 3-9 3-10 3-11 3-12 3-13 3-14 3-15 3-16 3-17 3-18 3-19 3-20 3-21

#### **Title Page**

# **FIGURES**

| Figure No. | · ·                                             | Title Page |

|------------|-------------------------------------------------|------------|

| 1-1        | DECsystem-10/DECSYSTEM-20 Configuration         |            |

|            | DECsystem-10/DECSYSTEM-20 Typical Block Diagram |            |

|            | Instruction Set Constructs                      |            |

| 2-2        | Move Instruction Construct                      |            |

| 2-3        | Instruction Format                              |            |

| 2-4        | User Process Table                              |            |

| 2-5        | Exec Process Table                              |            |

| 3-1        | DECsystem-10/DECSYSTEM-20 Typical Block Diagram |            |

|            | Microprogram Structure                          |            |

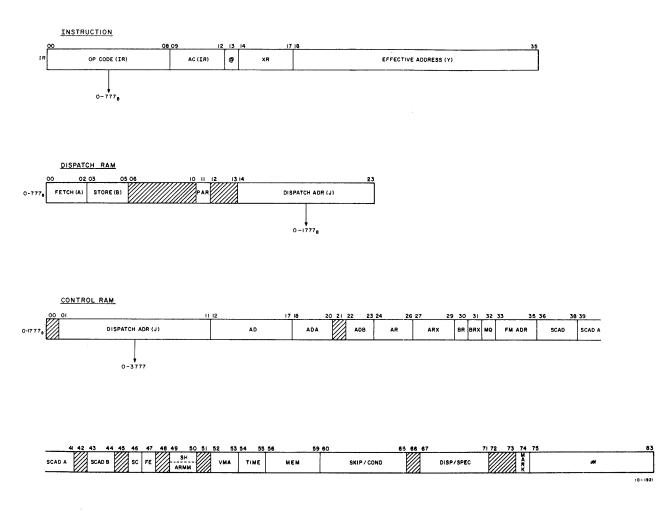

| 3-3        | Instruction Dispatch and Control Formats        |            |

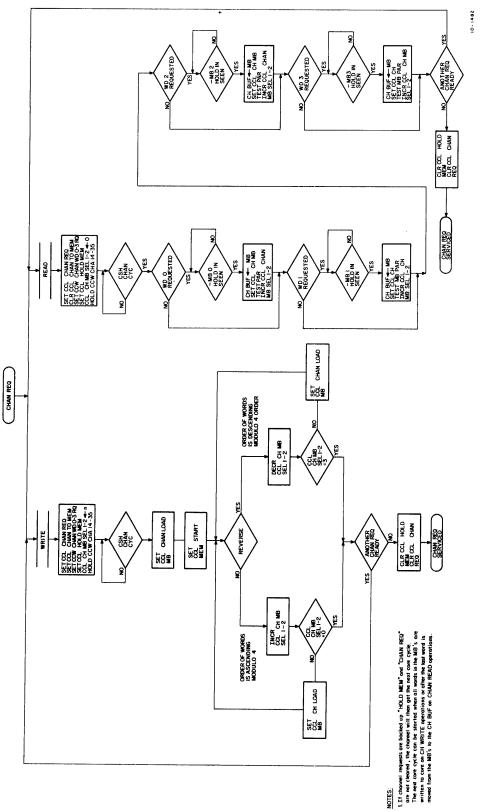

| 3-4        | CHAN/CSH Configuration                          |            |

| 3-5        | Channel Request Dialog                          |            |

| 3-6        | E/M Interface Configuration                     |            |

| 3-7        | EBox Request Dialog                             | 3-26       |

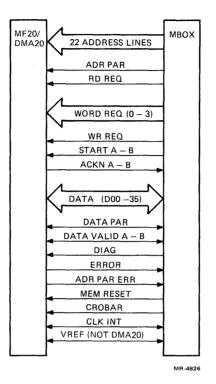

| 3-8        | XBus Signals                                    |            |

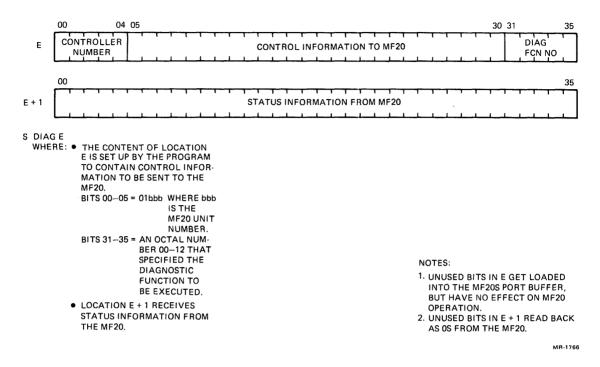

| 3-9        | Diagnostic Function Format                      | 3-34       |

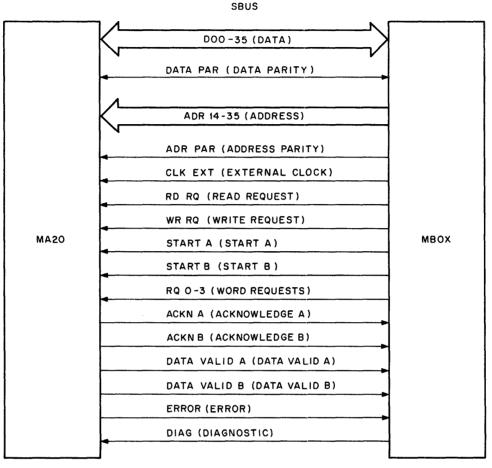

| 3-10       | SBus Configuration                              |            |

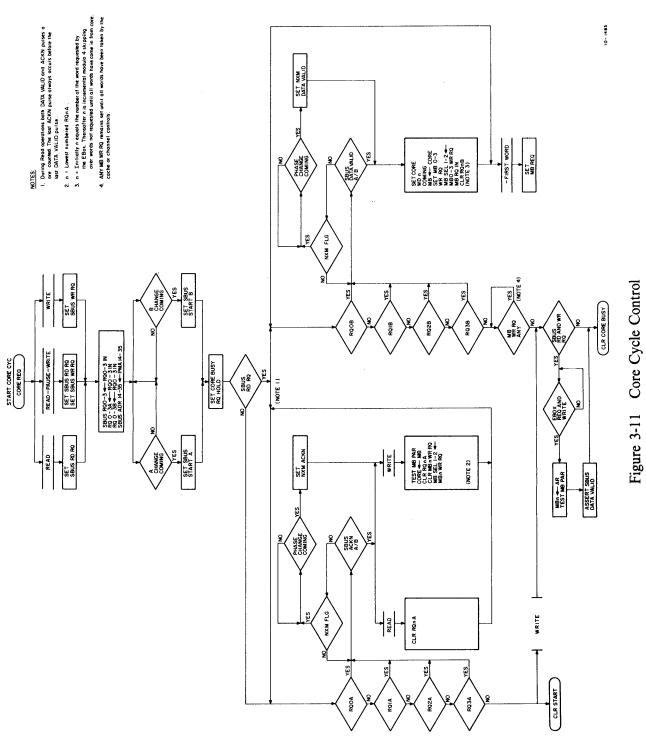

| 3-11       | Core Cycle Control                              |            |

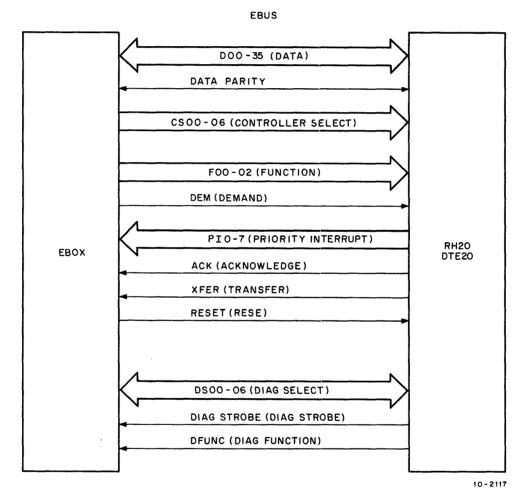

| 3-12       | EBus Configuration                              |            |

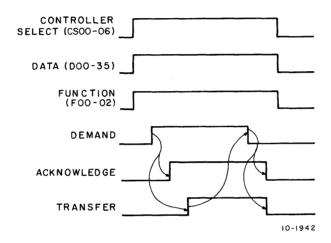

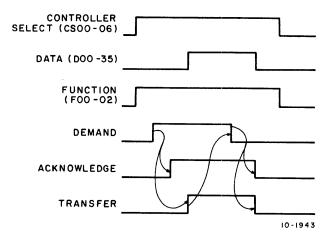

| 3-13       | CONO/DATAO Operation Sequence                   |            |

| 3-14       | CONI/DATAI Operation Sequence                   |            |

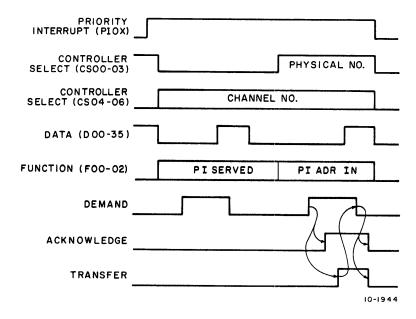

| 3-15       | Priority Interrupt Operation Sequence           | 3-54       |

| 3-16       | CBus Configuration                              |            |

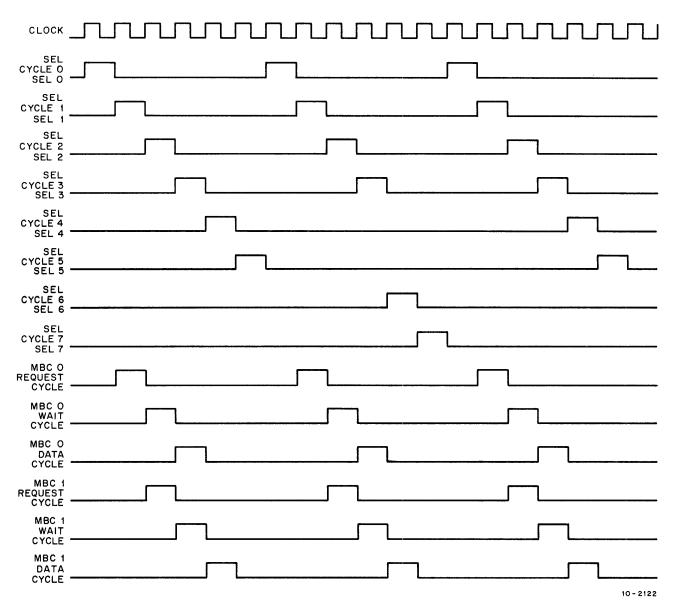

| 3-17       | Basic RH20 Selection Timing                     | 3-60       |

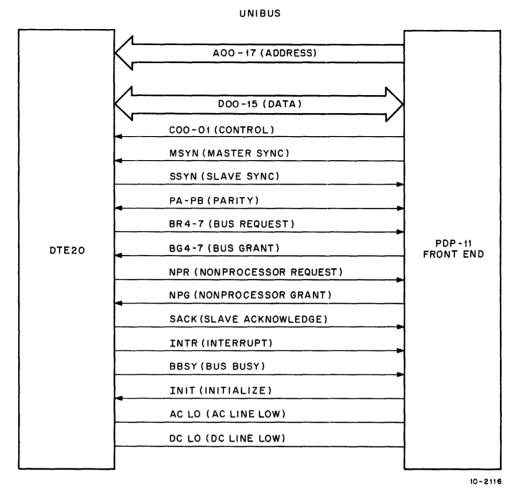

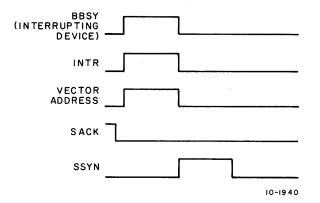

| 3-18       | Unibus Configuration                            |            |

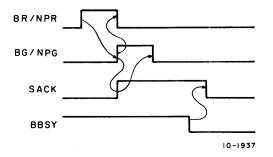

| 3-19       | Priority Transfer Sequence                      |            |

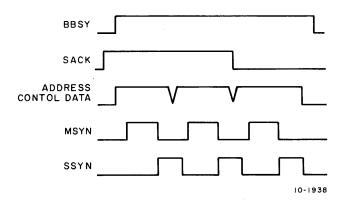

| 3-20       | Multiple Data Transfer Sequence                 |            |

| 3-21       | DATI Bus Sequence                               |            |

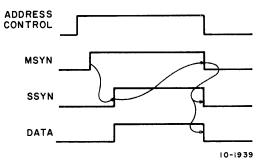

| 3-22       | Interrupt Sequence                              | 3-69       |

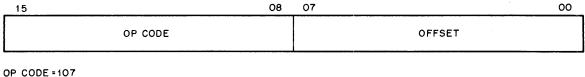

| 3-23       | EMT Instruction Format                          |            |

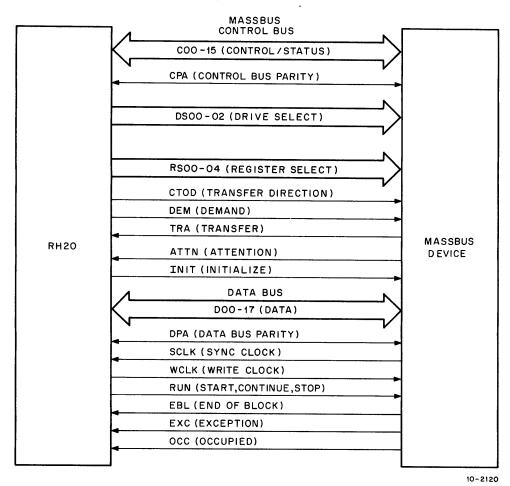

| 3-24       | Massbus Configuration                           |            |

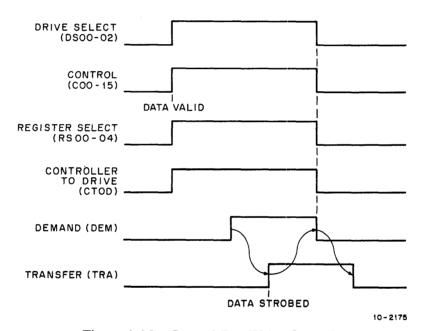

| 3-25       | Control Bus Write Operation                     |            |

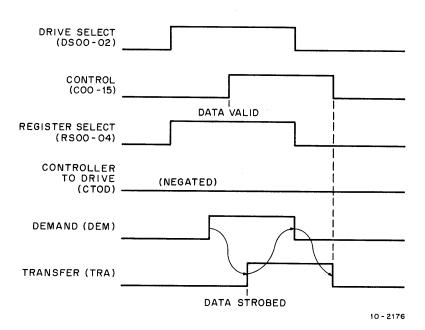

| 3-26       | Control Bus Read Operation                      |            |

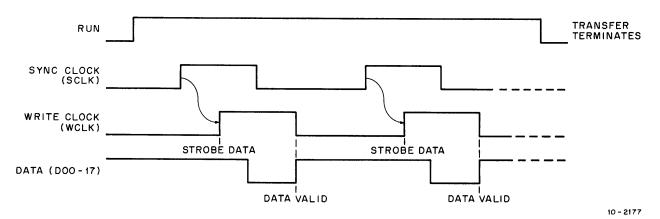

| 3-27       | Data Bus Write Operation                        |            |

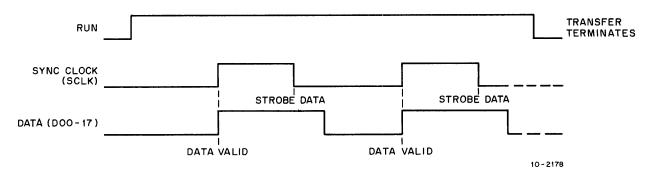

| 3-28       | Data Bus Read Operation                         |            |

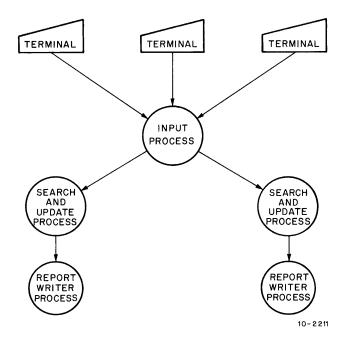

| 4-1        | Parallel and Inferior Processes                 |            |

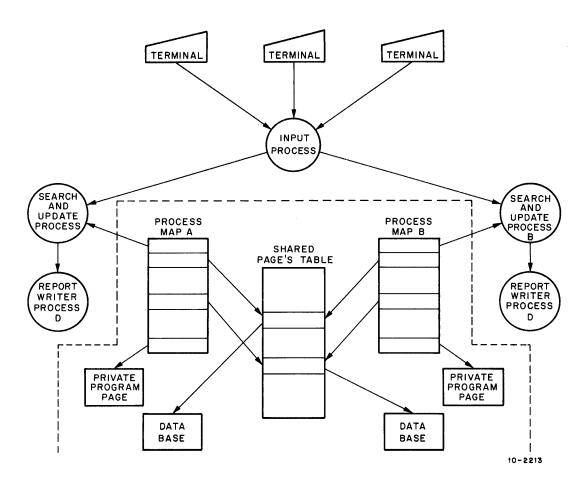

| 4-2        | Process Mapping                                 |            |

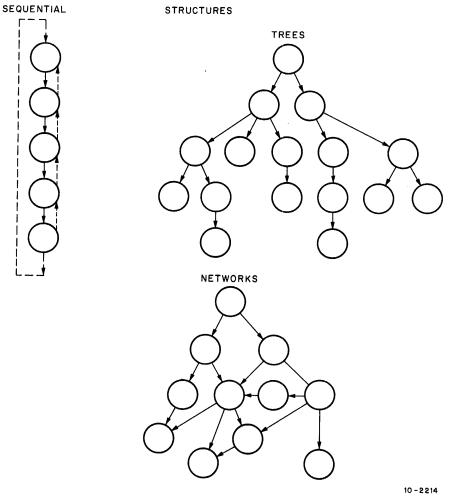

| 4-3        | Basic Data Structures                           |            |

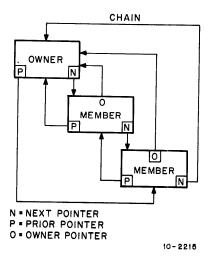

| 4-4        | Chaining of Data Records                        |            |

# PREFACE

This manual contains the system-level technical description of the DECsystem-10/DECSYSTEM-20 computer, the KL10-R-based machine. The manual provides an integrated hardware/software system display with appropriate overviews of timesharing/batch operation and system features. The chapters of this system-level description are as follows.

- 1. Introduction

- 2. System Features

- 3. The Hardware

- 4. The Software

· · ·

.

# CHAPTER 1 INTRODUCTION

#### 1.1 DECsystem-10/DECSYSTEM-20 TECHNICAL INTRODUCTION

#### **1.1.1** Purpose and Use

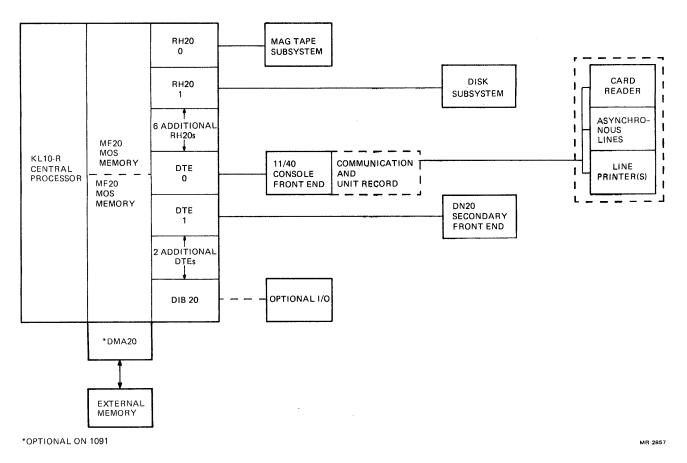

The KL10-R is a version of the present KL-based DECsystem-10/DECSYSTEM-20 system. It offers a complete system with large capacity memories and increased disk, tape, and user capability. The software, which supports extended addressing, provides service for 40 to 80 users. Ongoing support and development for current customers protect their investment in TOPS-20 and application software already developed. Figure 1-1 shows a typical DECsystem-10/DECSYSTEM-20 configuration.

#### Figure 1-1 DECsystem-10/DECSYSTEM-20 Configuration

#### **1.1.2 General Description**

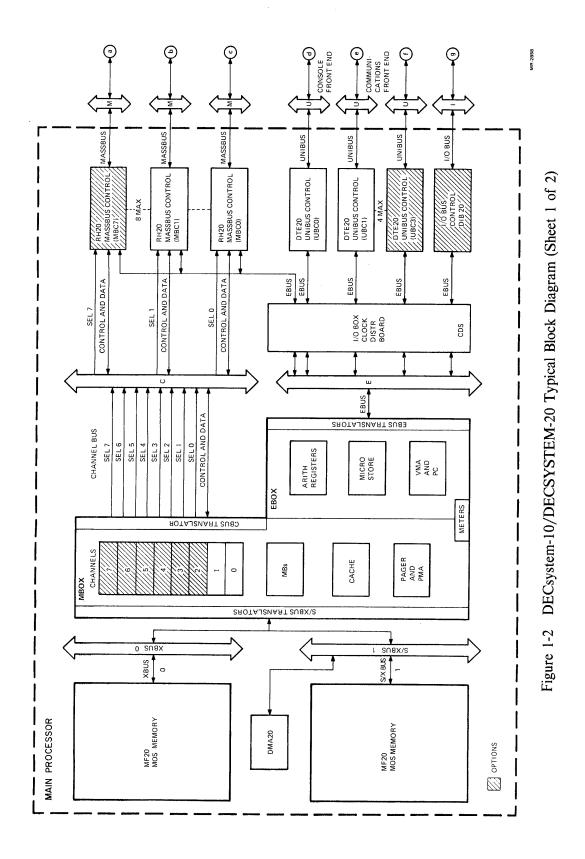

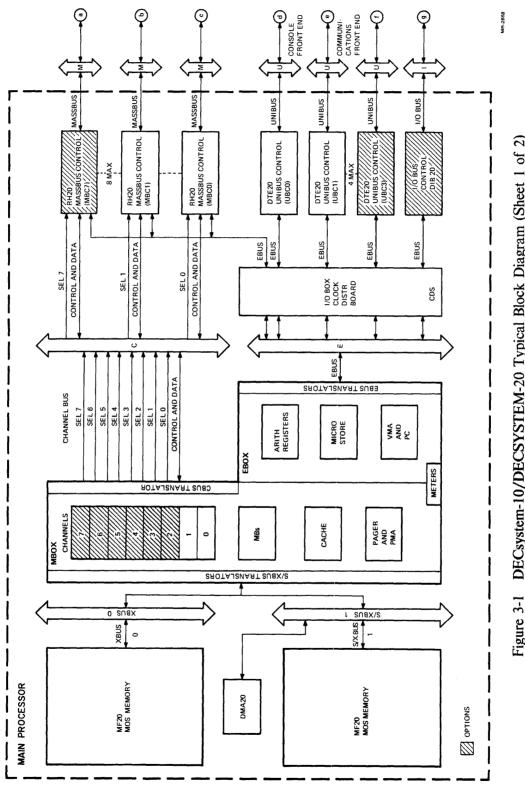

The DECsystem-10/DECSYSTEM-20 is a large-scale, high-performance system (DECsystem-10/DEC-SYSTEM-20 family) using a KL10-R central processing unit (see Figure 1-2). It contains at least 512 K words of memory, TOPS-20 extended features, and both hardware and software support for MOS memory.

The following features are included within the mainframe.

- Microprogrammed KL10-R CPU

- Minimum memory size of 512 K words MOS (except 1091)

- Internal data channels

- Internal Massbus controllers

- Integral PDP-11/40 front-end processor (supports asynchronous communication and unitrecord equipment)

- Optional secondary front-end communications

#### **1.1.3 Related Documents**

**1.1.3.1 Hardware Documentation** – The following documents are available only on microfiche except where identified. Hard copy documents can be ordered from:

Digital Equipment Corporation 444 Whitney Street Northboro, Massachusetts 01532 Attention: Printing and Circulating Services (NR2/M15) Customer Services Section

| Title                                                                                   | <b>Document</b> Number |

|-----------------------------------------------------------------------------------------|------------------------|

| AN10/AN20 ARPANET Interface Technical Manual                                            | EK-AN1/2-TM            |

| CD20 Maintenance Manual                                                                 | ED-CD11-TM             |

| DECsystem-10/DECSYSTEM-20 Front End<br>(Console Channel Interface Description)          | EK-FE-ID               |

| DIA20 IBus Adapter Unit Description                                                     | EK-DIA20-TM            |

| DTE20 Unit Description*                                                                 | EK-DTE20-UD            |

| DN200 Remote Batch Station, Terminal Concentrator<br>(DECSYSTEM-10, -20) Remote Station | EK-DN200-TM            |

| DX20/DX20F Programmed Device Adapter Technical Manual                                   | EK-ODX20-TM            |

|                                                                                         |                        |

\*Microfiche and hard copy †Hard copy only

1-3

Figure 1-2 DECsystem-10/DECSYSTEM-20 Typical Block Diagram (Sheet 2 of 2)

| EBox Unit Description*                                                 | EK-EBOX-UD  |

|------------------------------------------------------------------------|-------------|

| Hardware Reference Manual†                                             | AA-H391A-TK |

| KL10-Based Site Preparation, Power System, and<br>Installation Manual† | EK-0KL10-SP |

| KL10 Maintenance Guide <sup>†</sup>                                    | EK-0KL10-MG |

| KLINIK User's Guide for KL10-Based Systems                             | EK-KLIN-UG  |

| MBox Unit Description*                                                 | EK-MBOX-UD  |

| MF20/MF20F MOS Memory Subsystem Technical Manual*                      | EK-0MF20-TM |

| Packet Switching System Layout Kit†                                    | EK-PACSS-LK |

| Packet Switching System Site Prep Guide <sup>†</sup>                   | EK-PACSS-SP |

| RH20 Unit Description*                                                 | EK-RH20-UD  |

# 1.1.3.2 Software Documentation – Software documents can be ordered from:

Software Distribution Center Digital Equipment Corporation 444 Whitney Street Northboro, Massachusetts 01532

| Title                                                 | Document Number |

|-------------------------------------------------------|-----------------|

| Operator's Guide                                      | AA-4176C-TM     |

| Operator's Guide Update                               | AD-4176C-TM     |

| RSX-20F System Specifications                         | AA-H213A-TK     |

| Software Installation Guide                           | AA-4195F-TM     |

| SPEAR Manual                                          | AA-J833A-TK     |

| SPEAR Reference Card                                  | EY-SPEAR-RC     |

| System Manager's Guide                                | AA-4169E-TM     |

| User Environment Test Package Reference Manual (UETP) | AA-D606A-TM     |

\*Microfiche and hard copy †Hard copy only

#### 1.2 DECsystem-10/DECSYSTEM-20 SITE PREPARATION AND PLANNING

#### 1.2.1 DECsystem-10/DECSYSTEM-20 Installation

The KL10-Based Site Preparation, Power System, and Installation Manual applies to this installation. The mechanical, environmental, and power requirements of various units that may be configured into a DECsystem-10/DECSYSTEM-20 are found in this manual. For information about equipment not included in these procedures, refer to the appropriate option manual, field service print set, and engineering installation/test specifications.

#### 1.2.2 DECsystem-10/DECSYSTEM-20 Operation/Programming

Field service diagnostic software support for the DECsystem-10/DECSYSTEM-20 is provided by the KLAD-10/20 diagnostic pack. The version required for this system must contain the diagnostics that support minimum revision level 4.

For system-level diagnostic support of most peripheral devices, the normal exec mode diagnostic method is used in addition to user mode diagnostics. User mode diagnostics are restricted to memory, disk, and tape subsystems, and secondary communication front ends.

The TOPS-20 operating system provides entries in the system's SPEAR log file and the TGHA files. In addition to the previously explained devices, SPEAR supports error logging information relative to network environments.

#### 1.2.3 DECsystem-10/DECSYSTEM-20 Service

The maintenance philosophy for DECsystem-10/DECSYSTEM-20s using the KL10-R processor is the same as for previous DECsystem-10/DECSYSTEM-20s. There have been no major logic changes.

Maintenance manuals for Digital manufactured equipment are available only on microfiche (except as identified in the list of related documents). Vendor manuals for purchased options will be sent with the system.

Field service engineering print sets are provided with the system. These print sets contain the unit assembly drawings for Digital manufactured subassemblies and show any features unique to the DECsystem-10/DECSYSTEM-20.

#### 1.2.4 DECsystem-10/DECSYSTEM-20 Engineering Drawing Sets

| Title                                                                  | Print Number       |

|------------------------------------------------------------------------|--------------------|

| KL10-R Field Maintenance Print Set                                     | MP01708            |

| DX20F Field Maintenance Print Set<br>DC20F Field Maintenance Print Set | MP01709<br>MP01710 |

| MF20F Field Maintenance Print Set                                      | MP01711            |

| DN20F Field Maintenance Print Set                                      | MP01712            |

# CHAPTER 2 SYSTEM FEATURES

#### 2.1 INTRODUCTION

The central processing unit (CPU) uses high-speed ECL logic, a microprogrammed instruction set, an automatic paging buffer, an automatic data buffer, and up to eight high-speed integral data channel processors. The system also features up to four front-end processing channels and up to 1.5 megawords of internal MOS memory. All of these functional elements are housed in three cabinets.

Besides the state-of-the-art hardware, the DECsystem-10/DECSYSTEM-20 features an advanced timesharing/batch operating system that allows both timesharing and batch users to have the benefit of system resources as if it were a system dedicated to each user. The software system also features advanced high-level languages, data base management facilities, and utilities.

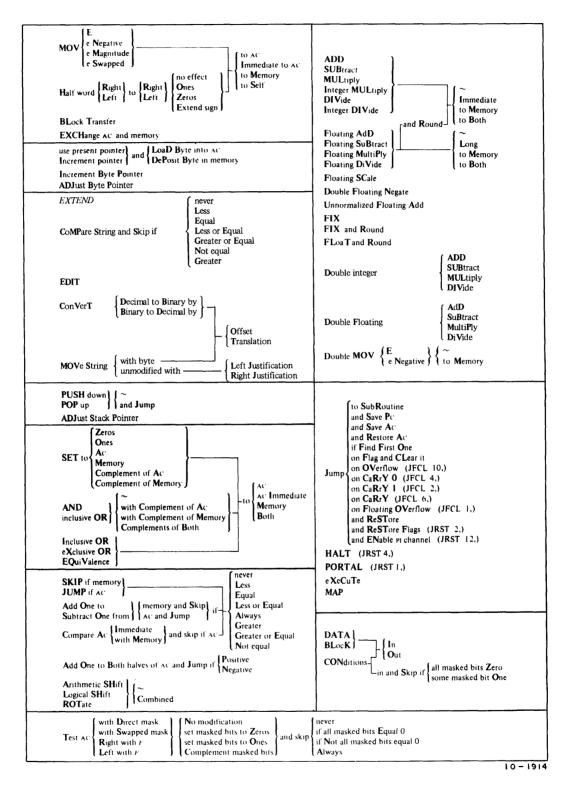

#### 2.2 INSTRUCTION SET

The DECsystem-10/DECSYSTEM-20 offers 398 instructions, a very large set that provides the flexibility required for special computing problems. The instruction set is microprogrammed; that is, each instruction is actually a series of microinstructions that perform various logical functions such as processor state control, data path control, and the actual execution of each instruction. The microcode is loaded into a 2 K words by 84-bit RAM (random-access memory) through the PDP-11 front-end processor. Since the set provides so many instructions to select from, fewer instructions are needed to perform a given function. Assembly language programs are, therefore, shorter than with other computers; and the instruction set simplifies the monitor, language processors, and utility programs. For example, compiled programs on a DECsystem-10/DECSYSTEM-20 are often 30 percent to 50 percent shorter, require less memory, and execute faster than those of corresponding computers.

In addition to the instructions, the DECsystem-10/DECSYSTEM-20 features 64 programmable operators, 33 of which trap to the monitor (monitor calls) and 31 of which trap to the user's area. An attempt to execute one of these unimplemented instructions results in a trap to the monitor.

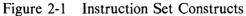

The instruction set, regardless of its size, is easy to learn. It is logically arranged into families of instructions and the mnemonic code is constructed modularly (Figure 2-1). All instructions are capable of directly addressing a full 256 K words (36-bit) of memory without sorting again to base registers, displacement addressing, or indirect addressing. Instructions may, however, use indirect addressing with indexing to any level. Most instruction classes, including floating-point, allow immediate mode addressing, where the result of the effective address calculation is used directly as an operand in order to save storage and speed execution.

Although there are a large number of instructions, they may be broken into easily learned, logically completed groups (Figure 2-1). To show this, the group to move full words (36 bits) takes the form shown in Figure 2-2.

To form a useful instruction, the following steps are taken.

- 1. The basic operator MOV is chosen. This specifies a full-word move.

- 2. One of four modifiers is chosen from the operator 1 group. This group specifies how the word is to be modified while being moved, where:

- E = No modification

- N = Take two's complement

- M = Take magnitude

- S = Swap left and right halves.

Figure 2-2 Move Instruction Construct

- 3. One of four modifiers is selected from the operator 2 group. This group specifies where the word is fetched from and where it is placed, therefore:

- (Blank) = No memory to the accumulator

- I = Take the 18-bit address as operand (immediate mode)

- M = Accumulator to memory

- S = Memory to memory (self).

This simple example illustrates the power and flexibility of the entire DECsystem-10/DECSYSTEM-20 instruction set. With one instruction class, a total of 16 instructions has been made. For example:

- MOVE AC, ADR moves the content of ADR to the specified AC.

- MOVEM AC, ADR moves the content of the specified AC to ADR.

- MOVEI AC, 5 moves the number 5 to AC.

- MOVNM AC, ADR moves the complemented content of AC or ADR.

A complete specification for the DECsystem-10/DECSYSTEM-20 instruction set is given in the Hardware Reference Manual.

#### 2.2.1 Full-Word Data Transmission

The full-word data transmission instructions move one or more full words of data from one place to another. The instructions may perform minor arithmetic operations, such as making the negative (two's complement) or the magnitude of the word being processed.

#### 2.2.2 Half-Word Data Transmission

The half-word data transmission instructions move a half word and may modify the contents of the other half of the destination location. There are 16 instructions that differ in the direction that they move the chosen half word and in the way in which they modify the other half of the destination location.

#### 2.2.3 Block-Transfer Instruction

The block-transfer instruction facilitates the saving of accumulators or moving of blocks of memory from one set of contiguous locations to another. This instruction works for any block size, moving the block from any location to any other location.

#### 2.2.4 Byte Manipulation

The five byte manipulation instructions pack or unpack bytes of any length anywhere within a word. In some systems, byte manipulation refers to 6-bit or 8-bit bytes. For the DECsystem-10/DECSYSTEM-20, byte manipulation refers to bytes of any size from 0 bits to a full word (36 bits). Note that ASCII is a 7-bit code, and on the DECsystem-10/DECSYSTEM-20, 7-bit bytes are efficiently stored 5 to a word. All the byte instructions on the DECsystem-10/DECSYSTEM-20 use a byte pointer that allows addressing of any size byte in any position in any of the 262,144 addressable words. Furthermore, both load and deposit byte instructions have a condition for automatic byte incrementation.

#### 2.2.5 Business Instruction Set

Five instructions make up the business instruction set in the DECsystem-10/DECSYSTEM-20 central processor. Four of these are new arithmetic instructions to add, subtract, multiply, and divide using double-precision, fixed-point operands. The new extend (string) instruction is capable of performing nine separate functions.

These functions include an edit capability; decimal-to-binary and binary-to-decimal conversion in both offset and translated mode; move string in both offset and translated mode; and compare string in both offset and translated mode. Offset mode is byte modification by addition of the effective address of the string instruction to the source byte string; translated mode is byte modification by translation through a table of half words located at the effective address of the string instruction. This also occurs in edit. In addition to providing the translation function, those instructions that use translation can control the flags in ACs and can detect special characters in the source string.

This business instruction set provides faster processing since there are specific instructions for doing more comprehensive string operations. These instructions can be used on a series of code types including ASCII, EBCDIC, and so on.

#### 2.2.6 Logic Instructions

The logic instructions provide for shifting and rotating, as well as performing the complete set of 16 Boolean functions on two variables.

#### 2.2.7 Fixed-Point Arithmetic

Fixed-point arithmetic is handled in two's complement notation with 36-binary-bit accuracy (10 decimal digits). Mode options include immediate to accumulator, to memory, or to both with a result. Three classes of shifting include arithmetic, logical, and rotating operations to single- or double-word accumulators.

#### 2.2.8 Floating-Point Arithmetic

The floating-point arithmetic instructions include instructions to perform scaling, negating (form two's complement), addition, subtraction, multiplication, and division upon numbers in single- and double-precision, floating-point format. In the single-precision, floating-point format, 1 bit is reserved for the sign, 8 bits are used for the exponent, and 27 bits are used for the fraction. In double-precision, floating-point format, 1 bit is used for the sign, 8 bits are used for the exponent, and 62 bits are used for the fraction.

#### 2.2.9 Arithmetic Operation Modes

All of the DECsystem-10/DECSYSTEM-20 arithmetic operations — floating-point as well as fixed — and Boolean (logical) operations have options allowing the storage location for the result of the operation to be specified in the selected accumulator, in the addressed memory location, or in both. All may take their immediate address as an operand.

#### 2.2.10 Fixed/Floating Conversions

Special instructions provide for converting fixed-point formats to or from floating-point formats. Two sets of instructions are provided to perform this function, one set optimized for FORTRAN and a second set optimized for ALGOL.

#### 2.2.11 Compare and Modify

The compare and modify instruction set is large (128 instructions) and extremely flexible. Half of these are arithmetic compare and modify instructions, which may compare two numbers or compare the content of an accumulator or a memory word to zero and skip or jump accordingly. It is also possible to increment or decrement the word being tested and copy the modified word into an accumulator, all in a single instruction. In all cases of arithmetic comparisons, any one of the eight possible ordering relations on two variables may be specified, namely, if X and Y are the variables, X = Y,  $X \neq Y$ , X > Y,  $X \ge Y$ , X < Y,  $X \le Y$ , true, and false.

The remaining 64 codes are logical compare and modify instructions that allow a variety of choices governing the way in which a bit selection mask is to be obtained, what the test condition is to be, and what modification is to be made on the selected bits.

#### 2.2.12 Program Control

Program control instructions include several types of jump instructions and the subroutine control PUSHJ and POPJ instructions.

Pushdown stacks are handled by the PUSH and POP instructions, which, through a stack pointer, process data on a first-in, last-out basis. Subroutine entry and return is accomplished by jump instructions (PUSHJ and POPJ) that insert return addresses on a pushdown stack. These instructions are vital to the efficient operation of the timeshared monitor and all of the reentrant system's programs.

#### 2.2.13 Input/Output

Input/output over the EBus is handled by eight straightforward instructions. Each instruction may reference one of 126 devices. In addition to reading status, writing status, reading data, and writing data, there are block-in and block-out instructions to handle blocks of data to and from memory and to a device in an efficient manner.

#### 2.2.14 Unimplemented User Operations (UUOs)

Many of the codes not assigned as specific instructions are executed as unimplemented user operations, where the word given as an instruction is trapped and must be interpreted by a routine included for this purpose by the programmer. Those UUOs reserved for use by the monitor are called monitor UUOs (MUUOs), while user UUOs are called local UUOs (LUUOs). Instructions that are illegal in user mode also trap in the same manner as MUUOs.

#### 2.2.15 Trap Handling

The DECSYSTEM-20 provides facilities for handling arithmetic overflow and underflow conditions, pushdown list overflow conditions, and page failures directly by the execution of programmed trap instructions. This trap capability avoids recourse to the program interrupt system. A trap instruction is executed in the same address space as the instruction that caused the trap.

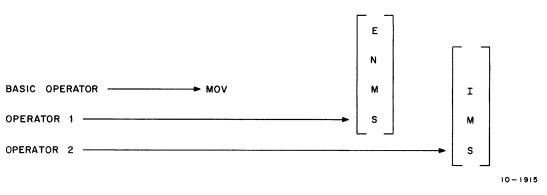

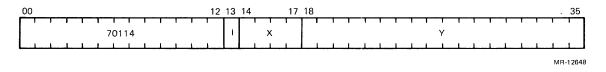

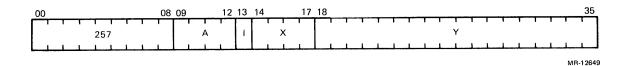

#### 2.3 INSTRUCTION FORMAT

In all the non-input/output instructions, the nine high-order bits (0-8) specify the operation, and bits 9-12 usually address an accumulator but are sometimes used for special control purposes such as addressing flags (Figure 2-3). The rest of the instruction word always supplies information for calculating the effective address, which is used for immediate mode data or is the actual address used to fetch the operand or alter program flow. Bit 13 specifies the type of addressing (direct or indirect), bits 14–17 specify an index register for use in address modification (zero indicates no indexing), and the remaining eighteen bits (18-35) contain a memory address.

The instruction codes that are not assigned as specific instructions are performed by the processor as socalled "unimplemented operations."

An input/output instruction is designated by three 1s in bits 0-2. Bits 3-9 address the input/output device to be used in executing the instruction, and bits 10-12 specify the operation. The rest of the word is the same as in non-input/output instructions.

Figure 2-3 Instruction Format

#### 2.4 NUMBER SYSTEM

The standard arithmetic instructions in the DECsystem-10/DECSYSTEM-20 use two's complement, fixed-point conventions to do binary arithmetic. In a word used as a number, bit 0 (the leftmost bit) represents the sign; 0 for positive, 1 for negative. In a positive number, the rest of the 35 bits represent the magnitude in typical binary notation. The negative of a number is found by taking its two's complement. Zero is represented by a word containing all 0s.

#### 2.4.1 Fixed-Point Arithmetic Conventions

Two common conventions are to consider a number as an integer (binary point at the right) or as a proper fraction (binary point at the left); in these two cases, the range of numbers represented by a single word is  $-2^{35}$  to  $2^{35} - 1$  or -1 to  $1 - 2^{-35}$ . Since multiplication and division make use of double-length numbers, there are special instructions for performing these operations to get results that can be represented by a single word.

The format for double-length, fixed-point numbers is an extension of the single-length format. The magnitude (or its two's complement) is the 70-bit string in bits 1–35 of the high- and low-order words. Bit 0 of the high-order word is the sign, and bit 0 of the low-order word is ignored. The range for double-length integer and proper fractions is, therefore,  $-2^{70}$  to  $2^{70} - 1$  or -1 to  $1 - 2^{-70}$ .

#### 2.4.2 Floating-Point Arithmetic Conventions

The DECsystem-10/DECSYSTEM-20 has firmware for processing both single- and double-precision, floating-point numbers.

Included in the arithmetic instruction set are eight double-precision instructions and three fixed/floating conversion instructions. A double-precision word consists of the sign, an 8-bit exponent, and a 62-bit fraction. This gives a precision in the fraction of 1 part in  $4.6 \times 10^{18}$  and an exponent of 2 to a power of from -128 to +127.

The same format is used for a single-precision number and the high-order word of a double-precision number. A single-precision, floating-point instruction interprets bit 0 as the sign, but interprets the rest of the word as an 8-bit exponent and a 27-bit fraction. Normalized single-precision, floating-point numbers have a fraction that ranges in magnitude from 1/2 to  $1 - 2^{-27}$ . Increasing the length of a number to two words does not change the range but instead increases the precision; in any format, the magnitude range of the normalized fraction is from 1/2 to 1, decreased by the value of the least significant bit. In all formats, the exponent range is from -128 to +127.

#### 2.5 EFFECTIVE ADDRESS CALCULATION

All instructions in the DECsystem-10/DECSYSTEM-20, without exception, calculate an effective address using bits 13-35 in exactly the same way. The steps are as follows.

- 1. Get the number in address field Y, bits 18–35. Any one of 262,144 locations can be specified.

- 2. If index field X, bits 14–17, is not zero, add the contents of the specified index register to the number found in step 1.

- 3. Get the indirect bit, I, bit 13. If it is 0, the calculation is done and the result of steps 1 and 2 is the effective address. If it is 1, then go to step 4.

- 4. Use the address calculated by steps 1 and 2 to get a new word from memory, and go back to step 1.

The effective address calculation continues until a word is found with a 0 in bit 13. At that point, the result of steps 1 and 2 is taken as the effective address for the instruction.

The calculation is done for all instructions, including those specifying immediate mode. As an example, it is possible in one immediate mode instruction to load an accumulator with the address of a particular entry within an indexed table for use as a subroutine argument.

#### 2.6 GENERAL-PURPOSE REGISTER BLOCKS

General-purpose registers are another DECsystem-10/DECSYSTEM-20 feature that help improve program execution. These sets of fast integrated circuit registers can be used as accumulators, as index registers, and as the first 16 locations in memory. Since the registers can be addressed as memory locations, they do not require special handling instructions.

Eight sets of 16 fast registers are included. Program switching time between register stacks is 500 nanoseconds.

Different register blocks can be used for the operating system and individual users. This eliminates the need for storing register contents when switching from user mode to executive mode. Also, a critical real-time program is able to maintain its own register block for handling data and interrupt sequences at maximum speed.

#### 2.7 MEMORY SYSTEM

#### 2.7.1 MOS Memory

The DECsystem-10/DECSYSTEM-20 memory system can provide storage for up to 3,145,728 44-bit words (36 data bits, 6 ECC bits, 1 ECC parity bit, and 1 spare bit) in increments of 256 K (262,144) words, 1.5 megawords internal, 1.5 megawords external.

#### 2.7.2 DMA

The DMA memory bus adapter adapts the KL10 storage bus (SBus) to the external memory bus structure. The DMA also separates the SBus into four separate buses (KBus 0-3) to allow 4-word transfers and 4-way interleaving of storage modules.

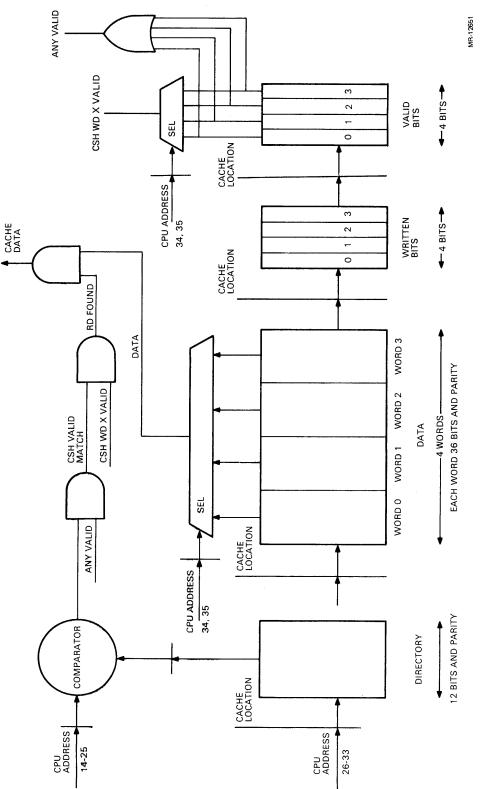

#### 2.7.3 Cache Memory

A DECsystem-10/DECSYSTEM-20 can also be equipped with a 150 nanosecond access time data cache or buffer memory. Data being read from memory is usually found already in the cache 90 percent to 95 percent of the time, therefore giving the DECsystem-10/DECSYSTEM-20 an effective memory access time of approximately 300 nanoseconds. Another feature of the state-of-the-art design cache memory is that unlike contemporary designs, it does not require write-through to memory. Instead, words to be written are written into the cache memory. This eliminates, for example, the necessity of writing back into main memory each value of an index in a loop made up of only a few instructions.

The cache is paged and words from one or more pages are written back to main memory from the cache only when it is necessary to make room for words from new pages. A cache sweep feature allows main memory to be updated with all or selected pages of the cache.

#### 2.8 PROCESSOR MODES

Instructions are executed in one of two modes depending on the state of a mode bit. Programs operate in either user mode or executive mode. In executive mode operations, all implemented instructions are legal. The monitor operates in executive mode and is able to control all system resources and the state of the processor. In user mode operations, certain instructions such as direct I/O are illegal, causing a trap to the monitor. Users are required to issue monitor calls for system services such as I/O.

Executive and user mode operations are each divided into two submodes. User mode is divided into public and concealed submodes and executive mode into supervisor and kernel submodes. For each 512 word page in the system, information is stored in a table (page map) maintained by the operating system that specifies whether or not a page can be accessed or changed and if it is defined to be public or concealed. The executive and user modes divide according to whether the active program is running in a public or concealed area.

If a program is running in public submode, pages within the user's addressing space are accessible only if they are listed in the user's page map and are defined to be accessible from public mode. Pages defined as public are, by definition, accessible. Pages defined as concealed may be accessed only at specific entry points; that is, portals that permit entry from public submode programs. In concealed submode operations, programs can access all of the virtual addressing space. However, if a program running in concealed submode executes an instruction from an area defined as public, the state of the processor transfers over into public submode. Typical user programs operate in public submode. Concealed areas can be used for proprietary coding that can be executed but not changed or examined by users operating in public mode. The supervisor and kernel submodes are similar but not identical to the public and concealed submodes. Supervisor submode programs can access but cannot modify areas defined as concealed. Also, any instruction executed out of a public area from either supervisor or kernel submode returns the processor to supervisor submode. In kernel submode operations, all of memory is accessible and can be modified. Programs operating in kernel submode can address portions of memory directly, without paging; and it is through the kernel submode program that page restrictions are made. Functions that go to supervisor submode generally include those affecting individual users as opposed to the whole system management of input/output, priority interrupts, page map accounting, and so on, which are handled by kernel submode programs. The ability of kernel submode programs to supply information that supervisor submode programs can read but not change, allows portions of the operating system to be hardware-protected from other portions having adjustments or design changes.

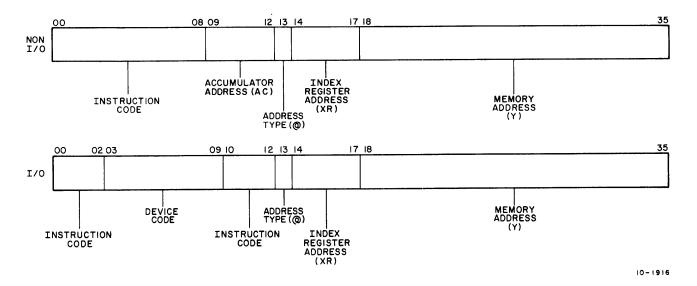

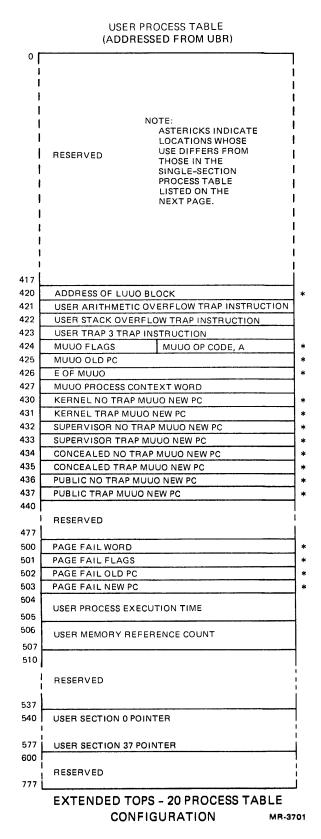

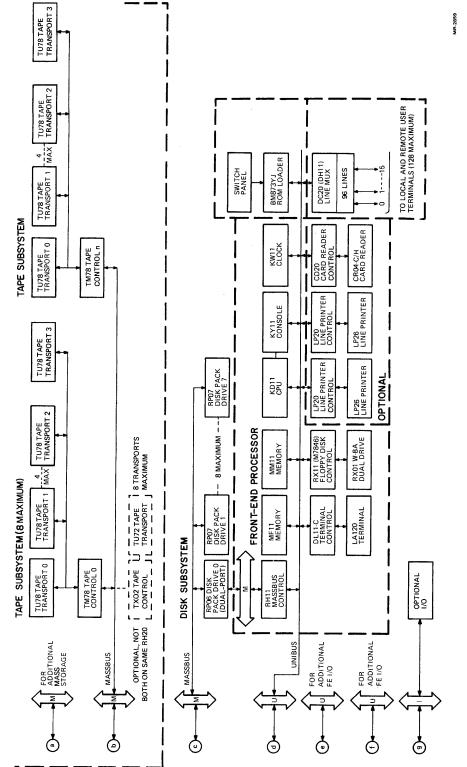

#### 2.9 PROCESS TABLES

There are two types of process tables in memory that are used by the hardware for both system and user management. These are the Exec Process Table (EPT) and the User Process Table (UPT). Each is one page long (Figures 2-4 and 2-5). One EPT is used for the monitor and one UPT for each user process in the system. The following is a partial list of the types of information that are maintained in these tables.

- 1. User Process Table

- a. Arithmetic overflow vector address. Overflow affects only the user and not the system so it is handled in the user address space.

- b. Memory and instruction processor convention accounting clocks. This information is kept for each user to help in exact user resource accounting.

- 2. Exec Process Table

- a. Channel recording area. Information about integrated channel status, which affects the entire system, is maintained here.

- b. Front-end processor communications area. Used in communications between the central processor and the front-end processor.

While the monitor is providing services for a user, such as I/O requests, it must be able to reference the user address space. There are two mechanisms provided to do this.

- 1. A special instruction called PXCT, which has bit settings to indicate which of the specified addresses are in the current address space and which are in the previous address space.

- 2. The Exec Page Table contains "indirect pointers" through the User Page Table. These are used to provide a per process area for each process in the system.

### 2.10 MEMORY ADDRESS MAPPING

The memory address mapping hardware has been developed in conjunction with the software so that memory management is transparent to the user. Physical memory is divided into 512 word segments called pages. All addresses — both monitor and user — are translated from the program's address space (referred to as the virtual address) to the physical memory address space. This facilitates protection of the monitor and allows efficient use of physical memory. For example, only a portion of the monitor need be permanently memory-resident, resulting in more available user memory.

#### EXECUTIVE PROCESS TABLE (ADDRESSED FROM EBR)

| οΓ             |                                                |

|----------------|------------------------------------------------|

| ·              | EIGHT CHANNEL LOGOUT AREAS                     |

| į              | EACH: 0 INITIAL CHANNEL COMMAND                |

|                | 1 GETS CHANNEL STATUS WORD                     |

| i              | 2 GETS LAST UPDATED COMMAND                    |

| 37 L           | 3 RESERVED                                     |

| 10             | RESERVED                                       |

| <sup>11</sup>  |                                                |

| 42  <br>       | STANDARD PRIORITY INTERRUPT INSTRUCTIONS       |

| 57             |                                                |

| 60  <br>63     | FOUR CHANNEL BLOCK FILL WORDS                  |

| 64  <br>I      | RESERVED                                       |

| 137            |                                                |

| 140            | FOUR DTE20 CONTROL BLOCKS                      |

| 1              | EACH: 0 TO11 BYTE POINTER                      |

| I              | 1 TO10 BYTE POINTER                            |

| 1              | 2 DTE INTERRUPT INSTRUCTION                    |

| I              | 3 RESERVED                                     |

| I              | 4 EXAMINE PROTECT                              |

| - 1            | 5 EXAMINE RELOCATION                           |

| - 1            | 6 DEPOSIT PROTECT                              |

| !              | 7 DEPOSIT RELOCATION                           |

| 177            |                                                |

| 200            |                                                |

|                | RESERVED                                       |

| ا<br>420       |                                                |

| 421            | EXECUTIVE ARITHMETIC OVERFLOW TRAP INSTRUCTION |

| 422            | EXECUTIVE STACK OVERFLOW TRAP INSTRUCTION      |

| 423            | EXECUTIVE TRAP 3 TRAP INSTRUCTION              |

| 424            |                                                |

| 424  <br> <br> | RESERVED                                       |

| , i            |                                                |

| 507            |                                                |

| 510            |                                                |

|                | TIME BASE                                      |

| 511            |                                                |

| 512            |                                                |

|                | PERFORMANCE ANALYSIS COUNT                     |

| 513            |                                                |

| 514            | INTERVAL COUNTER INTERRUPT INSTRUCTION         |

| 515            |                                                |

|                | RESERVED                                       |

| 537            |                                                |

| 540            | EXECUTIVE SECTION 0 POINTER                    |

| 577            | EXECUTIVE SECTION 37 POINTER                   |

| 600            |                                                |

| 777            | RESERVED                                       |

|                | SINGLE-SECTION TOPS-20 PROCESS                 |

|                | TABLE CONFIGURATION MB-3702                    |

Figure 2-5 Exec Process Table

The high-order nine bits of an 18-bit virtual address make up the virtual page number and are used to index into a hardware page map. If the 13-bit physical page number is found in the hardware page map, then the low-order nine bits of the virtual address are appended to the 13-bit physical page number to form the complete physical address. If the entry in the hardware page map is not there, the memory processor gets the entry from the individual page map in memory and updates the hardware page map.

There is a page map in memory for the monitor and one for each user. These maps contain storage address pointers that identify either a page in memory or on disk. They may be of three basic types.

- 1. Private The page is owned by one user.

- 2. Shared The page is shared by more than one user.

- 3. Indirect Points to another page map page where the pointer may again be one of the three types.

In addition to the physical page numbers in the page map, control bits are present to serve various functions. For example, one bit is used to indicate that the page is read-only; another to indicate that no physical page at that time agrees to this virtual address slot.

Page level sharing among users is supported by a hardware Shared Page Table, which holds the physical address of the shared page. This table, which is addressed through a hardware register, enables the software memory management routines to maintain only one pointer to a page no matter how many processes are sharing it.

Information about how long a page has been in memory and the number of processes sharing it is also stored by the hardware in a Core Status Table to help the monitor in core management.

#### 2.11 **DIRECT I/O**

The EBus is used as a control and data path to/from a large number of low-speed I/O devices. Transfers are performed for 36-bit words at speeds of 370 K words/s. Therefore, each I/O instruction moves one word of data between memory and the buffer of the device controller (DTE20 or RH20). When block input or output instructions are used, entire blocks of data are moved to or from the device with a single instruction.

To initiate high-speed data channel transfers directly between memory and a device connected to the Massbus, a control word is first transferred over the EBus to the command register of a Massbus controller (RH20). Then, entire data blocks are moved between a drive and memory under the control of a channel command list.

#### 2.12 CHANNEL I/O

### 2.12.1 Integrated Massbus Controller

The integrated Massbus controllers are high-speed mass storage controllers that interface the RP06, RP07, and RP20 disk drives and the TU72, TU77, and TU78 magnetic tape drives to the integrated data channels in the memory controller. The controllers have been designed to provide high throughput by features such as the following.

- 1. All controllers can transfer data simultaneously since each controller is connected to the memory system with its own channel.

- 2. While one device on a controller is transferring data, control operations such as seek or rewind

may be issued to another device on the same controller. The operation can be initiated and an interrupt generated when it is complete.

- 3. Each controller has a lookahead command register, which enables the software to preload the next transfer request during the current transfer. Therefore, the next transfer can start with the next sector on the same device with no rotational delay.

- 4. When the controller has completed an operation it interrupts the central processor via a vectored interrupt so the central processor does not have to poll a series of devices to determine which device caused the interrupt.

Error checking is provided for both the channel and device data paths. The controller will terminate a command if certain errors are detected.

The connection between the controller and its devices is called the Massbus and contains parallel data and control paths. These parallel paths permit simultaneous data transfer and control operations.

#### 2.12.2 Integrated Channels

Within the storage controller there is one channel control for each device controller. Each channel control has a 15 word data buffer, a channel command word register, and a control word location pointer; or each has a program counter. A channel consists of a channel control, a device controller, and its associated drives.

The channels perform data transfer by executing channel programs, which are loaded into memory by the device service routines. The channel loads a channel command word into the command register and then executes it. The direction of transfer is specified in the instruction sent to each controller.

Channel instructions contain a memory address, a word count, and function control bits to facilitate efficient I/O programming. Each time a word is transferred, the word count is decremented.

If the initial address is 0 and the operation is a read, the number of words indicated by the word count is skipped. If the operation is a write, the channel transmits software-specified block-fill words for the required count.

If the initial word count is 0, the channel will jump to the address indicated in the instruction, where a new command word will be selected and decoded.

System I/O programs can select between two ways of halting, depending on which is more efficient for the device. They may use a channel program chaining technique in which a halt instruction, which contains the address of the next channel program, is the last command word. Alternatively, if the last data transfer command word has the halt control bit set, the channel will halt when the word count is decremented to 0. This saves time because it saves a halt command memory fetch.

If a channel detects an error, it stores two channel status words in the appropriate controller location in the Exec Process Table. The first status word contains bits to indicate what type of error occurred and the control word location pointer. The second status word contains the command word that was being executed with the up-to-date word count and address.

#### 2.13 PRIORITY INTERRUPT SYSTEM

The DECsystem-10/DECSYSTEM-20 interrupt facility does not require devices to be hardwired to a particular level. Instead, devices are assigned under program control to any one of seven priority levels through the dynamic loading of device registers. Therefore, the monitor can change the priority level of any device or disconnect the device from the system and later reinstate it at another level. This is an

advantage over permanently hardwired systems, which require a large number of levels, often operate at very high overhead, and cannot change device priorities without system shutdown and rewiring.

Priority level 0 is above the seven programmable levels and is reserved for the front-end processor, which is therefore able to interrupt the system at any time for console or diagnostic operations.

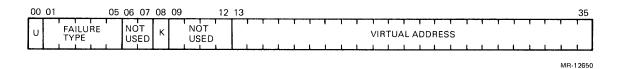

#### 2.14 TRAP FACILITY

The system also provides a trapping mechanism to handle certain conditions that affect a single job. Conditions that are detected by the trapping hardware include:

- Address violation

- Arithmetic overflow

- Pushdown overflow

- Illegal instruction

- Monitor calls

- Page faults.

#### 2.15 ACCOUNTING AND PERFORMANCE METERS

The meters built into the DECsystem-10/DECSYSTEM-20 provide a number of timing and counting functions, as follows.

- 1. Interval timer A programmable source of interrupts with a range from 10 microseconds to 40.96 milliseconds.

- 2. Time base A one microsecond relative time-of-day clock that is used by the monitor for system accounting.

- 3. Performance analysis counter Designed as a tool for testing and evaluating the system, this counter monitors either duration or rate of occurrence of various hardware conditions and events.

- 4. Two accounting meters The first is an instruction processor meter, which measures the amount of the instruction processor time used. This information is stored in the User Process Table. While the default count is user time only, the monitor may also include interrupt time and/or exec mode time in this accounting. The second is a memory reference meter, which measures user program accesses to core memory. This information is also stored in the User Process Table.

#### 2.16 FRONT-END PROCESSOR

#### 2.16.1 Functions

One of the significant features of the DECsystem-10/DECSYSTEM-20 architecture is the PDP-11 frontend processor. It has the following uses.

- 1. Control of low-speed peripherals such as card readers, line printers, and asynchronous communications devices

- 2. Console operations for the central processor including push-button functions such as load, start, and stop

- 3. On-line and remote diagnostic analysis

- 4. Microcode loading and system startup

The front-end processor communicates with the central processor through an interface that permits concurrent two-way data transfers.

As a diagnostic computer, the front-end processor can examine the data paths and control logic of the central processor even if that unit is completely unable to operate. A diagnostic bus linkage permits automated testing procedures that allow a larger number of diagnostic tests to be run than would be possible with conventional techniques. Accuracy is increased since not only is there less chance for human error, but maintenance engineers do not have to rely upon a malfunctioning central processor to help diagnose itself. Other capabilities include remote and timesharing diagnosis.

If system power fails, a detection circuit senses the condition and causes an interrupt. The interrupt can trigger the operation of a program that saves changing registers and provides an orderly system shutdown so that the system can be restarted with a minimum amount of lost time.

All three phases of ac power are monitored. Low voltage on any phase will initiate the power-down sequence. A program-selectable automatic restart capability is provided to allow resumption of operation when power returns. Alternatively, a manual restart may be used.

Temperature sensors strategically placed within the equipment detect high temperature conditions and cause power shutdown. This, in turn, initiates the power failure interrupt.

The front end boots the DECsystem-10/DECSYSTEM-20 by reading in an initial program from the front-end disk (via the RH11) attached to the Unibus. This in turn brings the main bootstrap program from the dual-ported disk, which boots the system into operation.

#### 2.16.2 Components

**2.16.2.1** DTE20 – The DTE20 console processor interface connects the central processor and the frontend processor to provide capabilities to interrupt, examine, deposit, and transfer data during timesharing and diagnostic operations.

**2.16.2.2** Console – The console provides the operator with a direct system interface by simulating the control switch and display indicator functions for the central processor. Therefore, the operator is provided with control of normal program and diagnostic operations, which allows him to start, stop, load, modify, or continue a program. The console is connected for simultaneous two-way transmission to the PDP-11 Unibus, through an asynchronous line interface.

**2.16.2.3 PDP-11** – The heart of the PDP-11 system is the Unibus, which is an asynchronous bidirectional bus interconnecting the front-end processor components. The front-end processor is connected to the Unibus as a subsystem and controls time allocation of the Unibus for peripheral devices. In addition, the front-end processor performs arithmetic and logic operations through instruction decoding and execution. The instruction set is implemented through a group of hardware subroutines stored within a read-only memory (ROM). Memory is read/write, random-access magnetic core with a maximum cycle time of 980 nanoseconds and a maximum access time of 425 nanoseconds. Storage capacity is 28 K words having an 18-bit word length (16 data bits plus two parity bits).

# CHAPTER 3 THE HARDWARE

#### 3.1 INTRODUCTION

The DECsystem-10/DECSYSTEM-20 includes the following subsystems.

- 1. A KL10-based main processor subsystem with up to 1.5 megawords of internal MOS memory and 1.5 megawords of external MOS memory (except with the 1091)

- 2. A PDP-11-based front-end processor subsystem

- 3. A mass storage subsystem

#### 3.2 THE MAIN PROCESSOR SUBSYSTEM

The main processor subsystem of the DECsystem-10/DECSYSTEM-20 contains the following units (Figure 3-1).

- 1. EBox

- 2. MBox

- 3. Meter board

- 4. MF20 MOS memory

- 5. DTE20 ten-eleven data interface (up to four)

- 6. RH20 Massbus controller (two at least, but there can be up to eight)

The EBox, MBox, and meter board are designed with high-speed, nonsaturating emitter-coupled logic (ECL) and are housed on the same assembly. These functional units make up the central processing unit (CPU). The DTE20 and RH20 are designed with TTL logic and serve as the interface controllers to the front-end processor and Massbus-compatible storage devices, respectively. An internal X/SBus serves as the control and data path between the CPU and its memory. An internal EBus serves as the control and lata path between the CPU and the controllers (DTE20 and RH20). Since both ECL and TTL logic are used in the main processor, logic level translators are included in the CPU assembly to convert from one ogic level to the other.

#### 3.2.1 The EBox

**3.2.1.1 Hardware** – The EBox is the instruction execution unit of the central processor. Basically, the nstruction execution unit consists of the following logic.

- 1. Memory request logic

- 2. 72-bit arithmetic logic

- 3. 23-bit address logic

- 4. 10-bit arithmetic logic

- 5. Eight general register blocks

Figure 3-1 DECsystem-10/DECSYSTEM-20 Typical Block Diagram (Sheet 1 of 2)

3-2

Figure 3-1 DECsystem-10/DECSYSTEM-20 Typical Block Diagram (Sheet 2 of 2)

3-3

- 6. EBus control logic

- 7. Microprogrammed instruction dispatch and control store

In addition, the EBox contains the master clock, meters, a processor status register, and the diagnostic control logic.

All operations in the DECsystem-10/DECSYSTEM-20 are synchronized to the master clock, which runs at 50 MHz. The master clock can be started, stopped, single-stepped, and otherwise controlled by the front-end processor via the diagnostic control logic. This logic is distributed between the EBox and the DTE. Besides being able to control the master clock, the diagnostic control logic provides a means for monitoring the processor status and diagnostic registers in both the EBox and the MBox. The master clock supplies a 30 MHz clock to the MBox, a 12.5 MHz clock for the EBox control store, and a 6.25 MHz clock to the EBus and SBus.

The program counter (PC), virtual memory address adder (VMA AD), virtual memory address register (VMA), and arithmetic adder (AD) form the basic address manipulation path in the EBox. This path is 23 bits wide to accommodate a virtual address space of 8 million words. (Only 18 bits of the virtual address are implemented for DECsystem-10/DECSYSTEM-20 to provide a virtual address space of 256 thousand words.) During the course of calculating the effective address for an instruction, AD will contain the value of Y, Y + XR, Y@, or (Y + XR)@ and pass it to the VMA. The source for Y, XR, and @ are specified by the corresponding fields of the instruction. The VMA can also receive PC + 1 and PC + 2 via the VMA AD. This is normally done for main line instruction fetches or for skip-type instructions.

The arithmetic register (AR) and arithmetic register extension (ARX), the buffer register (BR) and buffer register extension (BRX), and the adder (AD) and adder extension (ADX) form a 72-bit data path for manipulating data. This data path is implemented so that half words, full words, and double words can be manipulated with ease. The AD and ADX are implemented with arithmetic logic units (ALU), which are capable of performing 16 arithmetic and 16 logical operations. Words fetched from memory may be moved into the AR, ARX, and IR. Usually data (operands) is placed in the AR and ARX, while instructions are moved to the ARX and IR. Words to be moved to memory are placed in the AR when a memory request is made. Data transfers to and from the EBus are made via the AD and AR, respectively.

The shift count adder (SCAD), floating exponent register (FE), and shift count register (SC) form the 10bit arithmetic logic, which is used in performing shift operations and operations on byte pointers and floating-point exponents.

The shifter (SH) is used in performing shift, rotate, and byte pointer operations. The shifter is also used in aligning a particular field of a word (such as the API function word) for dispatching into the control store as a function of the contents of that field.

The multiplier quotient register (MQ) is primarily used in performing floating-point and double-precision integer arithmetic operations. The MQ is also used as a temporary storage register for saving the API function word.

Each of the eight general register blocks (AC blocks 0–7) consists of a set of 16 general-purpose, highspeed registers. Block 0 is permanently assigned to the monitor and blocks 6 and 7 to the microcode. The monitor uses its AC block in the same way as the user program described in the following paragraphs. The microcode uses the assigned AC block when executing complex instruction algorithms. Of the remaining blocks, two can be assigned under program control (DATAO PAG) to the user as the current and previous context AC blocks. The current context AC block is used by the user program for indexing, for general storage as specified by the AC field of the instruction and/or by the effective virtual address (location 0-17), and for instruction execution if desired. The previous context AC block is used by the monitor to allow the monitor to reference the previous user's address space to pass arguments, data, or status information between the previous user's program and the monitor. This is normally done when the user program executes a monitor call for some type of service.

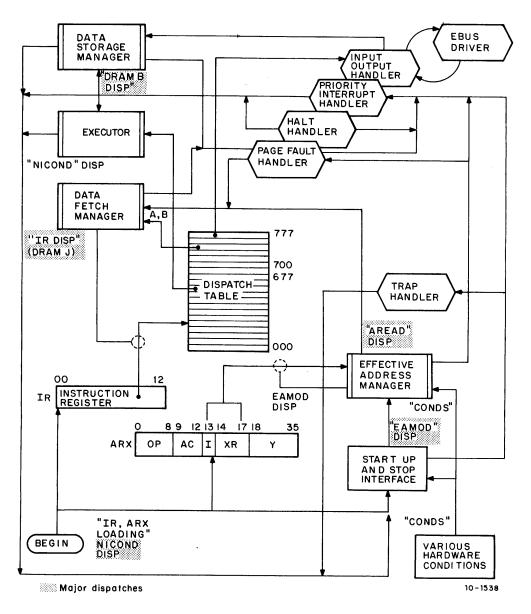

The instruction register (IR), dispatch RAM (DRAM), and control RAM (CRAM) form the instruction dispatch control and execution logic. Essentially, the IR holds the instruction's operation code (000–777), which is used to address the DRAM. The DRAM contains a dispatch address into the CRAM, and the CRAM contains the microcode for executing the instruction. Along with the dispatch address, the DRAM also contains control bits for initiating an operand fetch, instruction prefetch, and the store operation. The dispatch address and associated control bits in the DRAM vary in accordance with the requirements of the dispatching instruction. The contents of both the DRAM and the CRAM are the assembled and formatted object code of the KL10 microprogram.

When an instruction is fetched from memory, it is normally placed into the ARX and the IR. The microcode detects that an instruction has been received and if no traps, interrupts, or errors are sensed, will start calculating the effective address. If indexing is specified by the instruction, the microprogram will access the assigned general register block at the location addressed by ARX bits 14–177 (the XR field). The initial address portion of the instruction word in ARX is the Y field, consisting of bits 18–35 of ARX. This is added to the contents of the addressed general register, and the result will enter VMA and AR. The effective address calculation continues; if the instruction specifies indirect addressing [ARX bit 13 (1)], a memory cycle is required. The fast memory is addressed by VMA bits 32–35 if VMA bits 18–31 = 0. If this is the case, then the indirect reference will access fast memory. As before, the word will pass via the addre into AR and VMA. If the indirect reference is not to fast memory, the microprogram generates a request via the MBox cache data lines and enters the AR and ARX. The DECsystem-10/DECSYS-TEM-20 is capable of multilevel indirect addressing; indexing may be specified at each level. The process continues until the indirect bit in a word entering ARX is zero. At this point only one level of indexing is possible and having completed this operation the VMA and AR will contain the effective address (E).

After computing the effective address, the microprogram uses the op code of the instruction in IR to address the dispatch RAM. The word fetched from the dispatch RAM is loaded into a register (dispatch register) where it will be available while the instruction is processed. The dispatch register word contains the equivalent of a fetch field, a store field, and an address field. This equivalent points to the location in the microprogram where the execution portion of the cycle for the instruction starts. The fetch and store fields are sampled by the microprogram at the appropriate time to initiate fetch and store operations where required. The microprogram consists of many microinstructions, each of which is composed of discrete fields. Some of these fields control the data path; others control the microprogram branching mechanism; still others control the clock, and so on.

If an operand is to be fetched or if a write operation is to be performed, the address is page-checked after the effective address has been calculated. After issuing the appropriate request, the microprogram diverts to a point where it will wait for the operand to be loaded into AR and ARX if an operand was to be fetched, or it will wait for the page check to be verified.

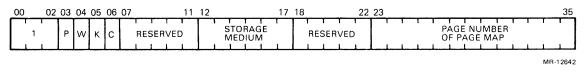

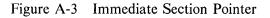

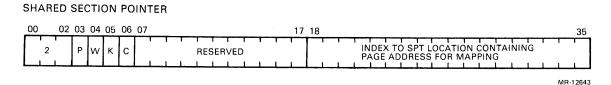

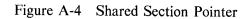

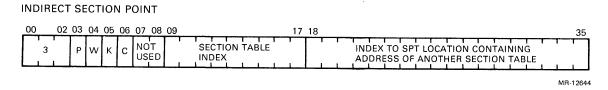

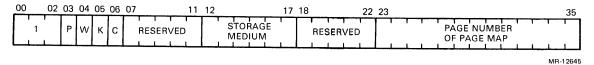

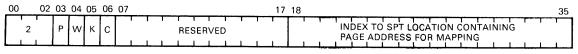

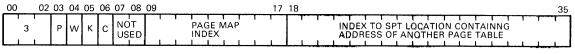

When this phase is completed, the microprogram uses the address portion of the dispatch word to enter the microprogram at a point that will start the execution of the particular instruction.