# VAX-11/VENUS

VENUS

SYSTEM

DEVELOPMENT PLAN

30 January 1981 Revision 3

**COMPANY CONFIDENTIAL**

digital

# VENUS

SYSTEM DEVELOPMENT PLAN

30 January 1981 Revision 3 This is the Phase 1 System Development Plan for the Venus Program. It has been reviewed and approved by the development managers, the product managers, and Product Line representatives, and was given formal approval at the Venus Phase 1 Review on December 17, 1980. Venus Product Management's Phase 1 Business Plan is expected to be available in February, 1981, and the Product Contract will be completed in March, 1981.

# COMPANY CONFIDENTIAL

This document contains confidential information on new products that should be disclosed only to those people engaged in the Program. Under no circumstances should any non-DEC persons be informed about any aspects of the Program or its existence.

Issued by: Vic Ku MR1-2/E47 Editor: Bill English MR1-2/F47

> 30 January 1981 Revision 3

digital

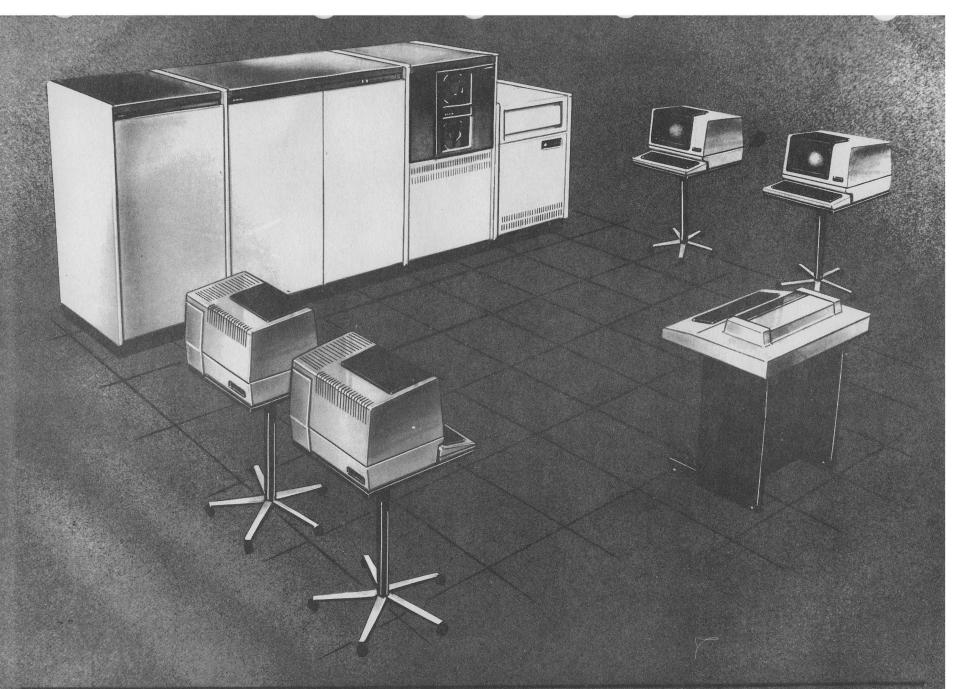

VENUS CI BASE SYSTEM

#### VENUS SYSTEM DEVELOPMENT PLAN

This plan presents an exposition of the intended course of the Venus Program. The first section is an executive summary that touches on the essentials of the plan. The next four sections explain what the system is, how it will be developed, how much it will cost, and how the objective of the development program - a marketable system - will be realized. The final section gives more detailed information about the functionality of the various parts of the system.

All of the information given in this plan is necessarily summary in nature, and is derived from the much more detailed plans and specifications the individual parts of the Program. These detailed documents are listed in Appendix Appendix B itemizes the capital equipment to be included in the Engineering breadboards Appendix prototypes. С lists the product requirements as defined by the Product Lines conjunction with Product Management and also gives Engineering's response to these requirements. Appendix D identifies all of the people associated with the Program. At the end is a glossary of the myriad mysterious combinations of letters that are tossed about with gay abandon.

The fundamental objective of the Program is to bring a competitive system to market as soon as possible. With this in mind, we developing an initial system based on the traditional Unibus for communications and unit record, and the new CI-HSC for mass storage (with use of the Massbus for a backup system). The CI project and its peripherals are well-enough along so we can be confident that a system based on it can be delivered in the timeframe set for the Program. The NI however is not yet at a sufficient confidence level - many projects are still only being planned. On the other hand, as soon as the initial system is wrapped up, the Venus design team will go to work on a mid-life kicker. involving not only conversion to NI but implementation of advanced packaging as well.

This plan has been approved by the Venus managers and supervisors whose signatures appear on the next page.

By signing this plan each of us indicates, in our best judgment, that

- I understand this plan and feel that I fully appreciate its implications both for myself and for the Venus Program;

- 2) I am aware of the expectations the Venus Program has of my group, and I am confident we can fulfill those expectations;

- 3) This plan fully addresses all expectations I have of the Venus Program, and I feel confident the Program can fulfill those expectations;

- 4) I am confident that, overall, the objectives of this plan are achievable in the timeframe indicated; and

- 5) I will communicate, in writing, to the Program Manager any specific reservations that I have about any item in the plan.

Engineering Group Manager George Hoff

Program Manager Vic Ku

Product Manager Carl Gibson

System Architect

Jud Leonard

CPU and Adapter Engineering Sas Durvasula

Peripheral Engineering John Bloem

Technology Engineering

Sultan Zia/Jim McElroy

Diagnostic Engineering

Dick Beaven/Dale Cook

VAX/VMS Engineering

Joe Carchidi/Chuck Samuelson

Customer Service

Walter Manter/Mike Robey

Manufacturing Charlie Bradshaw/John Grose

MCA/LSI Manufacturing

Ken Brabitz/Bill Walton

Qualification Engineering Ron Setera

Educational Services Ed McFaden

Site Engineering/Operations Roy Rezac/Nick Cappello SAM WITTED

( Post Cham C.A. Sen D

Malten De Stalten

Com Figure

The Alexander

# CONTENTS

| -       |      |            |            |         |           |              |                  |       |      |      |    |       |         |      |      |       |     |   |     |

|---------|------|------------|------------|---------|-----------|--------------|------------------|-------|------|------|----|-------|---------|------|------|-------|-----|---|-----|

| 1       | THE  | VEN        | IUS        | PR      | OGI       | RAM          | l                | •     |      |      | •  | •     | •       | •    |      |       |     |   | 1   |

| 1.1     |      | Pro        | gr         | am      | Pri       | ior          | it               | ies   | s a  | nd   | Н  | ligh  | nl io   | ht   | s.   |       |     |   | 1   |

| 1.2     |      | Why        | / V        | enu     | s?        |              | •                | •     | •    |      |    | •     | •       | •    | •    |       | •   | • | 8   |

| 2       | THE  | SYS        | TE         | M .     |           |              |                  |       |      |      |    |       |         |      |      |       |     |   |     |

| 2.1     |      | Ind        | ic         | <br>    | 020       | ,<br>, , , , | •                | •     | •    |      | •  | •     | •       | •    | •    | •     | •   | • | 12  |

| 2.2     |      | Log        | 701        | a       | OFC       | 911          | 12               | a t i | on.  |      | •  | •     | •       | •    | •    | •     | •   | • | 12  |

| 2.3     |      | L II A     | 2 T (      | cal     | U         | . qa         | $\mathbf{n}_{1}$ | zaτ   | :10  | n    |    |       | •       | •    | •    | •     | •   | • | 15  |

| 2.4     |      | Per        | Tbi        | ner     | аı        | Eq           |                  |       |      |      |    |       | •       |      | •    |       |     | • | 20  |

|         |      | So f       |            |         |           | •            | •                | •     | •    |      | •  | •     | •       | •    | •    |       | , , | • | 23  |

| 2.5     |      | Per        | IO:        | rma     | nce       | <del>)</del> | •                | •     | •    |      | •  | •     | •       | •    |      |       | , , | • | 24  |

| 2.6     |      | RAM        | P          | and     | Da        | ta           | I                | nte   | g r  | it   | У  | Fea   | tui     | es   | •    | •     | , , | • | 28  |

| 3       | DEV  | ELOP       | TNO        | ን ጥ     | HE.       | SV           | <b>ድ</b> ሞነ      | ЕM    |      |      |    |       |         |      |      |       |     |   | 2 1 |

| 3.1     |      |            |            |         |           |              |                  |       |      |      | •  | •     | •       | •    | •    | •     | •   | • | 31  |

| 3.2     |      | Dev<br>Dev | ٥١،        | 2 Day   | 011 t     | . D          | C L C            | 3 L E | У У  |      | •  | •     | •       | •    | •    | •     | •   | • | 31  |

| 3.3     |      | Dha        | CI         | De.     | ent       | . 1          | 00.              | LS    | •    |      | •  | •     | •       | •    | •    | •     | •   | • | 37  |

| 3.4     |      | LIIG       | -3 C       | ve      | νте       | : w          | •                |       | _    |      | _  | _     | _       | _    |      |       |     | • | 39  |

|         |      | FIO        | ar c       | 3 III   | IIa       | CK           | 1 no             | a a   | na   | Mid  | דו | or    | $M_{1}$ | est  | on   | 65    |     |   | 40  |

| 3.5     |      | RIS        | KS         | and     | a L       | e p          | enc              | den   | Ci   | es   |    |       |         |      |      | _     | _   |   | 45  |

| 3.6     |      | TIM        | e i        | co i    | ma r      | Ke           | t,               | Sy    | st   | em   | C  | onf   | iqu     | ırat | io   | n,    |     |   |     |

|         |      |            | and        | i Si    | upp       | or           | tec              | i P   | er   | ipl  | ìе | ral   | s       |      |      | ٠.    |     |   | 49  |

|         |      |            |            |         |           |              |                  |       |      | -    |    |       |         |      | _    |       |     |   |     |

| 4       | COST |            | •          | •       |           |              |                  |       |      |      |    | _     |         | _    | _    |       |     |   | 52  |

| 4.1     |      | Dev<br>Man | elo        | ma c    | ent       | C            | ost              | _     |      |      |    | •     | •       | •    | ٠    | •     | •   | • | 52  |

| 4.2     |      | Man        | ufa        | acti    | ıri       | na           | Cc               | ) st  | •    |      | •  | •     | •       | •    |      | •     | •   | , | 55  |

| 4.3     |      | Lif        | e (        | יער:    | <br>ا م ا |              | c+               | ,     | •    | •    |    |       |         |      | •    | •     | •   |   |     |

|         |      |            |            | - y C . | 1.0       | CU           | JL               | •     | •    | •    | •  | •     | •       | •    | •    | •     | •   |   | 58  |

| 5       | SYST | EM         | REA        | LIZ     | ZAT       | IOI          | N S              | STR   | AΤΙ  | EGI  | E. | 5     |         |      |      |       |     |   | 59  |

| 5.1     |      | Man        | ufa        | cti     | ıri       | na           | St               | ra    | + 60 | 1 17 |    |       | •       | •    | •    |       | •   |   |     |

| 5.2     |      | Doc        | k N        | lero    | 10        | 9            |                  | - L U | CC   | 3 X  |    | •     | •       | •    | •    |       | •   |   | 59  |

| 5.3     |      | Doc        | n .<br>Iif | ice     | )         | a n          | •<br>D]          | •     | •    | •    | ı  | •     | •       | •    | •    |       | •   |   | 6g  |

| 5.4     |      | Qua        | ~ ~ ~      |         |           | CT.          | P 1              | an    | •    | •    |    | •     | •       | •    | •    | •     | •   |   | 62  |

| 5.5     |      | Dia        | 9110       | SC.     | r C       | St!          | rat              | eg    | y    | •    |    | •     | •       | •    | •    | •     | •   |   | 63  |

| 5.5     |      | Cus        | COI        | ıer     | Se        | rv           | 1Ce              | P     | lar  | n .  |    | •     | •       | •    |      |       | •   |   | 65  |

| 6       | FUNC | TIO        | NA I       | . CI    | HAR       | AC.          | ref              | RIS   | TIC  | cs   |    | _     | _       |      |      |       |     |   | 68  |

| 6.1     |      | CPU        | Cl         | ust     | er        |              | _                | _     |      | _    |    | •     | •       | •    | •    | •     | •   |   | 68  |

| 6.2     |      | Per        |            |         |           |              |                  | •     | •    | •    |    | •     | •       | •    |      |       | •   |   |     |

| 6.3     |      | Sof        |            |         |           |              |                  |       |      |      |    |       |         |      | •    |       | •   |   | 7Ø  |

| 6.4     |      | Tecl       |            |         |           | •            | •                | •     | •    | •    |    | •     | •       | •    | •    | •     | •   |   | 72  |

|         |      | 160        | 11110      | 109     | ΙΥ        | •            | •                | •     | •    | •    |    | •     | •       | •    | •    | •     | •   |   | 74  |

| 7 n n a |      |            |            |         |           |              |                  |       |      |      |    |       |         |      |      |       |     |   |     |

| Appe    | ndic | es         |            |         |           |              |                  |       |      |      |    |       |         |      |      |       |     |   |     |

| Α       | Syst | em 1       | Rel        | ate     | d         | Pla          | ns               | aı    | nd   | Sp   | ec | if    | ica     | tio  | ns   | _     | _   |   | 80  |

| В       | Brea | dboa       | ard        | /Pr     | ot(       | ots          | /pe              | Ca    | api  | ta   | 1  | Eat   | nip     | men  | †    |       | •   |   | 82  |

| С       | Prod | uct        | Re         | qui     | rei       | mer          | its              |       | En   | a i  | ne | eri   | i na    | Re   | Sno  | nne.  | •   |   | 85  |

| D       | Who' | s Wh       | าด         | in      | the       | <br>         | /en              | 115   | Pr   | שה.  | ra | m     | •       |      | 2 PC | ,1126 | •   |   |     |

|         |      |            |            |         |           | - '          |                  |       |      | ~9   |    | . 441 | •       | •    | •    | •     | •   |   | 93  |

| Glos    | sary | •          |            | •       | •         |              |                  | •     |      |      |    | •     |         |      |      |       |     |   | 98  |

#### THE VENUS PROGRAM 1

This section summarizes the elements of the Program and explains why Venus is the best candidate to carry the Digital logo at the high end of the VAX line. Here elsewhere in this plan, the discussion of schedules and commitments employs such terms as FRS and FVC; these terms are explained in the Glossary.

#### PROGRAM PRIORITIES AND HIGHLIGHTS

At the core of the Program is an engineering development plan organized around a set of priorities or overall goals. Within the framework of these goals, we have defined a product using state-of-the-art technology.

# Program Priorities

The development strategy is geared to these goals listed in order of importance to the Program.

Maximize customer satisfaction (superior to comparable IBM systems)

Minimize life cycle cost

Cost of ownership less than comparable 11/780 systems (we believe we are achieving this, but the model is unclear)

Meet transfer cost targets: comparable to equivalent 11/780 systems (\$73K for the CI Base and < \$52K for the IDTC Base defined on the next page vs. \$48K for the VAX11/78ØSV-AXCVA)

Maximize price/performance gain over 11/780 times 11/780 performance except floating point timing without FPA)

IO architecture based on new Corporate interconnects (CI at FRS, NI on Unibus as soon as possible)

SBI capability for 11/780 migration

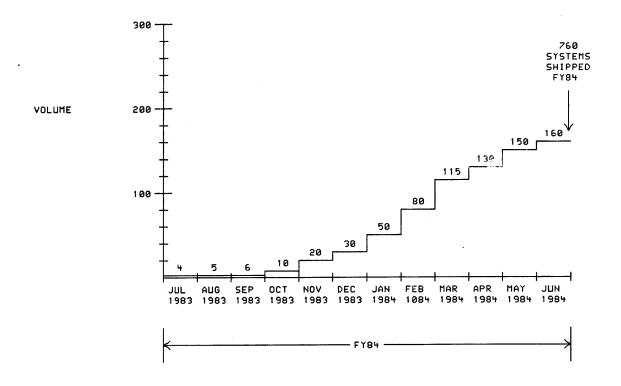

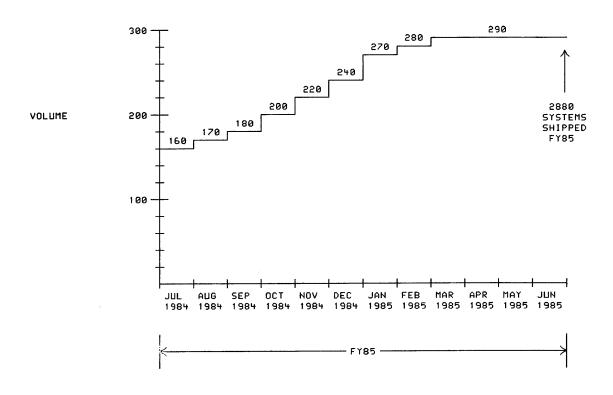

FRS by 7/83; total number of systems shipped in first two years: 760 in FY84, 2880 in FY85

Full-featured system to ship no later than nine months after FRS of initial midrange system

Design system for maximum dock mergeability

Maximize RAMP features

Minimize development cost

Naturally these various goals conflict with one another. A significant part of the decision making reflected in this document and that will be exercised thoughout the development is determining what tradeoffs to make among these goals to create the most viable product.

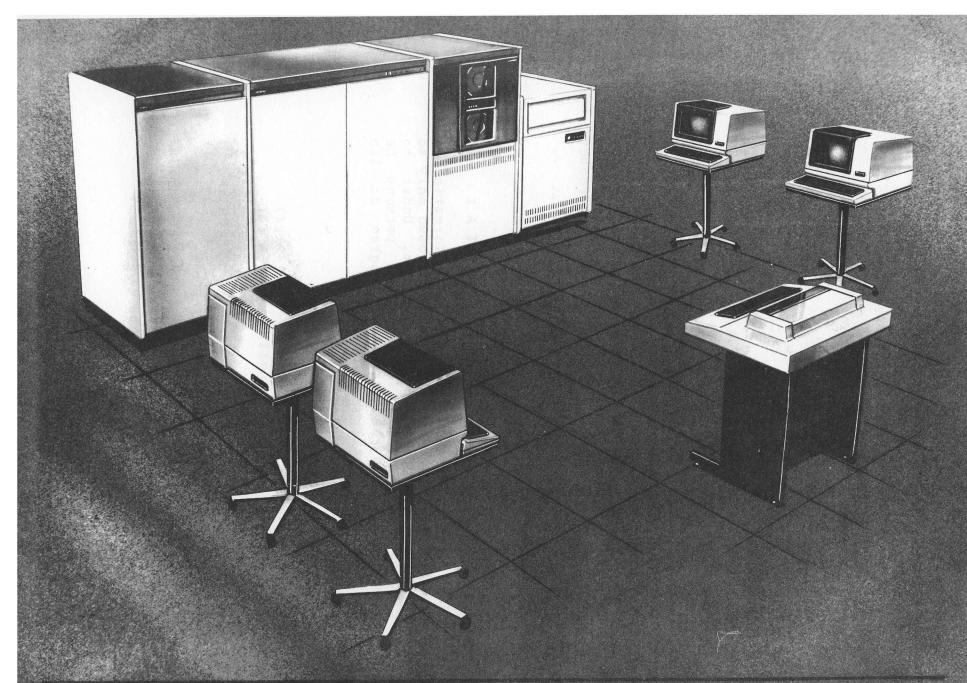

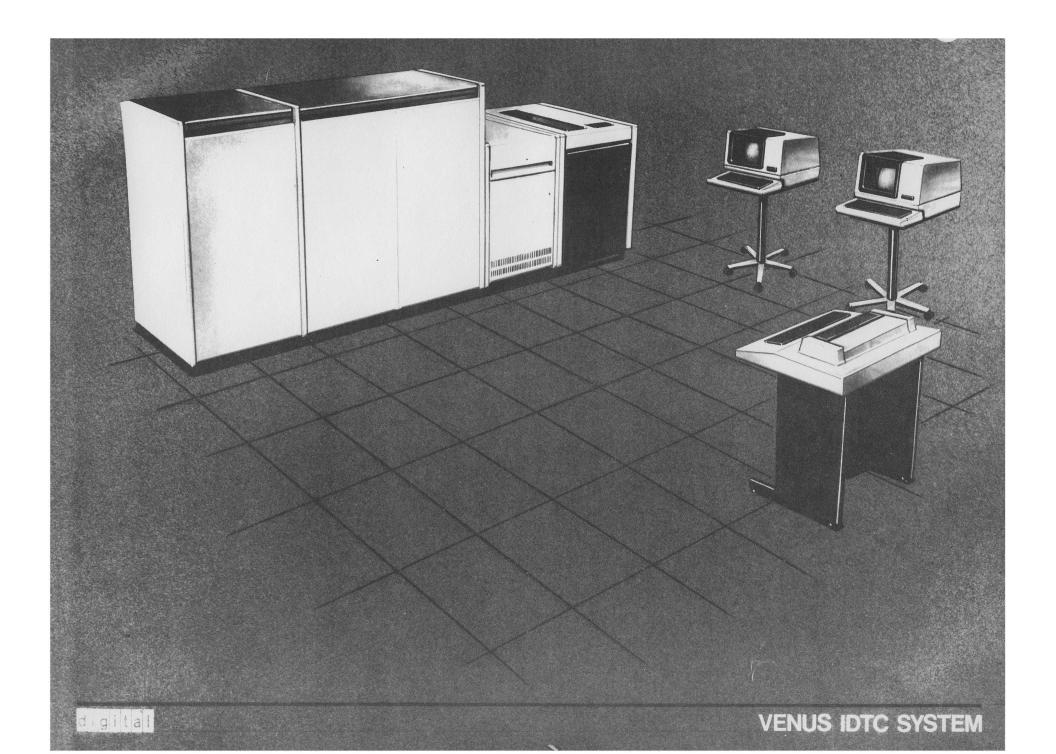

# System Definition

Listed here are the fundamental constituents of the three categories of system upon which the Program is based. The CI Base defines the principal system configuration and is expected to be the basis for all midrange and larger systems. The IDTC Base, which Marketing may not make available until almost a year after FRS so as not to compete with the 11/780, has a disk-tape controller within the CPU cabinet and is the basis for the smaller systems, although it too is expandable. Note that the integrated disk-tape controller is composed of current products - DW780 and UDA50 - just with new packaging and a special backplane; it involves no new hardware, and no new VMS software is needed. The Massbus Base is a backup at FRS for the CI-based systems, and it will be available months later for 11/780 upgrade. Note that the DZ730, the "Combo" board, has controllers for eight asynchronous lines, one synchronous line, and one line printer; which controllers are actually used depends what other equipment is attached and what arrangements are made in terms of distribution panels for the various lines. All three system types in turn contain a set of common elements that we shall first define as the "CPU cluster".

# CPU cluster

Processor (including power)

1 LA120 console terminal

1 RL02 console load device

1 megabyte of MCS memory

1 SBI adapter (SBIA)

1 DW780 Unibus adapter

1 DZ730 Combo (8 asynchronous lines)

#### CI Base

CPU cluster

3 additional megabytes of MOS memory

1 additional DZ730 (16 asynchronous lines total)

1 CI780 CI adapter

1 HSC50 controller

1 RA81 disk

1 TA78 tape

# IDTC Base (Integrated Disk-Tape Controller)

CPU cluster

1 DW780-UDA50 integrated disk-tape controller

(4 disk ports and 1 tape port)

1 Pinon or RA81 disk

1 LCGCR tape

# Massbus Base

CPU cluster

1 additional megabyte of MOS memory

1 additional DZ730 (16 asynchronous lines total)

2 RH780 Massbus adapters

1 RP07 disk

1 TM78-TU78 tape

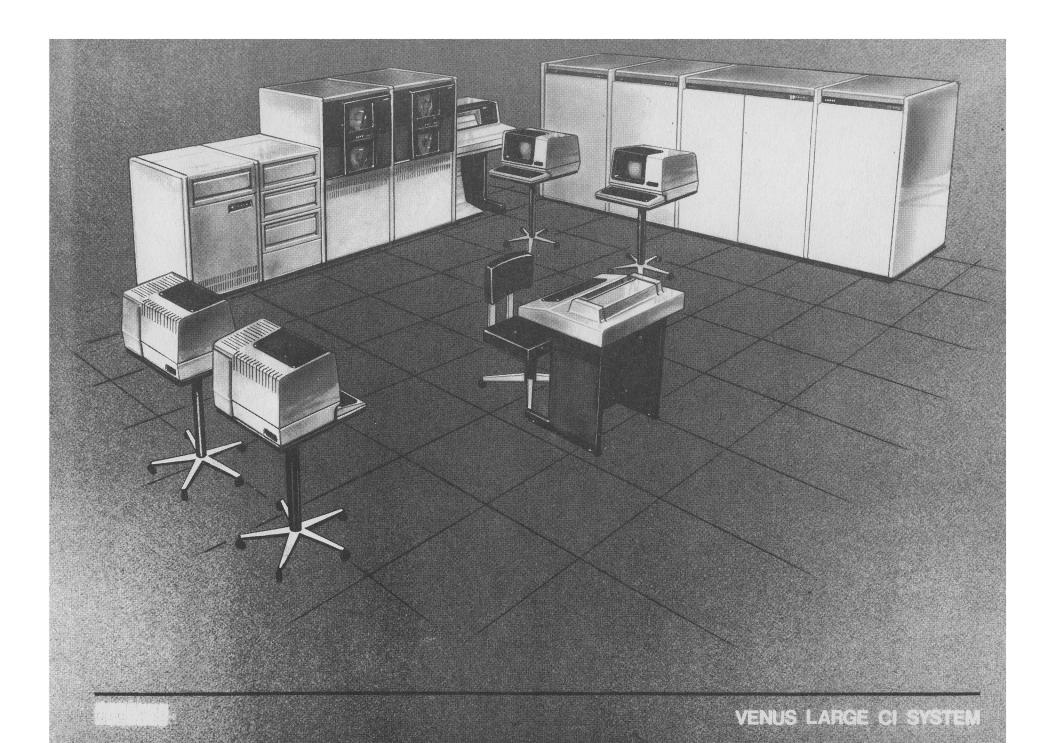

From these basic configurations, the Venus Business Plan defines a number of dock-mergeable packaged systems for handling the largest volume markets at the lowest cost. Unless otherwise specified, information in the present document pertains generally to the CI Base and systems containing it. The term "system base" refers to the base of any type of system.

The basic DMT system is the CI Base minus disk and tape. The CPU kernel (for DMT and similar purposes) is the processor plus 1 MB of memory.

# Program Highlights

The System

High Availability

CPU cluster - 99.5%

System base (including software) - 98.5%

No more than 1 software crash per month

MTBF (mean time between failures)

In each case the second number is the MTBF perceived by the customer, taking into consideration the fault tolerance of the CPU kernel and scheduling maintenance during off time. Figures include field performance data for the LA120 and RL02, but in Venus these devices will have a lower duty cycle, which will increase the MTBF somewhat.

CPU kernel (DMT) - 1790/1967 hours CPU cluster - 895/943 hours CI Base - 411/423 hours IDTC Base - 597/618 hours Massbus Base - 463/476 hours

Hydra-type system configuration possible (Venus satisfies the established criteria for use as a node in Hydra, although no qualification plan has yet been developed)

System MTTR - 3 hours; MDT - 5 hours

System installation and acceptance < 48 hours

Warranty cost: CPU cluster - \$5823 CI Base - \$14,399 IDTC Base - \$9519 Massbus Base - \$15,799

Maintenance cost (at 20th quarter of shipments) CPU cluster - \$401 per month CI Base - \$1237 per month IDTC Base - \$689 per month Massbus Base - \$965 per month

BMC (basic monthly charge) - TBD in Phase 2

Advanced RAMP features

Instruction retry

digital

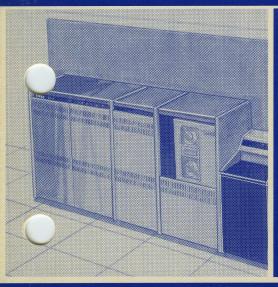

VENUS CI BASE SYSTEM

Multiplexers built into terminator chips for diagnostic inspection of all backplane signals

Diagnostic resolution to module in at least 95% of solid failures; resolution to chip level for RAM failures

All MCA chips and most RAMs mounted in sockets to allow field replacement

Integrated, intelligent maintenance/operator

console (T-11 based)

Loopback diagnostics for IO controllers

User mode diagnostics

Etch backplanes (> 90%)

Early warning on low voltage/high temperature

Power fail recovery

Remote diagnostic link

Battery backup on time-of-year meter (100 hours) and memory (10 minutes)

# The Technology

Press pin, multilayer, controlled impedance backplanes (16 layers)

8-layer, controlled impedance L-type modules (4 signal layers)

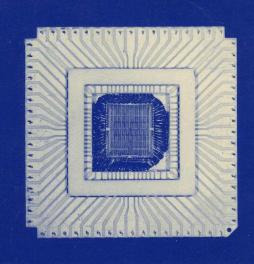

Macrocell arrays (MCA) - Motorola Mosaic I ECL gate array LSI technology

Digital Hudson plant second source for MCAs

ECL 10K MSI/SSI chips

Air cooled

Individual heat sinks mounted on each MCA

1K and 4K ECL RAMs

64K MOS memory chips (16K backup for breadboard)

Corporate "switching regulator" modular power supplies

The Product

High end VAX system - corresponds exactly to the VAX architecture defined in the VAX System Reference Manual (DEC Standard 32); the AXE program, VMS and layered products will be used to verify the architecture

Supplements the VAX11/780 RP06-TE16-based system (codes SV-AXCVA-LA and LD) and all larger 11/780 systems; it will be the primary offering for applications requiring greater than 1 MB of memory and 200 MB of disk

Many configurations dock mergeable

Absolute compatibility with VAX/VMS and layered software products for equivalent hardware (at present the medium for software distribution is an open issue, and a task force is investigating the matter vis-a-vis the entire VAX family)

16K byte writeback cache with ECC

4 times VAX 11/780 performance

Instruction byte prefetch

Custom register file for A bus adapters

8K writable control store (there is no WCS option, but 1K is available to the user with limited support comparable to that on 11/78%)

Optional floating point accelerator, 4 times  $11/78\mathfrak{C}$  FPA performance

MOS memory in 1 MB increments to 32 MB (8 at FRS)

Memory data register chip

Supports new CI interconnect - in fact the Program depends on the CI for HSC50 and Hydra

3 taps on adapter bus: 2 for SBI adapters and 1 (single slot) for Product Lines or special equipment (second SBI available 3 months after FRS)

VMS support for Venus Processor initialization, error handling, IO adapters and console

Supports PDP-11 compatibility mode

High volume fabrication, assembly and test

Optimized cooling/packaging for class A environment (air conditioned, 15-32 degrees C, relative humidity 20-80%; raised floor prefered but not necessary

Meets or exceeds requirements of DEC Standards 60 and 102, including RFI/EMI, UL, CSA, IEC, VDE (we are also working with the Corporate Central RFI/EMI Group to ensure compliance with new FCC regulations)

Power consumption

CPU cabinet: 5.2 kW, 17,700 Btu/hour, 8.7 kVa (CPU, FPA, 8 MB, console, 1 SBIA, 2 DW780s, CI780)

Unibus-console cabinet: .8 kW, 2700 Btu/hour, 1.3 kVa (RL02, BA11, 2 DZ730, etc)

Memory expansion cabinet with 24 MB: 2.5 kW, 8300 Btu/hour, 4.1 kVa

System fully DMTed and PMTed

Meets or betters European noise standard (60 dbA), and we will deal aggressively with vendors concerning noise requirements for peripherals

Will provide a strong functional base for:

High end real time

Foreign device connect

Transaction processing

Timesharing

Batch

Distributed processing

Distributed data base management

When and How Much?

The individual Venus managers and supervisors have identified the various tasks and events that make up the overall Program and have determined reasonable schedules for implementing them. Combining these schedules, taking into account the interdependencies among them, results in these dates that guide the Program.

CI Base FRS July 1983

Transfer cost: \$73K

Floating Point Accelerator FRS July 1983 Transfer cost: \$3.5K Massbus Base FRS January 1984 Transfer cost: < \$71K Backup July 1983

Dual SBI System FRS October 1983 Transfer cost: configuration dependent

Memory Expansion Box FRS January 1984

Transfer cost:

Up to 12 MB: \$6900 + \$2004/MB More than 12 MB: \$7900 + \$2004/MB

IDTC Base FRS May 1984 Transfer cost: < \$52K

The current schedules for the CI780, HSC50 and CI peripherals support the given FRS date for the CI Kernel. However, four to six quarters before FRS, the status of these projects will be reviewed, and a decision will then be made whether to continue on the present course or switch to the backup system. If the latter becomes necessary, we will natheless endeavor to bring out the CI system as soon as possible, depending on availability of the needed options.

It should be noted that the above are the times at which the Program will have the various products ready for FRS. Because of Marketing considerations however, Product Management may in some cases prefer actually to make them available at a later time.

# 1.2 WHY VENUS?

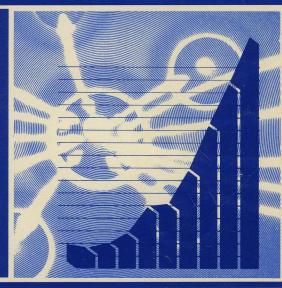

In every category - from market suitability to customer satisfaction, from cost/performance to expansion capability - Venus is the computer for the high end of the VAX line in the mid-Eighties. It is also consistent with the Corporate strategy of settling principally on a 32-bit architecture by 1985.

#### Leadership

In terms of performance, availability, cost of ownership, and range of applicability, Venus is a major stride both within Digital and in the industry as a whole. These exceptional improvements are due to use of state-of-the-art Mosaic I ECL array technology.

Venus will be the most powerful system in Digital's VAX product offering, with higher availability and lower cost of ownership than any comparable Digital system. With the layered

software products planned for delivery in the early Eighties, Venus will meet the needs of a broad range of technical, commercial, and special-application customers. By incorporating the latest technology in hardware and software, Venus will bring "people oriented" computing to performance levels never attained before.

# Cost/Performance

Venus-based systems will exceed the 22% per year cost/performance improvement shown by the computer industry as a whole. Thus in raw cost/performance terms, Venus can be expected to be as competitive in the mid-Eighties as the 11/780 is today; furthermore, in functionality terms, our large software development for VAX systems will make Venus systems even more attractive.

#### Performance

On computation-limited workloads, Venus will have 4 times the throughput of a comparable 11/780. On IO-limited workloads, the improvement will depend principally on the capability of the HSC50. Within the mechanical constraints (and most IO limits are mechanical), the SBI-CI-HSC50 subsystem is capable of considerable data-transfer optimization; but beyond this, the HSC50 also has features for optimizing the mechanical operations of the disk itself.

#### Cost

The cost of ownership of Venus systems will be equal to or better than comparably configured 11/780 systems. "Comparably configured" means that Venus main memory and disk capacity are three to four times that of "comparable" 11/780s. We expect to reduce FA&T costs by dock merge of many systems and offering packaged systems, and to minimize cycle cost by careful design of the system, life its RAMP features, and our service manufacturing strategies. As an example the total CPU cluster warranty and maintenance cost for a representative sample of 13,710 systems will range from \$91.6 to \$102 million depending on the extent to which sockets are utilized. Hence maximum socket use will save \$10.4 million over the life of the product.

# Market Suitability

Venus will span two very different market places: as a small mainframe, it will be comparable in performance to a 370/168; as a high end minicomputer, it will pick up the real time, interactive, and distributed processing applications as they grow to higher throughput requirements. Although initially most appropriate to midrange scientific computation markets, Venus will be able to take full advantage of VAX/VMS software efforts to penetrate commercial ADP applications. Over its life, Venus is expected to be installed in roughly as many commercial as scientific applications.

#### Timeliness

The 11/780 is presently under fire from many directions - the IBM 4331 and 4341 (and to-be-announced low-end H-series system), the Interdata 3240, and expected offerings from DG, SEL and HP are all aggressive products in the 11/780 market space. Venus's market introduction in 1983 will provide Digital with a resource to meet these challenges.

# Flexibility

While Venus's high marks in performance, cost and other characteristics make it an excellent instrument for attacking new markets and attracting new customers, its compatibility not only with VAX/VMS and all VAX layered software products, but also with the PDP-11 will make it exceptionally attractive to present customers for upgrading and networking.

#### Customer Satisfaction

Low component count, design that anticipates exceptional conditions, and extensive checking circuitry give Venus high inherent reliability. Ride-through strategies to survive transient errors help minimize vulnerability to intermittent failures, and error logging gives Customer Service the information to locate and repair such faults. The diagnostic logic supports module-level fault isolation, and in many cases isolation to chip level. These and other RAMP features contribute directly to customer satisfaction, as does the resulting lower life cycle cost.

# Interconnectability

Venus will interface to existing and anticipated applicable Corporate interconnect mechanisms. Easy access to traditional Unibus and Massbus devices will be available.

# Multicomputing

Venus processors can be loosely coupled via the CI, e.g. the Hydra configuration. With full exploitation of the Corporate interconnect strategies, Venus can lead the real computer revolution of the Eighties - using arrays of \$350K machines to solve multimillion dollar problems.

#### 2 THE SYSTEM

A Venus System is more than just hardware - it is also the software that makes the system go, and its performance characteristics and RAMP features, all of which we consider here.

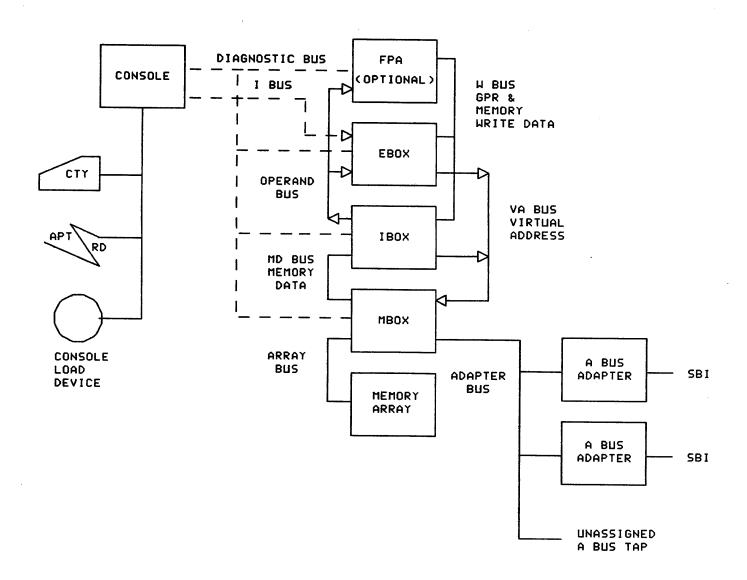

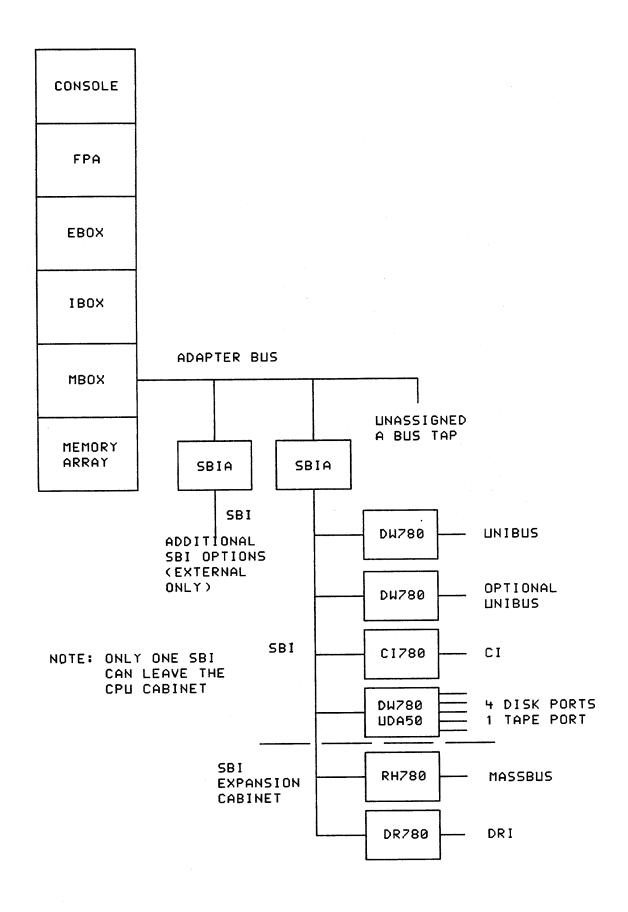

#### 2.1 LOGICAL ORGANIZATION

In the block diagram of the central part of the system, Figure 2.1, the processor comprises the five blocks interconnected by the diagnostic bus: the single block in the upper left and the upper four blocks in the center column. These four blocks represent the instruction or I box, the execution or E box, the floating point accelerator FPA (also called the F box), and the memory control or M box. The last of these provides the connecting link to both memory and the IO subsystem, whereas the upper three blocks comprise the "processing" part of the processor.

The heart of the entire system is the instruction which receives the instruction stream of bytes from memory, and from it determines what information to retrieve and what activity to initiate in the E box. The execution of each instruction is done in four stages, with the I box handling the first three: fetching the instruction, calculating required addresses, and fetching the operands. It then turns the execution of the instruction over to the E box, but at the same time it helps to speed up overall operation by starting to work on the next instruction. The E box, based on a binary/BCD ALU, carries out whatever logical, arithmetic and other operations are required to execute the instruction, after which it sends to the I box any results that are to be written in memory. If the optional FPA is included, the E box uses it to speed up the execution of floating point instructions, but from the point of view of the I box, the FPA is simply an extension of the E box. Basic to

FIGURE 2.1 VENUS PROCESSOR LOGICAL ORGANIZATION

the accurate and fast manipulation of data are the general purpose registers (GPR), of which each of the three boxes has one or two sets of sixteen. Altogether five copies of the GPRs are kept to guarantee very fast and flexible access and instruction retry.

Interconnecting the various boxes are a number of buses. All movement of data between the processor and both the memory array and the IO subsystem occurs via the MD bus that connects the M and I boxes. Over this bus the I box receives the I stream and the memory operands. It passes the latter on to the E and F boxes over the operand bus. Results from either of these boxes are sent via the W bus to the I box, which in turn passes them on to the M box over the MD bus. The W bus is also used for keeping the five sets of GPRs identical to one another. Both I box and E box can supply addresses (almost always virtual) over the VA bus to the M box. All buses and registers handle 32-bit longwords.

Also contained in the processor is a microprocessor-based console, which is connected to all four of the boxes by a serial diagnostic bus. console provides the system clock, a time-of-year clock, and environmental monitoring. Associated with the console are a local LA120 terminal for use by the operator, an RL02 removable disk (mounted in the Unibus cabinet) for bootstrapping and diagnostic activities, and a remote diagnostic link which can be utilized by an APT window. Bootstrapping is done by the console passing initializing and setup information in bytes to the various boxes over the diagnostic bus. The 8K x 84 bit control store for the microcode is the E box, but each of the other boxes has a small control store to hold special microcode for its own operations. Also connecting the console to the E box is the C bus for communicating with the software and performing console funnctions.

The M box includes a 16K-byte data cache, error detection and correction circuits for the cache and memory array, and microcode-driven control logic for governing communication with the IO subsystem as well as handling memory. The control part includes special byte write logic to speed up the insertion of bytes in longwords, and refresh logic for the MOS RAMs in the array. Connection to memory is via the array bus, and to the IO subsystem via the adapter or A bus. Each array board contains one MB of MOS storage; a typical memory is one to eight MB, with expansion to 32 MB possible. It is expected that within two years after FRS, memory density will improve by a factor of four (the addressing capability of the processor hardware is 512 MB). On the A bus are adapters for one or two

SBIs. IO bandwidth is significantly increased over 11/780 by removing all CPU-memory traffic from the SBI. There can be no SBI memory, and there is no support for a device like the MA780.

Although the FPA is optional and memory size variable, most variation from one system to another occurs in the IO subsystem. Such variation is considerable, including both the interconnects and a large variety of peripheral equipment, but in general system configurations are of two fundamental types, based either on the CI Base or the IDTC Base. basic constituents of these systems are shown in Figure 2.2. Available initially will be systems built on the CI Base, where the IO subsystem has an SBI with units that interface to a Unibus and a CI. The latter has fifteen nodes that allow connection to HSC50 disk or tape systems, and to other computers in multicomputer system. For a smaller scale system, the IDTC Base has a DW780-UDA50 disk-tape controller in place of the CI780. Either system can have a second Unibus adapter in the CPU cabinet; more adapters, including the RH780 and DR780, can be added outside the cabinet; and a second SBI can be installed the external adapters and thus share the load. The Massbus Base, which is the backup system, has DW780s in the CPU cabinet, and requires an expansion cabinet to accommodate the Massbus adapters.

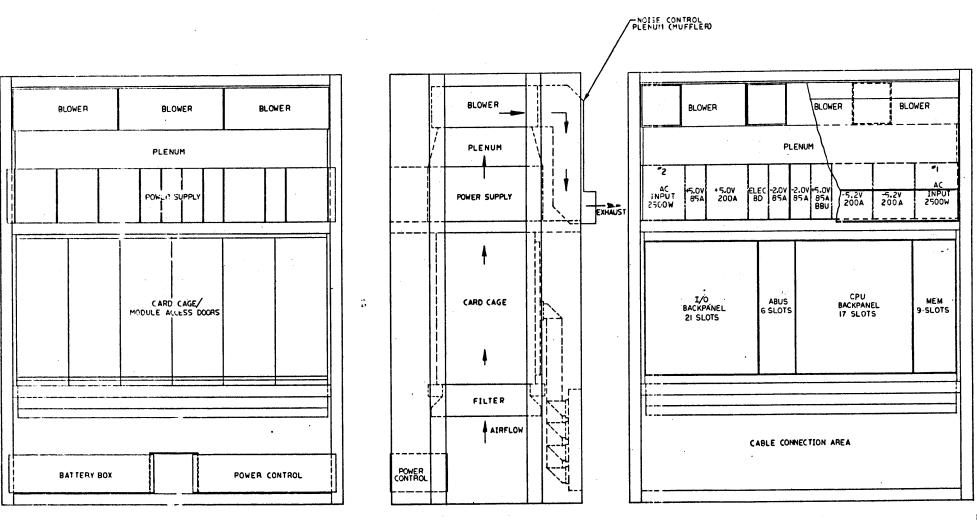

# 2.2 PHYSICAL ORGANIZATION

Figure 2.3 shows the physical layout of the CPU cabinet. In terms of general organization - position of backplanes, power supplies, cables, blowers and the like - the layout is the same for all systems. Viewed from the front, the left half of the module area is a single CPU card cage containing two backplanes for memory and processor, both implemented in L-type modules. The left backplane accomodates eight memory array boards of one MB each. Beside the memory is the processor, which if the optional floating point accelerator is included, requires seventeen modules.

| CPU Box                                                  | Number | of                         | Modules |

|----------------------------------------------------------|--------|----------------------------|---------|

| I box E box System clock Control store M box FPA Console |        | 3<br>4<br>1<br>2<br>3<br>3 |         |

| Console                                                  |        | 1                          |         |

FIGURE 2.2 BASIC SYSTEM CONFIGURATION

FIGURE 2.3 CPU CABINET CONFIGURATION

.SIDE VIEW

FRONT VIEW

REAR VIEW

BACKPLANE "PIN SIDE" SHOWN

Modules with MCAs are one inch apart, those without use half-inch spacing.

The right half is also a single card cage containing the small A bus backplane and the larger IO backplane; this entire cage could be replaced for special applications or to make way for a mid-life kicker. The A bus backplane (on the left) has space for two SBI adapters of two L modules each (the first SBIA is plugged in at the farther end from the processor), and a spare slot for the third A bus tap. IO backplane accomodates a mixture of extended hex and L modules for the adapters on the internal SBI. This backplane contains one DW780, space a second, optional DW780, and either a CI780 CI adapter or a DW780-UDA50 integrated disk-tape controller (although there is nothing to prevent a single system having both should that be desired). Any adapters beyond these must be mounted outside the CPU cabinet; such adapters can include the DR780 and RH780 (standard in Massbus systems) as well as those available in the CPU cabinet. In any system a single can handle all adapters, or a second SBI can be added to handle the external ones (i.e. only one SBI can leave the CPU cabinet).

In systems built for shipment outside the United States and Canada, there will be a 10 kVa transformer to interface with the numerous variations in available utility voltages. This transformer is mounted at the bottom of the Unibus-console cabinet at the left of the CPU cabinet. Voltage conversion requirements for Unibus expansion cabinets, SBI expansion cabinets and the like will be handled in the fashion determined by the groups responsible for their design.

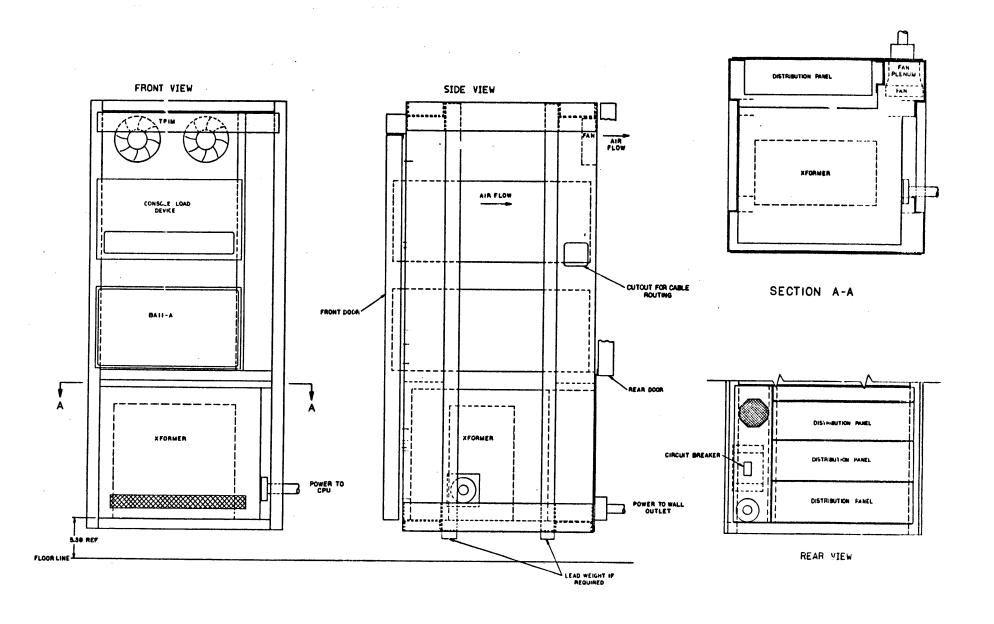

### Cabinet Arrangements

Every system that has no more than 8 MB of memory has Unibus-console cabinet attached to the left side of the CPU cabinet viewed from the front. Besides typical Unibus communication and unit record controllers, this cabinet (Figure 2.4) contains the console load device the stepdown transformer wherever that is necessary. If additional Unibus cabinets are required, they are bolted on at the right. If external adapters are needed, they are installed in one or two SBI expansion cabinets (four per cabinet) attached at the right of the CPU cabinet, between it and additional Unibus cabinets. Cabinets for Unibus disks and tapes are attached at the far right. CI and Massbus devices can be attached at the right or placed separately elsewhere in the computer room.

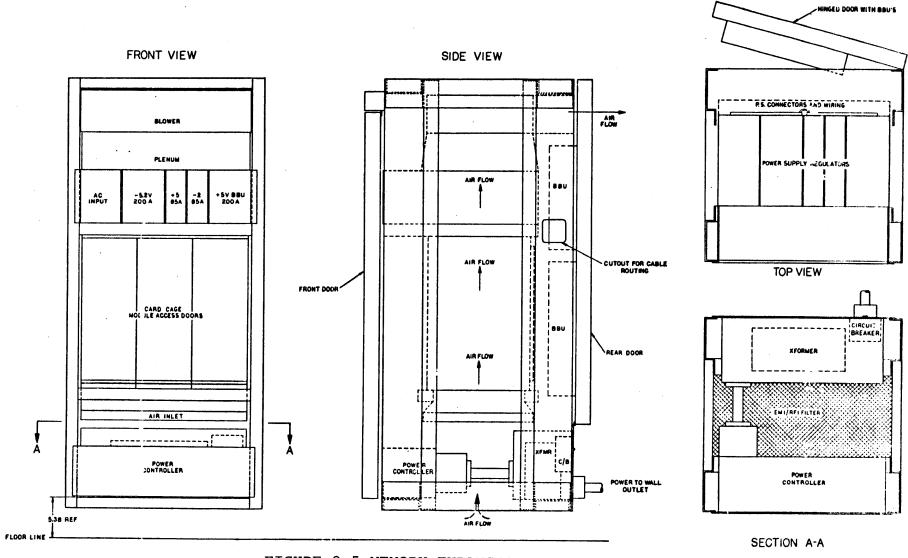

FIGURE 2.4 UNIBUS-CONSOLE CABINET CONFIGURATION

Should memory expansion beyond 8 MB be desired, a expansion cabinet (Figure 2.5) must be installed at the left between the CPU cabinet and the Unibus-console cabinet. This can accommodate an additional 24 memory boards bringing total memory capacity to 32 MB. It is expected that within the next few years, memory density will quadruple with introduction of 256K MOS RAMs. At that time Venus will convert to 4 MB memory array boards, so the CPU cabinet can accommodate 32 MB of memory, and expansion to 128 MB will then be possible. Where required, a  $\,\,$ 5 kVa stepdown transformer for the additional memory is installed at the bottom of the cabinet.

# 2.3 PERIPHERAL EQUIPMENT

The peripheral equipment includes both new and current products in all categories: interconnects, adapters, controllers, and individual IO devices.

# Interconnects

Venus configurations are based on system interconnects reflecting Corporate strategies. The characteristics and status of these interconnects are given below; all have high data integrity and provide appropriate electrical isolation.

- SBI Synchronous Backplane Interconnect present VAX interconnect to Unibus, Massbus and other adapters; high bandwidth, medium cost.

- CI Computer Interconnect joins loosely coupled computers, and mass storage, real time and communication subsystems; high bandwidth, 16 nodes; under development

- SI Storage Interconnect joins disk and tape drives to controller; high bandwidth; being tested (the principal Venus version of the SI is the SDI standard disk interface and several disk projects are being based on it).

- NI Network Interconnect joins computers, work stations, intelligent terminals, etc in local network; moderate bandwidth, moderate number of drops; currently being defined.

FIGURE 2.5 MEMORY EXPANSION CABINET CONFIGURATION

# Adapters

These interface the A Bus to the SBI or the SBI to subsidiary interconnects such as the CI and Unibus.

SBIA SBI adapter on A bus, scheduled and funded.

DW780 Unibus Adapter - current product.

CI780 CI adapter, scheduled and funded.

DR780 High Speed Block Transfer Port for customer equipment or CPU-CPU communication; current product.

RH780 Massbus Adapter - current product.

# Controllers

Two major controllers are expected to be utilized in the Venus system. Minor controllers, such as for unit record equipment, are included with the devices themselves.

HSC50 Hierarchical Storage Controller - intelligent mass storage controller on the CI; contains six subcontrollers for SDI disks and tapes; unit has many RAMP and high-performance features; project funded with FRS scheduled for Q4/FY83.

UDA50 Intelligent mass storage controller on the Unibus; contains four subcontrollers for SDI disks; some RAMP and high-performance features; project funded with FRS scheduled for Q2/FY82.

# Recommended IO Devices

Following are those products we strongly feel should be developed for Venus. Current products we intend to support are listed at the end of Section 3.6.

Pinon removable disk on SDI, 180 MB capacity.

RA81 fixed disk on SDI, 400 MB capacity, 3 MB per second maximum transfer rate.

TA78 tape, 1600/6250 bpi, 125 ips, HSC50 controller.

LCGCR tape on Unibus, 1600/6250 bpi, 75 ips.

TU78 tape, 1600/6250 bpi, 125 ips, TM78 controller on Massbus.

#### 2.4 SOFTWARE

As far as the software is concerned, the most important thing to keep in mind is that Venus is a VAX processor, that its operating system is VMS, and that there is only one version of VMS for all VAX processors. VMS development operates under fundamental requirements: that no matter what processor the single version of VMS is booted on, it shall be capable of configuring the support for that processor automatically and transparently; and that a user program or higher level system program that runs on any VAX processor shall run on all. As shown by the examples in the chart below, the many elements that constitute the complete VAX software package are organized into three layers that are superimposed or built upon the VAX hardware.

| Unbundled<br>(Layered)<br>Products | DBMS<br>Fortran<br>Coral-66                      | Datatriev<br>Basic<br>Ada | ve<br>Cobol<br>APL | Pearl<br>Bliss<br>Pascal                     |

|------------------------------------|--------------------------------------------------|---------------------------|--------------------|----------------------------------------------|

| Bundled<br>Products                | DECnet Linke<br>Error Log An                     |                           |                    | tch SYSGEN<br>me Library                     |

| Executive                          | Scheduler De<br>IO Adapter Su<br>Processor Error | pport                     | Memory             | stem Services<br>Management<br>nitialization |

#### VAX Hardware

In this structure, the bundled products are those programs that are intimately associated with the executive and that together with the executive constitute the basic software necessary for effective operation of the system. The higher level products in the unbundled layer (usually themselves referred to as the "layered" products) maintain a certain independence of the operating system, in that they are developed, released and sold separately. Such organization naturally requires that any changes in the lower layers be made in an upward compatible way. Unbundled products are not done directly by the VMS Group.

In terms of Venus software, it should be noted that processor dependencies are visible almost exclusively to the programs in the executive layer. Moreover any features or enhancements added to the layered products for Venus automatically become available to all VAX systems.

# 2.5 PERFORMANCE

The overall performance goal of the Venus Program is four times the performance of the 11/780.

# Processor

As against the 11/780, pipelining in Venus halves the number of cycles required in most instructions, and the cycle time itself is reduced from  $200~\mathrm{ns}$  to 67 ns. minimize processor idle time, the I box continuously prefetches the instruction stream, the writeback cache eliminates 50% of the memory writes required. Taking all of these factors account, the table on the next page compares our best estimate of instruction times on Venus against times for identical instructions on 11/780. The figures listed are based on these assumptions.

$11/78\emptyset$  main memory read access time, as seen from the E box, is  $140\emptyset$  ns. This is actually the best case, since it assumes the access is to the first longword, and the SBI and memory are idle.

Venus main memory read access time, as seen from the E box, is 533 ns. This does not account for writeback time or IO interference, which we believe to be negligible. Moreover it assumes the memory being used is in the CPU cabinet; read access to addon memory in an expansion cabinet takes 25% longer (overall system performance degradation with expanded memory is 5-10%).

11/780 write cycle time is 200 ns. This does not account for contention at the SBI write buffer or in the memory control.

Venus cache write cycle time is 67 ns. This does not account for writeback, and assumes aligned longword writes. Masked writes take two cycles.

There is no contention for general register access while waiting for updates. Such contention would occur primarily when a register destination of one instruction is used in the address calculation of the first operand of the next.

Memory references are aligned.

| Operation                                                                                                                                                                                                                                                                                        | 100% cad                                                                                                                           | che hit<br>Venus                                                                                             |                                                                                                              | at                                                                       | Ratio<br>hit r<br>95%                                                                |                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| ADDL2 R,R ADDL2 ^B(R),R ADDL2 R,^B(R) ADDL2 ^B(R),^B(R) MCVL R,^B(R) MOVL ^B(R),^B(R) INCL R INCL ^B(R) ADDL3 R,R,R ADDL3 ^B(R),^B(R),R ADDL3 ^B(R),^B(R),^B(R) BR successful BR unsuccessful MOVC3 per byte (1) MOVC5 clear per byte (2)                                                        | 1400<br>800<br>1000<br>400<br>1000<br>600<br>1200<br>1600<br>600<br>400<br>300                                                     | 67<br>133<br>267<br>267<br>200<br>200<br>67<br>200<br>133<br>133<br>267<br>200<br>133<br>33                  | 1/0<br>2/0<br>2/1<br>3/1<br>1/1<br>2/1<br>1/0<br>2/1<br>1/0<br>4/0<br>5/1<br>1/0                             | 6.0<br>6.5<br>5.20<br>5.00<br>5.00<br>5.00<br>6.00<br>9.00<br>9.00<br>18 | 5. 2<br>5. 2<br>3. 9<br>4. 4<br>4. 6<br>4. 1<br>5. 2<br>4. 1<br>4. 3<br>5. 1<br>3. 1 | 4.8<br>4.9<br>3.6<br>4.0<br>3.7<br>4.8<br>3.7<br>4.2<br>4.7<br>4.3<br>3.2<br>6.0<br>5.5                      |

| ADDF2 R,R Small difference ADDF2 ^B(R),R Small difference ADDF2 ^B(R),^B(R) Small difference ADDD2 R,R Small difference ADDD2 ^B(R),R Small difference ADDD2 ^B(R),R Small difference ADDD2 ^B(R),R Small difference MULF2 R,R MULF2 ^B(R),R MULF2 ^B(R),R MULD2 R,R MULD2 ^B(R),R MULD2 ^B(R),R | 800<br>800<br>1400<br>1400<br>1800<br>1400<br>1400<br>2200<br>3600<br>1200<br>1800<br>2200<br>3600<br>3600<br>1200<br>4600<br>6200 | 133<br>200<br>133<br>200<br>267<br>333<br>400<br>333<br>400<br>533<br>600<br>200<br>200<br>333<br>733<br>733 | 1/0<br>1/0<br>2/0<br>2/0<br>3/1<br>3/1<br>1/0<br>3/0<br>3/0<br>5/2<br>1/0<br>2/0<br>3/1<br>1/0<br>3/0<br>5/2 | 6.0                                                                      |                                                                                      | 5.3<br>3.9<br>7.1<br>5.7<br>4.2<br>4.1<br>3.5<br>5.9<br>4.9<br>4.9<br>4.9<br>5.4<br>6.9<br>9.3<br>7.5<br>5.6 |

#### Notes:

- (1) MOVC3 times in the 90% column assume steady-state cache performance for long strings the 11/780 waits for memory read every eighth byte, memory write every fourth; Venus waits for read and write every sixteenth byte.

- (2) MOVC5 clear times in the 90% column assume steady-state performance for long strings the 11/780 waits for full memory modify cycle on each longword and Venus waits for writeback every sixteen bytes.

Venus cache miss ratio is assumed to be half that of 11/780, because the Venus cache is twice as large. Thus the data shown as 95% hit rate compares Venus at 95% with 11/780 at 90%, and the 90% column compares Venus at 90% with 11/780 at 80%.

100% cache hit times were calculated by counting the maximum number of cycles required by the given instruction from each box, M, I and E, and multiplying by 67 ns. 95% and 90% times were then obtained by adding an "average miss penalty" for each memory access performed by the instruction. For 11/780, this penalty per location read is 120 ns for the 95% hit rate, 240 ns for 90%; for Venus it is estimated at 33 ns for 95% and 65 ns for 90% per location read or written.

In Venus, 3-operand instructions with register destination take one cycle longer than the 2-operand equivalents with register destination. With memory destination, 3-operand instructions take the same time as the 2-operand forms, unless the destination specifier requires indexing or indirection.

## Floating Point Performance

The lower half of the table shows the most recent attempt to quantify the performance of the Venus floating point accelerator as against that of the 11/780. There are still many uncertainties in these estimates:

The single precision add path is extremely tight. The large effect of going from two to three cycles is a high incentive for making it work, but this is still a major risk.

The microsequencer and control store in the FPA have not received significant attention. Neither is expected to present a major problem, but we need to be sure.

It may be feasible to gain significant improvement in the multiply times by enlarging the multiplier, but this is a complex tradeoff involving the size of the control store, the clocking scheme, and the pinouts available on the adder module. We have therefore set expectations on the basis of a 16 x 16 network.

Note that two sets of statistics are given for all additive operations, the second being for an ADD or SUB involving a small difference in the operands,

i.e. an operation in which one fraction is subtracted (add where the signs differ, subtract where the signs are equal) and the exponents differ by  $\emptyset$  or 1. This is the case where normalization may require a long shift or negation of the fraction, which in the Venus FPA takes an extra cycle.

The comparisons above are of course with FPAs installed in both 11/780 and Venus. For machines without FPAs the improvement is not as good, but it is assumed that any customer concerned about floating point performance will buy an FPA; it is therefore not worth the cost to make any special effort to improve non-FPA performance.

## Memory

Not only has the memory cycle time been reduced considerably, but once a write cycle has been started in one array board, the M Box can initiate a second write in another. Timing is such that different array boards can absorb writes as fast as the M Box can request them. Memory access times in nanoseconds at the M Box are as follows (a block is four longwords, sixteen bytes).

|                         | In memory | From CPU   |

|-------------------------|-----------|------------|

| Read access, first word |           |            |

| In CPU cabinet          | 400       | 533        |

| In expansion cabinet    | 533       | 667        |

| Block read access       | 333       | 007        |

| In CPU cabinet          | 600       | 733        |

| In expansion cabinet    | 733       | 733<br>877 |

| Block write access      | 267       | 077        |

| Block write cycle       | 467       |            |

| Overlapped operation    | 307       |            |

| Block write access      | 267       |            |

| Block write cycle       | 333       |            |

| •                       | 000       |            |

Figures from CPU include time for request from CPU to memory and time to get data from memory back to CPU. No write times are given for the CPU, as writing in main memory is only for writeback; if this delays the CPU, the wait depends on a variety of circumstances. The write cycle time in overlapped operation is the time between write requests to different array boards.

# Peripheral Subsystem

The overall performance of the IO subsystem depends both on the performance of its individual parts, and also on the characteristics of processor and memory, as the peripheral adapters and controllers interact so much with them. For a typical mix of traffic, the memory burst bandwidth on the A bus is 13.3 MB per second with one SBIA, 17.1 with two (for details refer to Appendix B in the IO Plan). The frequency of interrupt checking will be greater than in the 11/780, reducing both the latency and the worst-case wait. The following table gives the maximum throughput or data transfer rates in megabytes per second for the various units in the IO subsystem.

|       | 13.3                      |

|-------|---------------------------|

| 1.5   |                           |

| 5.25  |                           |

| 6     |                           |

| 2.2   |                           |

|       | 3.125                     |

|       | 6.25                      |

| 3.125 |                           |

| 2     |                           |

|       | 1.5                       |

|       | 5.25<br>6<br>2.2<br>3.125 |

Maximum A bus bandwidth with two or more ultra high speed adapters using octaword transfers would be 34.3 MB per second.

## Software

Software performance depends not only on the activities of those who create the software, but also on the performance of the hardware on which it runs. Hence the most direct improvement of VMS as an operating system for Venus will be the improvements in processor speed, memory size and speed, and IO capabilities of Venus as against the 11/780. On the other hand, each release of VMS has goals for quality, functionality and performance, among others, to varying degrees. Venus will usually benefit from performance enhancements engineered for the whole VAX family.

# 2.6 RAMP AND DATA INTEGRITY FEATURES

Features to guarantee the integrity of the data in the system and to promote its reliability, availability and maintainability are built into Venus at every level: they range from minor characteristics of individual circuits to major provisions embracing the entire system. Some of the more significant features are these.

Inherent reliability achieved through low component count and worst-case logic design.

Dynamic monitor error reporting, by means of an error logger, to aid in identifying the source of an intermittent failure. This logger will be used for both hardware and software malfunctions. The log is kept in a disk file.

Instruction retry whenever it is appropriate to the error type. For example five copies are kept of the general purpose registers. Hence on a GPR parity error, the instruction can be repeated using a different copy.

Additional software features in this area include automated patching and updating procedures, powerfail-restart support, user mode diagnostics, extensive protection facilities, and dynamic memory configuration to exclude bad pages.

Parity checking at all RAMs and buses, and parity continuity carried through all major data paths. Parity is kept not only for data, but also for physical addresses and the microcode.

Separate selects to each memory array board, so the control logic for storage selection is all in one place, and faults can be isolated to an individual board.

Single bit error correction and double bit error detection for the cache and memory array, with automatic rewriting of the corrected word.

Memory battery backup for 10 minutes. Backup can be set shorter to save on battery recharge time, thus allowing user to choose riding out several short power failures at the cost of going down during a long one.

The ability to reconfigure the system without the FPA when troubleshooting floating point failures.

Optional redundant IO transfer paths. For example, interconnected disk systems, so that should one controller fail, an individual disk can maintain a transfer path through another (the switchover must be handled by the operator however).

Fast, accurate diagnostics, with first-failure fault isolation to field replacable unit in CPU cluster and to module in peripherals.

Error logic for monitoring all backplane signals from the console via the diagnostic bus.

A "keep alive" count kept by the console to determine if the system is hung. Should the hung condition be detected, the console saves the state of the machine.

Other console diagnostic features, including remote capability, flexible clock control, and some visual indicators should the console be unable to report its own failures.

For high availability, the Hydra configuration, where one processor takes over all activity should the other fail. The three criteria for Venus to qualify as a Hydra node are: it runs on VMS, it has a CI, and the console uses the standard midrange console language.

Extensive console monitoring of the environment and the power system.

#### 3 DEVELOPING THE SYSTEM

The Venus Program is organized around a strategy for developing a complete computer system. This strategy has a number of stages, and it is accompanied by phase reviews and thorough program tracking, with major milestones pinpointed. The process culminates in the marketing of two classes of systems at specific times. There are of course risks attendant on the development process, and these are duly noted.

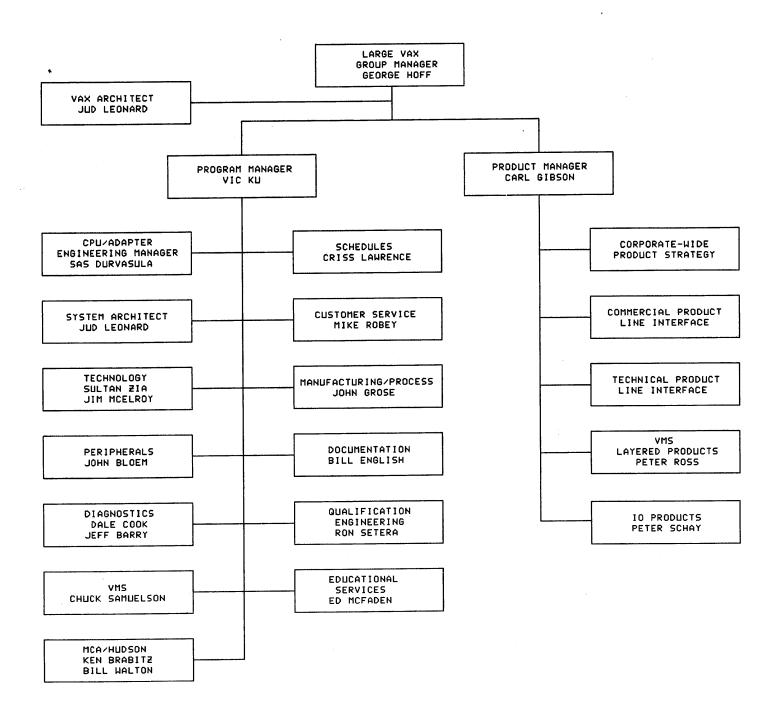

Almost all of the staff and all key personnel are already in place. Figure 3.1 illustrates the Program organization.

#### 3.1 DEVELOPMENT STRATEGY

The overall strategy is to develop a system whose IO subsystem is based on the SBI, using the CI for mass storage and the Unibus for communications and unit record. However Massbus systems will be available for backup, and employment of a Unibus-UDA50 integrated disk-tape controller in place of the CI will allow systems at lower cost with moderate IO performance. The reasons for taking this approach are several:

SBI and the Unibus form a known, well-defined bus structure with mature software, and the CI with its mass storage peripherals is well enough along so we can depend on it with confidence.

Improved cost/performance ratio of CI-HSC over Massbus in medium-to-large system configurations.

Better chance of meeting FCC and acoustic goals with CI peripherals.

Satisfy current 11/780 customers via upgrading.

Offer Unibus and Massbus upgrades.

FIGURE 3.1 VENUS PROGRAM ORGANIZATION

The Venus development strategy is organized in the following seven stages.

## System Performance Analysis

The Venus Program is funding two people in the SPA Group in Maynard to do system and IO performance analysis and system simulation to determine whether the Venus structure is properly designed conceptually. They will use benchmarks and workloads to determine whether functionalities of the different parts of the system are consistent with one another, e.g. are there any bottlenecks? is there enough IO bandwidth?

#### 2. SAGE 2 Simulation

Throughout the Program, before any element is actually built it undergos complete SAGE2 simulation. This occurs at both the chip level and the box level (e.g. I and E boxes); simulation and delay analysis at the complete system level will be started well ahead of breadboard power on.

## 3. Technology Evaluation

Concurrent with the above two stages, the Technology Group has been evaluating the various technological innovations that are under consideration for use in Venus. This involves generating specifications, working with vendors to meet those specifications, and collecting the information on which the Program can base its decisions on which technologies to use and what tradeoffs to make. The most extensive evaluation procedure is that for the MCAs, discussed below.

#### 4. Breadboard Stage

Engineering will build two breadboards that will run at reduced speed but will allow verification of system functionality. It is expected that the functionality of the breadboard will be equivalent to that of the final machine, but revisions will made as necessary. This stage in the development will enable Diagnostics and Software begin debug. It is planned that people from Manufacturing, Customer Service, and Qualification will participate; they will begin learning the system in terms relevant to their own and will be actively involved identifying problem areas where Engineering help them. Moreover since a simulator is not a real machine and also runs perhaps a million times slower than a real machine, the breadboards will

allow real-world functional verification of the simulated hardware as well as procedures that could not be simulated at all.

The breadboards will use backplanes that are mostly wirewrapped and printed circuit modules. We are pursuing an effective emulator strategy in case we require individual hardware simulators for any MCAs that are not functional. It is expected that at least 90% of first-pass MCAs will be available and 30% of them will be operational at this stage. Emulators will automatically be built for the thirteen most complex MCAs.

# 5. Post Breadboard and Prototype Stage

Engineering will build and drive five machines that implement a transition from advanced breadboards to prototypes. These will run at full speed, will use all etched pc boards and backplanes, and will make use of the second-pass to third-pass MCA chips. The use of these five machines is: one for preliminary 102 testing, one for preliminary DMT, one for software development and VMS verification, and two for engineering and diagnostic operations, system quality verification, and the like. People from Manufacturing, Customer Service, and System Qualification are expected to be deeply involved in these activities.

## 6. Manufacturing Prototype Stage

Manufacturing will build twenty-five prototypes and will then update them to reflect the documentation when it is released. The goal is for these to be functionally identical to the Engineering prototypes. The Manufacturing prototypes will be built with Engineering support and maintained by Customer Service. These machines will utilize the revised versions of the pc boards and backplanes, and they will have the second- and then third-pass MCA chips. Checkout will begin when the Engineering prototype runs AXE and the diagnostics. Disposition of these machines will be:

One to the Memory Group to test array modules, One to Production for FA&T, Four for final DMT verification, Two for Field Service training, Six to Production for quick verification, One to Spit Brook for the software team, One for System Evaluation, One for Mass Storage Production, and Eight will be assigned by the Product Manager.

At this stage, System Engineering will use the prototypes to verify a limited number of system configurations. Since the initial prototype systems will be built and verified without released documents, we will set up an account for purchasing components and mechanical parts and to track actual costs instead of standardized costs.

# 7. Advanced Test Stage

This final stage is for testing and verification (qualification) of many more system configurations utilizing CI and Unibus devices.

# MCA Engineering and Evaluation

The engineering and evaluation effort in MCA technology lies in three principal areas: development of software design tools, verification of the hardware design, and characterization and qualification of the finished parts.

The various steps in the creation of an MCA use many of the design, layout and testing tools discussed in the next section. The most important new tool in layout is MCACUT, the MCA version of the Merlin placement optimization system. This uses a cutline approach that minimizes the number of nets crossing an imposed boundary by swapping equivalent entities; these entities may be complete cells, equivalent functions within cells, equivalent gates within functions, and equivalent pins within gates. Other parts of the project include enhancements to the IDEA circuit routing system, programs for creating and checking the artwork data base that serves as the input for making the IC mask, and programs for manipulating and analyzing test patterns.

The hardware part of the project includes determining those circuit parameters that predict operational performance of the chips, to verify that the various circuit elements implemented on a chip function correctly - both in theory through circuit simulation and in practice through evaluation and test verification - and to determine worst-case conditions that may be applied to automatic test hardware to support verification. The hardware development group also provides the necessary application support to the Venus design team and serves as the technical interface to Motorola.

Completing the development strategy is a complete characterization of the test chips, followed by a qualification procedure that includes correlation among test systems, compliance with specifications, verification of the burn-in procedure, verification of performance of parts from several wafer lots, and thermal, mechanical, electrical and reliability testing.

Related functions are installation and organization of MCA manufacturing and test procedures in the Hudson facility and acquisition of parts.

# Software Strategy

To ensure an operating system for Venus in the hardware development time frame, the development strategy of the VMS Group in Spit Brook is to be heavily involved as an integral pert of the Venus team throughout the design of the system. The following strategy is based on the belief that there are no areas where the VMS executive lacks the mechanisms and structure to support the changes required by Venus; it is expected that enhancements to the current system will be sufficient for Venus support.

- Place product quality as the primary and overriding goal above addition of new features.

- 2. Have a VMS release with appropriately tested Venus support in the SDC when Venus ships, with a fallback strategy of releasing VMS with partially tested support and providing binary update patches when final testing is accomplished.

- 3. Assume that VMS does nothing to interfere with or to bottleneck the system performance for a Venus class processor. This assumption will be tested empirically by the System Performance Analysis Group. If the assumption proves false, the scope of this project will be modified; the answer to this question must be determined before the Phase 1 review for the VMS release that supports Venus.

- 4. Schedule and implement VMS support for newinterconnect adapters and peripherals as they

become available. The general rule of thumb is

that to support a given peripheral, firm

specifications must be available one year before

support is to be provided, and hardware must be

available to VMS Development six months before

submission of the VMS release to the SDC. However

exceptional devices such as HSC50 will require

longer leadtime.

- The present Venus-VMS Project is restricted to activities in the executive layer of the software three categories: booting and initialization, system error handling, and IO. Venus requirements that imply software development the bundled products will be scheduled and implemented by the VMS Group in the normal phase review process for the appropriate VMS release. Even though the current project will not directly result in the implementation of bundled products, a major role of this project is to provide a communication and consulting path between Venus and VMS. As Venus product requirements identified, this project will provide a focus to help ensure schedule and technical needs are made known and satisfied within the constraints of the phase review process.

- 6. Venus requires the development of layered products. Layered product requirements are defined by the Venus Program, in which this project is a participant. The products themselves are defined and implemented using the phase review process, managed by the responsible development group. Conformance to the appropriate VMS standards and testing and integrating them into VMS is monitored by VMS program management. Refer to Appendix C for the current status of the layered products.

#### 3.2 DEVELOPMENT TOOLS

Being developed internally are a number of programs, many very large and complicated, to aid in hardware design. Although many of these tools are available thoughout the Corporation, most are being developed or enhanced specifically for the Venus Program by the LSG CAD Group. These programs are generally referred to as CAD tools, for "computer aided design".

Basic Circuit Design

The fundamental CAD tool is SUDS, the Stanford University Design System. This is based on a sophisticated graphics editor that aids in the design and checking of logic circuits and drawing of circuit schematics. It also contains programs to create wirelist and plot files. The outputs of SUDS provide the inputs to CALDEC, IDEA, and most of the other software discussed below. The program also has facilities for interacting with the various intermediate products of the board and MCA layout procedures.

#### SAGE2 Simulator

From information provided by the SUDS wirelist file, SAGE2 simulates the hardware of individual MCAs and Venus subsystems with the ability to inspect the interaction between individual gates in real time (although many times slower than actual gate speeds), to determine whether the logic actually does what it was designed to do. The whole system can also be simulated, with inspection at levels higher than individual gates.

#### VOTE Simulator

This program determines the effectiveness of the test patterns, test programs and test microcode generated by Diagnostics and Manufacturing. VOTE effectively runs the tests on a simulation of the hardware with the equivalent of physical fault insertion done entirely in software, and from this determines which of the faults the test was unable to detect.

#### IDEA

This program is the successor to CALDEC. Like the earlier procedure, it uses SUDS outputs to lay out circuits, but it is more advanced and handles many more layers. Only IDEA has the capability needed for laying out MCA chips.

#### Delay Calculation

This software package allows the designer to determine the physical delays between individual signal points in a circuit design, either a single board or a set of boards in a backplane. From the SUDS wirelist file and the CALDEC output (eventually the IDEA output), DLY creates a database that represents the physical hardware as it would be built, and from that CAL calculates all signal propagation times taking into account gate delays, wire links, and even stubs. Then with DLYED, the user can determine the delay structure of his design by inspection of propagation times across individual elements in each signal path. For MCA inspection, a file equivalent to the CAL output can be generated directly by SUDS.

# Merlin Placement Optimization System

These programs help the designer determine the optimal position of circuit elements from critical parameters supplied by the designer and known characteristics of the materials, including even the capacitance of metal runs. The original program (MINCUT) is being enhanced in two stages to handle first MCAs and then pc and

multiwire boards. With the information provided by this software, the designer can go back via SUDS to SAGE2 to get real delays.

#### MCA Verification

From the IDEA database, the TENART software checks design rules, verifies interconnections, and ultimately generates the CALMA database, which is the representation of the MCA design used by Motorola to create the chip.

## Wirewrap

From wiring rules and from information about the special character of runs, their type and termination supplied by the user, the wirewrap package generates the pattern for wirewrapping a circuit board or backplane, including assigning twisted pair grounds and generating an NC tape.

#### Test Pattern Generation

Phase 5 Product Retirement

The Digitest D-LASAR program implements an algorithm that generates input and output test patterns for both simulators and hardware testers. This is used principally for MCA designs, which are generally sent to Digitest, but arrangements have been made to use the program in-house.

#### 3.3 PHASE REVIEW

The Venus Program will follow the "Product Development Process" used by the Large System Group in Marlboro. This document details the entry and exit criteria for six phases, listed here with their completion dates. (Copies are available from Terry Mahoney, MR1-2/E78, DTN 231-6270.)

| Phase Ø | Product Strategy and Requirements                                  | Completed Q2/FY8Ø |

|---------|--------------------------------------------------------------------|-------------------|

| Phase 1 | Product Definition and Planning                                    | Completed Q2/FY81 |

| Phase 2 | Product Implementation                                             | Q3/FY83           |

| Phase 3 | Product Qualification,<br>Product Release, and<br>Pilot Production | Q4/FY83           |

| Phase 4 | Product Continuation                                               |                   |

During Phase 1 the many detailed plans and specifications were created, the design reviews held, the necessary contracts signed, and the manufacturing plant selected. The culmination of this phase was the completion of the Product Business Plan and System Implementation Plan, and the signing of the Product Contract. These last three items, which constituted the subject of the Phase 1 Review, detail the course of the Program in Phase 2. During Phase 2 the Program will accomplish the following major tasks.

Renew the commitment of Engineering, Manufacturing, Marketing and Customer Service to the revised Product Business Plan.

Hold technical reviews of the engineering design, manufacturing process, and service process.

Complete the detailed design, hardware breadboard and prototype test, and software internal tests; at the end of Phase 2, DMT and field testing will be ready to begin.

Run performance benchmarks and publish a performance report.

Make sure announcement criteria can be met. The principal criteria are that DMT be one-third done and there be a reliable second source for MCAs.

# 3.4 PROGRAM TRACKING AND MAJOR MILESTONES