## DMF32 USER'S GUIDE

## DMF32 USER'S GUIDE

Prepared by Educational Services of Digital Equipment Corporation

### Copyright © 1982 by Digital Equipment Corporation All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in South Lawrence, MA.

The following are trademarks of Digital Equipment Corporation:

| d i g i t a l | DECtape      | Rainbow        |

|---------------|--------------|----------------|

| DATATRIEVE    | DECUŚ        | RSTS           |

| DEC           | DECwriter    | RSX            |

| DECmate       | DIBOL        | UNIBUS         |

| DECnet        | MASSBUS      | VAX            |

| DECset        | PDP          | VMS            |

| DECsystem-10  | P/OS         | <b>VT</b> .    |

| DECSYSTEM-20  | Professional | Work Processor |

### CONTENTS

| CHAP   | PTER 1 GENERAL DESCRIPTION                 |     |

|--------|--------------------------------------------|-----|

| 1.1    | INTRODUCTION                               | 1   |

| 1.1.1  | Asynchronous Multiplexer                   |     |

| 1.1.2  | Synchronous Interface                      |     |

| 1.1.3  | Line Printer Interface                     |     |

| 1.1.4  | Parallel Interface                         |     |

| 1.2    | PHYSICAL DESCRIPTION                       |     |

| 1.2.1  | DMF32 Configurations                       | 4   |

| 1.2.1. |                                            |     |

| 1.2.1. |                                            |     |

| 1.2.1. | 3 DMF32-AC Option                          |     |

| 1.2.2  | Test Connectors                            |     |

| 1.3    | GENERAL SPECIFICATIONS                     |     |

| 1.3.1  | Environment                                |     |

| 1.3.2  | Power Specifications                       |     |

| 1.3.3  | DMF32 Functional Parameters                |     |

| 1.3.4  | DMF32 Performance Parameters               | 8   |

| 1.3.5  | Installation Distances                     |     |

|        |                                            |     |

|        |                                            |     |

| CHAP   | PTER 2 INSTALLATION                        |     |

| 2.1    | SCOPE                                      | c   |

| 2.2    | UNPACKING AND INSPECTION                   |     |

| 2.2    | DEVICE AND VECTOR ADDRESS ASSIGNMENTS      |     |

| 2.4    | INSTALLATION PROCEDURE                     |     |

| 2.4.1  | M8396 Module Installation                  |     |

| 2.4.2  | DMF32 Distribution Panel Installation      |     |

| 2.4.2  | Distribution Panel Installation Procedure  |     |

| 2.4.3  | BC06R Cable Routing                        |     |

| 2.4.4  | Verifying Standalone Operation             |     |

| 2.4.5  | Communications Equipment Interface Cabling | 17  |

| 2.4.7  | Distribution Panel Switch Settings         |     |

| 2.4.7  | Verifying System-Integrated Operation      |     |

| ∠.4.0  | vernying System-integrated Operation       | ≀ ⊱ |

#### CHAPTER 3 DMF32 DIAGNOSTICS

| 3.1     | INTRODUCTION                              | 21 |

|---------|-------------------------------------------|----|

| 3.1.1   | Diagnostic Supervisor                     |    |

| 3.1.2   | DMF32 CSR Address and Vector Address      | 22 |

| 3.1.3   | Hardware Loopback Methods                 | 22 |

| 3.1.3.1 | Internal Wrap                             |    |

| 3.1.3.2 | H3248 Single-Line Loopback Connector      | 22 |

| 3.1.3.3 | H3249 Staggered Loopback Connector        | 23 |

| 3.1.3.4 | Local Modem                               | 25 |

| 3.1.3.5 | Programmable Modem                        | 25 |

| 3.1.4   | Distribution Panel Switch Settings        | 25 |

| 3.1.5   | Self Test                                 | 25 |

| 3.2     | DMF32 LEVEL 3 DIAGNOSTICS                 | 26 |

| 3.2.1   | Level 3 Hardware Prerequisites            | 26 |

| 3.2.2   | EVDLB Diagnostic Description              | 26 |

| 3.2.2.1 | Loading, Attaching, and Running EVDLB     | 26 |

| 3.2.3   | EVDLC Diagnostic Description              | 28 |

| 3.2.3.1 | Loading, Attaching, and Running EVDLC     | 28 |

| 3.2.4   | EVDLD Diagnostic Description              | 28 |

| 3.2.4.1 | Loading, Attaching, and Running EVDLD     | 28 |

| 3.2.4.2 |                                           |    |

| 3.3     | DMF32 LEVEL 2R DIAGNOSTICS                |    |

| 3.3.1   | Level 2R Hardware Prerequisites           |    |

| 3.3.2   | EVDLA Diagnostic Description              | 32 |

| 3.3.2.1 | Loading, Attaching, and Running EVDLA     | 32 |

| 3.3.3   | EVDAC Diagnostic Description              | 32 |

| 3.3.3.1 | Loading, Attaching, and Running EVDAC     | 32 |

| OUADT   |                                           |    |

| CHAPT   | TER 4 PROGRAMMING                         |    |

| 4.1     | INTRODUCTION                              | 35 |

| 4.1.1   | DMF32 CSR 0                               |    |

| 4.1.2   | DMF32 CSR 1 Diagnostic Register           |    |

| 4.1.3   | DMF32 Device Control Status Registers     |    |

| 4.2     | SYNCHRONOUS INTERFACE                     |    |

| 4.2.1   | Synchronous Interface Protocol Support    | 38 |

| 4.2.2   | Synchronous Interface Baud Rate           |    |

| 4.2.3   | Synchronous Interface Device Registers    |    |

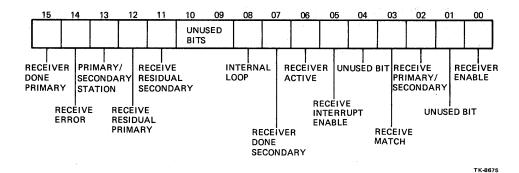

| 4.2.3.1 | Receive Control Status Register           | 38 |

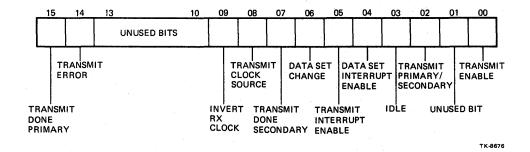

| 4.2.3.2 | Transmit Control Status Register          | 39 |

| 4.2.3.3 |                                           |    |

| 4.2.3.4 | Data Set Change Flag Register             |    |

| 4.3     | SYNCHRONOUS OPERATION                     | 40 |

| 4.3.1   | Synchronous Transmit Operation            |    |

| 4.3.1.1 | Pretransmission Considerations            | 40 |

| 4.3.1.2 |                                           |    |

| 4.3.1.3 |                                           | 41 |

| 4.3.1.4 | Synchronous Interface Transmission Errors |    |

| 4.3.2            | Synchronous Receiver Operation                   | 42 |

|------------------|--------------------------------------------------|----|

| 4.3.2.1          | Synchronous Receiver Synchronization             |    |

| 4.3.2.2          | Synchronous Interface Data Reception             | 42 |

| 4.3.2.3          | Synchronous Interface Receiver Errors            | 43 |

| 4.4 SYI          | NCHRONOUS INTERFACE DEVICE REGISTERS             | 43 |

| 4.4.1            | Receive Control Status Register                  | 43 |

| 4.4.2            | Transmit Control Status Register                 | 43 |

| 4.4.3            | Miscellaneous Register                           | 48 |

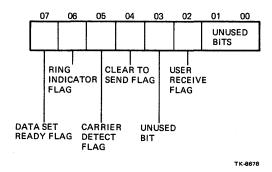

| 4.4.4            | Data Set Change Flag Register                    |    |

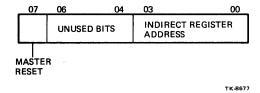

| 4.5 SYI          | NCHRONOUS INDIRECT REGISTERS                     |    |

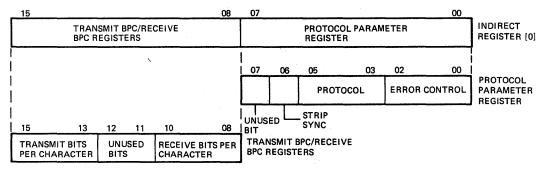

| 4.5.1            | Indirect Register [0]                            |    |

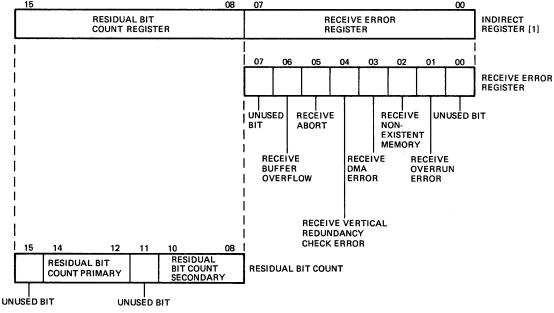

| 4.5.2            | Indirect Register [1]                            |    |

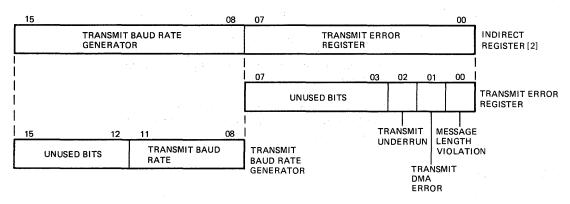

| 4.5.3            | Indirect Register [2]                            |    |

| 4.5.4            | Indirect Register [3]                            |    |

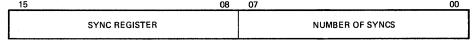

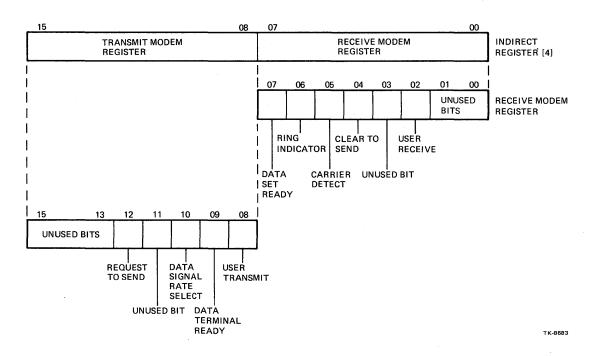

| 4.5.5            | Indirect Register [4]                            |    |

| 4.5.6            | Indirect Register [5]                            |    |

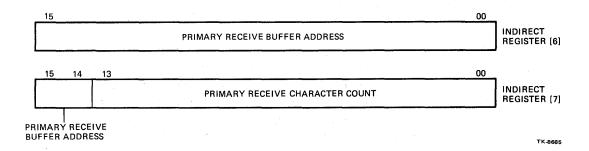

| 4.5.7            | Indirect Registers [6] and [7]                   |    |

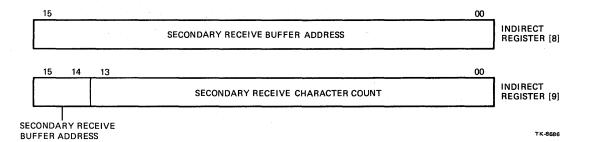

| 4.5.8            | Indirect Registers [8] and [9]                   |    |

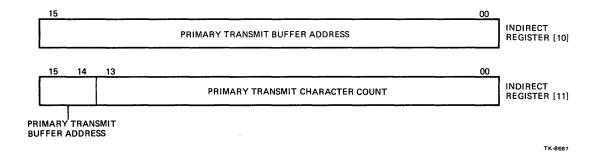

| 4.5.9            | Indirect Registers [10] and [11]                 |    |

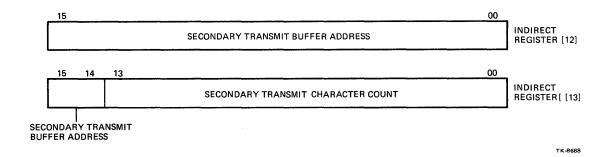

| 4.5.10           | Indirect Registers [12] and [13]                 |    |

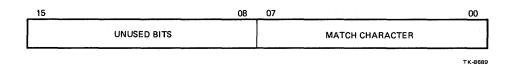

| 4.5.11           | Indirect Register [14]                           |    |

| 4.5.12           | Indirect Register [15]                           |    |

|                  | NCHRONOUS INTERFACE PROTOCOLS                    | 72 |

| 4.6.1            | Bit-Oriented Protocol – Transmit Operation       |    |

| 4.6.1.1          | Bit Stuffing                                     |    |

| 4.6.1.2          | Bit-Oriented Protocol Transmit Errors            |    |

| 4.6.2            | Bit-Oriented Prrotocol - Receive Operation       |    |

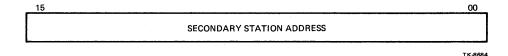

| 4.6.2.1          | Bit-Oriented Protocol Secondary Station Address. | 7° |

| 4.6.2.2          | ADCCP Protocol                                   |    |

| 4.6.2.3          | Bit-Oriented Protocol CRC                        |    |

| 4.6.2.4          | Bit-Oriented Protocol Receive Errors             |    |

| 4.6.3            | DDCMP – Receive Operation                        |    |

| 4.6.3.1          |                                                  |    |

| 4.6.3.2          | DDCMP Received Message                           |    |

| 4.6.3.3          | DDCMP Data Streams                               |    |

| 4.6.3.3<br>4.6.4 | DDCMP Receive Synchronization                    |    |

| -                | DDCMP - Transmit Operation                       |    |

| 4.6.4.1          | DDCMP Transmit Errors                            |    |

| 4.6.5            | General Byte-Oriented (GEN BYTE) Protocol        |    |

| 4.6.5.1          | GEN BYTE Protocol                                |    |

| 4.6.5.2          | GEN BYTE CRC                                     |    |

| 4.6.5.3          | Transmit Operation                               |    |

|                  | (NCHRONOUS INTERFACE                             |    |

| 4.7.1            | Asynchronous Device Registers                    |    |

| 4.7.1.1          | Control Status Register                          |    |

| 4.7.1.2          | Line Parameter Register                          |    |

| 4.7.1.3          | Receive Buffer Register                          |    |

| 4.7.1.4          | Receive Silo Parameter Register                  |    |

| 4.7.2            | Asynchronous Device Operation                    |    |

| 4.7.2.1          | Asynchronous Transmit Operation                  |    |

| 4.7.2.2          | Asynchronous Receiver Operation                  | 79 |

| 4.8     | ASYNCHRONOUS DEVICE REGISTERS                                                  | 79   |

|---------|--------------------------------------------------------------------------------|------|

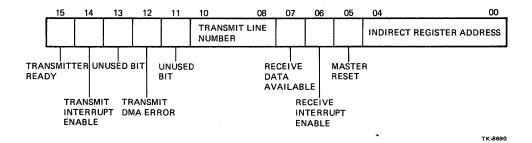

| 4.8.1   | Control Status Register                                                        | 82   |

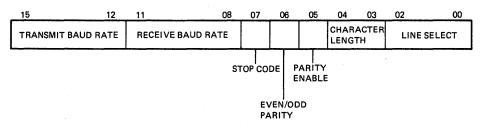

| 4.8.2   | Line Parameter Register                                                        | 82   |

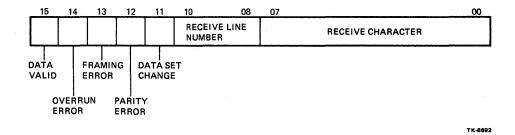

| 4.8.3   | Receiver Buffer Register                                                       | 86   |

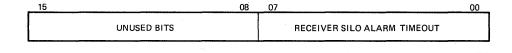

| 4.8.4   | Receive Silo Parameter Register                                                | 87   |

| 4.9     | ASYNCHRONOUS INDIRECT REGISTERS                                                | 87   |

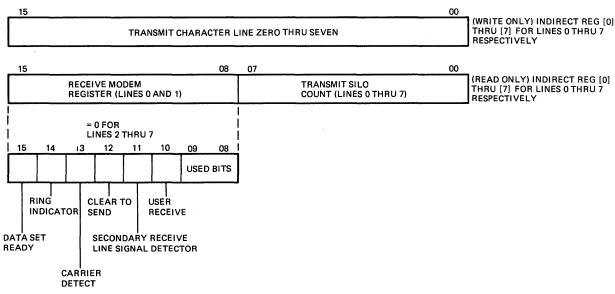

| 4.9.1   | Indirect Registers [0] Through [7]                                             | 89   |

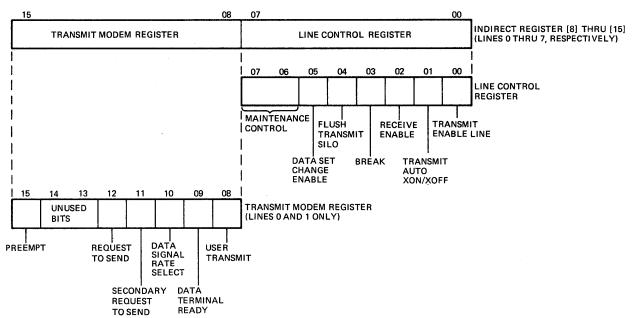

| 4.9.2   | Indirect Registers [8] Through [15]                                            | 93   |

| 4.9.3   | Indirect Registers [16] Through [23] (Read/Write)                              | 94   |

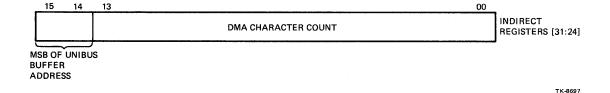

| 4.9.4   | Indirect Registers [24] Through [31]                                           | 94   |

| 4.10    | Indirect Registers [24] Through [31] RELATIONSHIP BETWEEN MAINTENANCE MODES AN | D    |

|         | MODEM SIGNALS                                                                  |      |

| 4.11    | LINE PRINTER CONTROLLER                                                        | . 97 |

| 4.11.1  | Line Printer Controller Operation                                              | 97   |

| 4.11.1. |                                                                                |      |

| 4.11.1. |                                                                                |      |

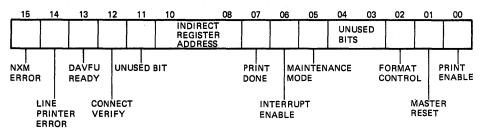

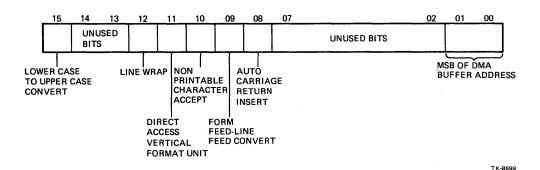

| 4.12    | LINE PRINTER CSR REGISTER                                                      |      |

| 4.13    | LINE PRINTER INDIRECT REGISTERS                                                | 107  |

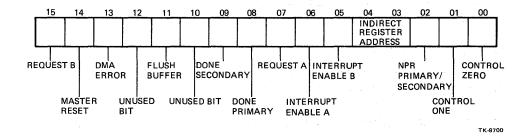

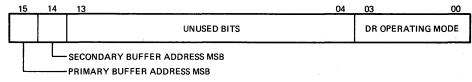

| 4.14    | PARALLEL INTERFACE (DR)                                                        | 107  |

| 4.14.1  | DR-11-C Functional Mode                                                        | 108  |

| 4.14.1. | 1 DR-11-C User Request A and B                                                 | 108  |

| 4.14.2  | Silo Mode                                                                      |      |

| 4.14.2. |                                                                                |      |

| 4.14.2. |                                                                                |      |

| 4.14.3  | DMA Mode                                                                       |      |

| 4.14.3. | 1 DMA Transfer                                                                 | 109  |

| 4.14.4  | Parallel Interface Device Registers                                            | 110  |

| 4.14.4. |                                                                                |      |

| 4.14.4. |                                                                                |      |

| 4.14.4. | 3 Parallel Interface Input Buffer                                              | 115  |

| 4.14.4. | 4 Miscellaneous Register                                                       | 115  |

| 4.14.5  | Parallel Interface Indirect Registers                                          | 117  |

| 4.15    | DIFFERENCES BETWEEN DMF32 AND THE DR11-C                                       |      |

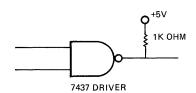

| 4.16    | DMF32 DRIVERS AND RECEIVERS                                                    | 119  |

|         |                                                                                |      |

| APPEN   | NDIX A SYNCHRONOUS 25-PIN CINCH CONNECTOR                                      | .121 |

| APPEN   | NDIX B ASYNCHRONOUS 25-PIN CINCH CONNECTOR                                     | 123  |

| APPEN   | NDIX C PARALLEL INTERFACE/LINE PRINTER SIGNALS.                                | 125  |

|         | ·                                                                              |      |

|         |                                                                                |      |

|         | FIGUR                                                                          | RES  |

|         |                                                                                |      |

| 1-1     | DMF32 Overview Block Diagram                                                   | 1    |

| 1-2     | DMF32 Components                                                               | 4    |

| 1-3     | DMF32 Test Connectors                                                          | 6    |

|         |                                                                                |      |

| 2-1  | DMF32 Switch Settings and Jumper Locations        |     |

|------|---------------------------------------------------|-----|

| 2-2  | Shielded Bulkhead Type Panel                      |     |

| 2-3  | H9544-SJ Frame Installation                       |     |

| 2-4  | BC06R Cable Connections                           | 14  |

| 2-5  | DMF32 Distribution Panel Installation             | 15  |

| 2-6  | Staggered Connector Installation                  | 16  |

| 2-7  | DMF32 Distribution Panel                          | 17  |

| 3-1  | Single-Line Connector Installation                | 23  |

| 3-2  | Staggered Connector Installation                  | 24  |

| 4-1  | CSR0                                              | 36  |

| 4-2  | Synchronous Receive CSR                           | 44  |

| 4-3  | Synchronous Transmit CSR                          | 48  |

| 4-4  | Miscellaneous Register                            | 52  |

| 4-5  | Data Set Change Flag Register                     | 54  |

| 4-6  | Synchronous Indirect Register [0]                 | 56  |

| 4-7  | Synchronous Indirect Register [1]                 | 60  |

| 4-8  | Synchronous Indirect Register [2]                 |     |

| 4-9  | Synchronous Indirect Register [3]                 |     |

| 4-10 | Synchronous Indirect Register [4]                 |     |

| 4-11 | Synchronous Indirect Register [5]                 | 68  |

| 4-12 | Synchronous Indirect Register [6] and [7]         |     |

| 4-13 | Synchronous Indirect Register [8] and [9]         |     |

| 4-14 | Synchronous Indirect Registers [10] and [11]      |     |

| 4-15 | Synchronous Indirect Registers [12] and [13]      |     |

| 4-16 | Synchronous Indirect Register [14]                |     |

| 4-17 | Asynchronous CSR                                  |     |

| 4-18 | Line Parameter Register                           |     |

| 4-19 | Receive Buffer                                    |     |

| 4-20 | Receive Silo Parameter Register                   |     |

| 4-21 | Asynchronous Indirect Registers [0] Through [7]   |     |

| 4-22 | Asynchronous Indirect Registers [8] Through [15]  |     |

| 4-23 | Asynchronous Indirect Registers [16] Through [23] |     |

| 4-24 | Asynchronous Indirect Registers [24] Through [31] |     |

| 4-25 | Line Printer CSR                                  |     |

| 4-26 | Line Printer Indirect Registers [6]               | 107 |

| 4-27 | Parallel Interface CSR                            |     |

| 4-28 | Miscellaneous Register                            |     |

| 4-29 | DMF32 Drivers and Receivers                       |     |

| A-1  | Synchronous 25 Pin Cinch Connector                | 123 |

| B-1  | Asynchronous 25 Pin Cinch Connector               | 125 |

#### **TABLES**

| 1-1  | DMF32-AA Options                                       | 5  |

|------|--------------------------------------------------------|----|

| 1-2  | DMF32-AB Option Additional Contents                    | 5  |

| 1-3  | Environmental Specifications                           | 6  |

| 1-4  | Synchronous Functional Parameters                      | 7  |

| 1-5  | Asynchronous Functional Parameters                     |    |

| 1-6  | Parallel Interface Functional Parameters               |    |

| 1-7  | Printer Controller Functional Parameters               |    |

| 2-1  | DMF32 Jumper Functions                                 |    |

| 2-2  | VAX Family Installation Manuals                        |    |

| 2-3  | Level 3 Diagnostics                                    | 16 |

| 2-4  | Recommended Cables                                     | 17 |

| 2-5  | Common Switch Setups for Asynchronous                  | 40 |

|      | Lines 0 and 1                                          | 18 |

| 2-6  | Common Switch Setups for the Synchronous Line          |    |

| 2-7  | DMF32 Device Configuration                             |    |

| 2-8  | Distribution Panel Jumpers                             |    |

| 2-9  | DMF32 Level 2R Diagnostics                             | 19 |

| 3-1  | Distribution Panel Switch Settings                     | 25 |

| 3-2  | DMF32 Level 3 Diagnostic Parameters                    | 26 |

| 3-3  | EVDLD Event Flags                                      | 31 |

| 3-4  | DMF32 Level 2R Diagnostic Parameters                   | 31 |

| 4-1  | DMF32 Floating Vectors                                 | 36 |

| 4-2  | CSR 0 Bit Functions                                    | 36 |

| 4-3  | Device Selection                                       | 36 |

| 4-4  | CSR 1 High Byte Functions                              | 37 |

| 4-5  | Synchronous Receive Control Status Register            |    |

| 4.0  | Functions                                              | 44 |

| 4-6  | Internal Loop                                          | 46 |

| 4-7  | Synchronous Transmit Control Status Register Functions | 49 |

| 4-8  | Transmit Clock Source Definitions                      |    |

| 4-9  | Miscellaneous Register Functions                       |    |

| 4-10 | Receive Modem Signals                                  |    |

| 4-11 | Synchronous Indirect Registers                         |    |

| 4-12 | Indirect Register [0] Functions                        |    |

| 4-13 | Error Control Codes                                    |    |

| -    |                                                        |    |

| 4-14       | Valid Error Control, Bits Per Character,                           |           |

|------------|--------------------------------------------------------------------|-----------|

|            | and Protocol Combinations                                          |           |

| 4-15       | Protocol Selection                                                 |           |

| 4-16       | Receive Bits Per Character Selection                               |           |

| 4-17       | Transmit Bits Per Character                                        |           |

| 4-18       | Indirect Register [1] Functions                                    |           |

| 4-19       | Indirect Register [2] Functions                                    |           |

| 4-20       | Transmit Baud Rates                                                |           |

| 4-21       | Indirect Register [3] Functions                                    |           |

| 4-22       | Indirect Register [4] Functions                                    | 67        |

| 4-23       | Asynchronous Control Status Register Functions                     | 80        |

| 4-24       | Line Parameter Register Functions                                  | 83        |

| 4-25       | Character Length Bit Codes                                         | 84        |

| 4-26       | Receiver and Transmit Baud Rates                                   | 84        |

| 4-27       | Receiver Buffer Register Functions                                 |           |

| 4-28       | Receive Silo Parameter Register Functions                          | 86        |

| 4-29       | Indirect Registers [0] Through [7] Functions                       |           |

| 4-30       | Indirect Registers [8] Through [15] Functions                      |           |

| 4-31       | Maintenance Control Function Bits                                  | 92        |

| 4-32       | Relationship Between Maintenance Modes and                         |           |

|            | Modem Signals                                                      | 94        |

| 4-33       | Line Printer Indirect Registers                                    | 99        |

| 4-34       | Line Printer Control Status Register Functions                     | 100       |

| 4-35       | Line Printer Indirect Registers Functions                          |           |

| 4-36       | Parallel Interface Control Status Register Functions               | 111       |

| 4-37       | Parelle Interface Miscellaneous Register Functions                 |           |

| 4-38       | Parallel Interface Operatingn Modes                                |           |

| 4-39       | Parallel Interface Indirect Registers Functions                    |           |

| 4-40       | DMF32 Drivers/Receivers and Associated Signals                     |           |

| C-1        | Parallel Interface/Line Printer Signals                            | 127       |

|            | EXA                                                                | MPLES     |

| 3-1        | Loading, Attaching, and Running EVDLB                              | 97        |

| 3-1        | Loading, Attaching, and Running EVDLC                              |           |

| 3-3        | Loading, Attaching, and Running EVDLD                              | 29<br>จก  |

| 3-3<br>3-4 |                                                                    |           |

| 3-4        | EVDLD Event Flag InstructionsLoading, Attaching, and Running EVDLA | ا ن<br>دو |

|            | Loading, Attaching, and Dunning EVDLA                              | دن<br>م   |

| 3-6        | Loading, Attaching, and Running EVDAC                              | 4         |

# GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

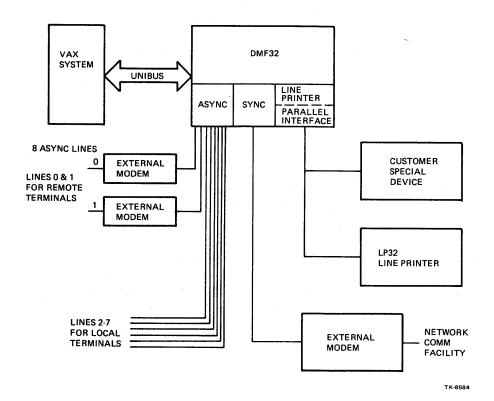

The DMF32 is an intelligent VAX family DMA UNIBUS controller that supports a combination of I/O devices, including the following (see Figure 1-1):

- Eight asynchronous lines

- One synchronous line

- One DMA line printer interface or one enhanced DR11-C functional parallel I/O port

Figure 1-1 DMF32 Overview Block Diagram

#### 2

#### 1.1.1 Asynchronous Multiplexer

The asynchronous multiplexer supports eight transmit and eight receive lines. Each pair of lines (one transmit and one receive) can be programmed to operate at one of 16 baud rates ranging from 50 bps to 19.2 Kbps. Both line 0 and line 1 have split-speed capability and full modem control. The asynchronous multiplexer also supports the auto echo function.

Transmission can be selected for DMA or SILO operation. In SILO mode, each line transmits characters from its own 32-character buffer. These buffers are loaded under host software control. In DMA mode, a transmit line transmits characters from the main memory location specified by the buffer address and character count.

All eight lines share a 48-character receive silo. There is a programmable silo timeout period for the receive silo.

An interrupt can be generated under one of the following conditions:

- Sixteen characters have entered the silo

- The silo has been non-empty for a time greater than a programmable timeout period. This timeout period can be set to zero.

The asynchronous lines are connected either to data terminal equipment (DTE) or data communications equipment (DCE) via standard EIA RS-232-C 25-pin connectors. The signal levels of the asynchronous multiplexer are RS423 compatible ( $1\mu$  second rise time).

#### 1.1.2 Synchronous Interface

The synchronous interface is a single-line DMA communications device with full modem control (EIA RS-232-C/CCITT-V.28). The signal levels of the synchronous interface are RS423 compatible ( $1\mu$  second rise time). The DMA transfers are double buffered; that is, both the transmitter and receiver have two sets of byte count and buffer address registers.

The synchronous interface supports various bit-oriented protocols (SDLC and HDLC) and byte-oriented protocols (DDCMP). The synchronous line can frame the messages, generate and check CRC, and DMA these messages to and from host memory. The host-level software performs all message acknowledgments and higher level network functions.

Running the GEN BYTE protocol (general byte-oriented synchronous) allows the synchronous interface to implement any byte-oriented protocol. The GEN BYTE protocol uses a straight transfer of data between main memory and the synchronous interface. The host-level software handles the protocol-specific functions.

The synchronous interface has modem control. The modem lines conform to EIA RS-232-C/CCITT-V.24 specifications for speeds up to 19,200 bits per second. The synchronous interface is connected to DTE or DCE via the standard 25-pin Cinch connector. Direct connection to another synchronous interface can be done via a null modem cable.

When using the DMF32 crystal-controlled baud rate generator, the synchronous line can transmit at one of sixteen different programmable speeds. With external clocking, any transmit or receive bit rate up to 19.2 kbps can be used. The receiver uses an external clock originating from the modem, except during maintenance testing.

#### 1.1.3 Line Printer Interface

The DMA line printer operates with the LP32 family of printers. This interface also supports low-level formatting functions.

#### 1.1.4 Parallel Interface

This 16-bit parallel interface is an enhanced DR11-C functional interface. It can also support SILO mode (half-duplex) or double-buffered DMA (half-duplex). Since the line printer interface and the parallel interface share hardware, both interfaces cannot be used concurrently.

#### 1.2 PHYSICAL DESCRIPTION

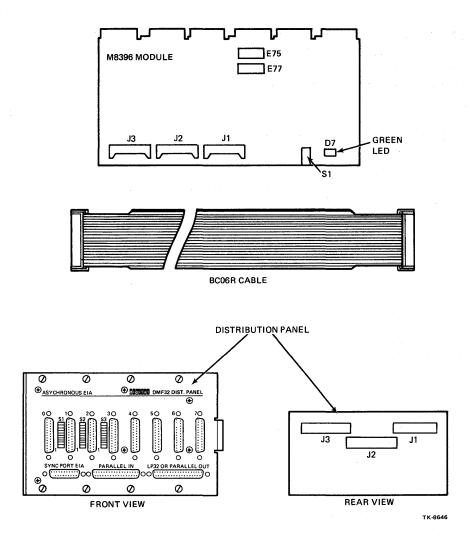

The DMF32 consists of a single hex-size peripheral controller (SPC) module, an 8.25-inch  $\times$  4-inch distribution panel, and three 40-pin shielded BC06R flat cables. The three BC06R cables connect the single hex module to the distribution panel via standard Berg connectors. Refer to Figure 1-2 for the DMF32 components.

The distribution panel has eleven Cinch connectors. Eight connectors are for the eight asynchronous lines, one connector is for the synchronous line, and two connectors are for the parallel port. The distribution panel also has three 10-position DIP switch packs.

#### 4 GENERAL DESCRIPTION

Figure 1-2 DMF32 Components

#### 1.2.1 DMF32 Configurations

The DMF32 is available in three different options; each is designated by two letters (AA, AB, or AC). These options are defined in the following paragraphs.

**1.2.1.1 DMF32-AA Option** – The DMF32-AA option is used in the VAX-11/730 system packages. Table 1-1 lists the contents of this option.

Table 1-1 DMF32-AA Options

| Part Number | Description                                             |

|-------------|---------------------------------------------------------|

| M8396       | Hex module                                              |

| BC06R-7     | 40-conductor cable                                      |

| 70-18754-00 | Distribution panel assembly                             |

| H3248       | Single-line loopback                                    |

| EK-DMF32-UG | DMF32 User's Guide                                      |

| MP01271     | DMF32 Field Maintenance Print Set                       |

|             | M8396<br>BC06R-7<br>70-18754-00<br>H3248<br>EK-DMF32-UG |

1.2.1.2 DMF32-AB Option - The DMF32-AB option is used in the BA11-KW expander cabinets. This option is identical to the DMF32-AA except that it has three BC06R-10 cables instead of three BC06R-7, and contains the additional items listed in Table 1-2.

Table 1-2 DMF32-AB Option Additional Contents

| Quantity | Part Number | Description                                |

|----------|-------------|--------------------------------------------|

| 1        | 74-27040-01 | H9544-SJ frame, I/O non-shielded           |

| 4        | 90-09700-00 | Screws, Sems Truss Phillips                |

| 4        | 90-06664-00 | Washer, flat SST                           |

| 4        | 90-07786-00 | Nut, U-nut Retainer (.240 inside diameter) |

1.2.1.3 DMF32-AC Option - This option is identical to the DMF32-AA except that it has three BC06R-12 cables instead of three BC06R-7 cables.

#### 1.2.2 Test Connectors

The H3248 and H3249 test connectors, shown in Figure 1-3, are used with the DMF32. Only the H3248 test connector is included in the DMF32 options. The H3248 plugs into the distribution panel to loop back data and modem signals on a single line. The H3249 test connector connects to the M8396 module via the three BC06R cables. This arrangement provides staggered turnaround of the data and modem lines, testing both the M8396 module and cables.

Figure 1-3 DMF32 Test Connectors

#### 1.3 GENERAL SPECIFICATIONS

This section provides the information on the necessary environment, power specifications, device functional specifications, and performance parameters.

#### 1.3.1 Environment

Table 1-3 lists the environment specifications for the DMF32.

**Table 1-3 Environmental Specifications**

| Environment           | Specification                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------|

| Class B Environment   | 10C (50°F) to 40C (104°F)                                                                  |

| Operating Temperature | Where maximum temperature is reduced 1.8°C per 1000 meters (1°F per 1000 feet) of altitude |

| Relative Humidity     | 10% to 90% with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (36°F)     |

| Cooling               | 11 cubic feet per minute                                                                   |

| Heat Dissipation      | 175 BTU per hour                                                                           |

#### 1.3.2 Power Specifications

The SPC slot the DMF32 is plugged into provides the power for the DMF32. The electircal requirements are as follows:

- 8.0 amperes @ +5 Vdc

- 0.5 amperes @ +15 Vdc

- 0.5 amperes @ -15 Vdc

#### 1.3.3 DMF32 Functional Parameters

Tables 1-4 through 1-7 list the functional parameters for the devices of the DMF32.

**Table 1-4 Synchronous Functional Parameters**

| Parameter           | Description                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------|

| DMA Transfer        | Double-Buffered                                                                                              |

| Protocols Supported | DDCMP, SDLC, HDLC, GEN BYTE                                                                                  |

| Protocol Functions  | Bit stuffing, bit removal, cyclic redundancy check generation and recognition, framing messages              |

| Modem Lines         | EIA RS-232-C/CCITT-V.24                                                                                      |

| Data Rates          | 800, 1200, 1760, 2152, 2400, 4800, 9600 and 19200 bits per second using internally genenrated transmit clock |

**Table 1-5 Asynchronous Functional Parameters**

| Parameter          | Description                                                                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode     | Full-duplex or half-duplex                                                                                                                             |

| Data Format        | Asynchronous, serial by bit, one start bit, and 1 or 2 stop bits provided by the hardware under program control.                                       |

| Character Size     | 5, 6, 7, or 8 bits, program-selectable. (Does not include the parity bit.)                                                                             |

| Parity             | Parity is program-selectable. There can be odd, even, or no parity. If parity is selected, a parity bit is added to the character in the MSB position. |

| Order of Bits      | Transmission/reception low-order bit first                                                                                                             |

| Data Rates         | 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 3600, 4800, 7200, 9600, and 19200 bits per second                                           |

| Split Speed        | Line 0 and line 1 only                                                                                                                                 |

| Full Modem Control | Line 0 and line 1 only                                                                                                                                 |

| Asynchronous Lines | RS-232-C compatible                                                                                                                                    |

Table 1-6 Parallel Interface Functional Parameters

| Parameter          | Description           |

|--------------------|-----------------------|

| Data Input         | 16 bits parallel in   |

| Data Output        | 16 bits parallel out  |

| Electrical Signals | Similar to the DR11-C |

**Table 1-7 Printer Controller Functional Parameters**

| Parameter               | Description                                                                        |  |

|-------------------------|------------------------------------------------------------------------------------|--|

| Printer Supported       | LP25, LP26, LP07                                                                   |  |

| Formatting Capabilities | Tab expansion, lower case to upper case conversion, line wrap, ff to If conversion |  |

#### 1.3.4 DMF32 Performance Parameters

Each of the eight asynchronous lines may transmit and receive at a maximum speed of 19,200 bits per second. The synchronous line may transmit and receive at a maximum speed of 19,200 bits per second. However, all of these lines may not operate at their maximum speed concurrently.

#### 1.3.5 Installation Distances

The recommended distance from the DMF32 to the RS-232-C/CCITT-V.24 terminal or modem is 15 meters (50 feet) at up to 9600 bps with a BC22 or similar cable. Operation which exceeds 50 feet does not meet the distances recommended in RS-232-C/CCITT-V.24. Operation is often possible at longer distances, depending on the terminal equipment, type of cable, speed of operation, and electrical environment. For these reasons, DIGITAL cannot guarantee error-free operation at distances greater than 15 meters (50 feet).

The DMF32 can be connected to local DIGITAL terminals (and most other terminals) at distances greater than 50 feet with acceptable results if the terminal and computer are in the same building, in a modern office environment. A shielded twisted pair cable (Belden 8777 or equivalent) is recommended and used in the BC22D null modem cable.

#### NOTE

The ground potential difference between the DMF32 and the terminal must not exceed two volts. This condition limits operation to within a single building served by one ac power service.

#### 2.1 SCOPE

This chapter describes the procedures for unpacking, installing, and checking out the DMF32.

#### 2.2 UNPACKING AND INSPECTION

The DMF32 is packed according to commercial packing practices. Remove all packing materials and check the equipment against the shipping list. Table 1-1 lists the items contained in the DMF32 options. Inspect all items and carefully check the module for cracks, loose components, and breaks in the etched paths. Report damages or missing items to the shipper immediately and inform the DIGITAL representative.

#### 2.3 DEVICE AND VECTOR ADDRESS ASSIGNMENTS

The DMF32's device addresses are selected from the floating address space of the UNIBUS input/output (I/O) page. The E75 switch pack on the DMF32 selects the first DMF32 CSR address. The DMF32 calculates the other DMF32 CSR addresses from the first address.

When there are no floating devices before the DMF32, the first floating address space for a DMF32 is 760340 (FE0E0 hex). The second floating address space for a DMF32 is 760400 (FE100 hex). The third floating address space for a DMF32 is 760440 (FE120 hex). When operating under VMS, the actual address(es) can be determined by using the SYSGEN utility. Refer to the *VAX/VMS Guide to Writing a Device Driver* (AA-H499B-TE) for the procedure to determine CSR address assignments.

There are no switches on the DMF32 for interrupt vectors. At autoconfigure time, the operating system loads the value of the base vector into the DMF32. The DMF32 calculates the other DMF32 vectors from this base vector.

#### 2.4 INSTALLATION PROCEDURE

#### 2.4.1 M8396 Module Installation

To install the M8396, perform the following steps.

Set the switches on the E77 switch pack to the correct priority level; also set switch 1 (E77) to ON and switch 10 (E77) to OFF. Refer to Figure 2-1 for the switch settings. Also confirm that all eight jumpers are installed on the DMF32. Table 2-1 lists the DMF32 jumper functions, and Figure 2-1 shows the jumper locations. 10

Figure 2-1 DMF32 Switch Settings and Jumper Locations

TK-8589

Name Jumper **Function** W1 **UNIBUS INIT** Out - Disables UNIBUS Init In - Enables UNIBUS Init W2 SYNC DSR Always installed W3 **RX D RTN** Always installed W4 **DSR RTN** Always installed W5 DCE TX CLK RTN Always installed W6 DCE RX CLK RTN Always installed W7 **ASYNC 0 DSR** Always installed **W8 ASYNC 1 DSR** Always installed

Table 2-1 DMF32 Jumper Functions

- 2. Set the switches on E75 for the DMF32 CSR address. Refer to Section 2.3 and Figure 2-1 for the correct E75 switch settings.

- 3. The DMF32 can be installed into any slot that provides 8 amperes at +5V and 0.5 amperes at +15V and -15V. Refer to the appropriate VAX-11 installation manual for the location of SPC slots into which the DMF32 can be installed. Table 2-2 lists the VAX family installation manuals.

#### **CAUTION**

Do not insert or remove the M8396 module with power ON. Insert and remove the module slowly and carefully to avoid catching components on the card guides or changing the switch settings.

Table 2-2 VAX Family Installation Manuals

| VAX System<br>Number | Title                                            | Document    |

|----------------------|--------------------------------------------------|-------------|

| VAX-11/780           | VAX-11/780 Installation Manual                   | EK-SI780-IN |

| VAX-11/750           | VAX-11/750 Installation and<br>Acceptance Manual | EK-SI750-IN |

| VAX-11/730           | VAX-11/730 Installation Guide                    | EK-SI730-IN |

#### 2.4.2 DMF32 Distribution Panel Installation

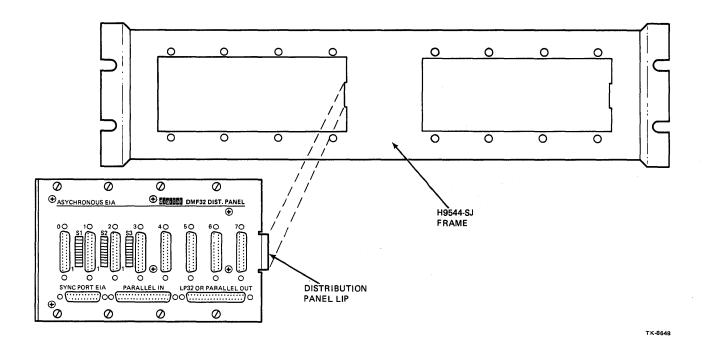

The DMF32 distribution panel is mounted in either a H9544-SJ mounting frame or a shielded bulkhead panel. To mount the distribution panel into the frame opening, position the distribution panel at an angle so that the lip of the distribution panel is behind the frame. The distribution panel is secured to the frame by eight screws.

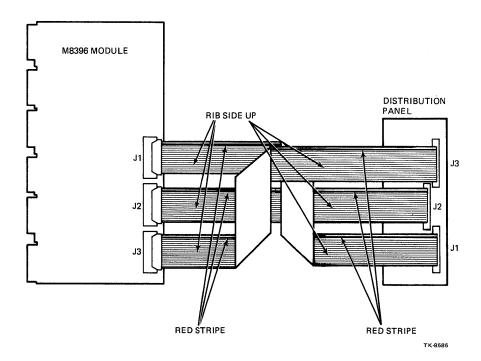

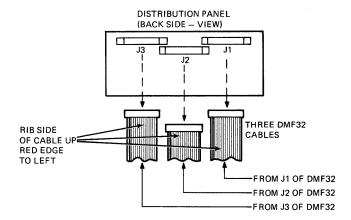

The BC06R-XX cables are connected from M8396 J1 to distribution panel J1, J2 to J2, and J3 to J3. To connect the cables in this way, the cables for J1 and J3 are crossed over. When connecting each cable, make sure that the cable's rib side is facing up and the red strip is on the correct side.

#### 2.4.3 Distribution Panel Installation Procedure

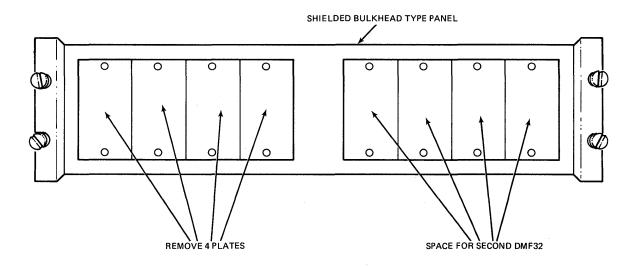

- Determine if the system/expander cabinet has a shielded bulkhead type panel included as part of the cabinet. If the system/expander cabinet DOES contain a shielded bulkhead type panel, continue with Step 2. If system/expander cabinet DOES NOT contain a shielded bulkhead type panel, proceed to Step 4.

- 2. Remove the four 2 inch plates from the bulkhead panel to enable mounting the DMF32 distribution panel (refer to Figure 2-2).

Figure 2-2 Shielded Bulkhead Type Panel

TK-8647

- 3. Discard the H9544-SJ "picture frame" (see Figure 2-3) from the DMF32-AB option package, since the frame is not used with the system/expander cabinets that contain the shielded bulkhead type frame. Now proceed to Step 7.

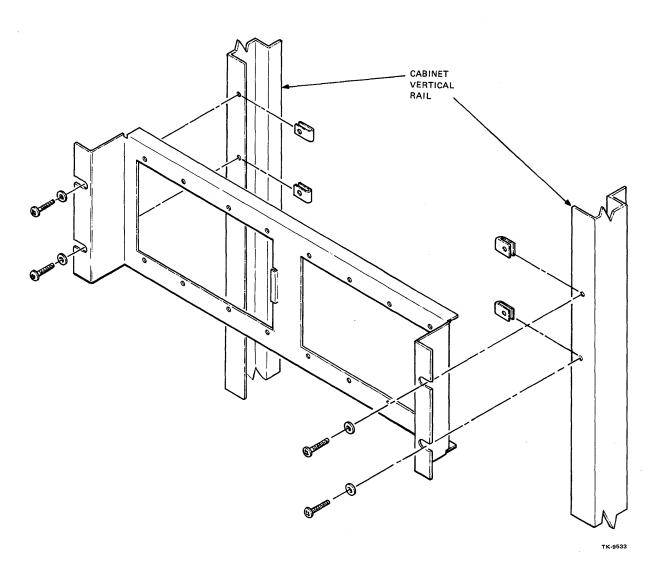

- 4. Remove the H9544-SJ picture frame from the DMF32-AB option package. Refer to Figure 2-3 to identify the frame.

- 5. Align the H9544-SJ frame on the cabinet vertical rails in the desired location. Mark the rail holes for reference, then install the U-nuts supplied with the option (see Figure 2-3).

- 6. Mount the H9544-SJ frame to the vertical rails of the cabinet with the screws and washers supplied.

Figure 2-3 H9544-SJ Frame Installation

- 7. Install the BC06R-XX cables, if these cables have not yet been installed. The BC06R-XX cables are connected from the M8396 module to the DMF32 distribution panel: J1 to J1, J2 to J2, and J3 to J3. To make these connections, cables from J1 and J3 must be crossed (see Figure 2-4). Refer to the proper VAX-11 installation manual for the proper cable routing. Table 2-2 list the VAX-11 installation manuals.

- 8. Connect the BC06R-XX cables to J1, J2, and J3 of the M8396 module.

- Pull the ends of the three BC06R-XX cables through the H9544-SJ/ shielded frame bulkhead opening that the DMF32 distribution panel is to be mounted in.

#### **CAUTION**

Connecting the BC06R-XX cables incorrectly can cause damage to the parallel port on the M8396.

Figure 2-4 BC06R Cable Connections

- 10. Connect the three BC06R-XX cables to the distribution panel, making sure that the cable's rib side is up and the red strip is on the correct side (see Figure 2-4).

- 11. Position the distribution panel at an angle so that the lip of the distribution panel is behind the frame (see Figure 2-5).

- 12. Secure the distribution panel to the frame with the eight capture screws (part of the distribution panel).

#### 2.4.4 BC06R Cable Routing

Refer to the appropriate VAX-11 installation manual for the BC06R cable routing. Table 2-2 lists the appropriate VAX family installation manuals.

Figure 2-5 DMF32 Distribution Panel Installation

#### 2.4.5 Verifying Standalone Operation

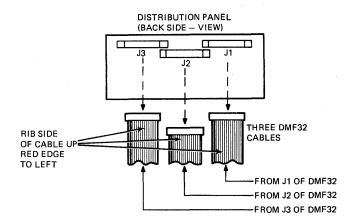

Run the Level 3 diagnostics with the H3249 staggered turnaround connector to verify the standalone operation of the DMF32. To verify the standalone operation, perform the following steps.

- 1. Connect the staggered turnaround connector (see Figure 2-6).

- 2. Run the Level 3 diagnostics listed in Table 2-3.

- 3. Disconnect the H3249 staggered turnaround connector. Connect the three BC06R cables to the distribution panel as shown in Figure 2-6.

STEP 1 — DISCONNECT THE THREE DMF32 CABLES FROM BACK SIDE OF THE DISTRIBUTION PANEL

Figure 2-6 Staggered Connector Installation

Table 2-3 Level 3 Diagnostics

| Diagnostic | Section Tested    | Operating Instruction |

|------------|-------------------|-----------------------|

| EVDLB      | Synchronous port  | Section 3.2.2         |

| EVDLC      | Asynchronous port | Section 3.2.3         |

| EVDLD      | Parallel port     | Section 3.2.4         |

#### 2.4.6 Communications Equipment Interface Cabling

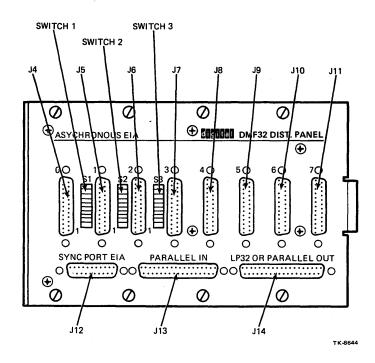

Connect the cables from the distribution panel to the communications devices, printers, terminals, etc. Figure 2-7 shows the connectors on the distribution panel. Table 2-4 lists the recommended cables.

Figure 2-7 DMF32 Distribution Panel

**Table 2-4 Recommended Cables**

| erminals                 |

|--------------------------|

|                          |

| C modems (lines 0 and 1) |

| modem                    |

| LP26                     |

|                          |

|                          |

<sup>\*</sup> The BC27A cable or the BC27B cable is provided with the LP32 option.

#### 2.4.7 Distribution Panel Switch Settings

Set the switches of the three switch packs on the distribution panel. Refer to Figure 2-7 for the switch pack locations. Table 2-5 lists the switch settings for the asynchronous line 0 (switch 1) and asynchronous line 1 (switch 2). Table 2-6 lists the switch settings for the synchronous line (switch 3). Table 2-7 lists the switch settings (switch 3) for the DMF32 device configurations. Table 2-8 shows the functions of jumpers W1 and W2 on the distribution panel. Both jumpers are normally installed.

Table 2-5 Common Switch Setups for Asynchronous Lines 0 and 1

| Switch Packs<br>1 and 2 | Local<br>Terminal | Modems and H3248<br>Single-Line Connector |

|-------------------------|-------------------|-------------------------------------------|

| Switch 1                | OFF               | OFF                                       |

| Switch 2                | ON                | ON                                        |

| Switch 3                | OFF               | OFF                                       |

| Switch 4                | ON                | ON                                        |

| Switch 5                | ON                | ON                                        |

| Switch 6                | ON                | ON                                        |

| Switch 7                | ON                | ON                                        |

| Switch 8                | ON                | OFF                                       |

| Switch 9                | ON                | ON                                        |

| Switch 10               | ON                | ON                                        |

Table 2-6 Common Switch Set-ups for the Synchronous Line

| Switch Pack 3 | Modems and H3248 Single<br>Line Loopback Connector |

|---------------|----------------------------------------------------|

| <br>Switch 1  | ON                                                 |

| Switch 2      | ON                                                 |

| Switch 3      | ON                                                 |

| Switches 6-10 | Not used                                           |

**Table 2-7 DMF32 Device Configuration**

| Switch Pack 3 |              | Active Device                                 |

|---------------|--------------|-----------------------------------------------|

| Switch 4 ON   | Switch 5 ON  | Asynchronous                                  |

| Switch 4 OFF  | Switch 5 ON  | Asynchronous, LP32                            |

| Switch 4 ON   | Switch 5 OFF | Asynchronous, parallel interface, synchronous |

| Switch 4 OFF  | Switch 5 OFF | Asynchronous, LP32, synchronous               |

**Table 2-8 Distribution Panel EIA Selection Jumpers**

| Jumper W1 | Jumper W2 | Function                                                         |

|-----------|-----------|------------------------------------------------------------------|

| In or Out | In        | Signal ground connected directly to frame ground                 |

| In        | Out       | Signal ground connected to frame ground through 100-ohm resistor |

| Out       | Out       | Signal ground isolated from frame ground                         |

#### 2.4.8 Verifying System-Integrated Operation

To verify system-integrated operation, run the DMF32 Level 2R diagnostics as follows:

- 1. Place all modems into loopback mode.

- 2. If modem loopback mode is not available, install a H3248 single-line loopback connector on one of the asynchronous connectors, and install a H3248 single-line loopback connector on the synchronous connector.

- 3. Run the DMF32 Level 2R diagnostics listed in Table 2-9.

Table 2-9 DMF32 Level 2R Diagnostics

| Diagnostic | <b>Section Tested</b> | Operating Instruction |

|------------|-----------------------|-----------------------|

| EVDLA      | Synchronous port      | 3.3.2                 |

| EVDAC      | Asynchronous port     | 3.3.3                 |

- 4. Return all modems to the normal mode of operation.

- 5. Disconnect the H3248 single-line connector and reconnect any disconnected cables.

- 6. Set the three switch packs on the distribution panel for normal mode of operation. Refer to Tables 2-5, 2-6, and 2-7 for the switch settings.

- 7. The attached devices can be verified by running the following user-level diagnostics.

**EVAAA - Line Printer Diagnostic**

**EVTAA - Terminal Diagnostic**

**EVTBA - Terminal Exerciser**

**EVDLF - Data Link Test**

# DMF32 DIAGNOSTICS

#### 3.1 INTRODUCTION

This chapter describes using the DMF32 diagnostics. The DMF32 is supported by both Level 3 and Level 2R diagnostics. The Level 3 diagnostics are standalone diagnostics that run under the Diagnostic Supervisor using direct I/O. There are three Level 3 diagnostics: EVDLB, EVDLC, and EVDLD. These diagnostics verify the functionality of the DMF32 as follows:

EVDLB-verifies the synchronous interface EVDLC-verifies the asynchronous multiplexer EVDLD-verifies the parallel interface

The Level 2R diagnostics enable fault isolation to the option level while running under VMS. Various loopback methods can be used at either the distribution panel connector, modem cable, local modem, or remote modem. These various loopback methods can isolate the fault to a specific component of the network. Also, the Level 2R diagnostics can be used to provide a complete link between the DMF32 and another DMF32 or similar device for end-to-end function verification.

The Level 2R diagnostics, running under the Diagnostic Supervisor, use the QIO interface of the VMS device driver. There are two DMF32 Level 2R diagnostics: EVDAC and EVDLA. EVDAC verifies the functionality of the asynchronous multiplexer, and EVDLA verifies the functionality of the synchronous interface.

#### 3.1.1 Diagnostic Supervisor

Both Level 3 and Level 2R diagnostics run under the Diagnostic Supervisor. Loading and using the Diagnostic Supervisor are described in both the *VAX-11/730 Diagnostic System Overview Manual* (EK-DS730-UG) and the *VAX Diagnostic System User's Guide* (EK-VX11D-UG).

#### 3.1.2 DMF32 CSR Address and Vector Address

The DMF32 CSR address 760340 is used as an example address in the following diagnostic procedures. The actual address depends on the switch settings of E77 on the DMF32.

The vector address is used as an example address. The actual address is floating; thus the vector address depends on the UNIBUS configuration.

When running under VMS, the actual CSR address and vector address can be determined. Use the VMS utility SYSGEN to determine the actual addresses.

#### 3.1.3 Hardware Loopback Methods

There are five loopback methods that can be used in running the DMF32 diagnostics. These loopback methods are sometimes referred to as "wraps". The five loopback methods are as follows:

- Internal wrap

- H3248 single-line loopback connector

- H3249 staggered loopback connector

- Local modem

- Programmable modem

- **3.1.3.1** Internal Wrap The internal wrap enables the data to be internally looped within the DMF32. No external loopback connector is needed with the internal wrap. This wrap tests the DMF32's functionality (except the drivers, the receivers, the cables from the DMF32 to the distribution panel, and the distribution panel).

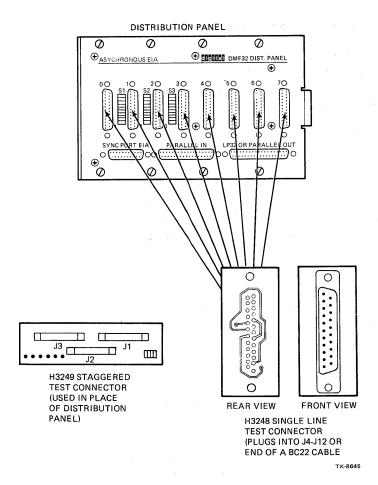

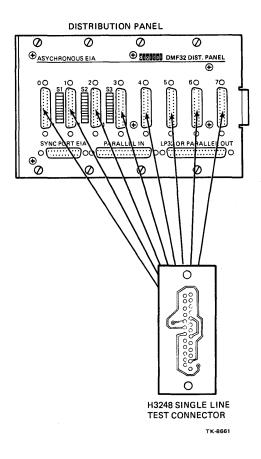

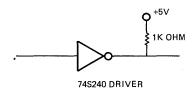

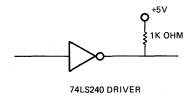

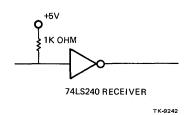

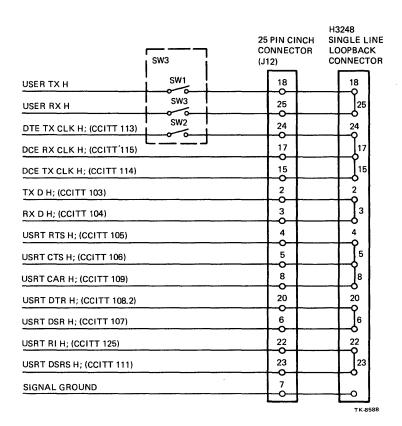

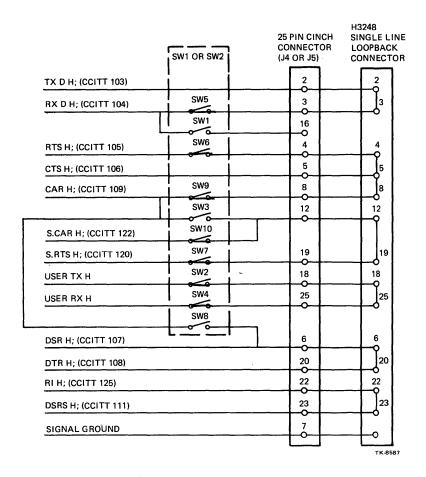

- **3.1.3.2** H3248 Single-Line Loopback Connector The H3248 single-line loopback connector can be used when running the synchronous or asynchronous diagnostics. When the H3248 is used, the functionality of the drivers, receivers, cables from the DMF32 to the distribution panel, and the distribution panel are verified. The H3248 single-line loopback connector is connected to the line that is to be tested. Figure 3-1 shows how the H3248 single-line loopback connector is connected.

Figure 3-1 Single-Line Connector Installation

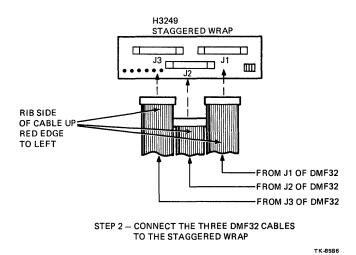

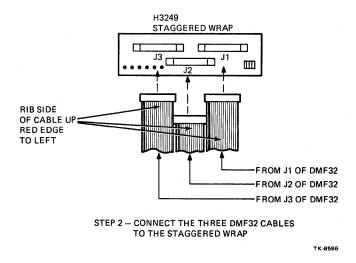

**3.1.3.3 H3249 Staggered Loopback Connector** – The H3249 staggered loopback connector can be used with any of the diagnostics, except EVDAC. This loopback connector is used to test the functionality of the DMF32 up to the distribution panel (exclusive of the distribution panel). The H3249 staggered loopback connector is required to test specific asynchronous multiple functions and to loop back the parallel port. Figure 3-2 shows how the H3249 staggered loopback connector is connected.

The dip switch pack on the H3249 staggered loopback connector is used for the following purpose. Switch 1 (H3249) is equivalent to switch 4 of SW-3 (distribution panel), and switch 2 (H3249) is equivalent to switch 5 of SW-3 (distribution panel). Both switches 3 and 4 (H3249) are not used. Refer to Table 2-7 for the equivalent switch positions of switches 1 and 2 (H3249).

The H3249 staggered loopback connector is part of each spares kit.

STEP 1 — DISCONNECT THE THREE DMF32 CABLES FROM BACK SIDE OF THE DISTRIBUTION PANEL

Figure 3-2 Staggered Connector Installation

- **3.1.3.4 Local Modem** Local modem is used when a modem is manually selected for analog (local) loopback testing. Any modem that can internally loop back data may be selected.

- **3.1.3.5 Programmable Modem** When a programmable modem is used, no manual intervention is required for local loopback. A programmable modem is any device that, whenever the diagnostics assert User TX (pin 18), provides a loopback path between the transmit data and the receive data.

#### 3.1.4 Distribution Panel Switch Settings

When asynchronous or synchronous diagnostics are run with the H3248 attached, the switches on the distribution panel must be set as listed in Table 3-1.

#### 3.1.5 Self Test

After each power-up, the DMF32 performs a self test. The first test of the EVDLB diagnostic verifies if this self test has been completed satisfactorily. The self test checks the following hardware elements:

- 1. 2901 ALU can perform computations correctly.

- 2. 2901 A and B registers can be addressed properly.

- 3. Condition codes can be set properly.

- 4. The local store RAM is operational.

- 5. The micro PC stack functions to four levels of the subroutine call correctly.

- 6. The UNIBUS slave trap hardware functions correctly.

- 7. The UNIBUS master I/O addressing and data transfers function correctly.

**Asynchronous Diagnostic Synchronous Diagnostic** Switches S1 and S2 Switch S3 **Switch** State Switch State **OFF** ON 1 1 2 ON 2 ON 3 **OFF** ON 4 Not used ON 4-10 5 ON 6 ON 7 ON 8 **OFF** 9 ON 10 ON

**Table 3-1 Distribution Panel Switch Settings**

### 3.2 DMF32 LEVEL 3 DIAGNOSTICS

There are three Level 3 diagnostics used to support the DMF32: EVDLB, EVDLC, and EVDLD. These diagnostics operate under the VAX Diagnostic Supervisor (DS). Table 3-2 lists some of the parameters of these diagnostics.

# 3.2.1 Level 3 Hardware Prerequisites

The following must be functional before the Level 3 diagnostics may be used.

- VAX-11 CPU

- Memory (256 KB minimum)

- UNIBUS adapter (DW730, DW750, or DW780, as applicable)

- Green LED on the DMF32 must be illuminated

# 3.2.2 EVDLB Diagnostic Description

The EVDLB diagnostic tests the synchronous port only; it ignores devices on the asynchronous and parallel ports. The default section of the EVDLB diagnostic provides internal loopback testing (no external loopback connector is required). An external connector (single-line loopback connector or the H3249 staggered loopback connector) can be used to verify the complete functionality of the synchronous interface.

The manual section of the EVDLB diagnostic provides for external loopback testing using the local modem or the remote modem as the rloopback device. Using the remote modem verifies the functionality of the communications facilities.

**3.2.2.1 Loading, Attaching, and Running EVDLB** – After the Diagnostic Supervisor is loaded, the operating instructions in Example 3-1 can be used for the EVDLB diagnostic. The underlined portions are what the user enters into the system.

| Diagnostic                              | EVDLB                     | EVDLC                                 | EVDLD                                     |

|-----------------------------------------|---------------------------|---------------------------------------|-------------------------------------------|

| Section<br>Tested                       | Synchronous port (DMF32S) | Asynchronous port (DMF32A)            | Parallel port<br>(DMF32P)                 |

| Generic Device                          | XGA0                      | TXA                                   | LCA                                       |

| VAX Diagnostic<br>Supervisor<br>Version | 6.6 of later              | 6.6 of later                          | 6.6 or later                              |

| Running Time                            | 1 minute                  | 3.00 minutes<br>(quick flag<br>clear) | 40 seconds<br>with H3249 or<br>LP on port |

|                                         |                           | 0.5 minutes<br>(quick flag set)       | 25 seconds<br>with nothing on<br>the port |

```

DIAGNOSTIC SUPERVISOR. ZZ-ENSAA-6.6-xxx dd-mm-yyyy hh:mm:ss.ss

; Loads synchronous port diagnostic

DS] LOAD EVDLB

DS] ATTACH DW730 HUB DW0

; Attaches UBA to 11/730

or

; Attaches UBA to 11/750

DS] ATTACH DW750 HUB DW0

DS] ATTACH DW780 SBI DW0 3 4

; Attaches UBA to 11/780

; Attaches DMF32 synchronous port

DS] ATTACH DMF32S

DEVICE LINK? DWØ

; The option is linked to the UBA

; The option is named XGAØ

DEVICE NAME? XGAØ

CSR? 760340

; The CSR address is 760340 (range

; = 760000-777776)

; Vector is 300 (range = 300-766)

VECTOR? 300

; BR interrupt level is 5

BR? 5

; (range = 5-6)

NONE - No external loopback

EXTERNAL WRAP? NONE

connector is connected

H3248 or H3249 loopback

WRAP

;

connector is connected

; MODEM -

External modem connected

DS] SEL XGAØ

; Selects the synchronous port to

; be run

If UNIBUS Init jumper W1 has been removed, event flag 2 must be

set before running the EVDLB diagnostic.

; Sets event flag 2

DS] SET EVENT 2

NOTE

To run EVDLB, the S3 switches on the

```

distribution panel must be set (refer to

; Runs the diagnostic

Example 3-1 Loading, Attaching, and Running EVDLB

Section 3.1.4).

DS) START

# 3.2.3 EVDLC Diagnostic Description

The EVDLC diagnostic tests the asynchronous port only; it ignores devices on the synchronous and parallel ports. This diagnostic performs both DMA and SILO mode testing with either an internal or external loopback connector connected. The EVDLC diagnostic has two sections: default and manual intervention.

The default section provides for internal loopback testing when no external loopback connector is used. Also, when an H3248 single-line loopback connector or a programmable modem is used, the default section provides an external loopback path for all the modem signals. Using the H3249 staggered loopback connector provides complete functional testing of the asynchronous device.

The default parameters are as follows:

- 8 bits per character

- 1 stop bit

- Parity disabled

- Baud rate selected from attach sequence

The manual section provides for external loopback testing when a nonprogrammable modem or a remote modem is used as the loopback device. Using the remote modem verifies the communications facilities.

**3.2.3.1 Loading, Attaching, and Running EVDLC** – After the Diagnostic Supervisor is loaded, the operating instructions in Example 3-2 can be used for the EVDLC diagnostic. The underlined portions are what the user enters into the system.

### 3.2.4 EVDLD DIAGNOSTIC DESCRIPTION

The EVDLD diagnostic tests the DMF32 parallel port only; it ignores the devices on the synchronous and asynchronous ports. This diagnostic tests both the parallel interface and line printer controller functions of the DMF32. To fully test the DMF32 line printer logic, a line printer must be attached to the line printer port. To fully test the DMF32 parallel interface logic, an H3249 loopback connector must be attached to the J2 and J3 connectors.

Testing the parallel port with the H3249 loopback connector is preferred since this is the only way that the parallel interface is completely tested. When neither a line printer or H3249 staggered loopback connector is attached to the parallel port, only the control and status register tests are performed. The diagnostic CSR low byte is used to loop the data that would normally be transferred to the printer. This tests the format functions without an attached printer.

**3.2.4.1 Loading, Attaching, and Running EVDLD** – After the Diagnostic Supervisor is loaded, the operating instructions in Example 3-3 can be used for the EVDLD diagnostic. The underlined portions are what the user enters into the system.

```

DIAGNOSTIC SUPERVISOR. ZZ-ENSAA-6.6-xxx dd-mm-yyyy hh:mm:ss.ss

; Loads asynchronous port diagnostic

DS) LOAD EVDLC

DS) ATTACH DW730 HUB DW0

; Attaches UBA to 11/730

or

DS] ATTACH DW750 HUB DW0

; Attaches UBA to 11/750

DS) ATTACH DW780 SBI DW0 3 4; Attaches UBA to 11/780

DS] ATTACH DMF32A

; Attaches the asynchronous

; diagnostic

; Option is linked to the UBA

DEVICE LINK? DWØ

DEVICE NAME? TXA

; The option is named TXA (range =

; A-F)

; The CSR address is 760340 (range =

CSR? 760340

; 76ØØØØ-777776)

VECTOR? 300

; Vector address is 300 (range =

; 300-766)

BR? 5

; BR interrupt level is 5 (range =

; 5-6)

ACTIVE LINES? 377

; All lines to be tested (octal bit

; map of lines to be tested)

; bit \emptyset = line \emptyset

; bit 1 = line 1, etc. (range =

; ØØØ-377)

; Baud rate that is to be used in

BAUD RATE? 9600

; external wrap tests. This parameter ; determines the line speed for the

; remote loopback (manual) modem test; and the single-line loopback test.

; Baud rates that can be selected are

; 50, 75, 110, 135, 150, 300, 600, ; 1200, 1800, 2000, 2400, 3600, 4800, ; 3600, 4800, 7200, 9600, 19200

WRAP TYPE? INTERNAL

INTERNAL - Data loopback path is

internal to the DMF32

H3248 - Single-line loopback

connector is connected at

the distribution panel H3249 - Staggered loopback

connector is used

LOCAL MODEM - A modem manually

selected for analog

(local) loopback testing

PROGRAMMABLE MODEM - A modem that

selects analog (local)

loopback test mode when

EIA pin 18 is asserted

UNIBUS INIT JUMPER? YES

; YES - Jumper W1 installed on DMF32 ; \overline{\text{NO}} - No jumper W1

DS) SEL TXA

; Select the device to run

NOTE

Sl and

S2 switches on the

distribution panel must be set (refer to Section 3.1.4) before running EVDLC.

DS] START

; Starts running the program

```

Example 3-2 Loading, Attaching, and Running EVDLC

```

DIAGNOSTIC SUPERVISOR. ZZ-ENSAA-6.6-xxx dd-mm-yyyy hh:mm:ss.ss

DS] LOAD EVDLD

; Loads the parallel port

DS] ATTACH DW730 HUB DW0

; Attaches UBA to 11/730

or

DS] ATTACH DW750 HUB DW0

; Attaches UBA to 11/750

DS] ATTACH DW78Ø SBI DWØ 3 4

; Attaches UBA to 11/780

DS] ATTACH DMF32P

; Attaches the parallel port

; diagnostic

DEVICE LINK? DWØ

The option is linked to

; the UBA

DEVICE NAME? LCA

; The option is named LCA

CSR] 760340

; The CSR address is 760340

; (range = 760000-777776)

VECTOR? 300

; Vector address is 300

; (range = 300-776)

; BR interrupt level is 5

BR? 5

; (range = 5-6)

; OTHER - Other than an H3249

PORT DEVICE? OTHER

staggered loopback connector or line

printer is

connected

; LP - Line printer is

connected

WRAP - H3249 loopback

connector is

connected

; Select the parallel port

DS] SEL LCA

; to be run

; Start running the program

DS] START

```

Example 3-3 Loading, Attaching, and Running EVDLD

**3.2.4.2 EVDLD Event Flags** – The EVDLD diagnostic uses three event flags: EV3, EV4, and EV5. The EV3 flag indicates to the diagnostic whether DMF32 jumper W1 has been removed. The EV4 and EV5 flags control the buffer type error message printouts. Refer to Table 3-3 for the EVDLD event flags. Example 3-4 shows EVDLD Event Flag instructions.

### 3.3 DMF32 LEVEL 2R DIAGNOSTICS

There are two Level 2R diagnostics used to support the DMF32: EVDLA and EVDAC. Both operate under the VAX Diagnostic Supervisor (DS) with VMS. Table 3-4 lists some of the parameters for these diagnostics.

Table 3-3 EVDLD Event Flags

| Event<br>Flag<br>State | EV3                                                                | EV4                                                     | EV5                                                                                                                            |

|------------------------|--------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Clear                  | UNIBUS Init will<br>affect the DMF32<br>(jumper W1<br>installed)   | Only first eight<br>errors in a buffer<br>are displayed | No effect                                                                                                                      |

| Set                    | UNIBUS Init will<br>not affect the<br>DMF32 (jumper<br>W1 removed) | All errors in the buffer are displayed                  | Entire buffer is<br>dumped regardless<br>of whether the data<br>is erroneous or not<br>(EV4 need to be set<br>when EV5 is set) |

DS] <u>SET EVENT 4,5</u>; Sets event flags 4 and 5

DS] <u>SHOW EVENTS</u>; Shows all event flags that are ; currently set

DS) CLEAR EVENTS 4,5 ; Clears event flags 4 and 5

Example 3-4 EVDLD Event Flag Instructions

Table 3-4 DMF32 Level 2R Diagnostic Parameters

| Diagnostic                           | EVDLA            | EVDAC             |

|--------------------------------------|------------------|-------------------|

| Section Tested                       | Synchronous port | Asynchronous port |

| Generic Device                       | XGA0             | TXA               |

| VMS Release                          | 3A or later      | 3A or later       |

| VAX Diagnostic<br>Supervisor Version | 6.6 or later     | 6.6 or later      |

# 3.3.1 Level 2R Hardware Prerequisites

The following must be functional before the Level 2R diagnostics may be used.

- VAX-11 CPU

- Memory (128 KB minimum)

- UNIBUS adapter (DW730, DW750, or DW780, as applicable)

- Green LED on the DMF32 must be illuminated

# 3.3.2 EVDLA Diagnostic Description

The EVDLA provides integrity testing and fault detection for the synchronous device while operating under VMS. The operating system (VMS) produces the error reports, which identify the failing functional area of the synchronous device, and the status reports of the synchronous device.

**3.3.2.1 Loading, Attaching, and Running EVDLA** – The instructions in Example 3-5 are used to load, attach, and run EVDLA. It is assumed that VMS is already loaded. Again, user input is underlined.

# 3.3.3 EVDAC Diagnostic Description

The EVDAC diagnostic tests the functionality of the asynchronous multiplexer while operating under VMS. This diagnostic has two selectable sections: default and link.

The default section is used for all normal testing. The link section is used for link testing. The EVDAC diagnostic exercises a DMF32 that is linked to another DMF32 (even in the same system) which is also running EVDAC.

**3.3.3.1 Loading, Attaching, and Running EVDAC** – The instructions in Example 3-6 are used to load, attach, and run EVDAC. It is assumed that VMS is already loaded.

```

$ RUN EVDLA

; Start supervisor (11/780 = ESSAA,

; 11/750 = ECSAA, 11/730 = ENSAA)

DIAGNOSTIC SUPERVISOR. ZZ-ENSAA-6.6-xxx 8-FEB-1982 Ø9:40:14.80

DS) ATTACH DW780 SBI DW0 3 4 ; Attaches the UBA on the SBI

or

; VAX-11/78Ø

DS] ATTACH DW750 HUB DW0

; For VAX-11/750 testing

DS] ATTACH DW73Ø HUB DWØ

; For VAX-11/730 testing

DS] LOAD EVDLA

; Loads the EVDLA program

DS] ATTACH DMF32S

; Attaches the synchronous

; diagnostic

DEVICE LINK? DWØ

; The option is linked to the UBA

DEVICE NAME? XGAØ

; The option is named XGAØ (range =

; A-F)

CSR? 760340

; The CSR address is 760340 (range =

; 76ØØØØ-777776)

VECTOR? 300

; Vector address is 300 (range =

; 300-776)

BR? 5

; BR interrupt level is 5 (range =

; 5-6)

WRAP TYPE? NONE

NONE - No external backloop

connector or modem

WRAP - External backloop

connector is connected

MODEM - External modem is

connected

DS) SEL XGAØ

; Select the synchronous port

DS) START

; Start running EVDLA without either

; an external loopback connector or

or

; a modem

DS) START/SELECTION: CABLE

; External loopback connector is

or

; connected

DS] START/SECTION: MODEM

; External modem is connected

```

Example 3-5 Loading, Attaching, and Running EVDLA

```

; Allocate all lines to be tested

$ ALLOCATE TXA(N)

; Start supervisor (11/780 = ESSAA

$ RUN ENSAA

; 11/750 = ECSAA, 11/730 = ENSAA)

DIAGNOSTIC SUPERVISOR. ZZ-ENSAA-6.6-xxx 8-FEB-1982 Ø9:40:14.80

DS) ATTACH DW780 SBI DW0 3 4; Attaches the UBA on the SBI

; VAX-11/780

; For VAX-11/750 testing

ATTACH DW750 HUB DW0

DS] ATTACH DW730 HUB DW0

; For VAX-11/730 testing

; Loads the EVDAC program

DS) LOAD EVDAC

DS] ATTACH DMF32A

; Attaches the asynchronous

; diagnostic

DEVICE LINK? DWØ

; The option is linked to the UBA

; The option is named TXA (range =

DEVICE NAME? TXA

; A-F)

; The CSR address is 760340 (range = ; 760000-777776)

CSR? 760340

VECTOR? 300

; Vector address is 300 (range =

; 300-776)

BR? 5

; BR interrupt level is 5 (range =

; 5-6)

ACTIVE LINES? 377

; All lines Ø-7 to be tested

; (octal bit map of lines to be

; tested)

; bit \emptyset = line \emptyset,

; bit 1 = line 1, etc. (range =

; 000-377)

; Baud rate that is to be used in

BAUD RATE? 9600

; external wrap tests. Baud rates

; that can be selected are 50, 75,

; 110, 135, 150, 300, 600, 1200, 1800

; 2000, 2400, 3600, 4800, 7200, 9600,

; 19200

WRAP TYPE? INTERNAL

; INTERNAL - Wrapped internally at

the UART

H3248 - Single-line wrap at the

distribution panel

LOCAL MODEM - Modem with internal

wrap

PROGRAMMABLE MODEM - A modem which

diagnostics can set to internal

wrap by setting the User

Transmit Modem signals

UNIBUS INIT JUMPER? YES

; Jumper on DMF32 module that

; inhibits UNIBUS Inits

DS] SEL TXA

; Selects the asynchronous port to

; be run

DS) START

; Start program running

```

Example 3-6 Loading, Attaching, and Running EVDAC

# PROGRAMMING —

### 4.1 INTRODUCTION

The DMF32 consists of four distinct devices. Each device is programmed independent of the other three devices, since each device contains its own set of registers. There are only two registers that are common to the DMF32: CSR 0 and CSR 1.

# 4.1.1 DMF32 CSR 0

The operating system uses CSR 0 at AUTOCONFIGURE time. CSR 0 contains a 4-bit code that indicates to the operating system which three of the four devices are available for operation. The parallel interface (DR) and the line printer controller (LP) cannot operate concurrently.

The DMF32 uses two dip switches to select the desired devices: switches 4 and 5 on switch pack 3 on the distribution panel. Refer to Table 2-7 for the valid switch setting combinations. These two switches, which are read by the DMF32, should be set before power up, since the microcode samples these switches only once after power up.

After power up, the program can write to CSR 0 bits \( 15:12 \) to change the device code to another valid combination. For example, to switch a diagnostic program from DR to LP or LP to DR without human intervention, execute a WRITE WORD (MOVW) instruction to CSR 0 bits \( 15:0 \). The WRITE WORD overwrites the base interrupt vector which occupies the low byte of CSR 0. To load the interrupt vector (CSR 0 high byte) without affecting the CSR 0 high byte (device available bits), execute a BYTE output instruction (MOVB). This MOVB instruction loads the low byte of CSR 0, regardless of whether the high or low byte is accessed.

Also at AUTOFIGURE time, the operating system loads the value of the first interrupt vector into CSR 0. There are no switches on the DMF32 for interrupt vectors. The DMF32 determines the value of the other seven interrupt vectors as contiguous with a greater value than the first vector in CSR 0. Table 4-1 lists the vectors.

Figure 4-1 shows the bit configurations for CSR 0; Table 4-2 defines the CSR 0 bit functions.

Table 4-1 DMF32 Floating Vectors

| Vector<br>Number | Vector                            | Vector Value (Octal)    |

|------------------|-----------------------------------|-------------------------|