DA11-F unibus window maintenance manual

digital

# DA11-F unibus window maintenance manual

Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC PDP FLIP CHIP FOCAL

DIGITAL COMPUTER LAB

# **CONTENTS**

|           | Pa                                     | age |

|-----------|----------------------------------------|-----|

| CHAPTER 1 | SYSTEM AND PHYSICAL DESCRIPTION        |     |

| 1.1       | General                                | 1-1 |

| 1.2       | Window Parameters                      | 1-2 |

| 1.3       | Physical Description                   | 1-3 |

| 1.4       | Typical Installation                   | 1-5 |

| 1.5       | Specification Summary                  | 1-5 |

| CHAPTER 2 | THEORY OF OPERATION                    |     |

| 2.1       | General                                | 2-1 |

| 2.2       | DA11-F Bus Cycles                      | 2-1 |

| 2.2.1     | DATO, DATOB Cycles                     | 2-2 |

| 2.2.2     | DATI, DATIP Cycles                     | 2-3 |

| 2.2.3     | Duplex Operation                       | 2-3 |

| 2.2.4     | DATO, DATOB Cycle Detailed Description | 2-5 |

| 2.2.5     | DATI, DATIP Cycle Detailed Description | 2-7 |

| 2.3       | DA11-F Block Diagram Description       | 2-9 |

| 2.4       | Relocated Target Address               | 11  |

| 2.4.1     | Window Size                            | 11  |

| 2.4.2     | Window Starting Address                | 12  |

| 2.4.3     | Target Address                         | 12  |

| 2.4.4     | Target Address Calculation             | 13  |

| 2.5       | Window Field Jumper Plugs              | 14  |

| 2.6       | Window Bus Control                     | 15  |

| 2.7       | Data Path Block Diagram Description    | 17  |

| 2.8       | Addressable Register Select Logic      |     |

| 2.9       | Interrupt Control Logic                | 21  |

| 2.10      | Power Fail                             | 22  |

| CHAPTER 3 | PROGRAMMING INFORMATION                |     |

| 3.1       | General                                | 3-1 |

| 3.2       | Control and Status Register (CSR)      | 3-2 |

| 3.3       | Output Data Buffer (DB)                | 3-5 |

| 3.4       | Input Data Buffer (DB)                 | 3-5 |

| 3.5       | Displacement Address Register (DAR)    | 3-6 |

| 3.6       | Relocation Address Register (RAR)      | 3-6 |

| 3.7       | Starting Address Register (SAR)        | 3-8 |

| 3.8       | Vector Address Register (VAR)          | 3-8 |

| 3.9       | Programming Examples                   | 3-8 |

# **CONTENTS (Cont)**

|            |                                              | Page   |  |  |  |  |  |  |

|------------|----------------------------------------------|--------|--|--|--|--|--|--|

| 3.9.1      | Open-The-Window Program                      | . 3-8  |  |  |  |  |  |  |

| 3.9.2      | Block Transfer Program                       | . 3-9  |  |  |  |  |  |  |

| 3.10       | Error Reporting Procedures                   | . 3-9  |  |  |  |  |  |  |

| CHAPTER 4  | MAINTENANCE                                  |        |  |  |  |  |  |  |

| 4.1        | General                                      | . 4-1  |  |  |  |  |  |  |

| 4.2        | Engineering Drawings                         | . 4-1  |  |  |  |  |  |  |

| 4.3        | Installation                                 | . 4-3  |  |  |  |  |  |  |

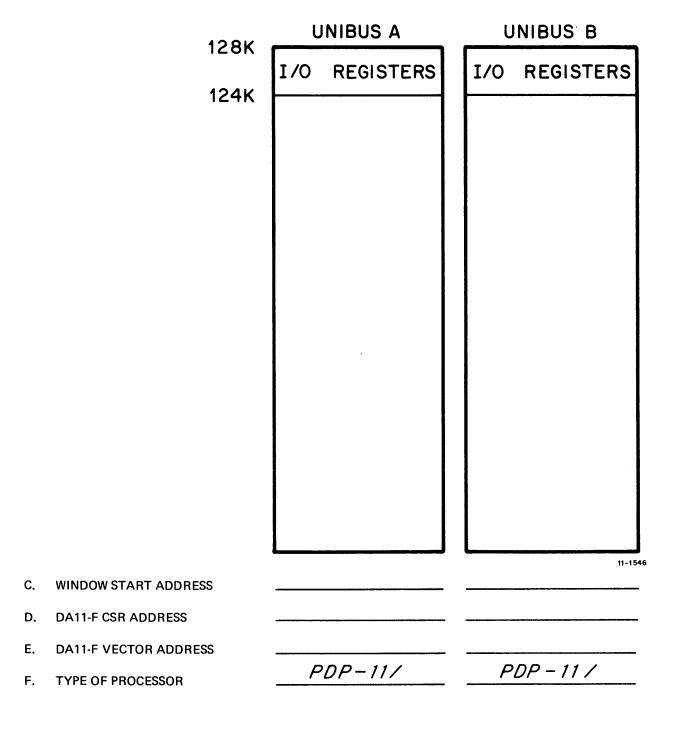

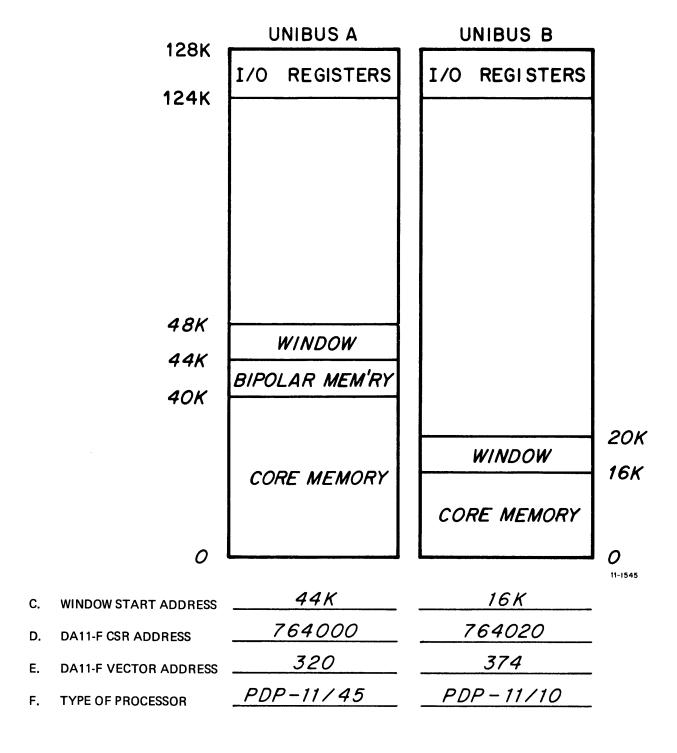

| 4.3.1      | Customer Specifications                      | . 4-3  |  |  |  |  |  |  |

| 4.3.2      | Implementing Customer Specifications         | . 4-6  |  |  |  |  |  |  |

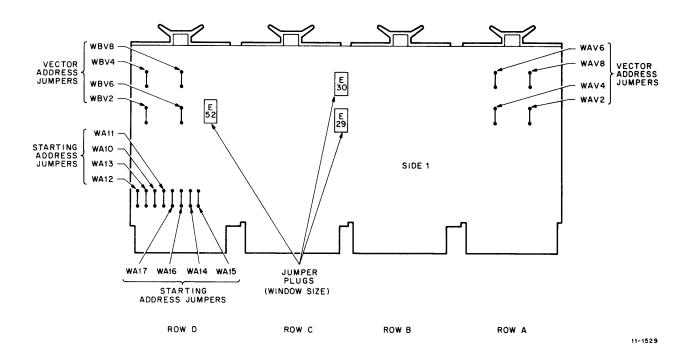

| 4.3.3      | Starting Address Jumpers                     | . 4-7  |  |  |  |  |  |  |

| 4.3.4      | Control and Status Register Address Jumpers  | . 4-11 |  |  |  |  |  |  |

| 4.3.5      | Vector Address Jumpers                       | . 4-12 |  |  |  |  |  |  |

| 4.3.6      | Priority Jumper Plugs                        |        |  |  |  |  |  |  |

| 4.3.7      | Window Size Jumper Plugs                     | . 4-12 |  |  |  |  |  |  |

| 4.3.8      | Mechanical Installation                      |        |  |  |  |  |  |  |

| 4.3.9      | Electrical Installation                      |        |  |  |  |  |  |  |

| 4.3.9.1    | Unibus Connection                            |        |  |  |  |  |  |  |

| 4.3.9.2    | Power Cable Connection                       |        |  |  |  |  |  |  |

| 4.4        | Preventive Maintenance                       |        |  |  |  |  |  |  |

| 4.5        | Corrective Maintenance                       |        |  |  |  |  |  |  |

| 4.6        | Diagnostic Programs                          |        |  |  |  |  |  |  |

| 4.6.1      | Bus Window Static Test                       |        |  |  |  |  |  |  |

| 4.6.2      | Bus Window Exerciser                         |        |  |  |  |  |  |  |

| 4.7        | Parts List                                   |        |  |  |  |  |  |  |

| 4.8        | IC Spare Parts List                          |        |  |  |  |  |  |  |

| APPENDIX A | IC DESCRIPTION                               |        |  |  |  |  |  |  |

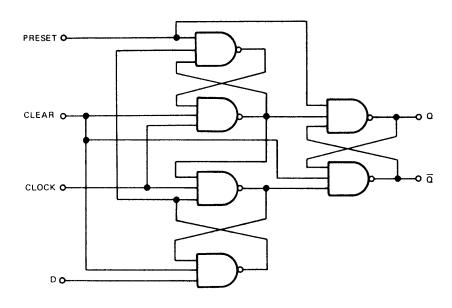

|            | 74H74-D-Type Edge-Triggered Flip-Flops       |        |  |  |  |  |  |  |

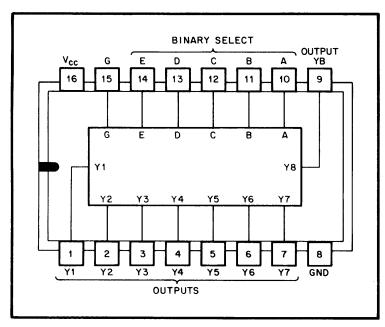

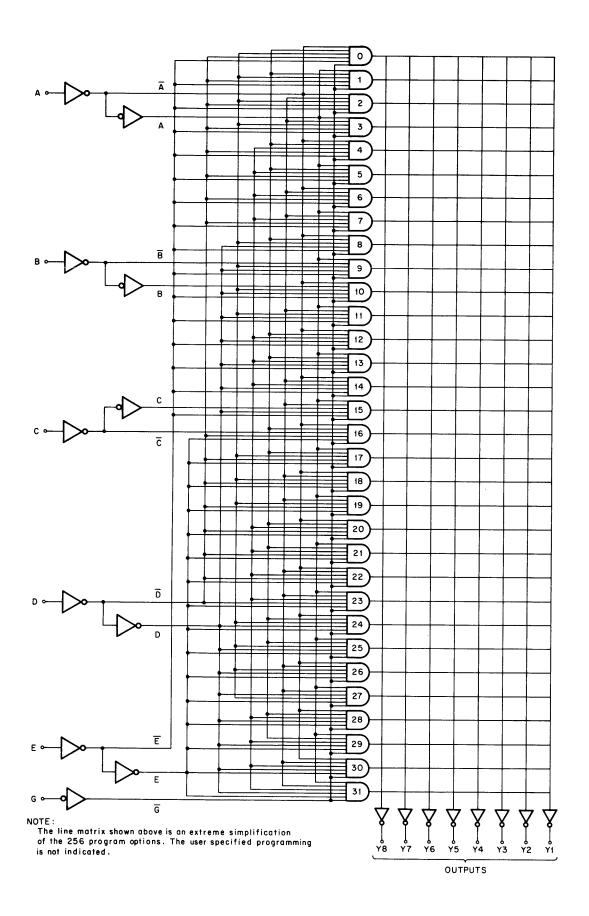

|            | 7488 Read-Only Memory                        |        |  |  |  |  |  |  |

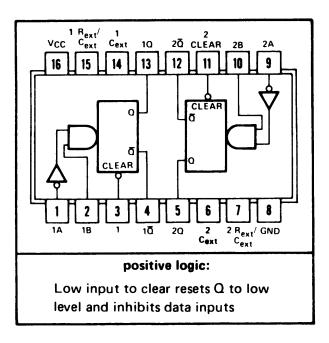

|            | 74123 Retriggerable Monostable Multivibrator |        |  |  |  |  |  |  |

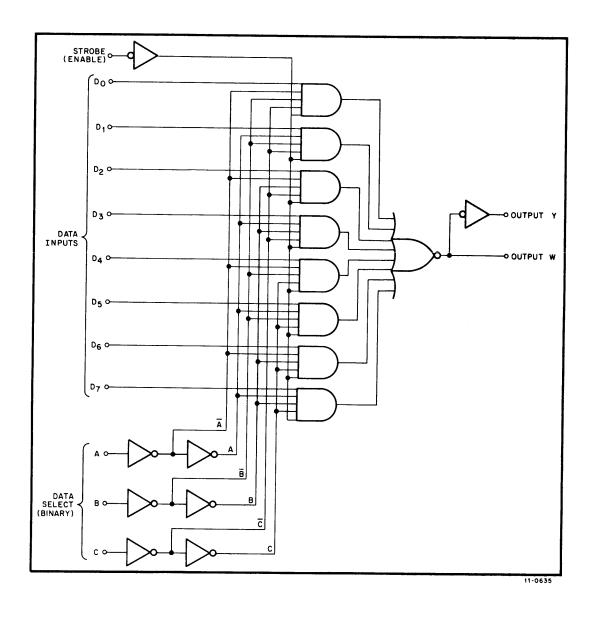

|            | 74151 8-Line to 1-Line Multiplexer           |        |  |  |  |  |  |  |

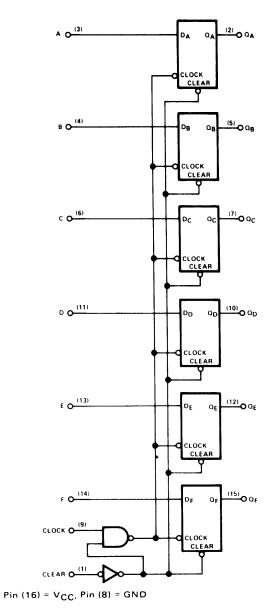

|            | 74174/74S174 Hex D-Type Flip-Flops           |        |  |  |  |  |  |  |

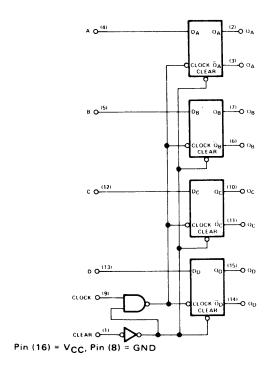

|            | 74175 Quad D-Type Flip-Flops                 |        |  |  |  |  |  |  |

|            | ILLUSTRATIONS                                |        |  |  |  |  |  |  |

| E' N       |                                              | _      |  |  |  |  |  |  |

| Figure No. | Title                                        | Page   |  |  |  |  |  |  |

| 1-1        | Unibus Window, Simplified Block Diagram      | . 1-1  |  |  |  |  |  |  |

| 1-2        | Relocated Target Address Concept             |        |  |  |  |  |  |  |

# **ILLUSTRATIONS** (Cont)

|      | P                                         | age                    |

|------|-------------------------------------------|------------------------|

| 1-3  | DA11-F Module Utilization                 | 1-4                    |

| 1-4  | DA11-F Functional Layout                  |                        |

| 1-5  | Typical DA11-F Window Installation        |                        |

| 2-1  | Unibus Window, Simplified Block Diagram   |                        |

| 2-2  | DATO and DATOB Cycle                      |                        |

| 2-3  | DATI Cycle                                |                        |

| 2-4  | DATIP-DATO(B) Cycle (Read, Modify, Write) |                        |

| 2-5  | Duplex DATO(B)/DATO(B) Cycles             |                        |

| 2-6  | Duplex DATIP-DATO(B)/DATO(B) Cycles       |                        |

| 2-7  | Duplex DATIP-DATO(B)/DATIP-DATO(B) Cycles |                        |

| 2-8  | Detailed DATO, DATOB Cycle                |                        |

| 2-9  | Detailed DATI, DATIP Cycle                |                        |

| 2-10 | DA11-F Functional Block Diagram           |                        |

| 2-11 | Unibus Window Concept                     |                        |

| 2-12 | Address Calculation Block Diagram         |                        |

| 2-13 | Jumper Plug Configuration                 |                        |

| 2-14 | Bit 13 Jumper Plug Concept                |                        |

| 2-15 | Window Bus Control                        |                        |

| 2-16 | DA11-F Data Paths                         |                        |

| 2-17 | Address Select, Simplfied Diagram         |                        |

| 2-18 | ROM Address Map                           |                        |

| 2-19 | Interrupt Control for a Port              |                        |

| 2-20 | Power Fail Simplified Block Diagram       |                        |

| 3-1  | ACSR Bit Format                           |                        |

| 3-2  | Cross Interrupt Logic                     |                        |

| 3-3  | Output Data Buffer Bit Format             |                        |

| 3-4  | Input Data Buffer Bit Format              |                        |

| 3-5  | Displacement Address Register Bit Format  |                        |

| 3-6  | Relocation Address Register Bit Format    |                        |

| 3-7  | Starting Address Register Bit Format      |                        |

| 3-8  | 77                                        | 3-8                    |

| 3-9  | 0 m m m                                   | 3-0<br>3-9             |

| 3-10 | Block Transfer Program                    |                        |

| 4-1  |                                           | 1-4                    |

| 4-2  | 74477                                     | 4-5                    |

| 4-3  |                                           | 4-7                    |

| 4-4  | WY 4 M                                    | <del>1-</del> 7<br>4-8 |

| 4-5  |                                           | <del>1-</del> 0<br>4-9 |

| 4-6  | Control Module Jumper Locations           |                        |

| 4-7  | CSR Address Chart                         |                        |

# ILLUSTRATIONS (Cont)

|           |                                                                | Page   |

|-----------|----------------------------------------------------------------|--------|

| 4-8       | Example of Completed CSR Address Chart                         | . 4-14 |

| 4-9       | Vector Address Chart                                           | . 4-15 |

| 4-10      | Vector Address Chart                                           | . 4-16 |

| 4-11      | Typical Power Cable Connections for a DA11-F                   | . 4-18 |

|           | TABLES                                                         |        |

| Table No. | Title                                                          | Page   |

| 2-1       | Jumper Plug Selection                                          | . 2-14 |

| 3-1       | Register Addresses                                             | . 3-1  |

| 3-2       | Control and Status Registers WCSR 764XXX                       | . 3-3  |

| 3-3       | Error Reporting Procedures After Illegal Window Channel Access | . 3-11 |

| 4-1       | Decimal-To-Octal Address Conversion Chart                      | . 4-10 |

| 4-2       | Window Size Chart                                              | . 4-17 |

# CHAPTER 1 SYSTEM AND PHYSICAL DESCRIPTION

## 1.1 GENERAL

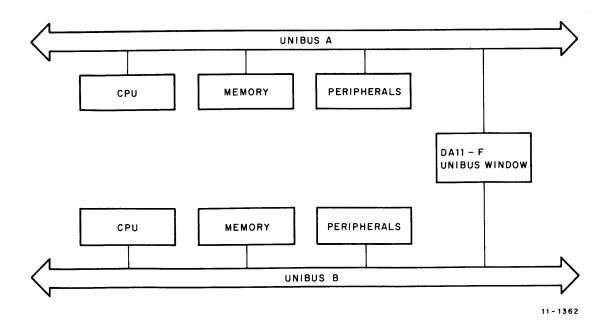

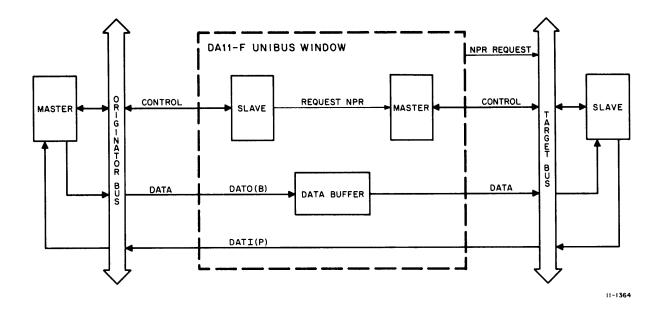

The DA11-F Unibus window option provides high-speed communication between two PDP-11 computer systems. The DA11-F is connected to the Unibuses of both computers as shown in Figure 1-1. For descriptive purposes, one Unibus is designated bus A and the second is designated bus B.

In order to provide high-speed data transfer between the computers, the DA11-F translates a bus cycle on one Unibus to a bus cycle on the other Unibus. In doing this, the DA11-F conforms to standard Unibus protocol.

The DA11-F is symmetrical and bilateral, i.e., data transfers may originate on either bus and data may flow in either direction. In order to accomplish this, the window contains two identical channels going in opposite directions. The logic for the two channels provides duplex capability allowing simultaneous transactions through the window from each Unibus. In addition to the channels, the window includes addressable registers and interrupt controls for full program operation by each computer.

Figure 1-1 Unibus Window, Simplified Block Diagram

Some significant features of the DA11-F Unibus window are tabulated below.

- High-speed interprocessor communications (through-the-window transactions).

- Random access to virtual memory space. The user can address memory that is actually attached to a different processor.

- Duplex operation data transfers can occur simultaneously in both directions.

- Minimum program overhead once opened the window is transparent to the user program.

- Data transfers between peripherals and memory can pass through the window automatically.

- Window field is adjustable in size and can be located anywhere in full 128K address space.

- Data and interrupts can be transferred between computers under program control.

- Extensive built-in debugging aids.

- Compact circuitry comprising one system unit for ease of installation.

- Interchangeable modules for ease of maintenance.

- Uses system unit mounting box internal power supply.

- Compatible with any PDP-11 processor.

It is assumed that the reader is familiar with PDP-11 Unibus theory and is acquainted with the information contained in the following manuals:

PDP-11 Processor Handbooks

PDP-11 Peripherals and Interfacing Handbook

# 1.2 WINDOW PARAMETERS

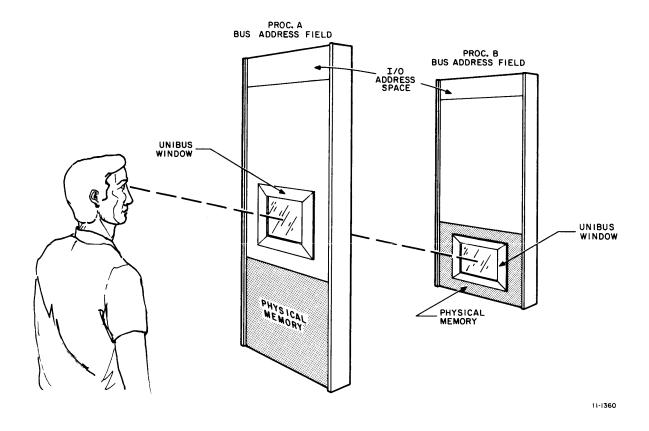

The originator bus is defined as the bus connected to the master initiating a bus cycle, and the target bus is defined as the bus connected to the slave device being addressed by the master. The window starting address on the originator bus can be anywhere in the full 128K of bus address space and is determined by a set of window address select jumpers. The target address, which is the address of the location containing the slave device, is relocatable from the window starting address and must be within the physical memory space of the target bus. This has the effect of making physical address space on the target bus appear as virtual address space on the originator bus (Figure 1-2). The relocated address is normally set under program control.

The size of the window field may be 1/2K, 1K, 2K, 4K, 8K, 16K, or 32K words and is determined by jumper selection.

Figure 1-2 Relocated Target Address Concept

# 1.3 PHYSICAL DESCRIPTION

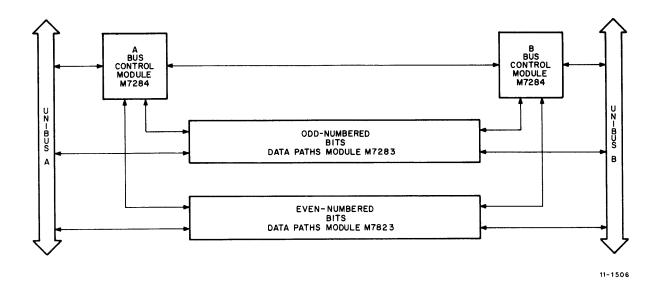

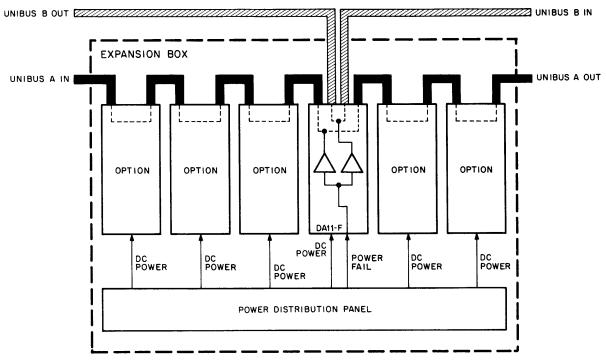

The DA11-F is mounted in a single system unit and consists of four quad-height boards and two pair of Unibus cables (A BUS IN and A BUS OUT; B BUS IN and B BUS OUT). The two inner modules contain the address and data path logic between the buses. The outside modules contain the bus control logic. One module controls the A bus and the other the B bus (Figure 1-3). Note that the Unibus connector pairs are located above the modules. Figure 1-4 shows a functional arrangement of the DA11-F. The data and address path logic is subdivided into "even bits" and "odd bits." The "even bits" board contains the even-numbered bit data and address logic for both the A and B buses, while the "odd bits" board contains the odd-numbered bit data and address logic for both buses. The A and B control modules interact with both data modules and also interact with each other.

The DA11-F is installed in any PDP-11 mounting box that can accommodate hex-height modules and draws power from the +5V regulator in the box's power supply.

|   | 1        | 2               | 3                | 4        |

|---|----------|-----------------|------------------|----------|

| A | A<br>Bus | B<br>Bus        | B<br>Bus         | A<br>Bus |

| В | In       | Out             | In               | Out      |

|   | M7284    | M7283           | M7283            | M7284    |

| С | A<br>Bus | Bus<br>to       | Bus<br>to        | B<br>Bus |

| D | Control  | Bus<br>Paths    | Bus<br>Paths     | Control  |

| E | ·        | Odd<br>Numbered | Even<br>Numbered |          |

| F |          | Bits            | Bits             |          |

Figure 1-3 DA11-F Module Utilization

Figure 1-4 DA11-F Functional Layout

#### 1.4 TYPICAL INSTALLATION

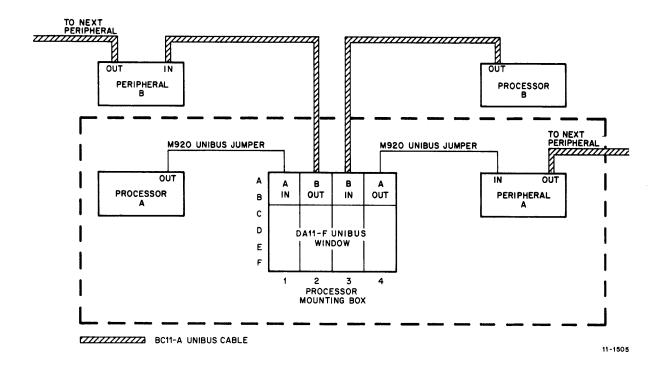

Figure 1-5 shows a typical DA11-F installation. Note that the A IN and A OUT connectors are located in the outside slots; this allows the use of M920 Unibus Jumper Modules to connect the DA11-F to an adjacent device. The DA11-F can be installed in either processor (or in an expansion box) but is shown in the A processor mounting box merely for illustrative purposes.

#### 1.5 SPECIFICATION SUMMARY

Window Size: 1/2K, 1K, 2K, 4K, 8K, 16K, or 32K words. Field Adjustable.

Window Starting Address: For "N" K size, start on any even "N" K boundary throughout 128K bus

address space, e.g., 8K window starts on any 8K boundary.

Addressable Registers: Seven normally assigned to user I/O area from 764000<sub>8</sub> to 764777<sub>8</sub>.

Control and Status XXXX00

Output Data Buffer XXXX02

Input Data Buffer XXXX04

Displacement Address XXXX06

Relocation Address XXXX10

Starting Address XXXX12

Vector Address XXXX14

Interrupt Vector: Assigned to floating vector field from 300<sub>8</sub> to 777<sub>8</sub>. DA11-F requires one vector

that is allocated after all other options have been assigned vectors. (Can also be

assigned to use vectors: 170, 174, 270, 274.)

Priority Level: BR7

Bus Loading: Places one unit bus load on each Unibus (A and B).

Mechanical: One system unit.

Power: +5Vdc, 5A maximum (drawn from mounting box power supply).

Environment: Temperature 10° to 50°C

Relative Humidity 8% to 90%

Installation: Can be installed in any system unit mounting box that accepts hex-height

modules.

Unibus Compatibility: Can be used with any PDP-11 Family processor.

Figure 1-5 Typical DA11-F Window Installation

# CHAPTER 2 THEORY OF OPERATION

#### 2.1 GENERAL

This chapter describes the theory of operation of the DA11-F. Several terms used throughout this chapter are defined below:

Originator Bus — The bus connected to the master initiating a bus cycle. The master may be an NPR device or a processor.

Target Bus – The bus connected to the slave being addressed by the master. The slave may be any Unibus device but is usually memory.

Two-port Device — The DA11-F is a two-port device. A port may be thought of as the interface between a PDP-11 device and the external Unibus cable.

Window Starting Address - The starting address of the window on the originator port.

Window Field – This is the window size and can be adjusted to 1/2K, 1K, 2K, 4K, 8K, 16K, or 32K words.

Target Address – The address of the register in the slave device that is being accessed through the window.

DATO(B) – designates a DATO or DATOB operation.

DATI(P) – designates a DATI or DATIP operation.

Window Transaction — operations from originator to target in which the DA11-F synchronizes the data transfer cycles on the two Unibuses connected to the window. Also called "through-the-window" transaction.

The DA11-F is a two-port device capable of duplex operation, i.e., requests for data transfers can be handled simultaneously by both ports. In order to simplify the description, the theory of operation describes the DA11-F as a simplex device where a request for data transfer is initiated by the A bus only. The reader should be aware that a simultaneous request for data transfer can be made by the B bus.

## 2.2 DA11-F BUS CYCLES

The DA11-F responds to all PDP-11 bus cycles for data transfers between Unibuses. When a device on the originator bus performs a bus cycle addressed to a location within its window field, the DA11-F gains control of the target bus with an NPR request and performs the same type of bus cycle but addressed to a location within the relocated window field on the target bus. In other words, a data transfer requires a bus cycle on each bus to complete the transaction.

A bus cycle operates on a master-slave "handshaking" sequence. As a result, the DA11-F appears as a slave to the master on the originator bus to accomplish the first bus cycle. In addition, the DA11-F appears as a master to the slave device on the target bus in order to accomplish the second bus cycle. This action is illustrated in Figure 2-1.

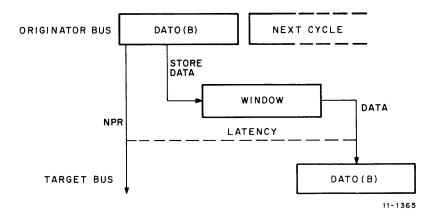

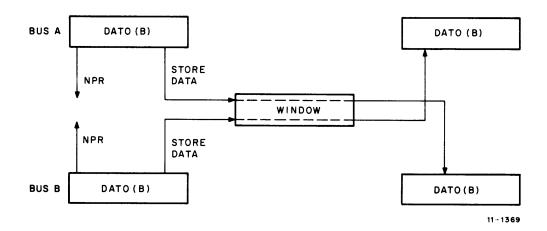

# 2.2.1 DATO, DATOB Cycles

If data is to be transferred from a master device on the originator bus to a slave on the target bus, a DATO(B) operation is performed. The first DATO(B) cycle causes the data on the originator bus to be transferred to a Data Buffer in the DA11-F. Since the data is stored in the DA11-F, the originator bus cycle (first DATO(B)) can be concluded. An NPR request is asserted on the target bus for the second DATO(B) cycle. When the DA11-F is granted control of the target bus, the second bus cycle causes the data to be transferred from the window Data Buffer to the target register (Figure 2-2).

Figure 2-1 Unibus Window, Simplified Block Diagram

Figure 2-2 DATO and DATOB Cycle

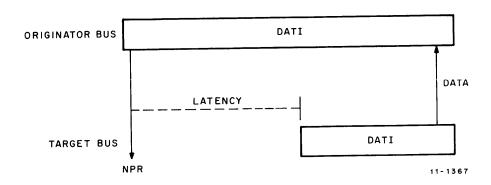

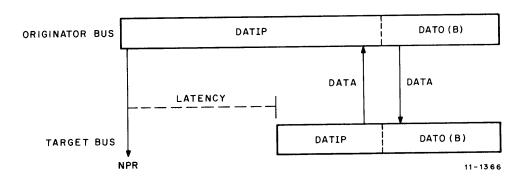

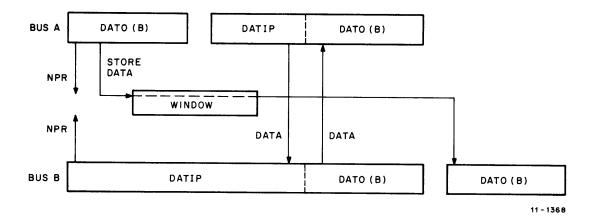

# 2.2.2 DATI, DATIP Cycles

If data is to be transferred from a slave device on the target bus to a master on the originator bus, a DATI(P) operation is required. In this type of operation, the originator bus cycle time is extended by the length of the NPR latency on the target bus. This is due to the fact that the data must be obtained from the slave and transferred to the master before the originator bus cycle can be terminated. The termination of the originator bus cycle is dependent on termination of the target bus cycle. This is illustrated for the DATI cycle in Figure 2-3 and for the DATIP in Figure 2-4. Data is gated directly through the window in a DATI or DATIP and is not stored in the Data Buffer as in the DATO and DATOB cycles.

Figure 2-3 DATI Cycle

Figure 2-4 DATIP-DATO(B) Cycle (Read, Modify, Write)

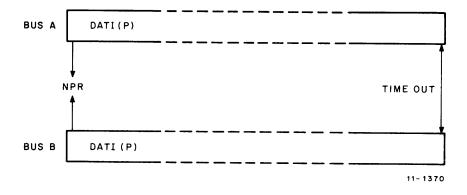

# 2.2.3 Duplex Operation

Duplex operation occurs when requests occur on both buses simultaneously. If both ports receive DATO or DATOB cycles, the data paths are independent and the data transfer is made without interference. This is shown in Figure 2-5. Separate Data Buffers exist for both buses and separate control circuits are used.

If a DATO or DATOB cycle is requested on the A bus and a DATI or DATIP is requested on the B bus, the DATI or DATIP takes precedence and is completed before the DATO or DATOB can be completed (Figure 2-6). The sequence of operations begins with the DATO cycle where the data is transferred from the A bus to the Data Buffer in the window. This concludes the A bus portion of the DATO cycle. At this point the window gains control of the A bus and does a DATI(P) cycle. The data is directly transferred from the A bus to the B bus, thereby finishing the DATI(P) cycle on both the A bus and B bus. Then, the window gains control of the B bus and transfers the data from the window Data Buffer to the B bus to conclude the B bus portion of the DATO(B) cycle.

If DATI or DATIP cycles are requested simultaneously on both buses, neither port can gain control of its target bus. Therefore, both requests are aborted and both originating masters will time-out. This situation is illustrated in Figure 2-7.

Figure 2-5 Duplex DATO(B)/DATO(B) Cycles

Figure 2-6 Duplex DATIP-DATO(B)/DATO(B) Cycles

Figure 2-7 Duplex DATIP-DATO(B)/DATIP-DATO(B) Cycles

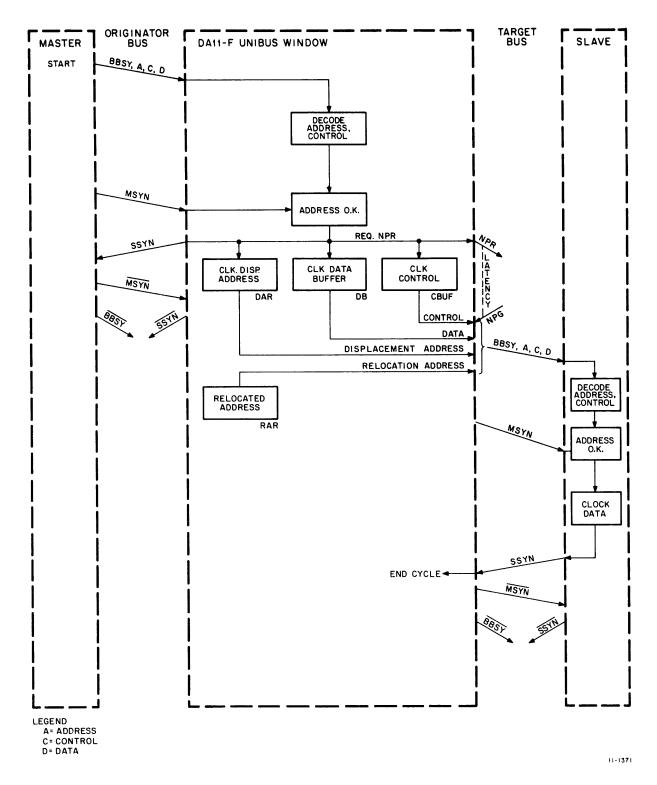

# 2.2.4 DATO, DATOB Cycle Detailed Description

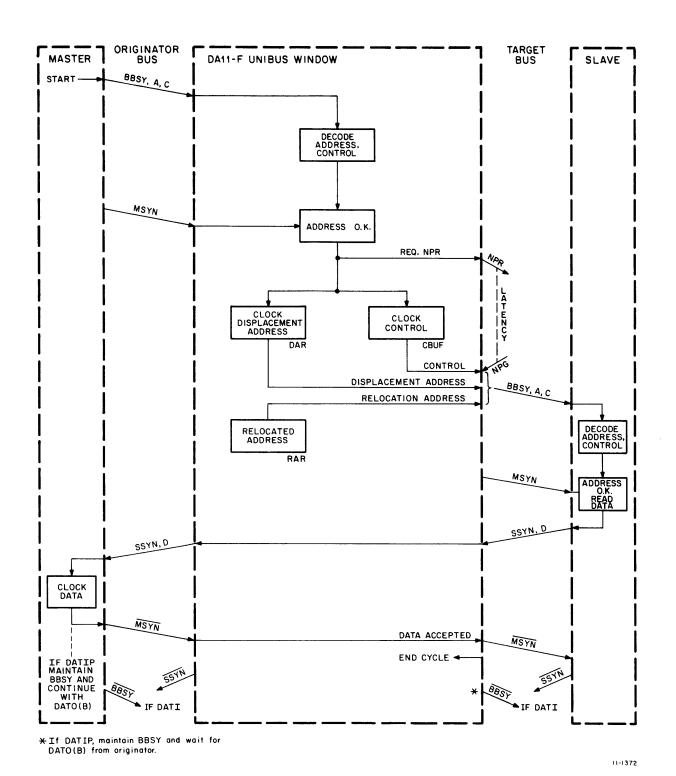

Figure 2-8 is a detailed diagram of the DATO and DATOB cycles. Since timing between the Unibus and the DA11-F is asynchronous, precise timing diagrams are not shown. Instead, a functional flow diagram with associated timing relationships is provided. Time is shown vertically on the diagram. The master device initially gains control of the bus, asserts BBSY, and places the address, control, and data on the bus. The address is decoded by the DA11-F to determine if it has been addressed by the master. A short time later, the master asserts MSYN. If the window was selected by the master, the window performs the following three functions.

a. Clocks the address, data, and control from the master into the following DA11-F registers.

Address to Displacement Address Register (DAR)

Data to Data Buffer (DB)

Control to Control Buffer (CBUF)

- b. Issues an NPR request to gain control of the target bus (if no error condition occurred).

- c. Returns SSYN to the master, indicating that the data from the master has been stored in the DA11-F. SSYN clears MSYN which, in turn, clears SSYN. BBSY is then cleared to complete the DATO cycle on the originator bus.

The latency time shown in Figure 2-8 is the time between issuance of the NPR request and the time that the DA11-F gains control of the target bus.

When the window gains control of the target bus, the DA11-F asserts BBSY and transfers address, data, and control information to the slave on the target bus.

#### **NOTE**

The address placed on the target bus (target address) is the summation of a displacement address and a relocation address and represents an address relocated from the originator address. This is described in detail in subsequent paragraphs in this chapter.

The slave device decodes the address to see if it is the device being addressed. The DA11-F then asserts MSYN. The slave that is being addressed clocks the data into its buffer and then returns SSYN, indicating that it has the data. SSYN clears MSYN and also generates an internal END CYCLE pulse, which clears the DA11-F bus cycle control logic. The clearing of MSYN clears SSYN and BBSY is then cleared to free the bus.

Figure 2-8 Detailed DATO, DATOB Cycle

# 2.2.5 DATI, DATIP Cycle Detailed Description

Figure 2-9 shows a detailed diagram of the DATI and DATIP cycles. As in the DATO cycle, the master device initially gains control of the bus, asserts BBSY, and places the address and control information on the bus. Note, however, that no data is present in this case since the data is to be transferred from the slave to the master. The window decodes the address to determine if it is the device being selected by the master. A short time later, the master asserts MSYN. If the window was the device selected by the master, the window performs the following two functions:

- a. Clocks the address into the Displacement Address Register and the control information into the Control Buffer.

- b. Raises an NPR request on the target bus.

#### **NOTE**

The originator bus DATI cycle is extended because the return of SSYN to the master is dependent on the completion of the target bus DATI cycle as shown. This is necessary because the data must be obtained from the slave on the target bus before it can be transferred to the master.

When the window gains control of the target bus as a result of the NPR request, it asserts BBSY and places the relocated target address and control information on the Unibus. This relocated target address is a summation of a displacement address and a relocation address and is described in subsequent paragraphs in this chapter. The slave being addressed by the window decodes the address and control information. When MSYN is asserted by the window, the slave reads the location and returns SSYN and the data to the window.

SSYN is transferred through the window to the originator bus. Simultaneously, the data is gated through the window and clocked into the master on the originator bus. The master clears MSYN, indicating that it has received the data, and after a short delay drops BBSY to release the bus (if the cycle was a DATI). The clearing of MSYN by the originator master causes the window to clear SSYN on the originator bus and also clears MSYN on the target bus. An internal signal, END CYCLE, clears the DA11-F bus cycle control logic.

If the cycle was a DATI, the window clears BBSY on the target bus. However, if the cycle was a DATIP, both the originating master and the window maintain BBSY asserted on both buses until the end of the DATO(B) cycle, which follows immediately.

Note the interlocking effect of the two DATI bus cycles, i.e., the originator bus DATI cycle cannot be terminated until SSYN from the target bus is received, and the target bus DATI cycle cannot be concluded until MSYN is cleared from the originator bus.

Figure 2-9 Detailed DATI, DATIP Cycle

2-8

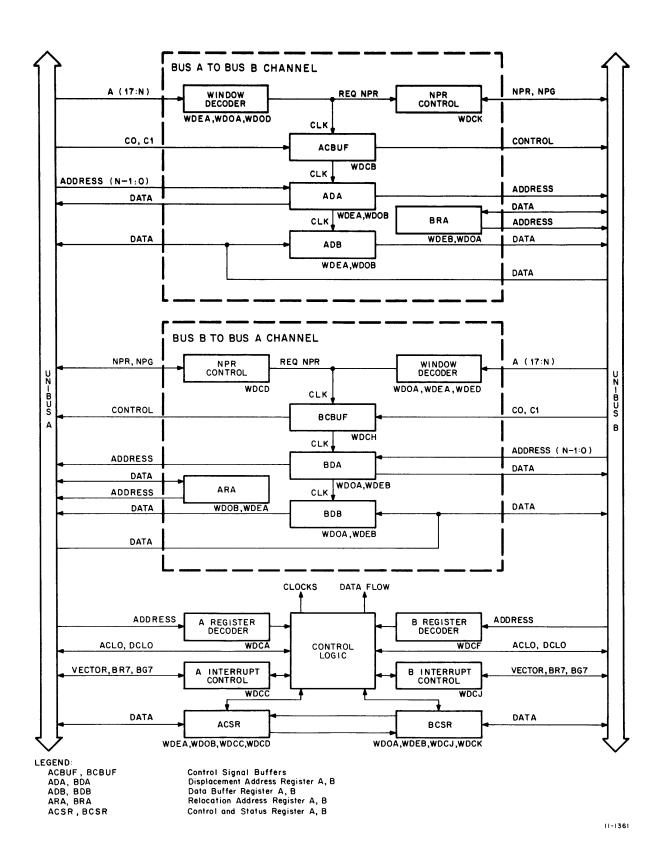

#### 2.3 DA11-F BLOCK DIAGRAM DESCRIPTION

Figure 2-10 is a functional block diagram of the DA11-F, showing the two separate channels — bus A to bus B logic and bus B to bus A logic. The bottom portion of the diagram shows the control logic for each channel and some control logic that is common to both channels. Each of the bus A to bus B logic elements on the block diagram are listed below, together with a brief description of the function performed by that element. Similar functions are performed by the bus B to bus A logic elements except for a direction reversal.

- a. Window Decoder used to decode high-order address bits (17:N) (Paragraph 2.4.3). Jumper plugs at the input to the window decoder determine the window size while jumpers in the window decoder itself determine the window starting address. The high-order bus address bits are compared to the jumpers in the window decoder and if a match occurs, the circuit following is enabled.

- b. NPR Control This circuitry asserts an NPR request on the target bus if the high-order address bits on the originator bus compare with the internal jumpers in the window decoder. When the request is acknowledged, NPG (Non-Processor Grant) is returned.

- c. ACBUF A buffer register to store control lines C0 and C1, which are used to determine the type of bus cycle to be performed.

- d. ADA The A bus Displacement Address Register used to store low-order address bits (N-1:0) (Paragraph 2.4.3) from the originator bus. These bits are transferred to the target bus through the ADA. The contents of this register can be read back to the originator bus as data.

- e. BRA The Relocation Address Register for the target bus. This register is loaded under program control and determines the upper portion (17–N) of the relocated target address.

- f. ADB The Data Buffer used to store the data during a DATO(B) bus cycle. This buffer is not employed during DATI(P) operations. The contents of this buffer can be read back on the originator bus.

- g. A Register Decoder The A register decoder consists of a decoding network to select one of the seven addressable DA11-F registers (refer to Chapter 3) during program transfers to the DA11-F.

- h. A Interrupt Control The interrupt control logic enables the DA11-F to cause an interrupt when the window gains bus control via one of the bus request (BR) lines. The processor acknowledges the interrupt request with a bus grant signal, and the DA11-F then sends the processor the vector address to initiate the device service routine.

- i. Control Logic This element contains the logic used to generate the various clock signals and data multiplexer select signals. This logic also is used to interrelate all the various control elements.

- j. A CSR The A port Control and Status Register used to pass parameters and interrupt requests from the A port to the B port. The Control and Status Register is also used to define allowable window operations and to report error conditions.

Figure 2-10 DA11-F Functional Block Diagram

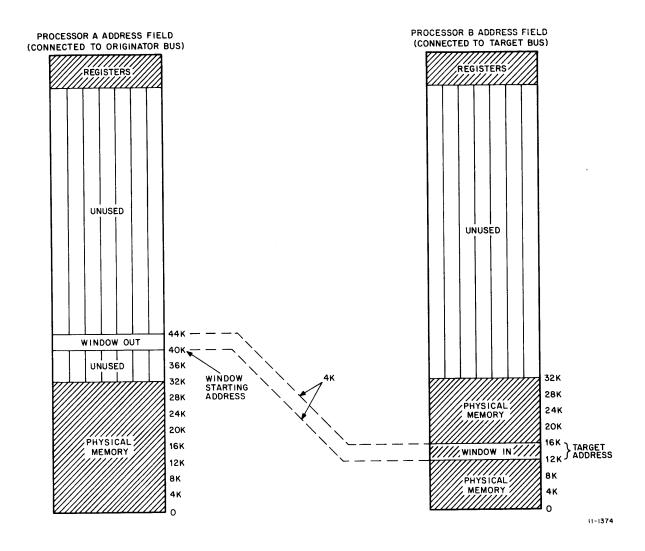

#### 2.4 RELOCATED TARGET ADDRESS

The relocated target address represents the address in physical memory on the target bus. This address appears as virtual memory to the processor connected to the originator port. Figure 2-11 illustrates this idea and shows a 4K window with a starting address of 40K on the originator port. The 4K window is relocated to 12K to 16K in the B processor's physical memory. Thus, the 12K to 16K of physical memory in processor B appears as additional processor A memory. Note that the window has been relocated from 40K to 44K on the originator port to 12K to 16K on the target port.

From the foregoing description, it can be concluded that three parameters are variables: 1) the window size, 2) the window starting address, and 3) the relocated target address. These are described in the following paragraphs.

Figure 2-11 Unibus Window Concept

# 2.4.1 Window Size

The window size or window field can be 1/2K, 1K, 2K, 4K, 8K, 16K, or 32K words. Window size is established by inserting a set of jumper plugs at the input to a hardwired window decoder. This is normally accomplished during installation of the DA11-F.

# 2.4.2 Window Starting Address

The window starting address (originator address) is determined by a set of window address select jumpers located in the window decoder (WDOD-A Bus; WDED-B Bus). The starting address is normally configured during installation of the DA11-F.

#### **NOTE**

Sheet designations of the logic prints are referenced, where applicable. For example, the A bus window decoder is on sheet WDOD as referenced above.

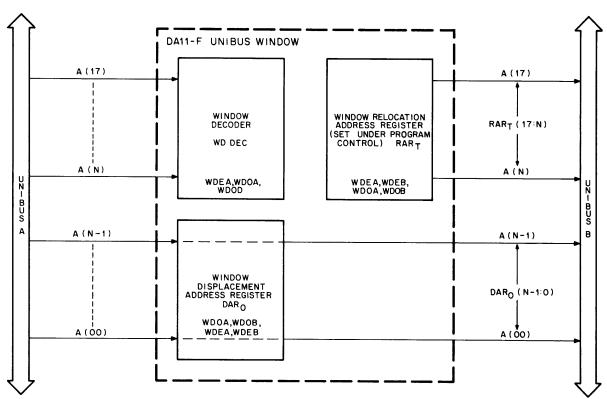

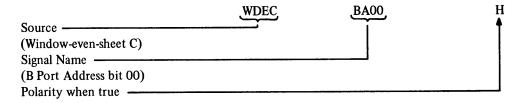

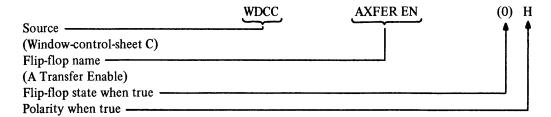

# 2.4.3 Target Address

The target address is the address of the slave device that the user desires to access. This address is derived from summation of a relocation address and a displacement address (Figure 2-12). The relocation address is program controllable and specifies bits (17:N) of the target address. N can be made equal to 10, 11, 12, 13, 14, 15, or 16 depending on the desired window size as shown below.

$RAR_T$  (17:N) = Window Relocation Address Register Target.  $DAR_0$  (N-1:O) = Window Displacement Address Register Originator. Target Address =  $RAR_T$  (17:N) +  $DAR_0$  (N-1:O).

11-1373

Figure 2-12 Address Calculation Block Diagram

| Window<br>Field | Window Decoder<br>(Relocation Address)<br>(17:N) | Window Displacement<br>Address Register (N-1:00)<br>(Displacement Address) |

|-----------------|--------------------------------------------------|----------------------------------------------------------------------------|

| 1/2 <b>K</b>    | 17:10                                            | 09:00                                                                      |

| 1K              | 17:11                                            | 10:00                                                                      |

| 2 <b>K</b>      | 17:12                                            | 11:00                                                                      |

| 4K              | 17:13                                            | 12:00                                                                      |

| 8 <b>K</b>      | 17:14                                            | 13:00                                                                      |

| 16K             | 17:15                                            | 14:00                                                                      |

| 32K             | 17:16                                            | 15:00                                                                      |

For example, the window decoder decodes bits 17 through 11 (N=11) to establish a 1K window size. The remaining address bits (10 through 00) are used to form the displacement address. Address bits (17:N) are replaced on the target bus by the contents of the DA11-F Relocation Register. Displacement address bits (N-1:00) are not replaced, but are simply transferred to the target bus via the DA11-F Displacement Address Register.

# 2.4.4 Target Address Calculation

The two equations below are used to calculate the target address. In the first equation, bus address bits (17:N) are compared with jumpered address bits (17:N) in the window decoder. If they agree bus address bits (N-1:00) are stored in Displacement Address Register DAR<sub>0</sub>. The second equation states that the target address is equal to the relocation address plus the displacement address.

a. If

$$A_0$$

(17:N) = WD DEC (17:N), then A (N-1:00) to DAR<sub>0</sub> (N-1:00)

b.

$$A_T(17:00) = RAR_T(17:N) + DAR_0(N-1:00)$$

To illustrate how the target address is calculated, an example is given. The example shows an originator bus address of 140646 and a desired target address of 520646. The window decoder detects bits 17 through 13, designating a 4K window. If originator bus address bits 17 through 13 match window decoder bits 17 through 13, the displacement address (bits 12 through 00) is stored and combined with the relocated address (bits 17 through 13) to yield 520646.

# Example:

```

A_0 \ (\text{originator address}) = 140646_8 \\ \text{Window} = 4\text{K}; \ \text{therefore}, \ N = 13 \ \text{and window decoder decodes bits 17 through 13}. \\ \text{Window Field} = 140000_8 \ \text{to } 157777_8 \ (24\text{K to } 28\text{K}) \\ \text{DAR}_0 \ (\text{Displacement Address}) = 0646_8 \ (\text{bits } 12 \ \text{through } 00) \\ \text{RAR}_T \ (\text{Relocation Address}) = 52_8 \ (\text{bits } 17 \ \text{through } 13) \\ A_T \ (\text{Relocated Target Address}) = 520646_8 \\ \end{aligned}

```

#### **BUS ADDRESS**

| Originator                          | 17       | 16 | 15     | 14            | 13       | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------|----------|----|--------|---------------|----------|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Address                             | L S      |    |        | <del></del> 1 | 7        | 0  | 0  | 0  | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| (140646)                            | 10       | -  | Equals | 1<br>S:       | ۱ د<br>ا | ı  | ı  | 1  | 1 | 1 | 1 | i | i | Ĭ | Ĭ | i | ì | Ī |

| WD Decoder (14)                     | 10<br>L_ | 0  | 1      | 1             | 0        |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Relocation<br>Address<br>(52)       | 1        | 0  | 1      | 0             | 1        |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Displacement<br>Address<br>(520646) | 1        | 0  | 1      | 0             | 1        | 0  | 0  | 0  | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

## 2.5 WINDOW FIELD JUMPER PLUGS

The size of the window is established by a group of jumper plugs (WDEA,WDOA) associated with address bits 15 through 10. The jumper plugs are inserted in sockets at the input to the hardwired window decoder. A DA (displacement address) or an RA (relocation address) plug can be inserted in the jumper plug receptacle associated with each of these six bits. The jumper plugs determine whether bits 15 through 10 are part of the displacement address or part of the relocation address. For example, N=13 for a 4K window as previously described. The relocation address is then designated by RA (17:13), and the displacement address is designated by DA (12:00) Since bits 15 through 13 are relocation bits, RA plugs are inserted in their plug receptacles, and since bits 12 through 10 are displacement address bits, DA plugs are inserted in the receptacles associated with these bits. Table 2-1 shows the type of plugs inserted to accommodate the various window sizes.

Table 2-1 **Jumper Plug Selection**

|                           |           |           | Addre     | ess Bits  |           |           |                       |                         |

|---------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------------|-------------------------|

| Window<br>Size<br>(Words) | Bit<br>15 | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Relocation<br>Address | Displacement<br>Address |

| 1/2K                      | RA        | RA        | RA        | RA        | RA        | RA        | (17:10)               | ( 9:00)                 |

| 1K                        | RA        | RA        | RA        | RA        | RA        | DA        | (17:11)               | (10:00)                 |

| 2K                        | RA        | RA        | RA        | RA        | DA        | DA        | (17:12)               | (11:00)                 |

| 4K                        | RA        | RA        | RA        | DA        | DA        | DA        | (17:13)               | (12:00)                 |

| 8K                        | RA        | RA        | DA        | DA        | DA        | DA        | (17:14)               | (13:00)                 |

| 16 <b>K</b>               | RA        | DA        | DA        | DA        | DA        | DA        | (17:15)               | (14:00)                 |

| 32K                       | DA        | DA        | DA        | DA        | DA        | DA        | (17:16)               | (15:00)                 |

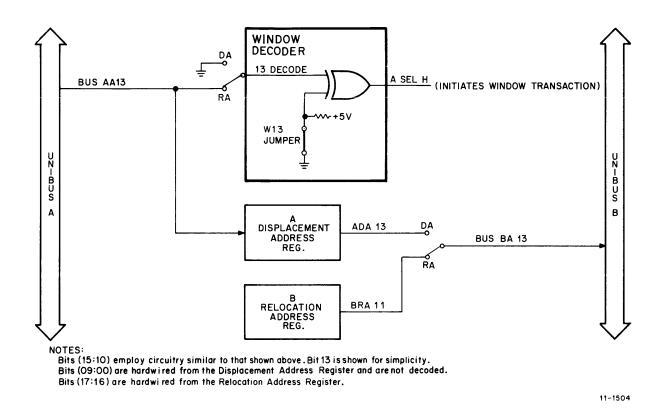

A simplified block diagram of this action is shown in Figure 2-13, where bus A is the originator bus and bus B the target bus. The figure shows the complete path for address bit 13 in a window equal to 4K words. Bit 13 from the A bus is applied to the A window decoder. Therefore, bit 13 of the B Relocation Address Register is supplied to the target bus. This action is caused by the insertion of an RA plug in the bit 13 position. Bits 15 and 14 are routed through identical circuits. On the other hand, bits 12 through 10 are displacement address bits. These bits are first stored in the A Displacement Address Register and then transferred to the target bus during the bus cycle. This action is caused by inserting DA plugs in these bit positions.

Figure 2-13 Jumper Plug Configuration

Figure 2-14 shows the jumper plugs on a block diagram level for one particular bit — namely, bit 13. The diagram shows DA bit 13 and RA bit 11 applied to the jumper plug, which selects one of the two bits. The jumper plug routes the bits to the appropriate data multiplexer, window decoder, or address line, depending on whether the bit is part of the displacement address or relocation address.

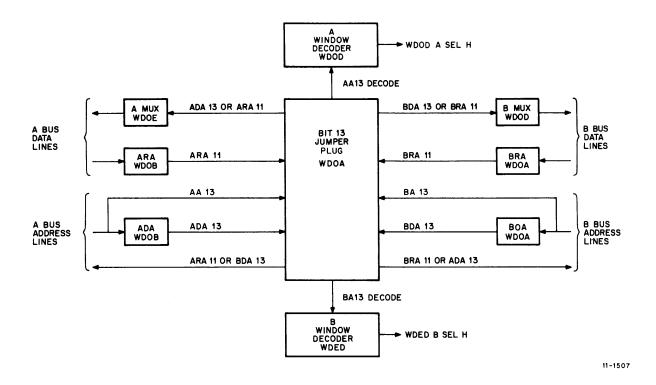

#### 2.6 WINDOW BUS CONTROL

Figure 2-15 represents a simplified logic diagram of the window bus control circuits. The originator bus address and MSYN are applied to the window decoder, which then generates an internal clock pulse.

If the access is invalid (e.g., because the target bus transfer enable bit is not set), the ACCESS ERROR flip-flop is set and an interrupt request is generated on the originator bus (if its interrupt enable bit is set). The program is thus informed that an access error has occurred. The cause of the error can be evaluated by examining the contents of the CSR. (Refer to Paragraph 3.10 for detailed description of error conditions).

Figure 2-14 Bit 13 Jumper Plug Concept

Figure 2-15 Window Bus Control

If, on the other hand, the access is valid, the REQUEST NPR flip-flop is set and an NPR request is asserted on the target bus. When granted control of the bus, the bus control circuit asserts BBSY and initiates the type of bus cycle specified by the control lines.

Three other events occur at the time of the internal clock pulse from the window decoder. First, the originator bus control signals C00 and C01 are stored in the Control Bit Buffer Register (CBUF). Second, the displacement address (i.e., the low-order portion of the originator bus address) is stored in the Displacement Address Register (DAR). And third, if the cycle is a DATO(B), the originator's data is stored in the Data Buffer (DB).

Since Unibus protocol requires that a DATIP cycle must be followed by a DATO(B) cycle and also that the master must maintain BBSY asserted continuously throughout both cycles, the DATIP flip-flop (part of CBUF) is set by the internal clock pulse when that type of cycle is detected. The DATIP flip-flop inhibits the resetting of REQUEST NPR and BBSY until the end of the DATO(B) cycle. Thus the DA11-F maintains BBSY properly asserted on the target bus during a DATIP-DATO(B) sequence.

At the end of each bus cycle, the bus control circuit generates an END CYCLE pulse to reset itself. If the cycle is not a DATIP, this pulse also resets REQUEST NPR, BBSY, and CBUF.

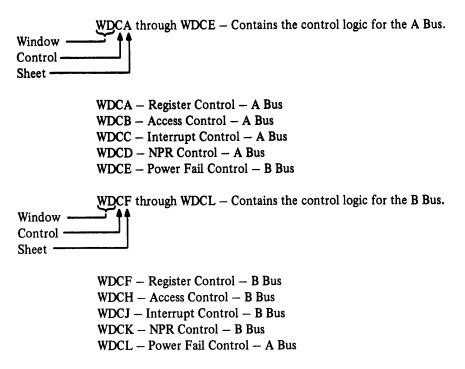

The general description above is for both the A and B buses. The following chart defines the above-mentioned signals for both the A and B buses and designates the applicable drawings where the signals originate.

| Signal Name                | A Bus                       | B Bus                       |

|----------------------------|-----------------------------|-----------------------------|

| ACCESS ERROR               | WDCC AACC ERR (1) H         | WDCJ BACC ERR (1) H         |

| Interrupt Request          | WDCC ABUS REQUEST L         | WDCJ BBUS REQUEST L         |

| REQUEST NPR                | WDCB AREQ NPR (1) H         | WDCH BREQ NPR (1) H         |

| Window Decoder Clock Pulse | WDCB ACLK H                 | WDCH BCLK H                 |

| C0, C1 Control Signals     | BUS AC1 L, BUS AC0 L (WDCB) | BUS BC1 L, BUS BC0 L (WDCH) |

| DATIP                      | WDCB ADATIP (1) H           | WDCH B DATIP (1) H          |

| END CYCLE                  | WDCD AEND CYCLE (1) H       | WDCK BEND CYCLE (1) H       |

| BBSY                       | BUS ABSY L (WDCA)           | BUS BBSY L (WDCF)           |

| CBUF                       | WDCB ACBUF 01 (1) H         | WDCH BCBUF 01 (1) H         |

|                            |                             |                             |

## 2.7 DATA PATH BLOCK DIAGRAM DESCRIPTION

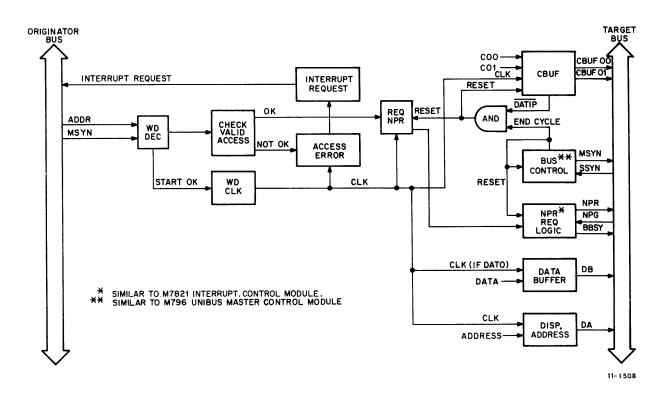

Figure 2-16 is a block diagram of the DA11-F data paths and shows how the data is routed through various registers during data transfer operations.

The key elements associated with routing the data are the data multiplexers. Each multiplexer has eight input lines and one common output. The multiplexer select signals (A MUX SEL, B MUX SEL) direct which input line is to be connected to the output line.

The data multiplexers are used in three modes — program addressable mode, window mode, and interrupt mode. In program addressable mode, a program instruction may read data from an addressable register. Each register is connected to a particular multiplexer input, which is selected by address bits 1, 2, and 3 (bit 0 being disregarded). The registers are connected to the multiplexer inputs in the same order in which the registers are addressed. The CSR is connected to input 0, Input Data Buffer to input 1, Output Data Buffer to input 2, displacement address to input 3, relocation address to input 4, the window starting address to input 5, and the interrupt vector address to input 6. During an interrupt cycle, input 6 is gated to the bus. This position is to place the interrupt vector address on the Unibus data lines. Input 7 is the position that is used to transfer the data directly from the target bus to the originator bus during DATI(P) operations. The data is gated through the window directly with no buffering.

Figure 2-16 DA11-F Data Paths

11-1509

In window mode operations during DATO(B) bus cycles, the data is transferred from the originator bus Data Buffer to input 2 of the target bus data multiplexer.

#### **NOTE**

The A Bus and B Bus multiplexers are divided into odd and even bits and are located on the sheets indicated below:

A Bus multiplexer — odd bits WDOE

A Bus multiplexer — even bits WDED

B Bus multiplexer — odd bits WDOD

B Bus multiplexer - even bits WDEE

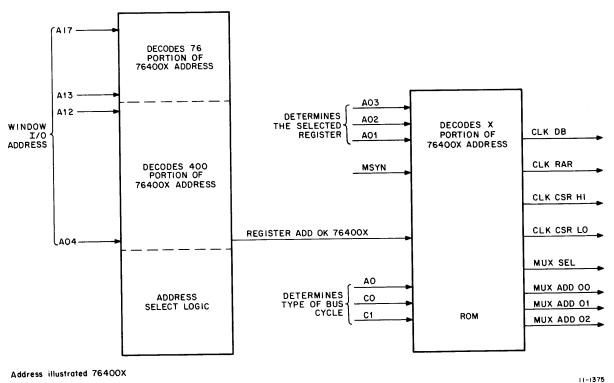

## 2.8 ADDRESSABLE REGISTER SELECT LOGIC

Figure 2-17 shows a simplified diagram of the logic used to select the addressable window registers. Address bits 17 through 13 establish the high-order bits of the I/O address area. Address bits 12 through 4 select the particular block of locations used by the DA11-F. Each address bit is compared against +3V for a 1 or ground for a 0. The output of the address selector is applied to a ROM (read-only memory). The ROM decodes the register specified by address bits A03, A02, and A01 and also decodes the type of bus cycle specified. The outputs of the ROM are used either to clock the specified register that is being written into, or to gate the specified register to the bus data lines when the register is being read (MUX ADDR 0, 1, and 2).

NOTE: Circuit is shown on sheet WDCA for A bus and sheet WDCF for B bus

Figure 2-17 Address Select, Simplified Diagram

Figure 2-18 shows the ROM mapping configuration. A total of 32 decimal locations is shown. The OCTAL LOC column is the octal equivalent of the decimal locations and represents the address where the binary data (in the BINARY DATA column) is stored. The first digit in the OCTAL LOC column specifies four groupings (each grouping being associated with eight ROM locations). These groupings represent the following commands.

| Grouping | Command         |  |  |

|----------|-----------------|--|--|

| 0        | CLOCK LOW BYTE  |  |  |

| 1        | CLOCK FULL WORD |  |  |

| 2        | CLOCK HIGH BYTE |  |  |

| 3        | READ            |  |  |

The first three groups of ROM locations (0, 1, and 2) represent 24 of the  $32_{10}$  addresses and are used during DATO operations to determine which of the seven addressable registers will get clock pulses. The fourth grouping  $(3_8)$  is used during DATI operations to generate MUX SEL signals, which select the addressable register that will be read. Address bit A0 and control lines C0 and C1 are combined to determine the type of bus cycle (DATO, DATI, DATIP) as shown below:

| <b>A0</b> | <b>C0</b> | <b>C1</b> |                   |

|-----------|-----------|-----------|-------------------|

| X         | 0         | 0         | DATI              |

| X         | 0         | 1         | DATIP             |

| X         | 1         | 0         | DATO              |

| 0         | 1         | 1         | DATOB CLK LO BYTE |

| 1         | 1         | 1         | DATOB CLK HI BYTE |

X = don't care

A0, C0, C1 are decoded to yield one of the four command groupings just discussed. The second octal digit in the OCTAL LOC column sequences from 0 through 7 and represents the address of the selected register as shown below:

| Register Address<br>(Second Octal Digit) | Register                                 |  |  |

|------------------------------------------|------------------------------------------|--|--|

| 0                                        | CSR                                      |  |  |

| 1                                        | Input Data Buffer                        |  |  |

| 2                                        | Output Data Buffer                       |  |  |

| 3                                        | Displacement Address                     |  |  |

| 4                                        | Relocation Address                       |  |  |

| 5                                        | Starting Address                         |  |  |

| 6                                        | Vector Address                           |  |  |

| 7                                        | Direct bus-to-bus data path during DATIP |  |  |

For example, if an instruction is executed that writes into the low byte of the CSR, ROM address  $00_8$  should be specified, and if an instruction is executed that writes into the upper and lower byte of the CSR, ROM address  $10_8$  should be specified.

| DECIMAL     | OCTAL      | BINARY   | OCTAL |

|-------------|------------|----------|-------|

| LOC         | LOC_       | DATA     | DATA  |

| Ø           | ଷଷ         | 11101111 | 357   |

|             | Ø1         | 1111111  | 377   |

| •           | 912        | 1111111  | 377   |

| 1<br>2<br>3 | Ø3         | 11111111 | 377   |

| 3           | γ. ο       | 1111111  | 0,,   |

| 4           |            | 1111111  | 377   |

| 5           | <b>75</b>  | 1111111  | 377   |

| 6           | Ø 6        | 1111111  | 377   |

| 7           | 97         | 1111111  | 377   |

| 8           | 10         | 11001111 | 317   |

| 9           | 11         | 01111111 | 177   |

| 10          | 12         | 11111111 | 377   |

| 11          | 13         | 1111111  | 377   |

| 12          | 14         | 10111111 | 277   |

| 13          | 15         | 1111111  | 377   |

| 14          | 16         | 1111111  | 377   |

| 15          | 17         | 1111111  | 377   |

| 16          | 20         | 11011111 | 337   |

| 17          | 21         | 1111111  | 377   |

| 18          | 22         | 1111111  | 377   |

| 19          | 23         | 11111111 | 377   |

| 20          | 24         | 1111111  | 377   |

| 21          | 25         | 1111111  | 377   |

| 22          | 26         | 1111111  | 377   |

| 23          | <b>2</b> 7 | 11111111 | 377   |

| 24          | 30         | 11110111 | 367   |

| 25          | 31         | 11110110 | 366   |

| 26          | 32         | 11110101 | 365   |

| 27          | 33         | 11110100 | 364   |

| 28          | 34         | 11110011 | 363   |

| 29          | 35         | 11110010 | 362   |

| 30          | 36         | 11110001 | 361   |

| 31          | 37         | 11110000 | 360   |

|             |            |          |       |

Figure 2-18 ROM Address Map

# 2.9 INTERRUPT CONTROL LOGIC

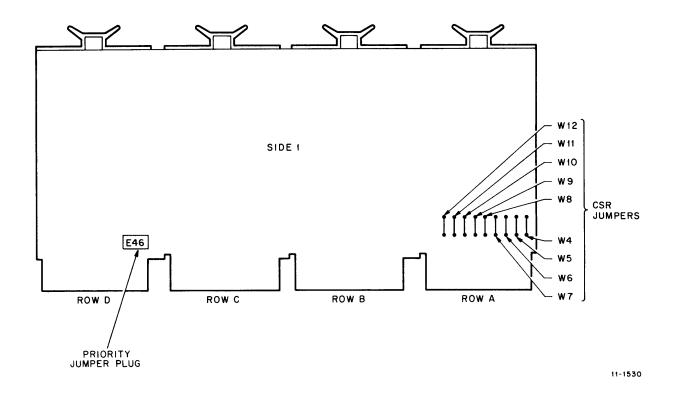

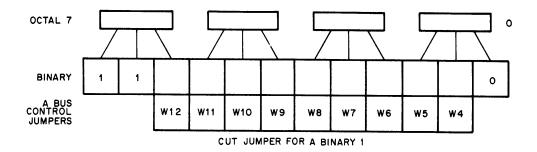

Figure 2-19 is a simplified block diagram of the interrupt control logic that is contained on the bus control modules. The DA11-F can be set to interrupt on either an error condition or a cross-communication request. The interrupt is raised on BR7, which is the highest priority level. The error conditions that can cause an interrupt are access errors (i.e., the originating master was unable to get through the window) or a power-fail sequence on the target bus. The cross-communications interrupt is used to pass parameters between computers. If the interrupt enable (IE) bit in the CSR is set and an interrupt request is asserted (either ERROR or NEW DATA), the interrupt control logic asserts BUS REQUEST. This signal is routed through the priority jumper plug on the control module to the BR7 signal line. When the bus priority arbitration logic in the processor recognizes the request, it issues the corresponding bus grant signal BG7. The interrupt control acknowledges receipt of BG7 by asserting SACK. After the previous bus master completes its operations and releases the bus, the interrupt control clears SACK and asserts BBSY and INTR to notify the processor that an interrupt operation is in progress. At the same time, the output of the BR BBSY flip-flop forces the data multiplexer select logic MUX SEL to gate the vector address from input 6 of the multiplexer

to the bus data lines. After the processor has read the interrupt vector address, it returns SSYN to the interrupt control. The interrupt control then clears INTR, BBSY, and the data lines and resets itself in preparation for the next interrupt request.

The chart below defines the signals described above for both the A bus and B bus and also references the applicable logic print.

| Signal Name                                                                      | A Bus                                                                                                                                                                                                              | B Bus                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR7 ERROR NEW DATA BUS REQUEST BG7 SACK BBSY INTR BR BBSY Flip-Flop MUX SEL SSYN | BUS ABR7 (WDCC) WDCC AACC ERROR (1) H WDCC ANEW DATA (1) H WDCC ABUS REQUEST L BUS BG7 IN H (WDCC) BUS ASACK L (WDCC) BUS ABSY L (WDCC) BUS AINTR L (WDCC) WDCC BR ABSY (1) H WDCA MUX SEL 2, 1, 0, L WDCA ASSYN L | BUS BBR7 L (WDCJ) WDCJ BACC ERROR (1) H WDCJ BNEW DATA (1) H WDCJ BBUS REQUEST L BUS BG7 IN H (WDCJ) BUS BSACK L (WDCJ) BUS BBSY L (WDCJ) BUS BINTR L (WDCJ) WDCJ BR BBSY (1) H WDCF MUX SEL 2, 1, 0, L WDCF BSSYN L |

| CROSS COMMUNICATION REQUEST  A ACCESS ERROR  B AC LO  B TIMEOUT  B NEW DATA      | "OR"  INTERRUPT CONTROL CIRCUIT*                                                                                                                                                                                   | VECTOR — 6  DATA MUX BR 7 TO A BUS WDEE  Y MUX SEL WDCA SELECT INPUT 6  A BUS BB 7 OUT                                                                                                                               |

\*THE INTERRUPT CONTROL CIRCUIT IS SIMILAR TO THE M7821 INTERRUPT CONTROL MODULE

11 - 1510

Figure 2-19 Interrupt Control for a Port

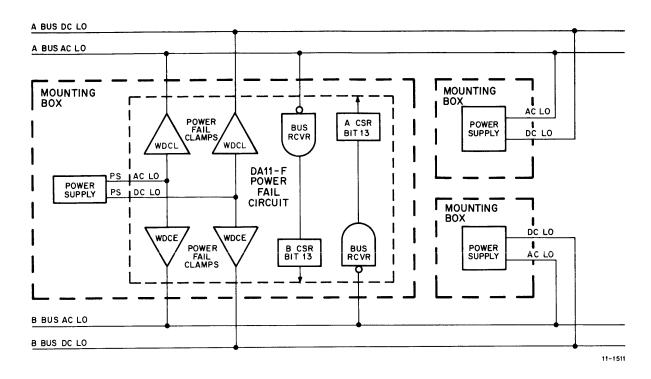

## 2.10 POWER FAIL

Figure 2-20 represents a simplified diagram of the power-fail circuitry in the DA11-F. Two power-fail situations are handled by the DA11-F: first, a powerdown by the DA11-F's mounting box power supply, and second, a powerdown by a power supply in some external mounting box.

Figure 2-20 Power Fail Simplified Block Diagram

If powerdown occurs in the supply that furnishes dc power to the window, the power-fail clamp circuits assert AC LO and DC LO on both buses, thereby initiating power shutdown sequences in both computers.

If powerdown in some external power supply occurs, that device asserts AC LO on the bus. The bus receiver connected to this bus senses the powerdown and reflects it in bit 13 of the CSR on the opposite bus. For example, if a power supply connected to bus A should power down, the bus receiver senses this and reflects it in bit 13 of the CSR connected to the B bus. An interrupt would be generated on the B bus if its interrupt enable (IE) were set. Furthermore, if the B bus processor tried to access the window while AC LO is asserted on bus A, an access error would occur since bus A is in the power-fail mode. This condition could be verified through examination of bit 13 of the CSR on the B bus.

The chart below defines the signals described above for both the A bus and B bus and also references the applicable logic print.

| Signal Name | A Bus               | B Bus               |

|-------------|---------------------|---------------------|

| PS AC LO L  | WDCE PS AC LO L     | WDCL PS AC LO L     |

| PS DC LO L  | WDCE PS DC LO L     | WDCL PS DC LO L     |

| BUS AC LO L | BUS AAC LO L (WDCE) | BUS BAC LO L (WDCL) |

| BUS DC LO L | BUS ADC LO L (WDCE) | BUS BDC LO L (WDCL) |

| CSR 13      | WDCE BAC HI L       | WDCL AAC HI L       |

# CHAPTER 3 PROGRAMMING INFORMATION

# 3.1 GENERAL

Each port of the DA11-F contains seven addressable registers that are under Read/Write control of their respective buses. The registers are assigned addresses in I/O address space as shown in Table 3-1. Note that all addresses in this chapter are in octal notation.

Table 3-1 Register Addresses

| Register             | Mnem                | onic | D          | Address |  |

|----------------------|---------------------|------|------------|---------|--|

|                      | Register A Port B P |      | B Port     |         |  |

| Control and Status   | ACSR                | BCSR | Read/Write | XXXX00  |  |

| Output Data Buffer   | ADB                 | BDB  | Read/Write | XXXX02  |  |

| Input Data Buffer    | BDB                 | ADB  | Read only  | XXXX04  |  |

| Displacement Address | ADA                 | BDA  | Read only  | XXXX06  |  |

| Relocation Address   | ARA                 | BRA  | Read/Write | XXXX10  |  |

| Starting Address     | ASA                 | BSA  | Read only  | XXXX12  |  |

| Vector Address       | AVA                 | BVA  | Read only  | XXXX14  |  |

The Control and Status Register can be assigned to any address in the I/O register page (760000 to 777777) on an even 20<sub>8</sub> boundary. The addresses of the other registers are assigned sequentially after the CSR. For example, if the CSR is assigned to 764000, the addressable registers are assigned the following addresses:

| Control and Status   | 764000 |

|----------------------|--------|

| Output Data Buffer   | 764002 |

| Input Data Buffer    | 764004 |

| Displacement Address | 764006 |

| Relocation Address   | 764010 |

| Starting Address     | 764012 |

| Vector Address       | 764014 |

These registers are normally assigned to the user address field from 764000 to 764776.

The DA11-F is normally to the user address field as follows:

|             | A Port | B Port |

|-------------|--------|--------|

| First Unit  | 764000 | 764020 |

| Second Unit | 764020 | 764040 |

| Third Unit  | 764040 | 764060 |

| Fourth Unit | 764060 | 764000 |

Each of the addressable I/O registers is described in detail in the following paragraphs.

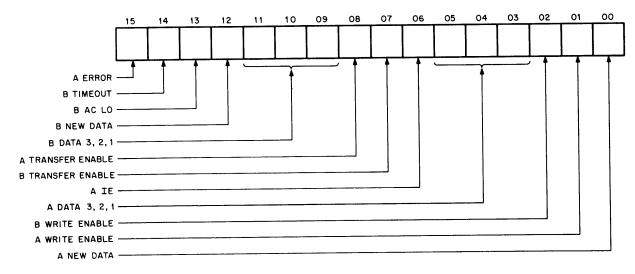

# 3.2 CONTROL AND STATUS REGISTER (CSR)

Each port contains a 16-bit Control and Status Register (CSR). The CSRs are interconnected to provide a means of transferring parameters and interrupt requests from one processor to another. Figure 3-1 illustrates the bit format of the CSR. Table 3-2 defines the interaction between each of the CSRs. For example, bits 11, 10, and 9 of the ACSR are used to read the contents of bits 5, 4, and 3 of the BCSR. The description in this chapter covers the ACSR; however, by reversing the A and B prefixes of each bit, the description is also applicable to the BCSR. Each bit is described in the following paragraphs. The program can read the contents of all bits but can only write into the bits so designated.

NOTE:

Bits are designated for A CSR. Reverse A and B prefixes to find equivalent B CSR designations.

11-1512

Figure 3-1 ACSR Bit Format

Table 3-2

Control and Status Registers WCSR 764XXX

| Bit | ACSR              | BCSR              | Program Action  |

|-----|-------------------|-------------------|-----------------|

| 15* | A Error           | B Error           | Read/Write 0**  |

| 14  | B Time Out        | A Time Out        | Read Only       |

| 13  | B ACLO            | A ACLO            | Read Only       |

| 12* | B New Data        | A New Data        | Read/Write 0**  |

| 11  | B Data 3          | A Data 3          | Read Only       |

| 10  | B Data 2          | A Data 2          | Read Only       |

| 9   | B Data 1          | A Data 1          | Read Only       |

| 8   | A Transfer Enable | B Transfer Enable | Read/Write      |

| 7   | B Transfer Enable | A Transfer Enable | Read Only       |

| 6   | A IE              | B IE              | Read/Write      |

| 5   | A Data 3          | B Data 3          | Read/Write      |

| 4   | A Data 2          | B Data 2          | Read/Write      |

| 3   | A Data 1          | B Data 1          | Read/Write      |

| 2   | B Write Enable    | A Write Enable    | Read/Write      |

| 1   | A Write Enable    | B Write Enable    | Read/Write      |

| 0   | A New Data        | B New Data        | Read/Write 1*** |

<sup>\*</sup>If bit 15 or bit 12 is set and the interrupt enable bit (bit 6) is set, an interrupt will occur.

All bits are cleared by INIT.

Bit Function

Error. Set on this port if an originating device on this bus cannot make a legal access to the opposite bus. The following conditions cause this bit to set:

- 1. Originator attempts a window transaction and the Transfer Enable of the opposite bus is not set. To clear, write a 0 into bit 15.

- 2. Originator attempts a DATO(B) or a DATIP-DATO(B) cycle and the Write Enable bit of the opposite bus is not set. To clear, write a 0 into bit 15.

- 3. SSYN Time Out occurs while the window is master of the opposite bus. (Also indicated by bit 14.) To clear, write a 0 into bit 15.

- 4. ACLO is asserted on the opposite bus. (Also indicated by bit 13.) To clear, restore power to opposite bus.

- 5. Originators on both buses attempted DATI(P) cycles simultaneously. To clear, write a 0 into bit 15. When the error bit is set, further window transactions originating on this bus are inhibited. An attempt to use the window will result in SSYN Time Out. If the Interrupt Enable bit (bit 6) is set when the Error bit sets, an interrupt will occur.

<sup>\*\*</sup>The program can read the contents of all bits but can only write a 0 into these bit positions.

<sup>\*\*\*</sup>The program can read the contents of all bits but can only write a 1 into this bit position.

| Bit    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14     | Time Out. Set on this port if SSYN Time Out occurs while the window is master of the opposite bus. When set, sets Error (bit 15). Clear by writing 0 into bit 15.                                                                                                                                                                                                                                                                                                                               |

| 13     | ACLO. Set on this port if ACLO is asserted on the opposite bus. When set, sets Error (bit 15). Clear by restoring power to opposite bus.                                                                                                                                                                                                                                                                                                                                                        |

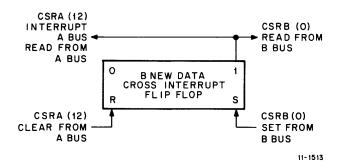

| 12     | New Data. Read out of contents of CSR (0) on the opposite port. Used by the opposite bus processor to indicate that it has loaded new information into its CSR or its Data Buffer (DB). The cross-interrupt bit (New Data) is read/set as bit 0 on one port and read/clear as bit 12 on the other port. If Interrupt Enable (bit 6) is set, then setting New Data on the opposite port causes an interrupt on this bus.                                                                         |

|        | For example, if bit 0 (B New Data) is set on the B port, a 1 appears at bit 12 of the A port. If Interrupt Enable (bit 6) on the A port is set, an interrupt request will be generated on the A bus. When the A processor has serviced the interrupt, it clears B New Data by writing a 0 into bit 12 of its own CSR. This action clears bit 0 of the B port CSR, thereby indicating that the message has been received. The cross interrupt logic for B New Data is illustrated in Figure 3-2. |

| (11:9) | Data (3:1). Read out of contents of CSR (5:3) on the opposite bus. Used to pass parameters between programs. Defined by program.                                                                                                                                                                                                                                                                                                                                                                |

| 8      | Transfer Enable. Set by program on this bus to indicate that this port is ready to be used as a target for transactions originating on the opposite bus. Setting Transfer Enable implies that the Relocation Address Register on this port is loaded with the correct relocation factor and that CSR1 Write Enable is in the correct state.                                                                                                                                                     |

| 7      | Transfer Enable. Read out of contents of CSR(8) on the opposite bus. When set, indicates that an originator on this bus may perform a window transaction to the opposite bus. If clear, an attempt to originate a window transaction from this bus will set Error on this port.                                                                                                                                                                                                                 |

| 6      | IE-Interrupt Enable. When set by program on this bus, allows interrupts to occur when CSR (15 or 12) of this port are set.                                                                                                                                                                                                                                                                                                                                                                      |

| (5:3)  | Data (3:1). Loaded by program on this bus to pass parameters to program on opposite bus. Defined by program.                                                                                                                                                                                                                                                                                                                                                                                    |

| 2      | Write Enable. Read out of contents of CSR(1) on the opposite bus. When set, indicates that an originator on this bus may do a DATO(B) cycle to a location on the opposite bus. If clear, an attempt to originate a DATO(B) cycle from this bus will set Error on this port.                                                                                                                                                                                                                     |

| 1      | Write Enable. Set by program on this bus to indicate that the program on the opposite bus may do a DATO(B) cycle to a location on this bus.                                                                                                                                                                                                                                                                                                                                                     |

0

New Data. Set by program on this bus to indicate that either the CSR or the Data Buffer (DB) on this

port is loaded with new information. Cleared by writing 0 into CSR(12) on the opposite port.

Figure 3-2 Cross Interrupt Logic

### 3.3 OUTPUT DATA BUFFER (DB)

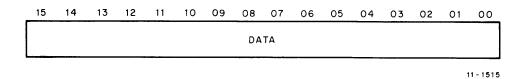

The Output Data Buffer operates (Figure 3-3) in two modes: either as temporary data storage during window transactions or as a cross communications register during interprocessor program transfers.

If Transfer Enable is set and this port is on the originator bus, the Data Buffer temporarily stores the data during DATO(B) cycles. In this mode, the Data Buffer is read only by the program.

If Transfer Enable is clear, the Data Buffer (DB) can be used by the program to pass information to the opposite processor. In this mode, the Data Buffer is Read/Write from this bus and read only from the opposite bus. The Data Buffer is cleared by INIT.

Figure 3-3 Output Data Buffer Bit Format

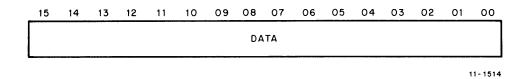

# 3.4 INPUT DATA BUFFER (DB)

The Input Data Buffer (Figure 3-4) is a read-only access to the contents of the Data Buffer on the opposite bus.

When Transfer Enable is clear, the Input Data Buffer can be used by the program to receive information from the opposite processor.

Figure 3-4 Input Data Buffer Bit Format

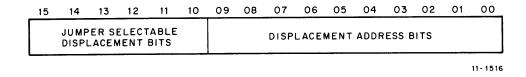

# 3.5 DISPLACEMENT ADDRESS REGISTER (DAR)

The Displacement Address Register (Figure 3-5) serves as temporary storage for the window displacement address when this port is on the originator bus.

When the originator window address decoder detects a match in bits (17:N), the low-order address bits (N-1:0) are stored in the DA Register and then used in conjunction with the Relocation Address Register on the opposite bus to form the relocated target address.

The window decoder and the Displacement Address Register vary in length according to the size of the window field:

| Window Field (Words) | Window Decoder | DAR   |

|----------------------|----------------|-------|

| 1/2K                 | 17:10          | 09:00 |

| 1 <b>K</b>           | 17:11          | 10:00 |

| 2K                   | 17:12          | 11:00 |

| 4K                   | 17:13          | 12:00 |

| 8 <b>K</b>           | 17:14          | 13:00 |

| 16 <b>K</b>          | 17:15          | 14:00 |

| 32 <b>K</b>          | 17:16          | 15:00 |

If an access error occurs, further transactions from originating devices on this bus are inhibited and the DAR then contains the address of the illegal access. The recovery program can inspect the DAR to determine the relative address that failed. The DAR is written into automatically by originating window transactions. The program can read the contents of the DAR but cannot write into it. The DAR is cleared by INIT.

Figure 3-5 Displacement Address Register Bit Format

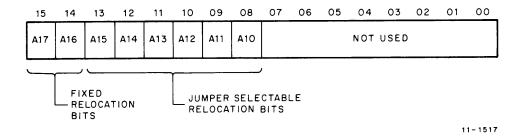

# 3.6 RELOCATION ADDRESS REGISTER (RAR)

The Relocation Address Register (Figure 3-6) specifies the high-order bits (17:N) of the relocated target address.

The RAR is loaded under program control and specifies bits (17:N) of the relocated target address when this port is master of the target bus. The RAR is used in conjunction with the Displacement Address Register on the opposite bus to form the complete target address.

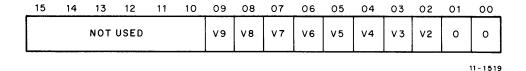

Figure 3-6 Relocation Address Register Bit Format

The length of the RAR is jumper selectable and is set to the same length as the window decoder on the opposite bus. The window address field may be set to 1/2K, 1K, 2K, 4K, 8K, 16K, or 32K words. The window field and the RAR are related as follows:

| Window Field (Words) | Window Decoder | RAR   |

|----------------------|----------------|-------|

| 1/2K                 | 17:10          | 15:8  |

| 1K                   | 17:11          | 15:9  |

| 2K                   | 17:12          | 15:10 |

| 4K                   | 17:13          | 15:11 |

| 8 <b>K</b>           | 17:14          | 15:12 |

| 16 <b>K</b>          | 17:15          | 15:13 |

| 32K                  | 17:16          | 15:14 |

Note that the data bits in the RAR are shifted two places from their corresponding address bits. That is:

| RAR | Specifies | Target Bus Address |

|-----|-----------|--------------------|

| 15  |           | 17                 |

| 14  |           | 16                 |

| 13  |           | 15                 |

| 12  |           | 14                 |

| 11  |           | 13                 |

| 10  |           | 12                 |

| 9   |           | 11                 |

| 8   |           | 10                 |

| -   |           |                    |

The RAR is Read/Write for bits (17:N). Bits (N-1:0) are always read as 0. Writing has no effect on (N-1:0). The RAR is cleared by INIT.

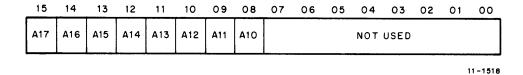

#### 3.7 STARTING ADDRESS REGISTER (SAR)

The Starting Address Register (SAR) is a read-only register containing the address bits of the window decoder. These bits are used to determine the window field starting address (Figure 3-7).

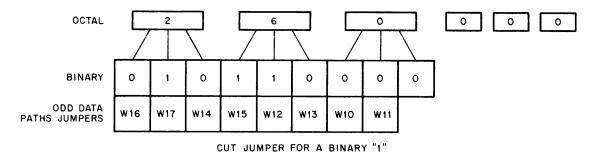

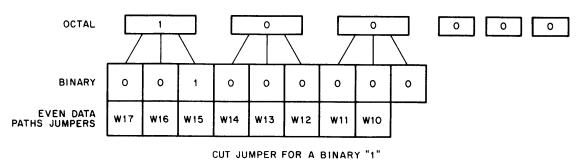

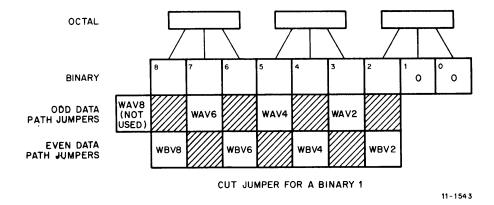

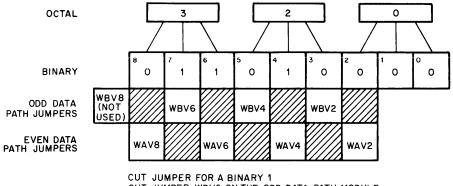

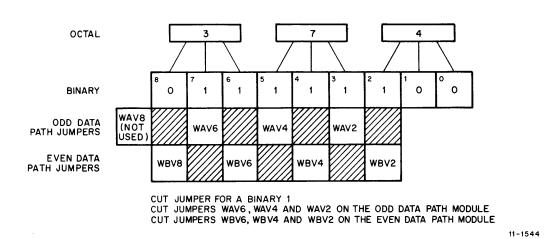

At installation, the window field starting address is established by cutting a set of jumpers on the data paths modules. The pattern cut in the jumpers is a binary representation of the address of the lower boundary of the window field on the originator port. The SAR provides the program with the capability to read the jumper pattern and verify that it is set to the correct address. Its main use is in maintenance diagnostics.

Note that SAR (7:0) are not used and are always read as 0s.

Figure 3-7 Starting Address Register Bit Format

# 3.8 VECTOR ADDRESS REGISTER (VAR)

The Vector Address Register (VAR) is a read-only register containing the vector address. This address is placed on the Unibus by the DA11-F during an interrupt cycle (Figure 3-8).

At installation, the vector address is established by cutting a set of jumpers on the data paths modules. The pattern cut in the jumpers is a binary representation of the vector address used by the DA11-F to interrupt the processor. The VAR provides the program with the capability to read the jumper pattern and verify that it is set to the correct address. Its main use is in maintenance diagnostics.

Note that VAR (15:10) are not used and are always read as 0s. Also, VAR (1:0) are always read as 0s since vector addresses occur only on even 48 boundaries.

Figure 3-8 Vector Address Register Bit Format

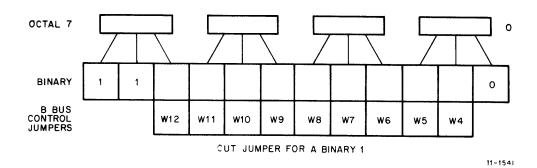

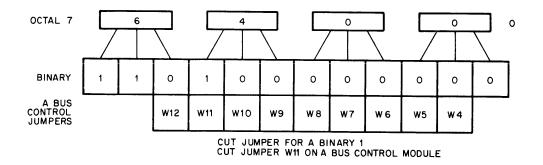

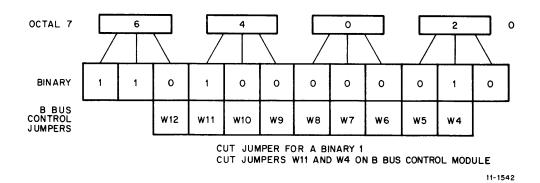

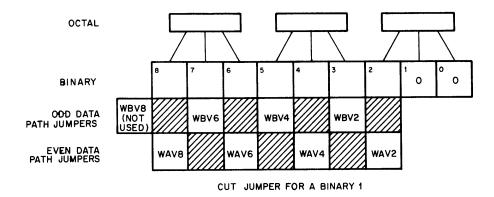

#### 3.9 PROGRAMMING EXAMPLES