digital

CR11 card reader system manual

# CR11 card reader system manual

DEC-11-HCRB-D

1st Edition October 1971 2nd Printing (Rev) March 1972

Copyright © 1971, 1972 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP **FOCAL**

FLIP CHIP DIGITAL

COMPUTER LAB

UNIBUS

#### CONTENTS

|           |                             | Page |

|-----------|-----------------------------|------|

| CHAPTER 1 | INTRODUCTION                |      |

| 1.1       | Introduction                | 1-1  |

| 1.2       | Scope                       | 1-1  |

| 1.3       | Specifications              | 1-2  |

| 1.4       | Maintenance                 | 1-2  |

| 1.5       | Engineering Drawings        | 1-4  |

| 1.6       | Terminology                 | 1-5  |

| CHAPTER 2 | GENERAL DESCRIPTION         |      |

| 2.1       | Introduction                | 2-1  |

| 2.2       | System Operation            | 2-1  |

| 2.3       | Card Reader                 | 2-1  |

| 2.4       | CR11 Controller             | 2-2  |

| CHAPTER 3 | OPERATION                   |      |

| 3.1       | Scope                       | 3-1  |

| 3.2       | Controls and Indicators     | 3-1  |

| 3.3       | Card Handling Procedures    | 3-5  |

| 3.3.1     | Loading Cards               | 3-5  |

| 3.3.2     | Unloading Cards             |      |

| 3.3.3     | Correcting Error Conditions | 3-5  |

| 3.4       | Operating Procedures        | 3-5  |

| 3.4.1     | Off-Line Operation          | 3-6  |

| 3.4.2     | On-Line Operation           | 3-7  |

| CHAPTER 4 | PROGRAMMING INFORMATION     |      |

| 4.1       | Scope                       | 4-1  |

| 4.2       | Device Registers            | 4-1  |

| 4.3       | Interrupts                  | 4-7  |

| 4.4       | Program Example             | 4-7  |

| CHAPTER 5 | THEORY OF OPERATION         |      |

| 5.1       | Introduction                | 5-1  |

| 5.2       | Address Selection           | 5-1  |

| 5.2.1     | Inputs                      | 5-2  |

| 5.2.2     | Outputs                     | 5-3  |

| 5.2.3     | Slave Sync (SSYN)           | 5-4  |

| 5.3       | Interrupt Control           | 5-4  |

| 5.4       | Status Register             | 5-6  |

| 5.4.1     | Error (Bit 15)              | 5-6  |

| 5.4.2     | Card Done (Bit 14)          | 5-7  |

#### CONTENTS (Cont)

Page

| 5.4.3                                                                    | Supply Error (Bit 13)                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-8                                                                |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 5.4.4                                                                    | Card Reader Check (Bit 12)                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-8                                                                |

| 5.4.5                                                                    | Timing Error (Bit 11)                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-8                                                                |

| 5.4.6                                                                    | Reader Transition to On-Line (Bit 10)                                                                                                                                                                                                                                                                                                                                                                                                            | 5-9                                                                |

| 5.4.7                                                                    | BUSY (Bit 09)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-9                                                                |

| 5.4.8                                                                    | Reader Ready Status (Bit 08)                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-9                                                                |

| 5.4.9                                                                    | Column Ready (Bit 07)                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-10                                                               |

| 5.4.10                                                                   | Interrupt Enable (Bit 06)                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-10                                                               |

| 5.4.11                                                                   | Eject (Bit 01)                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-11                                                               |

| 5.4.12                                                                   | READ (Bit 00)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-11                                                               |

| 5.5                                                                      | Data Buffer Register                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-12                                                               |

| 5.6                                                                      | Encoding Network                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-12                                                               |

| APPENDIX A                                                               | GDI CARD READERS                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| A.1                                                                      | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                            | A-1                                                                |

| A.2                                                                      | GDI Model 100 Card Reader                                                                                                                                                                                                                                                                                                                                                                                                                        | A-1                                                                |

| A.3                                                                      | GDI Model 100M Card Reader                                                                                                                                                                                                                                                                                                                                                                                                                       | A-3                                                                |

| APPENDIX B                                                               | CARD READER INTERFACE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| APPENDIX C                                                               | HOLLERITH CODE                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                                                                          | HOLDERATH CODE                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                                                                          | INTEGRATED CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

|                                                                          | INTEGRATED CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                               |

| APPENDIX D                                                               | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Page</b><br>2-3                                                 |

| APPENDIX D                                                               | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                  |

| APPENDIX D Figure No. 2-1                                                | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                 | 2-3                                                                |

| APPENDIX D  Figure No. 2-1 3-1                                           | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators                                                                                                                                                                                                                                                                                                             | 2-3<br>3-2                                                         |

| APPENDIX D  Figure No. 2-1 3-1 4-1                                       | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments                                                                                                                                                                                                                                                                             | 2-3<br>3-2<br>4-2                                                  |

| APPENDIX D  Figure No. 2-1 3-1 4-1 4-2                                   | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1)                                                                                                                                                                                                                                 | 2-3<br>3-2<br>4-2<br>4-5                                           |

| Figure No. 2-1 3-1 4-1 4-2 4-3                                           | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2)                                                                                                                                                                                     | 2-3<br>3-2<br>4-2<br>4-5<br>4-6                                    |

| APPENDIX D  Figure No. 2-1 3-1 4-1 4-2 4-3 5-1                           | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram                                                                                                                                        | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3                             |

| APPENDIX D  Figure No.  2-1 3-1 4-1 4-2 4-3 5-1 5-2                      | ILLUSTRATIONS  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram Controller Select Address Format                                                                                                                        | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3<br>5-3                      |

| Figure No. 2-1 3-1 4-1 4-2 4-3 5-1 5-2 5-3                               | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram Controller Select Address Format Interrupt Control Logic — Simplified Diagram                                                          | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3<br>5-3<br>5-5               |

| APPENDIX D  Figure No.  2-1  3-1  4-1  4-2  4-3  5-1  5-2  5-3  A-1      | INTEGRATED CIRCUIT DESCRIPTION  ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram Controller Select Address Format Interrupt Control Logic — Simplified Diagram GDI Model 100 Card Reader                                | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3<br>5-3<br>5-5<br>A-4        |

| APPENDIX D  Figure No.  2-1  3-1  4-1  4-2  4-3  5-1  5-2  5-3  A-1  A-2 | ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram Controller Select Address Format Interrupt Control Logic — Simplified Diagram GDI Model 100 Card Reader GDI Model 100 Control Panel                                    | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3<br>5-3<br>5-5<br>A-4<br>A-4 |

| Figure No. 2-1 3-1 4-1 4-2 4-3 5-1 5-2 5-3 A-1 A-2 A-3                   | ILLUSTRATIONS  Title  CR11 Controller — Simplified Block Diagram Card Reader Controls and Indicators Status Register Bit Assignments Data Buffer Register Bit Assignments (CRB1) Data Buffer Register Bit Assignments (CRB2) Address Selection Logic — Simplified Diagram Controller Select Address Format Interrupt Control Logic — Simplified Diagram GDI Model 100 Card Reader GDI Model 100 Control Panel GDI Model 100M Optical Mark Reader | 2-3<br>3-2<br>4-2<br>4-5<br>4-6<br>5-3<br>5-3<br>5-5<br>A-4<br>A-4 |

#### **TABLES**

| Table No. | Title                                  | Page |

|-----------|----------------------------------------|------|

| 1-1       | Applicable Documents                   | 1-2  |

| 1-2       | CR11 Controller Specifications         | 1-3  |

| 1-3       | Documation Card Reader Specifications  | 1-3  |

| 1-4       | GDI Card Reader Specifications         | 1-4  |

| 1-5       | Master Drawing List                    | 1-5  |

| 3-1       | Front Panel Controls and Indicators    | 3-3  |

| 3-2       | Rear Panel Controls                    | 3-4  |

| 3-3       | Error Alarm Causes and Remedies        | 3-6  |

| 4-1       | Standard Device Register Assignments   | 4-1  |

| 5-1       | Gating and Select Line Signals         | 5-2  |

| 5-2       | Select Lines                           | 5-4  |

| 5-3       | Gating Control Signals                 | 5-4  |

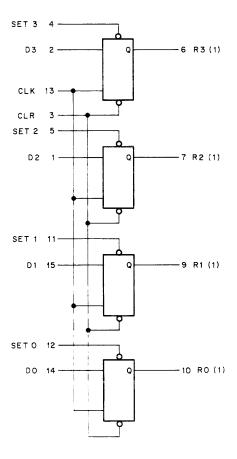

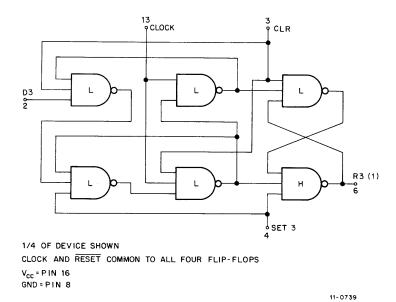

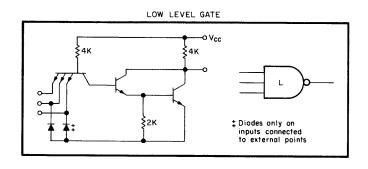

| 5-4       | Status Register Bits on 4015 IC        | 5-6  |

| 5-5       | Encoding Network Truth Table           | 5-13 |

| A-1       | GDI Model 100 Controls and Indicators  | A-1  |

| A-2       | GDI Model 100M Controls and Indicators | A-6  |

| B-1       | Interfacing Signals                    | B-1  |

| D-1       | Truth Table                            | D-3  |

## CHAPTER 1 INTRODUCTION

#### 1.1 INTRODUCTION

The CR11 Card Reader System is a card handling system designed to interface with the PDP-11 family of processors and peripherals to read marked or punched Hollerith data cards at rates up to 600 cards per minute. The CR11 System consists of two distinct components: a card reader and a DEC PDP-11 interface unit, which is referred to as the CR11 Controller.

a. Card Reader

A motorized card handling device that reads information from EIA standard (Hollerith code) cards. The unit reads 12-row, 80-column cards at a nominal rate of 200 to 600 cards per minute, depending on the specific card reader used

The CR11 System is fully compatible with Documation punched card readers, GDI punched card readers, and GDI mark/sense readers.

b. CR11 Controller

An interface between the card reader and the PDP-11 Unibus. Controls data transfers between the card reader and other devices in a PDP-11 System. Provides a 12-bit output character for standard data transfers and an 8-bit output character (one byte) when it is desired to use the proposed compressed Hollerith code. Also monitors reader operation and issues appropriate control commands.

The controller is completely plug-compatible with the above-mentioned card readers; no modifications are required.

Also referred to an "control unit", "interface", and "reader control".

#### 1.2 SCOPE

This manual provides the user with the information needed to operate the CR11 Card Reader System and provides the theory of operation and logic diagrams necessary to understand and maintain the CR11 Controller.

This manual and the appropriate card reader manual must be used together for a complete understanding of the entire CR11 System. The prime subject of this manual is the CR11 Controller. In addition to providing complete coverage of the controller, this manual includes sections covering overall system operation and programming. Because of the number of different card readers that can be used with the CR11 Controller, this manual only covers the operation of the Documation Model M200 Card Reader. Operation of other card reader models, as well as any significant differences, are included in Appendix A.

Documation is a trademark of Documation, Incorporated, Melbourne, Florida.

The prime subject of the card reader manual is the card reader itself. The manual presents a detailed discussion of the print mechanism and electronics including installation, operation, principles of operation, maintenance, troubleshooting, and engineering drawings.

Table 1-1 lists related PDP-11 System documents that are applicable to the CR11 Card Reader System.

Table 1-1

Applicable Documents

| Title                                          | Number                                    | Coverage                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unibus Interface Manual,<br>Second Edition     | DEC-11-HIAB-D                             | Provides detailed theory, flow, and logic descriptions of the Unibus and external device logic.                                                                                                                                                                                                            |

| PDP-11/20 System* (7-volume series)            | DEC-11-HR1B-D<br>through<br>DEC-11-HR7B-D | Provides detailed theory of operation, flow, logic diagrams, operation, installation, and maintenance for components of the PDP-11 System including processor, memory, console, and power supply.                                                                                                          |

| PDP-11 Processor<br>Handbook                   | DEC, 1972                                 | A two-part general handbook. The first part discusses system architecture, addressing modes, the instruction set, and programming techniques. The second part is devoted to a discussion of software.                                                                                                      |

| PDP-11 Peripherals and<br>Interfacing Handbook | DEC, 1972                                 | A two-part handbook. The first part is devoted to a discussion of the various peripherals used with PDP-11 Systems. The second part provides detailed theory, flow, and logic descriptions of the Unibus and external device logic; methods of interface construction; and examples of typical interfaces. |

| Paper-Tape Software<br>Programming Handbook    | DEC-11-GGPB-D                             | Provides a detailed discussion of the PDP-11 software system used to load, dump, edit, assemble, and debug PDP-11 programs; input/output programming; and the floating-point and math package.                                                                                                             |

<sup>\*</sup>Applicable PDP-11/05, 11/15, and 11/45 manuals provide system coverage on other PDP-11 Systems.

#### 1.3 SPECIFICATIONS

Operating and physical specifications for the CR11 Controller are given in Table 1-2. Specifications for all Documation type card readers are given in Table 1-3 and specifications for GDI (General Design, Inc.) card readers are given in Table 1-4.

#### 1.4 MAINTENANCE

The basic maintenance philosophy of the CR11 Card Reader System is to present the user with the information necessary to understand normal system operation. The user can utilize this information when analyzing trouble symptoms to determine necessary corrective action. It is beyond the scope of this manual to present detailed troubleshooting information.

Table 1-2

CR11 Controller Specifications

Registers: Status Register (CRS)

Data Buffer Register (CRB1)

Data Buffer Register Encoded Output (CRB2)

Register Addresses: CRS 777160

CRB1 777162 CRB2 777164

Data Outputs: CRB1 = 12-bit character (Hollerith code)

CRB2 = 8-bit character (compressed Hollerith code)

Interrupts: Priority = BR6 (may be changed by jumper plug)

Vector = location 230

Types = error, transition to on-line, column ready, and card done

Commands: Read, eject, and interrupt enable

Status Indications: Error conditions = error, card supply error, card reader check, timing error

Operational conditions = reader ready, reader transition to on-line, busy,

column ready, card done

Card Reader Plug-compatible with Documation and GDI card readers. If reader handles

only punched cards, two jumpers must be removed from status register; if

reader handles both punched and mark sense cards, no modification needed.

Size: The CR11 Controller consists of a single quad module (M8290) that occu-

pies 1/4 of a DD11-A or one of two controller slots in a KA11, KC11, or

other PDP-11 Processor System unit.

Power: 1.5A @ +5V (derived from H720 Power Supply in mounting box where

controller is installed).

Table 1-3

Documation Card Reader Specifications

#### All Models

Compatibility:

Card Type:

Standard 80-column EIA card

Light Source:

Infrared light emitting diode

Read Station:

Photo transistor, 12 bits simultaneously

Electronics:

7400 Series TTL integrated circuit logic

Internal Clock: Crystal oscillator

#### Variations

|                              | Model M200 | Model M300 | Model M600 |

|------------------------------|------------|------------|------------|

| Card Rate (cards/minute)     | 300        | 300        | 600        |

| Hopper/Stacker Card Capacity | 600        | 100        | 0          |

| Power (in VA):               |            |            |            |

| Starting Load                | 950        | 100        | 0          |

| Running Load                 | 400        | 450        | )          |

(continued on next page)

### Table 1-3 (Cont) Documation Card Reader Specifications

| Variations (cont) |            |            |            |

|-------------------|------------|------------|------------|

|                   | Model M200 | Model M300 | Model M600 |

| Dimensions:       |            |            |            |

| Height            | 11 in.     | 13-        | 9/16 in.   |

| Width             | 19-1/4 in. |            | 1/16 in.   |

| Depth             | 14 in.     | 18         | •          |

| Weight            | 60 lb      | 75 lb      | 75 lb      |

Table 1-4

GDI Card Reader Specifications

| Card Type:                    | Standard 80-column EIA card                                           |

|-------------------------------|-----------------------------------------------------------------------|

| Card Rate:                    | 200 cards/minute (nominal)                                            |

| Rate Control:                 | Frequency of pick (read) command at discretion of controller          |

| Hopper/Stacker Card Capacity: | 450 cards                                                             |

| Read Station:                 | Silicon photocells, 12 bits simultaneously                            |

| Internal Clock:               | Timing disk and photocell                                             |

| Electronics:                  | Positive logic DTuL 930 series integrated circuits                    |

| Input Power:                  | 115 ± 10 Vac, 60 Hz, single-phase                                     |

| Power Consumption:            | Less than 300W                                                        |

| Size:                         | 14 in. wide, 18 in. deep, 18 in. high                                 |

| ations                        |                                                                       |

| Weight:                       | Model 100 = 47 lb                                                     |

|                               | Model $100M = 52 lb$                                                  |

| Card Type:                    | Model 100 = Reads only 80-column punched cards                        |

|                               | Model 100M = Reads punched or marked 40-column cards with clock track |

General PDP-11 maintenance information is presented in the *PDP-11 Conventions Manual*, DEC-11-HR6B-D. Detailed maintenance and troubleshooting information is normally included in each manual covering a specific card reader.

#### 1.5 ENGINEERING DRAWINGS

A complete set of reduced engineering drawings and module circuit schematics is provided in a companion volume to this manual entitled CR11 Card Reader System, Engineering Drawings. A list of these drawings is presented in Table 1-5. The general logic symbols used on these drawings are described in the DEC Logic Handbook, 1971. Specific symbols and conventions are also included in the PDP-11 Conventions Manual, DEC-11-HR6B-D.

Table 1-5 Master Drawing List

| No. of Sheets | Title                          |

|---------------|--------------------------------|

| 2             | Card Reader Control            |

| 1             | Card Reader Control Parts List |

| 1             | CR11 Module Utilization        |

| 1             | CR11 Module Parts List         |

| 1             | Device Control                 |

| 4             | Reader Control                 |

|               | No. of Sheets  2 1 1 1 1 4     |

#### 1.6 TERMINOLOGY

The PDP-11 Conventions Manual, DEC-1!-HR6B-D, contains a list of terminology and abbreviations used with the PDP-11 family of systems. A glossary of PDP-11 terms, as well as general computer and programming terms, is also included.

1-5

## CHAPTER 2 GENERAL DESCRIPTION

#### 2.1 INTRODUCTION

The CR11 Card Reader System is designed to operate on-line with the PDP-11 System and associated peripherals such as magnetic tape units, line printers, or communications terminals. The card reader is a self-contained table-top unit consisting of a motorized card deck, read electronics, local control logic, and an internal power supply. The controller, which interfaces the card reader to the Unibus  $^{\text{TM}}$ , consists of a single quad module mounted in 1/4 of a system unit (slots 1, 2, 3, or 4 in a DD11-A Peripheral Mounting Panel). Thus, four reader control interfaces can be mounted in the space of a single system unit. The interface is connected to the card reader by a single cable.

Various card reader models may be used in this system. This manual describes the Documation Model M200. Although other models are similar and are compatible with this system, they may differ in card reading rates, indicator panels, etc. The other card reader models are covered in Appendix A.

#### 2.2 SYSTEM OPERATION

A read instruction from the controller moves a card from the input hopper into the read station where all 80 columns are read on a column-by-column basis beginning with column 1. The card data may be read in one of two modes. In the normal mode, data is transferred directly from the rows (zones) of the card to corresponding bit positions in a data buffer for transfer to the bus as a 12-bit character. The bits in this output character correspond directly to zones in the card column.

The second reading mode is the compressed data mode which is compatible with the proposed expansion of the Hollerith code. In this mode, card zones 12 through 08 are transferred directly to the data buffer; however, zones 01 through 07 are encoded into a 3-bit octal representation before loading into the buffer. This encoding is possible because of the lack of double punches in zones 01 through 07 of both the present and proposed Hollerith codes. As a result of this encoding, the 12-bit data from the card column is compressed into an 8-bit character that is transferred as a low-order byte to the Unibus.

Regardless of the reading mode used, a punched hole or mark is interpreted as a binary 1 and the absence of a hole or mark is a binary 0.

#### 2.3 CARD READER

Most available card readers operate in a characteristic manner. The reader itself consists of an input hopper for loading a number of cards, a photoelectric read station for reading data from the card, an output hopper for

(M) Unibus is a trademark of Digital Equipment Corporation.

stacking the cards after reading, a motorized mechanism for moving the cards, and control logic for generating command and status signals.

Operation begins when the controller issues a read command. When the card reader receives this command, it picks the first card from the hopper and feeds it into the read station. As the data holes or marks pass through the read station, they are sensed by a photoelectric device. At the same time, the reader generates a series of index or clock marks. These marks are transmitted to the controller simultaneously with the data bits read from the holes in the card. Thus, the controller receives 12 bits of parallel data on the 12 data output lines of the card reader connector.

The card reader furnishes alarm signals to warn of any error condition present in the reader. It also provides signals for certain housekeeping functions such as hopper empty, stacker full, and unit busy.

Each reader has a control panel for manual operations of the reader and for indicating various error conditions. These controls and indicators may vary from reader to reader, depending on the type and model used.

Four program flags indicate the status of the card reader. These flags are monitored by the controller and are tied to the interrupt logic so that setting any one of these flags generates an interrupt request.

The ON-LINE flag is set whenever the ready line from the card reader goes true indicating that the card reader is ready to accept commands. This feature permits the program to perform other tasks while awaiting manual intervention to clear a card reader problem such as lack of cards in the input hopper. This flag notifies the controller when the card reader is ready to resume on-line operation under program control.

The COLUMN DONE flag requests a program interrupt when a column of information has been read and is ready to be transferred to the bus. The CARD DONE flag is set when the card leaves the read station. The controller should then immediately issue a new read command to keep the card reader operating at full rated speed. The ERROR flag indicates that an error condition is present in the card reader and an interrupt request is made so that the program can branch to an error-handling routine.

#### 2.4 CR11 CONTROLLER

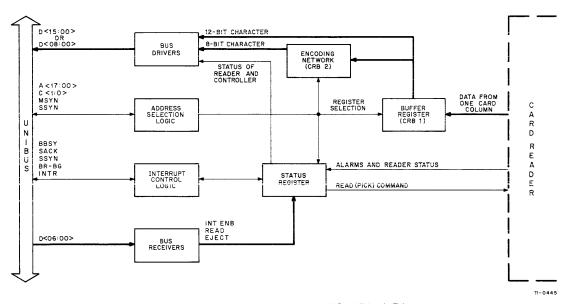

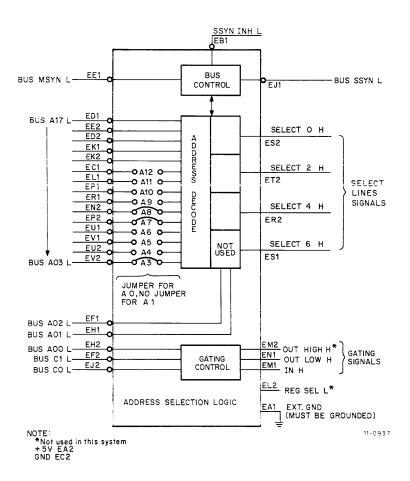

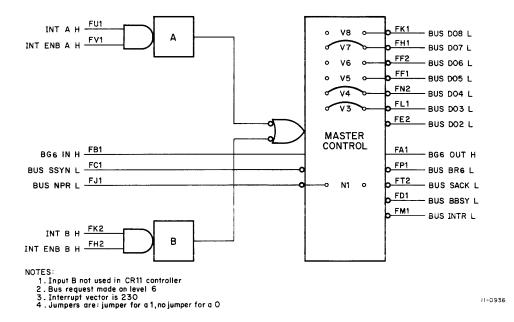

The CR11 Controller provides the command and monitoring functions for the card reader, in addition to handling data transfers from the card reader to the Unibus. When the processor addresses the bus, the controller decodes the address to determine if the card reader is the selected external device and, if selected, whether it is to perform an input or output operation. For the following discussion, refer to the simplified block diagram shown in Figure 2-1.

The address selection logic decodes the incoming address and responds to one of four possible sequential addresses. The register that is selected and the type of bus data transfer operation being performed determine whether a command is being issued, status is being monitored, or data is being read from a card in one of two reading modes.

If, for example, data is to be read, the status register is first addressed so that a read command can be sent to the card reader. The card reader moves a card into the read station, detects the data from the first card column, and loads it into the buffer register. Once the buffer is loaded, the controller sets a COLUMN READY flag so that an interrupt can be generated to transfer the data to the bus.

Figure 2-1 CR11 Controller – Simplified Block Diagram

At this point, either the buffer register (CRB1) or the encoding network (CRB2) would be addressed so that the data, in the form of either a 12-bit or 8-bit character, could be transferred through the bus drivers to the Unibus. When CRB1 is addressed, data from the buffer register is applied directly to the bus. When CRB2 is addressed, the 12 bits from the buffer are compressed into an 8-bit character before application to the bus.

When the status register is addressed, it can serve either as a command register to specify certain functions to be performed or as a status register to monitor operations within the controller and the card reader.

When the status register is used as a command register, it is loaded from the bus and can perform one or more of the following functions: interrupt enable, read, and eject. Interrupt enable is used to condition appropriate controller circuits so that an interrupt is initiated whenever an error occurs, the card reader goes on-line, or the reading of a card column or an entire card is completed. The read function is the only command sent to the card reader and is used to start operation of the reader. The eject function prevents the COLUMN READY flag from being set so that data from the buffer register is not transmitted to the bus. However, transfers between the card reader and the buffer register still take place. As far as the controller is concerned, the card has been ejected even though the reader continues normal operation.

When the status register is used to monitor system functions, it operates as a read-only register and its output is applied to the bus for monitoring by the program. Some of the bits in the register are set or cleared by alarm and status signals from the card reader itself; other bits are set or cleared by the controller.

Most card readers supply two status signals to the controller: READY, which indicates that the card reader is placed on-line; and BUSY or CARD IN READER (CIR), which indicates that the reader is currently processing a card. The reader normally signals an alarm simply by dropping the READY line whenever a reader error condition arises. However, in some readers, such as the Documation readers, additional alarm lines are included so that specific error signals can be sent to the controller. These alarm lines include: HOPPER CHECK (input hopper empty/output stacker full); ERROR (failure of light or dark check); and MOTION CHECK (card not picked or card hung up in card track).

Status and alarm signals are also generated internally by the controller. These include: ERROR, TIMING ERROR, COLUMN READY, and CARD DONE. These bits are described more fully in Chapter 4 of this manual.

### CHAPTER 3 OPERATION

#### 3.1 SCOPE

This chapter provides the information necessary for normal operation of the CR11 Card Reader System and is divided into three major parts: controls and indicators, card loading and unloading, and operating procedures. Additional procedures, such as calibration and mechanical adjustments, are beyond the scope of this manual and are covered in the appropriate card reader manual.

This chapter covers only operation of the Documation, Inc. card readers. Operating procedures for GDI card readers are described in Appendix A.

The description of the controls and indicators (Paragraph 3.2) is in tabular form and provides the user with the type and function of each operating switch and indicator on the card reader. Card handling procedures are given in Paragraph 3.3 and step-by-step operating procedures for both on-line and off-line operation are given in Paragraph 3.4.

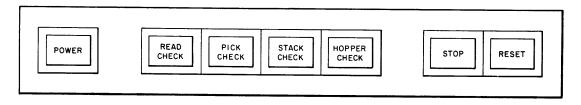

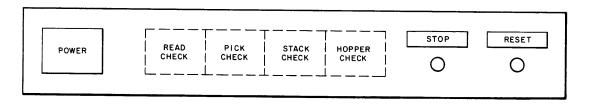

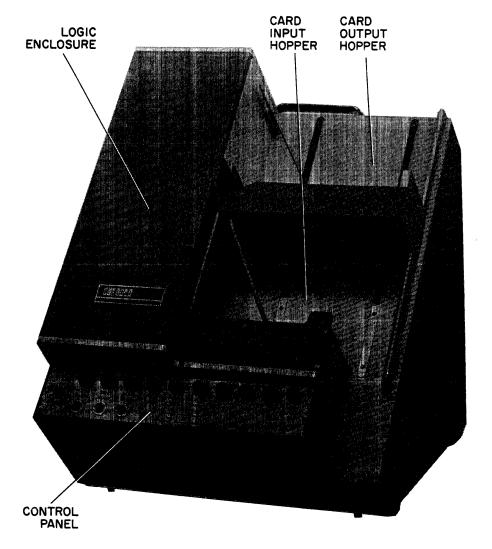

#### 3.2 CONTROLS AND INDICATORS

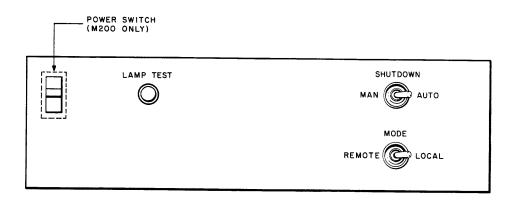

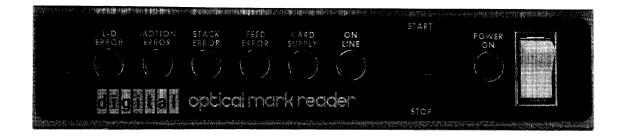

The controls and indicators used to operate the CR11 Card Reader System are shown in Figure 3-1 and listed in Tables 3-1 and 3-2. Although the front control panel is shown for both the M200 and M600 card reader models, only the M600 model is covered in the table. This particular model is described in order to provide coverage of the additional indicators. The M200 model is basically a similar version except the switches and associated indicators are mounted separately. The functions are identical with those described for the M600 model.

The items covered in each table are listed below:

| Table 3-1 | Front Control Panel (see Figure 3-1, a) | This control panel is located at the upper left-hand corner of the front of the reader. This panel contains the controls and indicators used for normal on-line/off-line operation of the card reader. |

|-----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3-2 | Rear Control Panel (see Figure 3-1, c)  | This panel is located at the upper right-hand corner of the back of the reader. This panel is used for initial set-up of the system and for maintenance purposes.                                      |

a. Front Control Panel (Model M600)

b. Front Control Panel (Model M200)

c. Rear Control Panel

11-0446

Figure 3-1 Card Reader Controls and Indicators

Table 3-1 Front Panel Controls and Indicators

| Control or Indicator   | Type                                                | Function                                                                                                                                                                                                  |  |  |  |  |

|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER switch           | alternate-action<br>pushbutton/indicator            | Controls application of all power to the card reader.                                                                                                                                                     |  |  |  |  |

|                        | switch                                              | When indicator is off, depressing switch applies power to reader and causes associated indicator to light.                                                                                                |  |  |  |  |

|                        |                                                     | When indicator is lit, depressing switch removes all power from reader and causes indicator to go out.                                                                                                    |  |  |  |  |

| READ CHECK indicator   | white light                                         | When lit, this light indicates that the card just read may be torn on the leading or trailing edges, or that the card may have punches in the 0 or 81st column positions.                                 |  |  |  |  |

|                        |                                                     | Because READ CHECK indicates an error condition, whenever this indicator is lit, it causes the card reader to stop operation and extinguishes the RESET indicator.                                        |  |  |  |  |

| PICK CHECK indicator   | white light                                         | When lit, this light indicates that the card reader failed to move a card into the read station after it received a READ COM-MAND from the controller.                                                    |  |  |  |  |

|                        |                                                     | Stops card reader operation and extinguishes RESET indicator.                                                                                                                                             |  |  |  |  |

| STACK CHECK indicator  | white light                                         | When lit, this light indicates that the previous card was not properly seated in the output stacker and therefore may be badly mutilated.                                                                 |  |  |  |  |

|                        |                                                     | Stops card reader operation and extinguishes RESET indicator.                                                                                                                                             |  |  |  |  |

| HOPPER CHECK indicator | white light                                         | When lit, this light indicates that either the input hopper is empty or that the output stacker is full.                                                                                                  |  |  |  |  |

|                        |                                                     | In either case, the operator must manually correct the condition before card reader operation can continue.                                                                                               |  |  |  |  |

| STOP switch            | momentary  pushbutton/indicator  switch (red light) | When depressed, immediately lights and drops the READY line, thereby extinguishing the RESET indicator. Card reader operation then stops as soon as the card currently in the read station has been read. |  |  |  |  |

|                        |                                                     | This switch has no effect on the system power; it only stops the current operation.                                                                                                                       |  |  |  |  |

Table 3-1 (Cont)

Front Panel Controls and Indicators

| Control or Indicator | Туре                                                      | Function                                                                                                                                                                                      |  |  |  |  |  |

|----------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RESET switch         | momentary<br>pushbutton/indicator<br>switch (green light) | When depressed and released, clears all error flip-flops and initializes card reader logic. Associated RESET indicator lights to indicate that the READY signal is applied to the controller. |  |  |  |  |  |

|                      |                                                           | The RESET indicator goes out whenever the STOP switch is depressed or whenever an error indicator lights (READ CHECK, PICK CHECK, STACK CHECK, or HOPPER CHECK).                              |  |  |  |  |  |

Table 3-2 Rear Panel Controls

| Control          | Туре              | Function                                                                                                                                                                                                   |

|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAMP TEST switch | pushbutton        | When depressed, illuminates all indicators on the front control panel to determine if any of the indicator lamps are faulty.                                                                               |

| SHUTDOWN switch  | 2-position toggle | Controls automatic operation of the input hopper blower.                                                                                                                                                   |

|                  |                   | MAN position — blower operates continuously whether or not cards are in the input hopper.                                                                                                                  |

|                  |                   | AUTO position — causes the blower to shut down automatically whenever the input hopper is emptied.  Blower automatically restarts when cards are loaded into the hopper and the RESET switch is depressed. |

|                  |                   | Blower activates approximately three seconds after RESET is depressed.                                                                                                                                     |

| MODE switch      | 2-position toggle | Permits selection of either on-line or off-line operation.                                                                                                                                                 |

|                  |                   | LOCAL position — removes the READ COMMAND input from the controller to allow the operator to run the reader off-line by using the RESET and STOP switches on the front control panel.                      |

|                  |                   | REMOTE position — enables the READ COMMAND input from the controller to allow normal on-line operation under program control once RESET is depressed.                                                      |

#### 3.3 CARD HANDLING PROCEDURES

The following paragraphs present the recommended procedures for loading the input hopper, unloading the output stacker, and correcting error conditions.

#### 3.3.1 Loading Cards

The following procedure is used when loading the input hopper with punched cards to be read:

| Step | Procedure                                                                                                                                                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Pull the hopper follower back with one hand and begin loading card decks into the hopper. Make certain that the first card to be read is placed at the front with the "9" edge down, column 1 to the left.                                                       |

| 2    | Continue placing cards into the input hopper until it is loosely filled (this is the approximate amount of cards listed as the capacity for a particular card reader model).                                                                                     |

|      | CAUTION  Do not pack the input hopper so full that the air from the blower cannot riffle the cards properly.  If the cards are packed too tightly, it impairs proper operation of the vacuum picker.                                                             |

| 3    | Cards may continue to be loaded while the reader is operating provided tension is maintained on the front portion of the deck as cards are added to the rear. Additional cards should not be loaded, however, until the hopper is approximately 1/2 to 1/3 full. |

|      | CAUTION                                                                                                                                                                                                                                                          |

|      | When maintaining tension on the card deck, use just enough pressure to maintain the riffle action to prevent card damage and jamming of the reader.                                                                                                              |

| 4    | Normally, all cards are moved through the reader into the stacker. However, if it is necessary to remove cards from the input hopper, simply pull back the follower and remove the card deck.                                                                    |

#### 3.3.2 Unloading Cards

To unload cards from the output stacker, pull the stacker follower back with one hand and remove the card deck from the stacker, being careful to maintain the order of the deck. The stacker may be unloaded while the cards are being read.

#### 3.3.3 Correcting Error Conditions

The four error alarm indicators on the front control panel of the card reader normally indicate a condition that can be corrected by operator intervention. These alarms, their causes, and the required operator intervention are given in Table 3-3.

#### 3.4 OPERATING PROCEDURES

The CR11 Card Reader System can be used in either a local or remote operating mode. The local (off-line) mode is controlled by switches on the front and rear panels of the card reader. The remote (on-line) mode is controlled by programmed commands from the PDP-11 System.

Table 3-3

Error Alarm Causes and Remedies

| Error Indicator | Possible Cause                                          | Corrective Action                                                                                                                                                        |  |  |  |  |  |

|-----------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| READ CHECK      | Card edges torn Punch in 0 or 81st column               | Remove faulty card and restart reader  If READ CHECK occurs for every card, it indicates a malfunction in the reader read logic                                          |  |  |  |  |  |

| PICK CHECK      | Damage to leading edge Torn webs Cards stapled together | Remove faulty card and restart reader  If there is no evidence of card damage, check for excessive warpage of card deck and/or a buildup of ink glaze on the picker face |  |  |  |  |  |

| STACK CHECK     | Jam in card track<br>Badly mutilated card               | Correct jam or remove mutilated card and restart reader                                                                                                                  |  |  |  |  |  |

| HOPPER CHECK    | Input hopper empty Output stacker full                  | Load input hopper Unload output stacker                                                                                                                                  |  |  |  |  |  |

The following paragraphs present procedures for both off-line and on-line operation of the card reader. Although procedures are given for setting up on-line operation, it is beyond the scope of this chapter to present any programming details. Programming information is covered in Chapter 4.

#### 3.4.1 Off-Line Operation

Off-line operation of the card reader is used primarily for setting up and checking reader operation prior to switching to on-line use; for correcting error conditions; and for maintenance tests. When placed off-line, the reader can be operated locally from the control panels. The following procedure is used to energize the reader and check off-line operation prior to switching to on-line operation.

| Step | Procedure                                                                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Make certain that the ac power cord is plugged in and that the circuit breaker on the rear base panel of the reader is in the ON position.                                                            |

| 2    | Set MODE switch to LOCAL position.                                                                                                                                                                    |

| 3    | Set SHUTDOWN switch to AUTO position.                                                                                                                                                                 |

| 4    | Depress POWER switch to energize reader. Note that POWER indicator lights but blower does not come on.                                                                                                |

| 5    | Depress LAMP TEST switch and observe that all front panel indicators are lit.                                                                                                                         |

| 6    | Load a card deck into the input hopper.                                                                                                                                                               |

| 7    | Depress RESET switch and observe that associated green indicator comes on. After approximately 3 seconds, cards should start being picked and moved through the read station into the output stacker. |

| 8    | When the input hopper is empty, observe that the HOPPER CHECK indicator lights, the green RESET indicator goes out, and the red STOP indicator lights.                                                |

| 9    | The card reader may now be operated locally or switched to on-line operation.                                                                                                                         |

#### 3.4.2 On-Line Operation

The following procedure is used to place the CR11 Card Reader System on-line. When placed on-line, the system is controlled by programmed commands from the PDP-11 System.

| Step | Procedure                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Make certain that the card reader is operational by performing the procedure given in Paragraph 3.4.1.                                                 |

| 2    | Make certain the output stacker is empty. Load the input hopper with the cards to be read.                                                             |

| 3    | Set the MODE switch to REMOTE.                                                                                                                         |

| 4    | Depress the RESET switch and observe that the associated green indicator lights. The system is now on-line.                                            |

| 5    | If the system goes off-line because of an error alarm, it can be placed back on-<br>line by correcting the error and then depressing the RESET switch. |

|      | Any time it is desired to go off-line, depress the STOP switch.                                                                                        |

### CHAPTER 4 PROGRAMMING INFORMATION

#### 4.1 SCOPE

This chapter presents general programming information for software control of the CR11 Card Reader System. Although a typical program example is included, it is beyond the scope of this manual to provide detailed programs. For more detailed information on programming in general, refer to the Paper Tape Software Programming Handbook, DEC-11-GGPB-D.

This chapter is divided into three major portions: device registers, interrupts, and program example.

#### 4.2 DEVICE REGISTERS

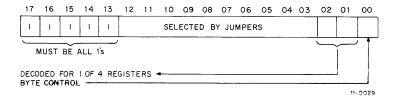

All software control of the CR11 Card Reader System is performed by two device registers within the controller. Although there are only two registers, three addresses have been assigned. The data buffer register, which holds one column of data from a card, can be addressed as a normal 12-bit register (compatible with standard Hollerith code) or it can be addressed so that the output passes through an encoding network to provide an 8-bit output (compressed Hollerith code).

The device registers and associated addresses are listed in Table 4-1. Note that these addresses can be changed by altering the jumpers on the address selection logic. However, any DEC programs or other software referring to these addresses must also be modified accordingly if the jumpers are changed.

Table 4-1 Standard Device Register Assignments

| Register             | Mnemonic | Address |

|----------------------|----------|---------|

| Status Register      | CRS      | 777160  |

| Data Buffer Register | CRB1     | 777162  |

| Data Buffer Register | CRB2     | 777164  |

- NOTES: 1. CRB1 is the actual register that holds one column of data from a card (Hollerith code).

- 2. CRB2 is the gated output of CRB1 such that the 12-bit buffer output is compressed into an 8-bit character (compressed Hollerith code).

- 3. The data buffer register is a read-only register. It cannot be loaded by the program.

Depending on the specific card reader used, bits 12 and 13 in the status register may or may not be used. If they are not used, corresponding jumpers on the M8290 module should be removed. A list of card readers supplying signals for these bits is given in Appendix B.

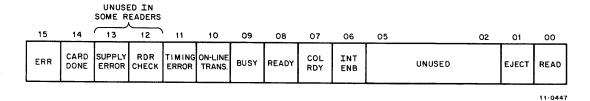

Figures 4-1 through 4-3 show the bit assignments for the three register addresses. "Unused" bits are always read as 0s. Loading "unused" or "read only" bits has no effect on the bit position. No data can be loaded into the high-order byte; therefore, use only word or low-byte addressing for writing into the status register.

The mnemonic INIT refers to the initialization signal issued by the processor. Initialization is caused by one of the following: issuing a programmed RESET instruction; depressing the START switch on the processor console; or occurrence of a power up or power down condition of the processor power supply.

Figure 4-1 Status Register Bit Assignments

Bit

15 ERROR

#### **Meaning and Operation**

Used to indicate an error condition is present. This bit is set (indicating an error) whenever an internal error flip-flop is set. This flip-flop is set when either one of the following conditions occurs:

- a. The card reader goes off-line from an on-line condition. During normal operation, this occurs when a card reader check or supply error is sensed.

- b. A timing error is present when the reader completes reading of the card (card done).

If an attempt is made to read a card while the error flip-flop is set and the error-causing conditions have not been corrected, the flip-flop remains set and subsequent read commands are ignored.

This bit is connected to the interrupt logic so that the program can branch to an error handling routine.

Read-only bit. Cleared by INIT.

#### NOTE

With the error removed, bits 15, 14, 11, and 10 are automatically cleared when the status register is loaded. However, if using a DATOB for loading, the low-order byte must be used because the high-order byte has no effect on the status register.

(continued on next page)

| Bit |                   | Meaning and Operation                                                                                                                                                                                                                                                                                            |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | CARD DONE         | When set, indicates that one card has passed through the read station and the next card may be requested from the input hopper. This bit is connected to the interrupt logic.                                                                                                                                    |

|     |                   | Read-only bit. Cleared by INIT or by loading the status register.                                                                                                                                                                                                                                                |

| 13  | CARD SUPPLY ERROR | When set, this bit indicates that either the input hopper is<br>empty or the output stacker is full. In either case, the con-<br>dition must be corrected before further operation can take<br>place.                                                                                                            |

|     |                   | Only certain card readers provide this error signal. If a card reader is used that <i>does not</i> supply this signal, then the jumper to this bit in the status register must be removed. This bit is then always read as 0. A list of card readers supplying this signal is given in Appendix B.               |

|     |                   | Read-only bit. Cleared by correcting error-causing condition.                                                                                                                                                                                                                                                    |

| 12  | CARD READER CHECK | When set, this bit indicates the presence of an abnormal condition in the card reader. Any one of the following four conditions sets this bit:                                                                                                                                                                   |

|     |                   | <ul> <li>Feed Error – Indicates that card reader feed<br/>mechanisms failed to deliver a card to the read<br/>station when demanded.</li> </ul>                                                                                                                                                                  |

|     |                   | <ul> <li>Motion Error – Indicates a card jam in the card<br/>reader.</li> </ul>                                                                                                                                                                                                                                  |

|     |                   | <ul> <li>Stack Fail – Indicates that card has not been delivered to the output stacker.</li> </ul>                                                                                                                                                                                                               |

|     |                   | <ul> <li>d. Dark/Light Error – Indicates that the read circuits do not agree with the usual dark and light areas of the card.</li> </ul>                                                                                                                                                                         |

|     |                   | This bit is similar to bit 13 in that only certain card readers provide this signal. If a reader is used that <i>does not</i> supply this signal, the associated status register jumper must be removed. This bit is then always read as 0. A list of card readers supplying this signal is given in Appendix B. |

|     |                   | Read-only bit. Cleared by correcting error-causing condition.                                                                                                                                                                                                                                                    |

| 11  | TIMING ERROR      | When set, this bit indicates that a new column of data has been loaded into the data buffer before a previously loaded column was read by the program. Clears COLUMN READY bit and causes ERROR bit to be indicated at CARD DONE time.                                                                           |

|     |                   | Once the timing error bit is set, the COLUMN READY bit is inhibited from setting and no data transfers can take place                                                                                                                                                                                            |

until TIMING ERROR is cleared.

| Bit       |                                 | Meaning and Operation                                                                                                                                                                                                 |

|-----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 (cont) | TIMING ERROR (cont)             | When the EJECT bit is set, it prevents TIMING ERROR from setting because a timing error is not pertinent if the card is ejected.                                                                                      |

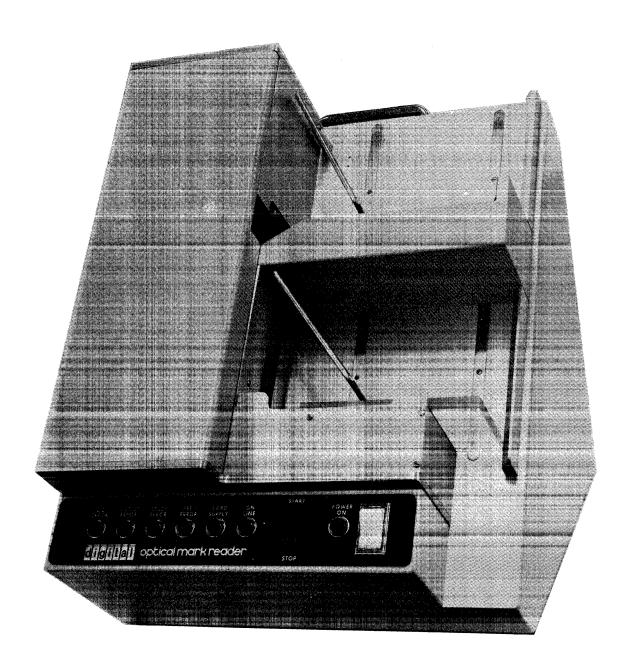

|           |                                 | Read-only bit. Cleared by INIT or by loading the status register.                                                                                                                                                     |