# KMV11 Programmable Communications Controller User Guide

Course Prepared by Educational Services of Digital Equipment Corporation

# Copyright © 1983 by Digital Equipment Corporation

# All Rights Reserved

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors herein.

# Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

| digital      |              |                |

|--------------|--------------|----------------|

| DEC          | MASSBUS      | UNIBUS         |

| DECmate      | PDP          | VAX            |

| DECsystem-10 | P/OS         | VMS            |

| DECSYSTEM-20 | Professional | VT             |

| DECUS        | Rainbow      | Work Processor |

| DECwriter    | RSTS         |                |

| DIROI.       | RSX          |                |

# CONTENTS

|                |                                                              | Page |

|----------------|--------------------------------------------------------------|------|

|                |                                                              |      |

| PREFACE        |                                                              |      |

| CII A DOTTED A |                                                              |      |

| CHAPTER 1      | INTRODUCTION                                                 |      |

|                |                                                              |      |

| 1.1            | SCOPE                                                        | 1-1  |

| 1.2            | KMV11 GENERAL DESCRIPTION                                    | 1-1  |

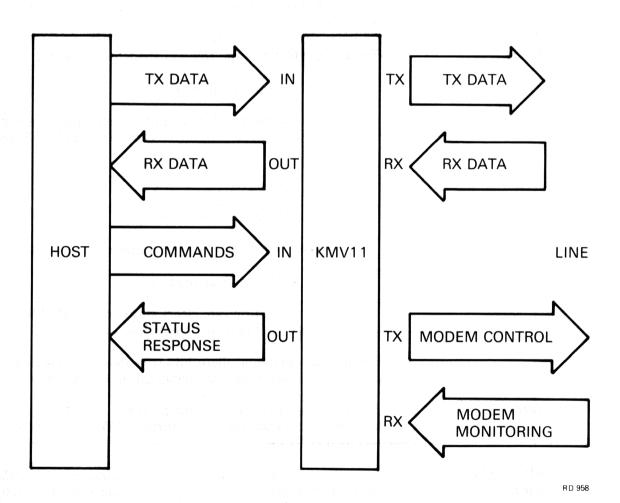

| 1.3            | SYSTEM OPERATION                                             | 1-2  |

| 1.4            | CSR LAYOUT                                                   | 1-2  |

| 1.5            | BSEL1 DEFINITIONS                                            | 1-3  |

| 1.6            | KMV11 – HOST INTERACTION                                     | 1-4  |

| CILL DEED A    | INSTALLATION                                                 |      |

| CHAPTER 2      | INSTALLATION                                                 |      |

| 2.1            |                                                              |      |

| 2.1            | SCOPE                                                        | 2-1  |

|                | UNPACKING AND CHECKOUT                                       | 2-1  |

| 2.3            | INSTALLATION PHASES                                          | 2-2  |

| 2.4            | PREINSTALLATION CONSIDERATIONS                               | 2-2  |

| 2.4.1          | Mounting Space                                               | 2-2  |

| 2.4.2          | Power Requirement                                            | 2-2  |

| 2.4.3          | Modem Cable Assembly Requirements                            | 2-3  |

| 2.5            | M7500 INSTALLATION                                           | 2-3  |

| 2.5.1          | Voltage Check                                                | 2-3  |

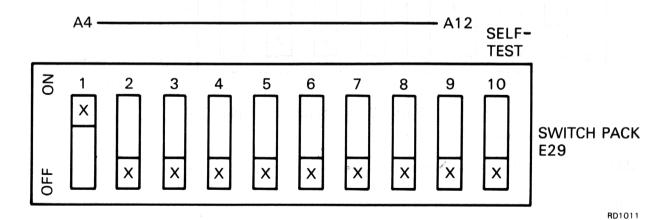

| 2.5.2          | Switch Settings                                              | 2-3  |

| 2.5.2.1        | Address Switches                                             | 2-3  |

| 2.5.2.2        | Vector Switches                                              | 2-4  |

| 2.5.3          | Jumper Configurations                                        | 2-5  |

| 2.5.4          | Standard Switch Setting and Jumper Configuration for KMV11-A | 2-6  |

| 2.5.5          | M7500 Insertion                                              | 2-7  |

| 2.6            | MODEM CABLE ASSEMBLY INSTALLATION                            | 2-8  |

| 2.6.1          | BC55H/BC55U/BC55P Considerations                             | 2-8  |

| 2.6.2          | BC55H, BC55U, and BC55P Installation on the H349 Panel       | 2-9  |

| 2.6.3          | BC55H, BC55U, and BC55P Installation Without H349 Panel      | 2-9  |

| 2.7            | KMV11 SYSTEM TESTING                                         | 2-9  |

| 2.7.1          | Functional Diagnostic Testing                                | 2-9  |

| 2.7.2          | DECX-11 System Exerciser                                     | 2-10 |

| 2.7.3          | Final Cable Connections                                      | 2-10 |

| 2.8            | KMV11 INSTALLATION CHECKOFF LIST                             | 2-10 |

| CHAPTER 3      | APPLICATION MODE                                             |      |

| 3.1            | CSR DESCRIPTION                                              | 3-1  |

| 3.2            | BSEL1 DEFINITIONS                                            | 3-1  |

| 3.3            | LOADING AND STARTING APPLICATION FIRMWARE                    | 3-2  |

# CHAPTER 4 APPLICATION FIRMWARE DEVELOPMENT

| 4.1       | KMV11 I/O PROGRAMMING                                 | 4-1  |

|-----------|-------------------------------------------------------|------|

| 4.1.1     | Front-End Processor Address Space                     | 4-1  |

| 4.1.2     | I/O Register Assignment                               | 4-1  |

| 4.1.3     | Front-End Processor Interrupt System                  | 4-3  |

| 4.2       | CSR AND DMA INTERFACE                                 | 4-5  |

| 4.2.1     | CSR and DMA Address Register Description              | 4-5  |

| 4.2.2     | CSR and DMA Programming                               | 4-6  |

| 4.2.2.1   | Programming Sequence for DMA OUT                      | 4-7  |

| 4.2.2.2   | Programming Sequence for DMA IN                       | 4-7  |

| 4.3       | LINE CONTROLLER INTERFACE                             | 4-7  |

| 4.3.1     | Line Controller Register Description                  | 4-13 |

| 4.3.1.1   | Channel A Receive Buffer                              | 4-13 |

| 4.3.1.2   | Channel A Transmit Buffer                             | 4-13 |

| 4.3.1.3   | Channel B Receive Buffer                              | 4-13 |

| 4.3.1.4   | Channel B Transmit Buffer                             | 4-13 |

| 4.3.1.5   | Channel A Command Registers                           | 4-13 |

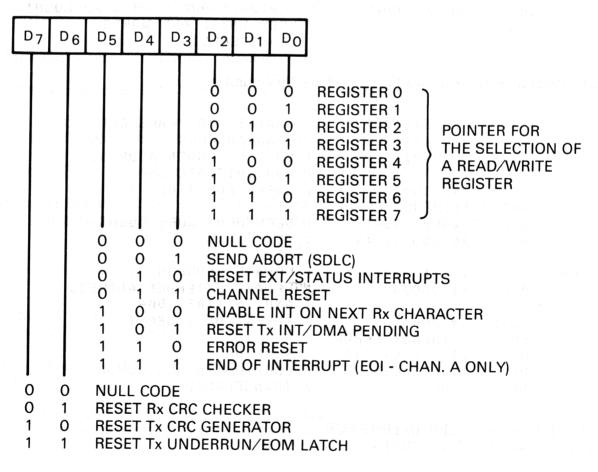

| 4.3.1.5.1 | Control Register 0                                    | 4-13 |

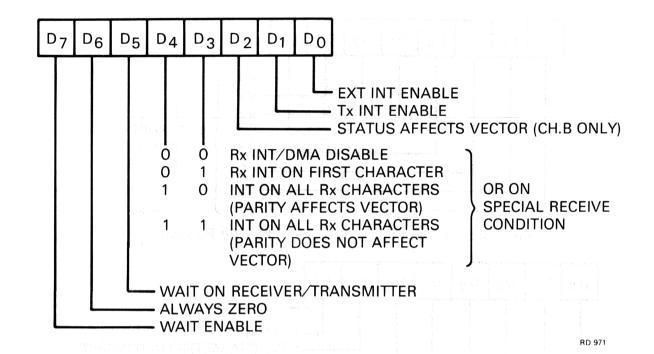

| 4.3.1.5.2 | Control Register 1                                    | 4-16 |

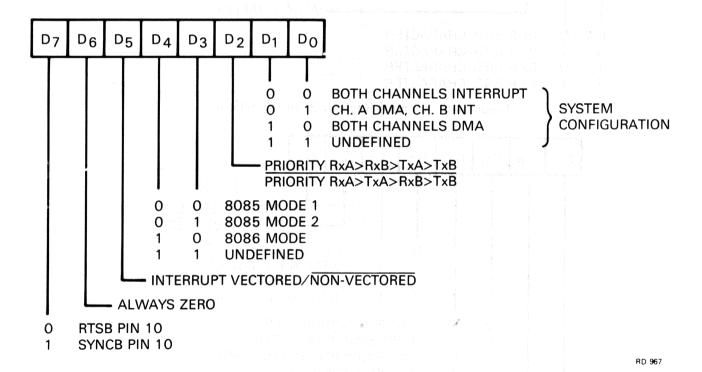

| 4.3.1.5.3 | Control Register 2 (Channel A)                        | 4-17 |

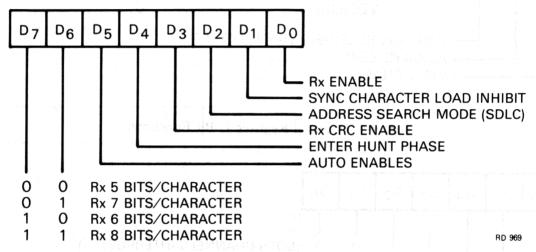

| 4.3.1.5.4 | Control Register 3                                    | 4-18 |

|           |                                                       | 4-20 |

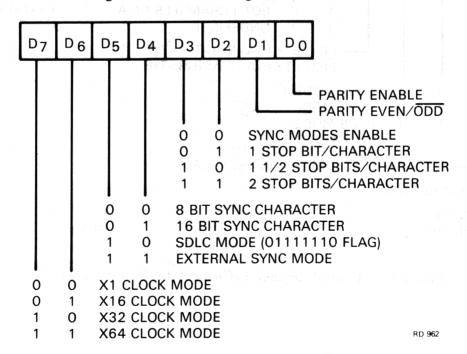

| 4.3.1.5.5 | Control Register 4                                    | 4-20 |

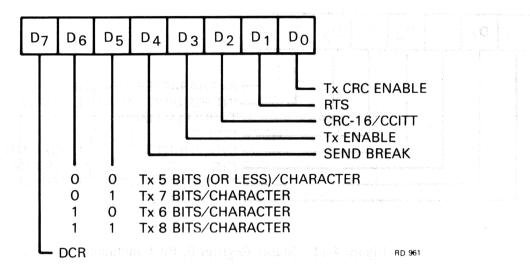

| 4.3.1.5.6 | Control Register 5                                    | 4-24 |

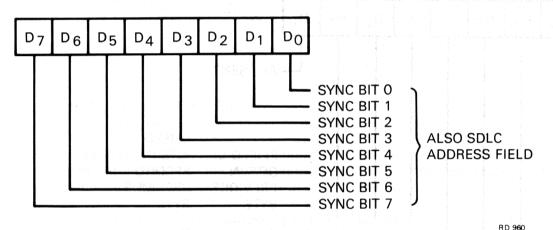

| 4.3.1.5.7 | Control Register 6                                    |      |

| 4.3.1.5.8 | Control Register 7                                    | 4-24 |

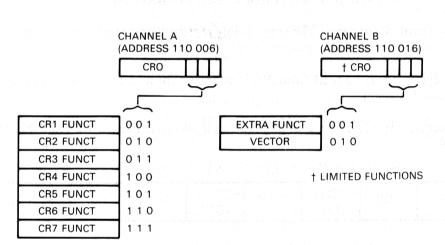

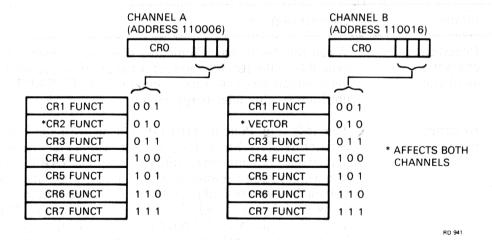

| 4.3.1.6   | Channel B Command Register                            | 4-24 |

| 4.3.1.6.1 | Control Register 0                                    | 4-25 |

| 4.3.1.6.2 | Control Register 1                                    | 4-25 |

| 4.3.1.6.3 | Control Register 2 (Channel B)                        | 4-26 |

| 4.3.1.7   | Channel A Status Register                             | 4-26 |

| 4.3.1.7.1 | Status Register 0                                     | 4-26 |

| 4.3.1.7.2 | Status Register 1                                     | 4-28 |

| 4.3.1.8   | Channel B Status Registers                            | 4-29 |

| 4.3.1.8.1 | Status Register 0 KMV11-A                             | 4-30 |

| 4.3.1.8.2 | Status Register 0 KMV11-B (dual line)                 | 4-30 |

| 4.3.1.8.3 | Status Register 1                                     | 4-30 |

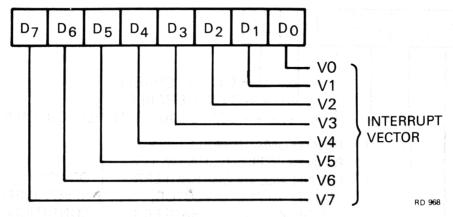

| 4.3.1.8.4 | Status Register 2                                     | 4-30 |

| 4.3.2     | Line Controller Interrupt System and Mode Selection   | 4-31 |

| 4.3.3     | HDLC Operation Example                                | 4-32 |

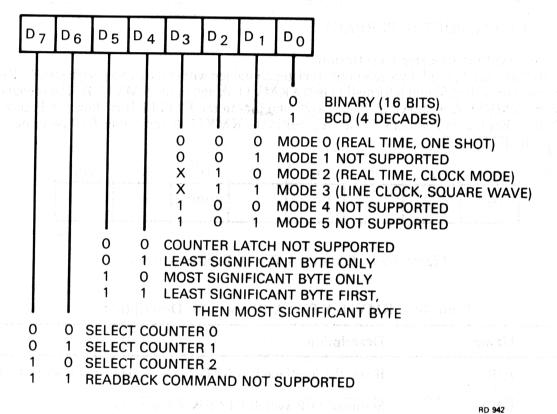

| 4.4       | LINE CLOCK – REAL-TIME CLOCK INTERFACE                | 4-34 |

| 4.4.1     | Line Clock – Real Time Clock Register Description     | 4-34 |

| 4.4.2     | Line Clock Programming                                | 4-35 |

| 4.4.3     | Real-Time Clock Programming                           | 4-36 |

| 4.4.4     | Line Clock – Real-Time Clock Parameter Setting        | 4-37 |

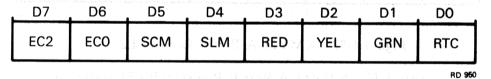

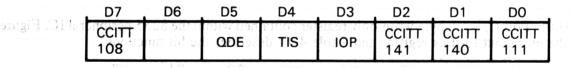

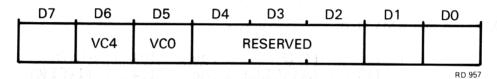

| 4.5       | PERIPHERAL PORT INTERFACE                             | 4-38 |

| 4.5.1     | Peripheral Port Register Description                  | 4-38 |

| 4.5.2     | Modem Monitoring and Control                          | 4-42 |

| 4.6       | HOST INTERRUPT AND Q-BUS CONTROL INTERFACE            | 4-46 |

| 4.6.1     | Host Interrupt and Q-Bus Control Register Description | 4-46 |

| 4.6.2     | Host Interrupt and Q-Bus Control Programming          | 4-47 |

|           | Troop Titterials with A was country tropismining      |      |

| CHAPTER 5                                                                                                                       | SERVICE                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.3.1<br>5.3.3.2<br>5.3.3.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.5 | SCOPE  MAINTENANCE PHILOSOPHY  MAINTENANCE TOOLS AND FEATURES  LED Indicators  Self-Test  Line Clock and Loopback Connectors  Line Clock  Real-Time Clock  Loopback Connectors/Tests  DIAGNOSTICS  VKMA Logic Diagnostic  VKMB Line Controller Diagnostic  VKMC Functional Diagnostic  XKMD DECX-11 Exerciser Module  PREVENTIVE MAINTENANCE  CORRECTIVE MAINTENANCE | 5-1<br>5-1<br>5-1<br>5-2<br>5-3<br>5-5<br>5-5<br>5-6<br>5-6<br>5-9<br>5-10<br>5-10<br>5-11<br>5-12<br>5-12 |

|                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |

|                                                                                                                                 | FIGURES                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

|                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |

| Figure No.                                                                                                                      | Tial and the second                                                                                                                                                                                                                                                       | sativité :                                                                                                 |

| rigure No.                                                                                                                      | Title                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                       |

| 1-1                                                                                                                             | CSR Definitions                                                                                                                                                                                                                                                                                                                                                      | 1-2                                                                                                        |

| 1-2                                                                                                                             | BSEL1 Definitions                                                                                                                                                                                                                                                                                                                                                    | 1-3                                                                                                        |

| 1-3                                                                                                                             | HOST - KMV11 Interaction                                                                                                                                                                                                                                                                                                                                             |                                                                                                            |

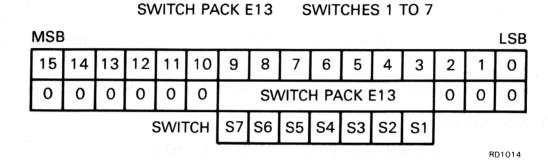

| 2-1                                                                                                                             | Address Switch Register Mapping                                                                                                                                                                                                                                                                                                                                      | 2-3                                                                                                        |

| 2-2                                                                                                                             | Address Switch Setting Example: 760020 <sub>8</sub>                                                                                                                                                                                                                                                                                                                  | 2-3                                                                                                        |

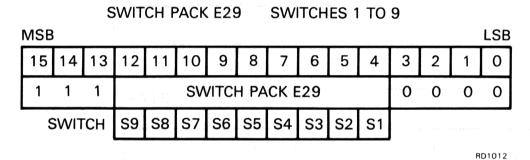

| 2-3                                                                                                                             | Vector Switch Register Mapping                                                                                                                                                                                                                                                                                                                                       | 2-4                                                                                                        |

| 2-4                                                                                                                             | Vector Switch Setting Example: 320                                                                                                                                                                                                                                                                                                                                   | 2-4                                                                                                        |

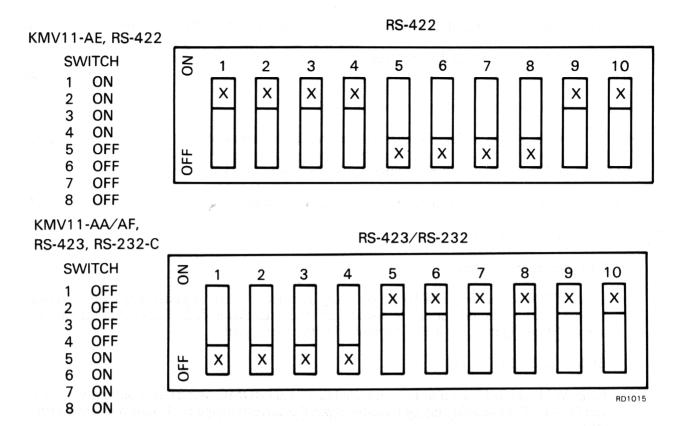

| 2-5                                                                                                                             | RS-422 Versus RS-423 (RS-232) on Switch Pack E85                                                                                                                                                                                                                                                                                                                     | 2-6                                                                                                        |

| 3-1                                                                                                                             | BSEL1 Bit Layout in Application Mode                                                                                                                                                                                                                                                                                                                                 | 3-1                                                                                                        |

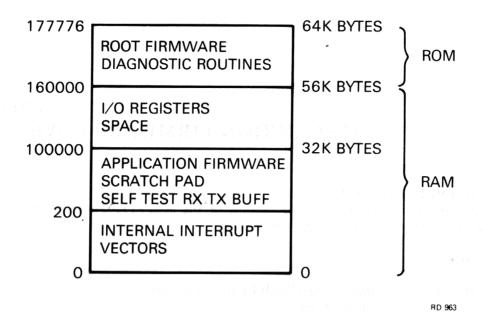

| 4-1                                                                                                                             | KMV11 Memory Map                                                                                                                                                                                                                                                                                                                                                     | 4-2                                                                                                        |

| 4-2<br>4-3                                                                                                                      | Control Register 0, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-8                                                                                                        |

| 4-3                                                                                                                             | Control Register 1, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-9<br>4-9                                                                                                 |

| 4-4                                                                                                                             | Control Register 2 (Channel B), Bit Functions                                                                                                                                                                                                                                                                                                                        | 4-10                                                                                                       |

| 4-6                                                                                                                             | Control Register 3, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-10                                                                                                       |

| 4-7                                                                                                                             | Control Register 4, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-10                                                                                                       |

| 4-8                                                                                                                             | Control Register 5, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-11                                                                                                       |

| 4-9                                                                                                                             | Control Register 6, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-11                                                                                                       |

| 4-10                                                                                                                            | Control Register 7, Bit Functions                                                                                                                                                                                                                                                                                                                                    | 4-11                                                                                                       |

| 4-11                                                                                                                            | Status Register 0, Bit Functions                                                                                                                                                                                                                                                                                                                                     | 4-12                                                                                                       |

| 4-12                                                                                                                            | Status Register 1, Bit Functions                                                                                                                                                                                                                                                                                                                                     | 4-12                                                                                                       |

| 4-13                                                                                                                            | Status Register 2, Bit Functions                                                                                                                                                                                                                                                                                                                                     | 4-13                                                                                                       |

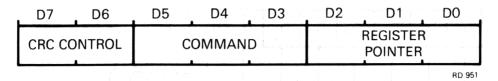

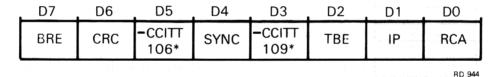

| 4-14                                                                                                                            | Control Register 0 Layout                                                                                                                                                                                                                                                                                                                                            | 4-14                                                                                                       |

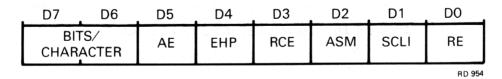

| 4-15                                                                                                                            | Control Register 1 Layout                                                                                                                                                                                                                                                                                                                                            | 4-16                                                                                                       |

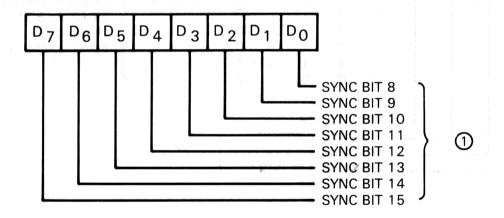

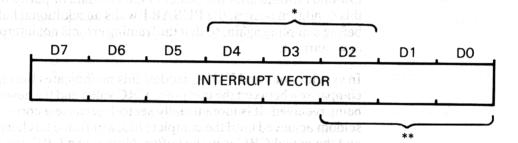

| 4-16                                                                                                                            | Control Register 2(A) Layout                                                                                                                                                                                                                                                                                                                                         | 4-17                                                                                                       |

| 4-17                                                                                                                            | Control Register 3 Layout                                                                                                                                                                                                                                                                                                                                            | 4-18                                                                                                       |

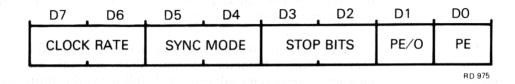

| 4-18                                                                                                                            | Control Register 4 Layout                                                                                                                                                                                                                                                                                                                                            | 4-20                                                                                                       |

| 4-19                                                                                                                                           | Control Register 5 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-21                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-20                                                                                                                                           | Control Register 6 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-24                                                                                                                                            |

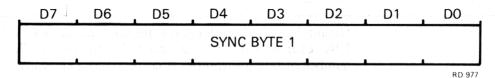

| 4-21                                                                                                                                           | Control Register 7 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-24                                                                                                                                            |

| 4-22                                                                                                                                           | Control Registers in the KMV11-A and KMV11-B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-25                                                                                                                                            |

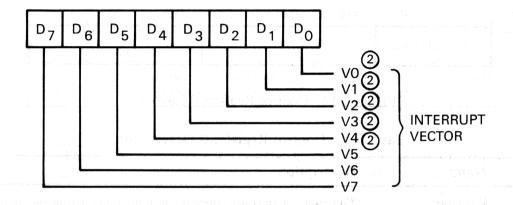

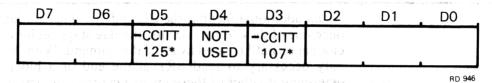

| 4-23                                                                                                                                           | Control Register 2(B) Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-26                                                                                                                                            |

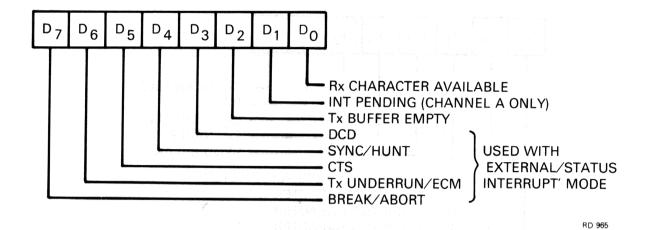

| 4-24                                                                                                                                           | Status Register 0(A) Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-26                                                                                                                                            |

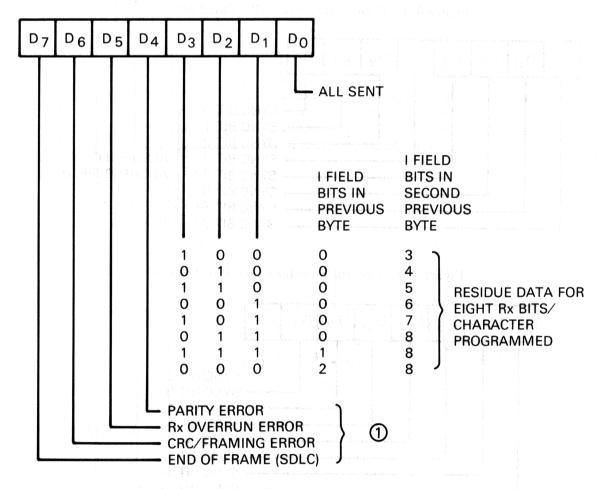

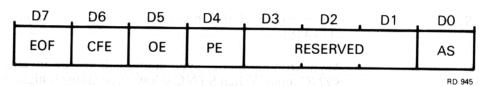

| 4-25                                                                                                                                           | Status Register 1 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-28                                                                                                                                            |

| 4-26                                                                                                                                           | Status Register 0(B) Layout in KMV11-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-30                                                                                                                                            |

| 4-27                                                                                                                                           | Status Register 2(B) Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-30                                                                                                                                            |

| 4-28                                                                                                                                           | Clock Control Register Bit Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-37                                                                                                                                            |

| 4-29                                                                                                                                           | KMV11-A Port A Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-38                                                                                                                                            |

| 4-30                                                                                                                                           | KMV11-B Port A Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-39                                                                                                                                            |

| 4-31                                                                                                                                           | Port C Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-39                                                                                                                                            |

| 4-32                                                                                                                                           | KMV11-A Port B Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-40                                                                                                                                            |

| 4-33                                                                                                                                           | KMV11-B Port B Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-41                                                                                                                                            |

| 4-34                                                                                                                                           | Q-Bus Control Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-46                                                                                                                                            |

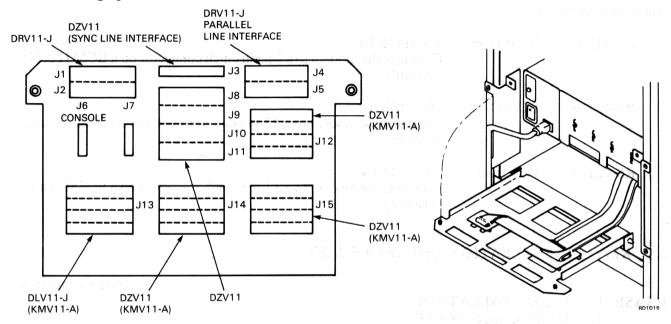

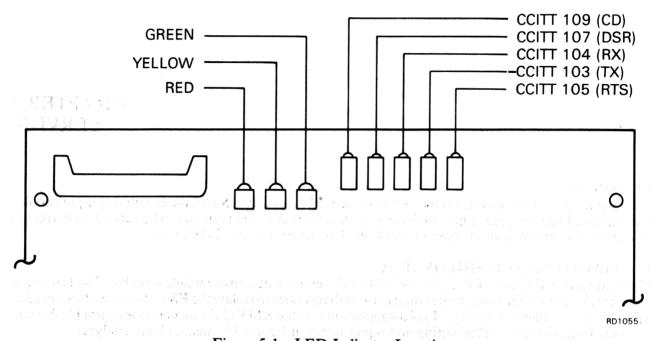

| 5-1                                                                                                                                            | LED Indicator Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-2                                                                                                                                             |

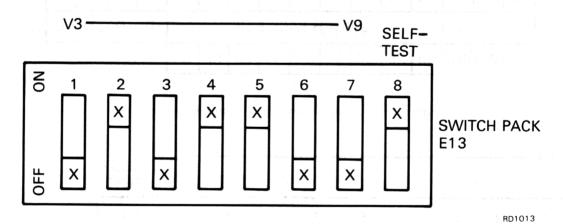

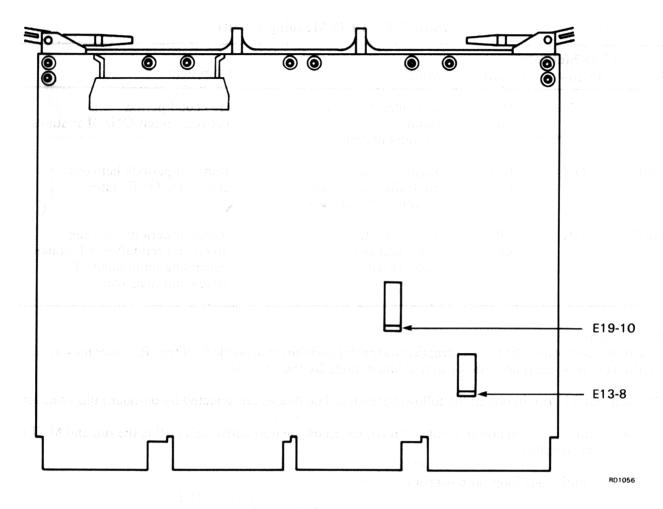

| 5-2                                                                                                                                            | Self-Test Switch Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-4                                                                                                                                             |

| 5-3                                                                                                                                            | KMV11 Loopback Connector H3255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-7                                                                                                                                             |

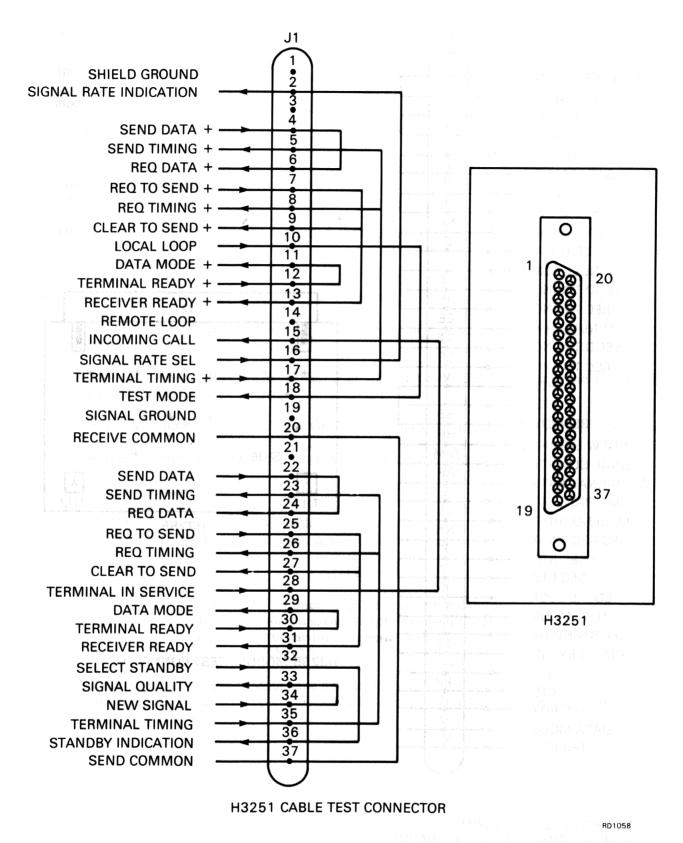

| 5-4                                                                                                                                            | KMV11 Loopback Connector H3251                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-8                                                                                                                                             |

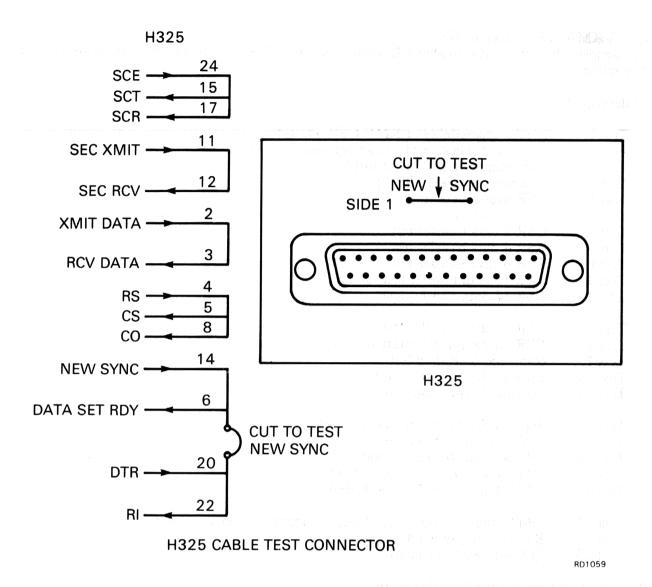

| 5-5                                                                                                                                            | KMV11 Turnaround Connector H325                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-9                                                                                                                                             |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|                                                                                                                                                | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

| Table No.                                                                                                                                      | na de la composição de la<br>La Title de la composição                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                            |

| Table No.                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ţ.:                                                                                                                                             |

| 2-1                                                                                                                                            | KMV11 Packing Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1                                                                                                                                             |

| 2-1 2<br>2-2                                                                                                                                   | KMV11 Packing Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1<br>2-6                                                                                                                                      |

| 2-1 <sup>2</sup><br>2-2 <sup>2</sup><br>2-3                                                                                                    | KMV11 Packing Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1<br>2-6<br>2-7                                                                                                                               |

| 2-1 2-2 2-3 2-4                                                                                                                                | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1<br>2-6<br>2-7<br>2-7                                                                                                                        |

| 2-1 2<br>2-2<br>2-3<br>2-4<br>2-5                                                                                                              | KMV11 Packing Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1<br>2-6<br>2-7<br>2-7<br>2-8                                                                                                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1                                                                                                         | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14                                                                                                         |

| 2-1 2<br>2-2<br>2-3<br>2-4<br>2-5                                                                                                              | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16                                                                                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1                                                                                                         | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18                                                                                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2                                                                                                  | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description  Control Register 1 Description  Control Register 2 Description  Control Register 3 Description                                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19                                                                                 |

| 2-1 2-2 2-3 2-4 2-5 4-1 4-2 4-3                                                                                                                | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description  Control Register 1 Description  Control Register 2 Description  Control Register 3 Description  Control Register 4 Description                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20                                                                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4                                                                                    | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description  Control Register 1 Description  Control Register 2 Description  Control Register 3 Description                                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22                                                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5                                                                             | KMV11 Packing Lists  KMV11-A Switch Register and Jumper Settings  KMV11-AA/AF Additional Switch and Jumper Settings  KMV11-AE Additional Switch and Jumper Settings  BC55H, BC55U, and BC55P Jumper Settings  Control Register 0 Description  Control Register 1 Description  Control Register 2 Description  Control Register 3 Description  Control Register 4 Description                                                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26                                                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6                                                                      | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description                                                                                                                                                                                                                                                                                                             | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28                                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7                                                               | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description                                                                                                                                                                                                                                                                               | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38                                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8                                                        | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description Status Register 1 Description                                                                                                                                                                                                                                                 | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38<br>4-39                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9                                                 | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description Status Register 1 Description Status Register 1 Description KMV11-A Port A Register Bit Description                                                                                                                                                                           | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38                                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10                                         | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description Status Register 1 Description Status Register 1 Description KMV11-A Port A Register Bit Description KMV11-B Port A Register Bit Description                                                                                                                                   | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38<br>4-39                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11                                 | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description Status Register 1 Description KMV11-A Port A Register Bit Description KMV11-B Port A Register Bit Description Port C Register Bit Description                                                                                                                                 | 2-1<br>2-6<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38<br>4-39<br>4-40<br>4-41                        |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12                         | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 5 Description Status Register 1 Description KMV11-A Port A Register Bit Description KMV11-B Port A Register Bit Description Port C Register Bit Description KMV11-A Port B Register Bit Description                                                                                         | 2-1<br>2-6<br>2-7<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38<br>4-39<br>4-39<br>4-40                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13                 | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 4 Description Status Register 5 Description Status Register 1 Description Status Register 1 Description KMV11-A Port A Register Bit Description KMV11-B Port A Register Bit Description KMV11-A Port B Register Bit Description KMV11-A Port B Register Bit Description KMV11-A Port B Register Bit Description           | 2-1<br>2-6<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-38<br>4-39<br>4-40<br>4-41                        |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14         | KMV11-A Switch Register and Jumper Settings KMV11-AA/AF Additional Switch and Jumper Settings KMV11-AE Additional Switch and Jumper Settings BC55H, BC55U, and BC55P Jumper Settings Control Register 0 Description Control Register 1 Description Control Register 2 Description Control Register 3 Description Control Register 4 Description Control Register 5 Description Status Register 0 Description Status Register 1 Description KMV11-A Port A Register Bit Description KMV11-B Port A Register Bit Description KMV11-B Port B Register Bit Description KMV11-B Port B Register Bit Description List of Supported Modem Signals Q-Bus Register Function Description LED Meaning | 2-1<br>2-6<br>2-7<br>2-8<br>4-14<br>4-16<br>4-18<br>4-19<br>4-20<br>4-22<br>4-26<br>4-28<br>4-39<br>4-39<br>4-40<br>4-41<br>4-43<br>4-46<br>5-2 |