# KMS11-P Synchronous Communication Processor Technical Manual

Prepared by Educational Services of Digital Equipment Corporation Copyright © 1984 by Digital Equipment Corporation

All Rights Reserved

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility

for any errors herein.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

# digital

DEC DECmate DECsystem-10 DECSYSTEM-20 DECUS DECwriter DIBOL MASSBUSUPDPVP/OSVProfessionalVWork ProcessorRaRSTSRSX

UNIBUS VAX VMS VT Rainbow

Dataphone<sup> $\mathbb{M}$ </sup> is a trademark of the AT&T Company Berg<sup> $\mathbb{M}$ </sup> is a trademark of Berg Inc.

# CONTENTS

## CHAPTER 1 INTRODUCTION

| 1.1       | SCOPE                                       | 1-1  |

|-----------|---------------------------------------------|------|

| 1.2       | GENERAL DESCRIPTION                         | 1-1  |

| 1.3       | KMS11-P SYSTEM OPERATION                    |      |

| .4        | GENERAL SPECIFICATIONS                      |      |

| .4.1      | Power Requirements                          |      |

| 1.4.2     | Environmental Requirements                  |      |

| 1.5       | EIA STANDARDS OVERVIEW (RS-449 vs RS-232-C) |      |

|           |                                             |      |

| CHAPTER 2 | INSTALLATION                                |      |

|           |                                             |      |

| 2.1       | SCOPE                                       | 2-1  |

| 2.2       | UNPACKING AND EXAMINATION                   |      |

| 2.3       | INSTALLATION CONSIDERATIONS                 | 2-1  |

| 2.4       | PREINSTALLATION CONSIDERATIONS              | 2-1  |

| 2.4.1     | System And Device Positioning               | 2-2  |

| 2.4.1.1   | System Positioning                          | 2-2  |

| 2.4.1.2   | Device Positioning                          | 2-2  |

| 2.4.2     | System Requirements                         | 2-2  |

| 2.5       | MICROPROCESSOR INSTALLATION                 | 2-3  |

| 2.5.1     | Backplane Considerations                    | 2-3  |

| 2.5.2     | M8206 Considerations                        | 2-4  |

| 2.5.3     | M8206 Insertion                             | 2-6  |

| 2.6       | LINE UNIT INSTALLATION                      | 2-7  |

| 2.6.1     | M8203 Considerations                        | 2-13 |

| 2.6.2     | M8203 Insertion                             | 2-14 |

| 2.7       | KMS11-P SYSTEM TESTING                      | 2-16 |

| 2.7.1     | Functional Diagnostic Testing               |      |

| 2.7.2     | DECX/11 System Exerciser (PDP-11)           |      |

| 2.7.3     | Final Cable Connections                     |      |

| 2.8       | KMS11-P INSTALLATION CHECK-OFF LIST         | 2-19 |

|           |                                             |      |

## CHAPTER 3 PROGRAMMING

| 3.1     | INTRODUCTION                               | 3-1  |

|---------|--------------------------------------------|------|

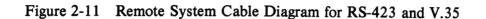

| 3.2     | LOGICAL ORGANIZATION OF REGISTERS          | 3-1  |

| 3.3     |                                            | 3-1  |

| ÷ · · - | KMC11-B (M8206) REGISTERS                  |      |

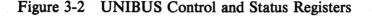

| 3.3.1   | UNIBUS Control and Status Registers        | 3-1  |

| 3.3.2   | OBUS*/IBUS* CSR Registers                  | 3-4  |

| 3.3.2.1 | NPR Control Register                       | 3-6  |

| 3.3.2.2 | Micro-P Miscellaneous Register             | 3-6  |

| 3.3.2.3 | Program Counter Register                   | 3-7  |

| 3.3.2.4 | Memory Address Register                    | 3-7  |

| 3.3.3   | OBUS/IBUS CSR Registers                    | 3-8  |

| 3.3.3.1 | The Microprocessor OBUS/IBUS CSR Registers | 3-8  |

| 3.3.4   | Line Unit CSR Registers                    | 3-8  |

| 3.3.4.1 | IBUS Register 10                           | 3-9  |

| 3.3.4.2 | OBUS Register 10                           | 3-10 |

| 3.3.4.3    | IBUS Register 11                                   | 3-11 |

|------------|----------------------------------------------------|------|

| 3.3.4.4    | OPLIS Desisten 11                                  |      |

| 3.3.4.5    | OBUS Register 11                                   | 3-12 |

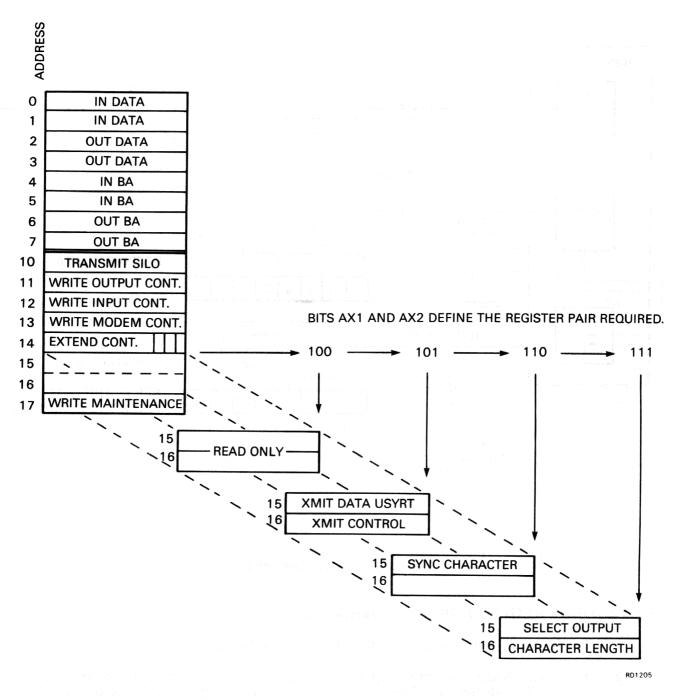

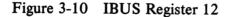

|            | IBUS Register 12                                   | 3-13 |

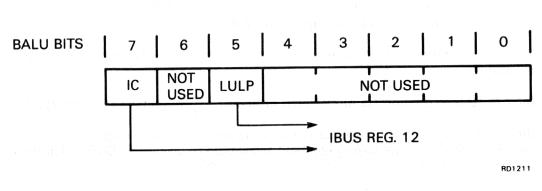

| 3.3.4.6    | OBUS Register 12                                   | 3-14 |

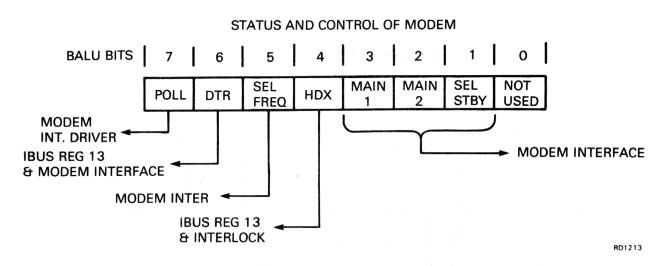

| 3.3.4.7    | IBUS Register 13                                   | 3-14 |

| 3.3.4.8    | OBUS Register 13                                   | 3-14 |

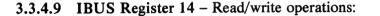

| 3.3.4.9    | IBUS Devictor 14                                   |      |

| 3.3.4.10   | IBUS Register 14                                   | 3-16 |

|            | OBUS Register 14                                   | 3-17 |

| 3.3.4.11   | IBUS Register 15                                   | 3-18 |

| 3.3.4.12   | OBUS Register 15                                   | 3-18 |

| 3.3.4.13   | IBUS Register 16                                   | 3-19 |

| 3.3.4.14   | OBUS Perister 16                                   |      |

| 3.3.4.15   | OBUS Register 16                                   | 3-19 |

|            | IBUS Register 17                                   | 3-20 |

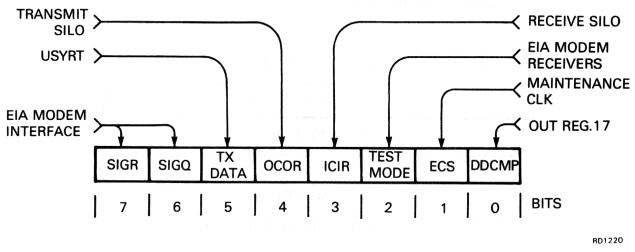

| 3.3.4.16   | OBUS Register 17                                   | 3-21 |

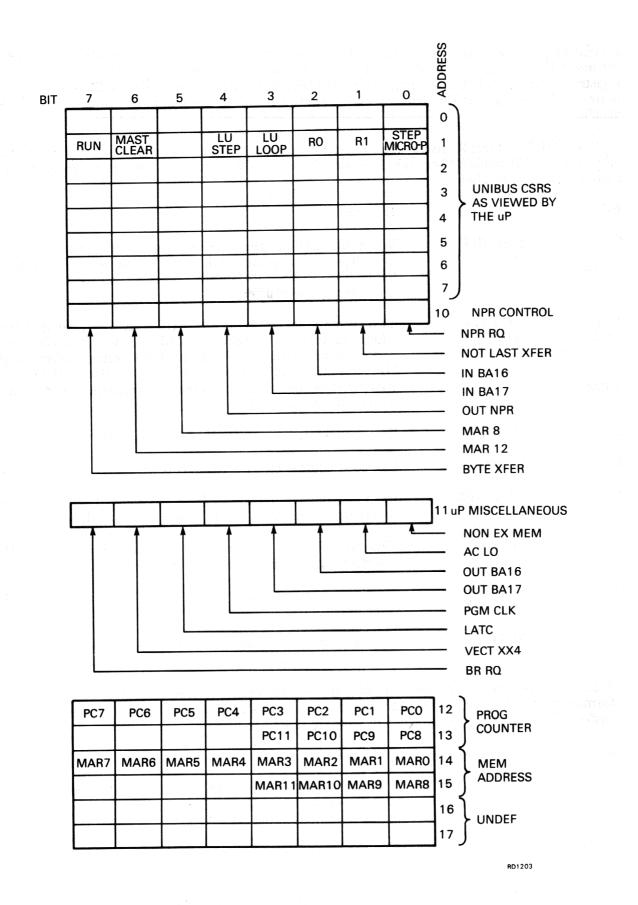

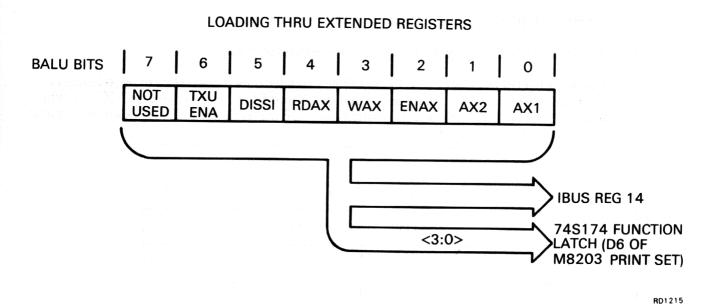

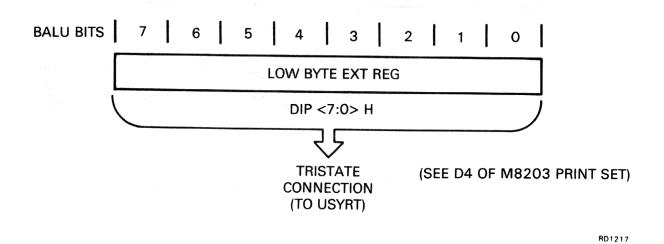

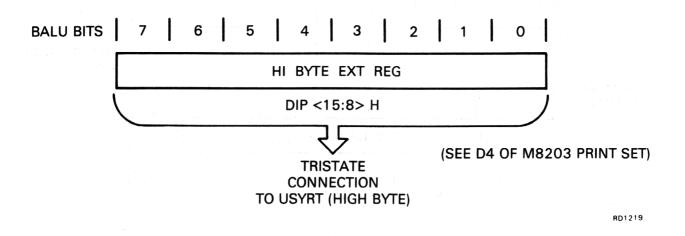

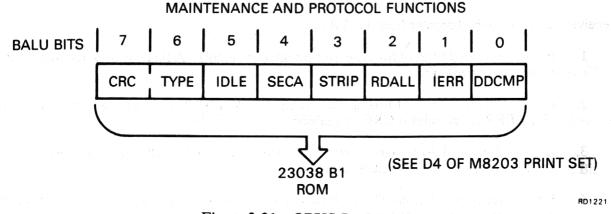

| 3.3.5      | Extended Registers/Indirect Addressing             | 3-22 |

| 3.3.5.1    | AX0-15 Register                                    | 3-22 |

| 3.3.5.2    | AX0-16 Register                                    |      |

| 3.3.5.3    |                                                    | 3-23 |

|            | AX1-15 Register                                    | 3-23 |

| 3.3.5.4    | AX1-16 Register                                    | 3-23 |

| 3.3.5.5    | AX2-15 Register                                    | 3-24 |

| 3.3.5.6    | AX2-16 Register                                    | 3-24 |

| 3.3.5.7    | AX3-15 Register                                    |      |

| 3.3.5.8    | AV2 16 Desister                                    | 3-25 |

| 5.5.5.0    | AX3-16 Register                                    | 3-26 |

| CHAPTER 4  | SERVICE                                            |      |

| 4.1        | SCOPE                                              | 4.1  |

| 4.2        |                                                    | 4-1  |

| 4.3        | MAINTENANCE PHILOSOPHY                             | 4-1  |

|            | MAINTENANCE FUNCTIONS/MAINTENANCE MODES            | 4-1  |

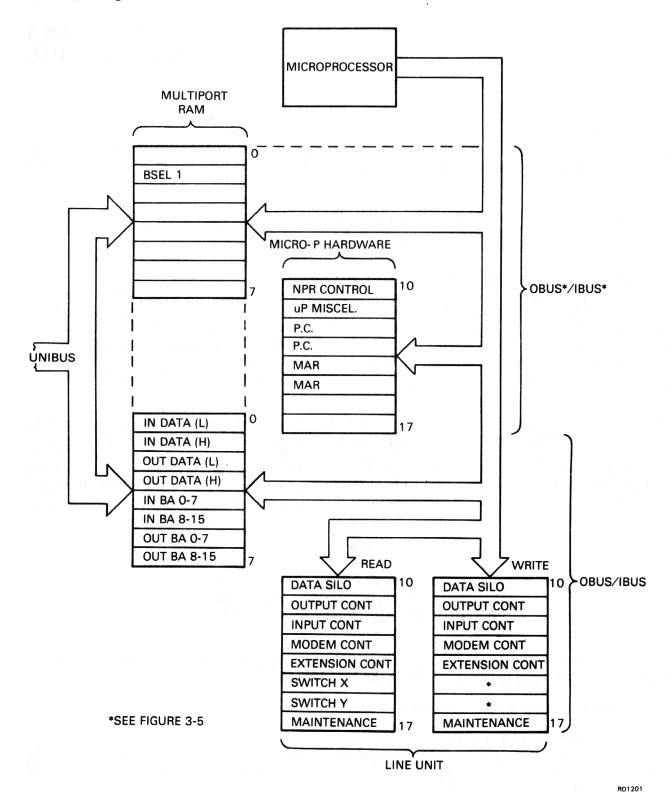

| 4.3.1      | Maintenance Register (BSEL 1)                      | 4-1  |

| 4.3.2      | Maintenance Modes                                  | 4-3  |

| 4.3.2.1    | Maintenance Mode                                   | 4-3  |

| 4.3.2.2    | Single Step Internal Maintenance Mode              |      |

| 4.3.2.4    | Sustem Test Internal Maintenance Made              | 4-3  |

| 4.3.2.5    | System Test Internal Maintenance Mode              | 4-3  |

|            | External Maintenance Mode                          | 4-3  |

| 4.3.3      | Maintenance (LED) Indicators                       | 4-4  |

| 4.4        | PREVENTIVE MAINTENANCE (PM)                        | 4-5  |

| 4.5        | CORRECTIVE MAINTENANCE ON A PDP-11 PROCESSOR       | 4-5  |

| 4.5.1      | CZKMB/CZKMC                                        |      |

| 4.5.2      | CZDMR/CZDMS                                        | 4-5  |

| 4.5.3      |                                                    | 4-8  |

| 4.5.4      | CZKMR                                              | 4-10 |

|            | DECX/11 KMC11-B Module                             | 4-11 |

| 4.5.5      | Examination of KMS11-P Internal Components         | 4-11 |

| 4.6        | CORRECTIVE MAINTENANCE ON A VAX-11                 | 4-13 |

| 4.6.1      | EVDHA REV. Microprocessor Repair Level Diagnostics |      |

| 4.6.2      | FSDHR REV. Microprocessor Empliment                | 4-13 |

| 4.6.3      | ESDHB REV. Microprocessor Functional Tests         | 4-14 |

|            | EVDMA REV. Line Unit Repair Level Diagnostics      | 4-14 |

| 4.6.4      | EVDIG REV. Line Unit Functional Tests              | 4-16 |

| APPENDIX A | FLOATING DEVICE ADDRESSES AND VECTORS              |      |

|            | 1. · · · · · · · · · · · · · · · · · · ·           |      |

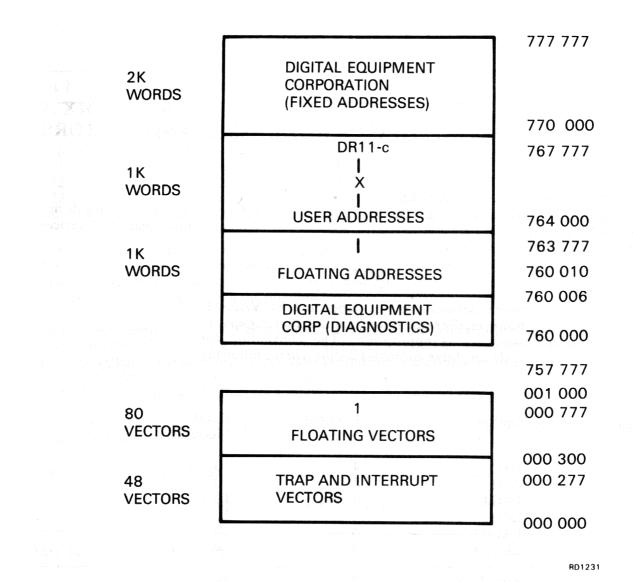

| A.1 | FLOATING DEVICE ADDRESSES | Δ_1        |

|-----|---------------------------|------------|

| A.2 | FLOATING VECTOR ADDRESSES | A-1<br>A-2 |

|     |                           | 11-4       |

| A.3<br>A.3.1 | EXAMPLES OF DEVICE AND VECTOR<br>ADDRESS ASSIGNMENT<br>Example 1 | A-4<br>A-4 |

|--------------|------------------------------------------------------------------|------------|

| A.3.2        | Example 2                                                        | A-5        |

| APPENDIX B   | PDP-11 DIAGNOSTIC SUPERVISOR SUMMARY                             |            |

| B.1          | INTRODUCTION                                                     | B-1        |

| B.2          | VERSIONS OF THE DIAGNOSTIC SUPERVISOR                            | <b>B-1</b> |

| <b>B.3</b>   | LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC                      | <b>B-1</b> |

| <b>B.3.1</b> | Five Steps to Run A Supervisor Diagnostic                        | <b>B-2</b> |

| <b>B.4</b>   | SUPERVISOR COMMANDS                                              | <b>B-3</b> |

| <b>B.4.1</b> | Command Switches                                                 | B-4        |

| B.4.2        | Control/Escape Characters Supported                              | B-5        |

| B.5          | SETUP UTILITY                                                    | B-5        |

| APPENDIX C   | DRIVER INTERFACE FOR EVDIG DIAGNOSTIC                            |            |

| C.1          | GENERAL                                                          | C-1        |

| C.2          | FUNCTIONS                                                        | C-1        |

| APPENDIX D   | COMMAND AND RESPONSE FORMAT FOR CZKMR DIAGNO                     | STIC       |

| APPENDIX E   | GLOSSARY                                                         |            |

| APPENDIX F   | CABINET KITS                                                     |            |

| F.1          | OVERVIEW                                                         | F-1        |

| F.2          | KIT DESCRIPTIONS                                                 | F-1        |

| F.3          | INSTALLATION                                                     | F-8        |

| F.3.1        | Cabinets with an I/O Bulkhead                                    | F-8        |

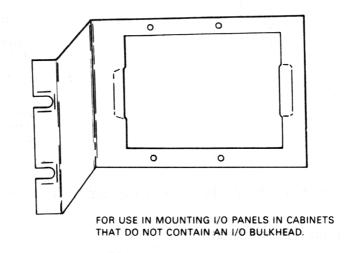

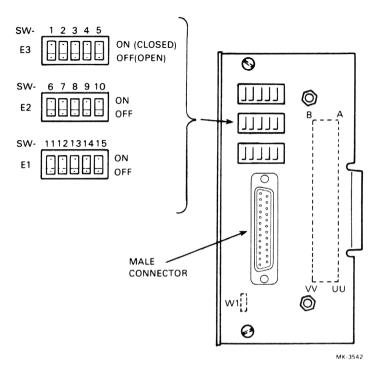

| F.3.2        | Cabinets without an I/O Bulkhead                                 | F-11       |

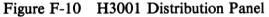

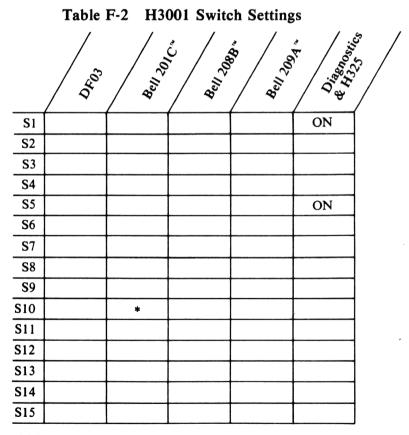

| F.3.3        | DIP Switch settings                                              | F-12       |

|              | FIGURES                                                          |            |

|              | FIGURES                                                          |            |

|              |                                                                  | R          |

| Figure No.   | Title                                                            | Page       |

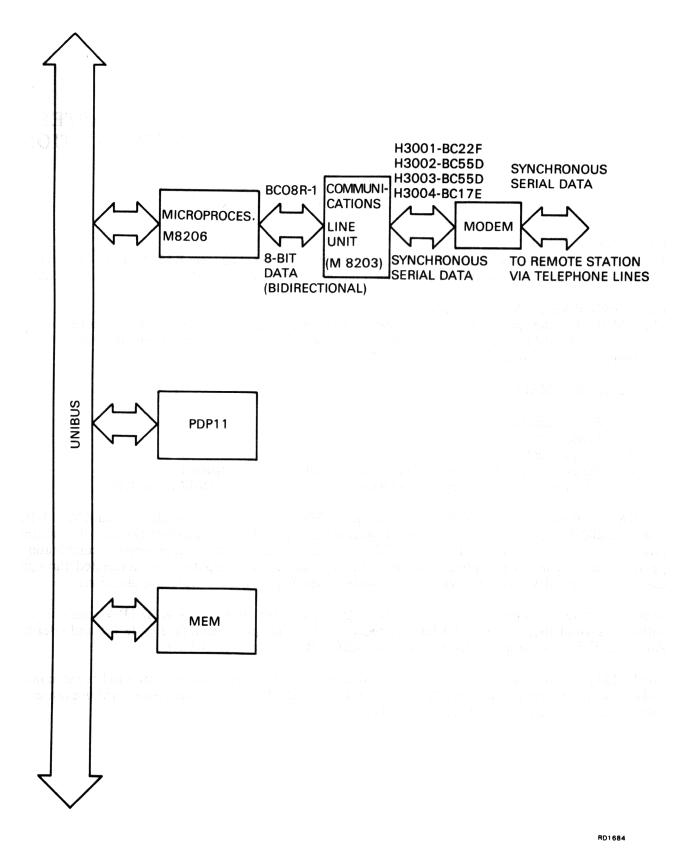

| 1-1          | Typical Applications                                             | 1-2        |

| 2-1          | M8206 (KMC11-B) Switch and Jumper Locations                      | 2-4        |

| 2-2          | M8206 (KMC11-B)) Address Selection                               | 2-4        |

| 2-3          | M8206 (KMC11-B) Device Address Switch Pack Layout                | 2-5        |

| 2-4          | M8206 (KMC11-B) Vector Address Selection                         | 2-5        |

| 2-5          | M8206 (KMC11-B) Vector Address Switch Pack Layout                | 2-6        |

| 2-6          | M8203 Line Unit Switch and Jumper Locations                      | 2-8        |

| 2-7          | Microprocessor/Line Unit Installation                            | 2-14       |

| 2-8          | H3254 Module Test Connector                                      | 2-16       |

| 2-9          | H3255 Module Test Connector                                      | 2-16       |

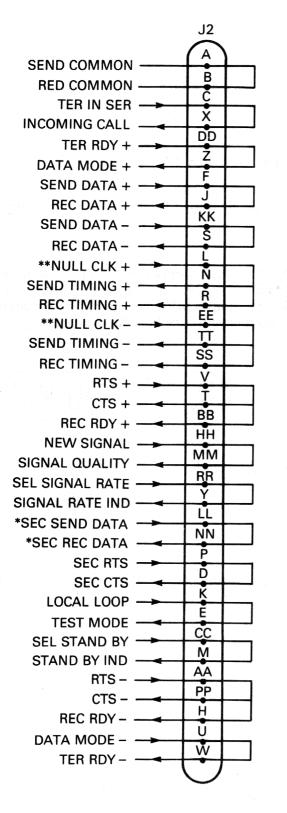

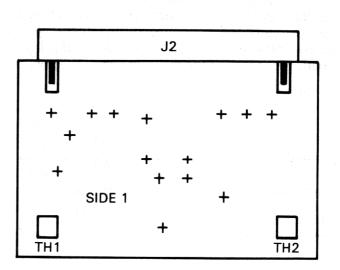

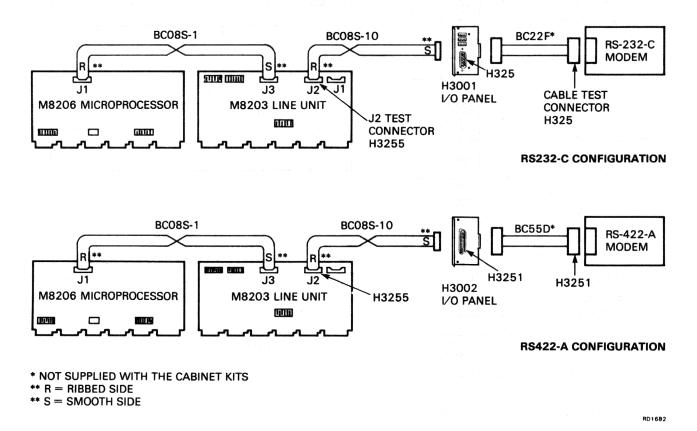

| 2-10         | Remote System Cable Diagram for RS-232 and RS-422                | 2-17       |

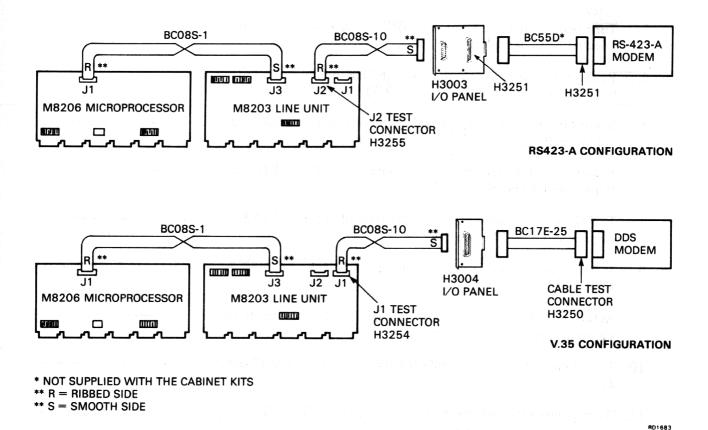

| 2-11         | Remote System Cable Diagram for RS-423 and V.35                  | 2-18       |

| 3-1          | Logical Organization of Control and Status Registers             | 3-2        |

| 3-2          | UNIBUS Control and Status Registers                              | 3-3        |

| 3-3  | OBUS*/IBUS* CSRs                                          | 3-5                |

|------|-----------------------------------------------------------|--------------------|

| 3-4  | OBUS/IBUS CSRs                                            | 3-7                |

| 3-5  | Schematic of OBUS CSRs                                    | 3-9                |

| 3-6  | IBUS Register 10                                          | 3-10               |

| 3-7  | OBUS Register 10                                          | 3-11               |

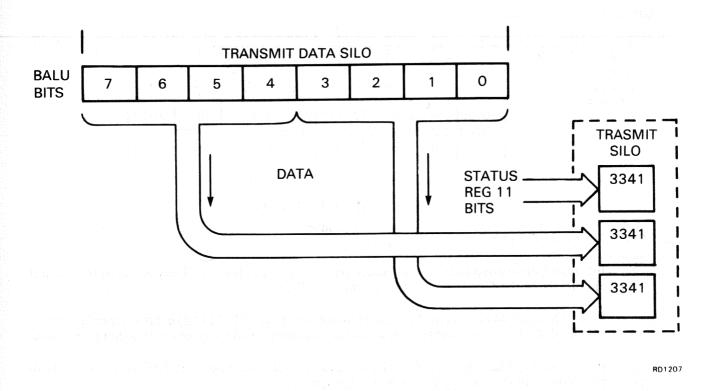

| 3-8  | IBUS Register 11                                          | 3-12               |

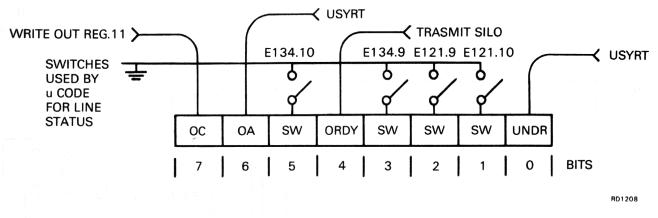

| 3-9  | OBUS Register 11                                          | 3-12               |

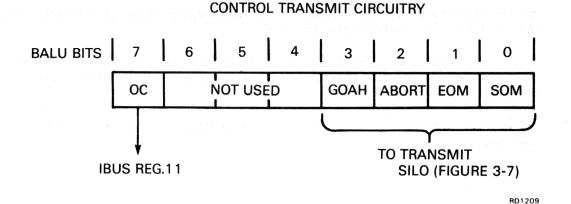

| 3-10 | IBUS Register 12                                          | 3-13               |

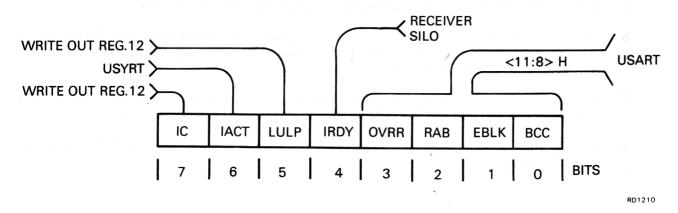

| 3-11 | OBUS Register 12                                          | 3-13               |

| 3-12 | IBUS Register 13                                          | 3-14               |

| 3-13 | OBUS Register 13                                          | 3-16               |

| 3-14 | IBUS Register 14                                          | 3-17               |

| 3-15 | OBUS Register 14                                          | 3-17               |

| 3-16 | IBUS Register 15                                          | 3-17               |

| 3-17 | OBUS Register 15                                          | 3-18               |

| 3-18 | IBUS Register 16                                          | 3-19               |

| 3-19 | OBUS Register 16                                          | 3-19               |

| 3-20 | IBUS Register 17                                          | 3-19               |

| 3-21 | OBUS Register 17                                          | 3-20               |

| 3-22 | IBUS Register AX0-15                                      | 3-21               |

| 3-23 | IBUS Register AX0-16                                      | 3-22               |

| 3-24 | IBUS/OBUS Register AX1-15                                 | 3-23               |

| 3-25 | IBUS/OBUS Register AX1-16                                 | 3-23               |

| 3-26 | IBUS/OBUS Register AX2-15                                 | 3-24               |

| 3-27 | IBUS Register AX2-16                                      | 3-24               |

| 3-28 | IBUS/OBUS Register AX3-15                                 | 3-25               |

| 3-29 | IBUS/OBUS Register AX3-16                                 | 3-26               |

| 4-1  | M8203 Maintenance LED Locations                           | <u>3-20</u><br>4-6 |

| A-1  | UNIBUS Address Map                                        | A-2                |

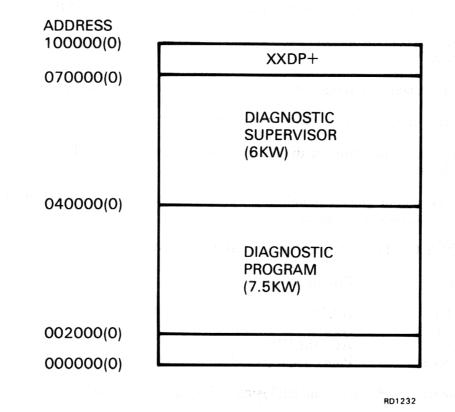

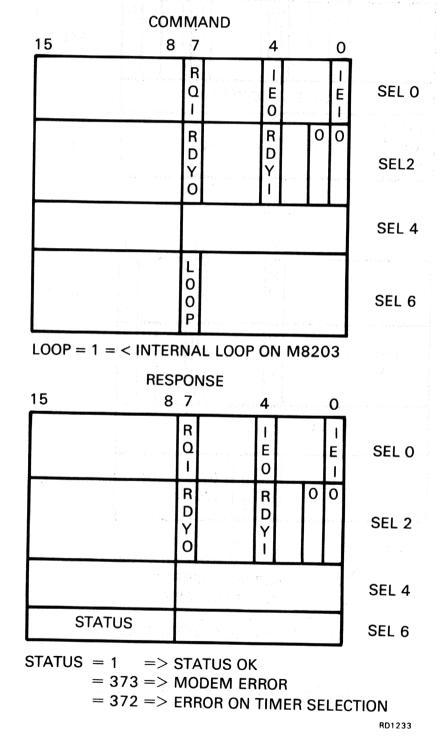

| B-1  | XXDP« Diagnostic Supervisor Memory Layout                 | A-2                |

|      | on a 16K word (minimum memory) System                     | B-2                |

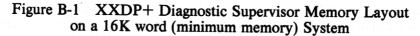

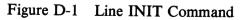

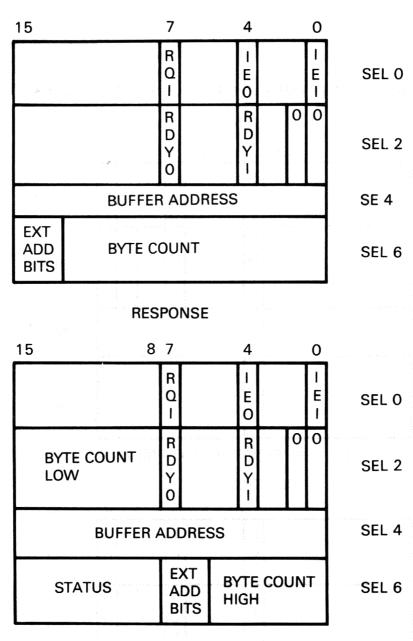

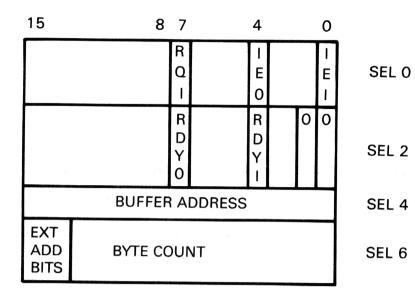

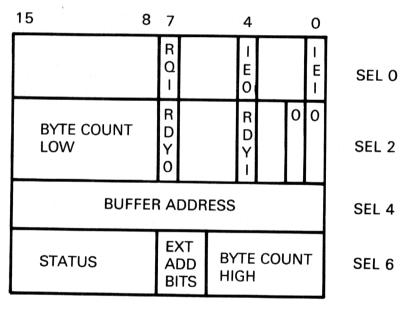

| D-1  | Line Unit INIT Command                                    | D-1                |

| D-2  | Receiver Buffer IN Command                                | D-1<br>D-2         |

| D-3  | Transmit Buffer IN Command                                | D-3                |

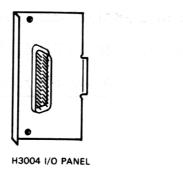

| F-1  | I/O Panel Drawings                                        | <b>F</b> -4        |

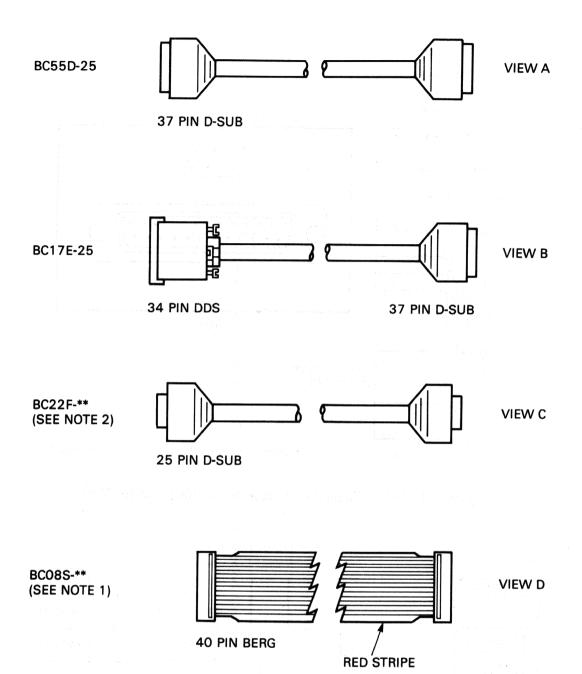

| F-2  | Cable Drawings                                            | F-5                |

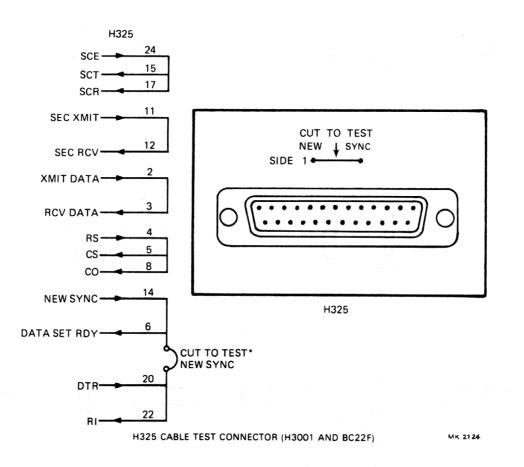

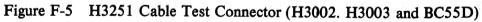

| F-3  | H325 Cable Test Connector (H3001 and BC22F)               | F-6                |

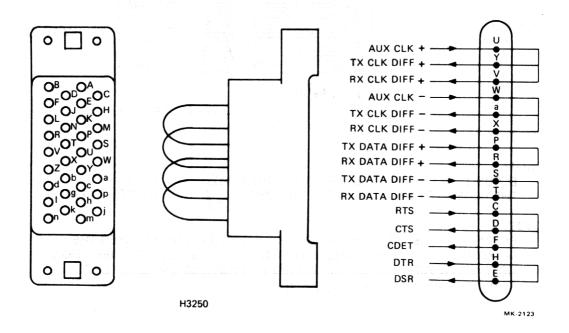

| F-4  | H3250 Test Connector                                      | F-6                |

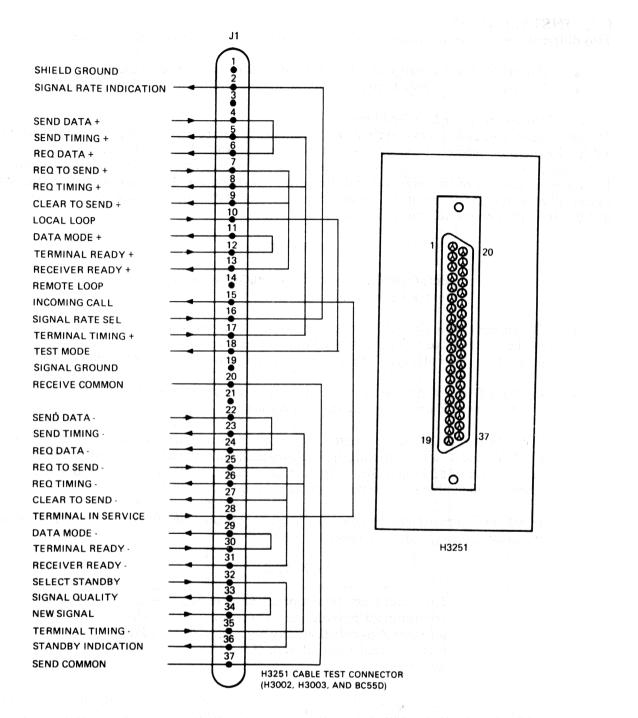

| F-5  | H3251 Cable Test Connector (H3002, H3003                  | - V                |

|      | and BC55D)                                                | F-7                |

| F-6  | Typical H3001 Installation in a Horizontally Oriented I/O | <b>_</b> /         |

|      | Bulkhead                                                  | FO                 |

| F-7  |                                                           | <b>F-9</b>         |

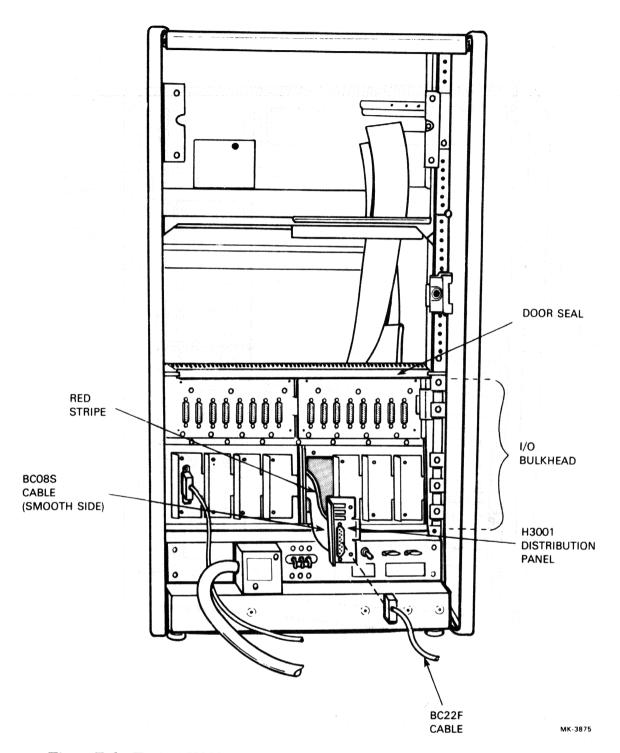

| 1-/  | H3004 Installation in a Vertically                        | 1 4 C              |

| F-8  | Oriented I/O Bulkhead                                     | F-10               |

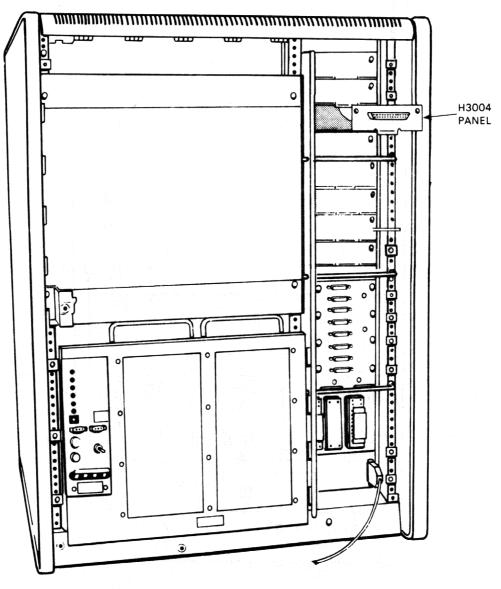

| F-9  | BC08S-10 to I/O Panel Cable Connection                    | F-11               |

| F-10 | 74-27292-01 Adaptor Bracket                               | F-12               |

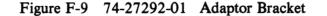

| 1-10 | H3001 Distribution Panel                                  | F-13               |

# **TABLES**

| Table No. | Title                           | Page |

|-----------|---------------------------------|------|

| 1-1       | KMS11-P Options                 | 1-3  |

| 2-1       | Option Packing List             | 2-2  |

| 2-2       | Voltages                        | 2-3  |

| 2-3       | Normal M8203 Configuration      | 2-9  |

| 2-4       | M8203 Jumper Functions          | 2-10 |

| 2-5       | Switch Pack E39 (Z) Selections  | 2-11 |

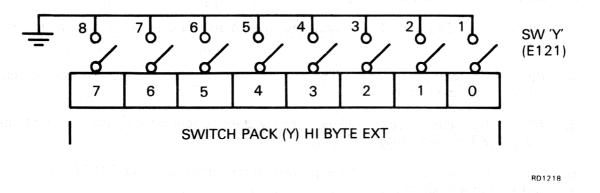

| 2-6       | Switch Pack E121 (Ý) Selections | 2-12 |

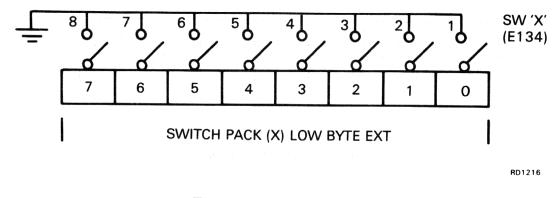

| 2-7       | Switch Pack E134 (X) Selections | 2-13 |

| 4-1       | CZKMB Diagnostic Summary        | 4-7  |

| 4-2       | CZKMC Diagnostic Summary        | 4-8  |

| 4-3       | CZDMR Diagnostic Summary        | 4-9  |

| 4-4       | CZDMS Diagnostic Summary        | 4-10 |

| 4-5       | CZKMR Diagnostic Summary        | 4-11 |

| 4-6       | EVDHA Diagnostic Summary        | 4-13 |

| 4-7       | EVDMA Diagnostic Summary        | 4-16 |

| 4-8       | EVDIG Diagnostic Summary        | 4-16 |

| F-1       | Cabinet Kit Descriptions        | F-1  |

| F-2       | H3001 Switch Settings           | F-13 |

|      | i i |

|------|-----|

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

| ж. 1 |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

|      |     |

# PREFACE

This manual describes in detail the installation requirements, programming considerations and servicing procedures, including diagnostic support, for the KMS11-P Synchronous Controller. A series of appendices is also provided.

Other documents which support the KMS11-P Synchronous Controler are:

- KMS11 Synchronous Communications Processor Pocket Service Guide (EK-KMS11-PS)-001)

- M8206 Microprocessor option description (YM-C093C-00)

- M8203 Line Unit Technical Manual (EK-M8203-TM-001)

- KMS11-P Print Set (MP 01175)

- Electronic Industries Association (EIA) Specifications

말 이 승규는 것이다.

<sup>an</sup>te de la companya <mark>e da ABRANIN</mark> Presidade de la companya de Presidade de la companya de la compa

and the state of the state. The state of the stat

a de la construcción de la constru La construcción de la construcción d

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This chapter presents a short introduction to KMS11-P operation. The term KMS11-P, as used in this manual, means the communication series which has a microprocessor module and a line unit module.

#### **1.2 GENERAL DESCRIPTION**

The KMS11-P is designed to be used in a network link for a high performance connection between a VAX-11 or a PDP-11 computer. It is a microprocessor based intelligent programmable synchronous communications controller.

Features of the KMS11-P:

- 1. Error reporting

- 2. Modem control

- 3. Diagnostic tests

- 4. Support for local or remote, full-duplex or half-duplex configurations

- 5. 18-bit non-processor request (NPR), direct memory access (DMA) transfers

The KMS11-P basic unit (KMS1P-M) is made up of a M8206 microprocessor (also named KMC11-B) and a M8203 line unit. The microprocessor operates as a parallel data interface between the central processor (VAX-11 or PDP-11) and the M8203 line unit. This line unit/microprocessor combination permits remote computer applications. (For remote operations, computers are connected through external modems that use common carrier facilities.) See Figure 1-1 for typical applications.

When associated with different types of cabinet kits (CK-KMS1P-XX) the KMS1P-M can operate within a range of speeds from 2.4 Kbits per second to 56 Kbits per second (see table 1-1 and refer to Appendix F-2 for a complete description of the different types of cabinet kits).

The KMS11-P system is made up of a basic subsystem and three options which allow it to have standard and special interface configurations. With these options, KMS11-P systems can operate within a range of speeds from 2.4K bits/s to 56K bits/s (see Table 1-1).

|                                       |                      |                                             | ·····································    |

|---------------------------------------|----------------------|---------------------------------------------|------------------------------------------|

| Optio                                 | on                   | Description                                 | Line Speed                               |

| KMS                                   | 51P-M                | Basic Unit                                  |                                          |

|                                       | KMS1P-Ax<br>KMS1P-Fx | EIA RS-232-C*<br>EIA RS-423-A<br>CCITT V.10 | Up to 19.2K bits/s<br>Up to 56K bits/s** |

| CK-F                                  | KMS1P-Bx             | ISO 2593/CCITT V.35***                      | Up to 56K bits/s                         |

| CK-F                                  | KMS1P-Ex             | EIA RS-422-A/CCITT V.11                     | Up to 56K bits/s                         |

| • • • • • • • • • • • • • • • • • • • | EIA – Electro        | nic Industries Association                  |                                          |

|                                       | Limited to 20        | K bits/s by RS-449 and 9600 bits/s by IS    | SO 4902                                  |

#### Table 1-1 KMS11-P Options

- \*\*\* ISO International Standards Organization CCITT (Comite Consultatif International de Telegraphie et Telephone)

- x Cabinet Family Dependent (Refers to Appendix F)

#### **1.3 KMS11-P SYSTEM OPERATION**

Operation of the KMS11-P is started and controlled by a user program residing in the memory of the central processor (CPU). A user program is made up of an application program and a device driver routine that interfaces with the KMS11-P. Communication between the user program and the KMS11-P is done by four 16-bit Control and Status Registers (CSRs) integrated in the microprocessor. These CSRs are used for:

- 1. Loading the microprocessor firmware

- 2. Initializing

- 3. Selecting the mode of operation

- 4. Assigning receive or transmit buffers to the KMS11-P

- 5. Getting receive and transmit buffer returns from the KMS11-P

- 6. Error reporting.

#### **1.4 GENERAL SPECIFICATIONS**

The following paragraphs contain performance, electrical and environmental specifications for all KMS11-P configurations.

#### 1.4.1 Power Requirements

The M8206 and M8203 line unit power requirements are listed below:

Module Voltage Rating (Approximate Values)

| M8206 | + 5 volts at 7.5 amperes   |

|-------|----------------------------|

| M8203 | + 5 volts at 3.0 amperes   |

|       | + 15 volts at 0.15 amperes |

|       | - 15 volts at 0.2 amperes  |

#### 1.4.2 Environmental Requirements

The KMS11-P is designed to operate in a class B environment as described in DEC Standard 102.B.

- 1. Operating temperature range 10 degrees C to 40 degrees C (50 degrees F to 104 degrees F)

- 2. Relative humidity 10 to 90 percent with a maximum wet bulb of 28 degrees C (82 degrees F) and a minimum dewpoint of 2 degrees C (36 degrees F)

#### 1.5 EIA STANDARDS OVERVIEW (RS-449 VS RS-232-C)

The most common interface standard used in the past few years has been the RS-232-C. It does, however, have serious limitations for use in modern data communications systems; the most important being speed and distance. For this reason, the RS-449 has been developed to replace the RS-232-C. It maintains a degree of compatibility with RS-232-C to allow an upward change to RS-449.

The most significant difference between RS-449 and RS-232-C is the electrical characteristics of signals used between the data communication equipment (DCE) and the data terminal equipment (DTE). The RS-232-C standard uses only unbalanced circuits while the RS-449 uses both balanced and unbalanced electrical circuits.

The specifications for these different types of electrical circuits supported by RS-449 are contained in EIA Standard RS-422-A for balanced circuits and RS-423-A for unbalanced circuits. These new standards permit much faster transmission speeds and will allow larger distances between the DTE and DCE. The maximum transmission speeds supported by RS-422-A and RS-423-A circuits vary with circuit length; the normal speed limits being 20K bits/s for RS-423-A at 61 meters (200 ft) and 2M bits/s for RS-422-A at 61 meters (200 ft). These speeds or distances can be exceeded in special applications by using lower speeds for long distances, and the reverse.

Another major difference between RS-232-C and RS-449 is that two new connectors have been specified, to allow for the additional pins needed to support new circuit functions and the balanced interface circuits. One connector is a 37-pin cinch used to accept most data communications applications. The other is a nine-pin cinch used in applications needing secondary channel functions. These are typically some of the new circuits that have been added in RS-449, to support local and remote loopback testing and standby channel selection.

The change from RS-232-C to RS-449 will take some time. Therefore, any applications that are interconnected between RS-232-C and RS-449 must follow the limitations of RS-232-C, which has a normal speed of 20K bits/s at a maximum distance of 15 meters (50 ft).

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides all the necessary information for installing and testing the KMS11-P microprocessor subsystem. A checklist, which can be used to verify the installation process, is also included.

#### 2.2 UNPACKING AND EXAMINATION

The KMS11-P is packed according to commercial practices. When unpacking, remove all packing material and check the equipment against the shipping list (Table 2-1 contains a list of the items provided for each configuration). Examine all parts and carefully examine the module for obvious damage. Report damages or shortage to the shipper and inform the local DIGITAL office.

#### 2.3 INSTALLATION CONSIDERATIONS

Installation of the KMS11-P microprocessor/line unit subsystem should be done in four phases:

Phase 1 – Preinstallation Considerations

Verify system requirements, system position, and configuration requirements.

Phase 2 – Microprocessor Installation

Configure, install and verify microprocessor module via the appropriate diagnostics.

#### Phase 3 – Line Unit Installation

Configure the line unit module for the customer application and install the cable, and verify it via appropriate diagnostics.

#### Phase 4 – KMS11-P System Testing

Verify the KMS11-P microprocessor subsystem operation with the functional diagnostics and system exerciser programs.

#### 2.4 PREINSTALLATION CONSIDERATIONS

The following list (Table 2-1) should have been considered before ordering a KMS11-P communications interface, to make sure that the system can accept the KMS11-P, and that it can be installed correctly. These steps should also be verified at installation time.

| Option    | Part List                             | Description                                    |

|-----------|---------------------------------------|------------------------------------------------|

| KMS1P-M   | M8206                                 | Microprocessor module                          |

|           | M8203                                 | Line unit module                               |

|           | BC08S-1                               | Module interconnect cable                      |

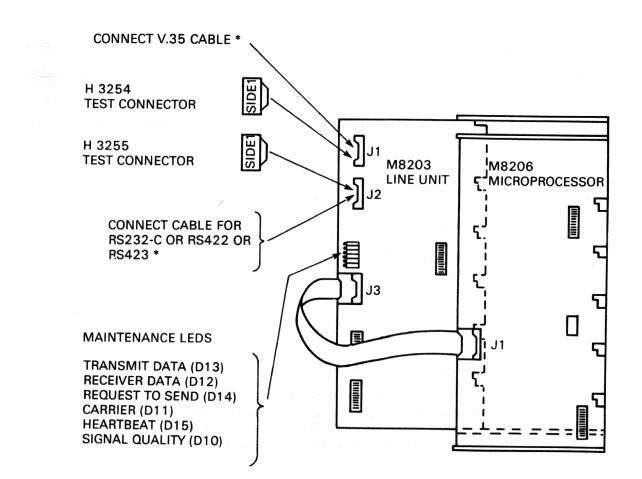

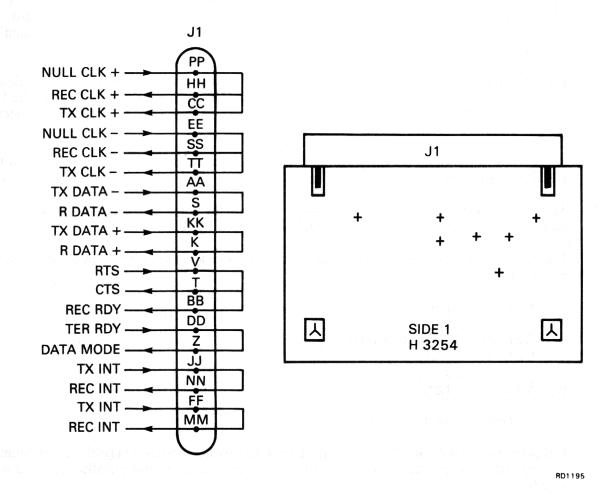

|           | H3254                                 | V.35 module test connector                     |

|           | H3255                                 | RS232-C/RS422-A/RS423-A                        |

|           |                                       | test connector                                 |

|           | · · · · · · · · · · · · · · · · · · · |                                                |

|           | EK-KMS11-IN                           | KMS11-P Installation Manual                    |

|           | EK-KMS11-TM<br>MP 01175               | KMS11-P Technical Manual<br>Customer print set |

|           |                                       | Diagnostic Package (as applicable)             |

| CK-KMS1P- | XX                                    | Cabinet Kits                                   |

|           |                                       | (Refer to Appendix F.2)                        |

Table 2-1Option Packing List

#### 2.4.1 System And Device Positioning

2.4.1.1 System Positioning – On systems that contain many high speed Direct Memory Access (DMA) devices, there is a chance of unacceptable bus latency. To help prevent this from occurring the nearer the physical position of the KMS11-P to the memory and CPU, the higher the DMA device priority.

**2.4.1.2** Device Positioning – The KMS11-P needs two hex-height, Small Peripheral Controller (SPC), backplane slots (two adjacent slots are best). A DD11-C or a DD11-D backplane can accept the KMS11-P.

#### CAUTION

Each KMS11-P needs approximately 10.5 amperes from the +5 Volt source. Check to make sure that the supply is capable of providing 10.5 amperes per KMS11-P.

#### 2.4.2 System Requirements

1. UNIBUS loading

M8206 microprocessor

#### 1 UNIBUS dc load 5 UNIBUS ac loads

M8203 line unit

No UNIBUS loads

2. Power Requirements

Check the power supply before and after installation to make sure the supply is not overloaded. The microprocessor/line unit total current requirement for the +5 volt supply is approximately 10.5 amperes. Also, the modules need plus and minus 15 volts. Power requirements for the microprocessor/line units are listed in Table 2-2.

| Module | Voltage Rating<br>(Approximate values) | Maximum<br>Voltage | Minimum<br>Voltage | Backplane<br>Pin |  |

|--------|----------------------------------------|--------------------|--------------------|------------------|--|

| M8206  | + 5 volts at 7.5 A                     | + 5.25             | + 5.0              | C1A2             |  |

| M8203  | + 5 volts at 3.0A                      | + 5.25             | + 5.0              | C1A2             |  |

|        | +15 volts at 0.15A                     | +15.75             | +14.25             | C1U1             |  |

|        | -15 volts at 0.2A                      | -15.75             | -14.25             | C1B2             |  |

Table 2-2 Voltages

#### 2.5 MICROPROCESSOR INSTALLATION

#### 2.5.1 Backplane Considerations

Perform the following on the SPC slot that will contain the KMS11-P, M8206 microprocessor module (selected at pre-installation).

- 1. Verify that backplane voltages are within the specified tolerances listed in Table 2-2.

- 2. Turn system power off and remove the NPR Grant (NPG) wire that runs between CA1 and CB1 on that backplane slot for the M8206 module.

#### NOTE

#### Make sure this jumper is replaced, if the microprocessor is removed from the system.

#### 2.5.2 M8206 Considerations

Perform the following on the KMS11-P M8206 microprocessor module:

- 1. Make sure that the priority plug (level 5 provided) is correctly seated in its socket.

- 2. Verify that jumper W1 (M8206) is installed (Figure 2-1). This jumper should not be removed in the field; it is removed only during automated module testing at the factory to inhibit the oscillator in the microprocessor clock logic.

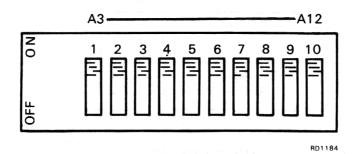

- 3. Set the switches at location E129, so that the module will respond to its assigned address. When a switch is OFF (open), a binary 1 is decoded; when ON (closed), a binary 0 is decoded. Note that the switch indicated '1' (Figure 2-2) controls address bit 3, '2' to address bit 4, '3' to address bit 5, and so on.

E 31 VECTOR SELECT (7-POLE SWITCH) E129 ADDRESS SELECT (10-POLE SWITCH) E82-18 PROGRAM TIMER SELECT (8-POLE SWITCH) W1 ALWAYS IN W3 NORMALLY IN (OUT TO DISABLE KMC11-B CONTROL OF AC LO)

Figure 2-1 M8206 (KMC11-B) Switch and Jumper Locations

| 1 | MSB |      |    |     |     |            |     |                   |            |       |                          |                   |                    |                                      |                                                                                                 | LSB                             |

|---|-----|------|----|-----|-----|------------|-----|-------------------|------------|-------|--------------------------|-------------------|--------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|

|   | 15  | 14   | 13 | 12  | 11  | 10         | 9   | 8                 | 7          | 6     | 5                        | 4                 | 3                  | 2                                    | 1                                                                                               | 0                               |

|   | 1   | 1    | 1  |     |     |            | SWI | ГСН Р             | ACK I      | E 129 |                          |                   | N. A. I            | 0.                                   | 0                                                                                               | 0                               |

|   |     |      |    |     |     |            |     |                   |            |       |                          |                   | 14 II A 14 14<br>1 |                                      |                                                                                                 |                                 |

|   | SW  | лтсн | NB | S10 | S9  | S8         | S7  | S6                | S5         | S4    | <b>S</b> 3               | S2                | S1                 | DE\                                  | /ICE A                                                                                          | DD.                             |

|   |     |      |    |     |     |            |     |                   | OFF<br>OFF | OFF   | OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF  | 7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | 6001<br>6002<br>6003<br>6004<br>6005<br>6006<br>6007<br>6007<br>6007<br>6007<br>6007<br>6007    | 0<br>0<br>0<br>0<br>0<br>0<br>0 |

|   |     |      |    |     | OFF | OFF<br>OFF | OFF | OFF<br>OFF<br>OFF | OFF<br>OFF | OFF   |                          |                   |                    |                                      | 6040<br>6050<br>6050<br>6050<br>6070<br>6070<br>6100<br>6100<br>6100<br>63200<br>63300<br>63400 | 0<br>0<br>0<br>0<br>0<br>0      |

NOTE : Switch off responds to logical one on the UNIBUS

RD1183

Figure 2-2 M8206 (KMC11-B) Address Selection

#### SWITCH PACK E129

Figure 2-3 M8206 (KMC11-B) Device Address Switch Pack Layout

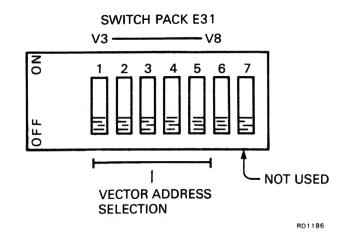

4. Vector selection is done using switches one to six, at location E31 (see Figure 2-4). When a switch is OFF (open) a binary 0 is decoded; when ON (closed), a binary 1 is decoded. Note that switch '1' controls vector bit 3, '2' bit 4, and so on.

MSB

1

LSB

|    |    |    |                       |      |    |                |                                        |                                        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |     |                                                                           | LOD  |                                                                                                                  |

|----|----|----|-----------------------|------|----|----------------|----------------------------------------|----------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------|

| 14 | 13 | 12 | 11                    | 10   | 9  | 8              | 7                                      | 6                                      | 5              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                                                                        | 2   | <b>1</b> .                                                                | 0    | l di j                                                                                                           |

| 1  | 0  | 0  | 0                     | 0    | 0  |                | SWI                                    | тсн р                                  | РАСК           | E31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          | 1   | 0                                                                         | 0    |                                                                                                                  |

|    | 3  |    |                       |      |    |                | 1                                      | n a da ga<br>na ga<br>na da            |                | i i<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen<br>Produčen | an an<br>1999 - China Anna an An |     |                                                                           |      | -                                                                                                                |

|    |    |    | SW                    | ITCH | NB | S6             | S5                                     | S4                                     | S3             | S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | S1                                                                                                                       | VEC | TOR                                                                       | ADD. |                                                                                                                  |

|    |    |    | in posta<br>ny Stanon |      |    | ON<br>ON<br>ON | ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON<br>ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ON<br>ON<br>ON                                                                                                           |     | 300<br>310<br>320<br>330<br>340<br>360<br>370<br>400<br>500<br>600<br>700 |      | and the second |

NOTE : Switch ON produces logical 1 on the UNIBUS

RD1185

## Figure 2-4 M8206 (KMC11-B) Vector Address Selection

Figure 2-5 M8206 (KMC11-B) Vector Address Switch Pack Layout

- 5. Jumper W3 is normally IN and should only be removed if the KMC11-B is not to control ACLO.

- 6. The microprocessor contains a timer to run certain protocol firmware. It is important that timer values are set accurately before installation.

The M8206 REV J microprocessor contains a switch pack at location E82, which is used to select the value of the program timer. E82-8 ON provides a timeout value of 115 milliseconds; OFF is 75 microseconds (E82 1-7 are not used).

#### NOTE

Make sure that the program timer selected is 115 millisecond when used with the KMS11-P option (E82-8 is ON).

#### 2.5.3 M8206 Insertion

- 1. Carefully insert the M8206 microprocessor module into the selected SPC slot and perform the following tasks.

- 2. Turn system power ON and verify that the backplane voltages are within the specified tolerances listed in Table 2-2.

- 3. Load and execute the M8206 static diagnostics, parts one and two (no test connectors are needed).

- a. PDP-11 system

M8206 Static Test 1 M8206 Static Test 2

b. VAX-11 systems

CZKMB CZKMC

| Microprocessor Repair Level Diagnostic | EVDHA |

|----------------------------------------|-------|

| Microprocessor Level 2 Diagnostic      | ESDHB |

Chapter 4 provides additional information on these diagnostics. On getting a minimum of five error-free end passes, proceed to the M8203 line unit installation section.

#### 2.6 LINE UNIT INSTALLATION

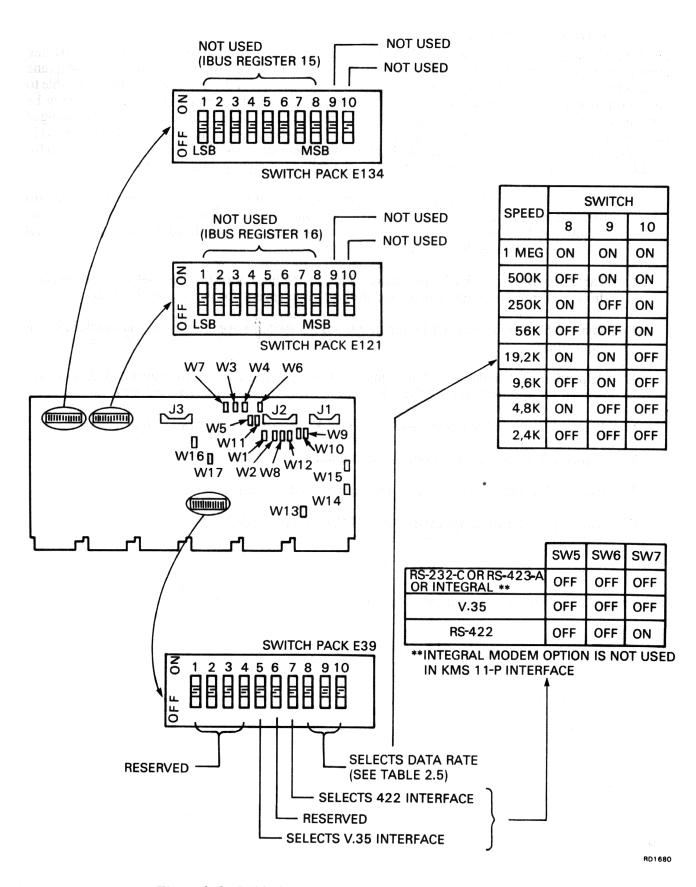

The M8203 line unit is a universal module with various types of interface capabilities. The M8203 line unit does not present any ac or dc loads to the UNIBUS system and takes power only from the backplane slot in which it resides. All data and control signals flow into and out of the line unit via a BC08R cable to the microprocessor. Because of the various M8203 applications, the configurations for each may be different, and are selected via switches, jumpers and different cables. To provide a better understanding of these variations, a number of tables describing each switch pack, jumper and cable function (as listed in Table 2-7) have been created for reference. Table 2-3 lists the normal M8203 line unit configuration for the different types of KMS11-P options. Refer to the following eight points as a guide.

- 1. Table 2-4 Jumper functions These jumpers are used to select various interface standard parameters and modem interface signals, depending on application and modem type. Additional DIP switches are available on the RS232-C Bulkhead Panels for additional interface signal selection. (Refer to Appendix F3.)

- 2. Table 2-5 Switch Pack E39 functions This switch pack allows correct selection of interface driver and receiver control logic and different line speeds for various applications.

- 3. Table 2-6 Switch Pack E121 functions This switch pack is not used in the KMS11-P application.

- 4. Appendix F2. Cabinet Kits Description This appendix lists the functions and uses of each cabinet kit used with the KMS11-P. (Shows the cables and test connectors.)

- 5. Figure 2-6 shows the jumper and switch pack positions on the M8203 line unit.

- 6. Figure 2-7 shows the microprocessor and line unit installation.

- 7. Figures 2-8 and 2-9 show the module turnaround test connectors.

- 8. Switch pack E134 is not used in the KMS11-P application.

Figure 2-6 M8203 Line Unit Switch and Jumper Locations

| M8203<br>Config.                 | Interface Type                            | EIA RS-232-C                                | CCITT V.35                                 | EIA<br>RS-422-A                            | EIA<br>RS-423-A                            |

|----------------------------------|-------------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| Jumper<br>config.*               | W1-W6, W11<br>W14-W17                     | OUT                                         | OUT                                        | OUT                                        | OUT                                        |

| Table 2-4                        | W7-W10<br>W12, W13                        | IN                                          | IN                                         | IN                                         | IN                                         |

| Switch<br>Pack E39<br>Table 2-5  | S1-4<br>S5<br>S6<br>S7<br>S8<br>S9<br>S10 | OFF<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>OFF | OFF<br>ON<br>OFF<br>OFF<br>ON<br>ON<br>OFF | OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>OFF | OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>OFF |

| Switch                           | S1-8                                      | NOT USED                                    | NOT USED                                   | NOT USED                                   | NOT USED                                   |

| Pack<br>E121                     | S9                                        | NOT USED                                    | NOT USED                                   | NOT USED                                   | NOT USED                                   |

| Table 2-6                        | <b>S</b> 10                               | NOT USED                                    | NOT USED                                   | NOT USED                                   | NOT USED                                   |

| Q                                | S1-8                                      | OFF                                         | OFF                                        | OFF                                        | OFF                                        |

| Switch<br>Pack E134<br>Table 2-7 | <b>S9</b>                                 | OFF                                         | OFF                                        | OFF                                        | OFF                                        |

|                                  | <b>S</b> 10                               | NOT USED                                    | NOT USED                                   | NOT USED                                   | NOT USED                                   |

| Cabinet Kit<br>required          |                                           | CK-KMS1P-Ax**                               | CK-KMS1P-Bx**                              | CK-KMS1P-Ex**                              | CK-KMS1P-Fx*                               |

| Module<br>Turnaround             |                                           | H3254<br>IN J1 AND<br>H3255 in J2           | H3254<br>IN J1 AND<br>H3255 in J2          | H3254<br>IN J1 AND<br>H3255 in J2          | H3254<br>IN J1 AND<br>H3255 in J2          |

# Table 2-3 Normal M8203 Configuration

Modem dependent

\*\* x Cabinet family dependent -For a complete description of the cabinet kits refer to Appendix F.2.

RD1688

2-9

| <br>Jumper  | Normal<br>Config. | Function                                                                                                                                                                                                                                               |

|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>W</b> 1  | OUT               | Clear to Send EIA/V.35                                                                                                                                                                                                                                 |

| W2          | OUT               | Data Mode EIA/V.35                                                                                                                                                                                                                                     |

| W3          | OUT               | Receive Data EIA                                                                                                                                                                                                                                       |

| W4          | OUT               | Receive Clock EIA                                                                                                                                                                                                                                      |

| <b>W</b> 5  | OUT               | Receive Ready EIA                                                                                                                                                                                                                                      |

| W6          | OUT               | Transmit Clock EIA                                                                                                                                                                                                                                     |

| W7          | IN                | Signal Rate Indicate – When removed, opens signal to interface in RS-422-A and RS-232-C configurations.                                                                                                                                                |

| <b>W8</b>   | IN                | Data Mode (Data Set Ready) – When removed,<br>opens signal to interface in RS-422-A/423-A<br>configurations. It has no effect in RS-232-C.                                                                                                             |

| W9          | IN                | Null Modem Clock – When removed the signal<br>amplitude is lowered below the interface<br>standards so as not to create interference in<br>some modems.                                                                                                |

| <b>W</b> 10 | IN                | Terminal Ready – When removed, it opens the signal to modem in RS-422-A/423-A configurations.                                                                                                                                                          |

| W11         | OUT               | Receiver Ready (Carrier Detect) – When<br>installed, it allows this signal to be on at all<br>times. This could cause a problem with the<br>microcode since the Universal Synchronous<br>Receiver/Transmitter (USYRT) will be enabled<br>all the time. |

| W12         | IN                | Terminal in Service (Make Busy) – When<br>removed, it opens this signal to the modem.<br>Some modems will not answer the phone and<br>will be put in Analog Loopback when this signal<br>is asserted.                                                  |

| <br>W13     | IN                | Oscillator Enable – To be removed only for factory automatic testing. Jumper should always be installed.                                                                                                                                               |

# Table 2-4M8203 Jumper Functions

| Jumper      | Normal<br>Config. | Function                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                  |

| W14 and W15 | OUT<br>OUT        | 56K Bandpass Filter Enable – With these jumpers installed, the bandpass filter is limited to 56K b/s. Used in special applications only.                                                                                                                                                                                                                                         |

| W16         | OUT               | Switched RTS-CTS Enable – When this jumper<br>is installed, it enables the Request To Send<br>interlock in the M8203 line unit which inhibits<br>asserting RTS, until CTS is dropped. This<br>jumper should never be installed when the<br>KMS11-P is operating with a modem that has<br>the constant CTS option installed.                                                      |

| <b>W17</b>  | OUT               | Half-Duplex Lockout Enable – When this<br>jumper is installed, it enables the M8203 line<br>unit half-duplex lockout feature when half-<br>duplex mode is selected. The lockout feature<br>disables the transmitter or receiver when the<br>other is active. This jumper applies only to half-<br>duplex applications. It must not be installed for<br>full-duplex applications. |

## Table 2-4 M8203 Jumper Functions (Cont)

#### NOTE

Jumpers W16 and W17 are mutually exclusive. Only one or the other may be installed, not both. Also, these jumpers are provided only on M8203 modules REV E or later. For modules up to REV D, refer to ECO-M8203-MK-007 for details of jumpers.

Table 2-5 Switch Pack E39 (Z) Selections

| Switches | Function                         |                     | n an |                                                                 |

|----------|----------------------------------|---------------------|------------------------------------------|-----------------------------------------------------------------|

| 1-4      | Not used in KMS11-P              |                     |                                          | addan da Alan ann an an an Alan an Alan<br>An an Alan Alan Alan |

| 5-7      | Interface Selection – Selects of | correct drivers and | receivers for e                          | ach interface type.                                             |

|          | Interface Type                   | SW5                 | SW6                                      | SW7                                                             |

|          | RS-232-C,RS-423-A                | OFF                 | OFF                                      | OFF                                                             |

|          | V.35                             | ON                  | OFF                                      | OFF                                                             |

|          | RS-422-A                         | OFF                 | OFF                                      | ON                                                              |

| Switches | Function            |                                                                                                 |        |    |       |     | 4      |     |  |  |

|----------|---------------------|-------------------------------------------------------------------------------------------------|--------|----|-------|-----|--------|-----|--|--|

| 8-10     | Line Speed testing. | Line Speed Selection – Selects modem speed for null modem applications, and diagnostic testing. |        |    |       |     |        |     |  |  |

|          |                     | $V_{i} \in \{1, \dots, n\}$                                                                     | Switch |    |       |     | Switch |     |  |  |

|          | Speed               | 8                                                                                               | 9      | 10 | Speed | 8   | 9      | 10  |  |  |

|          | Not used            | ON                                                                                              | ON     | ON | 19.2K | ON  | ON     | OFF |  |  |

|          | Not used            | OFF                                                                                             | ON     | ON | 9.6K  | OFF | ON     | OFF |  |  |

|          | Not used            | ON                                                                                              | OFF    | ON | 4.8K  | ON  | OFF    | OFF |  |  |

|          | 56K                 | OFF                                                                                             | OFF    | ON | 2.4K  | OFF | OFF    | OFF |  |  |

# Table 2-5 Switch Pack E39 (Z) Selections (Cont)

## NOTE

Switch OFF equals a logical one (1).

\_

| Table | 2-6 | Switch | Pack | E121 | (Y) | Selections |  |

|-------|-----|--------|------|------|-----|------------|--|

|       |     |        |      |      |     |            |  |

|       |     |        |      |      |     |            |  |

. ....

. .

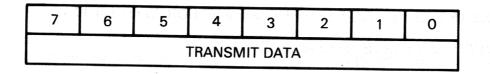

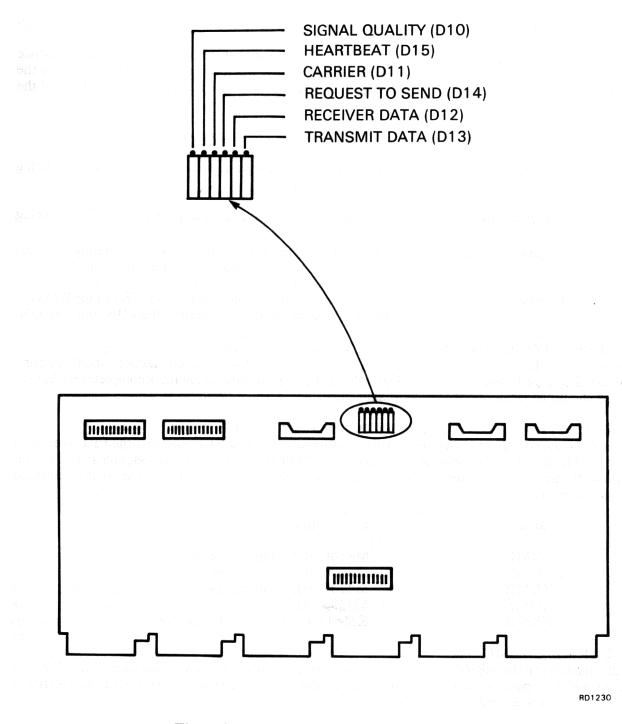

| Switches | Function second temperatures and the first second |