KD11-B processor maintenance manual

### Copyright © 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

**PDP**

FLIP CHIP

**FOCAL**

**DIGITAL**

**COMPUTER LAB**

**UNIBUS**

## CONTENTS

|           |                                               | Page |

|-----------|-----------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                  |      |

| 1.1       | SCOPE                                         | 1-1  |

| 1.2       | ORGANIZATION                                  | 1-1  |

| CHAPTER 2 | MICROPROGRAM CONTROL                          |      |

| 2.1       | INTRODUCTION                                  | 2-1  |

| 2.2       | MICROPROGRAMMED VERSUS CONVENTIONAL CONTROL   | 2-1  |

| 2.3       | CONTROL STORE                                 | 2-1  |

| 2.4       | BRANCHING WITHIN MICROROUTINES                | 2-7  |

| 2.5       | MICROPROGRAM FLOW                             | 2-10 |

| 2.5.1     | Flow Chart Notation                           | 2-11 |

| 2.5.2     | Interrupts and Traps                          | 2-17 |

| 2.5.3     | Console Functions                             | 2-18 |

| 2.6       | MICROPROGRAM SYMBOLIC LISTING                 | 2-20 |

| 2.7       | MICROPROGRAM BINARY LISTING                   | 2-20 |

| 2.8       | MICROPROGRAM CROSS REFERENCE LISTING          | 2-24 |

| CHAPTER 3 | CONSOLE DESCRIPTION                           |      |

| 3.1       | INTRODUCTION                                  | 3-1  |

| 3.2       | GENERAL DESCRIPTION                           |      |

| 3.2.1     | ADDRESS/DATA Register Logic                   | 3-1  |

| 3.2.2     | Control Switch Logic                          | 3-1  |

| 3.3       | DETAILED DESCRIPTION                          | 3-2  |

| 3.3.1     | Multiplexer                                   | 3-2  |

| 3.3.2     | Clock                                         | 3-3  |

| 3.3.3     | Counter                                       | 3-4  |

| 3.3.4     | Display Buffer and Driver                     | 3-6  |

| 3.3.5     | Control Switches and Logic                    |      |

| 3.3.5.1   | Normal Operating Mode                         | 3-8  |

| 3.3.5.2   | Panel Lock Mode                               |      |

| 3.3.5.3   | Power Loss During Operation                   |      |

| CHAPTER 4 | KD11-B DETAILED DESCRIPTION                   |      |

| 4.1       | INTRODUCTION                                  | 4-1  |

| 4.2       | ROMs AS GENERALIZED GATES                     |      |

| 4.3       | KD11-B DATA PATH, SIMPLIFIED DESCRIPTION      | 4-3  |

| 4.3.1     | Data Path (DP) Detailed Description           | 4-3  |

| 4.3.2     | DP Data Polarities                            | 4-3  |

| 4.3.3     | Control Logic and Microprogramming (CON)      | 4-4  |

| 4.3.4     | A-Multiplexer                                 |      |

| 4.3.5     | Arithmetic Logic Unit (ALU)                   | 4-6  |

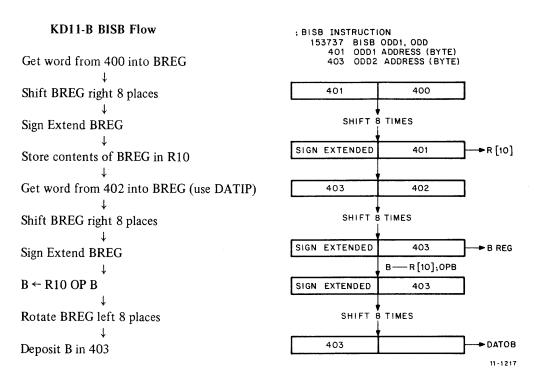

| 4.3.6     | B Register                                    | 4-9  |

| 4.3.6.1   | Functional Description                        | 4-9  |

| 4.3.6.2   | BLEG Operations That Provide Input to the ALU | 4-12 |

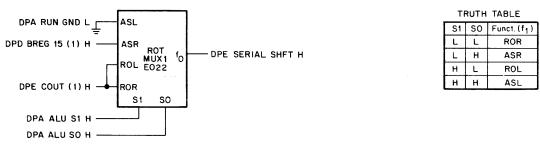

| 4.3.6.3   | BREG Shifting Operations                      | 4-13 |

| 4.3.7     | Byte Instructions                             | 4-15 |

| 4.3.8     | Scratch Pad Memory                            | 4-15 |

# CONTENTS (Cont)

|           |                                              | Page   |

|-----------|----------------------------------------------|--------|

| 4.3.9     | Scratch Pad Memory Address Multiplexer       | 4-18   |

| 4.3.10    | Processor Status Word Register               |        |

| 4.3.11    | Constants Generator                          |        |

| 4.3.12    | Console Switch Register                      |        |

| 4.3.13    | Switch Register Multiplexers                 |        |

| 4.3.14    | Console Multiplexer                          |        |

| 4.4       | INSTRUCTION DECODING                         | 4-27   |

| 4.4.1     | Introduction                                 |        |

| 4.4.2     | Double Operand Instructions                  |        |

| 4.4.3     | Branch On Unary                              |        |

| 4.4.4     | PDP-11 Branch Instructions                   |        |

| 4.4.5     | Operate Instructions                         |        |

| 4.4.6     | Auxiliary ALU Control                        |        |

| 4.5       | PROCESSOR CLOCK                              |        |

| 4.6       | UNIBUS CONTROL                               |        |

| 4.6.1     | DATI Timing                                  |        |

| 4.6.2     | DATI Operation                               |        |

| 4.6.2.1   | DATIP Operation                              |        |

| 4.6.2.2   | DATIP Logic                                  |        |

| 4.6.3     | DATO                                         |        |

| 4.6.4     | Byte Operations                              |        |

| 4.6.5     | Bus Errors                                   |        |

| 4.7       | INTERNAL UNIBUS ADDRESSES                    |        |

| 4.8       | BUS REQUESTS                                 |        |

| 4.9       | NON-PROCESSOR REQUESTS (NPR)                 |        |

| 4.10      | SERIAL COMMUNICATIONS LINE DESCRIPTION (SCL) | 4.40   |

| 4.11      | BAUD RATE ADJUSTMENT                         | 4-40   |

| 4.12      | LINE CLOCK                                   |        |

| 4.12.1    | Introduction                                 |        |

| 4.12.2    | Flag Control                                 |        |

| 4.12.3    | Interrupt Control                            |        |

| 4.13      | POWER FAIL                                   |        |

| 7.13      | TOWERTAIL                                    | . 4-40 |

| CHAPTER 5 | KD11-B AND CONSOLE MAINTENANCE               |        |

| 5.1       | INTRODUCTION                                 | . 5-1  |

| 5.2       | DIAGNOSTICS                                  |        |

| 5.3       | TYPES OF FAILURES                            |        |

| 5.4       | SUGGESTED EQUIPMENT                          |        |

| 5.5       | PROCEDURES                                   |        |

| 5.6       | ADJUSTMENTS                                  |        |

| 5.7       | KD11-B PRINT FUNCTION TABLE                  |        |

| 5.8       | EXTERNAL CLOCK INPUTS                        |        |

| 5.9       | KM11 MAINTENANCE PANEL                       |        |

| 5.10      | USING KM11 MAINTANENCE PANEL                 | . 5-9  |

| 5.11      | CONSOLE MAINTENANCE                          |        |

# ILLUSTRATIONS

| Figure No. | Title                                                                  | Page   |

|------------|------------------------------------------------------------------------|--------|

| 2-1        | Control Store Word Bit and Field Format                                |        |

| 2-2        | KD11-B Simplified Flow Diagram                                         | 2-10   |

| 2-3        | Excerpt from Microprogram Flow (KMP-KDL-B-1)                           | 2-11   |

| 2-4        | CMP #15, CHAR (022767), Simplified Flow Diagram                        | 2-13   |

| 2-5        | Excerpt of (K-WL-KD11-B-2) Microprogram Symbolic Listing               | 2-21   |

| 2-6        | Excerpt of Microprogram Binary Listing (K-W-KD11-B-3)                  | 2-22   |

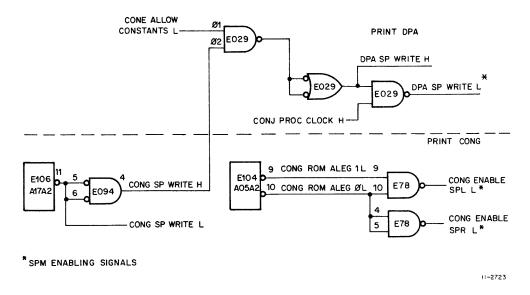

| 2-7        | Generation of SPM Enabling Signals                                     | 2-24   |

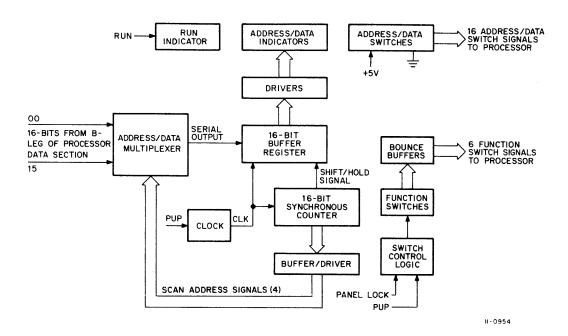

| 3-1        | Console Functional Block Diagram                                       | . 3-2  |

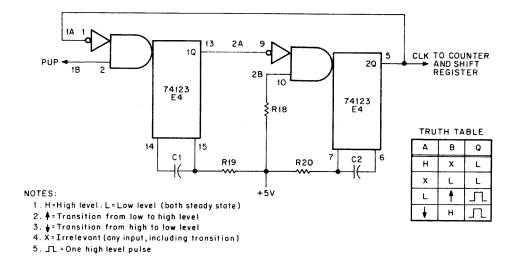

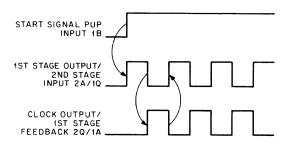

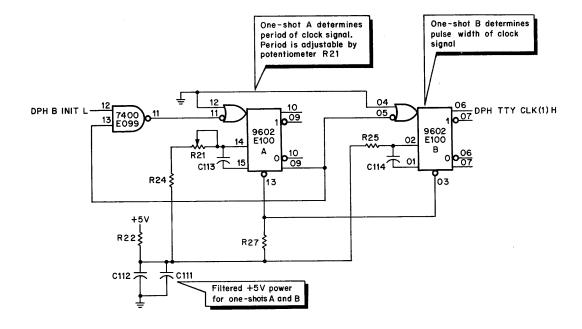

| 3-2        | Console Clock, Schematic and Timing Diagram                            | . 3-4  |

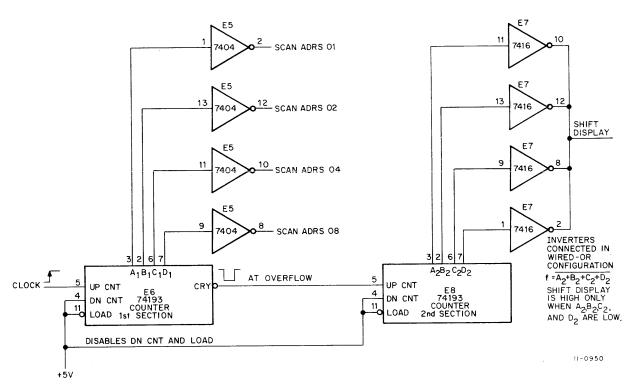

| 3-3        | Counter, Simplified Logic Diagram                                      |        |

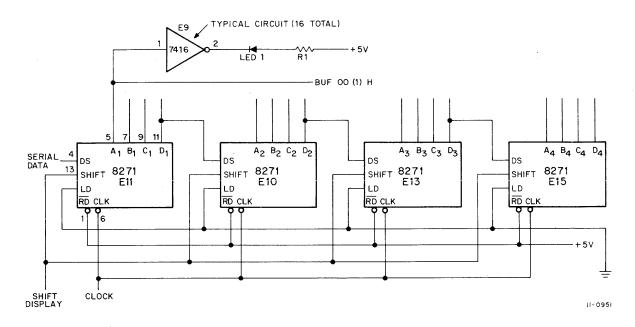

| 3-4        | Display Buffer and Driver, Simplified Logic Diagram                    |        |

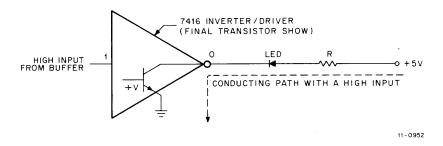

| 3-5        | LED Driver Circuit                                                     |        |

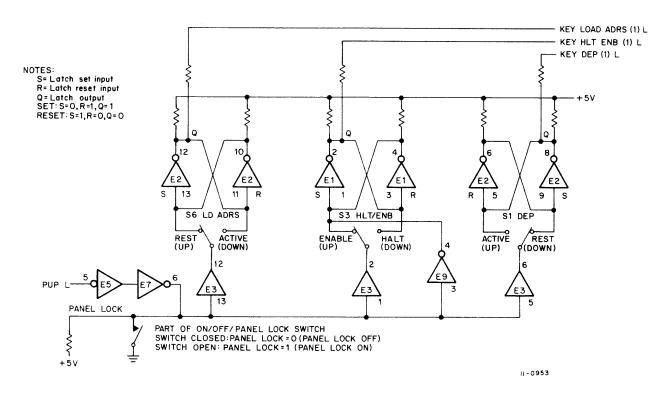

| 3-6        | Control Switches and Bounce Buffers, Logic Diagram                     |        |

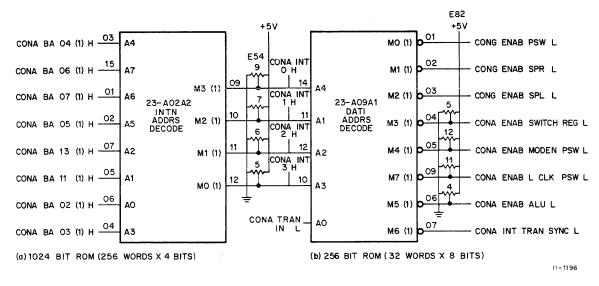

| 4-1        | 1024-Bit and 256-Bit ROMs                                              |        |

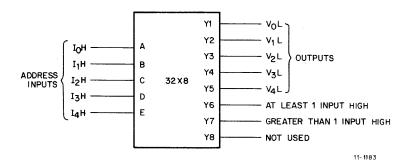

| 4-2        | 32 X 8 ROM used as Generalized Gate                                    |        |

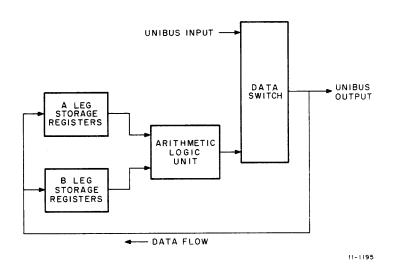

| 4-3        | KD11-B Simplified Data Path Block Diagram                              | 4-3    |

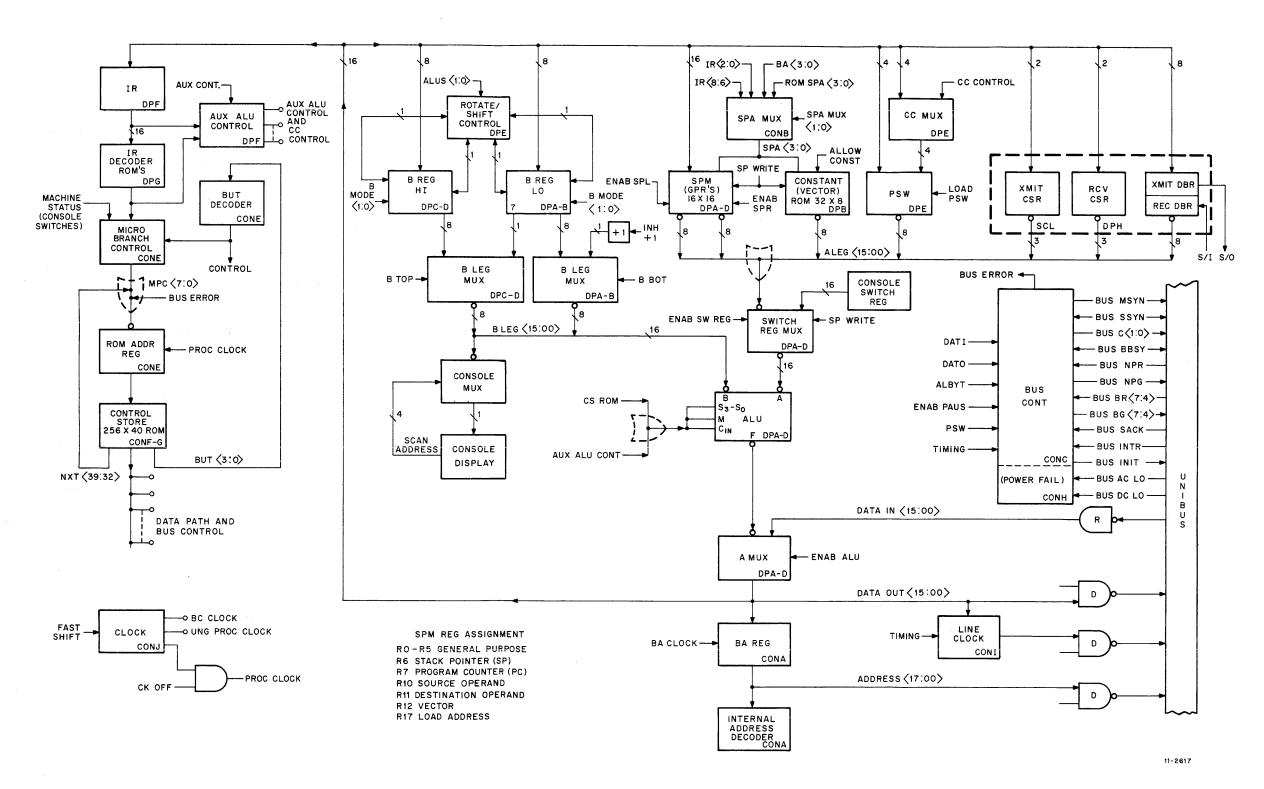

| 4-4        | KD11-B Detailed Block Diagram                                          |        |

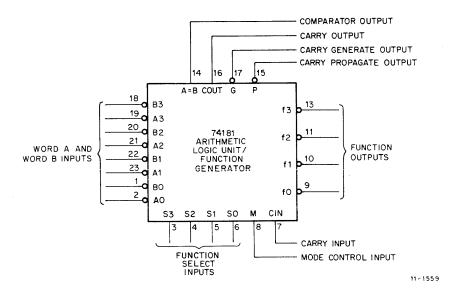

| 4-5        | 74181 Pin and Signal Desginations                                      |        |

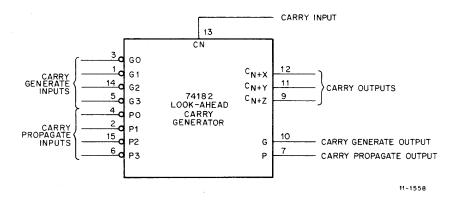

| 4-6        | 74182 Pin and Signal Designations                                      |        |

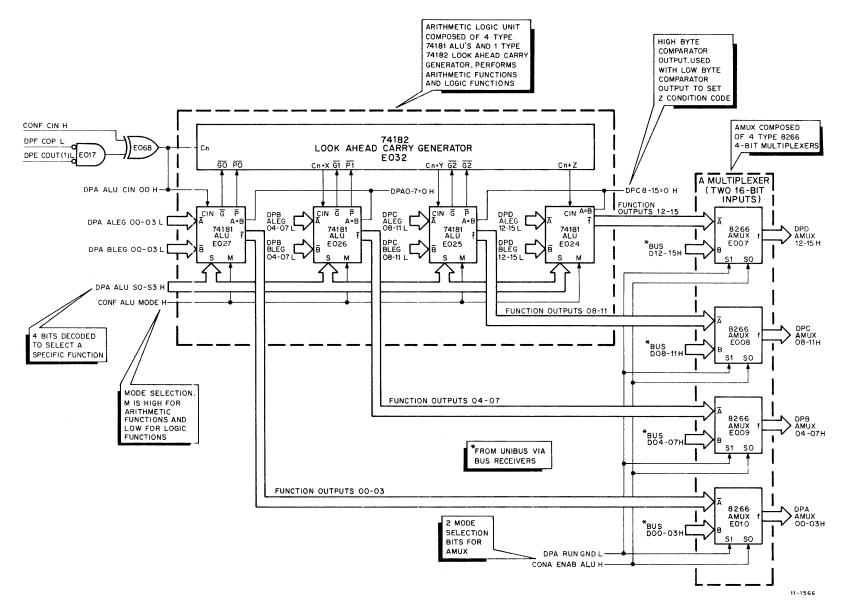

| 4-7        | Arithmetic Logic Unit Block Diagram                                    |        |

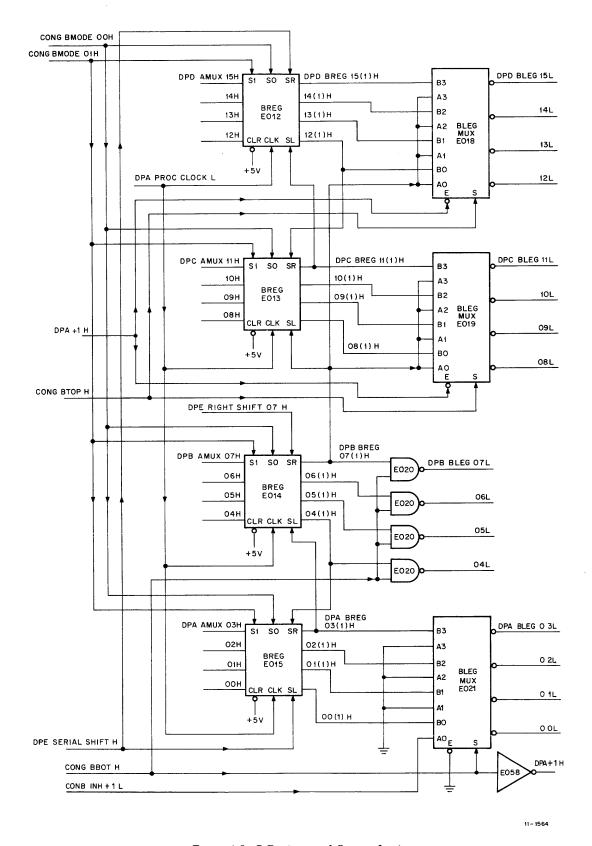

| 4-8        | B Register and Output Logic                                            |        |

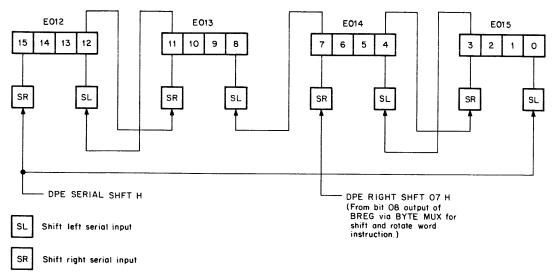

| 4-9        | B Register Shift Signal Inputs                                         |        |

| 4-10       | Byte Format for Shifting Instructions                                  |        |

| 4-11       | Block Diagram and Function Table for Scratch Pad Memory                |        |

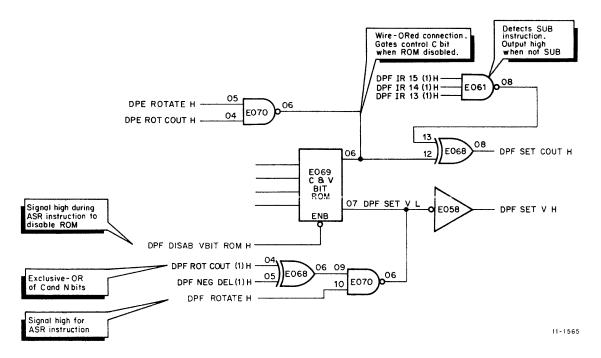

| 4-12       | Logic for Determining C and V Bits (Example Shown for ASR Instruction) | . 4-24 |

| 4-13       | Typical Switch Register Multiplexer                                    |        |

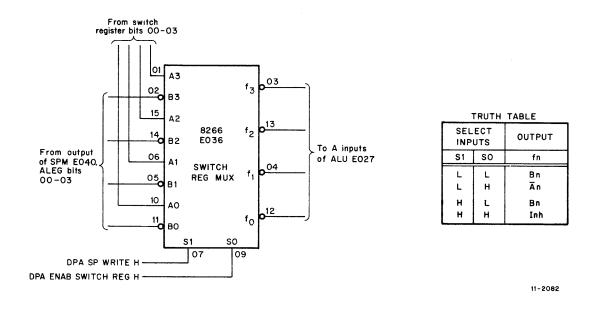

| 4-14       | Console Multiplexer Block Diagram                                      | . 4-27 |

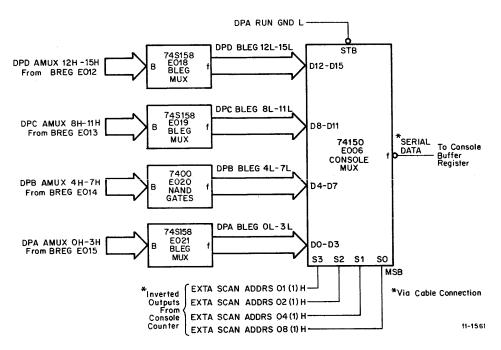

| 4-15       | Processor Clock Timing Diagram                                         | 4-30   |

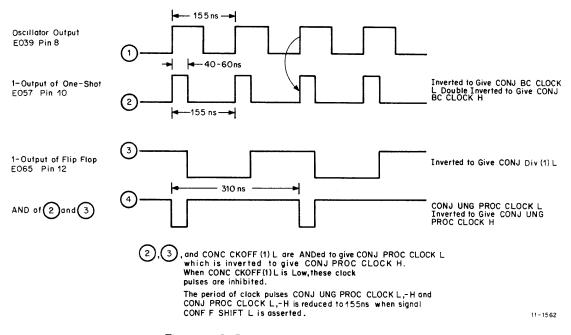

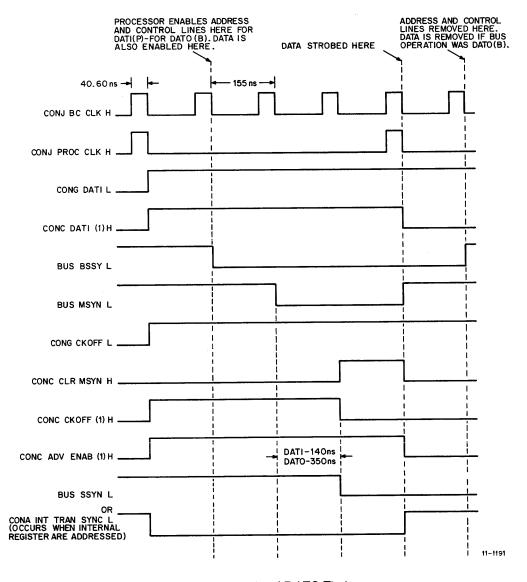

| 4-16       | DATI and DATO Timing                                                   | . 4-33 |

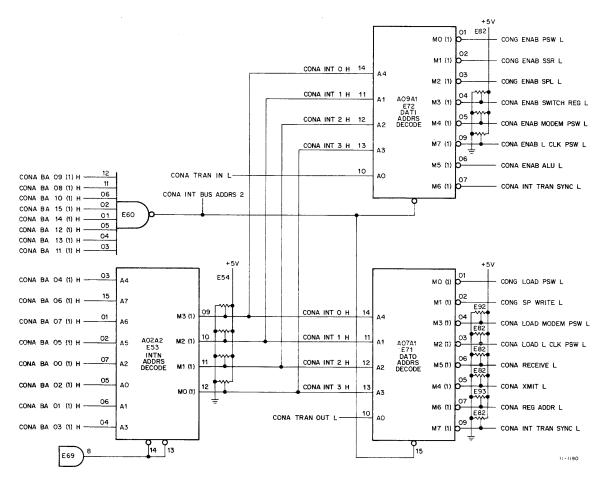

| 4-17       | Unibus Address Decoding                                                | . 4-37 |

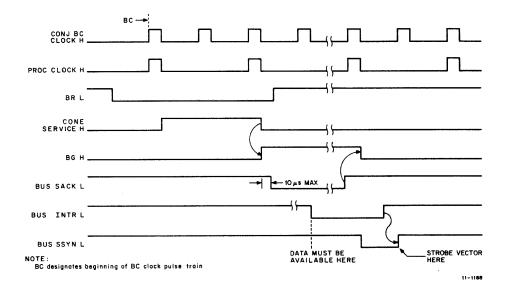

| 4-18       | Bus Request (BR) Timing                                                | . 4-38 |

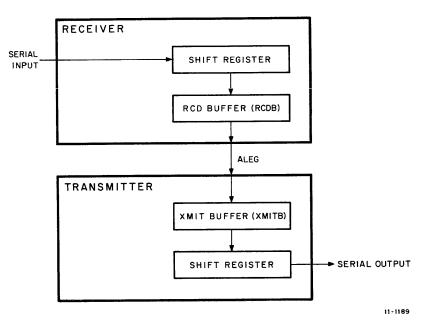

| 4-19       | Double-Buffering Data Flow                                             | . 4-41 |

| 4-20       | SCL Oscillator Schematic and Timing Diagram                            |        |

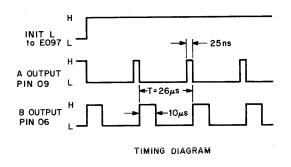

| 4-21       | Baud Selection Logic                                                   |        |

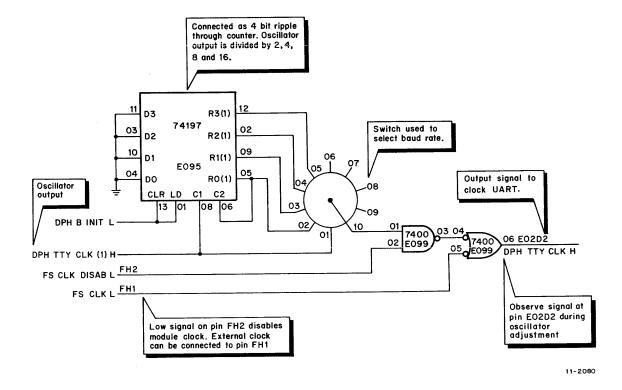

| 4-22       | BUS AC LO and BUS DC LO Timing Diagram                                 |        |

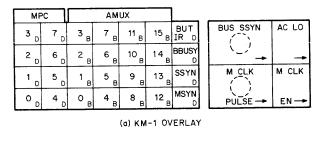

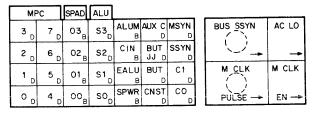

| 5-1        | KM11 Maintenance Module, KD11-B Overlays                               |        |

### **TABLES**

| Table No. | Title                                                            | Page   |

|-----------|------------------------------------------------------------------|--------|

| 1-1       | Related Documents                                                | . 1-1  |

| 2-1       | KD11-B Control Store Fields                                      |        |

| 2-2       | Microprogram Branches (BUT)                                      |        |

| 2-3       | Flow Notation Glossary                                           |        |

| 3-1       | Scan Address Signal Generation                                   |        |

| 3-2       | Counter States                                                   |        |

| 4-1       | ALU Control Signals                                              | . 4-9  |

| 4-2       | Control Store Signals for BLEG Operations                        |        |

| 4-3       | Register Utilization in SPM                                      |        |

| 4-4       | SPM Address Line Signals                                         |        |

| 4-5       | SPAM Input Data Sources                                          |        |

| 4-6       | Processor Status Word Bit Assignments                            |        |

| 4-7       | Effect of E066 Outputs DPG CMP+BIT L, DPG MOVE L, and DPG BYTE L |        |

| 4-8       | Auxiliary Control for Binary and Unary Instructions              |        |

| 4-9       | Unibus Addresses                                                 | . 4-37 |

| 4-10      | Trap Priorities                                                  |        |

| 4-11      | Baud Selection                                                   |        |

| 5-1       | Test Equipment and Tools                                         |        |

| 5-2       | Baud Rate Adjustment                                             |        |

| 5-3       | Engineering Drawing Print List and Functions                     | . 5-4  |

| 5-4       | KM-1 and KM-2 Overlay Designations                               |        |

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual describes the KD11-B Processor, which is the basic component of the PDP-11/05/10 and PDP-11/05S computer systems. The processor is connected to the Unibus as a subsystem and controls time allocation of the Unibus for peripherals, and performs arithmetic and logic operations through instruction decoding and execution. The information contained in this manual pertains primarily to the processor itself.

Table 1-1 lists other manuals that are necessary for a complete understanding of the basic PDP-11/05 or PDP-11/05S system.

Table 1-1

Related Documents

| Title                           | Document<br>Number | Remarks                                                                                                    |

|---------------------------------|--------------------|------------------------------------------------------------------------------------------------------------|

| PDP-11/05/10 Computer<br>Manual | DEC-11-H05AA-B-D   | Describes overall PDP-11/05/10 computer and includes sections on installation, operation, and programming. |

| PDP-11/05S System<br>Manual     | DEC-11-H05SS-A-D   | Describes overall PDP-11/05S system and includes sections on installation, operation, and programming.     |

| BA11-K Mounting Box<br>Manual   | DEC-11-HBKEF-A-D   | Describes power system for KD11-B when it is mounted in the 10-1/2 in. mounting box.                       |

#### 1.2 ORGANIZATION

The discussion of the KD11-B Processor is divided into four major sections: microprogramming (Chapter 2), console description (Chapter 3), KD11-B detailed description (Chapter 4), and KD11-B and console maintenance (Chapter 5).

Chapter 2 discusses the processor first then briefly covers the conventional method of implementing the instruction set. The remainder of the chapter is devoted to a discussion of microprogrammed implementation, the basic microprogram memory, and the structure of the microprogram word.

Chapter 3 provides a general and a detailed description of the console logic. The general description is keyed to the block diagram level, the detailed description covers the theory of operation of the console logic. The function and use of the console controls are discussed in the PDP-11/05S System Manual.

Chapter 4 describes the logic and physical implementation of the KD11-B data path (DP), data path control (DPC), Unibus control, serial communications line (SCL), and the line clock. Extensive use is made of bipolar, medium, and large scale integrated circuits in the processor.

Chapter 5 describes techniques for isolating and repairing failures in the KD11-B and the console. The basic procedures are aimed at differentiating between failures in the processor and the remainder of the computer.

# CHAPTER 2 MICROPROGRAM CONTROL

#### 2.1 INTRODUCTION

This chapter describes the microprogram control implemented in the KD11-B processor. The flow notation used in the microprogram flow section of the prints is described in Paragraph 2.5.1. The difference between microprogram control and conventional control in a computer processor is described in Paragraph 2.2. Paragraph 2.3 describes the KD11-B control store (CS) structure; Paragraph 2.4 describes the technique of branching within microroutines in the CS; and Paragraph 2.5 describes the microprogram flow, including instruction interpretation, Unibus control coordination, interrupts, traps, and console functions.

#### 2.2 MICROPROGRAMMED VERSUS CONVENTIONAL CONTROL

The control section of a conventional computer is a complex collection of specialized logic circuits. These circuits generate the timing signals that constitute the major and minor time states of a machine cycle. During each time state, these control signals configure the data path (DP), determine function performed within the arithmetic/logic units (ALU), influence the Unibus control (BC), etc. Major disadvantages associated with this conventional approach are its complexity, the large amount of logic required, its inflexibility, and difficulty of making modifications.

A microprogrammed processor such as the KD11-B results in a reduction in the amount and complexity of the control logic, while facilitating a systematically implemented and easily modified control section. Basically, a microprogram involves the execution of a sequence of microsteps from the control store (ROMs). Execution of a microstep causes the assertion of a set of control signals specified in the control store word associated with that microstep. By executing appropriate sequences of microsteps (known as a microroutine), the KD11-B can be made to interrupt PDP-11 instructions. Other functions such as console functions, interrupts, and traps are also accomplished by specialized microroutines.

#### 2.3 CONTROL STORE

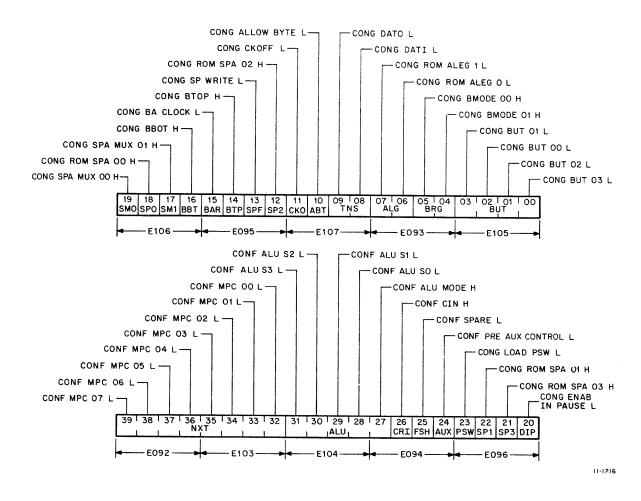

Figure 2-1 shows the format of the KD11-B control store (CS) word. There are 256 such words, each having the same fields. The fields, the possible values they may contain, and the significance of each value are described in Table 2-1. The CS is shown on prints CONF and CONG.

An explanation of the notation will aid in relating the CS word to the reset of the print set. Each field within the CS has been given a name (e.g., BUT, BRG, ALG,...,ALU, NXT). These field names are used throughout documentation of the microprogram.

The signal coming from each bit is named according to the convention used in the print set. Several signals may be associated with a single field (e.g., the BUT field controls four signals: CONG BUT 01 L, CONG BUT 00 L, CONG BUT 02 L, and CONG BUT 03 L).

Figure 2-1 Control Store Word Bit and Field Format

Table 2-1 KDI 1-B Control Store Fields

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BUT   | Branch on microtest. The BUT field has two uses: a) specify microprogram conditional branches, and b) as an encoded miscellaneous field. The values this field can assume are grouped by these two uses.                                                                                                                                                                                                                                         |  |  |

|       | Branching within the microprogram is accomplished by wiring conditional signals with the open-collector outputs of the NXT field of the CS. Each BUT condition has the minimum number of control bits required. This makes the range of branching restrictive, but it minimizes logic (print CONE). Table 2-2 lists the microstep in which each BUT is performed, the possible conditions, and resulting destination of the microprogram branch. |  |  |

|       | Microprogram conditional branches:                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| NON   | No effect                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

# Table 2-1 (Cont) KD11-B Control Store Fields

| Field                                                             |       | Description                                                                                                                                  |  |  |  |

|-------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BUT                                                               | JSRMP | Microprogram branch on JMP or JSR instruction                                                                                                |  |  |  |

| (Cont)                                                            | IRD   | Microprogram branch on results of Instruction Register Decode                                                                                |  |  |  |

|                                                                   | BYT   | Microprogram branch to distinguish: a) byte and non-byte instructions, and b) odd/even byte references                                       |  |  |  |

|                                                                   | DST   | Microprogram branches on destination mode IR (5:3)                                                                                           |  |  |  |

|                                                                   | MOV   | Microprogram branch to distinguish both MOV and MOVB from other instructions                                                                 |  |  |  |

|                                                                   | INT   | Microprogram branch on interrupt to be processed                                                                                             |  |  |  |

|                                                                   | UNY   | Microprogram branch to distinguish unary instructions                                                                                        |  |  |  |

|                                                                   | SW    | Microprogram branch dependent on console switch action                                                                                       |  |  |  |

| NMD<br>SRV                                                        |       | Microprogram branches to distinguish non-modifying instructions (e.g., CMP, TST, etc.)                                                       |  |  |  |

|                                                                   |       | Microprogram branch at end of instruction sequence to determine if any condition requires service before going off to fetch next instruction |  |  |  |

|                                                                   |       | Miscellaneous encoded field:                                                                                                                 |  |  |  |

|                                                                   | CON   | Enable the constants ROM on the A-leg                                                                                                        |  |  |  |

|                                                                   | INI   | Trigger BUS INIT L during the RESET instruction                                                                                              |  |  |  |

|                                                                   | SVS   | Set SSYN on Unibus during the interrupt sequence                                                                                             |  |  |  |

|                                                                   | ENO   | Enable the stack overflow detection logic                                                                                                    |  |  |  |

|                                                                   | IRC   | Clock data into the instruction register                                                                                                     |  |  |  |

| BRG                                                               |       | Control the B register                                                                                                                       |  |  |  |

|                                                                   | П     | Hold, do not modify.                                                                                                                         |  |  |  |

|                                                                   | L     | Load.                                                                                                                                        |  |  |  |

|                                                                   | SR    | Shift right once.                                                                                                                            |  |  |  |

|                                                                   | SL    | Shift left once.                                                                                                                             |  |  |  |

| ALG A-leg control; determines what is enabled onto the A-inputs o |       | A-leg control; determines what is enabled onto the A-inputs of the ALU                                                                       |  |  |  |

# Table 2-1 (Cont) KD11-B Control Store Fields

| Field  |     | Description                                                                                                                  |  |  |  |  |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ALG SP |     | Scratch pad                                                                                                                  |  |  |  |  |

| (Cont) | NUL | Nothing                                                                                                                      |  |  |  |  |

|        | SPR | Low orders eight bits (right half) of the scratch pad                                                                        |  |  |  |  |

|        | PSW | Program Status Word                                                                                                          |  |  |  |  |

| TNS    |     | Initiation of Unibus transfer                                                                                                |  |  |  |  |

|        | NON | No effect                                                                                                                    |  |  |  |  |

|        | I   | Initiate DATI                                                                                                                |  |  |  |  |

|        | O   | Initiate DATO                                                                                                                |  |  |  |  |

|        | IP  | Initiate DATIP                                                                                                               |  |  |  |  |

| ABT    |     | Allow byte reference on current Unibus transfer.                                                                             |  |  |  |  |

|        | NO  |                                                                                                                              |  |  |  |  |

|        | YES |                                                                                                                              |  |  |  |  |

| СКО    |     | Inhibit the processor clock until pending Unibus transfer is complete.                                                       |  |  |  |  |

|        | OFF | No effect                                                                                                                    |  |  |  |  |

|        | ON  |                                                                                                                              |  |  |  |  |

| SPA    |     | Scratch pad address. This field is physically split in the control store word. It is made up of:                             |  |  |  |  |

|        |     | SPA = SP0 = CS (18)<br>SP1 = CS (22)<br>SP2 = CS (12)<br>SP3 = CS (21)                                                       |  |  |  |  |

|        |     | Scratch pad address (R0 through R17)                                                                                         |  |  |  |  |

| SPF    |     | Scratch pad control function                                                                                                 |  |  |  |  |

|        | REA | Scratch pad contents not modified                                                                                            |  |  |  |  |

|        | WRI | Write into scratch pad                                                                                                       |  |  |  |  |

| BLG    |     | B-leg control. Determines what is enabled onto the B-input of the ALU. This field is physically split in control store word. |  |  |  |  |

## Table 2-1 (Cont) KD11-B Control Store Fields

| Field         |     | Description                                                                                        |  |  |

|---------------|-----|----------------------------------------------------------------------------------------------------|--|--|

| BLG<br>(Cont) |     | BLG = BTP (B Top - Upper Byte) = CS (14) BBT (B Bottom - Lower Byte) = CS (16)                     |  |  |

|               | BRG | B register                                                                                         |  |  |

|               | SEX | B register sign extended. Bit 7 of the B register is propagated from bit 7 to bit 15.              |  |  |

|               | +1  | The constant +1                                                                                    |  |  |

| BAR           |     | Bus Address Register Control                                                                       |  |  |

|               | Н   | Hold, do not modify.                                                                               |  |  |

|               | L   | Load.                                                                                              |  |  |

| SAM           |     | Scratch pad address multiplexer control. This field is physically split in the control store word. |  |  |

|               |     | SAM = SM0 (19)<br>SM1 (17)                                                                         |  |  |

|               | ROM | Scratch pad address taken from control store word (see SPA field)                                  |  |  |

|               | IRS | Scratch pad address taken from source register bits of Instruction Register, IR (8:6).             |  |  |

|               | IRD | Scratch pad address taken from destination register bits of Instruction Register, IR (2:0).        |  |  |

|               | BAR | Scratch pad address taken from Bus Address Register low order three bits, BA (2:0).                |  |  |

| PSW           |     | Program Status Word control                                                                        |  |  |

|               | Н   | Hold                                                                                               |  |  |

|               | L   | Load                                                                                               |  |  |

| AUX           |     | Auxiliary ALU control enabled                                                                      |  |  |

|               | OFF |                                                                                                    |  |  |

|               | ON  |                                                                                                    |  |  |

| CRI           |     | Enable carry in to ALU                                                                             |  |  |

|               | OFF |                                                                                                    |  |  |

|               | ON  |                                                                                                    |  |  |

Table 2-1 (Cont)

KD11-B Control Store Fields

| Field  | Description                                                                   |  |  |  |  |

|--------|-------------------------------------------------------------------------------|--|--|--|--|

| ALU    | ALU function                                                                  |  |  |  |  |

| AL     | A logical                                                                     |  |  |  |  |

| AA     | A arithmetic                                                                  |  |  |  |  |

| AB     | A and B                                                                       |  |  |  |  |

| ABBAR  | A and ones complement of B                                                    |  |  |  |  |

| ZERO   | Output zero                                                                   |  |  |  |  |

| A OR B | A or B                                                                        |  |  |  |  |

| BL     | B logical                                                                     |  |  |  |  |

| A + B  | A plus B                                                                      |  |  |  |  |

| AXORB  | A exclusive or B                                                              |  |  |  |  |

| A-B-1  | A minus B minus 1                                                             |  |  |  |  |

| BBAR   | 1's complement of B  Output the constant minus one                            |  |  |  |  |

| -1     |                                                                               |  |  |  |  |

| A-1    | A minus one                                                                   |  |  |  |  |

| ABAR   | 1's complement of A                                                           |  |  |  |  |

| ASL    | Arithmetic shift B left                                                       |  |  |  |  |

| ROL    | Rotate B left  These are used during shift and rotate instructions to control |  |  |  |  |

| ASR    | Arithmetic shift B right  the serial shift inputs to the B register.          |  |  |  |  |

| ROR    | Rotate B right                                                                |  |  |  |  |

A field may contain any one of a number of different alternative bit patterns. To facilitate microprogramming, these alternatives have been given symbolic names, making it possible to work with the microprogram at a symbolic level rather than in binary. For example (Table 2-1), one of the alternative values that can be assigned to the ALU field is OR (A or B). This value corresponds to a bit pattern of 01001 [CS (37:33) = 01001].

The data word output from the CS is determined by the contents of the MPC registers (E111 and E101 shown on print CONF).

#### 2.4 BRANCHING WITHIN MICROROUTINES

A microroutine is composed of a sequence of microsteps. Every microstep specifies the location of the next microstep in a sequence, namely, the NXT field. During the execution of a microstep, the signals resulting from the NXT field are loaded into the MPC (microprogram counter). The MPC specifies the location from which the next microstep will be executed (print CONF). Conditional branching within a microroutine is accomplished by wire-ORing signals into those signals coming from the NXT field, while they are being loaded into the MPC. Each branch condition controls the minimum number of bits required. This restricts the range of branching, but it minimizes the logic (print CONE). This provides control for all the bits in the MPC. Table 2-2 shows the location of each microcode branch, the destination, and associated conditions.

In general, microsteps are not executed from numerically sequential locations. This extra degree of complexity (and an extra eight bits in each CS word to specify the NXT location) enables the minimization of logic.

Table 2-2 Microprogram Branches (BUT)

| BUT                | Source      | Destination       | Comment                         |

|--------------------|-------------|-------------------|---------------------------------|

| IRD (IR decode)    | F-5         | S0-1 through S7-1 | All double operand instructions |

|                    |             | D0-1 through D7-1 | Single operand instructions     |

|                    |             | B-1               | Branch, change PC               |

|                    |             | B2-2D             | Branch, PC unchanged            |

|                    |             | MCC-1             | Set or 0 clear condition codes  |

|                    |             | R1-1              | RTS                             |

|                    |             | R2-1              | RTI                             |

|                    |             | W-1               | WAIT                            |

|                    |             | Ĥ-1               | HALT                            |

|                    |             | ET-1              | EMT                             |

|                    |             | BT-1              | Break Point Trap                |

|                    |             | IT-1              | IOT                             |

|                    |             | T-1               | Trap                            |

|                    |             | RT-1              | Reserved instruction            |

|                    |             | RST-1             | RESET                           |

| DST (destination)* | S0-2, SBE-2 | D0-1 through D7-1 |                                 |

|                    | CCM-2       | CC-1              | Clear condition codes           |

|                    |             | SC-1              | Set condition codes             |

<sup>\*</sup>Always has a branching destination (i.e., NXT field always modified).

Table 2-2 (Cont) Microprogram Branches (BUT)

| BUT                 | Source                                                                                                 | Destination | Comment                                 |

|---------------------|--------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|

| BYT (byte)          | S0-1                                                                                                   | SBE-1       | Byte source data (Mode 0)               |

|                     | S1-2                                                                                                   | SBE-1       | Even byte source data                   |

|                     |                                                                                                        | SBO-1       | Odd byte source data                    |

| MOVE                | D0-1                                                                                                   | DBO-1       | Byte instruction other than MOVE        |

|                     |                                                                                                        | MB-0        | MOVB instruction (BYTE)                 |

|                     |                                                                                                        | D0-3A       | MOV instruction (NOT BYTE)              |

| NMD (non-modifying) | D0-3, D0-3A                                                                                            | B2-2A       | Non-modifying instruction TST, CMP, Bit |

|                     | D1-4                                                                                                   | B2-2B       |                                         |

|                     | DBO-2                                                                                                  | B2-2        |                                         |

|                     | DO-10                                                                                                  | B2-2C       |                                         |

| SRV (service)       | B-3, B2-2<br>B2-2A, B2-2B<br>B2-2C, B2-2D,<br>CC-1, CS-3,<br>D0-4, DB0-3,<br>J1-2, J2-8,<br>MB-2, SC-1 |             | In order of priority highest to lowest  |

|                     |                                                                                                        | BT-1        | T-bit trap                              |

|                     |                                                                                                        | ERT-IA      | Stack overflow trap                     |

|                     |                                                                                                        | PF-1        | Power fail                              |

|                     |                                                                                                        | BG-1        | BR 7 (bus request level)                |

|                     |                                                                                                        | BG-1        | BR 6                                    |

|                     |                                                                                                        | LC-1        | Internal line clock                     |

|                     |                                                                                                        | BG-1        | BR 5                                    |

|                     |                                                                                                        | BG-1        | BR 4                                    |

|                     |                                                                                                        | URTR        | UART Receive                            |

|                     |                                                                                                        | URTX        | UART Transmit                           |

Table 2-2 (Cont) Microprogram Branches (BUT)

| BUT             | Source                    | Destination | Comment                                                               |

|-----------------|---------------------------|-------------|-----------------------------------------------------------------------|

| SRV             |                           | H-1         | Console STOP                                                          |

| (Cont)          | v                         | F-1         | None of the above                                                     |

|                 |                           | W-1         | When executing WAIT instruction, LOOP ON W-1 instead of going to F-1. |

| SW (switch)     | H-2                       | CS-1        | Start                                                                 |

|                 | ,                         | CCS-1       | Continue                                                              |

|                 |                           | CE1-1       | Examine 1st.                                                          |

|                 |                           | CE2-1       | Examine                                                               |

|                 |                           | CD1-1       | Deposit 1st.                                                          |

|                 |                           | CD2-1       | Deposit                                                               |

|                 |                           | CL-1        | Load                                                                  |

|                 |                           | H-2         | None                                                                  |

|                 |                           | CE1-1       | Loop until examine is released.                                       |

| INT (interrupt) | BG-1                      | INT-1       | Interrupt service                                                     |

| JSRMP           | D1-1, D2-3,<br>D3-5, D6-5 | J1-1        | JMP instruction mode of operation to change PC.                       |

|                 | D6-5                      | J2-1        | JSR instruction                                                       |

| INITIALIZE      | RST-1                     |             | Initialize computer RESET instruction.                                |

| UNY (unary)     | D0-2                      | ERT-1       | JMP or JSR Mode 0 - illegal instruction                               |

|                 |                           | SB1-1       | SWAB                                                                  |

|                 |                           | U1-1        | Other unary                                                           |

|                 | D1-3                      | SB2-1       | SWAB                                                                  |

|                 |                           | U2-1        | Other unary                                                           |

|                 | DB0-1                     | U3-1        | Unary other than JMP, JSR, or SWAB                                    |

Table 2-2 (Cont) Microprogram Branches (BUT)

| BUT           | Source | Destination | Comment                            |

|---------------|--------|-------------|------------------------------------|

| UNY<br>(Cont) | DE-1   | U5-1        | Unary other than JMP, JSR, or SWAB |

|               | DO-9   | U4-1        | Unary other than JMP, JSR, or SWAB |

| NON (none)    |        |             | No branch test                     |

#### 2.5 MICROPROGRAM FLOW

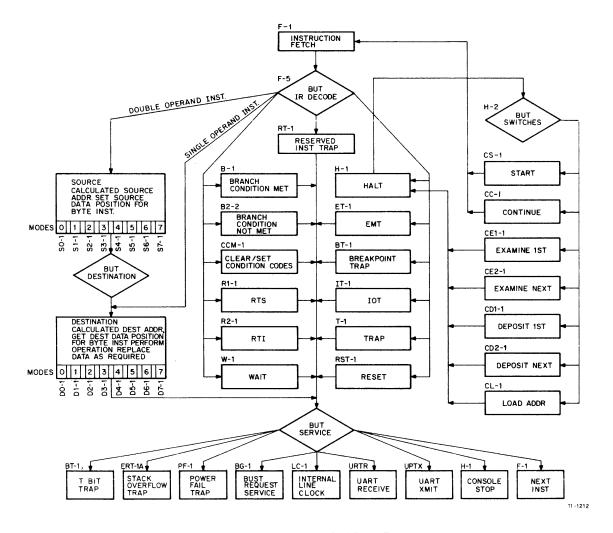

The microprogram flow chart is shown in full detail in engineering drawing K-MP-KD11-B-1. Figure 2-2 is a simplified flow that provides an overview and aids in using the detailed flow. No attempt is made in this manual to trace through each path of the microcode. An explanation of the detailed flow notation is provided along with examples to illustrate instruction interpretation, interrupts and traps, and console functions.

Figure 2-2 KD11-B Simplified Flow Diagram

#### 2.5.1 Flow Chart Notation

Figure 2-3 illustrates an excerpt from the microprogram flow section of the prints. Notice that the listing is grouped into microroutines (source mode 0 through mode 3); these microroutines start with an identifying comment, the first character of which (disregarding the LOC and NXT columns) is an asterisk. Other comment lines begin with a slash.

| LOC      | NXT      | * SOURCE MODE 0 (REGISTER), GET SOURCE DATA                   |  |  |  |

|----------|----------|---------------------------------------------------------------|--|--|--|

|          |          | / GET TO S0-1 FROM F-5 VIA BUT IR DECODE IR 11:9 = 0          |  |  |  |

| 201      | 007      | SO-1 B R[S]; BUT BYTE                                         |  |  |  |

|          | 204      | / IF BYTE INST GOTO SBE-1 (MUST BE EVEN BYTE)                 |  |  |  |

| 007      | 001      | S0-2 R[10] B; BUT DESTINATION                                 |  |  |  |

|          |          | / IF IR 5:3 = 0 GOTO D0-1<br>/ = 1 D1-1                       |  |  |  |

|          |          | 1                                                             |  |  |  |

|          |          | !                                                             |  |  |  |

|          |          | $ = 3 \qquad D3-1 $                                           |  |  |  |

|          |          | / = 4 D4-1                                                    |  |  |  |

|          |          | $ = 5 \qquad D5-1 $                                           |  |  |  |

|          |          | $\begin{array}{ccc} & & & & & & & \\ & & & & & & \\ & & & & $ |  |  |  |

|          |          | / = 7 D7-1                                                    |  |  |  |

| LOC      | NXT      | * SOURCE MODE 1 (REG. DEFERRED) GET SOURCE DATA               |  |  |  |

| LOC      | 11/21    | / GET TO S1-1 FROM F-5 VIA BUT IR DECODE IR 11:9              |  |  |  |

| 203      | 244      | SI-1 BA R[S]; DATI; CKOFF; ALBYT                              |  |  |  |

| 203      | 211      | / GET TO S1-2 FROM S2-3 VIA GOTO                              |  |  |  |

|          |          | / S3-5 "                                                      |  |  |  |

|          |          | ' S6-5 "                                                      |  |  |  |

| 244      | 007      | S1-2 B UNIBUS DATA; BUT BYTE; GOTO S0-2                       |  |  |  |

| <b>5</b> | 00.      | / IF ODD BYTE GOTO SBO-1                                      |  |  |  |

|          |          | / IF EVEN BYTE GOTO SBE-1                                     |  |  |  |

|          |          | / IF NOT BYTE FALL THROUGH TO S0-2                            |  |  |  |

|          |          |                                                               |  |  |  |

| LOC      | NXT      | * SOURCE MODE 2 (AUTO-INC.) GET SOURCE DATA                   |  |  |  |

|          |          | / GET TO S2-1 FROM F-5 VIA BUT IR DECODE IR 11:9 = 2          |  |  |  |

| 205      | 301      | S2-1 BA R[S]; DATI; ALBYT                                     |  |  |  |

| 301      | 014      | S2-2 B R[S]+1+BYTE. BAR                                       |  |  |  |

|          |          | / GET TO S2-3 FROM S4-1 VIA GOTO                              |  |  |  |

| 214      | 244      | S2-3 R[S] 8; CKOFF; GOTO S1-2                                 |  |  |  |

| LOC      | NXT      | * SOURCE MODE 3 (AUTO-INC DEFERRED) GET SOURCE DATA           |  |  |  |

| 200      | . 11 8 4 | / GET TO S3-1 FROM F-5 VIA BUT IR DECODE IR 11:9 = 3          |  |  |  |

| 207      | 016      | S3-1 BA R[S]; DATI (MUST BE AN EVEN ADDRESS HERE)             |  |  |  |

| 216      | 017      | S3-2 B R[S]+2                                                 |  |  |  |

|          |          | E 3.                                                          |  |  |  |

Figure 2-3 Excerpt from Microprogram Flow (KMP-KDL-B-1)

All microsteps have mnemonic names such as S0-1 (source mode 0, step 1), S2-2 (source mode 2, step 2), etc. A microroutine will often weave back and reuse part of another. For example, the source mode 1 routine weaves back into the source mode 0 routine by the GOTO S0-2 in S1-2 (Figure 2-3).

To the left of every microstep is the location of that step in the CS (in octal) and the contents of the NXT field. Observe the microprogram counter (MPC) while single stepping through the microprogram. The LOC and NXT columns provide useful information relating to the path taken by the microprogram.

The flow is well commented and should be self-explanatory. Table 2-3 is a useful glossary of flow notation.

Table 2-3 Flow Notation Glossary

| Designation | Definition                                                                                       |  |  |

|-------------|--------------------------------------------------------------------------------------------------|--|--|

| BA          | Bus Address Register                                                                             |  |  |

| <b>←</b>    | Assignment operator                                                                              |  |  |

| ;           | Separator                                                                                        |  |  |

| DATI        | Initiate DATI operation on Unibus.                                                               |  |  |

| +           | Plus, the arithmetic operator                                                                    |  |  |

| PC          | Program Counter = R 7                                                                            |  |  |

| CKOFF       | Set the Clock Off bit of the control store.                                                      |  |  |

| В           | B-leg register                                                                                   |  |  |

| IR          | Instruction Register                                                                             |  |  |

| B Sex       | B-leg register sign extended (bit 7 repeated in bits 8 through 15)                               |  |  |

| R [S]       | Scratch Pad Register specified by the source portion of the current instruction [IR (8:6)].      |  |  |

| R [D]       | Scratch Pad Register specified by the destination portion of the current instruction [IR (2:0)]. |  |  |

| R [n]       | Scratch Pad Register n specified by the control ROM                                              |  |  |

| BUT         | Branch on microtest                                                                              |  |  |

| ALBYT       | Allow byte Unibus reference                                                                      |  |  |

| BYTE.BAR    | A signal indicating the absence of a byte in instruction                                         |  |  |

| ENABOVER    | Enable the stack overflow detection logic (working BUT)                                          |  |  |

| DATO        | Initiate DATO operation on Unibus.                                                               |  |  |

| DATIP       | Initiate DATIP operation on Unibus.                                                              |  |  |

| INIT        | Initialize the logic (working BUT).                                                              |  |  |

#### Table 2-3 (Cont) Flow Notation Glossary

| Designation | Definition                                                                                                                         |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SVS         | Set slave sync (working BUT).                                                                                                      |  |  |  |  |

| IRC         | Clock the Instruction Register (working BUT).                                                                                      |  |  |  |  |

| K [n]       | That location of the constants chip (on the data path A-leg) containing the value n.                                               |  |  |  |  |

| R [10] OP B | ALU function determined by the auxiliary ALU control logic as a function of the instruction currently in the Instruction Register. |  |  |  |  |

| дото x      | NXT field is to contain the address of X. Unconditional GOTO.                                                                      |  |  |  |  |

To illustrate the interpretation of PDP-11 instructions, the execution of a CMP instruction is traced through the microcode. The machine is in the RUN state (i.e., the machine is executing instructions) and the instruction is located in memory location 1000.

| Location | Assembler Symbolic | Octal  |

|----------|--------------------|--------|

| 1000     | CMP #15, CHAR      | 022767 |

| 1002     |                    | 000015 |

| 1004     |                    | 000100 |

| •        |                    |        |

| •        |                    |        |

| 1106     | CHAR: WORD 0       |        |

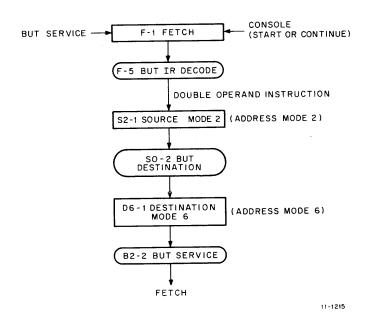

This instruction compares the literal 15 to the contents of CHAR and sets the condition code accordingly. Source mode is immediate (mode 2, register 7 = PC) and destination mode is relative (mode 6, register 7 = PC). Figure 2-4 shows the simplified flow for the CMP example.

Figure 2-4 CMP #15, CHAR (022767), Simplified Flow Diagram

First the instruction is fetched from memory (microsteps F-1 through F-5). This is the same fetch microroutine used to get each instruction from memory and update the PC.

| Location | NXT | Microstep<br>Name | Action                      | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-----|-------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 062      | 053 | F-1               | BA ← PC: DATI               | /Load the Bus Address Register (BA) with<br>the contents of the PC (R7) and initiate a<br>DATI by the Unibus control (BC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 053      | 365 | F-2               | B ← PC+2                    | /Load the B register with the contents of the PC+2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 365      | 364 | F-3               | PC ← B; CKOFF               | /Update the PC. CKOFF inhibits execution of the next microstep until the pending Unibus transfer (DATI, initiated in F-1) is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 364      | 061 | F-4               | B, IR ← UNIBUS DATA         | /Load the data from the Unibus (instruction fetched from memory) into the B register and Instruction Register (IR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 061      | 001 | F-5               | B ← B SEX; BUT<br>IR DECODE | /Sign extend the low order eight bits of the copy of the instruction in the B register (used in branch instruction interpretation) and branch on microtest (BUT) determined by the IR decode logic. Note that NXT (F-5) = 1 which is the CS location of the RE-SERVED instruction microroutine. If the IR decode logic does not recognize the instruction, no signals are wire-ORed into the MPC and the RESERVED instruction microroutine (RT-1) is executed by the microprogram. In this example, CMP is recognized (by the IR decode logic) and 204 is wire-ORed with NXT (F-5 = 1) to cause the MPC to be loaded with 205, the location of the microroutine which operates on source mode 2 (S2-1). |

Since the instruction is of the double operand group, the next step is to get the source data. Source mode 2 is autoincrement. (Autoincrement implies one level of deferred addressing.) When used with R7 (the PC), it becomes an immediate mode.

| Location | NXT | Microstep<br>Name | Action                   | Comment                                                                                                                                                                                                                                                       |

|----------|-----|-------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 205      | 301 | S2-1              | BA←R [S];<br>DATI; ALBYT | /Load the BA with the contents of the register specified by IR (08:06). The register will contain the location of the source data (1002) in this example. Initiate a Unibus DATI to actually get the data. ALBYT will allow an odd Unibus transfer, if the IR |

| Location | NXT | Microstep<br>Name | Action                         | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     |                   |                                | contains a byte instruction and the BA contains an odd address. Without the ALBYT, a Unibus transfer that addresses an odd BA results in a bus error (Paragraph 2.3).                                                                                                                                                                                                                                                                                                            |

| 301      | 014 | S2-2              | B←R [S] +1+<br>BYTE.BAR        | /For byte instructions, the autoincrement is by one, for non-byte instructions, auto-increment is by two. BYTE BAR indicates that BLG (S2-2) = +1, and this signal is conditioned by the logic, such that it is true (+1) only when the IR does not contain a byte instruction. So actually, R [S] is on the A-leg of the ALU, CARRY IN is enabled, and the +1 constant (enabled only if the IR does not contain a byte instruction) is on the B-leg. The ALU function is A + B. |

| 014      | 244 | S2-3              | $R[S] \leftarrow B;$           | /Update the register which is to be auto-incremented. Inhibit the processor clock until the DATI initiated in S2-1 is complete. From here, the microroutine is woven back into S1-2 [i.e., NXT (S2-3) = S1-2].                                                                                                                                                                                                                                                                   |

| 244      | 007 | S1-2              | B ← UNIBUS DATA;               | /Load the source data which has come in from memory into the B register. The microcode at this point joins the microroutine associated with source mode 0 (S0-2). Not a byte instruction, so go to S0-2.                                                                                                                                                                                                                                                                         |

| 007      | 001 | S0-2              | R [10] ← B;<br>BUT DESTINATION | /Source data is stored in the scratch pad register, R [10], while the destination data is retrieved. BUT DESTINATION will cause a microcode branch dependent on IR (3:5). In this case, the destination mode of 6 will cause 114 to be wire-ORed into the NXT (S0-2) = 1, such that the MPC will be loaded with 115 = LOC (D6-1).                                                                                                                                                |

The microroutine starting in D6-1 will get the destination data and perform the operation indicated by the OP code of the instruction. Mode 6, when used with the PC, requires that the index contained in the word currently pointed to by the PC be added to the updated PC (address of the index word plus two) to get the location of the source data.

| Location | NXT | Microstep<br>Name | Action                | Comment                                                          |

|----------|-----|-------------------|-----------------------|------------------------------------------------------------------|

| 115      | 075 | D6-1              | BA ← PC; DATI         | /Initiate the Unibus transfer to get the index word from memory. |

| 075      | 077 | D6-2              | $B \leftarrow PC + 2$ | /Prepare to update PC to next word.                              |

| Location | NXT | Microstep<br>Name | Action                                                    | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 077      | 057 | D6-3              | PC ← B; CKOFF                                             | /Update the PC and inhibit the processor clock until the Unibus DATI initiated in D6-1 is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 057      | 300 | D6-4              | B ← UNIBUS DATA                                           | /Receive the index word into the B register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 300      | 200 | D6-5              | B, BA ← B+R (D); DATI; BUT JSRMP; ALBYT; CKOFF; GOTO D1-2 | /The actual location of the destination data is formed by adding the index (in the B register) to the destination register [IR (2:0)], which is the PC in the example. This address is loaded into the BA, and a DATI is issued to retrieve the data from memory. As in S2-1, ALBYT makes odd byte Unibus transfers legal. BUT JSRMP involves a collection of logic which examines the contents of the IR to see if the instruction is a JMP or JSR. If either of these instructions are present, the appropriate bit is wire-ORed with NXT (D6-5) = D1-2 into the MPC, such that the MPC is loaded with J1-1 or J2-1, respectively for JMP or JSR instruction. In the example, neither of these instructions are present and the MPC is loaded with NXT (D6-5) = D1-2. CKOFF inhibits the processor clock until the DATI initiated in this microstep is complete. Note that this is the first time in this example that memory reference has not been overlapped with microprograms. |

| 200      | 210 | D1-2              | D ← UNIBUS DATA;<br>BUT BYTE                              | /Receive the destination data from memory. If the instruction had been a byte instruction (e.g., CMPB), the microprogram would be diverted to D0-1 (for odd byte address) to get the byte operand into the right half of the B register. This is not the case in this example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 210      | 143 | D1-3              | R [11] ← B;<br>BUT UNARY                                  | /It is at this point in the microroutine that a branch occurs for unary instructions (e.g., SWAB, CLR, COM, etc.). Unary instructions would have caused the BUT IR DECODE done in F-5 to take the appropriate destination microroutine (there is no source field in a unary instruction). R [11] is used in unary instruction interpretation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |