## KB11-A,D central processor unit maintenance manual

digital equipment corporation · maynard. massachusetts

1st Edition, April 1972

2nd Printing (Rev), July 1972

3rd Printing, October 1972

4th Printing, February 1973

5th Printing, July 1973

6th Printing (Rev), December 1973

7th Printing, May 1974

8th Printing, September 1974

9th Printing (Rev), August 1976

## Copyright © 1972, 1973, 1974, 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

## CONTENTS

|           |                                                        | Page       |

|-----------|--------------------------------------------------------|------------|

| CHAPTER 1 | INTRODUCTION                                           |            |

| 1.1       | GENERAL                                                | 1 1        |

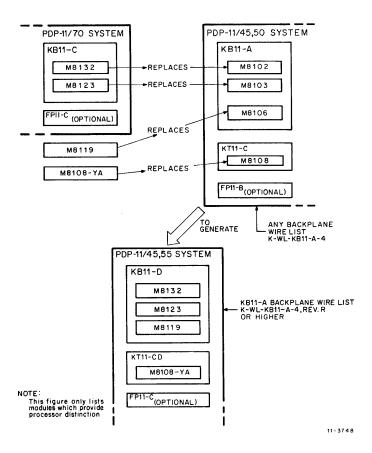

| 1.2       | KB11-D vs. KB11-A                                      | . 1-1      |

| 1.3       | RELATED DOCUMENTS                                      | . 1-1      |

| CHAPTER 2 | GENERAL DESCRIPTION                                    | . 1-2      |

| 2.1       |                                                        |            |

| 2.1.1     |                                                        | 2-1        |

| 2.1.2     |                                                        | 2-3        |

| 2.2       | A Virtual Machine System                               | 2-3        |

| 2.2.1     | FUNCTIONAL DESCRIPTION                                 | 2-4        |

| 2.2.2     | Data Manipulation                                      | 2-4        |

| 2.2.3     | Transferring Data                                      | 2-5        |

| 2.2.4     | Handling Instructions                                  | 2-5        |

| 2.2.1     | Handling Asynchronous Conditions                       | 2-6        |

| CHAPTER 3 | CONCEPTS                                               |            |

| 3.1       | MICROPROGRAMMING                                       | 2 1        |

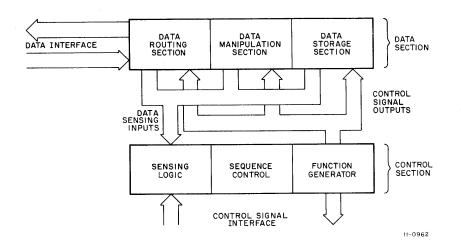

| 3.1.1     | Digital Computer Description                           | 3-1<br>3-1 |

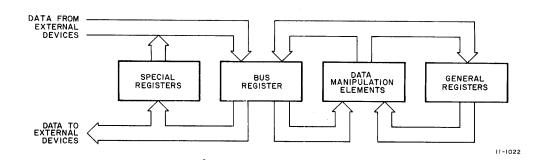

| 3.1.2     | The Data Section                                       | 3-1        |

| 3.1.2.1   | The Data Storage Section                               | 3-2<br>3-2 |

| 3.1.2.2   | The Data Manipulation Section                          | 3-2        |

| 3.1.2.3   | The Data Routing Section                               | 3-3<br>3-3 |

| 3.1.2.4   | The Data Section in the KB11-A, D                      | 3-3<br>3-3 |

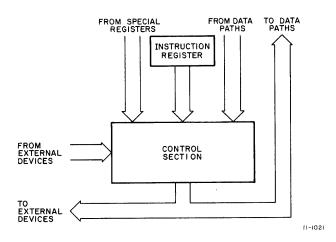

| 3.1.3     | The Control Section                                    | 3-3<br>3-3 |

| 3.1.3.1   | The Sequence Control Section                           | 3-3<br>3-3 |

| 3.1.3.2   | The Function Generator                                 | 3-3<br>3-3 |

| 3.1.3.3   | The Sensing Logic                                      |            |

| 3.1.3.4   | The Control Section in the KB11-A, D                   | 3-3<br>3-3 |

| 3.1.4     | Microprogramming in the Control Section Implementation | 3-3<br>3-4 |

| 3.1.4.1   | Conventional Implementation                            | 3-4<br>3-4 |

| 3.1.4.2   | Microprogrammed Implementation                         | 3-4        |

| 3.2       | PARALLEL OPERATION (PIPELINING)                        | 3-5        |

| 3.3       | VIRTUAL MACHINES                                       | 3-6        |

| 3.3.1     | Mapping                                                |            |

| 3.3.2     | Resource Management                                    | 3-7        |

| 3.3.2.1   | Processor Management                                   | 3-8        |

| 3.3.2.2   | Memory Management                                      | 3-8        |

| 3.3.2.3   | Memory Use Statistics                                  | 3-8        |

| 3.3.3     | Communication                                          | 3-9        |

| 3.3.3.1   | Context Switching                                      | 3-9        |

| 3.3.3.2   | Inter-Program Data Transfers                           |            |

| 3.3.3.3   | Returning to the Previous Context                      | 3-10       |

| 3.3.4     | Protection                                             | 3.11       |

| 3.3.4.1   | Separate Address Spaces                                | 3-11       |

| 3.3.4.2   | Access Modes                                           | 3.11       |

| 3.3.4.3   | Privileged Instructions                                | 3-12       |

| 3.4       | RE-ENTRANT AND RECURSIVE PROGRAMMING                   | 3-12       |

| 3.4.1     | Recursive Functions                                    | 3-12       |

|           |                                               | Page   |

|-----------|-----------------------------------------------|--------|

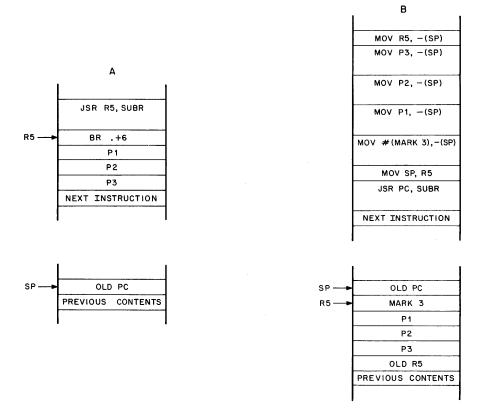

| 3.4.2     | Use of a Stack in Recursive Routines          | 3-12   |

| 3.4.3     | Re-Entrant Functions                          | 3-13   |

| 3.4.4     | Indexed Addressing of Parameters              | 3-13   |

| 3.4.5     | Separate Stack and Index Pointers             | . 3-14 |

| 3.4.6     | Subroutine Call Compatibility                 | . 3-14 |

| 3.4.7     | The MARK Instruction                          | . 3-15 |

| 3.5       | PROCESSOR STATUS OPERATIONS                   | . 3-16 |

| 3.5.1     | Current Processor Mode                        | 3-16   |

| 3.5.2     | Previous Processor Mode                       | . 3-16 |

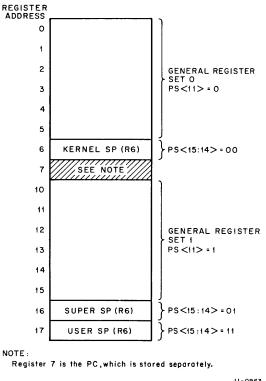

| 3.5.3     | Resister Set Selection                        | . 3-17 |

| 3.5.4     | Processor Priority                            | . 3-17 |

| 3.5.4.1   | Device Priorities                             | . 3-18 |

| 3.5.4.2   | Program Priorities                            | . 3-18 |

| 3.5.4.3   | Programmed Interrupt Requests                 | . 3-18 |

| 3.5.5     | The Trace Bit                                 | . 3-18 |

| 3.5.6     | The Condition Codes                           | . 3-18 |

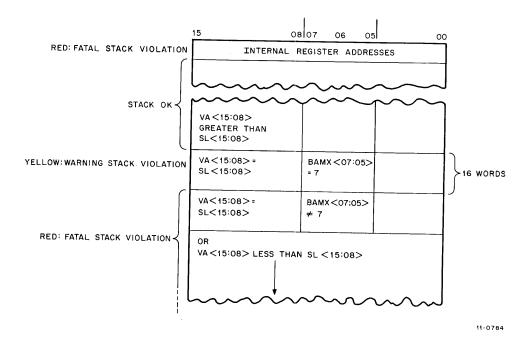

| 3.6       | STACK LIMIT PROTECTION                        | . 3-19 |

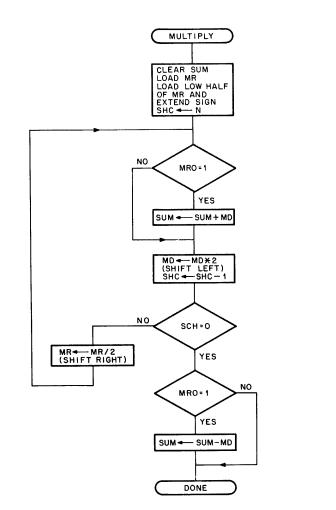

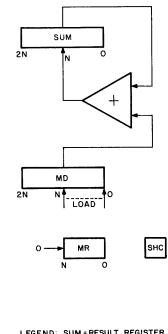

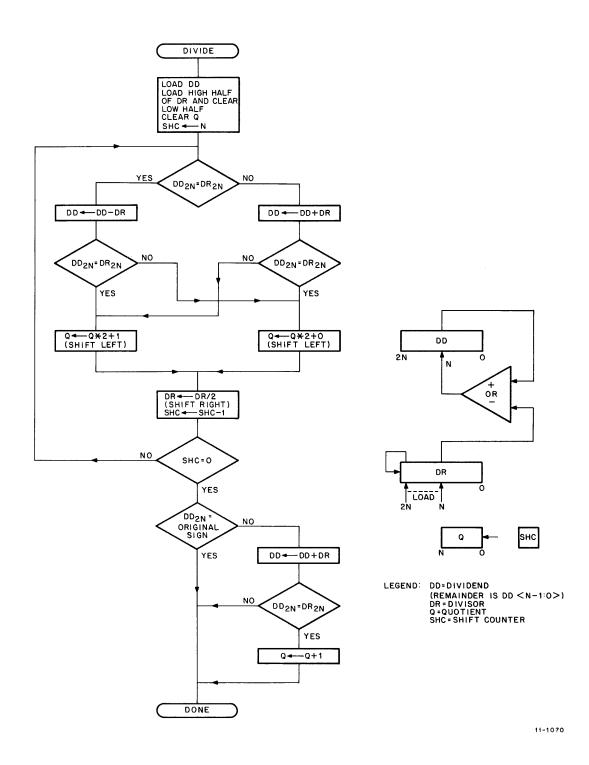

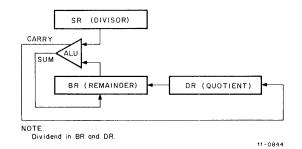

| 3.7       | THE MULTIPLY AND DIVIDE INSTRUCTIONS          | . 3-20 |

| 3.7.1     | Number Representation                         | . 3-20 |

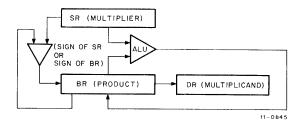

| 3.7.2     | The Multiply Algorithm                        | . 3-21 |

| 3.7.3     | Sign Correction During Multiplication         | . 3-21 |

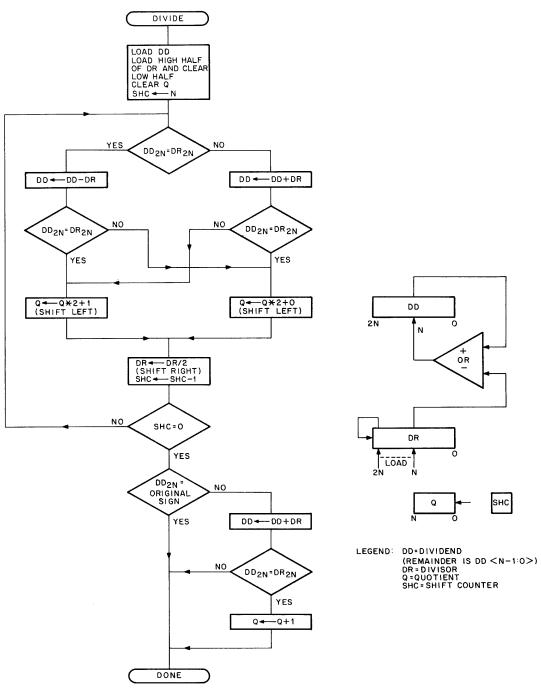

| 3.7.4     | The Divide Instruction                        | . 3-23 |

| 5.7.4     |                                               |        |

| CHAPTER 4 | BLOCK DIAGRAM DESCRIPTION                     |        |

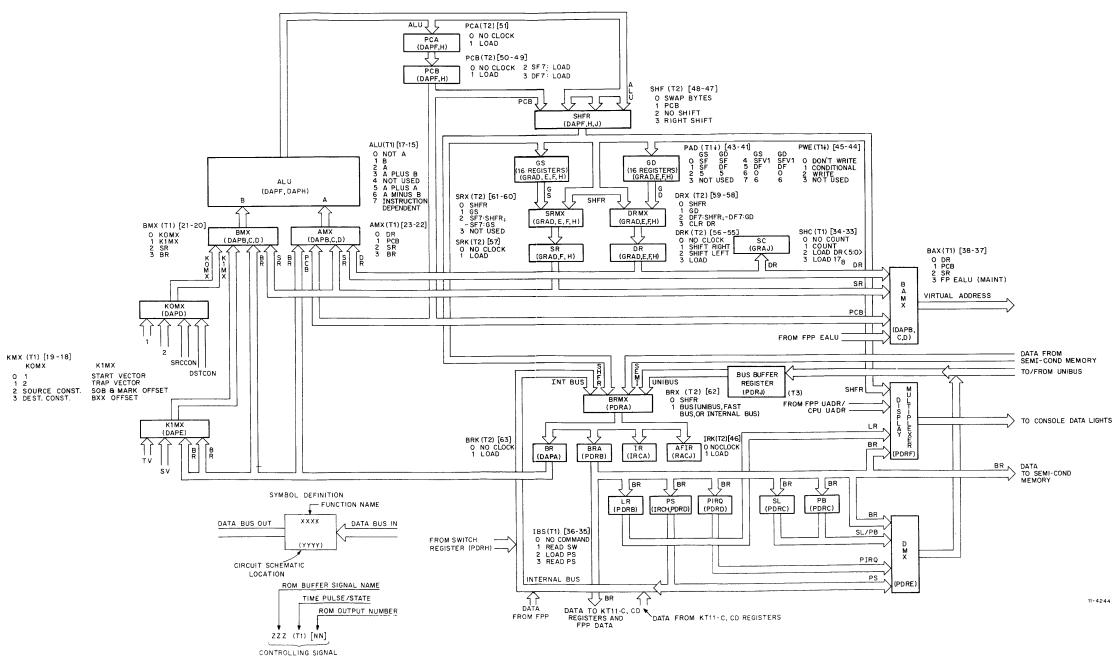

| 4.1       | DATA PATHS BLOCK DIAGRAM                      | . 4-1  |

| 4.2       | GENERAL STORAGE REGISTERS                     | . 4-1  |

| 4.2.1     | Program Counter (PC)                          | . 4-1  |

| 4.2.2     | Stack Pointers (SP)                           | . 4-3  |

| 4.2.3     | - General Register Sets                       | . 4-3  |

| 4.3       | TEMPORARY STORAGE REGISTERS                   | . 4-4  |

| 4.3.1     | Source Register (SR)                          | . 4-5  |

| 4.3.2     | Destination Register (DR)                     | . 4-5  |

| 4.3.3     | Bus Register (BR and BRA)                     | . 4-5  |

| 4.4       | SPECIAL PURPOSE REGISTERS                     |        |

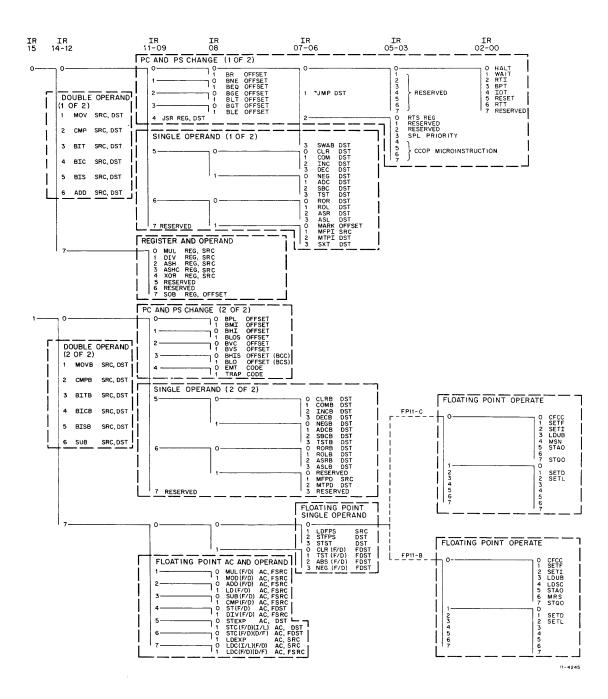

| 4.4.1     | Instruction Register (IR)                     | . 4-6  |

| 4.4.2     | Shift Counter (SC)                            | . 4-6  |

| 4.4.3     | Processor Status Register (PS)                | . 4-6  |

| 4.4.4     | Programmed Interrupt Request Register (PIRQ)  |        |

| 4.4.5     | Stack Limit Register (SL)                     | . 4-8  |

| 4.4.6     | Microprogram Break Register (PB)              |        |

| 4.4.7     | Console Switches (SW) and Light Register (LR) |        |

| 4.5       | DATA MANIPULATION                             | . 4-9  |

| 4.5.1     | Arithmetic and Logic Unit (ALU)               | . 4-9  |

| 4.5.2     | Shifter (SHFR)                                | . 4-9  |

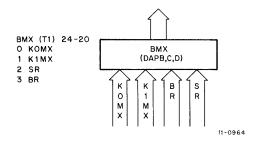

| 4.5.3     | Constant Multiplexers (KOMX, K1MX)            | . 4-10 |

| 4.5.4     | Destination Register (DR)                     | . 4-10 |

| 4.5.5     | Shift Counter (SC)                            | . 4-10 |

| 4.6       | DATA ROUTING ELEMENTS                         | . 4-10 |

| 4.6.1     | ALU Interface Multiplexers                    | . 4-10 |

|           |                                               |        |

|           | · · · · · · · · · · · · · · · · · · ·                                  | Page   |

|-----------|------------------------------------------------------------------------|--------|

| 4.6.2     | Temporary Storage Register Input Multiplexers                          | 4-10   |

| 4.6.3     | External Interface Multiplexers                                        | 4-11   |

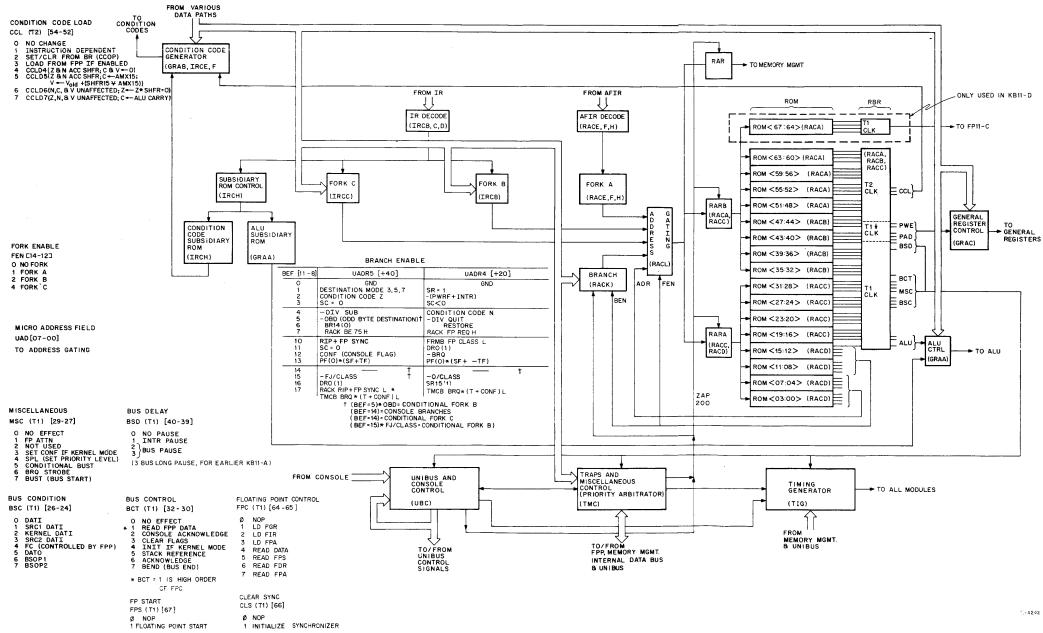

| 4.7       | CONTROL SECTION                                                        |        |

| 4.7.1     | ROM Microprogram Control                                               |        |

| 4.7.2     | External Interface Control                                             | 4.14   |

| 4.7.2.1   | Unibus and Console Control (UBC) Module                                |        |

| 4.7.2.2   | Traps and Miscellaneous Control (TMC) Module                           |        |

| 4.7.2.3   | The Timing Generator (TIG) Module                                      |        |

| 4.8       | SPECIAL CONTROL LOGIC                                                  |        |

| 4.8.1     | Arithmetic and Logic Unit (ALU) Control                                | 4.15   |

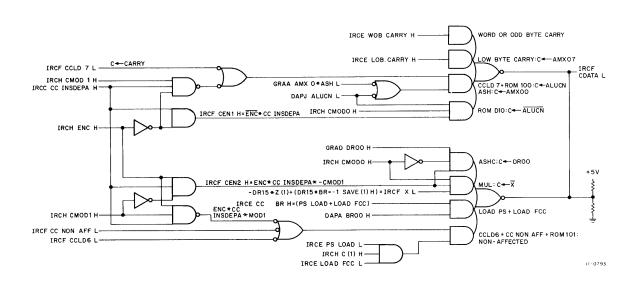

| 4.8.2     | Condition Code Control                                                 | 4.16   |

| 4.8.3     | General Register Control                                               |        |

|           |                                                                        | 4-10   |

| CHAPTER 5 | ADDRESS MODES AND INSTRUCTIONS SETS                                    |        |

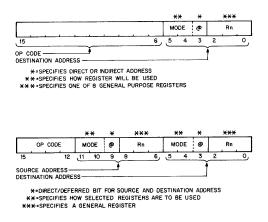

| 5.1       | ADDRESS MODES                                                          | . 5-2  |

| 5.2       | KB11-A, D INSTRUCTIONS                                                 | . 5-4  |

| 5.3       | KB11-A, D INSTRUCTION TIME                                             | . 5-19 |

| 5.3.1     | Approaches – Typical/Minimum/Maximum/Measured                          |        |

| 5.3.2     | Steps to Calculate Instruction Times                                   |        |

| 5.3.2.1   | Step 1: Subcycle Times                                                 |        |

| 5.3.2.2   | Step 2: Cycle Times                                                    |        |

| 5.3.2.3   | Step 3: Instruction Time                                               |        |

| 5.3.3     | Determining Subcycle Times                                             |        |

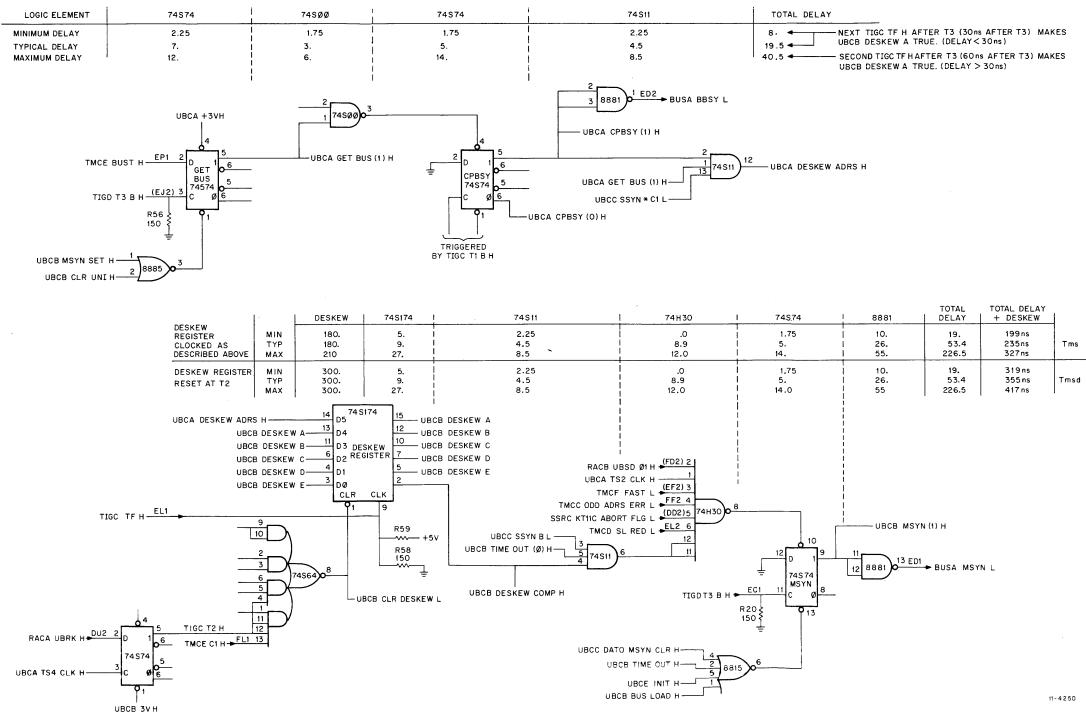

| 5.3.3.1   | MSYN Generation Time (T <sub>MS</sub> )                                |        |

| 5.3.3.2   | MSYN Generation Time Delayed (T <sub>MSD</sub> )                       | 5-21   |

| 5.3.3.3   | MM11-L Access Time $(T_A)$                                             | 5-21   |

| 5.3.3.4   | MM11-L Cycle Time $(T_C)$                                              |        |

| 5.3.3.5   | Unibus Propagation Delay $(T_P)$                                       |        |

| 5.3.3.6   | SSYN Resynce Time ( $T_{SS}$ )                                         |        |

| 5.3.4     | Calculating Cycle Times                                                |        |

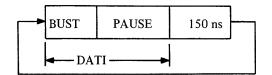

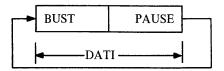

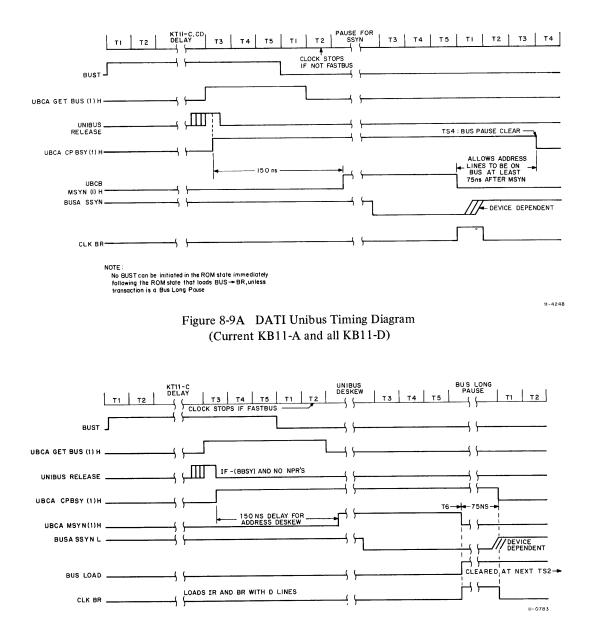

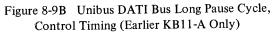

| 5.3.4.1   | DATI and DATIP                                                         |        |

| 5.3.4.2   | DATO                                                                   |        |

| 5.3.4.3   | DATI or DATIP with Immediately Previous DATO                           |        |

| 5.3.4.4   | DATI or DATIP with Immediately Previous DATI                           |        |

| 5.3.4.5   | DATO with Immediately Previous DATI                                    |        |

| 5.3.4.6   | DATO with Immediately Previous DATO                                    |        |

| 5.3.4.7   | DATO (with T <sub>MSD</sub> )                                          |        |

| 5.3.5     | Example of Calculating an Instruction Time                             |        |

| 5.3.5.1   | Step 1                                                                 |        |

| 5.3.5.2   | Step 2                                                                 |        |

| 5.3.5.3   | Step 3                                                                 |        |

| 5.3.6     | Comments on the Instruction Times Table (PDP-11/04, 05, 10, 35, 40, 45 | 5 21   |

|           | Processor Handbook)                                                    | 5-25   |

| 5.3.7     | KB11-A, D Cycle Delays and Speed Variation                             |        |

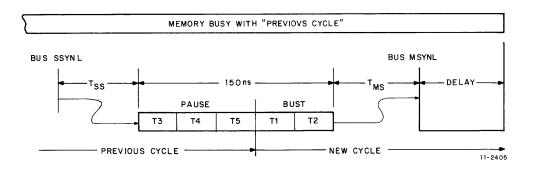

| 5.3.7.1   | Basic Memory Cycle                                                     |        |

| 5.3.7.2   | Effect of Previous Cycle Memory Busy                                   |        |

| 5.3.7.3   | Fast Processor                                                         |        |

| 5.3.7.4   | Slow Processor                                                         |        |

|           |                                                                        | 5-50   |

| CHAPTER 6 | OPERATION                                             |

|-----------|-------------------------------------------------------|

| 6.1       | CONSOLE CONTROLS AND INDICATORS                       |

| 6.2       | POWER ON                                              |

| 6.2.1     | ENABL Function                                        |

| 6.2.2     | HALT Function                                         |

| 6.3       | CONSOLE OPERATIONS 6-5                                |

| 6.3.1     | HALT Switch Functions 6-5                             |

| 6.3.1.1   | HALT/CONT with S INST 6-5                             |

| 6.3.1.2   | HALT/CONT with S BUS CYCLE 6-5                        |

| 6.3.2     | EXAM Switch Functions                                 |

| 6.3.3     | DEP Switch Functions 6-6                              |

| 6.3.4     | REG EXAM and REG DEP Functions                        |

| 6.4       | ADDRESS DISPLAY SELECT                                |

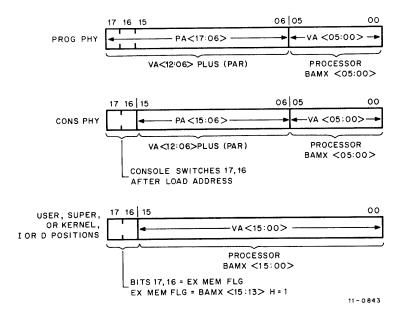

| 6.4.1     | PROG PHY Function                                     |

| 6.4.2     | CONS PHY Function                                     |

| 6.4.3     | USER, SUPER, or KERNEL Functions                      |

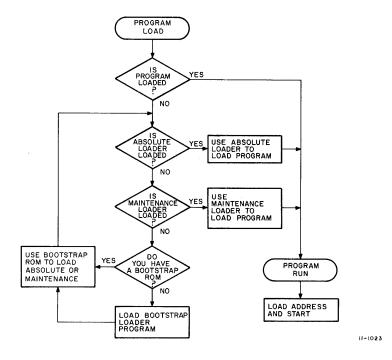

| 6.5       | HOW TO LOAD AND RUN PROGRAMS 6-8                      |

| 6.5.1     | Loading the PDP-11 Bootstrap Loader                   |

| 6.5.2     | Loading the PDP-11 Absolute Binary Loader             |

| 6.5.3     | Loading the Maintenance Loader                        |

| 0.0.0     | Louging the manifold bound in the transferrer and the |

| CHAPTER 7 | KB11-A, D FLOWS                                       |

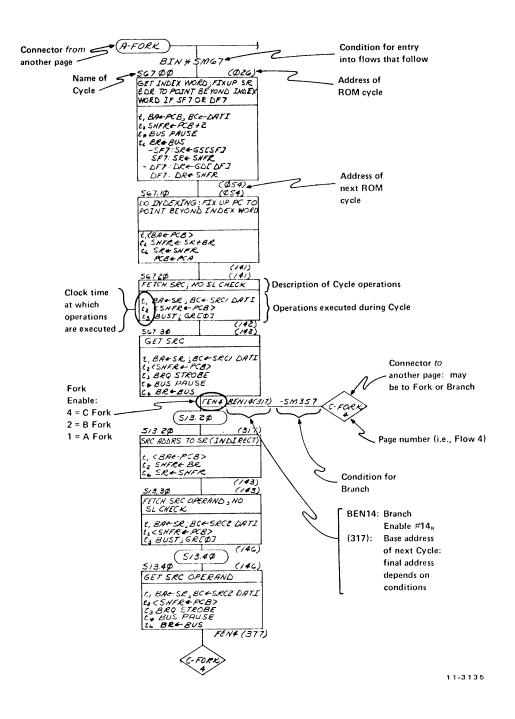

| 7.1       | FLOW DIAGRAMS                                         |

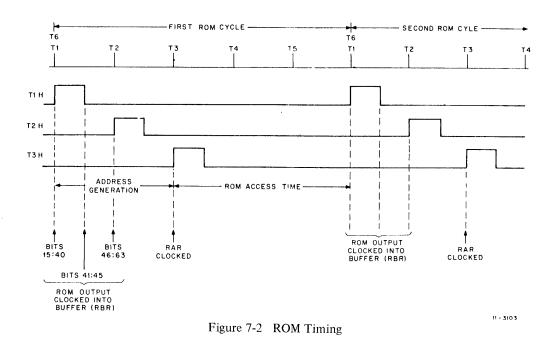

| 7.1.1     | ROM Timing                                            |

| 7.1.2     | Glossary                                              |

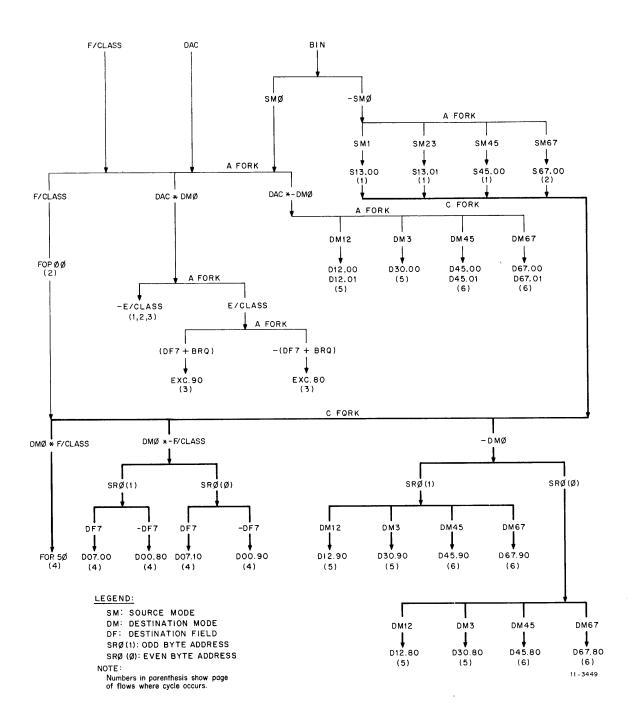

| 7.2       | A AND C FORKS: OPERAND FETCH 7-5                      |

| 7.3       | FLOWCHART DESCRIPTION 7-5                             |

| 7.3.1     | Flows 1                                               |

| 7.3.2     | Flows 2                                               |

| 7.3.3     | Flows 3                                               |

| 7.3.4     | Flows 4                                               |

| 7.3.5     | Flows 5                                               |

| 7.3.6     | Flows 6                                               |

| 7.3.7     | Flows 7                                               |

| 7.3.8     | Flows 8                                               |

| 7.3.9     | Flows 9 and 10                                        |

| 7.3.10    | Flows 11                                              |

| 7.3.11    | Flows 12 and 13                                       |

| 7.3.12    | Flows 14                                              |

| 7.4       | FOLLOWING AN INSTRUCTION THROUGH THE FLOWCHARTS       |

| 7.4.1     | Figures and Tables                                    |

|           |                                                       |

| CHAPTER 8 | LOGIC DESCRIPTION                                     |

| 8.1       | DAP MODULE M8100                                      |

| 8.1.1     | Bus Register                                          |

| 8.1.2     | A, B, and Bus Address Multiplexers                    |

| 8.1.3     | Constant Multiplexer 1 (K1MX) 8-2                     |

| 8.1.4     | Arithmetic Logic Unit, Shifter, and Program Counter   |

|           |                                                       |

|                    |                                                                       | Page       |

|--------------------|-----------------------------------------------------------------------|------------|

| 8.1.4.1            | Arithmetic Logic Unit (ALU)                                           | 8-3        |

| 8.1.4.2            | Shifters and Program Counter                                          |            |

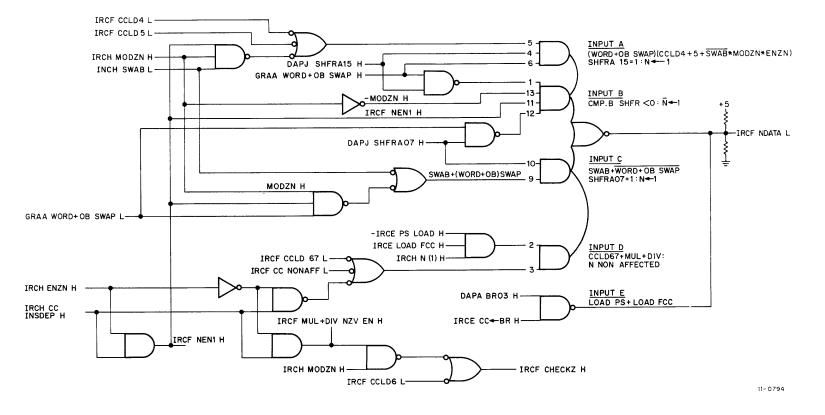

| 8.1.4.3            | Shifter Logic                                                         |            |

| 8.1.4.4            | Program Counter Clocks                                                | 8-4        |

| 8.1.4.5            | Control Signals                                                       |            |

| 8.2                | GRA MODULE M8101                                                      |            |

| 8.2.1              | Arithmetic and Logic Unit Control                                     | 8-5        |

| 8.2.1.1            | Non-Instruction-Dependent Control                                     |            |

| 8.2.1.2            | Instruction-Dependent Control                                         |            |

| 8.2.2              | Shifter Zero Detection                                                |            |

| 8.2.2.1            |                                                                       |            |

| 8.2.2.2            | Odd Byte Destination                                                  |            |

| 8.2.3              | General Register Address Logic                                        |            |

| 8.2.3.1            | Source and Destination Address Multiplexers                           |            |

| 8.2.3.2            | General Register Set Selection                                        |            |

| 8.2.3.3            | General Register Control Signals                                      |            |

| 8.2.4              | General Registers, Source and Destination Multiplexers, and Registers |            |

| 8.2.4.1            | General Registers                                                     |            |

| 8.2.4.2            | Source and Destination Multiplexers                                   | 0-9<br>0 0 |

| 8.2.4.3            | Source Register (SR)                                                  |            |

| 8.2.4.4            | Destination Register (DR)                                             |            |

| 8.2.4.5            |                                                                       |            |

| 8.2.4.6            | Control Logic                                                         | 8-10       |

| 8.2.4.7            | Special Signals                                                       |            |

| 8.2.5              | SR15 and DR15                                                         |            |

| 8.2.5              | Shift Counter                                                         |            |

| 8.3.1              | IRC MODULE (M8102 in the KB11-A, M8132 in the KB11-D)                 | 8-11       |

| 8.3.2              | Instruction Register (IR)                                             |            |

| 8.3.3              | B Fork Logic                                                          |            |

| 8.3.4              | C Fork Logic                                                          |            |

| 8.3.5              | CCL Decoding                                                          |            |

| 8.3.6              | C Bit Data                                                            |            |

| 8.3.7              | N Bit Data                                                            |            |

| 8.3.7.1            |                                                                       |            |

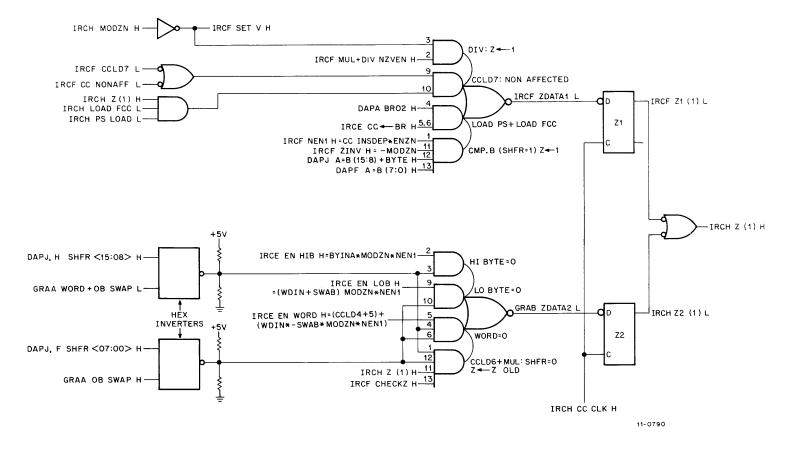

| 8.3.7.2            | ZDATA1 Sources                                                        |            |

| 8.3.8              | ZDATA2 Sources                                                        |            |

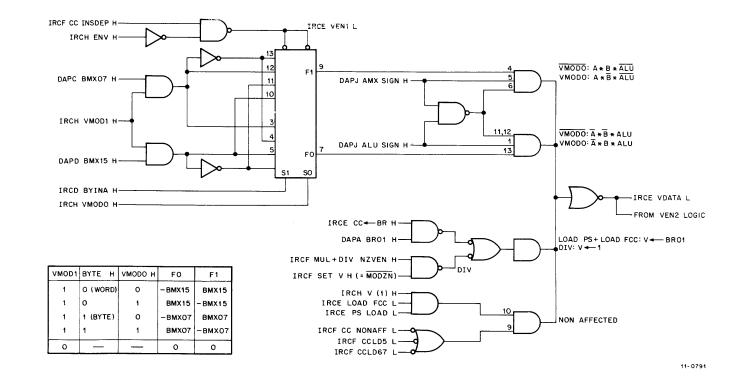

|                    | V Bit Data                                                            |            |

| 8.3.8.1<br>8.3.8.2 | VEN1                                                                  |            |

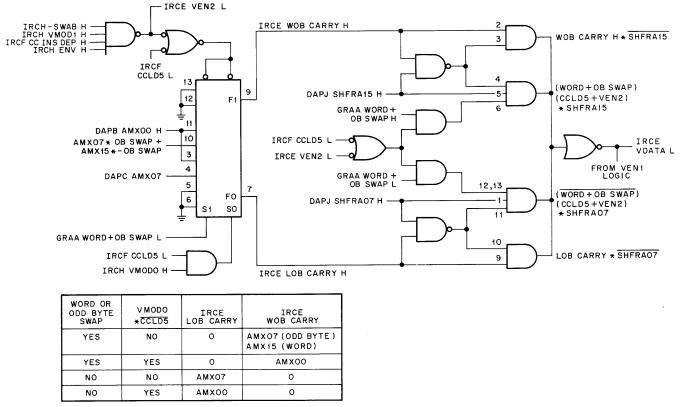

| 8.3.9              | VEN2                                                                  |            |

|                    | Condition Code Storage                                                |            |

| 8.3.9.1            | Clocked Inputs                                                        |            |

| 8.3.9.2            | BR Inputs                                                             |            |

| 8.3.9.3            | IR Inputs                                                             |            |

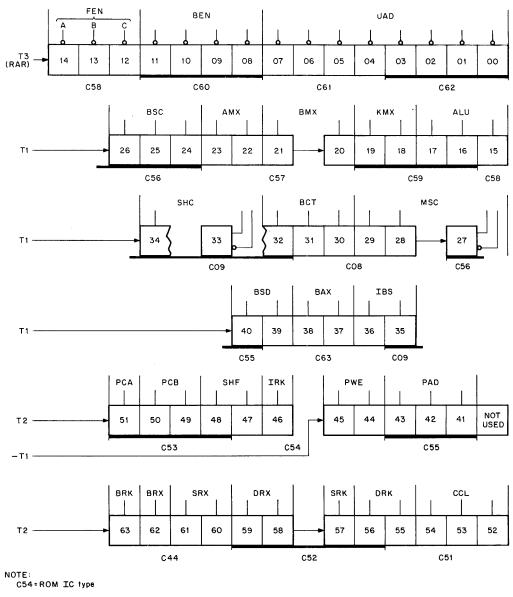

| 8.3.9.4            | Subsidiary ROMs Address Generation                                    |            |

| 8.3.9.5            | ROM Address Multiplexer                                               |            |

| 8.3.9.6            | Subsidiary ROMs                                                       |            |

| 8.4                | PDR MODULE M8104                                                      |            |

| 8.4.1              | Bus Register Multiplexer                                              |            |

| 8.4.2              | Bus Register A and Light Register                                     |            |

| 8.4.3              | Program Break Register                                                | 8-27       |

Page

| 8.4.5       Program Interrupt Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------|

| 84.6       Processor Status Register       \$-28         84.6.1       Condition Codes       \$-28         84.6.2       T Bit       \$-29         84.6.3       Priority Bits       \$-29         84.6.4       General Register Set Bit       \$-29         84.6.5       Previous Mode Bits       \$-29         84.6.6       Current Mode Bits       \$-30         84.7       Unibus A Data Multiplexer       \$-30         84.8       Display Multiplexer       \$-30         84.7       Unibus A Data Multiplexer       \$-30         84.8       Display Multiplexer       \$-30         84.9       Console Interconnections       \$-30         85.1       RAC MOPULE (M8103 in the KB11-A, M8123 in the KB11-D)       \$-31         85.2       Microprogram ROM and Buffer Register       \$-31         85.3       Fork A Instruction Decoding       \$-32         85.3.1       Decode Logic       \$-36         85.3.2       Address Bit Generation       \$-36         85.3.3       RACE 40 RAB03       \$-37         85.3.4       RACE 40 RAB03       \$-37         85.4       Fork A Croutits       \$-37         85.4.1       HALT Through Op Code 7       \$-38     <               | 8.4.4   | Stack Limit Register                                  |

| 8.4.6.1       Condition Codes       8-28         8.4.6.2       T Bit       8-29         8.4.6.3       Priority Bits       8-29         8.4.6.4       General Register Set Bit       8-29         8.4.6.5       Previous Mode Bits       8-29         8.4.6.6       Current Mode Bits       8-29         8.4.6.7       Read PS       8-30         8.4.7       Unitous A Data Multiplexer       8-30         8.4.8       Display Multiplexer       8-30         8.4.9       Console Interconnections       8-30         8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE 40 RAB03       8-37         8.5.3.4       RACE 40 RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.5                                                                  | 8.4.5   |                                                       |

| 84.6.2       T Bit       8-29         84.6.3       Priority Bits       8-29         84.6.4       General Register Set Bit       8-29         84.6.5       Previous Mode Bits       8-29         84.6.6       Current Mode Bits       8-30         84.6.7       Read PS       8-30         84.7       Unibus A Data Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.9       Console Interconnections       8-30         85.1       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         85.2       Microprogram ROM and Buffer Register       8-31         85.3       Fork A Instruction Decoding       8-32         85.3.1       Decode Logic       8-36         85.3.2       Address Bit Generation       8-36         85.3.3       RACE AO RAB03       8-37         85.3.4       RACE AO RAB03       8-37         85.3.5       RACE AO RAB04       8-37         85.4.4       Fork A Circuits       8-37         85.4.5       RACE AO RAB05       8-37         85.4.4       RACE AO RAB05       8-37         85.4.5       RACE AO RAB05       8-37         85.4.4                                                                  | 8.4.6   |                                                       |

| 8.4.6.3       Priority Bits       8-29         8.4.6.4       General Register Set Bit       8-29         8.4.6.5       Previous Mode Bits       8-29         8.4.6.6       Current Mode Bits       8-30         8.4.6.7       Read PS       8-30         8.4.8       Display Multiplexer       8-30         8.4.8       Display Multiplexer       8-30         8.4.8       Display Multiplexer       8-30         8.5.1       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB03       8-37         8.5.3.4       RACE AO RAB03       8-37         8.5.3.5       RACE AO RAB04       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.4       Fork A Logic       8-38         8.5.4.5       FACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38                                                            | 8.4.6.1 |                                                       |

| 84.6.4       General Register Set Bit       8-29         84.6.5       Previous Mode Bits       8-29         84.6.7       Read PS       8-30         84.7       Unibus A Data Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.9       Console Interconnections       8-30         85.5       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         85.2       Microprogram ROM and Buffer Register       8-31         85.3       Fork A Instruction Decoding       8-32         85.3.1       Decode Logic       8-36         85.3.2       Address Bit Generation       8-36         85.3.3       RACE AO RAB (02:00)       8-36         85.3.4       RACE AO RAB03       8-37         85.3.5       RACE AO RAB04       8-37         85.4       Fork A Circuits       8-37         85.4.1       HALT Through Op Code 7       8-38         85.4.4       RTS Through CCOP       8-38         85.4.5       RACF AO RAB03       8-38         85.4.6       TRUE 1:2       8-38         85.5.1       Branch Instruction Address Generation       8-39                                      | 8.4.6.2 |                                                       |

| 84.6.5       Previous Mode Bits       8-29         84.6.6       Current Mode Bits       8-30         84.6.7       Read PS       8-30         84.7       Unibus A Data Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.8       Display Multiplexer       8-30         85.5       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         85.1       ROM Address Register (RAR)       8-31         85.2       Microprogram ROM and Buffer Register       8-31         85.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB02-000       8-36         8.5.3.4       RACE AO RAB05       8-37         8.5.3.5       RACE AO RAB05       8-37         8.5.4.1       HALT Through Op Code 7       8-38         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through COP       8-38         8.5.5.1       Branch Instruction Address Generation       8-39                                       | 8.4.6.3 |                                                       |

| 84.6.6       Current Mode Bits       8-30         84.6.7       Read PS       8-30         84.7       Unibus A Data Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.8       Display Multiplexer       8-30         84.9       Console Interconnections       8-30         85.1       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         85.1       ROM Address Register (RAR)       8-31         85.2       Microprogram ROM and Buffer Register       8-31         85.3       Fork A Instruction Decoding       8-32         85.3.1       Decode Logic       8-36         85.3.2       Address Bit Generation       8-36         85.3.3       RACE AO RAB 02:00)       8-36         85.3.4       RACE AO RAB04       8-37         85.3.5       RACE AO RAB05       8-37         85.4       Fork A Circuits       8-37         85.4.1       HALT Through Op Code 7       8-38         85.4.2       X Class       8-37         85.4.4       RTS Through CCOP       8-38         85.4.5       RACF A2 RAB03       8-38         85.5.1       Branch Instruction Address Generation       8-39                                         | 8.4.6.4 |                                                       |

| 8.4.6.7       Read PS       8-30         8.4.7       Unibus A Data Multiplexer       8-30         8.4.8       Display Multiplexer       8-30         8.4.9       Console Interconnections       8-30         8.5.1       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.4       RACE AO RAB 02:00       8-36         8.5.3.5       RACE AO RAB04       8-37         8.5.3.6       RACE AO RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       RCF AO RAB03       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF AZ RAB03       8-38         8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39 </td <td>8.4.6.5</td> <td></td> | 8.4.6.5 |                                                       |

| 8.4.7       Unibus A Data Multiplexer       8-30         8.4.8       Display Multiplexer       8-30         8.4.9       Console Interconnections       8-30         8.5       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         8.5.1       ROM address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB03       8-37         8.5.3.4       RACE AO RAB04       8-37         8.5.3.5       RACE AO RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       Fork A Logic       8-38         8.5.5       Fork A Logic       8-39         8.5.5       Fork A Logic       8-39         8.5.6       A Fork Instruction Address Generation       8-39         8.5.7       Pork A Logic       8-39                                         | 8.4.6.6 |                                                       |

| 8.4.8       Display Multiplexer       8.30         8.4.9       Console Interconnections       8.30         8.5       RAC MODULE (MI03 in the KB11-A, M8123 in the KB11-D)       8.31         8.5.1       ROM Address Register (RAR)       8.31         8.5.2       Microprogram ROM and Buffer Register       8.31         8.5.3       Fork A Instruction Decoding       8.32         8.5.3.1       Decode Logic       8.36         8.5.3.2       Address Bit Generation       8.36         8.5.3.3       RACE AO RAB 02:00)       8.36         8.5.3.4       RACE AO RAB03       8.37         8.5.3.5       RACE AO RAB05       8.37         8.5.4       Fork A Circuits       8.37         8.5.4       Fork A Circuits       8.37         8.5.4.1       HALT Through Op Code 7       8.37         8.5.4.2       X Class       8.38         8.5.4.3       U Class       8.38         8.5.4.4       RTS Through CCOP       8.38         8.5.5       Fork A Logic       8.38         8.5.4       RCF 42 RAB03       8.39         8.5.5       Fork A Logic       8.39         8.5.5       Fork A Logic       8.39         8.5.6                                                               | 8.4.6.7 |                                                       |

| 84.9       Console Interconnections       8-30         8.5       RAC MODULE (M8103 in the KB11-A), M8123 in the KB11-D)       8-31         8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB 02:00)       8-36         8.5.3.4       RACE AO RAB03       8-37         8.5.3.5       RACE AO RAB04       8-37         8.5.3.6       RACE AO RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-38         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-38         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39                                      | 8.4.7   |                                                       |

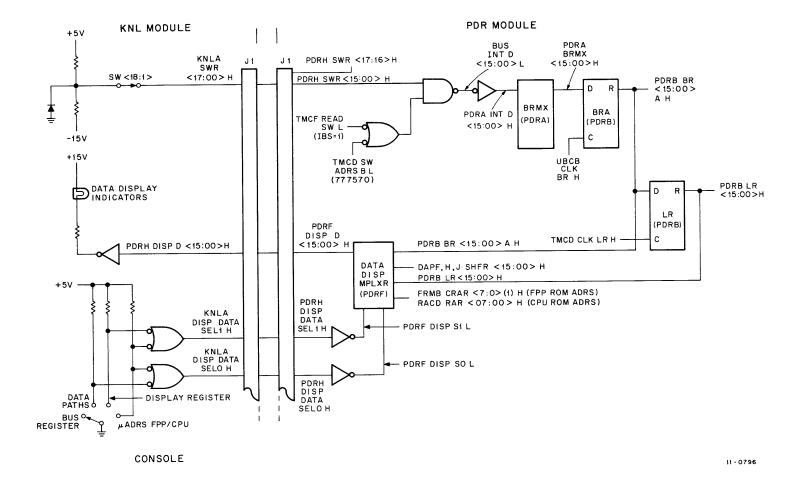

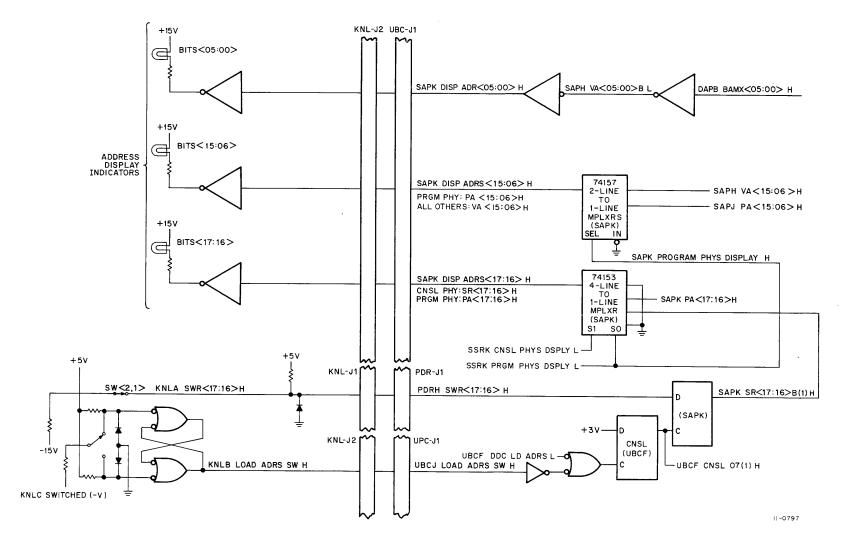

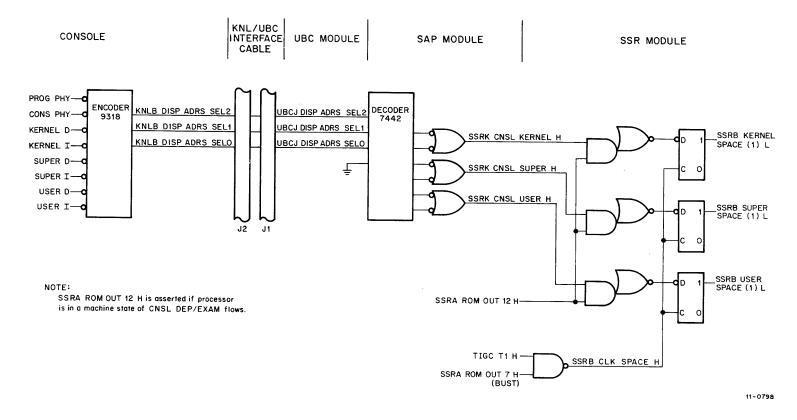

| 8.5       RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D)       8-31         8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB 02:00       8-36         8.5.3.4       RACE AO RAB04       8-37         8.5.3.5       RACE AO RAB04       8-37         8.5.4       Fork A Circuits       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5       Fork A Logic       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Address Assembly       8-44                                    | 8.4.8   | Display Multiplexer                                   |

| 8.5.1       ROM Address Register (RAR)       8-31         8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE A0 RAB (02:00)       8-36         8.5.3.4       RACE A0 RAB03       8-37         8.5.3.5       RACE A0 RAB04       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Address Generation       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.7       Microprogram Address Assembly       8-40         8.6       Microprogram Address Assembly       8-42                                    | 8.4.9   |                                                       |

| 8.5.2       Microprogram ROM and Buffer Register       8-31         8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE AO RAB (02:00)       8-36         8.5.3.4       RACE AO RABO3       8-37         8.5.3.5       RACE AO RABO4       8-37         8.5.3.6       RACE AO RABO5       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through COP       8-38         8.5.4.5       RACF A2 RABO3       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Diable BUST       8-39         8.5.5       Fork A Logic       8-39         8.5.6       A Fork Instruction Address Generation       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Branch Logic       8-39         8.                                                         | 8.5     | RAC MODULE (M8103 in the KB11-A, M8123 in the KB11-D) |

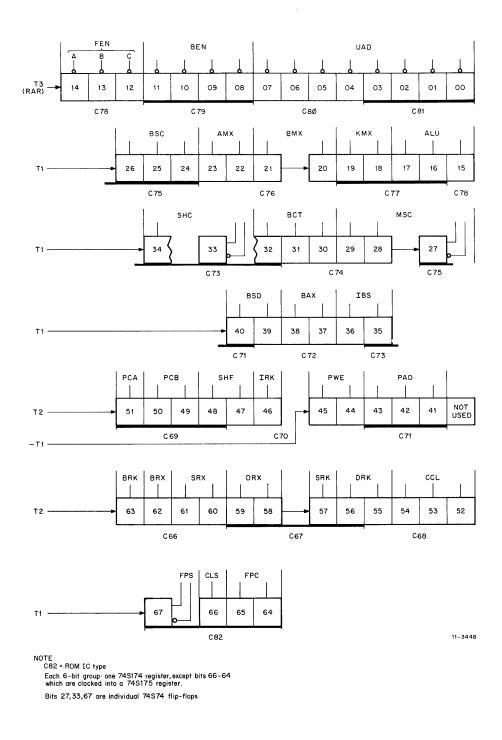

| 8.5.3       Fork A Instruction Decoding       8-32         8.5.3.1       Decode Logic       8-36         8.5.3.2       Address Bit Generation       8-36         8.5.3.3       RACE A0 RAB (02:00)       8-36         8.5.3.4       RACE A0 RAB03       8-37         8.5.3.5       RACE A0 RAB04       8-37         8.5.3.6       RACE A0 RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through COP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-40         8.6                                                                   | 8.5.1   | ROM Address Register (RAR) 8-31                       |

| 8.5.3.1       Decode Logic       8.36         8.5.3.2       Address Bit Generation       8.36         8.5.3.3       RACE AO RAB (02:00)       8.36         8.5.3.4       RACE AO RAB(03       8.37         8.5.3.5       RACE AO RAB05       8.37         8.5.3.6       RACE AO RAB05       8.37         8.5.4       Fork A Circuits       8.37         8.5.4.1       HALT Through Op Code 7       8.37         8.5.4.2       X Class       8.37         8.5.4.3       U Class       8.38         8.5.4.4       RTS Through OCOP       8.38         8.5.4.5       RACF A2 RAB03       8.38         8.5.4.6       TRUE 1:2       8.38         8.5.5       Fork A Logic       8.38         8.5.5       Fork A Logic       8.39         8.5.5.1       Branch Instruction Address Generation       8.39         8.5.5       Fork Instruction Register       8.39         8.5.6       A Fork Instruction Register       8.39         8.5.7       Microprogram Address Assembly       8.40         8.6       TMC MODULE M8105       8.42         8.6.1       Request Storage       8.42         8.6.1       Request Storage                                                                       | 8.5.2   | Microprogram ROM and Buffer Register                  |

| 8.5.3.2       Address Bit Generation       8.36         8.5.3.3       RACE AO RAB (02:00)       8.36         8.5.3.4       RACE AO RAB03       8.37         8.5.3.5       RACE AO RAB04       8.37         8.5.3.6       RACE AO RAB05       8.37         8.5.4       Fork A Circuits       8.37         8.5.4       Fork A Circuits       8.37         8.5.4.1       HALT Through Op Code 7       8.37         8.5.4.2       X Class       8.37         8.5.4.3       U Class       8.37         8.5.4.4       RTS Through CCOP       8.38         8.5.4.5       RACF A2 RAB03       8.38         8.5.4.6       TRUE 1:2       8.38         8.5.5.1       Branch Instruction Address Generation       8.39         8.5.5.2       Disable BUST       8.39         8.5.6       A Fork Instruction Register       8.39         8.5.7       Microprogram Branch Logic       8.39         8.5.8       Microprogram Address Assembly       8.40         8.6       TMC MODULE M8105       8.42         8.6.1       Request Storage       8.42         8.6.1.3       Power Fail Clear       8.42         8.6.1.4       Internal B                                                                  | 8.5.3   | Fork A Instruction Decoding                           |

| 8.5.3.3       RACE A0 RAB (02:00)       8-36         8.5.3.4       RACE A0 RAB03       8.37         8.5.3.5       RACE A0 RAB04       8.37         8.5.3.6       RACE A0 RAB05       8.37         8.5.4.1       Fork A Circuits       8.37         8.5.4.2       X Class       8.37         8.5.4.3       U Class       8.37         8.5.4.4       RTS Through Op Code 7       8.38         8.5.4.5       RACF A2 RAB03       8.38         8.5.4.6       TRUE 1:2       8.38         8.5.5.1       Branch Instruction Address Generation       8.39         8.5.5.2       Disable BUST       8.39         8.5.6       A Fork Instruction Register       8.39         8.5.7       Microprogram Branch Logic       8.39         8.5.8       Microprogram Address Assembly       8.40         8.6       TMC MODULE M8105       8.42         8.6.1       Request Storage       8.42         8.6.1.3       Power Fail Clear       8.44         8.6.3       Control Logic       8.44         8.6.3       Control Logic       8.44         8.6.3       Control Logic       8.44         8.6.3.1       BRQ TRUE       8.4                                                                           | 8.5.3.1 | Decode Logic                                          |

| 8.5.3.4       RACE A0 RAB03       8-37         8.5.3.5       RACE A0 RAB04       8-37         8.5.3.6       RACE A0 RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through COP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-44         8.6.1.3       Power Fail Clear       8-42         8.6.1.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3       Control Logic                                                                        | 8.5.3.2 | Address Bit Generation                                |

| 8.5.3.5       RACE A0 RAB04       8-37         8.5.3.6       RACE A0 RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4       Fork A Circuits       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-42         8.6.1       Request Storage       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-42         8.6.1       Request Storage       8-44         8.6.3       Control Logic       8-44                                                                                     | 8.5.3.3 | RACE AO RAB (02:00)                                   |

| 8.5.3.6       RACE A0 RAB05       8-37         8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.4       Control Logic       8-44         8.6.3       Control Logic       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.2       Enable Vector       8-45                                                                                | 8.5.3.4 | RACE A0 RAB03                                         |

| 8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       842         8.6.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.4       Control Logic       844         8.6.3       Control Logic       844         8.6.3       BRQ TRUE       844         8.6.3       BRQ TRUE       844         8.6.3       BRQ TRUE       845                                                                                                              | 8.5.3.5 | RACE A0 RAB04                                         |

| 8.5.4       Fork A Circuits       8-37         8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-37         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-39         8.5.6       A Fork Instruction Address Generation       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.7       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       842         8.6.1       Request Storage       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-42         8.6.1.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3       Dontrol Logic       8-44                                                                                     | 8.5.3.6 | RACE A0 RAB05                                         |

| 8.5.4.1       HALT Through Op Code 7       8-37         8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.6       TRUE 1:2       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.1.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3       Enable Vector       8-45         8.6.3.2       Enable Vector <td>8.5.4</td> <td>Fork A Circuits</td>                             | 8.5.4   | Fork A Circuits                                       |

| 8.5.4.2       X Class       8-37         8.5.4.3       U Class       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.1.4       Internal Bus Initialization       8-44         8.6.3.1       BRQ TRUE       8-44         8.6.3.2       Enable Vector       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                                                                        | 8.5.4.1 |                                                       |

| 8.5.4.3       U Class       8-38         8.5.4.4       RTS Through CCOP       8-38         8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.5       Fork A Logic       8-39         8.5.5       Josable BUST       8-39         8.5.6       A Fork Instruction Address Generation       8-39         8.5.7       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                                                                           | 8.5.4.2 | Ų I                                                   |

| 8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.1       Internal Bus Initialization       8-44         8.6.2       Priority Arbitration       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.2       Enable Vector       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                      | 8.5.4.3 |                                                       |

| 8.5.4.5       RACF A2 RAB03       8-38         8.5.4.6       TRUE 1:2       8-38         8.5.5       Fork A Logic       8-38         8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.1       Internal Bus Initialization       8-44         8.6.2       Priority Arbitration       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.2       Enable Vector       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                      | 8.5.4.4 | RTS Through CCOP                                      |

| 8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.5.4.5 |                                                       |

| 8.5.5       Fork A Logic       8-38         8.5.5.1       Branch Instruction Address Generation       8-39         8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       8-40         8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-44         8.6.4       Internal Bus Initialization       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.5.4.6 | TRUE 1:2                                              |

| 8.5.5.1Branch Instruction Address Generation8-398.5.5.2Disable BUST8-398.5.6A Fork Instruction Register8-398.5.7Microprogram Branch Logic8-398.5.8Microprogram Address Assembly8-408.6TMC MODULE M81058-428.6.1Request Storage8-428.6.1.2Priority Clear8-428.6.1.3Power Fail Clear8-448.6.4Internal Bus Initialization8-448.6.3Control Logic8-448.6.3BRQ TRUE8-458.6.3.3Branch Enable 13 (BE13)8-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                                       |

| 8.5.5.2       Disable BUST       8-39         8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       842         8.6.1       Request Storage       842         8.6.1.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3       Control Logic       844         8.6.3.1       BRQ TRUE       845         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.5.5.1 |                                                       |

| 8.5.6       A Fork Instruction Register       8-39         8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       842         8.6.1       Request Storage       842         8.6.1.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3       Control Logic       844         8.6.3.1       BRQ TRUE       845         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.5.5.2 |                                                       |

| 8.5.7       Microprogram Branch Logic       8-39         8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       842         8.6.1       Request Storage       842         8.6.1.2       BRQ Clock       842         8.6.1.3       Priority Clear       842         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3.1       BRQ TRUE       844         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.5.6   |                                                       |

| 8.5.8       Microprogram Address Assembly       840         8.6       TMC MODULE M8105       842         8.6.1       Request Storage       842         8.6.1.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3       Control Logic       844         8.6.3.1       BRQ TRUE       845         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.5.7   |                                                       |

| 8.6       TMC MODULE M8105       8-42         8.6.1       Request Storage       8-42         8.6.1.1       BRQ Clock       8-42         8.6.1.2       Priority Clear       8-42         8.6.1.3       Power Fail Clear       8-42         8.6.1.4       Internal Bus Initialization       8-44         8.6.2       Priority Arbitration       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.2       Enable Vector       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45         8.6.4       Odd Address Error       8-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.5.8   |                                                       |

| 8.6.1.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3       Control Logic       844         8.6.3.1       BRQ TRUE       845         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845         8.6.4       Odd Address Error       846                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.6     |                                                       |

| 8.6.1.1       BRQ Clock       842         8.6.1.2       Priority Clear       842         8.6.1.3       Power Fail Clear       844         8.6.1.4       Internal Bus Initialization       844         8.6.2       Priority Arbitration       844         8.6.3       Control Logic       844         8.6.3.1       BRQ TRUE       845         8.6.3.2       Enable Vector       845         8.6.3.3       Branch Enable 13 (BE13)       845         8.6.4       Odd Address Error       846                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.6.1   |                                                       |

| 8.6.1.2       Priority Clear       8.42         8.6.1.3       Power Fail Clear       8.44         8.6.1.4       Internal Bus Initialization       8.44         8.6.2       Priority Arbitration       8.44         8.6.3       Control Logic       8.44         8.6.3.1       BRQ TRUE       8.44         8.6.3.2       Enable Vector       8.45         8.6.3.3       Branch Enable 13 (BE13)       8.45         8.6.4       Odd Address Error       8.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.6.1.1 |                                                       |

| 8.6.1.3       Power Fail Clear       8.44         8.6.1.4       Internal Bus Initialization       8.44         8.6.2       Priority Arbitration       8.44         8.6.3       Control Logic       8.44         8.6.3.1       BRQ TRUE       8.44         8.6.3.2       Enable Vector       8.45         8.6.3.3       Branch Enable 13 (BE13)       8.45         8.6.4       Odd Address Error       8.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.6.1.2 |                                                       |

| 8.6.1.4       Internal Bus Initialization       8-44         8.6.2       Priority Arbitration       8-44         8.6.3       Control Logic       8-44         8.6.3.1       BRQ TRUE       8-45         8.6.3.2       Enable Vector       8-45         8.6.3.3       Branch Enable 13 (BE13)       8-45         8.6.4       Odd Address Error       8-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.6.1.3 |                                                       |

| 8.6.2       Priority Arbitration       8.44         8.6.3       Control Logic       8.44         8.6.3.1       BRQ TRUE       8.45         8.6.3.2       Enable Vector       8.45         8.6.3.3       Branch Enable 13 (BE13)       8.45         8.6.4       Odd Address Error       8.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.6.1.4 |                                                       |

| 8.6.3       Control Logic       8.44         8.6.3.1       BRQ TRUE       8.45         8.6.3.2       Enable Vector       8.45         8.6.3.3       Branch Enable 13 (BE13)       8.45         8.6.4       Odd Address Error       8.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.6.2   |                                                       |