# VAX 9000 Family SCU Technical Description

Order Number EK-KA90J-TD-001

digital equipment corporation maynard, massachusetts

**DIGITAL INTERNAL USE ONLY**

#### First Edition, May 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

The postpaid Reader's Comment Card included in this document requests the user's critical evaluation to assist in preparing future documentation.

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation:

| KDM          | RSTS                                                                               | VAX FORTRAN                                                                                         |

|--------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| KLESI        | RSX                                                                                | VAX MACRO                                                                                           |

| MASSBUS      | RT                                                                                 | VAXBI                                                                                               |

| MicroVAX     | RV20                                                                               | VAXcluster                                                                                          |

| NI           | RV64                                                                               | VAXELN                                                                                              |

| PDP          | TA                                                                                 | VMS                                                                                                 |

| P/OS         | TK                                                                                 | VT                                                                                                  |

| Professional | ULTRIX                                                                             | Work Processor                                                                                      |

| RA           | UNIBUS                                                                             | XMI                                                                                                 |

| Rainbow      | VAX                                                                                |                                                                                                     |

| RD           | VAX C                                                                              | digital                                                                                             |

|              | KLESI<br>MASSBUS<br>MicroVAX<br>NI<br>PDP<br>P/OS<br>Professional<br>RA<br>Rainbow | KLESI RSX MASSBUS RT MicroVAX RV20 NI RV64 PDP TA P/OS TK Professional ULTRIX RA UNIBUS Rainbow VAX |

- ® IBM is a registered trademark of International Business Machines Corporation.

- ® Intel is a registered trademark of Intel Corporation.

- TM Hubbell is a trademark of Harvey Hubbel, Inc.

- ® Motorola is a registered trademark of Motorola, Inc.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

**DIGITAL INTERNAL USE ONLY**

# **Contents**

| Αb | oout This Manual                                                                                                                                                    | xxiii                                  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1  | General Description                                                                                                                                                 |                                        |

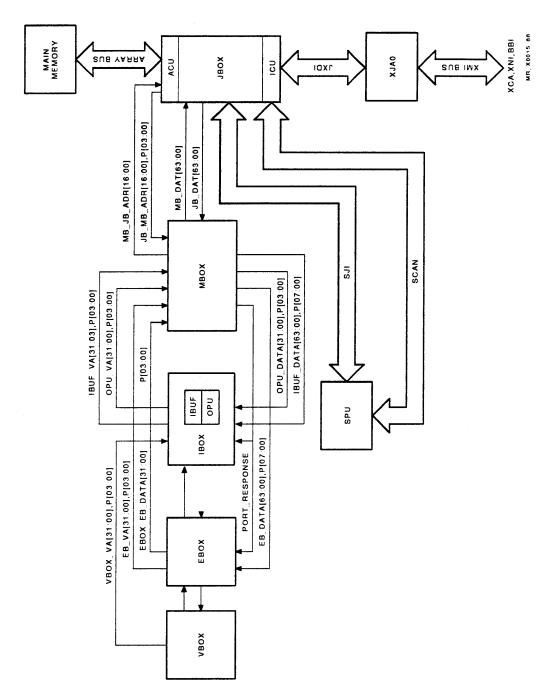

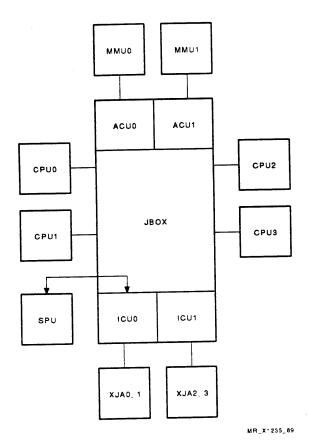

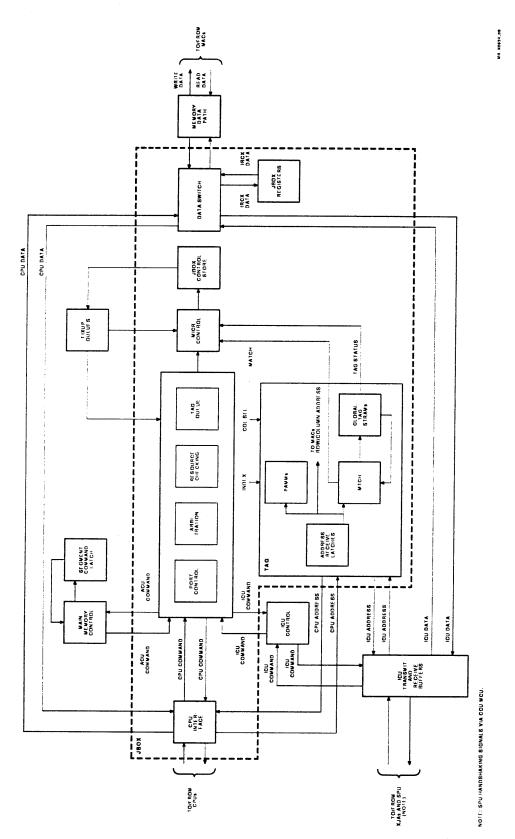

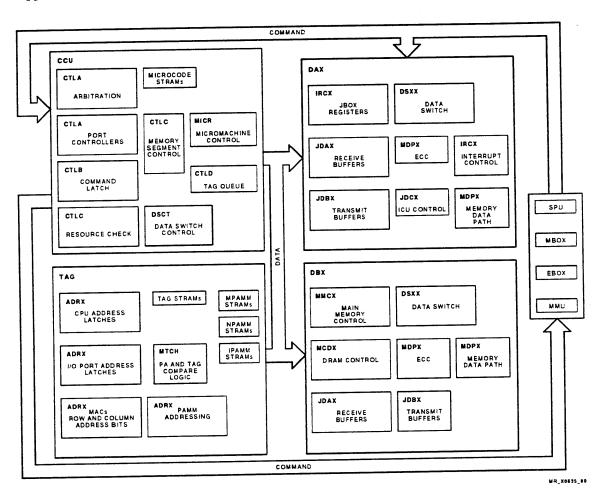

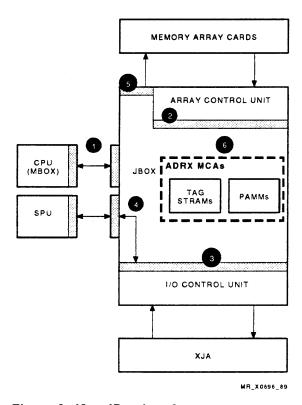

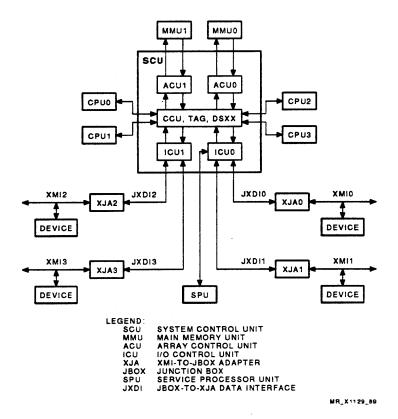

|    | 1.1       Overview         1.1.1       SCU Logical Units         1.1.1.1       JBox         1.1.1.2       Array Control Unit         1.1.1.3       I/O Control Unit | 1-1<br>1-3<br>1-3<br>1-5<br>1-5<br>1-6 |

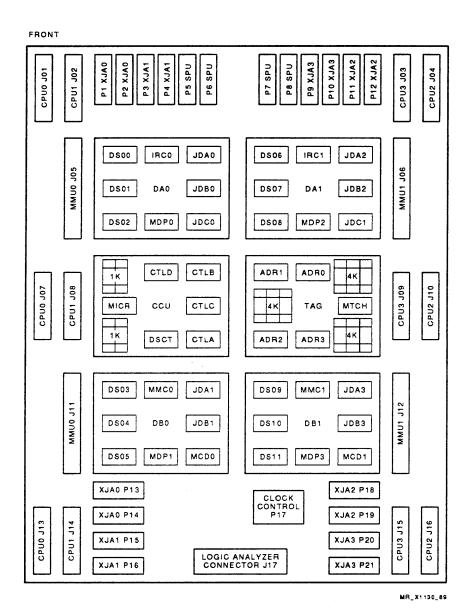

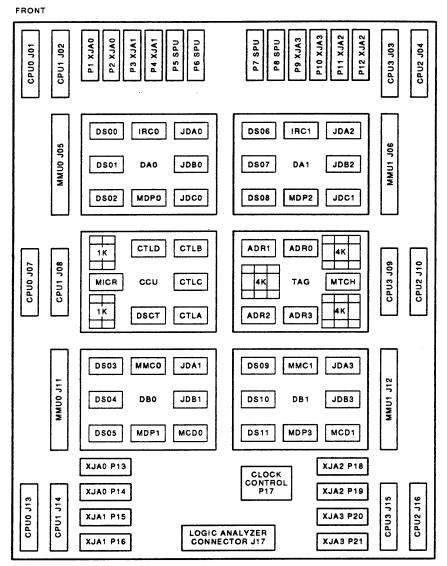

|    | 1.2       Physical Organization         1.2.1       CCU MCU         1.2.2       DAX MCUs         1.2.3       DBX MCUs         1.2.4       Tag MCU                   | 1–9<br>1–9<br>1–10                     |

| 2  | JBox Port Arbitration                                                                                                                                               | 2.4                                    |

|    | 2.1 Overview                                                                                                                                                        |                                        |

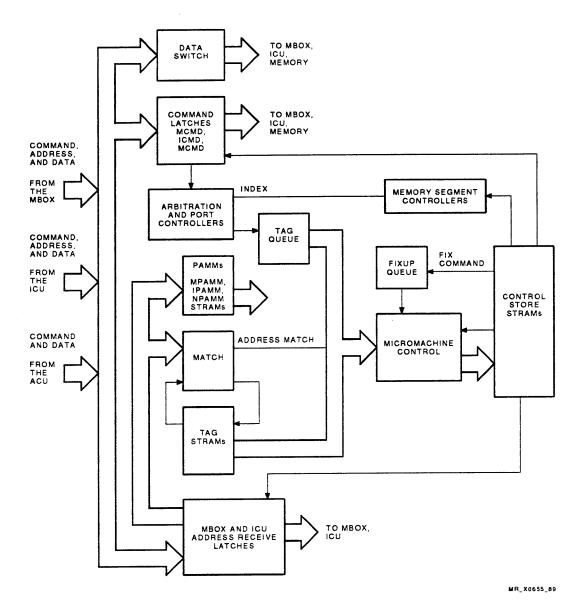

|    | 2.2 JBox Control                                                                                                                                                    | 2–3                                    |

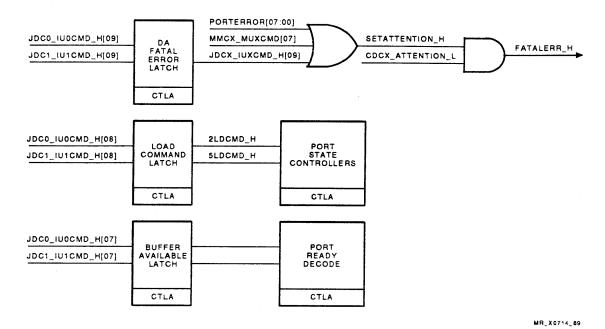

|    | 9.9.1 CTLA MCA                                                                                                                                                      | 2–3                                    |

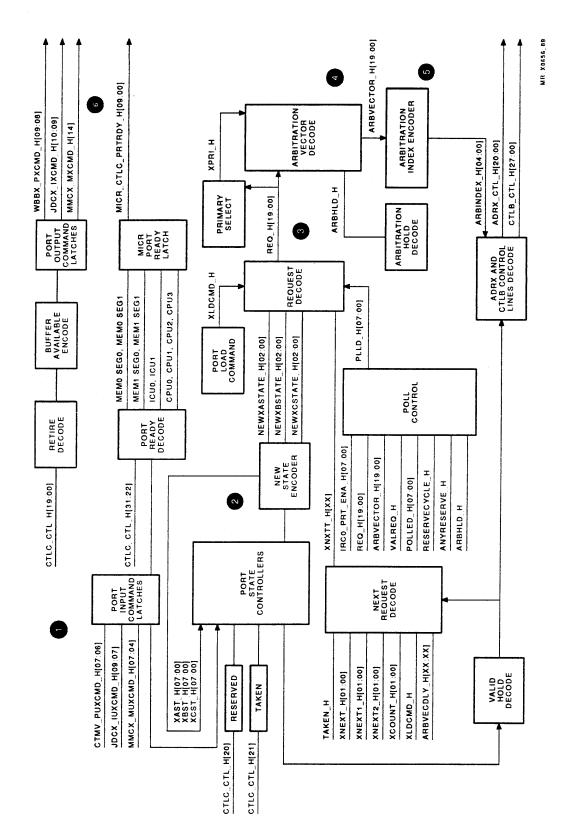

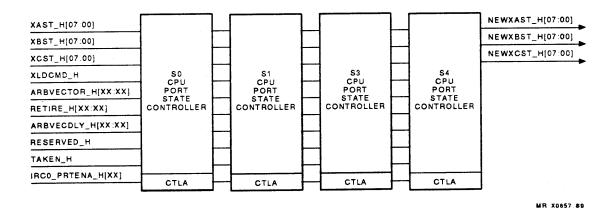

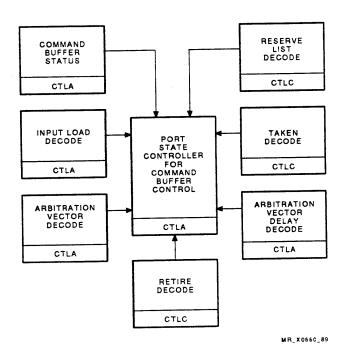

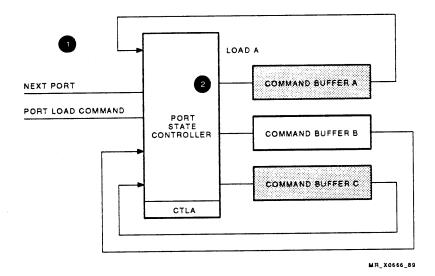

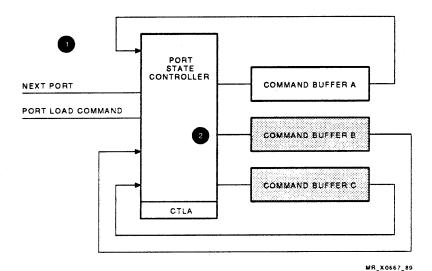

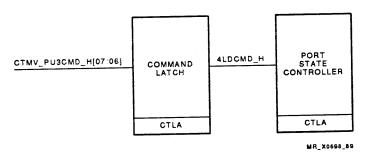

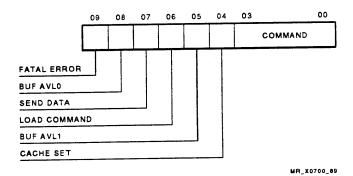

|    | 2 2 1 1 Port State Controllers                                                                                                                                      | . 2–5                                  |

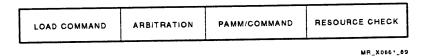

|    | 2 2 1 2 Pipeline Stages                                                                                                                                             | . 2-7                                  |

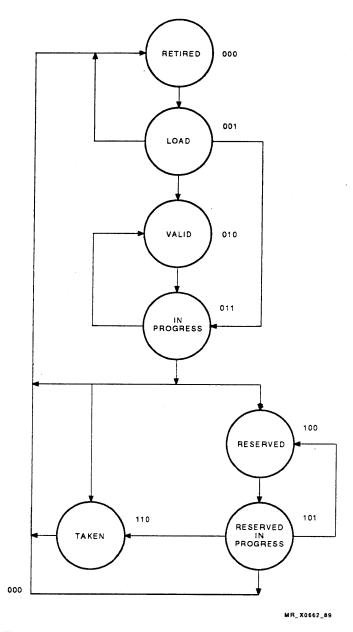

|    | 2.2.1.3 Monitoring the States of a Request                                                                                                                          | . Z-c                                  |

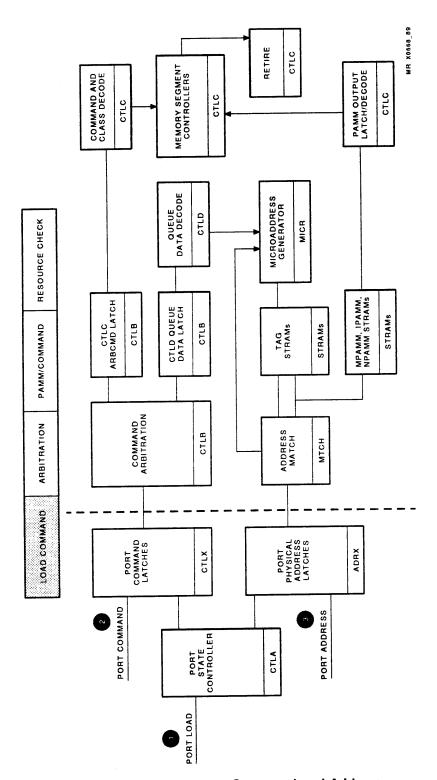

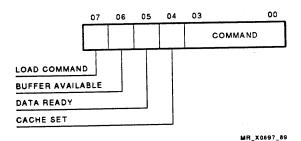

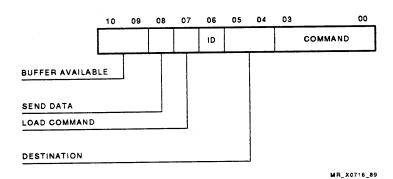

|    | 2.2.1.4 Load Command — Pipeline Stage                                                                                                                               | . <b>2</b> –12                         |

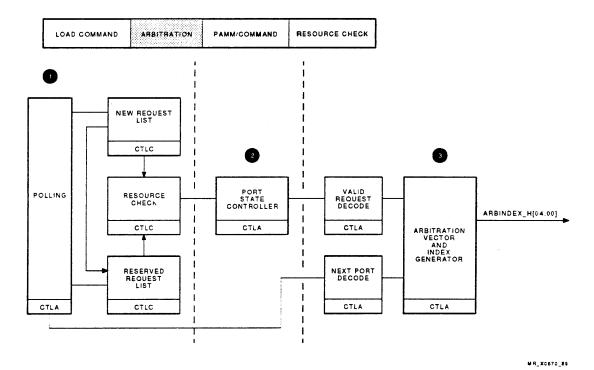

|    | 2.2.1.5 Arbitration                                                                                                                                                 | . 2–14                                 |

|    | 2.2.1.6 Arbitration Index                                                                                                                                           | . 2–17<br>. 2–19                       |

|    | 2.2.1.7 PAMM STRAMs                                                                                                                                                 |                                        |

|    | 2.2.1.8 MPAMM                                                                                                                                                       |                                        |

|    | 2.2.1.9 IPAMM                                                                                                                                                       | -                                      |

|    | 2.2.1.10 NPAMM                                                                                                                                                      |                                        |

|    | 2.2.1.11 CTLA MCA — Inputs and Outputs                                                                                                                              |                                        |

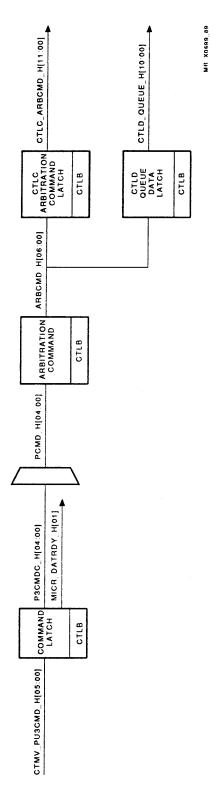

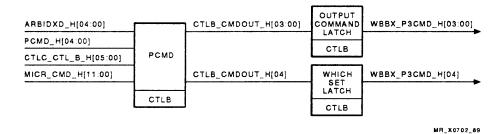

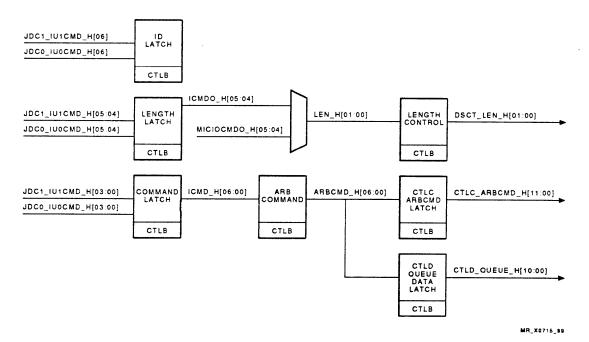

|    | 2.2.2 CTLB MCA                                                                                                                                                      |                                        |

|    | 2.2.2.1 PAMM/CMD Stage                                                                                                                                              | -                                      |

|    | 2.2.2.2 CTLB MCA — Inputs and Outputs                                                                                                                               | . 2-2-                                 |

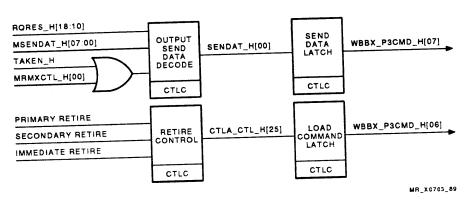

| 2.2.3  | CTI C MCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 00 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–26 |

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–28 |

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–32 |

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–33 |

| 2.2.3  | -y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2–34 |

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–35 |

| 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–35 |

| 2.2.3. | The state of the s | 2–36 |

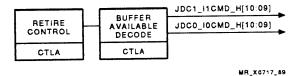

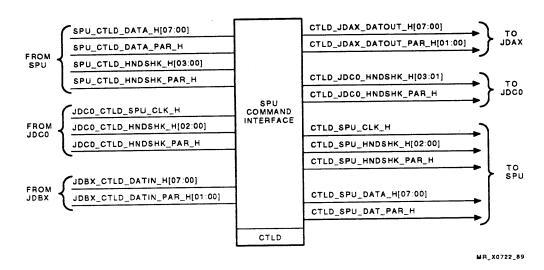

|        | CTLD MCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2–37 |

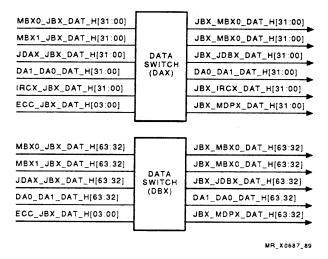

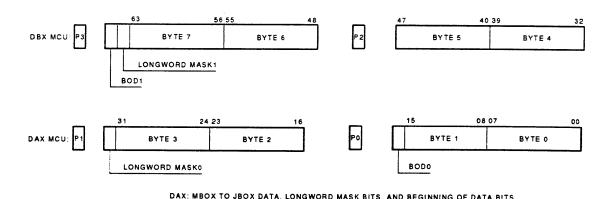

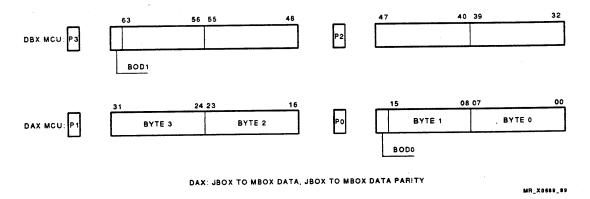

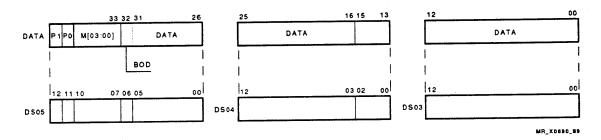

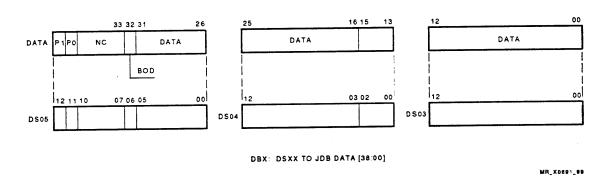

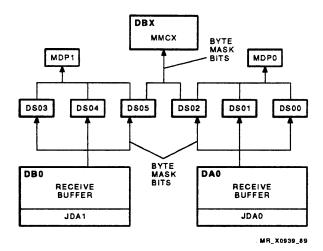

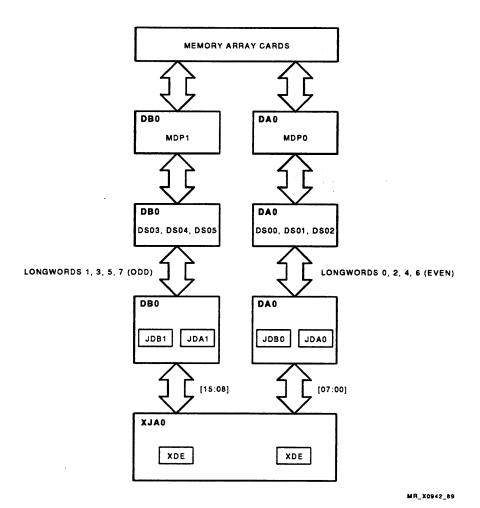

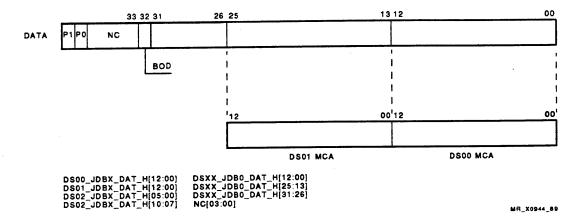

| 2.3    | JBox Data Paths and Data Path Control (DSXX and DSCT MCAs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–39 |

| 2.4    | JBox Address Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2–42 |

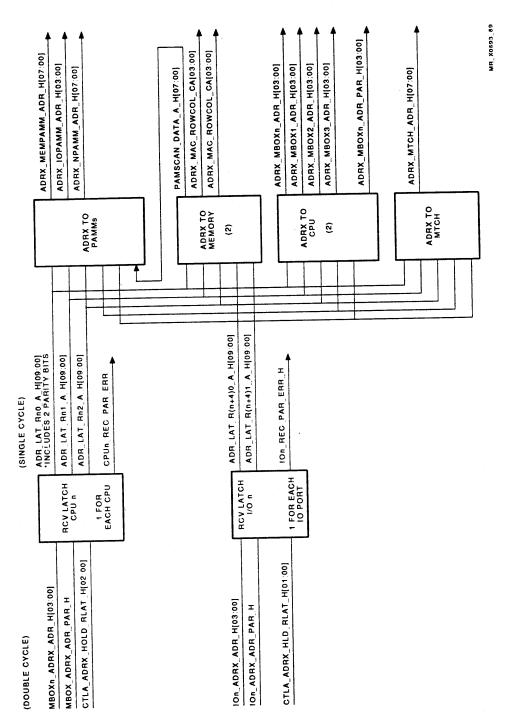

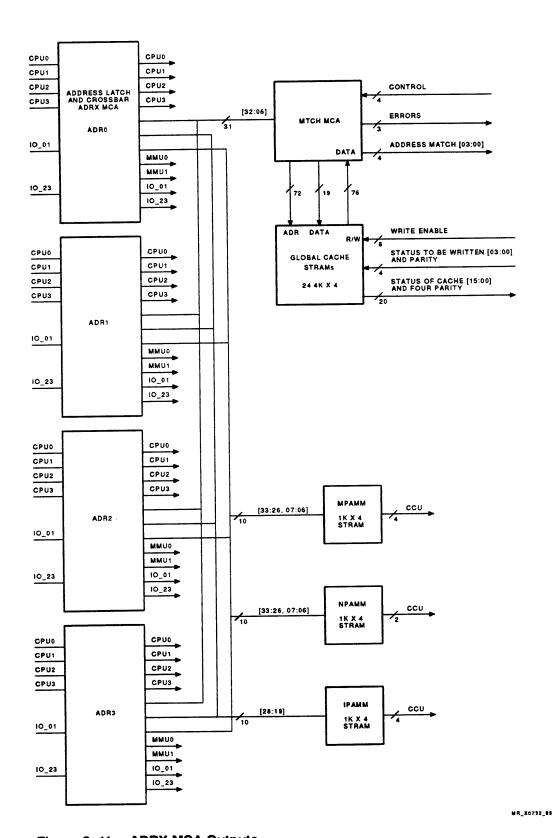

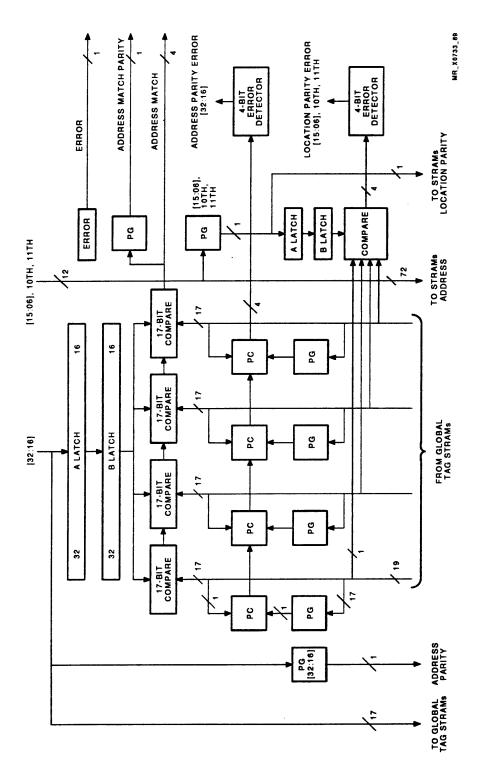

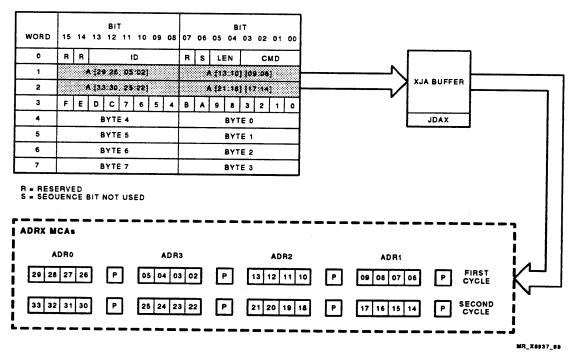

| 2.4.1  | ADRX MCAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-42 |

| 2.4.2  | Address Receive Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-44 |

| 2.4.2. | - Of O Indecire Educates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-44 |

| 2.4.2. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-46 |

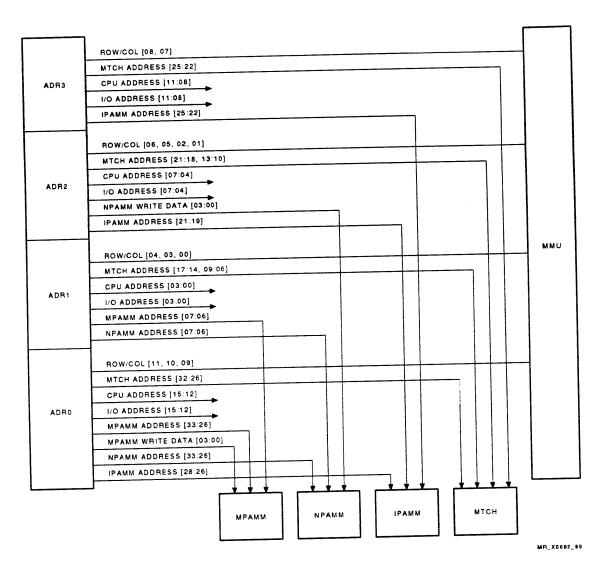

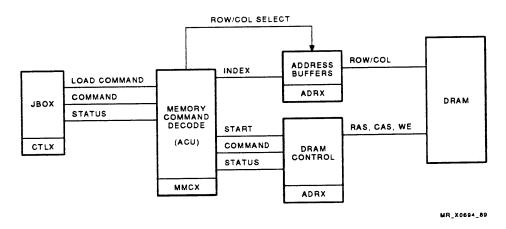

| 2.4.3  | JBox-to-Memory Address Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-47 |

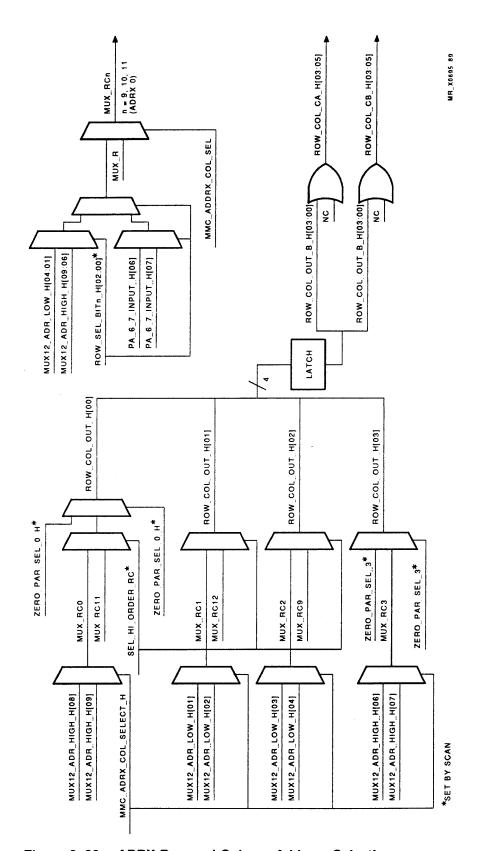

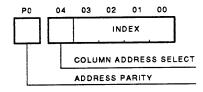

| 2.4.3. | DRAM Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-47 |

| 2.4.3. | PAMM STRAMs Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-49 |

| 2.5    | JBox Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–50 |

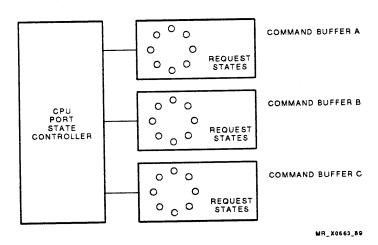

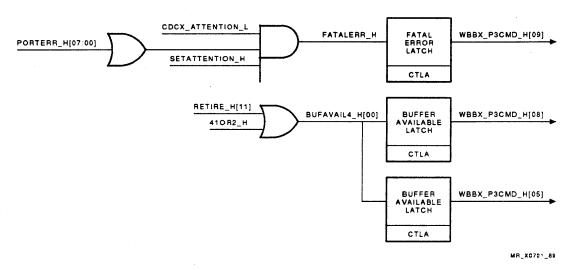

| 2.6    | CPU (MBox) Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2–50 |

| 2.6.1  | ID IZ O' 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–55 |

| 2.6.2  | TD G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2–57 |

| 2.6.3  | NAD TZ O: )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2–58 |

| 2.6.4  | Arp. o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-60 |

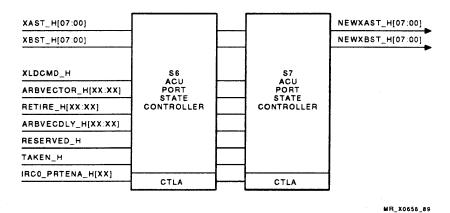

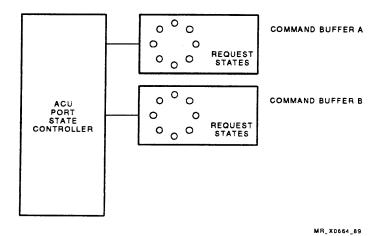

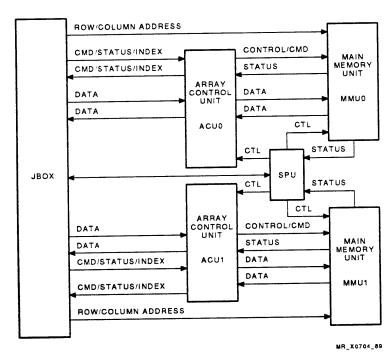

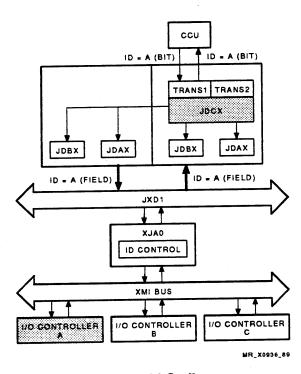

| 2.7    | ACU Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2–61 |

| 2.7.1  | ID IZ O: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–69 |

| 2.7.2  | ID C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2–69 |

| 2.7.3  | A CITY TZ CO: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–69 |

| 2.7.4  | ACTIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2–69 |

| 2.7.5  | DJ.D.CII D. J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2–69 |

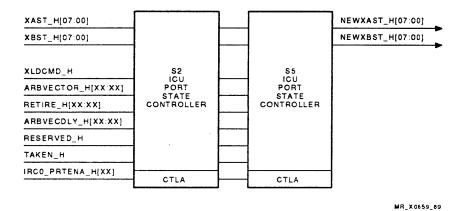

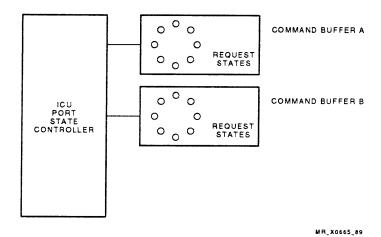

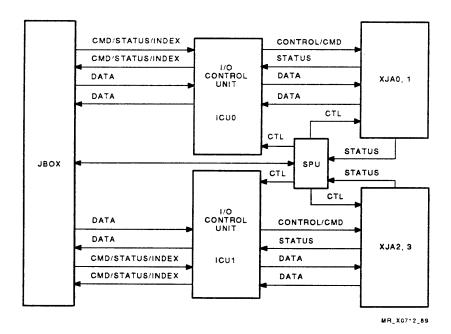

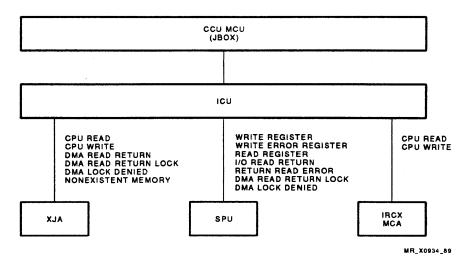

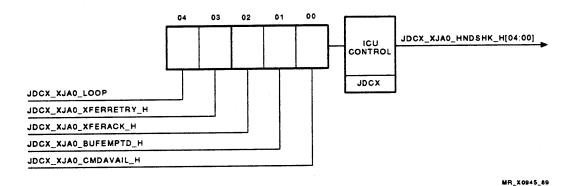

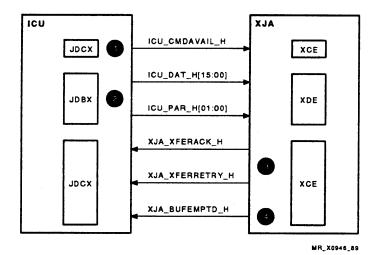

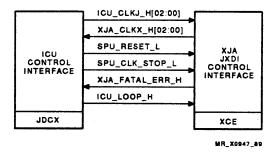

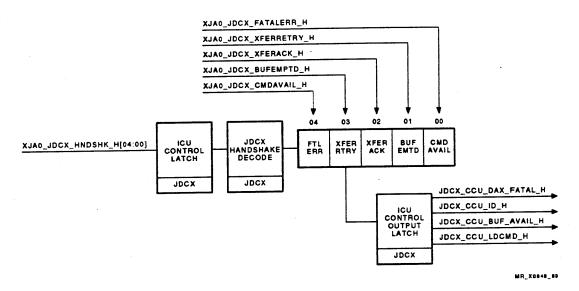

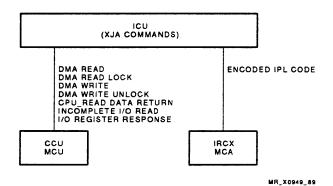

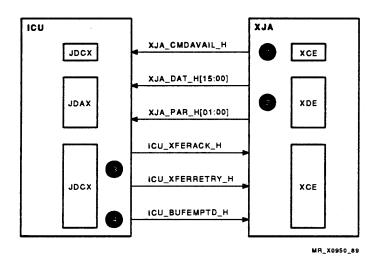

| 2.8    | ICU Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2–70 |

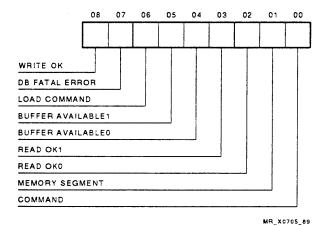

| 2.8.1  | JBox Key Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2–75 |