# VAX 9000 Family XJA Technical Description

Order Number EK-KA90A-TD-001

digital equipment corporation maynard, massachusetts

DIGITAL INTERNAL USE ONLY

#### First Edition, May 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

The postpaid Reader's Comment Card included in this document requests the user's critical evaluation to assist in preparing future documentation.

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation:

| BI        | KDM          | RSTS   | VAX FORTRAN    |

|-----------|--------------|--------|----------------|

| CI        | KLESI        | RSX    | VAX MACRO      |

| DEC       | MASSBUS      | RT     | VAXBI          |

| DECmate   | MicroVAX     | RV20   | VAXcluster     |

| DECUS     | NI           | RV64   | VAXELN         |

| DECwriter | PDP          | TA     | VMS            |

| DHB32     | P/OS         | TK     | $\mathbf{VT}$  |

| DIBOL     | Professional | ULTRIX | Work Processor |

| DRB32     | RA           | UNIBUS | XMI            |

| EDT       | Rainbow      | VAX    |                |

| KDB50     | RD           | VAX C  | digital        |

® IBM is a registered trademark of International Business Machines Corporation.

® Intel is a registered trademark of Intel Corporation.

<sup>TM</sup> Hubbell is a trademark of Harvey Hubbel, Inc.

De Motorola is a registered trademark of Motorola, Inc.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

#### DIGITAL INTERNAL USE ONLY

# Contents

# **About This Manual**

xiii

# 1 General Description

| 1.1 I/O Configuration                                      | . 1–1  |

|------------------------------------------------------------|--------|

| 1.1.1 JXDI Bus                                             | . 1–1  |

| 1.1.2 XJA                                                  | . 1–3  |

| 1.1.3 XMI Bus                                              | . 1–4  |

| 1.1.4 XMI Node Adapters                                    | . 1–4  |

| 1.2 Physical Configuration                                 | . 1–5  |

| 1.3 XJA Registers                                          | . 1–7  |

| 1.4 XJA Transactions                                       | . 1–8  |

| 1.4.1 DMA Transactions                                     | . 1–11 |

| 1.4.2 CPU Transactions                                     | . 1–16 |

| 1.4.2.1 CPU Transactions to XMI Nodes (Excluding XJA)      | . 1–16 |

| 1.4.2.2 CPU Transactions to XJA Private Registers          | . 1–20 |

| 1.4.2.3 CPU Transactions to XMI Space Registers            | . 1–21 |

| 1.4.3 Interrupt Transactions                               | . 1–21 |

| 1.4.3.1 XJA Interrupts                                     | . 1–21 |

| 1.4.3.2 XMI Interrupts                                     | . 1–23 |

| 1.4.4 Add-On Self-Test                                     | . 1–24 |

| 1.5 System Address Space                                   | . 1–24 |

| 1.5.1 System I/O Space Allocation                          | . 1–25 |

| 1.5.2 XJA Private Register Space                           | . 1–27 |

| 1.5.3 XMI I/O Space Allocation                             | . 1–28 |

| 1.5.4 XMI Address to VAX 9000 System Address               | . 1–28 |

| 1.5.5 VAX 9000 System Address to XMI Address               | . 1–30 |

| 1.5.5.1 VAX 9000 System Address to XMI Node Space Address  |        |

| 1.5.5.2 VAX 9000 System Address to BI Window Space Address | . 1–33 |

## 2 JXDI Bus

| 2.1 J              | XDI Description                         | 2–1    |

|--------------------|-----------------------------------------|--------|

| 2.1.1              | DMA Transactions                        | 2–5    |

| 2.1.2              | CPU Transactions                        | 2–5    |

| 2.1.3              | Interrupt Transactions                  | 2–5    |

| 2.1.4              | JXDI Transfer Functions                 | 2–5    |

| 2.2 D              | MA Read                                 | 2–6    |

| 2.2.1              | Command Available Cycle                 | 2–9    |

| 2.2.2              | Read Request Command Cycle              | 2–9    |

| 2.2.2.1            | Command Field                           | 2–9    |

| 2.2.2.2            | Length Field                            | 2–9    |

| 2.2.2.3            | ID Field                                | 2–10   |

| 2.2.3              | Address Cycles                          | 2–10   |

| 2.2.4              | Memory Address Wraps                    | 2–10   |

| 2.2.5              | Data Parity                             | 2 - 12 |

| 2.2.6              | Acknowledge Cycle and Retry Cycle       | 2–12   |

| 2.2.7              | ICU Buffer Emptied Cycle                | 2 - 12 |

| 2.2.8              | Command Available Cycle                 | 2–12   |

| 2.2.9              | Return Data Command Cycle               | 2 - 13 |

| 2.2.9.1            | Command Field                           | 2–13   |

| 2.2.9.2            | Length Field                            | 2 - 13 |

| 2.2.9.3            | ID Field                                | 2 - 14 |

| 2.2.10             | Data Cycles                             | 2–14   |

| 2.2.11             | Data Parity                             | 2 - 14 |

| 2.2.12             | Acknowledge Cycle and Retry Cycle       | 2–14   |

| 2.2.13             | XJA Buffer Emptied Cycle                | 2 - 14 |

| 2.2.14             | Read Locked Status or Read Error Status | 2 - 15 |

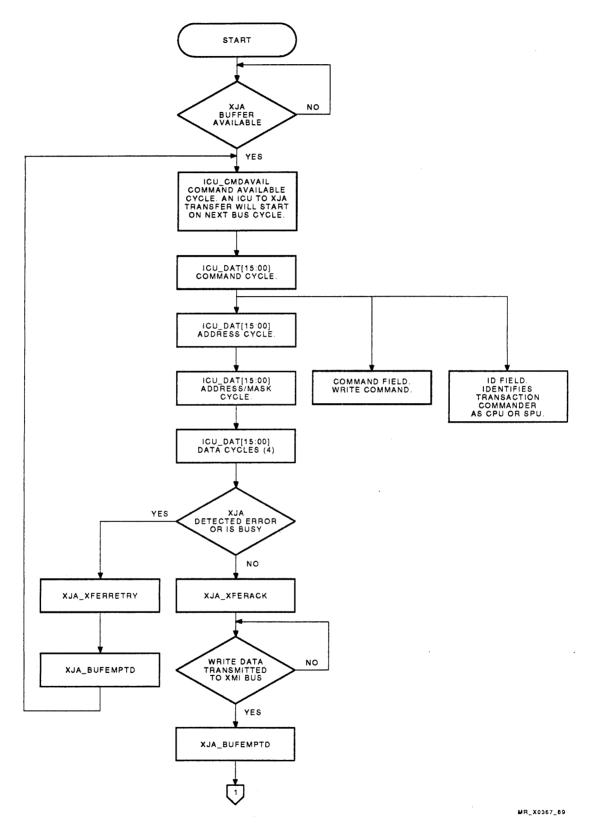

| 2.3 D              | MA Write                                | 2–15   |

| 2.3.1              | Command Available Cycle                 | 2–17   |

| 2.3.2              | Write Command Cycle                     | 2 - 17 |

| 2.3.2.1            | Command Field                           | 2–18   |

| 2.3.2.2            | Length Field                            | 2–18   |

| 2.3.2.3            | ID Field                                | 2–18   |

| 2.3.3              | Address Cycles                          | 2–18   |

| 2.3.4              | Mask Cycle                              | 2–18   |

| 2.3.5              | Data Cycles                             | 2–18   |

| 2.3.6              | Data Parity                             | 2–19   |

| 2.3.7              | Acknowledge Cycle and Retry Cycle       | 2–19   |

| 2.3.8              | ICU Buffer Emptied Cycle                | 2–19   |

| 2.4 C              | PU Read                                 | 2–19   |

| 2.4 0.             | Command Available Cycle                 | 2–19   |

| 2.4.1<br>2.4.2     | Read Request Command Cycle              | 2-23   |

| 2.4.2<br>2.4.2.1   | Command Field                           | 2-23   |

| 2.4.2.1<br>2.4.2.2 | ID Field                                | 2-23   |

| 2.4.2.2<br>2.4.3   | Address Cycles                          | 2-23   |

| 2. I.U             |                                         |        |

| 2.4.4  | Data Parity                       | 2–24         |

|--------|-----------------------------------|--------------|

| 2.4.5  | Acknowledge Cycle and Retry Cycle | 2–24         |

| 2.4.6  | XJA Buffer Emptied Cycle          | 2–24         |

| 2.4.7  | Command Available Cycle           | 2–24         |

| 2.4.8  | Return Data Command Cycle         | <b>2–</b> 25 |

| 2.4.9  | Data Cycles                       | 2–25         |

| 2.4.10 | Data Parity                       | 2–25         |

| 2.4.11 | Acknowledge Cycle and Retry Cycle | 2–25         |

| 2.4.12 | ICU Buffer Emptied Cycle          | 2–26         |

| 2.4.13 | Read Error Status                 | 2–26         |

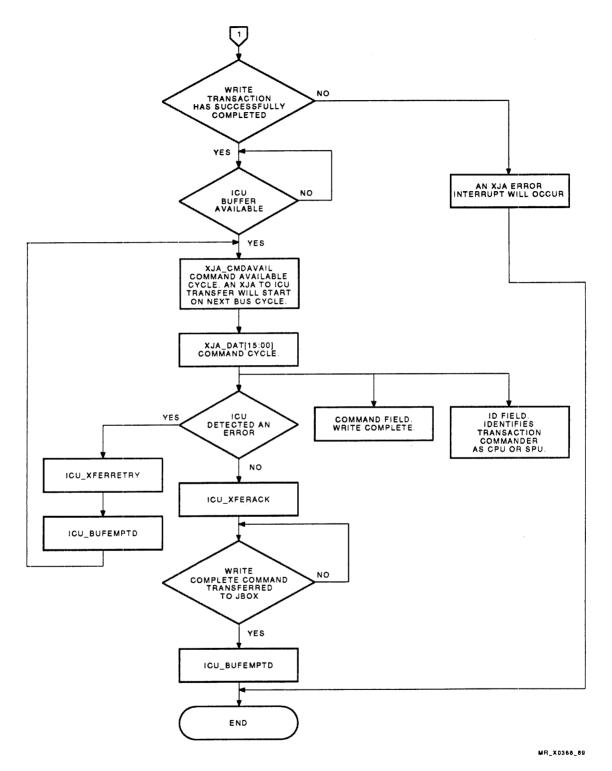

| 2.5    | CPU Write                         | 2–26         |

| 2.5.1  | Command Available Cycle           | 2–29         |

| 2.5.2  | Write Command Cycle               | 2–29         |

| 2.5.3  | Address/Mask Cycles               | 2–29         |

| 2.5.4  | Data Cycles                       | 2–30         |

| 2.5.5  | Data Parity                       | 2–30         |

| 2.5.6  | Acknowledge Cycle and Retry Cycle | 2–30         |

| 2.5.7  | XJA Buffer Emptied Cycle          | 2–30         |

| 2.5.8  | Write Complete Transaction        | 2–31         |

| 2.6    | Interrupt Transactions            | 2–31         |

| 2.7    | Data Envelopes                    | 2–34         |

## 3 XMI Bus

•

| 3.1 X   | MI Description                   | 3–1 |

|---------|----------------------------------|-----|

| 3.1.1   | XMI Clock/Arbiter Module (CCARD) | 3–2 |

| 3.1.2   | XMI Corner                       | 3–2 |

| 3.2 X   | MI Signal Descriptions           | 3–3 |

| 3.2.1   | Arbitration Signals              | 3–4 |

| 3.2.1.1 | XMI_CMD_REQ                      | 3–4 |

| 3.2.1.2 | XMI_RES_REQ                      | 3–4 |

| 3.2.1.3 | XMI_GRANT                        | 3–4 |

| 3.2.1.4 | XMI_HOLD                         | 3–4 |

| 3.2.1.5 | XMI_SUP                          | 3-4 |

| 3.2.2   | Information Signals              | 3–5 |

| 3.2.2.1 | XMI_FUNCTION[03:00]              | 3–5 |

| 3.2.2.2 | XMI_DATA[63:00]                  | 3–5 |

| 3.2.2.3 | XMI_ID[05:00]                    | 3–5 |

| 3.2.2.4 | XMI_PARITY[02:00]                | 3–6 |

| 3.2.3   | Response Signal: XMI_CNF[02:00]  | 3–6 |

| 3.2.4   | Control Signals                  | 3–7 |

| 3.2.4.1 | XMI_BAD                          | 3–7 |

| 3.2.4.2 | XMI_FAULT                        | 3–7 |

| 3.2.4.3 | XMI_DEFAULT                      | 3–7 |

| 3.2.4.4 | XMI_RESET                        | 3–7 |

| 3.2.4.5            | XMI_TIME                                  | 3–7          |

|--------------------|-------------------------------------------|--------------|

| 3.2.4.6            | XMI_PHASE                                 | 3-7          |

| 3.2.4.7            | XMI_AC_LO                                 | 3-7          |

| 3.2.4.8            | XMI_DC_LO                                 | 3-7          |

| 3.2.5              | Miscellaneous Signal: XMI_NODE_ID[03:00]  | 3-7          |

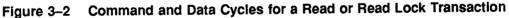

|                    | ead and Read Lock Transactions            | 38           |

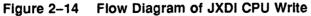

| 3.3.1              | Longword and Quadword Read                | 3-9          |

| 3.3.1.1            | Arbitration                               | 3-9          |

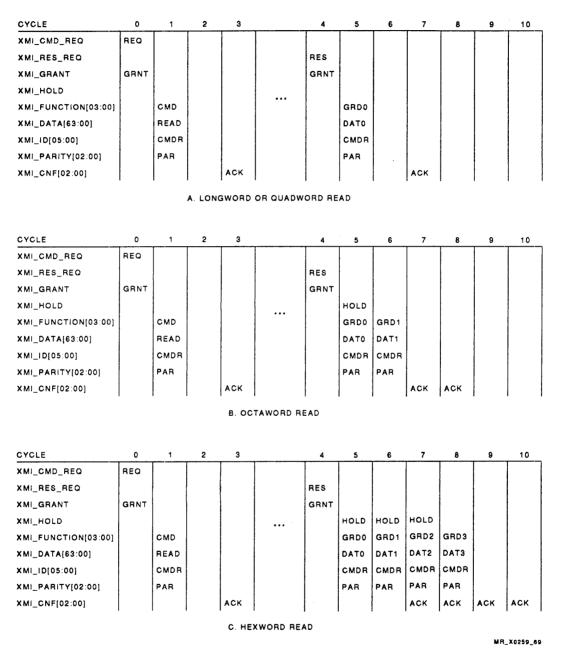

| 3.3.1.2            | Command Cycle                             | 3-9          |

| 3.3.1.3            | Acknowledge Cycle                         | 3-10         |

| 3.3.1.4            | Arbitration                               | 3-11         |

| 3.3.1.5            | Read Data Cycle                           | 3–11         |

| 3.3.1.6            | Acknowledge Cycle                         | 3–11         |

| 3.3.2              | Octaword Read                             | 3–11         |

| 3.3.2.1            | Arbitration                               | 3–11         |

| 3.3.2.2            | Command Cycle                             | 3-12         |

| 3.3.2.3            | Acknowledge Cycle                         | 3-12         |

| 3.3.2.4            | Arbitration                               | 3-12         |

| 3.3.2.5            | Read Data Cycles                          | 3-12         |

| 3.3.2.6            | Acknowledge Cycles                        | 3–13         |

| 3.3.3              | Hexword Read.                             | 3-13         |

| 3.3.4              | Read Error Responses                      | 3–13         |

| 3.3.4.1            | Correctable Read Error                    | 3-13         |

| 3.3.4.2            | Uncorrectable Read Error                  | 3–14         |

| 3.3.4.3            | Read-Locked Error                         | 3–14         |

| 3.3.5              | Multiple Read-Data-Return Transfers       | 3-15         |

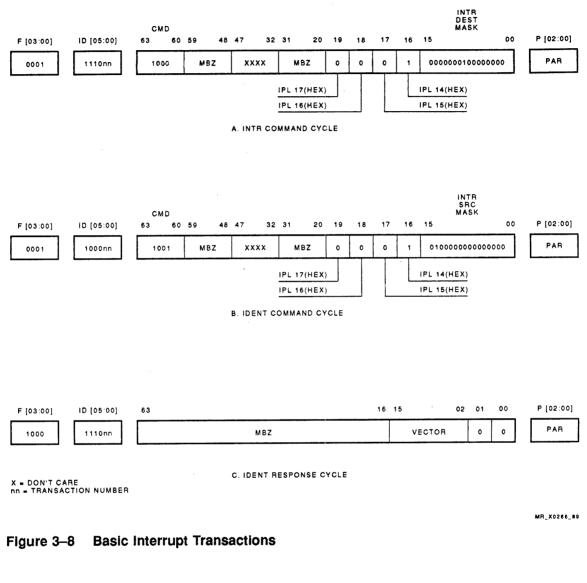

|                    | asked Write and Write Unlock Transactions | 3-15         |

| 3.4.1              | Longword and Quadword Write               | 3-15         |

| 3.4.1<br>3.4.1.1   | Arbitration                               | 3-17         |

| 3.4.1.1<br>3.4.1.2 | Command Cycle                             | 3-17<br>3-17 |

| 3.4.1.2<br>3.4.1.3 | Write Data Cycle                          | 3–18         |

| 3.4.1.3<br>3.4.1.4 | Acknowledge Cycle                         |              |

| 3.4.1.4<br>3.4.2   | Octaword Write                            | 3-18         |

| 3.4.3              | Hexword Write                             | 3-19         |

|                    |                                           |              |

|                    | MI Address Mapping                        | 3–19         |

|                    | terrupt Transactions                      | 3–20         |

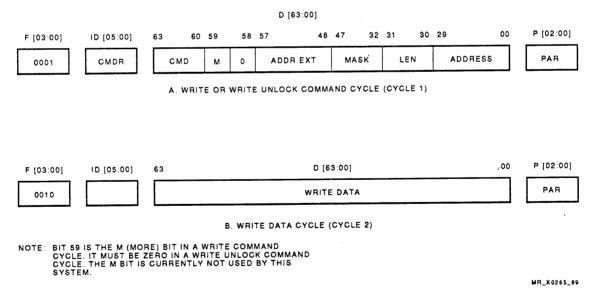

| 3.6.1              | Basic Interrupts                          | 3–20         |

| 3.6.1.1            | INTR Transaction                          | 3–20         |

| 3.6.1.2            | IDENT Transaction                         | 3-22         |

| 3.6.2              | IVINTR Interrupts                         | 3–22         |

.

# 4 XJA

| 4.1 Overview                                                                  | 4–1  |

|-------------------------------------------------------------------------------|------|

| 4.1.1 DMA Read                                                                | 4–5  |

| 4.1.2 DMA Write                                                               | 4-6  |

| 4.1.3 CPU Read of XMI Registers Excluding XMI Space Registers in XJA          | 4–6  |

| 4.1.4 CPU Write of XMI Registers Excluding XMI Space Registers in XJA         | 4–6  |

| 4.1.5 CPU Read of XMI Space Registers in XJA                                  | 4–6  |

| 4.1.6 CPU Write of XMI Space Registers in XJA                                 | 4–7  |

| 4.1.7 CPU Read of XJA Private Registers                                       | 4–7  |

| 4.1.8 CPU Write of XJA Private Registers                                      | 4–8  |

| 4.1.9 XMI Bus Initiated Normal Interrupts                                     | 4–8  |

| 4.1.10 XMI Implied Vector Interrupts — Interprocessor Interrupts              | 48   |

| 4.1.11 XMI Implied Vector Interrupts — Write Error Interrupts                 | 4–9  |

| 4.1.12 XJA Generated Nonfatal Interrupts                                      | 4–9  |

| 4.1.13 XJA Generated Fatal Interrupts                                         | 4–10 |

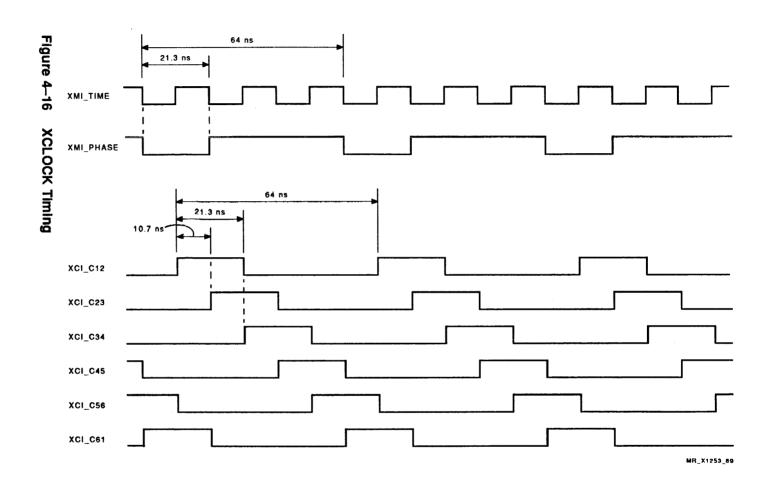

| 4.2 XJA Clock System                                                          | 4–10 |

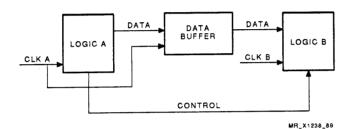

| 4.2.1 Crossing Asynchronous Boundaries Between Clock Systems                  | 4–11 |

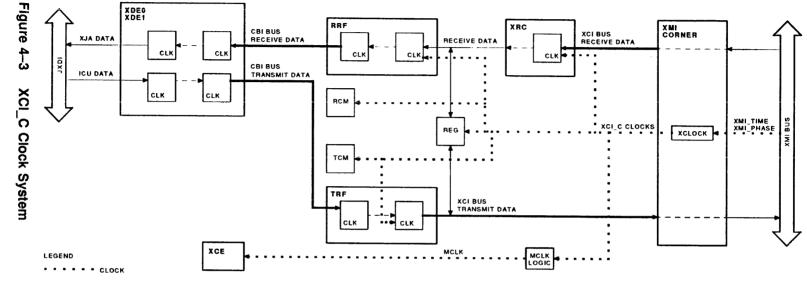

| 4.2.2 XCI_C Clock System                                                      | 4–11 |

| 4.2.3 CLKJ Clock System                                                       | 4–13 |

| 4.2.4 CLKX Clock System                                                       | 4–13 |

| 4.3 XDE Data Flow                                                             | 4–16 |

| 4.3.1 Transmit Data Flow                                                      | 4–16 |

| 4.3.2 Receive Data Flow                                                       | 4–17 |

| 4.3.3 Alignment of Received Data                                              | 4–19 |

| 4.4 XCE Data Flow Control Logic                                               | 4–22 |

| 4.4 ACE Data Flow Control Logic                                               | 4-22 |

| 4.4.2 Receive Logic                                                           | 4-27 |

| -                                                                             |      |

| 4.5 XMI Corner                                                                | 4-31 |

| 4.5.1 Physical Description                                                    | 4-31 |

| 4.5.2 XCI Clocks                                                              | 4–31 |

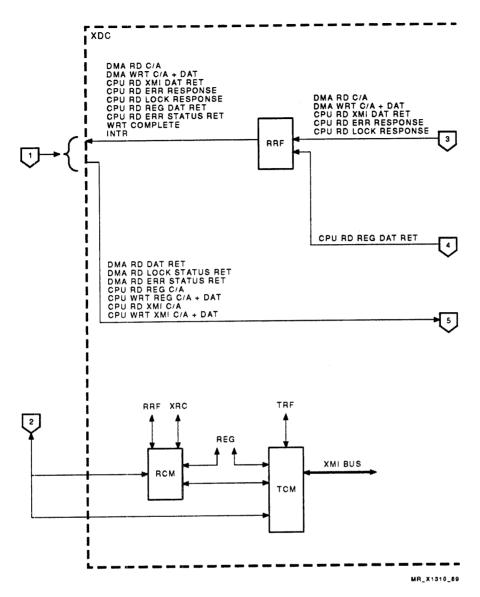

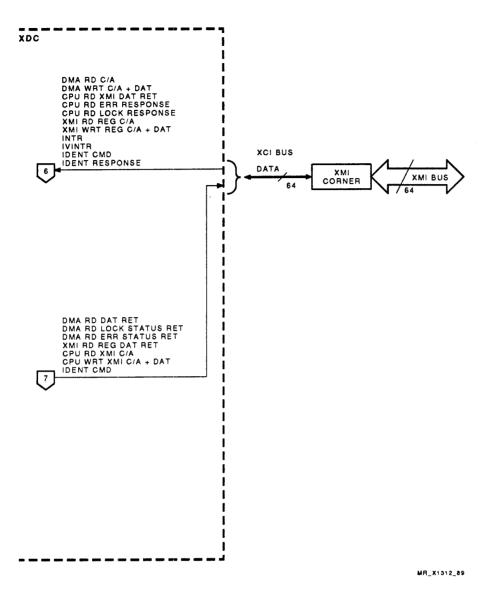

| 4.6 XDC Receive Logic                                                         | 4-33 |

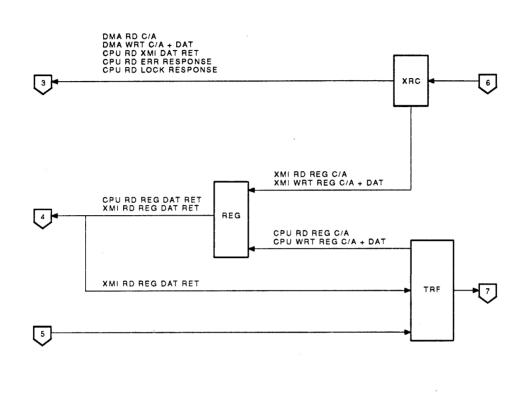

| 4.6.1 XRC                                                                     | 4–33 |

| 4.6.2 RRF                                                                     | 4–38 |

| 4.6.3 Packet Processing                                                       | 4-39 |

| 4.6.3.1 DMA Read/Write Packet Processing                                      | 4-40 |

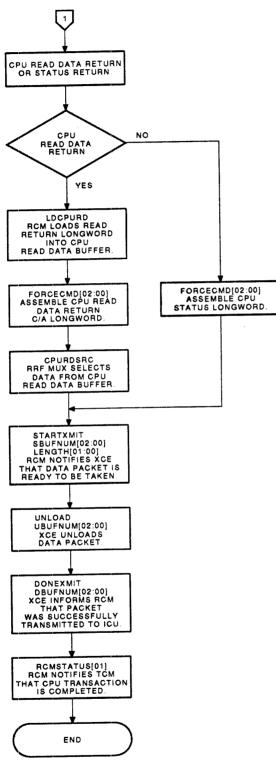

| 4.6.3.2 CPU Read Data Return and CPU Read Status Return                       | 4-43 |

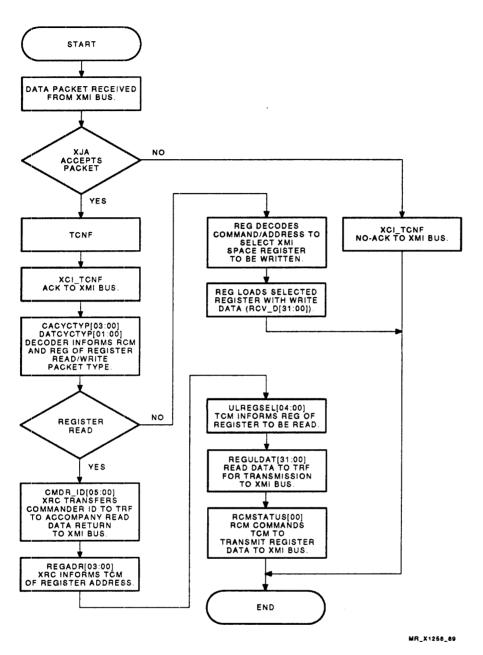

| 4.6.3.3 XMI Read/Write of XMI Space Register Packet Processing                | 4-45 |

| 4.6.3.4 Basic Interrupt and WEI Implied Vector Interrupt Packet<br>Processing | 4-47 |

| 4.6.3.5 IDENT Command Cycle                                                   | 4-48 |

| 4.6.4 CPU Write Complete                                                      | 4-48 |

| 4.6.5 CPU Read of an XJA Private Register                                     | 4–49 |

| 4.7 XDC Transmit Logic                                                        | 4-49 |

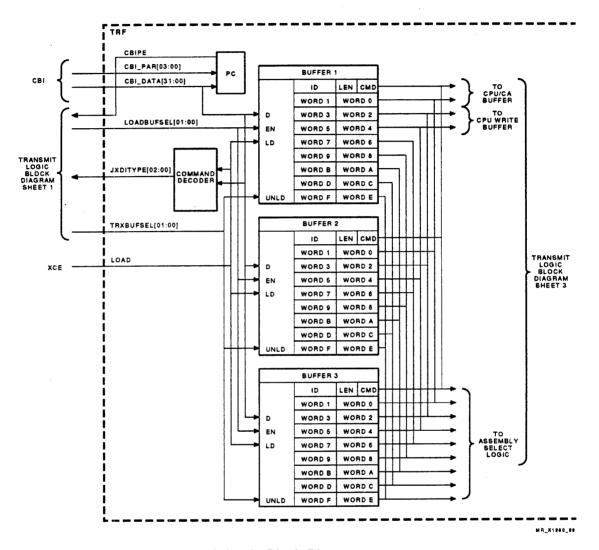

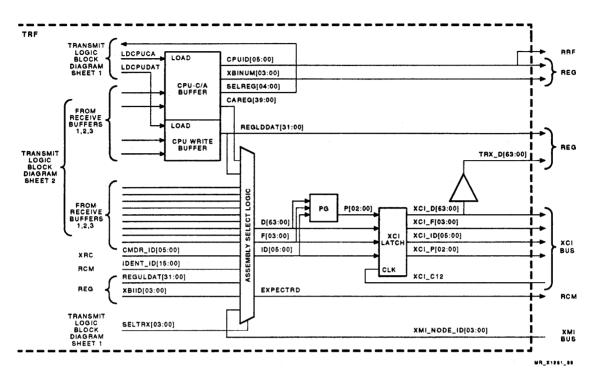

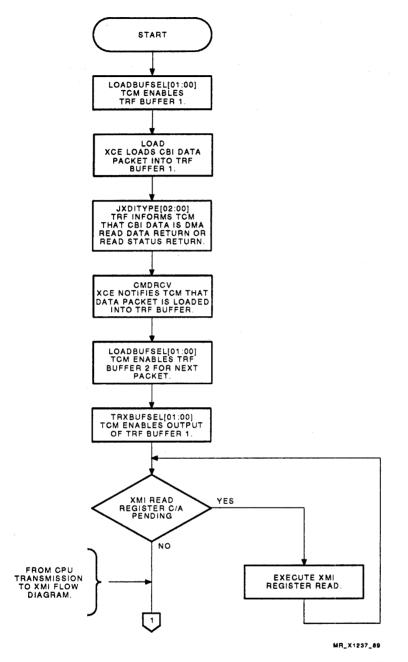

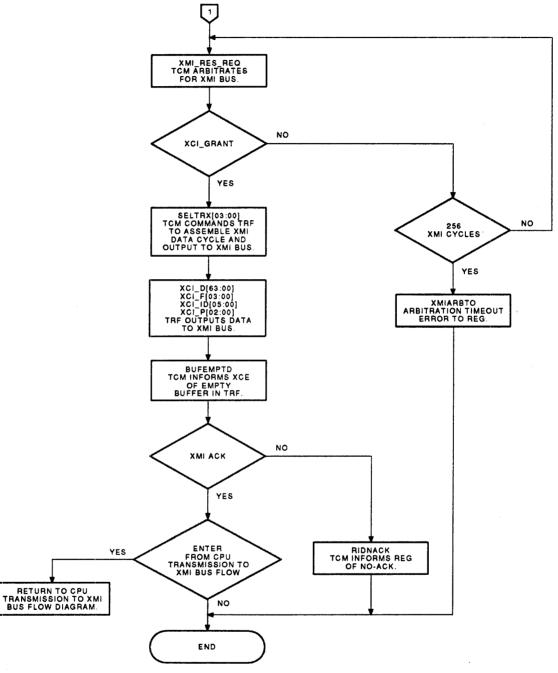

| 4.7.1 Transmit Register File                                                  | 4–51 |

| DMA Read Data Return                                 | 4–54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                      | 4-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

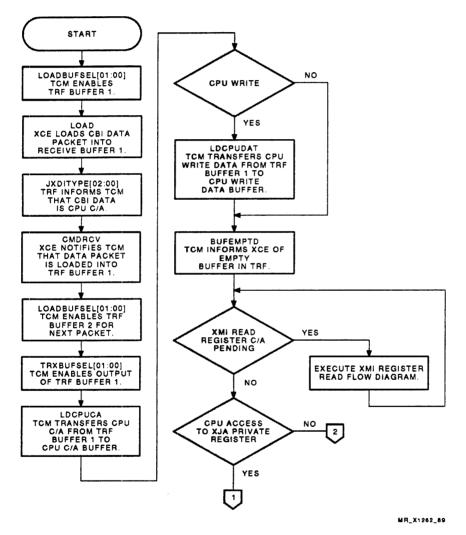

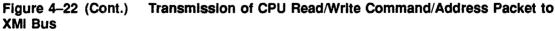

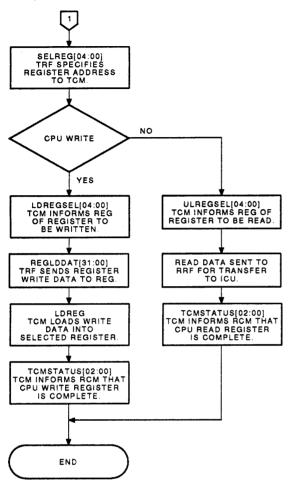

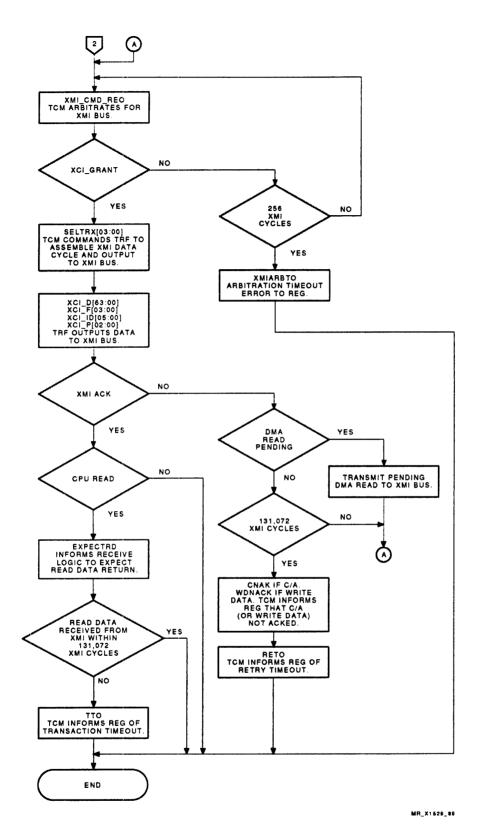

| CPU Read/Write                                       | 4-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Access to XJA Private Register                       | 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Access to XMI Register                               | 4–62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Read Register Data Return                            | 4-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IDENT                                                | 4-65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A Registers (REG)                                    | 4-65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI Space Registers                                  | 4–65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XJA Private Registers                                | 465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

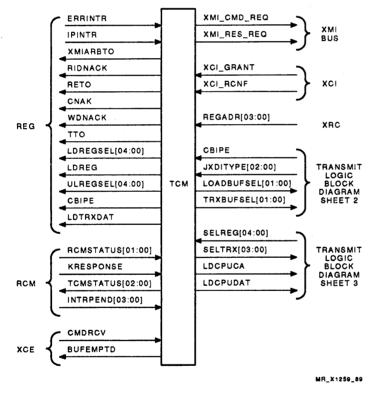

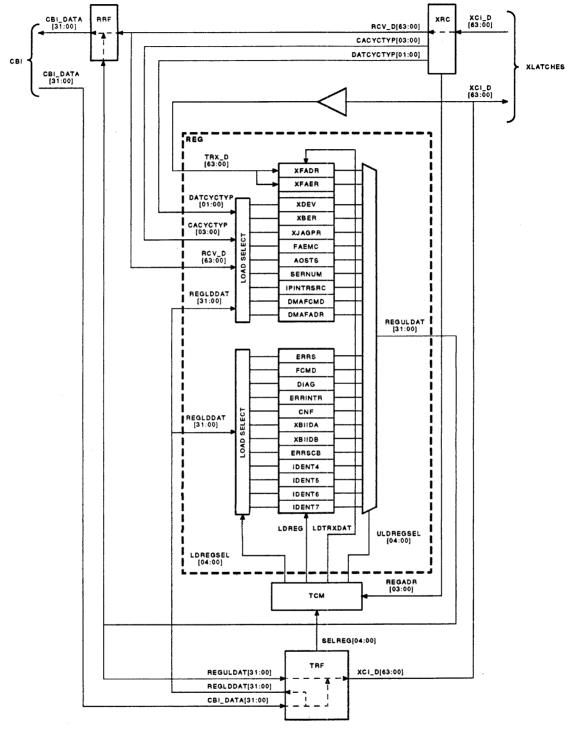

| REG Data Flow                                        | 4–66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI Space Register Read                              | 4-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI Space Register Write                             | 4–68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CPU Register Read of XJA Private Register            | 4-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CPU Register Write of XJA Private Register           | 4–68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI Failing Address Register                         | 4–68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DMA Failing Command/Address Registers                | 4–69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| errupts                                              | 469                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Nonfatal Interrupts                                  | 4–69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI Normal Interrupt                                 | 4–69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMI IPINTR (Interprocessor Implied Vector Interrupt) | 4–70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Nonfatal Errors Detected by XJA                      | 4–70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fatal Interrupts                                     | 4–71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

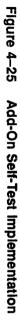

| d-On Self-Test                                       | 4-71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AOST Implementation                                  | 4–71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

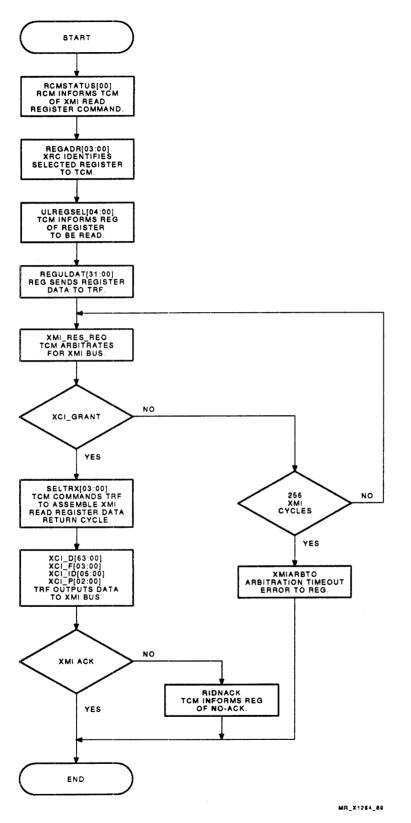

| XJA Register Read Transaction                        | 4–77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XJA Register Write Transaction                       | 4-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                      | Access to XJA Private RegisterAccess to XMI RegisterRead Register Data ReturnIDENTA Registers (REG)XMI Space RegistersXJA Private RegistersXJA Private RegistersREG Data FlowXMI Space Register ReadXMI Space Register ReadXMI Space Register WriteCPU Register Read of XJA Private RegisterCPU Register Write of XJA Private RegisterCPU Register Write of XJA Private RegisterMA Failing Address RegisterDMA Failing Command/Address RegistersNonfatal InterruptsXMI Normal InterruptXMI IPINTR (Interprocessor Implied Vector Interrupt)Nonfatal Errors Detected by XJAFatal InterruptsAOST ImplementationXJA Register Read Transaction |

# 5 Register Descriptions

| 5.1   | XJA Register Overview                       | 5–1    |

|-------|---------------------------------------------|--------|

| 5.2   | XMI Space Registers                         | 5–3    |

| 5.2.1 | Device Register                             | 5–3    |

| 5.2.2 | XMI Bus Error Register                      | 5–4    |

| 5.2.3 | Failing Address Register                    | 5–11   |

| 5.2.4 | Failing Address Extension Register          | 5 - 12 |

| 5.2.5 | XJA General-Purpose Register                | 5–13   |

| 5.2.6 | Full System Emulation Mode Control Register | 5–13   |

| 5.2.7 | Add-On Self-Test Status Register            | 5–14   |

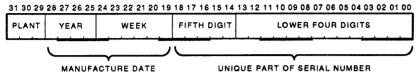

| 5.2.8 | XJA Serial Number Register                  | 5–15   |

| 5.3   | XJA Private Registers                       | 5–17   |

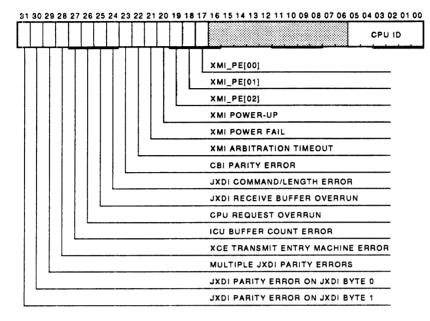

| 5.3.1 | Error Summary Register                      | 5–18   |

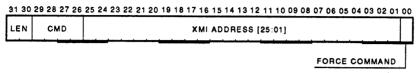

| 5.3.2 | Force Command Register                      | 5–21   |

| 5.3.3 | Interprocessor Interrupt Source Register    | 5–23   |

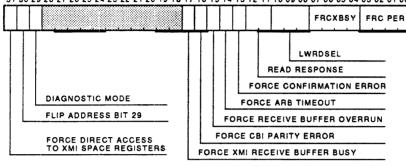

| 5.3.4 | XJA Diagnostic Control Register             | 5–24   |

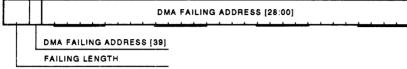

| 5.3.5  | DMA Failing Address Register     | 5–28 |

|--------|----------------------------------|------|

| 5.3.6  | DMA Failing Command Register     | 5–29 |

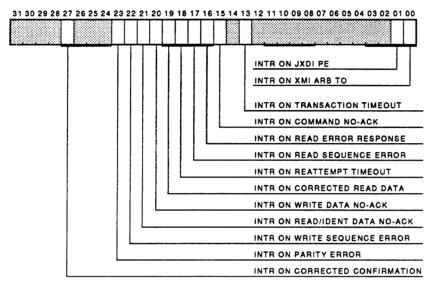

| 5.3.7  | Error Interrupt Control Register | 5–30 |

| 5.3.8  | Configuration Register           | 5–32 |

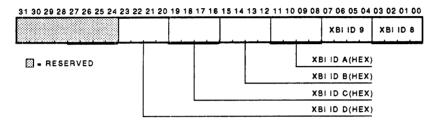

| 5.3.9  | XBI ID A Register                | 5–33 |

| 5.3.10 | XBI ID B Register                | 5–34 |

| 5.3.11 | Error SCB Offset Register        | 535  |

| 5.3.12 | SCB Offset IPL 14(Hex) Register  | 5–36 |

| 5.3.13 | SCB Offset IPL 15(Hex) Register  | 5–37 |

| 5.3.14 | SCB Offset IPL 16(Hex) Register  | 538  |

| 5.3.15 | SCB Offset IPL 17(Hex) Register  | 5–39 |

|        |                                  |      |

# Index

| Figure | S                                                         |        |

|--------|-----------------------------------------------------------|--------|

| 1-1    | System I/O Block Diagram                                  | 1–2    |

| 1-2    | XJA Simplified Block Diagram                              | 1–3    |

| 1-3    | XMI Card Cage                                             | 1–6    |

| 1-4    | XJA Block Diagram                                         | 1–9    |

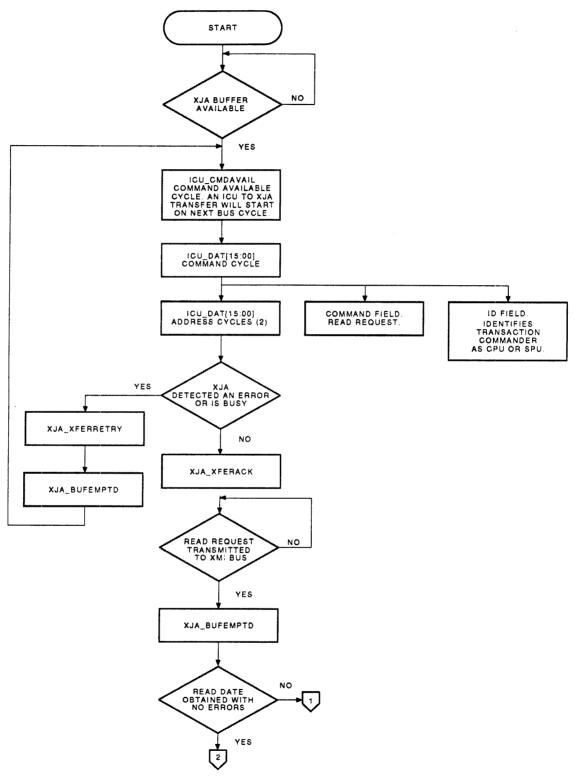

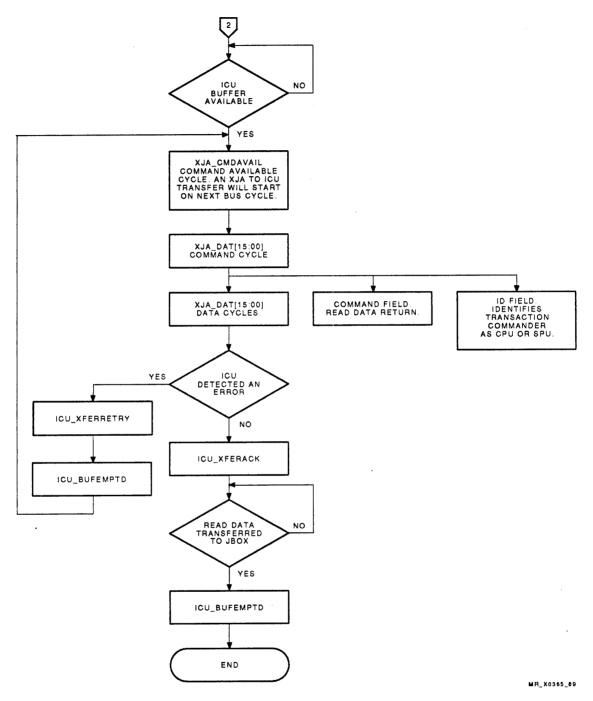

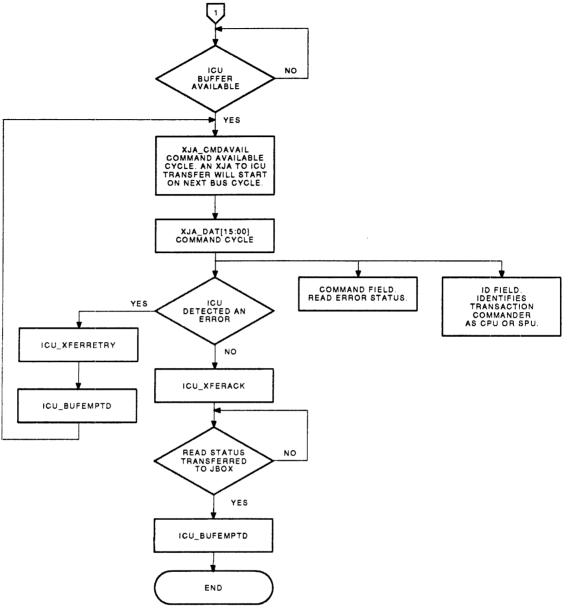

| 15     | Flow Diagram of DMA Transactions                          | 1 - 12 |

| 1-6    | Flow Diagram of CPU Transactions                          | 1–17   |

| 1-7    | Flow Diagram of Interrupt Transactions                    | 1 - 22 |

| 1-8    | System Address Space                                      | 1 - 24 |

| 1-9    | System I/O Space Allocation                               | 1 - 25 |

| 1-1    | 0 Address of XMI Space Registers                          | 1–26   |

| 1-1    | 1 Address of XJA Private Registers                        | 1 - 27 |

| 1-1    | 2 XMI I/O Space Allocation                                | 1–29   |

| 1-1    |                                                           | 1–30   |

| 1-1    | 4 Flow Diagram of CPU Request Address Processing          | 1 - 32 |

| 2-1    | JXDI Signals                                              | 2-1    |

| 2-2    | ICU and XJA Transmit and Receive Buffers                  | 2-4    |

| 2–3    | Flow Diagram of JXDI DMA Read or Read Lock                | 2–6    |

| 2-4    | DMA Read Request or Read Lock Request Bus Cycles          | 2–9    |

| 2-5    | Octaword and Hexword Wraparound Reads                     | 2 - 11 |

| 2-6    | DMA Read Data Return or Read Lock Data Return Bus Cycles  | 2–13   |

| 2–7    | DMA Read Locked Status or Read Error Status Command Cycle | 2-15   |

| 28     | - ·····                                                   | 2–16   |

| 2–9    |                                                           | 2-17   |

| 2-1    |                                                           | 2–20   |

| 2–1    |                                                           |        |

| 2–1    |                                                           |        |

| 2-1    |                                                           |        |

| 2-1    |                                                           |        |

| 2-2    |                                                           |        |

| 2–1    | 6 Flow Diagram of Interrupt Transactions                  | 2–32   |

| 2–17 | Interrupt Request Command Cycle                                                    | 2–33 |

|------|------------------------------------------------------------------------------------|------|

| 3–1  | Read or Read Lock Transactions                                                     | 3–8  |

| 3–2  | Command and Data Cycles for a Read or Read Lock Transaction                        | 3–9  |

| 3–3  | Uncorrectable Read Error in a Hexword Read Transaction                             | 3–14 |

| 3-4  | Read Lock Transaction to a Locked Location                                         | 3–14 |

| 3–5  | Octaword Read Transaction with Multiple Read-Data-Return Transfers                 | 3–15 |

| 36   | Write or Write Unlock Transactions                                                 | 3–16 |

| 3–7  | Command and Data Cycles for a Write or Write Unlock Transaction                    | 3–17 |

| 3–8  | Basic Interrupt Transactions                                                       | 3–21 |

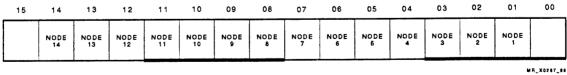

| 3–9  | Interrupt Node Specifier Field                                                     | 3–21 |

| 3–10 | Implied Vector Interrupt Transaction (IVINTR)                                      | 3–22 |

| 4–1  | XJA Block Diagram                                                                  | 4–1  |

| 4-2  | Data Communication Across Asynchronous Boundaries                                  | 4–11 |

| 43   | XCI_C Clock System                                                                 | 4–12 |

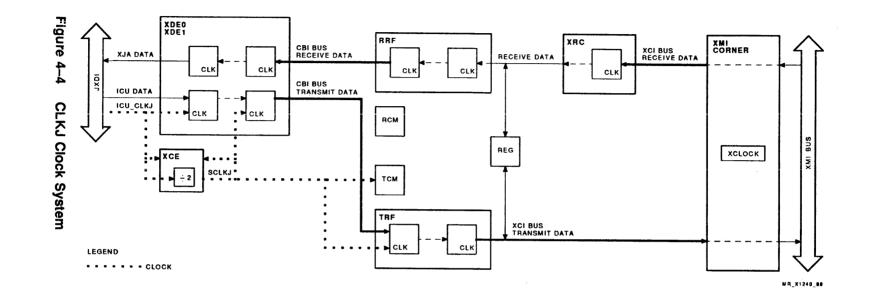

| 4-4  | CLKJ Clock System                                                                  | 4–14 |

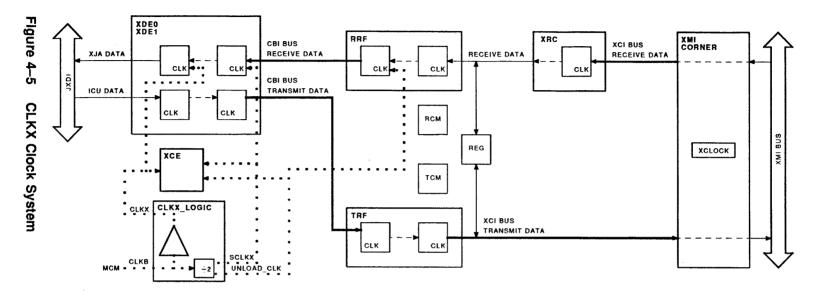

| 45   | CLKX Clock System                                                                  | 4–15 |

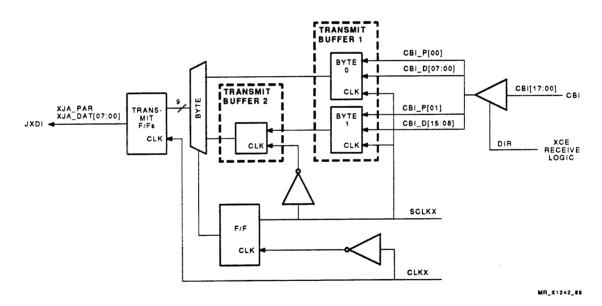

| 46   | XDE Transmit Data Path                                                             | 4–16 |

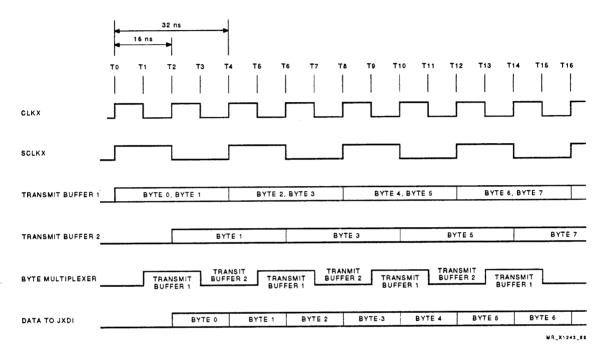

| 4-7  | XDE Transmit Timing Diagram                                                        | 4–17 |

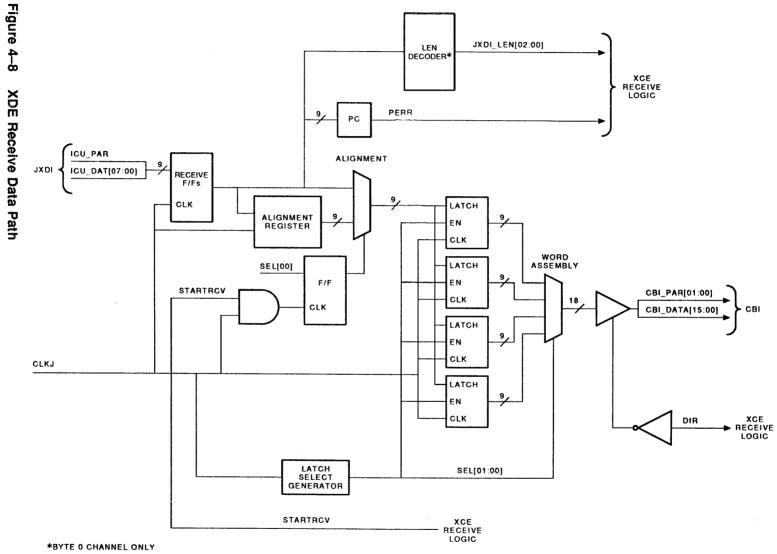

| 4–8  | XDE Receive Data Path                                                              | 4–18 |

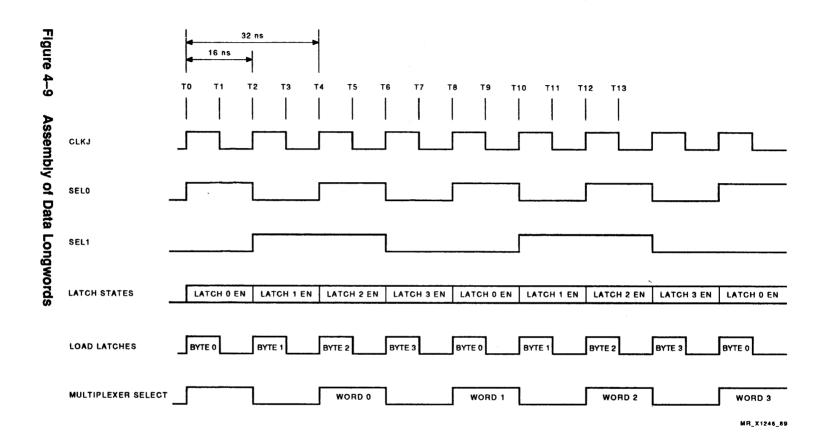

| 4–9  | Assembly of Data Longwords                                                         | 4-20 |

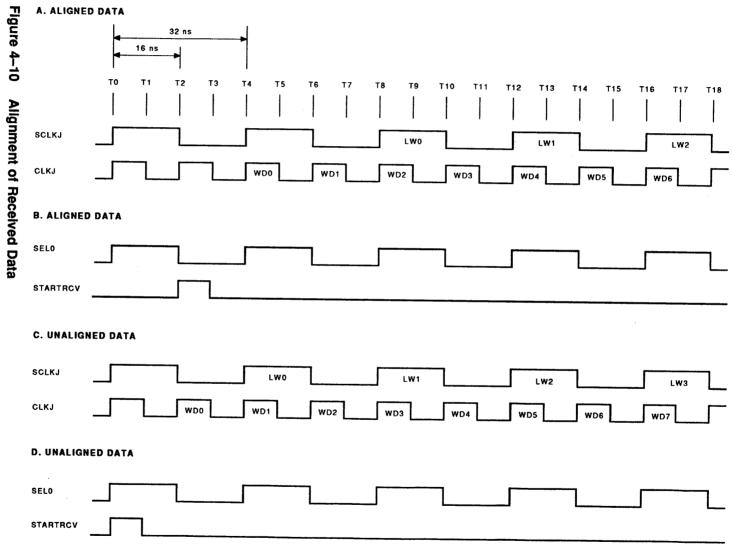

| 4–10 | Alignment of Received Data                                                         | 4-21 |

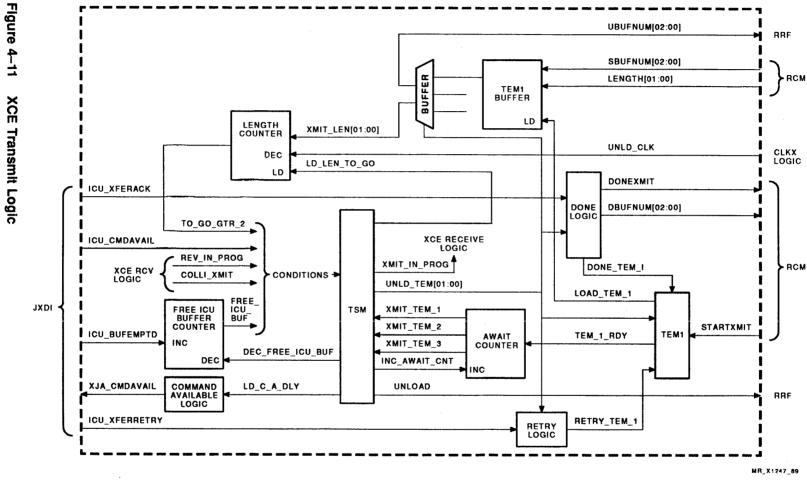

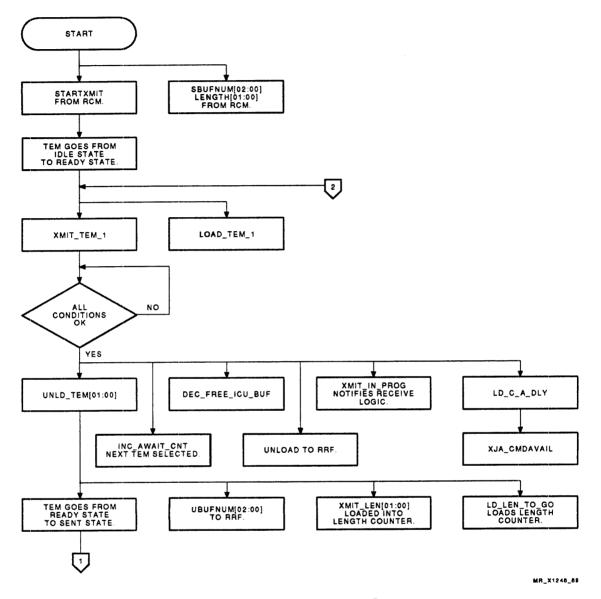

| 4–11 | XCE Transmit Logic                                                                 | 4–23 |

| 4–12 | Flow Diagram of XCE Transmit Sequence                                              | 4–24 |

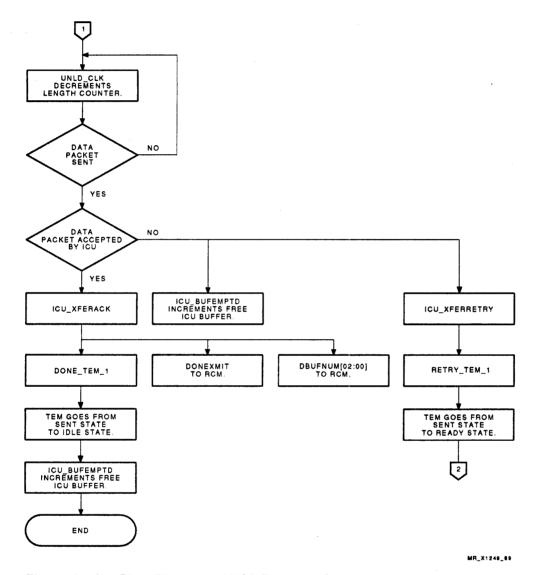

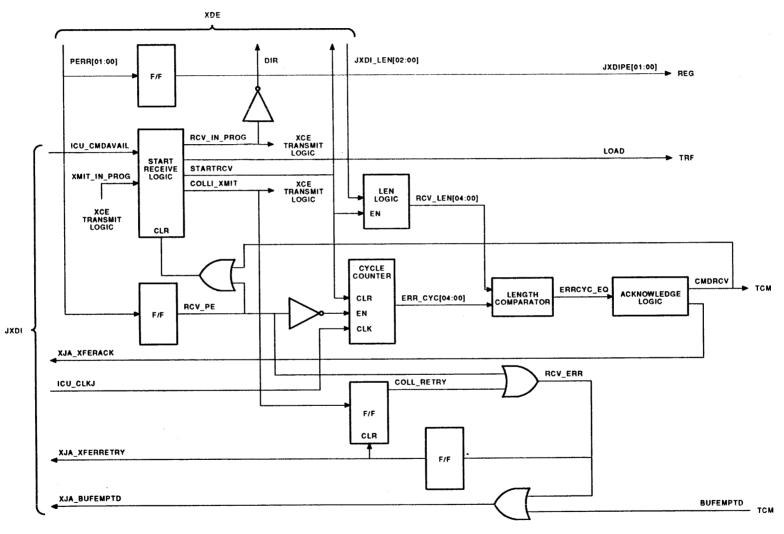

| 4–13 | XCE Receive Logic                                                                  | 4–28 |

| 4–14 | Flow Diagram of XCE Receive Sequence                                               | 4–29 |

| 4–15 | XMI Corner Block Diagram                                                           | 4-31 |

| 4–16 | XCLOCK Timing                                                                      | 4–32 |

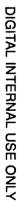

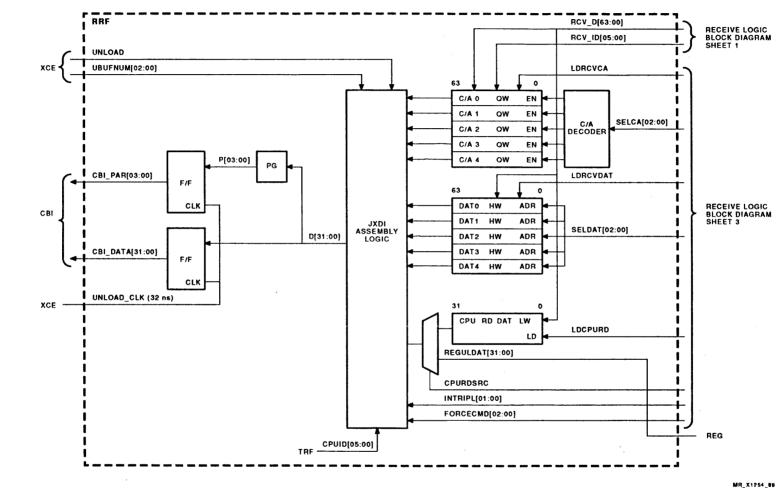

| 4–17 | Receive Logic Block Diagram                                                        | 4–34 |

| 4–18 | Reception of DMA Command/Address Packets and CPU Return                            |      |

|      | Data/Status Packets from XMI Bus                                                   | 4-41 |

| 4–19 | Reception of XMI Space Register Read/Write Command/Address<br>Packets from XMI Bus | 4-46 |

| 1 90 | Transmit Logic Block Diagram                                                       | 4-40 |

|      | Transmission of DMA Read Data/Status Return to XMI Bus                             | 4-55 |

| 4-21 | Transmission of CPU Read/Write Command/Address Packet to XMI                       | 4-00 |

| 4-22 | Bus                                                                                | 4-58 |

| 4–23 | Transmission of Read Register Data Return to XMI Bus                               | 4-64 |

| 4-24 | REG Data Flow                                                                      | 4-67 |

| 4–25 | Add-On Self-Test Implementation                                                    | 4-72 |

| 4–26 | Flow Diagram of Add-On Self-Test                                                   | 4-74 |

| 4–27 | AOST Control Register                                                              | 4-75 |

| 4–28 | Format of CPU Read Request                                                         | 4-77 |

| 4–29 | Format of CPU Read Data Return                                                     | 4-79 |

| 4-30 | Format of CPU Write Request                                                        | 4-80 |

| 4-31 | Format of CPU Write Complete                                                       | 4-81 |

| 5–1  | Device Register                                                                    | 5–3  |

| 5–2  | XMI Bus Error Register                                                             | 5–5  |

|      |                                                                                    |      |

| 5–3    | Failing Address Register                    | 5 - 11 |

|--------|---------------------------------------------|--------|

| 5–4    | Failing Address Extension Register          | 5 - 12 |

| 55     | XJA General-Purpose Register                | 5–13   |

| 56     | Full System Emulation Mode Control Register | 5–13   |

| 5–7    | Add-On Self-Test Status Register            | 5–14   |

| 5–8    | XJA Serial Number Register                  | 5–15   |

| 5–9    | Error Summary Register                      | 5–18   |

| 5–10   | Force Command Register                      | 5–21   |

| 5–11   | Interprocessor Interrupt Source Register    | 5–23   |

| 5 - 12 | XJA Diagnostic Control Register             | 5–24   |

| 5–13   | DMA Failing Address Register                | 5–28   |

| 5–14   | DMA Failing Command Register                | 5–29   |

| 5–15   | Error Interrupt Control Register            | 5-30   |

| 5–16   | Configuration Register                      | 5–32   |

| 5–17   | XBI ID A Register                           | 5–33   |

| 5–18   | XBI ID B Register                           | 5–34   |

| 5–19   | Error SCB Offset Register                   | 5–35   |

| 5–20   | SCB Offset IPL 14(Hex) Register             | 5–36   |

| 5–21   | SCB Offset IPL 15(Hex) Register             | 5–37   |

| 5–22   | SCB Offset IPL 16(Hex) Register             | 5–38   |

| 5–23   | SCB Offset IPL 17(Hex) Register             | 5–39   |

|        | •                                           |        |

### Tables

•

| 1–1   | Types of XMI Devices                    | 1–5  |

|-------|-----------------------------------------|------|

| 1 - 2 | VAX 9000 system I/O Adapter Limitations | 1–5  |

| 1–3   | XJA Registers                           | 1–7  |

| 1–4   | XJA Mnemonics                           | 1–8  |

| 2–1   | JXDI Signal Functions                   | 2–2  |

| 2–2   | JXDI Transfer Functions                 | 2-5  |

| 2–3   | Length Field Codes                      | 2–9  |

| 2–4   | ID Code for DMA Transaction Commanders  | 2–10 |

| 2–5   | ID Code for CPU Transaction Commanders  | 2–23 |

| 2–6   | Address Bits [01:00] Versus Mask Field  | 2–24 |

| 2-7   | IPL Codes                               | 2–33 |

| 2–8   | JXDI Data Envelopes                     | 2–34 |

| 3–1   | XMI Signals                             | 3–3  |

| 3–2   | Function Codes                          | 3–5  |

| 3–3   | XMI Node ID Codes                       | 3–6  |

| 34    | Parity Coverage                         | 3–6  |

| 3–5   | Confirmation Codes                      | 3–7  |

| 36    | Command Codes                           | 3–10 |

| 3–7   | Length Codes                            | 3–10 |

| 3–8   | XMI Address Mapping                     | 3–19 |

| 3–9   | IPL Codes                               | 3–20 |

| 4–1   | XJA Clocks                              | 4–10 |

| 4-2   | RRF Buffer Select Code                  | 4–22 |

| 4–3   | Data Packet Length Code                  | 4–22 |

|-------|------------------------------------------|------|

| 4-4   | Command/Address Cycle Type               | 4-37 |

| 4–5   | Data Cycle Type                          | 4–37 |

| 4–6   | Write Length                             | 4-37 |

| 4–7   | Buffer Status Code                       | 4-38 |

| 4–8   | Force Command Code                       | 4-44 |

| 4–9   | Status of Pending Interrupts             | 4-47 |

| 4–10  | Data Type Code                           | 452  |

| 4–11  | XMI Cycle Type Code                      | 4-52 |

| 4–12  |                                          |      |

| 4–13  | TRF Buffer Select Code                   | 454  |

| 4–14  | XJA Registers                            | 4-66 |

| 4–15  | Nonfatal Interrupts                      |      |

| 4–16  | Nonfatal Errors Detected by the XJA      | 4–70 |

| 4–17  | Fatal Errors Detected by the XJA         | 4-71 |

| 4–18  | 8096 Memory Map                          |      |

| 4–19  | AOST Control Register                    | 4–76 |

| 4–20  | CBI Command Codes                        | 4-78 |

| 5 - 1 | XJA Registers                            | 5–2  |

| 5 - 2 | XMI Space Registers                      | 5–3  |

| 5–3   | Device Register                          | 5-4  |

| 5-4   | VAX 9000 XMI Device Types                | 5-4  |

| 5–5   | XMI Bus Error Register                   | 5-6  |

| 5–6   | Failing Address Register                 | 5–11 |

| 5–7   | Failing Address Extension Register       | 5–12 |

| 5–8   | XJA General-Purpose Register             | 5-13 |

| 5–9   | Add-On Self-Test Status Register         | 5–14 |

| 5–10  | XJA Serial Number Register               | 5–15 |

| 5–11  | XJA Private Registers                    | 5–17 |

| 5–12  | Error Summary Register                   | 5–18 |

| 5–13  | Force Command Register                   | 5–21 |

| 5–14  | Force Command Implementation             | 5–22 |

| 5–15  | Interprocessor Interrupt Source Register | 5-23 |

| 5–16  | XJA Diagnostic Control Register          | 5-24 |

| 5–17  | DMA Failing Address Register             | 5–28 |

| 5-18  | DMA Failing Command Register             | 5–29 |

| 5–19  | Error Interrupt Control Register         | 5–30 |

| 5–20  | Configuration Register (CNF)             | 5–32 |

| 5–21  | XBI ID A Register                        | 5–33 |

| 5–22  | XBI ID B Register                        | 5–34 |

| 5–23  | Error SCB Offset Register                | 5–35 |

| 5–24  | SCB Offset IPL 14(Hex) Register          | 5–36 |

| 5–25  | SCB Offset IPL 15(Hex) Register          | 5–37 |

| 5–26  | SCB Offset IPL 16(Hex) Register          | 5–38 |

| 5–27  | SCB Offset IPL 17(Hex) Register          | 5–39 |

# **About This Manual**

This manual describes the operation of the VAX 9000 system XJA adapter, the JXDI bus that connects the XJA with the system control unit (SCU), and the XMI bus that connects the XJA to the various I/O adapters.

This manual is a reference manual for Customer Services personnel as well as a training resource for Educational Services.

### **Intended Audience**

The content, scope, and level of detail in this manual assumes that the reader:

- Is familiar with the VAX architecture and VMS operating system at the user level

- Has experience maintaining midrange and large VAX systems

#### Manual Structure

The manual has five chapters and an index.

- Chapter 1, General Description, provides an overview of the I/O channel. It briefly describes the functions of the JXDI bus, the XJA, and the XMI bus; and the physical makeup of the I/O channel. Also described are interrupts and the various types of I/O transactions. The chapter closes with a discussion of VAX 9000 system I/O space.

- Chapter 2, JXDI Bus, provides a detailed description of the JXDI bus. DMA, CPU, and interrupt transactions are described along with the data formats used for each type of transaction. The chapter includes a detailed description of all the bus signals.

- Chapter 3, XMI Bus, provides a detailed description of the XMI bus, including a description of all the signals transferred on the bus. Read, write, and interrupt transactions are described along with the data formats used for each type of transaction. XMI address mapping is also discussed.

- Chapter 4, XJA, provides a detailed functional description of the XJA adapter. The functional areas of the XJA are identified, followed by a description of DMA, CPU, and interrupt transactions, and how the functional areas operate during the various types of transactions. Each functional area is then described in detail to explain how the area accomplishes its roll in the various transactions. Other areas described are the XJA registers, the XJA clock system, and the add-on self-test (AOST) logic.

- Chapter 5, Register Descriptions, provides a detailed description of the XJA registers. It includes a description of the bits in each register and the function each bit serves.

#### xiv About This Manual

• The index provides an alphabetical list of topics and subjects described in this manual. An entry with an f appended to the page number (for example: XMI bus, card cage slot assignments, 1-8f) indicates a figure reference. An entry with a t appended to the page number (for example: XRC, definition of, 1-11t) indicates a table reference.

# **1** General Description

This chapter provides an overview of the XJA I/O channel and the types of I/O and interrupt transactions that execute through the channel. The parts of the channel (JXDI bus, XJA, XMI bus) are described along with a brief explanation of how the parts function during the various transactions. A brief discussion of the XJA registers is also included. The latter part of the chapter discusses system address space.

### 1.1 I/O Configuration

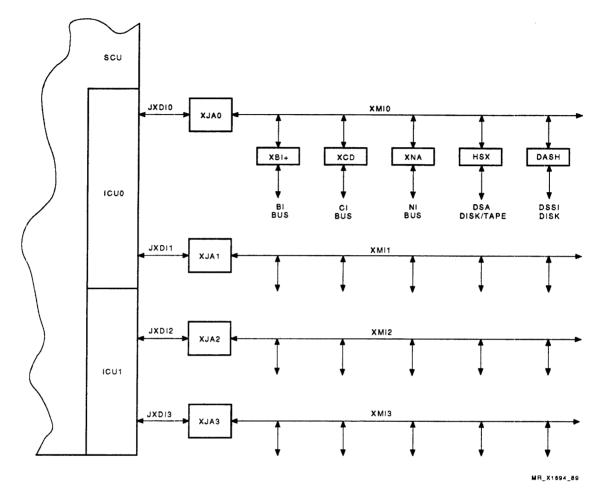

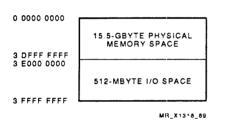

Figure 1-1 is an overview of the VAX 9000 system I/O section. The system can have up to four I/O channels that interface with the I/O control unit (ICUs) in the system control unit (SCU). The SCU can have up to two ICUs, each capable of interfacing with up to two I/O channels.

An I/O channel consists of the following components:

- JXDI bus

- XJA

- XMI bus

- XMI node adapters

#### 1.1.1 JXDI Bus

The JBox-to-XJA data interconnect (JXDI) is a bus that interfaces the ICU with the XMIto-JBox adapter (XJA). The bus is composed of four cables each with 30 lines. Of the 120 total lines, 107 are signal and 13 are ground. Most of the signal lines are in differential pairs. The JXDI cables are about 4 meters (12 feet) long.

#### 1-2 General Description

Figure 1–1 System I/O Block Diagram

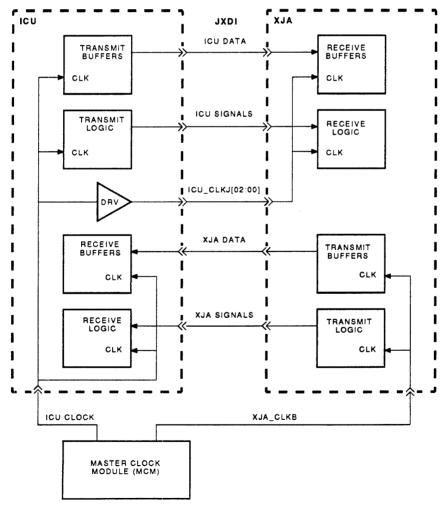

### 1.1.2 XJA

The XJA is the interfacing adapter between the SCU and the XMI bus. The XJA:

- Transfers data between the JXDI and the XMI bus

- Formats the data as required for the JXDI and the XMI bus

- Checks data and reports any errors

- Generates interrupts resulting from I/O errors

- Contains the registers required to monitor and control the I/O system

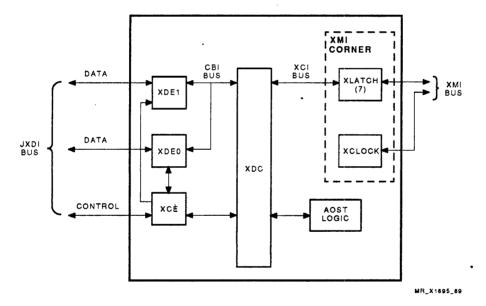

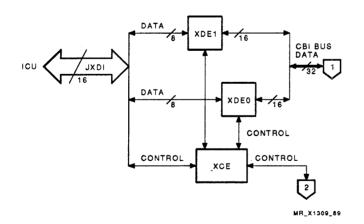

Figure 1-2 is a simplified block diagram of the XJA. The XJA has 12 chips plus some board mounted discrete components. The 12 chips are:

- One XDC chip (XJA data path CMOS gate array)

- Two XDE chips (XJA data path ECL gate array)

- One XCE chip (XJA JXDI control ECL gate array)

- Seven XLATCH chips

- One XCLOCK chip

Figure 1–2 XJA Simplified Block Diagram

1-4 General Description

The XDC chip is an LCA10129 series CMOS gate array. The chip implements LSI logic and contains most of the XJA logic. The XDC chip controls and formats the data flowing between the XMI corner and XDE chips, generates interrupts, and contains all the XJA registers.

The XDE and XCE chips are AMMC Q3500 series bipolar gate arrays. The XDE chips provide bidirectional data paths between the JXDI and the XDC chip, and they perform parity checking of the data received from the JXDI. The XCE chip provides the control interface with the JXDI and controls the data flow through the XDE chips.

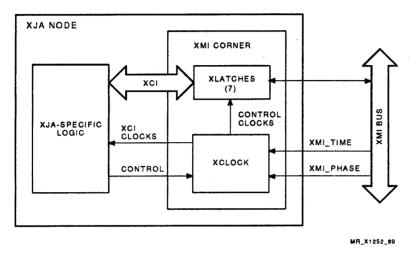

The XLATCH chips (DC530) and the XCLOCK chip (DC531) comprise the XMI corner. The XMI corner is a standard XMI interface required of all XMI nodes. The seven XLATCH chips provide a bidirectional data path between the XDC and the XMI bus. The XCLOCK chip generates clocks that are supplied to the XLATCH chips and the XDC chip.

The XJA contains add-on self-test (AOST) logic that interfaces with the XDC chip. The logic provides test inputs that check XJA operation and reports any test failures.

The XJA has two internal buses, the CBI and XCI. The CBI bus (CMOS to bipolar interconnect) is a bidirectional data bus connecting the XDE chips to the XDC chip. The XCI bus (XMI to CMOS interconnect) is a bidirectional data bus connecting the XMI corner to the XDC chip.

#### 1.1.3 XMI Bus

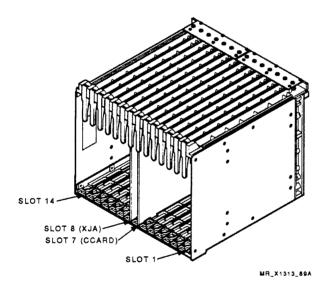

The XMI bus is a standard bus used by the VAX 9000 system as an I/O bus. The XMI bus is a pended, synchronous bus with centralized arbitration. Bus node adapters are housed in an XMI card cage (Figure 1-3) with the higher numbered slots having a higher arbitration priority than the lower numbered slots.

The bus has a clock card (CCARD) module containing the arbitration logic and the clock generation logic for the bus clocks. The XMI bus has a 64-ns cycle.

#### 1.1.4 XMI Node Adapters

The XMI node adapters are all passive adapters. That is, no CPUs interface to the XMI bus through any of these adapters. The VAX 9000 system CPUs are the only CPUs that exist in the entire system configuration.

Five types of adapters are supported on the XMI bus. These are identified in Table 1-1 along with the device to which they interface.

There are some physical and address space limitations on the number and types of adapters that can be used. A summary of these limitations is given in Table 1--2.

| Device | Description                      | Adapter<br>Mnemonic | Adapter<br>Module(s)                          |

|--------|----------------------------------|---------------------|-----------------------------------------------|

| KFMSA  | DSSI <sup>1</sup> disk interface | DASH                | T2036                                         |

| DEMNA  | XMI-to-NI adapter                | XNA                 | <b>T2020</b>                                  |

| CIXCD  | XMI-to-CI adapter                | XCD                 | <b>T2080</b>                                  |

| KDM70  | Local DSA disk/tape interface    | HSX                 | T2022 and T2023 <sup>2</sup>                  |

| DWMJA  | XMI-to-JBox adapter              | XJA                 | T1061                                         |

| DWMBB  | XMI-to-BI adapter                | XBI+                | T2018 (XBIA) and<br>T1043 <sup>3</sup> (XBIB) |

Table 1–1 Types of XMI Devices

<sup>1</sup>Digital storage system interconnect.

<sup>2</sup>The HSX adapter requires two slots in the XMI card cage.

<sup>3</sup>The T1043 module is in the VAXBI expander cabinet.

| Table 1–2 VAX 9000 System I/O Adapter Limitations |                                                                   |  |

|---------------------------------------------------|-------------------------------------------------------------------|--|

| Limitation Reason                                 |                                                                   |  |

| Maximum of 12 adapters per card cage              | Only 12 physical slots available (Section 1.2).                   |  |

| Maximum of 8 XBI+ adapters per<br>XMI card cage   | Maximum of 8 BI units accessible per I/O cabinet (Section 1.2).   |  |

| Maximum of 14 XBI+ adapters per system            | System I/O space has room for only 14 BI windows (Section 1.5.1). |  |

Table 1–2 VAX 9000 system I/O Adapter Limitations

### **1.2 Physical Configuration**

The XJA is an extended T-series module (T1061) that is housed in the XMI card cage located in the I/O cabinet. In the VAX 9000 model 210 system, there is one XMI card cage per I/O cabinet, resulting in a limitation of one XJA I/O channel per VAX 9000 model 210 system. In the VAX 9000 model 400 systems, there are two XMI card cages per I/O cabinet, allowing up to the maximum of four XJA I/O channels per system. The JXDI cables are located in the rear of the cabinets and connect the ICU in the SCU cabinet to the XJA module in the I/O cabinet.

Another physical limitation exists with regard to the XBI+ (XMI-to-BI adapter). Up to eight BI units may be located in two VAXBI expander cabinets (four BI units per cabinet) with one XBI+ adapter required per BI unit. Consequently, no more than eight XBI+ adapters per I/O cabinet can be used. This limits models 410 and 420 to eight XBI+ adapters. In the model 430 and 440, a third and a fourth VAXBI expander cabinet house additional BI units that connect to the XBI+ adapters in the XMI card cages in the second I/O cabinet (Table 1-2).

#### NOTE

A third BI expander cabinet cannot be used with models 410 and 420 due to cabling limitations. Model 210 has only one VAXBI expander cabinet.

#### 1-6 General Description

Figure 1-3 shows the XMI card cage. The cage has 14 slots, 2 of which are used by the XJA and the CCARD modules, and the remaining 12 are for other XMI adapter modules. The CCARD module contains the XMI arbitration and clock generation logic and is an integral part of the XMI bus. The CCARD is centrally located in the card cage (slot 7) to distribute the XMI clocks radially to the XMI adapters. This radial distribution minimizes clock skew between the adapters and improves signal integrity. The XJA can fit on the left side of the CCARD but not on the left side of any of the other XMI adapters. Therefore, the XJA is always located in slot 8 beside the CCARD. The only other restriction on placement of the XMI card cage adapter modules is that slot 1 or 14 must be used to implement the XMI\_DEFAULT function on the XMI bus (Section 3.2.4). After the first XMI adapter is placed in slot 1 or 14, other adapters may be located in any slot. Adapters in the higher numbered slots have a higher arbitration priority than those in the lower numbered slots.

Each slot in an XMI card cage has a 4-bit, hardwired, node ID number that identifies the slot and the adapter in the slot. XMI adapters match the node ID against selected address bits to determine if an XMI transaction is directed to their node (Sections 1.5.5.1 and 1.5.5.2).

Figure 1–3 XMI Card Cage

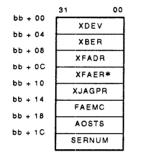

## 1.3 XJA Registers

The 23 registers in the XJA are used for monitoring and controlling XJA operations. The registers and their functions are listed in Table 1–3. The XJA registers fall into two groups: XMI space registers and XJA private registers. The XMI space registers are accessed from the XMI bus. If a system CPU wishes to access an XMI space register, it places its command/address on the XMI bus with the XJA as the addressed XMI adapter. The XJA private registers cannot be accessed from the XMI bus. Only the system CPU can access the XJA private registers and this is done completely within the XJA.

| Register                           | Mnemonic  | Description                                                                                         |

|------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|

| XMI Space Registers                |           |                                                                                                     |

| Device                             | XDEV      | Describes the node device.                                                                          |

| Bus error                          | XBER      | Contains a summary of the XMI status and errors.                                                    |

| Failing address                    | XFADR     | Saves the low-order four bytes of a failing XMI command/address.                                    |

| Failing address extension          | XFAER     | Saves the high-order four bytes of a failing XMI command/address.                                   |

| XJA general purpose                | XJAGPR    | Used for diagnostic testing.                                                                        |

| Full system emulation mode control | FAEMC     | Controls XJA operation in full system emulation mode.                                               |

| Add-on self-test status            | AOSTS     | Contains the results of various tests run by AOST logic.                                            |

| XJA serial number                  | SERNUM    | Contains the year and week of<br>manufacture, manufacturing plant,<br>and serial number of the XJA. |

| XJA Private Registers              |           | · · · · · · · · · · · · · · · · · · ·                                                               |

| Error summary                      | ERRS      | Contains summary of errors detected by the XJA.                                                     |

| Force command                      | FCMD      | Forces XJA transactions for testing purposes.                                                       |

| Interprocessor interrupt source    | IPINTRSRC | Identifies the source of interprocessor interrupts.                                                 |

| XJA diagnostic control             | DIAG      | Controls diagnostic testing of the XJA.                                                             |

| DMA failing address                | DMAFADDR  | Saves address and length information<br>of a failing DMA or interrupt<br>transaction.               |

| DMA failing command                | DMAFCMD   | Saves command, mask, and address information of a failing DMA or interrupt transaction.             |

| Error interrupt control            | ERRINTR   | Disables various error interrupts<br>during diagnostic testing.                                     |

| Table | 1–3 | XJA | Registers |

|-------|-----|-----|-----------|

|-------|-----|-----|-----------|

#### 1-8 General Description

| Register               | Mnemonic | Description                                                                           |

|------------------------|----------|---------------------------------------------------------------------------------------|

| Configuration          | CNF      | Contains the XJA number and node<br>ID, and main memory size and starting<br>address. |

| XBI ID A               | XBIIDA   | Contains 4-bit node ID of BI adapters 0 through 7.                                    |

| XBI ID B               | XBIIDB   | Contains 4-bit node ID of BI adapters 8 through D(hex).                               |

| Error SCB offset       | ERRSCB   | Contains SCB offset for XJA detected errors at IPL 17(hex).                           |

| SCB offset IPL 14(hex) | IDENT4   | Contains SCB offset for XMI generated interrupts at IPL 14(hex).                      |

| SCB offset IPL 15(hex) | IDENT5   | Contains SCB offset for XMI generated interrupts at IPL 15(hex).                      |

| SCB offset IPL 16(hex) | IDENT6   | Contains SCB offset for XMI generated interrupts at IPL 16(hex).                      |

| SCB offset IPL 17(hex) | IDENT7   | Contains SCB offset for XMI generated interrupts at IPL 17(hex).                      |

#### Table 1–3 (Cont.) XJA Registers

### **1.4 XJA Transactions**

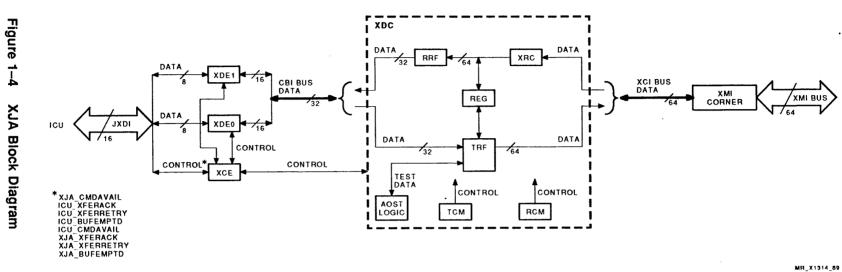

Figure 1–4 is a block diagram of the XJA. Table 1–4 defines the mnemonics of XJA chips, buses, and logic areas used in Figure 1–4 and in the following discussion.

| Mnemonic | Definition                          |

|----------|-------------------------------------|

| AOST     | Add-on self-test                    |

| CBI      | CMOS to bipolar interconnect        |

| JXDI     | JBox to XJA data interconnect       |

| RCM      | Receive control machine             |

| REG      | XJA registers                       |

| RRF      | Receive register file               |

| TCM      | Transmit control machine            |

| TRF      | Transmit register file              |

| XCE      | XJA JXDI control ECL gate array     |

| XCI      | XMI bus to CMOS interconnect        |

| XDC      | XJA data path CMOS gate array       |

| XDE      | XJA data path ECL gate array        |

| XJA      | XMI to JBox adapter                 |

| XMI      | General-purpose memory interconnect |

| XRC      | XMI receive logic                   |

Table 1–4 XJA Mnemonics

.

.

#### 1-10 General Description

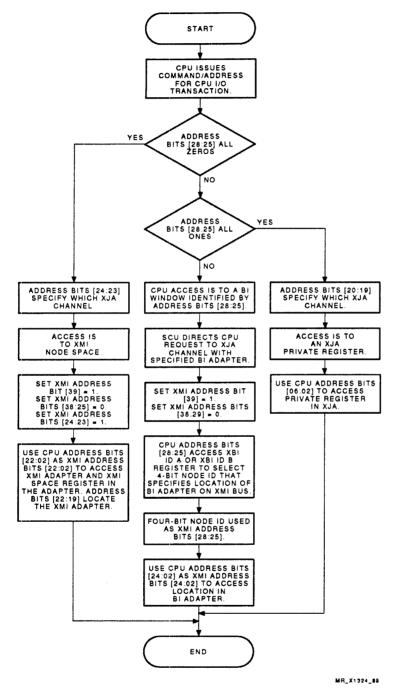

Data packets that flow between the JXDI bus and the XMI bus undergo format, timing, and data length changes as they pass through the XJA. Packets from the XMI bus have data lengths of 64 bits per cycle and are clocked at a 64-ns rate. From the XMI bus, the 64-bit data packets pass through the XMI corner and the XRC, and then into the RRF where the data length is changed to 32 bits per cycle. The 32-bit data cycles are clocked at a 32-ns rate. The 32-bit data packets cross the CBI bus and then split into two 16-bit sections that are applied to the XDE chips. The XDE chips change the data lengths from 16 to 8 bits per cycle clocked at a 16-ns rate. The 8-bit outputs of the XDE chips are combined to form a 16-bit data length per cycle for the JXDI data packets. The 16-bit JXDI data cycles are clocked at the 16-ns rate.

Data packets traversing the XJA in the other direction undergo a similar change in timing and data length. JXDI packets from the ICU have a 16-bit data length and are clocked at a 16-ns rate. The data is split into two 8-bit sections and applied to the XDE chips. In the XDE, the data is assembled into 16-bit data lengths clocked at a 32-ns rate. The 16-bit data outputs from the XDE chips are combined into 32-bit longwords and clocked across the CBI bus at a 32-ns rate. The 32-bit data packet is sent to the TRF where it is changed into a 64-bit data length clocked at a 64-ns rate. The 64-bit data packet is transmitted through the XMI corner to the XMI bus.

Three separate clock systems are used in the XJA. One is a 64-ns clock system to control the 64-bit data interfacing with the XMI bus. A second controls the movement of data from the XJA to the ICU. This clock system includes a 32-ns clock to transfer data from the RRF, across the CBI bus, and into the XDE chips; and a 16-ns clock to transfer data from the XDE to the JXDI. A third clock system controls the movement of data from the ICU to the XJA. This clock system includes a 16-ns clock to transfer data from the JXDI into the XDE, and a 32-ns clock to transfer data from the XDE to TRF.

Four types of transactions occur within the XJA:

- **DMA** (direct memory access) This transaction is a read or write of the VAX 9000 system main memory by an XMI device.

- **CPU** This transaction is a read or write of an I/O register by the VAX 9000 system CPU. The I/O register may be in an XMI device or in the XJA.

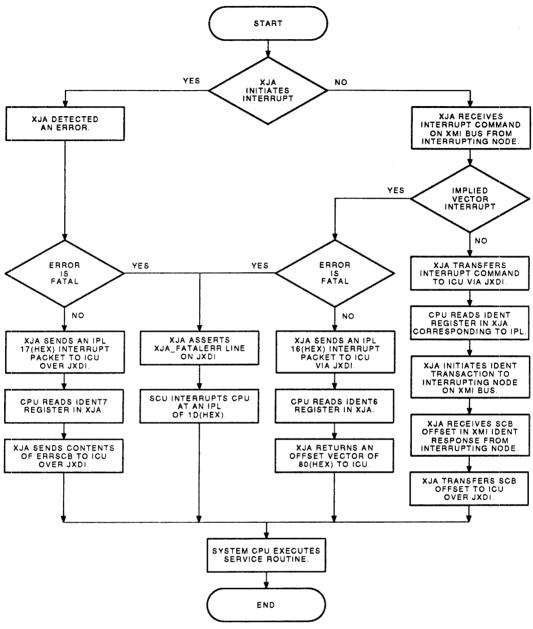

- Interrupts This transaction may be initiated by the XJA or by an XMI device. An interrupt initiated by the XJA is transferred over the JXDI to the system CPU for processing. An interrupt initiated by an XMI device is received by the XJA and passed on to the system CPU over the JXDI.

- AOST (add-on self-test) This transaction consists of a test packet injected into the XJA by the AOST logic. The test packet is processed as a CPU transaction and the results are checked in the AOST logic.

#### 1.4.1 DMA Transactions

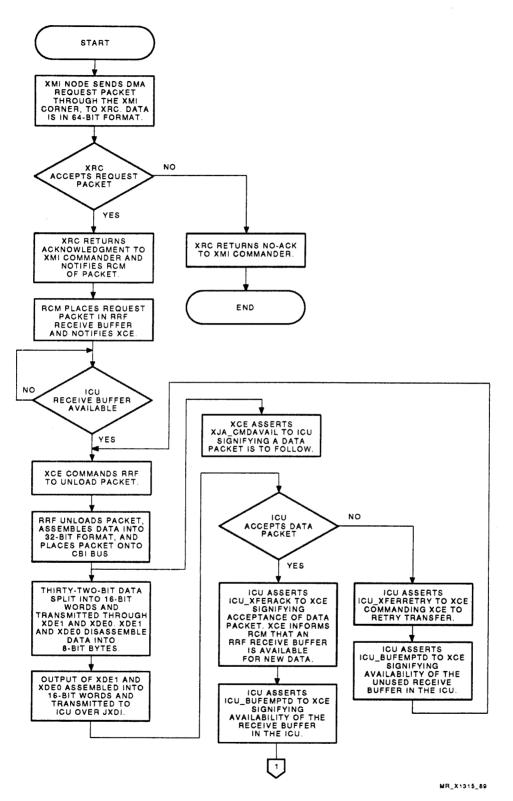

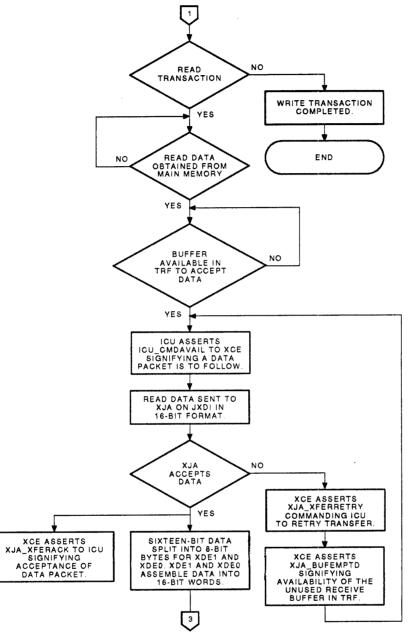

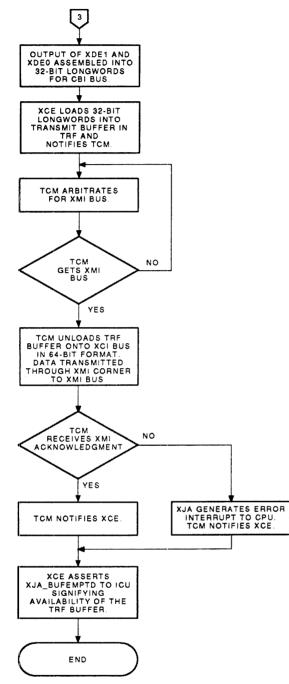

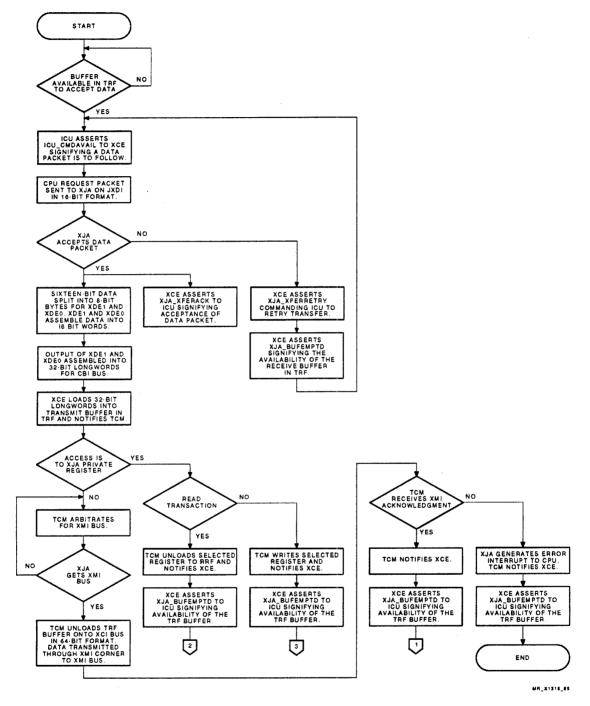

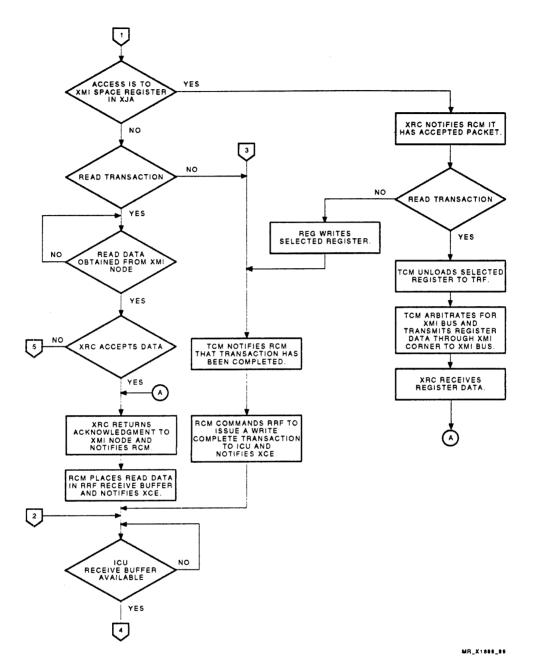

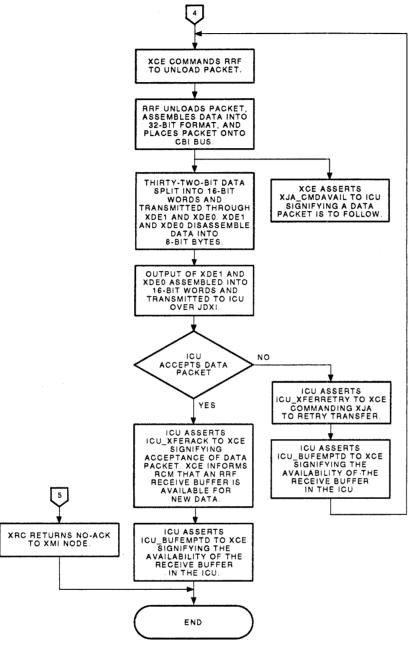

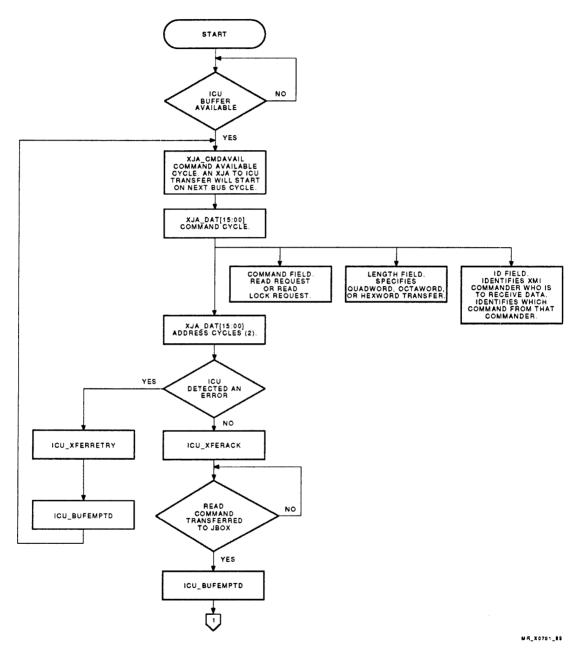

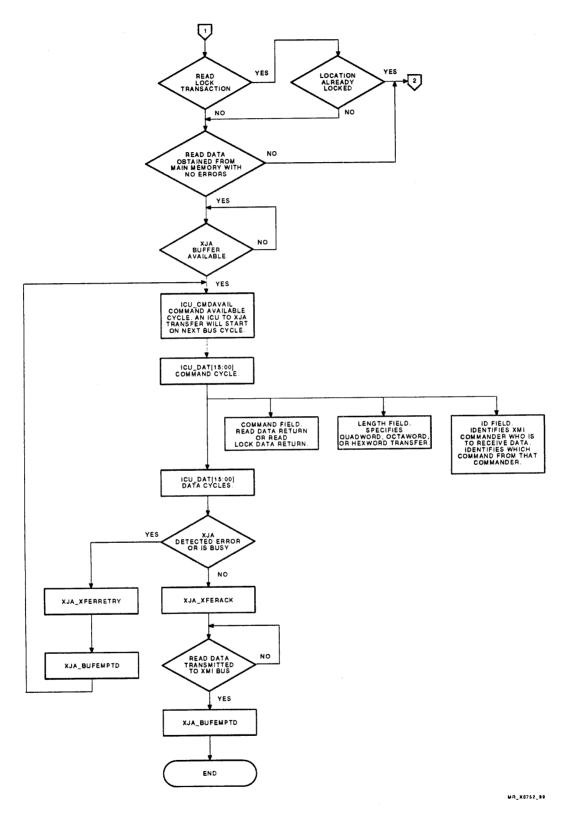

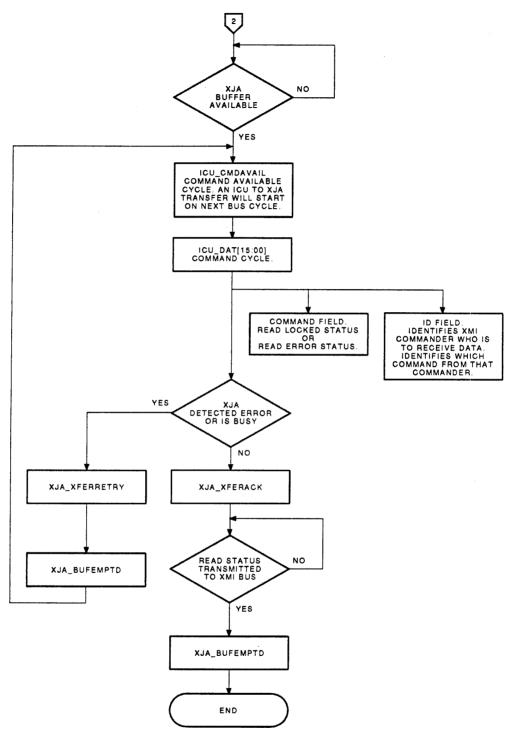

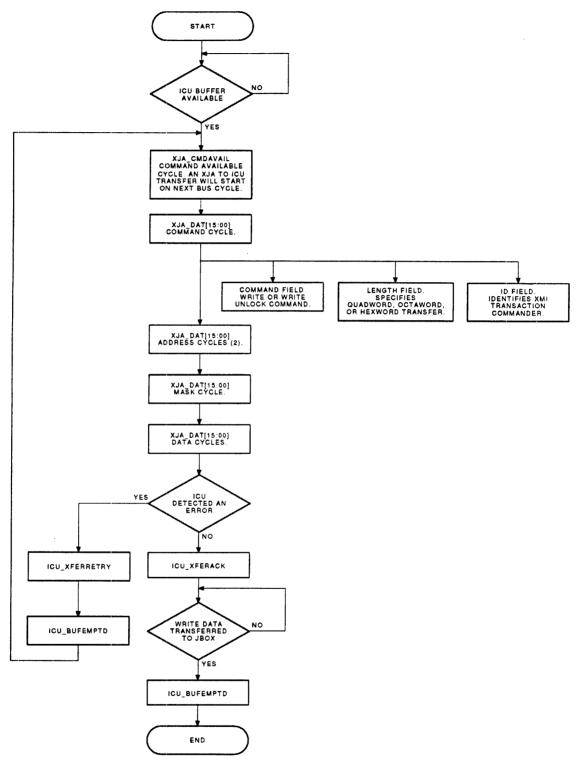

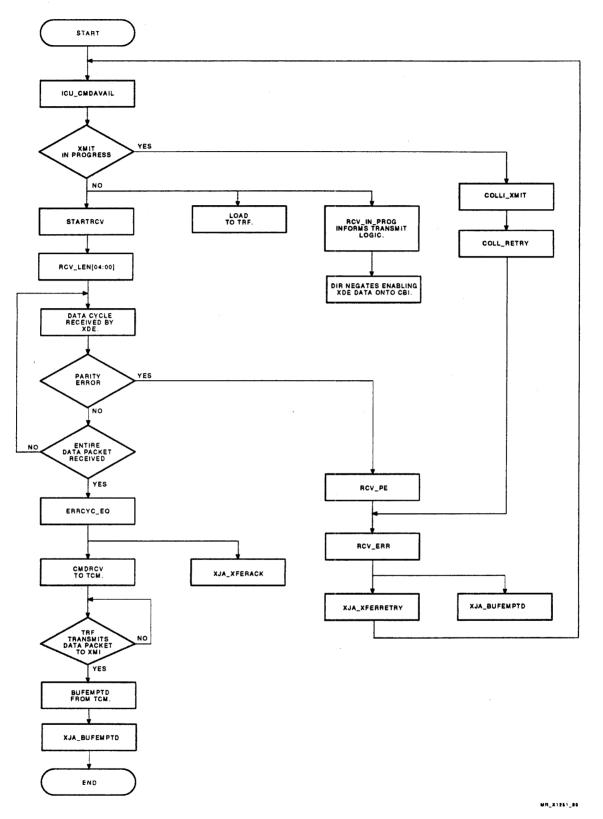

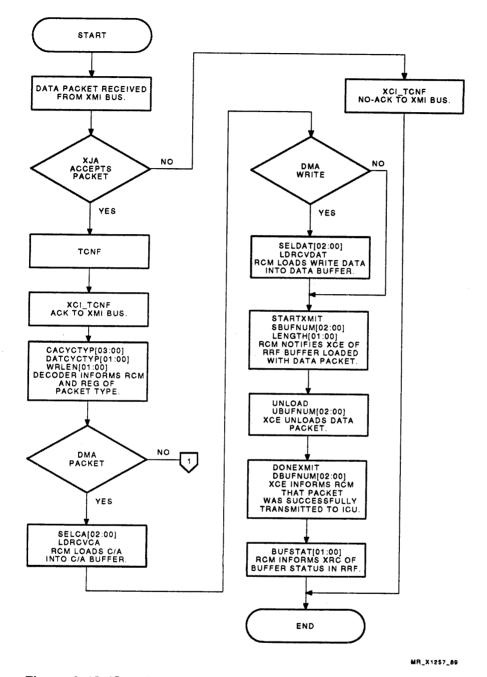

Figure 1–5 is a flow diagram of a DMA transaction. Refer to the flow diagram and to the XJA block diagram (Figure 1–4) during the following discussion.

DMA transactions are initiated by XMI devices to the VAX 9000 system main memory. The DMA command/address is contained in one 64-bit XMI cycle. If the transaction is a write, the write data follows the command/address cycle. Write transactions can be quadword writes (one XMI cycle of write data) or octaword writes (two XMI cycles of write data).<sup>1</sup> Read transactions can be quadword, octaword, or hexword. A hexword transaction is four XMI cycles of read data.

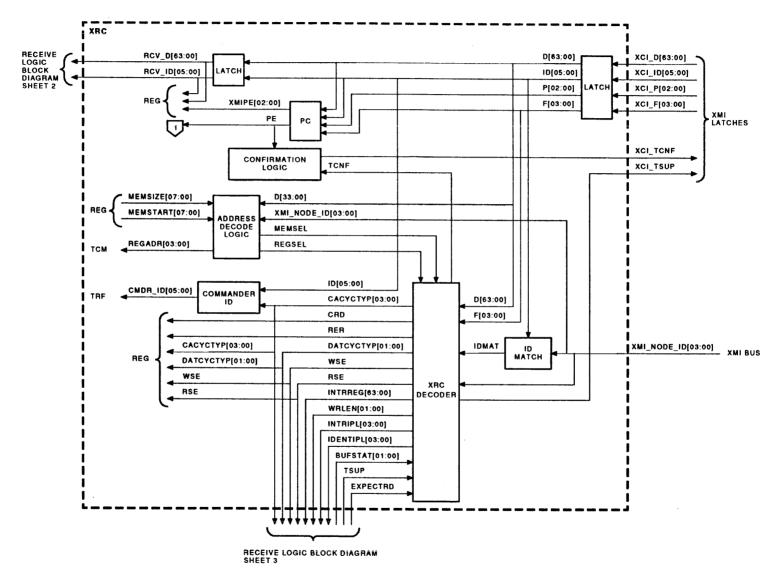

A DMA request packet on the XMI passes through the XMI corner and is received by the XRC logic. The XRC checks parity and checks that the address is valid. If either of these checks fails, the packet is not acknowledged to the XMI commander (the XMI node that transmitted the command/address packet). If the XRC accepts the packet, it returns an acknowledgment to the XMI commander and notifies the RCM, which then controls the processing of the packet.

The RCM places the packet in a receive buffer in the RRF and notifies the XCE that a packet is ready to be sent to the ICU. The ICU has two receive buffers that receive data from the XJA. The XCE contains an ICU buffer available counter with which it monitors the status of the two ICU receive buffers. If an ICU receive buffer is available, the XCE commands the RRF to unload the packet from the RRF receive buffer. The RRF unloads the packet, assembles it into a 32-bit format, and sends it across the CBI to the XDEs.

The 32-bit data from the RRF is split into two halves with one half going to each XDE. The XCE controls the transfer of data through the XDEs and the disassembly of the data from 16-bit words into 8-bit bytes. At the same time, the XCE asserts XJA\_CMDAVAIL to the ICU, informing it that a packet is to follow starting with the next cycle. The 8-bit outputs of the XDEs are combined to form 16-bit words for the JXDI. The packet is sent to the ICU in the 16-bit word format.

The ICU checks parity on the packet data and if an error is detected, it asserts ICU\_ XFERRETRY to the XCE, commanding the XCE to retry the transfer. The XCE once again unloads the packet from the RRF receive buffer and repeats the transmission process to the ICU. The ICU also asserts ICU\_BUFEMPTD to the ICU buffer available counter in the XCE, informing the XCE that the ICU buffer reserved for the packet is still available.

<sup>&</sup>lt;sup>1</sup> The XJA also supports hexword writes, but the SCU does not.

#### 1-12 General Description

Figure 1–5 (Cont.) Flow Diagram of DMA Transactions

#### DIGITAL INTERNAL USE ONLY

MR\_X1690\_89

Figure 1–5 (Cont.) Flow Diagram of DMA Transactions

MR\_X1691\_89

Figure 1–5 Flow Diagram of DMA Transactions

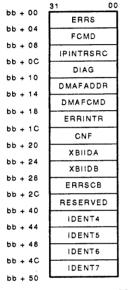

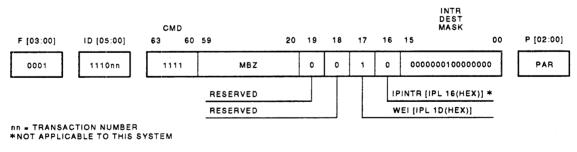

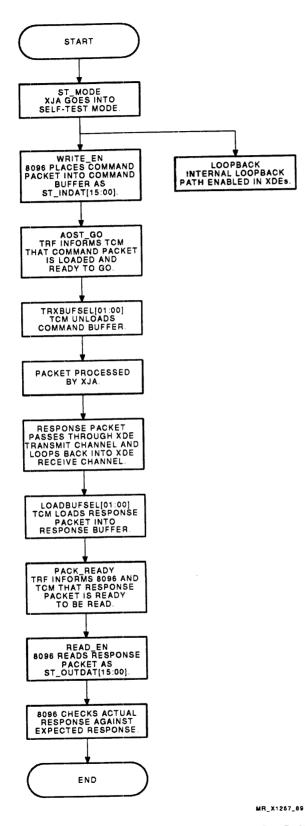

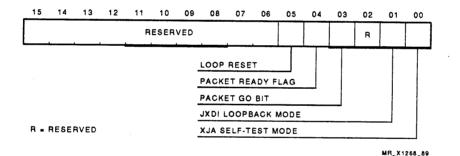

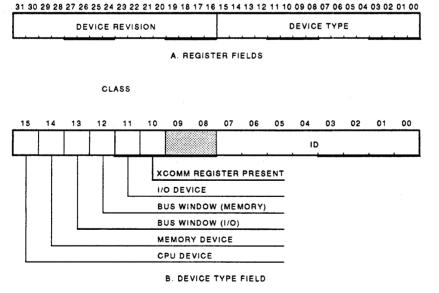

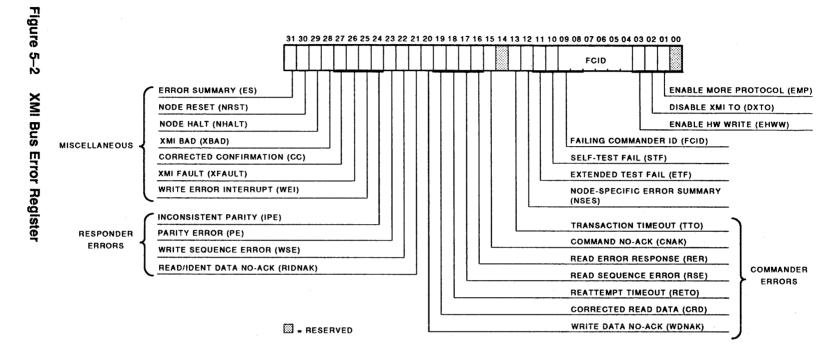

If the ICU finds no parity error in the packet, it asserts ICU\_XFERACK to the XCE, indicating that the packet is accepted. The XCE then informs the RCM that the receive buffer in the RRF is available to receive another packet from the XRC.