EK-KA630-UG-001

# KA630-AA CPU Module User's Guide

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, February 1986

# © Digital Equipment Corporation 1986.

All Rights Reserved.

The material in this document is for informational purposes and is subject to change without notice; it should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

FCC Notice: This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

#### Printed in U.S.A.

The manuscript for this book was created on a VAX-11/780 system running WPS-PLUS. The book was produced by Educational Services Development and Publishing in Marlboro, MA.

Motorola is a registered trademark of Motorola, Inc.

The following are trademarks of Digital Equipment Corporation:

| 5090130   | MASSBUS      | RSTS           |

|-----------|--------------|----------------|

| DEC       | OMNIBUS      | RSX            |

| DECmate   | OS/8         | RT             |

| DECNET    | PDP          | UNIBUS         |

| DECUS     | PDT          | VAX            |

| DECwriter | P/OS         | VAXstation     |

| DIBOL     | Professional | VMS            |

| IAS       | Q-Bus        | VT             |

| LSI-11    | Rainbow      | Work Processor |

# Page

#### PREFACE

| CHAPTER                                                                     | 1 | OVERVIEW                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10         |   | INTRODUCTION. 1-1<br>MicroVAX 78032 MICROPROCESSOR CHIP. 1-2<br>MicroVAX 78132 FRU CHIP. 1-3<br>MicroVAX INTERFACE GATE ARRAY. 1-3<br>LOCAL MEMORY. 1-3<br>64 KBYTE BOOT AND DIAGNOSTIC ROM. 1-3<br>CONSOLE SERIAL LINE UNIT (SLU). 1-3<br>Q22-BUS INTERFACE. 1-5<br>KA630-AA OPERATION MODES. 1-8<br>KA630-AA SPECIFICATIONS. 1-8 |

| CHAPTER                                                                     | 2 | INSTALLATION                                                                                                                                                                                                                                                                                                                       |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.4<br>2.4.1<br>2.5         |   | INTRODUCTION                                                                                                                                                                                                                                                                                                                       |

| CHAPTER                                                                     | 3 | BOOTING AND CONSOLE PROGRAM INTERFACE                                                                                                                                                                                                                                                                                              |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.6.1 |   | INTRODUCTION                                                                                                                                                                                                                                                                                                                       |

| 3.2.6.2                                                                     |   | Console Terminal Determination                                                                                                                                                                                                                                                                                                     |

| 3.2.7     | Console Message Language Check                   |

|-----------|--------------------------------------------------|

| 3.3       | ENTRY/DISPATCH                                   |

| 3.4       | DIAGNOSTICS                                      |

| 3.5       | RESTART                                          |

| 3.6       | BOOTSTRAP                                        |

| 3.6.1     | Primary Bootstrap Program (VMB)                  |

| 3.6.1.1   | Bootstrap Devices                                |

| 3.6.1.2   | Bootstrap Command Fl                             |

| 3.6.1.3   | Booting from Disk                                |

| 3.6.1.4   | Booting from Tape                                |

| 3.6.1.5   | Booting from PROM                                |

| 3.6.1.6   | Booting from DEQNA                               |

| 3.6.1.7   | Booting an Auxiliary Processor                   |

| 3.6.2     | Secondary Bootstrap Program                      |

| 3.7       | CONSOLE I/O MODE (SYSTEM HALTED)                 |

| 3.7.1     | Console Control Characters                       |

| 3.7.2     | Console Command Syntax                           |

| 3.7.3     | References to Processor Registers and Memory3-24 |

| 3.7.4     | Console Commands                                 |

| 3.7.4.1   | Binary Load and Unload (X)                       |

| 3.7.4.2   | Boot                                             |

| 3.7.4.3   | Comment (!)                                      |

| 3.7.4.4   | Continue                                         |

|           | Deposit                                          |

| 3.7.4.5   |                                                  |

| 3.7.4.6   | Examine                                          |

| 3.7.4.7   | Find                                             |

| 3.7.4.8   | Initialize                                       |

| 3.7.4.9   | Halt                                             |

| 3.7.4.10  | Repeat                                           |

| 3.7.4.11  | Start                                            |

| 3.7.4.12  | Test                                             |

| 3.7.4.13  | Unjam                                            |

| 3.7.5     | Console Errors and Error Messages                |

| 3.7.6     | Halts and Halt Messages                          |

| 3.8       | CONSOLE I/O MODE (SYSTEM RUNNING)                |

|           |                                                  |

| CHAPTER 4 | ARCHITECTURE                                     |

| 4.1       | INTRODUCTION4-1                                  |

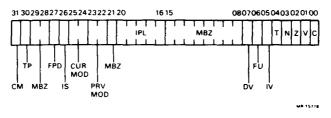

| 4.2       | PROCESSOR STATE4-1                               |

| 4.2.1     | General Purpose Registers4-1                     |

| 4.2.2     | Processor Status Longword4-1                     |

| 4.2.3     | Processor Registers4-3                           |

| 4.3       | INSTRUCTION SET                                  |

| 4.4       | EXCEPTIONS AND INTERRUPTS4-6                     |

| 4.4.1     | Interrupts                                       |

| 4.4.2     | Exceptions                                       |

| 4.4.3     | Machine Check Parameters                         |

| 4.4.4     | Halt Conditions4-9                               |

| 4.4.5     | System Control Block                             |

| 4.5       | HARDWARE DETECTED ERRORS                         |

| 4.5.1     | Nonexistent Memory Errors                        |

| 4.5.2     | Parity Error Detection                           |

| 4.5.3     | Interrupt Vector Timeouts                        |

| 4.5.4     | No Sack Timeouts                                 |

|           | HA PACK TIMEANCOTOPICITION                       |

.

| 4.6                              | LATENCY                                                                |

|----------------------------------|------------------------------------------------------------------------|

| 4.6.1                            | Interrupt Latency4-14                                                  |

| 4.6.2                            | DMA Latency4-14                                                        |

| 4.7                              | SYSTEM IDENTIFICATION REGISTER (SID)4-15                               |

| 4.8                              | MEMORY MANAGEMENT4-16                                                  |

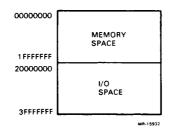

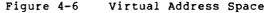

| 4.8.1                            | Physical and Virtual Address Space4-16                                 |

| 4.8.2                            | Memory Management Control Registers4-16                                |

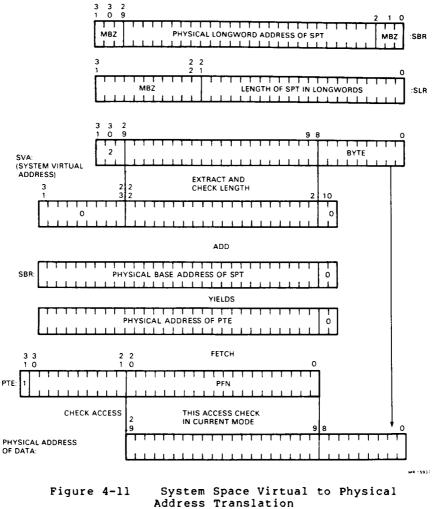

| 4.8.3                            | System Space Address Translation4-17                                   |

| 4.8.4                            | Process Space Address Translation4-17                                  |

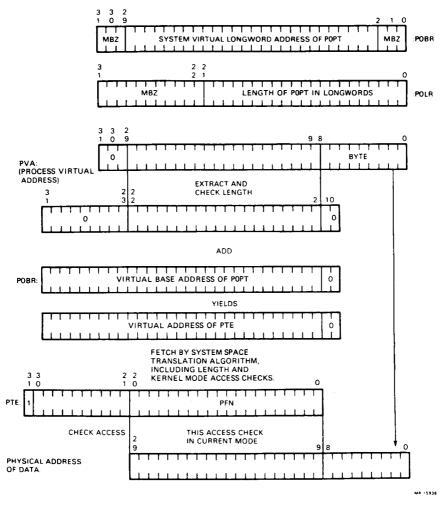

| 4.8.4.1                          | PO Region Address Translation                                          |

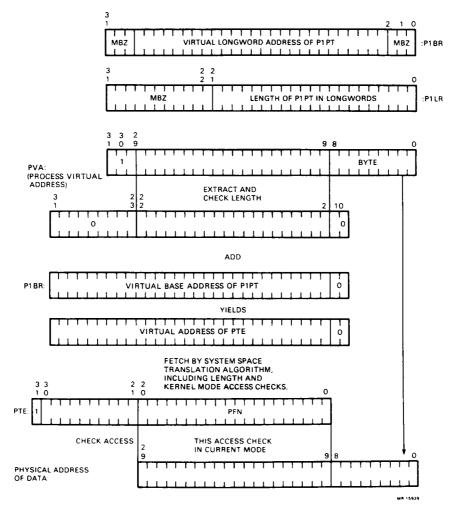

| 4.8.4.2                          | Pl Region Address Translation4-20                                      |

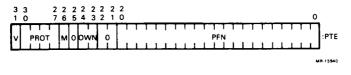

| 4.8.5                            | Page Table Entry                                                       |

| 4.9                              | KA630-AA MEMORY SYSTEM4-21<br>Local Memory Mapping Register Format4-21 |

| 4.9.1                            |                                                                        |

| 4.9.2                            | Mapping Register Addresses (2008XXXX Hex)4-22                          |

| 4.9.3                            | Q22-Bus Map Operation                                                  |

| 4.9.4                            | Memory System Registers                                                |

| 4.9.4.1                          |                                                                        |

| 4.9.4.2                          | CPU Error Address Register                                             |

| <b>4.9.4.</b> 3<br><b>4.9.</b> 5 | Memory System Operation                                                |

| <b>4.9.</b> 5<br><b>4.10</b>     | KA630-AA BOOT AND DIAGNOSTIC FACILITY                                  |

| 4.10.1                           | Boot and Diagnostic Register                                           |

| 4.10.2                           | ROM Memory                                                             |

| 4.10.2.1                         | ROM Sockets                                                            |

| 4.10.2.2                         | ROM Address Space                                                      |

| 4.10.2.3                         | KA630-AA Console Program Operation                                     |

| 4.11                             | KA630-AA TOY CLOCK                                                     |

| 4.11.1                           | Battery Backed-Up Watch Chip4-34                                       |

| 4.11.2                           | Watch Chip Registers                                                   |

| 4.11.2.1                         | TOY Data Registers                                                     |

| 4.11.2.2                         | Control and Status Register A                                          |

| 4.11.2.3                         | Control and Status Register B                                          |

| 4.11.2.4                         | Control and Status Register C4-37                                      |

| 4.11.2.5                         | Control and Status Register D                                          |

| 4.11.2.6                         | RAM Memory                                                             |

| 4.11.3                           | Power-Up                                                               |

| 4.11.3.1                         | Valid RAM and Time4-38                                                 |

| 4.11.3.2                         | Invalid RAM and Time4-38                                               |

| 4.12                             | INTERVAL TIMER                                                         |

| 4.12.1                           | Interval Clock Control and Status                                      |

|                                  | Register (ICCS)4-40                                                    |

| 4.12.2                           | Interval Timer Operation4-40                                           |

| 4.13                             | CONSOLE SLU                                                            |

| 4.13.1                           | Console Functionality4-40                                              |

| 4.13.2                           | Console Registers4-41                                                  |

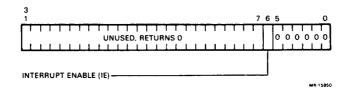

| 4.13.2.1                         | Console Receiver CSR (IPR 32)                                          |

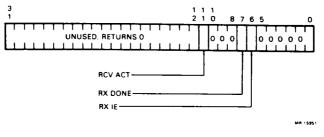

| 4.13.2.2                         | Console Receiver Data Buffer (IPR 33)4-41                              |

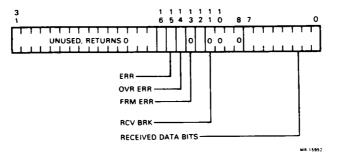

| 4.13.2.3                         | Console Transmitter CSR (IPR 34)4-44                                   |

| 4.13.2.4                         | Console Transmitter Data Buffer (IPR 35)4-45                           |

| 4.13.3                           | Break Response4-45                                                     |

| 4.14                             | Q22-BUS CONTROL                                                        |

| 4.14.1<br>4.14.2                 | Bus Initialize Register (IPR 55)                                       |

| 4.14.2                           | Multilevel Interrupts4-45                                              |

| 4.14.3<br>4.14.3.1<br>4.14.3.2<br>4.15<br>4.15.1<br>4.15.2<br>4.15.3<br>4.15.4                                                                                           | Interprocessor Communications Facility4-46<br>Interprocessor Communication Register4-46<br>Interprocessor Doorbell Interrupts4-48<br>MULTIPROCESSOR CONSIDERATIONS4-48<br>Auxiliary/Arbiter Differences4-48<br>Multiprocessor Features4-49<br>KA630-AA Based Multiprocessor Systems4-49<br>PDP-11 Based Multiprocessor Systems4-50 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 5                                                                                                                                                                | DIAGNOSTICS                                                                                                                                                                                                                                                                                                                        |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.7<br>5.2.4<br>5.2.8<br>5.3<br>5.4 | INTRODUCTION                                                                                                                                                                                                                                                                                                                       |

-

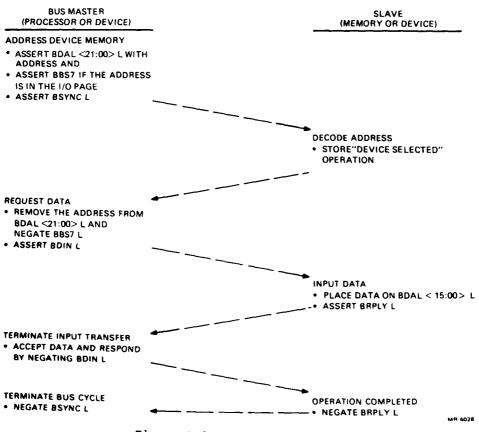

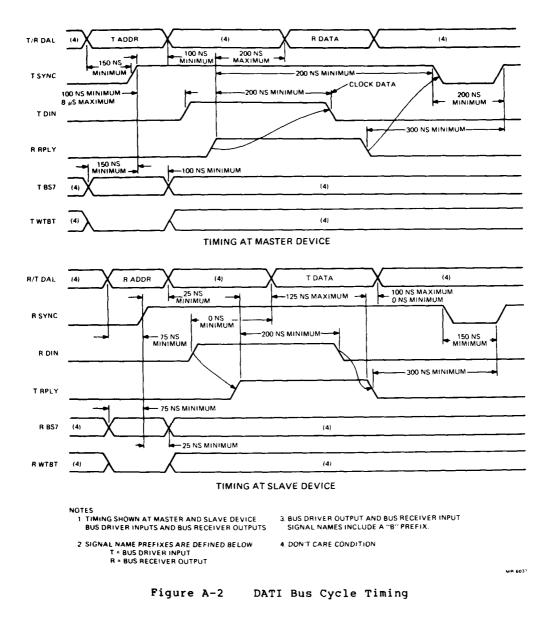

- APPENDIX A Q22-BUS SPECIFICATION

- APPENDIX B ACRONYMS

# FIGURES

| Fi | ig | u | e | No | • |

|----|----|---|---|----|---|

|----|----|---|---|----|---|

# Title

# Page

\_

| 1-1 | KA630-AA (MicroVAX 630) CPU Module1-1              |

|-----|----------------------------------------------------|

| 1-2 | MS630 Memory Modules1-4                            |

| 1-3 | KA630-AA Block Diagram1-5                          |

| 1-4 | MicroVAX II System Level Block Diagram1-6          |

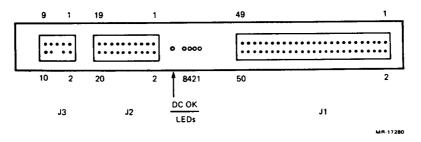

| 2-1 | KA630-AA Pin and LED Orientation2-1                |

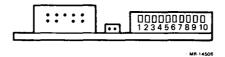

| 2-2 | KA630CNF Configuration Board2-6                    |

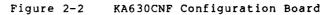

| 2-3 | KA630CNF J2 and J3 Pin Orientation2-6              |

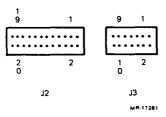

| 2-4 | KA630CNF J1 and J4 Pin Orientation2-6              |

| 2-5 | CK-KA630-A Distribution Panel Insert2-9            |

| 2-6 | CK-KA630-A Connectors (Front View)2-10             |

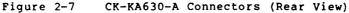

| 2-7 | CK-KA630-A Connectors (Rear View)2-10              |

| 3-1 | Console Memory Map After Initialization            |

| 3-2 | RPB Format                                         |

| 3-3 | Bootblock Format                                   |

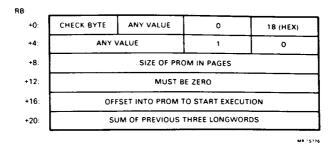

| 3-4 | PROM Bootstrap Memory Format (Signature Block)3-18 |

| 3-5 | Extended RPB                                       |

| 3-6 | Secondary Bootstrap Argument List                  |

| 3-7 | Secondary Bootstrap Memory Map                     |

| 4-1  | Processor Status Longword (PSL)4-3               |

|------|--------------------------------------------------|

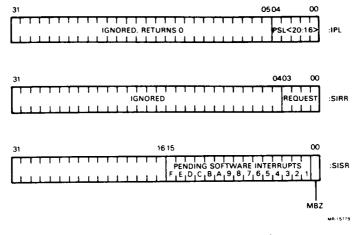

| 4-2  | Interrupt Registers                              |

| 4-3  | Machine Check Parameters4-8                      |

| 4-4  | System Control Block Base Register (SCBB)4-10    |

| 4-5  | System Identification Register (SID)4-15         |

| 4-6  | Virtual Address Space4-16                        |

| 4-7  | Physical Address Space4-16                       |

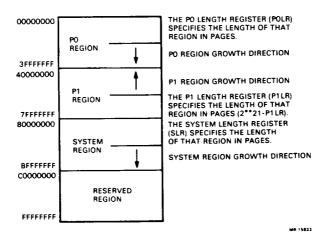

| 4-8  | Memory Management (Mapping) Enable Register      |

|      | (MAPEN)                                          |

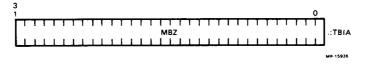

| 4-9  | Translation Buffer Invalidate Single Register    |

|      | (TBIS)                                           |

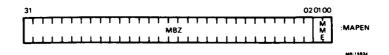

| 4-10 | Translation Buffer Invalidate All Register       |

|      | (TBIA)                                           |

| 4-11 | System Space Virtual to Physical Address         |

|      | Translation                                      |

| 4-12 | PO Virtual to Physical Address Translation4-19   |

| 4-13 | Pl Virtual to Physical Address Translation4-20   |

| 4-14 | Page Table Entry (PTE)4-21                       |

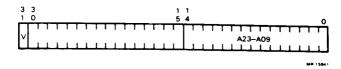

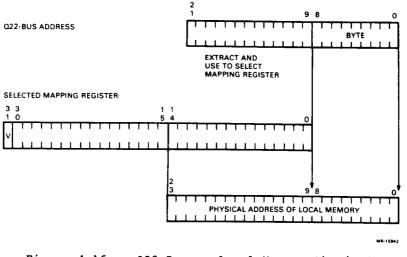

| 4-15 | Mapping Register4-22                             |

| 4-16 | Q22-Bus to Local Memory Physical Address         |

|      | Translation                                      |

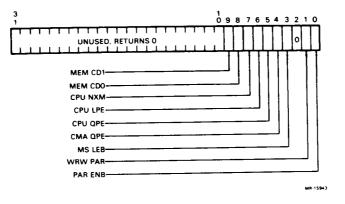

| 4-17 | Memory System Error Register (MSER)4-25          |

| 4-18 | CPU Error Address Register (CEAR)                |

| 4-19 | DMA Error Address Register (DEAR)4-28            |

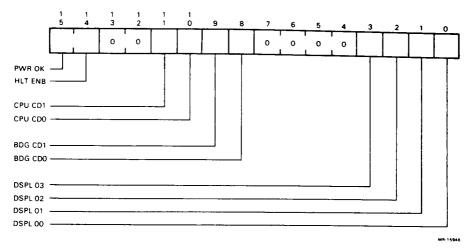

| 4-20 | Boot and Diagnostic Register (BDR)4-32           |

| 4-21 | Control and Status Register A (CSR A)4-36        |

| 4-22 | Control and Status Register B (CSR B)4-36        |

| 4-23 | Control and Status Register D (CSR D)4-37        |

| 4-24 | Console Program Mailbox (CPMBX)4-38              |

| 4-25 | Interval Clock Control and Status Register       |

|      | (ICCS)                                           |

| 4-26 | Console Receiver CSR4-42                         |

| 4-27 | Console Receiver Data Buffer4-43                 |

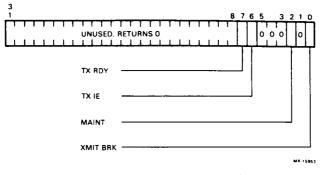

| 4-28 | Console Transmitter CSR4-44                      |

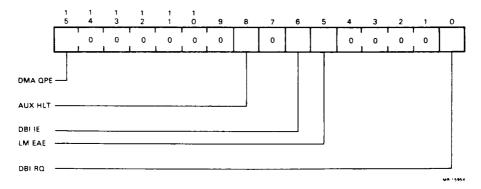

| 4-29 | Interprocessor Communication Register (IPCR)4-46 |

#### TABLES

# Table No.

# Title

# Page

| 1-1 | MS630 Memory Module Variants1-4                     |

|-----|-----------------------------------------------------|

| 1-2 | Electrical Specifications                           |

| 1-3 | Environmental Specifications                        |

| 2-1 | Memory Expansion Connector (J1) Pinouts2-2          |

| 2-2 | Configuration and Display Connector (J2) Pinouts2-3 |

| 2-3 | Console SLU Connector (J3) Pinouts                  |

| 2-4 | KA630CNF Switch Selections2-7                       |

| 2-5 | KA630CNF Connector and Switches                     |

| 3-1 | Power-Up Modes                                      |

| 3-2 | Additional Language Selections (VCB01 Only)3-7      |

| 3-3 | Console Entry Decision Table                        |

| 3-4 | VMB Register Usage                                  |

| 3-5  | VMB Bootstrap Command Flags                      |

|------|--------------------------------------------------|

| 3-6  | Console Error Messages                           |

| 3-7  | KA630-AA Halt Messages                           |

| 4-1  | Processor Status Longword Description4-2         |

| 4-2  | Processor Register Summary4-4                    |

| 4-3  | System Control Block Format                      |

| 4-4  | System Identification Register Format4-15        |

| 4-5  | Memory Register Format                           |

| 4-6  | Mapping Register Addresses                       |

| 4-7  | Memory System Error Register Format              |

| 4-8  | Boot and Diagnostic Register Format              |

| 4-9  | Watch Chip Registers                             |

| 4-10 | Time-of-Year Data Register Addresses             |

| 4-11 | Console Program Mailbox Format                   |

| 4-12 | SLU Console Registers4-41                        |

| 4-13 | Console Receiver CSR Format                      |

| 4-14 | Console Receiver Data Buffer Format              |

| 4-15 | Console Transmitter CSR Format                   |

| 4-16 | Interprocessor Communication Register Format4-47 |

| 5-1  | Diagnostic Tests                                 |

| 5-2  | KA630-AA LED Interpretation                      |

•

This manual is intended for the design engineer or applications programmer who is familiar with Digital's extended LSI-11 bus (Q22-Bus) and the VAX instruction set. This manual is divided into the following chapters:

- 1 OVERVIEW -- Introduces the KA630-AA MicroVAX CPU module and MS630 memory modules, including module features and specifications.

- 2 INSTALLATION -- Describes the installation of the KA630-AA and MS630 modules in Q22-Bus backplanes and system enclosures.

- 3 BOOTING AND CONSOLE PROGRAM INTERFACE -- Describes the console program, device booting sequence and console commands.

- 4 ARCHITECTURE -- Provides a description of KA630-AA registers, instruction set and memory.

- 5 DIAGNOSTICS -- Describes the KA630-AA boot diagnostics.

#### CONVENTIONS

The following chart lists the conventions used in this manual.

Convention Meaning

- <mm:nn> Read as "mm through nn," it indicates a bit field

or a set of lines or signals. For example,

A <17:00> is the mnemonic device that stands for

address lines 17 through 00.

- <CR> A label enclosed by angle brackets represents a key

(usually a control or special character key) on the

keyboard (in this case, the carriage return).

- NOTE Contains general information.

- CAUTION Contains information to prevent damage to equipment.

- XX Boldface capital Xs indicate variables.

#### RELATED DOCUMENTS

The following is a list of related documentation.

| Microcomputer Interfaces Handbook    | EB-20175-20 |

|--------------------------------------|-------------|

| Microcomputers and Memories Handbook | EB-18451-20 |

| VAX Architecture Handbook            | EB-19580-20 |

| VAX-11 Architecture Reference Manual | EK-VAXAR-RM |

You can order these documents from:

Digital Equipment Corporation Accessories and Supplies Group P. O. Box CS2008 Nashua, NH 03061

Attention: Documentation Products

CHAPTER 1 OVERVIEW

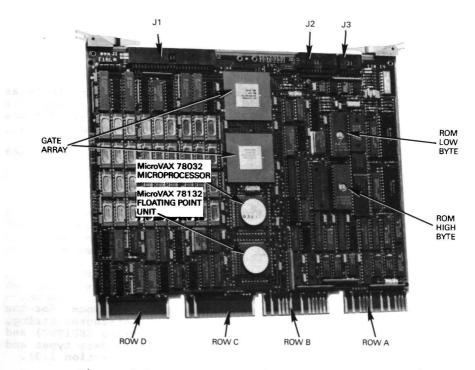

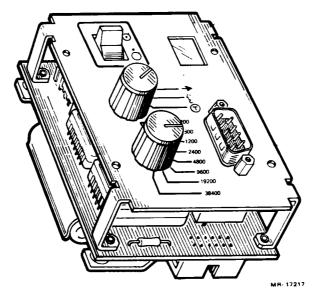

1.1 INTRODUCTION The KA630-AA (Figure 1-1) is a quad-height VAX processor module for the Q22-Bus (extended LSI-11 bus). It is designed for use in high speed, real-time applications and for multiuser, multitasking environments. It can be configured as an arbiter or auxiliary CPU. The major components of the KA630-AA are described in the following paragraphs.

Figure 1-1 KA630-AA (MicroVAX 630) CPU Module

#### 1.2 MicroVAX 78032 MICROPROCESSOR CHIP

The MicroVAX 78032 (referred to as the MicroVAX CPU chip in this manual) is a 32-bit virtual memory microprocessor packaged in a 68-pin ZMOS (double metal NMOS) chip. It requires no special clock generator or support chips. At its maximum frequency, the MicroVAX CPU chip achieves a 200 ns microcycle and a 400 ns I/O (memory) cycle. The MicroVAX CPU chip contains a 32-bit extension of the industry standard microprocessor interface.

The MicroVAX CPU chip includes a VAX compatible, demand-paged Memory Management Unit (MMU). This MMU provides direct access to four gigabytes (2\*\*32) of virtual memory and one gigabyte (2\*\*30) of physical memory. Virtual mapping of system space addresses is accomplished through single level page tables. Virtual mapping of process space addresses is accomplished through double level page tables.

The MicroVAX CPU chip provides the following subset of the VAX data types.

- Byte

- Word

- Longword

- Quadword

- Character string

- Variable length bit field

The MicroVAX 78132 Floating Point Unit (FPU) chip (referred to as the MicroVAX FPU chip in this manual) provides support for F floating, D floating and G floating data types. Support for the remaining VAX data types can be provided by macrocode emulation.

The MicroVAX CPU chip provides the following subset of the VAX instruction set.

- Integer arithmetic and logical

- Address

- Variable length bit field

- Control

- Procedure call

- Miscellaneous

- Queue

- Character string moves (MOVC3 and MOVC5)

- Operating system support

The MicroVAX CPU chip provides microcode assistance for the emulation of the remaining VAX instructions: character string, decimal string, EDIT Packed to Character string (EDITPC) and Cyclic Redundancy Check (CRC). Support for floating data types and instructions is provided by the MicroVAX FPU chip (Section 1.3).

#### 1.3 MicroVAX 78132 FPU CHIP

The MicroVAX FPU chip supports D\_floating, F\_floating and G\_floating data types and instructions. It does not support H\_floating data types or instructions. H\_floating data types can be provided by macrocode emulation.

#### 1.4 MICTOVAX INTERFACE GATE ARRAY

The MicroVAX interface gate array consists of two custom Large Scale Integration (LSI) chips. The gate array includes the following features.

- Provides interface between the MicroVAX CPU and FPU chips and module logic

- Provides signals to the KA630-AA LEDs indicating console and diagnostic boot state

- Decodes signals from the KA630-AA connector J2 to determine module characteristics

- Contains a local decoder and address latch, for use by the memory subsystem and other KA630-AA logic elements

#### 1.5 LOCAL MEMORY

The KA630-AA CPU contains 1 Mbyte of on-board local memory, and supports one or two MS630 memory expansion modules (Figure 1-2) for a maximum of 9 Mbytes of local memory. The KA630-AA communicates with MS630 memory modules through the CD interconnect of a system backplane and through a 50-conductor cable included with each memory module. MS630 memory modules are available in three variants (Table 1-1), all populated with 256 K RAM chips.

The KA630-AA provides byte parity generation and checking for all local memory. The memory mapping procedure is described in Chapter 4.

#### 1.6 64 KBYTE BOOT AND DIAGNOSTIC ROM

The KA630-AA boot and diagnostic ROM provides power-up diagnostics, boot programs for standard devices, and a subset of the VAX console program. The power-up diagnostics, booting procedure and console program are described in Chapter 3.

#### 1.7 CONSOLE SERIAL LINE UNIT (SLU)

The console SLU, described in Chapter 2, is accessed by the processor using four VAX Internal Processor Registers (IPRs), and features externally selectable baud rates. The IPRs are described in Chapter 4.

Figure 1-2 MS630 Memory Modules

Table 1-1 MS630 Memory Module Variants

| Variant  | Storage<br>(Mbytes) | Module<br>Height | Module<br>Number | Current at<br>+5 Vdc (Max) |

|----------|---------------------|------------------|------------------|----------------------------|

| MS630-AA | 1                   | Dual             | M7607-AA         | 1.0 A                      |

| MS630-BA | 2                   | Quad             | M7608-AA         | 1.3 A                      |

| MS630-BB | 4                   | Quad             | M7608-BA         | 1.8 A                      |

#### 1.8 Q22-BUS INTERFACE

The Q22-Bus interface provides the following features.

- Block mode and single transfer Direct Memory Access (DMA)

- Q22-Bus I/O map, which allows DMA devices to access local memory through a 4 Mbyte window divided into 8192 independent pages

- Q22-Bus interrupt requests BIRQ7 through 4 (when configured as an arbiter CPU)

- 240  $\Omega$  termination

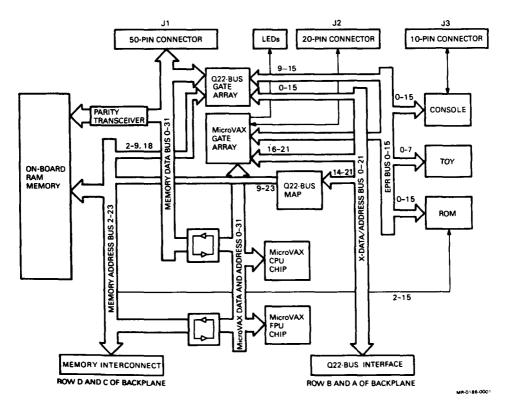

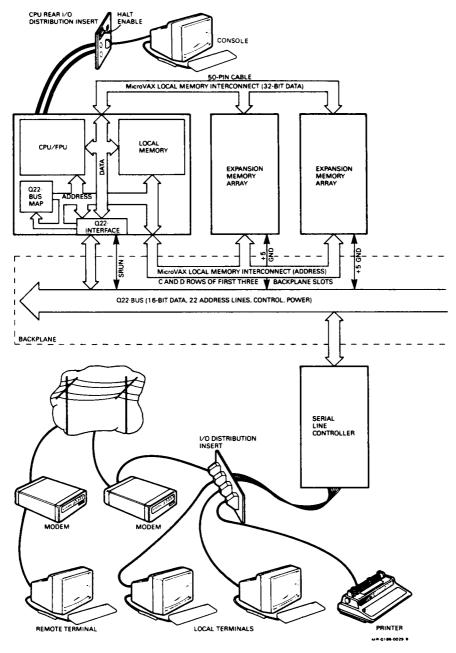

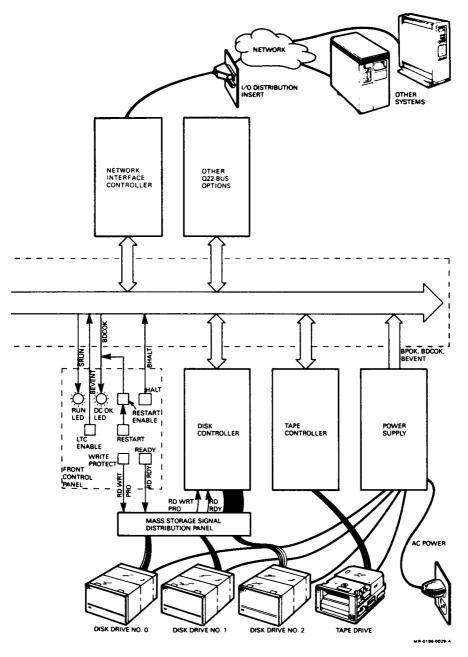

Figure 1-3 is a block diagram of the KA630-AA. Figure 1-4 is a system level block diagram.

Figure 1-3 KA630-AA Block Diagram

.

Figure 1-4 MicroVAX II System Level Block Diagram

Figure 1-4 (Cont)

#### 1.9 KA630-AA OPERATION MODES

When configured as an arbiter CPU, the KA630-AA must be installed in the first slot of a Q22-Bus backplane containing the CD interconnect. It arbitrates bus mastership and fields Q22-Bus interrupt requests BIRQ7 through 4. It also responds to interrupt requests from its own interval timer, console SLU and interprocessor doorbell. The interprocessor doorbell provides a means for auxiliary CPUs to request control of the Q22-Bus.

When configured as an auxiliary CPU, the KA630-AA can be installed in any backplane slot containing the CD interconnect. The arbiter may be a Q22-Bus PDP-11 CPU or another KA630-AA. The auxiliary KA630-AA requests bus mastership to access the Q22-Bus. It does not field Q22-Bus interrupt requests, but can respond to interrupt requests from its own interval timer, console SLU and interprocessor doorbell.

#### 1.10 KA630-AA SPECIFICATIONS

The KA630-AA CPU module electrical and environmental specifications are listed in Tables 1-2 and 1-3, respectively.

| Table  | 1-2     | Electrical | Specification | ns    |

|--------|---------|------------|---------------|-------|

| Module | Maximum | Currents   | Q22-Bus       | Loads |

|        | +5 Vđc  | +12 Vdc    | AC            | DC    |

| Quad   | 6.2 A   | 0.14 A     | 2.7           | 1.0   |

Table 1-3 Environmental Specifications

| Specification                                           | Range                                                                                                                                                       |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ambient storage temperature                             | $-40$ to $+65^{\circ}C$ (-40 to $+149^{\circ}F$ )                                                                                                           |  |  |

| Operating temperature (CPU<br>mounted in an enclosure): |                                                                                                                                                             |  |  |

| 150 ft/min air flow<br>250 ft/min air flow              | 5 to 40°C (41 to 104°F)<br>5 to 50°C (41 to 122°F)                                                                                                          |  |  |

| Relative humidity:                                      |                                                                                                                                                             |  |  |

| Storage                                                 | 10 to 90% noncondensing, altitude<br>to 9.1 km (50,000 ft). Derate<br>maximum temperature by 1°C for each<br>1000 m (1 ft for each 1000 ft) of<br>altitude. |  |  |

| Operating                                               | 10% to 90% noncondensing                                                                                                                                    |  |  |

CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

This chapter contains information required to install the KA630-AA in a system. It describes the following.

- KA630-AA connectors

- Configuration board

- CPU distribution panel

- Compatible system enclosures

### 2.2 KA630-AA CONNECTORS

The KA630-AA communicates with local memory, the console device, and the Q22-Bus through three J connectors and through its four module fingers. The user can configure the KA630-AA through a CPU distribution panel insert or a configuration board. The slot pinouts on the fingers of the KA630-AA are listed in Appendix A.

The KA630-AA has three connectors (Figure 2-1), Jl through J3.

Figure 2-1 KA630-AA Pin and LED Orientation

#### 2.2.1 Memory Expansion Connector (J1)

board. Table 2-2 lists J2 pinouts.

The 50-pin memory expansion connector provides the interface between the KA630-AA and MS630 memory modules installed in the CD rows of slots 2 and 3 of a Q22-Bus backplane containing the CD interconnect. Table 2-1 lists J1 pinouts. The memory expansion connector contains the following control, data and ground signals.

| • | BUFENL | <01:00> | (2 pins)                    |

|---|--------|---------|-----------------------------|

| • | BDIRTL |         | (1 pin)                     |

| • | PE     | <03:00> | (4 pins)                    |

| • | MD     | <31:00> | (memory data lines 32 pins) |

| • | GND    |         | (ground 11 pins)            |

2.2.2 Configuration and Display Connector (J2) The KA630-AA has no jumper or switch settings to change or set. Module configuration is done using switches on the CPU distribution panel insert or the KA630CNF configuration board. The 20-pin configuration and display connector is connected to the inside of the CPU distribution panel insert by a 20-conductor cable, or directly to connector J2 of the KA630CNF configuration

| Pin | Mnemonic | Pin | Mnemonic |

|-----|----------|-----|----------|

| 01  | GND      | 26  | GND      |

| 02  | MDO      | 27  | PEL3     |

| 03  | MD1      | 28  | BUFENL 0 |

| 04  | MD2      | 29  | MD15     |

| 05  | MD3      | 30  | GND      |

| 06  | GND      | 31  | GND      |

| 07  | MD5      | 32  | PEL2     |

| 08  | MD4      | 33  | MD17     |

| 09  | MD7      | 34  | MD18     |

| 10  | MD6      | 35  | MD19     |

| 11  | MD9      | 36  | MD20     |

| 12  | MD8      | 37  | MD21     |

| 13  | GND      | 38  | GND      |

| 14  | MD10     | 39  | MD23     |

| 15  | MD11     | 40  | MD22     |

| 16  | MD12     | 41  | MD25     |

| 17  | MD13     | 42  | MD24     |

| 18  | MD14     | 43  | MD27     |

| 19  | PELO     | 44  | MD26     |

| 20  | GND      | 45  | GND      |

| 21  | BDIRTL   | 46  | MD28     |

| 22  | MD16     | 47  | MD29     |

| 23  | BUFENL 1 | 48  | MD30     |

| 24  | PEL1     | 49  | MD31     |

| 25  | GND      | 50  | GND      |

Table 2-1 Memory Expansion Connector (J1) Pinouts

| Pin                  | Mnemonic                                         | Meaning                                                                                                                                                                                                                                                                          |

|----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01                   | GND                                              | Ground.                                                                                                                                                                                                                                                                          |

| 02                   | GND                                              | Ground.                                                                                                                                                                                                                                                                          |

| 03                   | GND                                              | Ground.                                                                                                                                                                                                                                                                          |

| 04<br>05             | CPU CDO L<br>CPU CD1 L                           | CPU Code <01:00>. This 2-bit code can be<br>configured only by using switches 7 and 8 on<br>the KA630CNF configuration board. (See Table<br>2-4.) It determines whether the KA630-AA is<br>configured as the arbiter or as one of three<br>auxiliaries.                          |

|                      |                                                  | CPU Code <01:00> Configuration                                                                                                                                                                                                                                                   |

|                      |                                                  | 00Arbiter01Auxiliary 110Auxiliary 211Auxiliary 3                                                                                                                                                                                                                                 |

|                      |                                                  | CPU Code <01:00> is read by software from the BDR.                                                                                                                                                                                                                               |

|                      |                                                  | If the CPU distribution panel insert is used,<br>no connections are made to pins 4 and 5. Ir<br>that case, signal levels are negated by<br>pull-up resistors on the KA630-AA, making it<br>the arbiter CPU.                                                                      |

| 06                   | GND                                              | Ground.                                                                                                                                                                                                                                                                          |

| 07<br>08<br>09<br>11 | DSPL 00 L<br>DSPL 01 L<br>DSPL 02 L<br>DSPL 03 L | Display Register Bits <03:00>. When asserted<br>each of these four output signals lights a<br>corresponding LED on the module. DSPL <03:00><br>are asserted (low) by power-up and by the<br>negation of DC OK. They are updated by book<br>and diagnostic programs from the BDR. |

| 10                   | BTRY VCC                                         | Battery backup voltage for TOY clock.                                                                                                                                                                                                                                            |

| 12                   | GND                                              | Ground.                                                                                                                                                                                                                                                                          |

| 13<br>14<br>14       | BDG CD0 L<br>BDG CD1 L<br>BDG CD1 L              | Boot and Diagnostic Code <01:00>. This 2-bit<br>code indicates power-up mode, and is read by<br>software from the BDR.                                                                                                                                                           |

Table 2-2 Configuration and Display Connector (J2) Pinouts\*

| Pin            | Mnemonic                            | Meaning                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             | HLT ENB L                           | Halt Enable. This input signal controls the<br>response to an external halt condition. If HLT<br>ENB is asserted (low), then the KA630-AA halts<br>and enters the console program if any of the<br>following occur.                                                                                                                                                                                    |

|                |                                     | <ul> <li>The program executes a halt instruction in<br/>kernel mode.</li> </ul>                                                                                                                                                                                                                                                                                                                        |

|                |                                     | <ul> <li>The console detects a break character.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

|                |                                     | <ul> <li>The KA630-AA is configured as an arbiter<br/>CPU and the Q22-Bus halt line is asserted.</li> </ul>                                                                                                                                                                                                                                                                                            |

|                |                                     | <ul> <li>The KA630-AA is configured as an auxiliary<br/>CPU and the interprocessor communication<br/>register AUX HLT bit is set.</li> </ul>                                                                                                                                                                                                                                                           |

|                |                                     | If HLT ENB is negated (high), then the halt<br>line and break character are ignored and the<br>ROM program responds to a halt instruction by<br>restarting or rebooting the system. If HLT ENB<br>is negated and the KA630-AA is configured as<br>an auxiliary CPU, then the ROM program<br>responds to assertion of the ICR AUX HLT bit<br>by rebooting. HLT ENB is read by software<br>from the BDR. |

| 16             | GND                                 | Ground.                                                                                                                                                                                                                                                                                                                                                                                                |

| 17<br>18<br>19 | CSBR 02 L<br>CSBR 01 L<br>CSBR 00 L | Console Baud Rate <02:00>. These three bits<br>are configured by using either the baud rate<br>select switch on the CK-KA630-A distribution<br>panel, or switches 2, 3 and 4 of the KA630CNF<br>configuration board.                                                                                                                                                                                   |

| 20             | +5 V                                | Fused +5 volts.                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 2-2 | Configuration | and | Display | Connector | (J2) | Pinouts* |

|-----------|---------------|-----|---------|-----------|------|----------|

|           | (Cont)        |     |         |           |      |          |

.

\* The KA630-AA module has 10 K pull-up resistors for the 8 input signals (pins 4 through 5, 13 through 15 and 17 through 19).

2.2.3 Console SLU Connector (J3)

The 10-pin console SLU connector provides the connection between the KA630-AA and the console terminal. It is connected to the inside of the CPU distribution panel by a 10-conductor cable, or directly to connector J3 of the KA630CNF configuration board. A cable from the outside of the distribution panel or J1 of the KA630CNF provides the external connection to the console terminal. Table 2-3 lists J3 pinouts.

| Pin      | Mnemonic             | Meaning                                             |

|----------|----------------------|-----------------------------------------------------|

| 01       |                      | EIA signal out.                                     |

| 02       | GND                  | Ground.                                             |

| 03       | SLU OUT L            | Console SLU output from the KA630-AA.               |

| 04       | GND                  | Ground.                                             |

| 05       | GND                  | Ground.                                             |

| 06       |                      | Key (no pin).                                       |

| 07<br>08 | SLU IN +<br>SLU IN - | Console SLU differential inputs to the<br>KA630-AA. |

| 09       | GND                  | Ground.                                             |

| 10       | +12 V                | Fused +12 volts.                                    |

Table 2-3 Console SLU Connector (J3) Pinouts

#### 2.3 KA630CNF CONFIGURATION BOARD

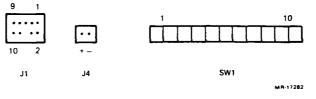

A KA630CNF (H3263-00) configuration board (Figures 2-2, 2-3, 2-4) is provided with each KA630-AA. The KA630CNF plugs directly into connectors J2 and J3 on the KA630-AA. It allows the user to configure the KA630-AA by setting the 10 switches on SW1 as listed in Table 2-4.

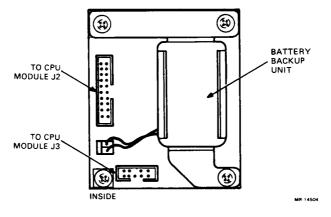

Connector J1 is used to connect a cable to the console SLU. Connector J4 is for a Battery Backup Unit (BBU). The J4 pin closest to connector J1 is the positive pin.

Table 2-5 lists the pins on the KA630-AA J2 and J3, and the corresponding KA630CNF connectors and switches on SW1. Note that connectors J2 and J3 both have more connectors than there are pins on the corresponding KA630-AA connector. The two left and two right side connectors on J2 and J3 of the KA630CNF are unused. Switches 1 through 8 on SW1 set values that enable or disable halts; and determine CPU operation mode, power-up mode, and console baud rate. SW1 switches 9 and 10 connect transmit and receive lines as required for normal operation or loopback testing.

•

SIDE VIEW

Figure 2-3

KA630CNF J2 and J3 Pin Orientation

Figure 2-4 KA630CNF J1 and J4 Pin Orientation

| Switch/Setting |           |          | Mode/Function |                                                                                              |

|----------------|-----------|----------|---------------|----------------------------------------------------------------------------------------------|

| 1              |           |          |               | Halt Mode                                                                                    |

| Off            |           |          |               | Disabled                                                                                     |

| On             |           |          |               | Enabled                                                                                      |

| 2              | 3         | 4        |               | Console Baud Rate                                                                            |

| Off            | Off       | Off      |               | 300                                                                                          |

| On             | Off       | Off      |               | 600                                                                                          |

| Off            | 0n        | Off      |               | 1,200                                                                                        |

| On             | On<br>Off | Off      |               | 2,400<br>4,800                                                                               |

| Off<br>On      | Off       | On<br>On |               | 9,600                                                                                        |

| Off            | On        | On       |               | 19,200                                                                                       |

| On             | On        | On       |               | 38,400                                                                                       |

| 5              | 6         | 9        | 10            | Power-Up Mode                                                                                |

| Off            | Off       | On       | Off           | Normal operation. Transmit line connected. Receive line connected.                           |

| On             | Off       | On       | Off           | Language inquiry mode. Transmit line connected. Receive line connected.                      |

| Off            | On        | Off      | On            | Loopback test mode (maintenance).<br>Transmit line connected to receive<br>line and console. |

| On             | On        | On       | Off           | Manufacturing use only. Bypasses<br>memory test.                                             |

| Note:<br>used. | Oth       | er se    | ttings        | for switches 5, 6, 9 and 10 should not be                                                    |

| 7              | 8         |          |               | CPU Operation Mode                                                                           |

| Off            | Off       |          |               | Arbiter                                                                                      |

| On             | Off       |          |               | Auxiliary l                                                                                  |

| Off            | On        |          |               | Auxiliary 2                                                                                  |

| On             | On        |          |               | Auxiliary 3                                                                                  |

Table 2-4 KA630CNF Switch Selections

Table 2-5 KA630CNF Connector and Switches

| CPU<br>J2<br>Pin                                                                                            | Mnemonic                                                                                                                                                                                                        | CNF J2<br>Connector                                                                                                                 | CNF SWl<br>Switch                    | CNF<br>J4<br>Pin | CPU<br>J3<br>Pin                                | Mnemonic                                                                                          | CNF J3<br>Connector                                                     | CNF SW1<br>Switch | CNF<br>Jl<br>Pin                                                     |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | GND<br>GND<br>CPU CD0 L<br>CPU CD1 L<br>GND<br>DSPL 00 L<br>DSPL 01 L<br>DSPL 02 L<br>BTRY VCC<br>DSPL 03 L<br>GND<br>BDG CD0 L<br>BDG CD1 L<br>HLT ENB L<br>GND<br>CSBR 02 L<br>CSBR 01 L<br>CSBR 00 L<br>+5 V | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | 7<br>8<br>5<br>6<br>1<br>2<br>3<br>4 | ]*               | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | EIA OUT<br>GND<br>SLU OUT L<br>GND<br>GND<br>Key (no pin)<br>SLU IN +<br>SLU IN -<br>GND<br>+12 V | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 10<br>9           | 2, 4, 5, 9<br>3<br>2, 4, 5, 9<br>2, 4, 5, 9<br>7<br>2, 4, 5, 9<br>10 |

\* +10 V from BBU to TOY clock chip on CPU

#### 2.4 CK-KA630-A CPU DISTRIBUTION PANEL INSERT

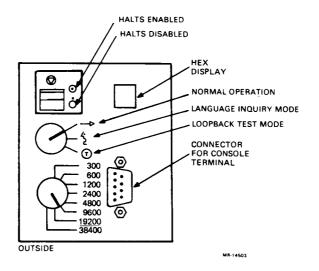

When the KA630-AA is installed in a MicroVAX II system, the CK-KA630-A CPU distribution panel insert (Figures 2-5, 2-6, 2-7) in the rear I/O distribution panel is used to select configuration settings. The KA630-AA can only function as an arbiter when it is connected to the CK-KA630-A.

The CK-KA630-A is available in two variants: the CK-KA630-AB and CK-KA630-AF. The difference is in the cable length for the J2 and J3 cables. The CK-KA630-AB is used in Digital BA23-A and BA123-A enclosures. The CK-KA630-AF is used in the H9642 and BA11-S enclosures.

#### 2.4.1 Time-Of-Year (TOY) Clock BBU

The CK-KA630-A also contains a BBU for the TOY clock chip. The BBU is located on the back of the CK-KA630-A. It consists of three nickel-cadmium batteries connected in series for a combined voltage of 3.75 Vdc. The minimum required voltage is 3.6 Vdc. The BBU provides power for the TOY clock chip when power is not supplied to the KA630-AA from the system power supply. The BBU recharges when dc power is applied to the KA630-AA. In addition to the time-of-year data, the TOY clock contains four Control and Status Registers (CSRs) and 50 bytes of RAM used by the console program (described in Chapter 3) to store information required to four CSRs are described in detail in Chapter 4.

Figure 2-5 CK-KA630-A Distribution Panel Insert

٠

Figure 2-6 CK-KA630-A Connectors (Front View)

#### 2.5 COMPATIBLE SYSTEM ENCLOSURES

The KA630-AA is compatible with the following Digital enclosures.

- BAll-S The BAll-S contains a 4 row X 9 slot backplane with 22-bit addressing on slots A/B. The C/D rows contain the CD interconnect. The backplane can contain up to nine dual-height or nine quad-height modules. Dimensions are 13.2 X 48.3 X 57.8 cm (5.2 X 19 X 22.7 in). The power supply includes a master console and provides 36 A at +5 V and 5 A at +12 V.

- BA23-A The BA23-A contains a 4 row X 8 slot 22-bit address backplane. Slots 1 through 3 provide 22-bit addressing on the A/B rows and the CD interconnect on the C/D rows. Slots 4 through 8 provide 22-bit addressing on both the A/B and C/D rows. Up to 8 guad-height, or 3 guad-height and 10 dual-height modules can be mounted. The BA23-A has mounting space for 2 13.2 cm (5.25 in) mass storage devices. The power supply includes a master console and provides 36 A at +5 V and 7 A at +12 V.

The BA23-A is also available in an H9642 cabinet, which provides 8 additional backplane slots and space for 2 26.5 cm (10.5 in) mass storage devices.

BA123-A The BA123-A contains a 4 row X 12 slot 22-bit address backplane. Slots 1 through 4 provide 22-bit addressing on the A/B rows and the CD interconnect on the C/D rows. Slots 5 through 12 provide 22-bit addressing on both the A/B and C/D rows. The BA123-A has mounting space for 5 13.2 cm (5.25 in) mass storage devices. The power supply includes a master console and 2 regulators that provide 36 A at +5 V and 7 A at +12 V per regulator. Total power from each regulator must not exceed 230 W.

#### CHAPTER 3 BOOTING AND CONSOLE PROGRAM INTERFACE

#### 3.1 INTRODUCTION

This chapter describes the KA630-AA console program and booting sequence. The console program, in conjunction with the KA630-AA hardware, gains control whenever the KA630-AA halts. For the KA630-AA, halting means only that control is transferred to this program, not that the processor stops executing instructions.

The console program is located in ROM on the KA630-AA. The ROM address range is located in the KA630-AA local I/O space. The console program uses the KA630-AA LEDs and console terminal output to communicate diagnostic progress and error reports to the user. In order for the console program to operate, the processor must be functioning at a level able to execute instructions from the console program ROM.

The console program provides the following services.

- Automatic restart or bootstrap following processor halts or initial power-up

- Interactive command language allowing the user to examine and alter the state of the processor

- Diagnostic tests executed on power-up that perform checks on the CPU, memory system and Q22-Bus I/O map

- Support of a video or hard-copy terminal as the console terminal

Users are not assumed to speak English. The console program can output console messages in 11 languages. If there is no language specified when the system powers up, the console program prompts the user for a language. The user language is then recorded (CPMBX <07:04>) in battery backed up RAM on the TOY clock chip. The preferred language is thus retained when the system is turned Off. The KA630-AA decodes the ROM addresses so that the same ROM appears more than once in the address space. The console program is written in position-independent code so that it can be executed from any address range. The KA630-AA uses this feature to selectively enable and disable the external halt circuitry. If the console program is executing in the first address range (20040000 to 2004FFFF hex), external halt conditions are ignored. If the console program is executing in the second address range (20050000 to 2005FFFF hex), external halt conditions are honored, the console program halts, and immediately starts again (at its beginning) to process the halt. The console program normally executes from the first address range.

A console terminal is not required for operation, but halts should not be enabled on a system not having a console terminal.

The console program is divided into the following major sections.

- Power-up

- Entry/dispatch

- Diagnostics

- Restart

- Bootstrap

- Console I/O mode (system halted)

- Console I/O mode (system running)

The console program receives control whenever the processor halts, which occurs as a result of any of the following conditions.

- Power-up

- External halt signal

- Execution of a halt instruction

- Serious system error

When any halt occurs, the processor performs the following.

- Switches to physical addressing

- Saves the Program Counter (PC), Processor Status Longword (PSL), and Interrupt Stack Pointer (ISP) internally

- Encodes and saves the condition that caused the halt in a halt code

- Branches to the start of the console program ROM

If the DC OK signal is present, the hex value F is displayed on the KA630-AA LEDS. Upon entry, the console program outputs the hex value E to the console LEDS, indicating that at least one instruction has been executed. It then loops until Boot and Diagnostic Register (BDR) bit 15 (PWR OK) is set, indicating that power is stable. The console program then checks bits <14:08> in IPR 43, noting if the halt is a power-up halt. If it is a power-up halt, the console program begins the power-up sequence described in Section 3.2. If the halt is the result of a condition other than power-up, control passes to the entry and dispatch code described in Section 3.3.

#### 3.2 POWER-UP

At power-up, the console initializes the KA630-AA by performing a variety of operations unique to the power-up process.

3.2.1 Power-Up Mode

At power-up, BDR <10:09> is interpreted as a power-up mode field (Table 3-1). Several power-up operations are dependent on the power-up mode.

| Mode | Language Prompt                                           | Diagnostics                             |  |  |

|------|-----------------------------------------------------------|-----------------------------------------|--|--|

| 0    | Prompt for language only if<br>TOY battery backup failed. | Run full diagnostics.                   |  |  |

| 1    | Prompt for language on every<br>power-up.                 | Run full diagnostics.                   |  |  |

| 2    | Set language to English.                                  | Run console terminal<br>loopback tests. |  |  |

| 3    | Set language to English.                                  | Run abbreviated<br>diagnostics.         |  |  |

| Table | 3-1 | Power-Up | Modes |

|-------|-----|----------|-------|

|-------|-----|----------|-------|

#### 3.2.2 Power Stabilization and ROM Checksum

The console program outputs the hex value D to the LEDs, indicating that the power stabilization wait is over. It then calculates a checksum of the console program ROM and checks it against the valid checksum stored in the ROM itself. If the computed checksum differs from the stored checksum, the console program hangs in a loop. If the checksum is the same, the power-up code proceeds to the next step.

#### 3.2.3 Console Program Initialization

The next step of the power-up initialization is location and initialization of the memory needed for the console program itself. The hex value C is output to the LEDs at the beginning of this step.

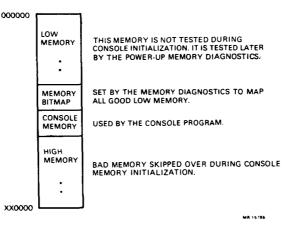

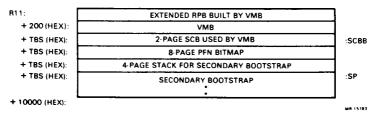

During this step, the console ROM code searches top-down through available memory for a contiguous block to be used by the console program for writeable storage. This block consists of two pages for the console's direct use and additional pages for use to store a bitmap of available memory. The amount of memory allocated to the bitmap varies according to the amount of memory available. Following initialization, memory appears as shown in Figure 3-1. The console program memory is used by the console program for its stack and other data structures.

The bitmap is filled in at a later time with a map of valid memory pages by the power-up memory diagnostics. This bitmap is passed to the bootstrap as a map of valid memory. Beginning from the base of the bitmap, the first bit corresponds to the first page of low memory, the second bit to the second page, and so on. If the bit is set, the page is good; if the bit is clear, the page failed the memory test. The bitmap does not map itself or any other memory that follows it in the console program.

Since system software is expected to use only pages marked as good in the bitmap, it is not expected to modify the bitmap or the console program memory. However, the console program memory pages and the bitmap are checksummed by the console program to guard against accidental modification by system software.

If the console program cannot locate enough memory for its own use and for the bitmap, it hangs. Following initialization of its memory, the console program clears the following Console Program Mailbox (CPMBX) register bits.

- (01:00) -- Processor halt action

- 2 -- "Bootstrap in progress" flag

- 3 -- "Restart in progress" flag

Figure 3-1 Console Memory Map After Initialization

#### 3.2.4 Battery Backup Check

The console program then checks the TOY clock to determine if the battery backup has failed. If this has happened, time-of-year data has been lost along with the contents of all the TOY clock RAM. If the battery backup has failed, the console program performs the following steps.

- Stops the TOY clock

- Zeros the time and all TOY RAM

- Initializes the four TOY clock CSRs

The operating system must check TOY clock CSR B and determine if the clock is stopped to know if the TOY clock contains a valid time. No change is made to the LEDs during this operation.

3.2.5 InterProcessor Communication Register (IPCR) Test Next, the IPCR is tested. The hex value B is output to the LEDs during this test. The test determines whether the Q22-Bus is arbitrating properly. If the CPU module is not arbitrating, the console program hangs at this point.

#### 3.2.6 Determining the Console Terminal Type

**3.2.6.1** Alternate Console Device Hardware Determination -- If the processor is an arbiter, the console program next checks for the presence of a VCB01 or VCB02 as the console device. If the KA630-AA is an auxiliary processor, this test is skipped. The hex value A is output to the LEDs during the test.

VCB01 and VCB02 alternate console devices are determined by testing for the presence of the CSR address first at 20001E92 hex (for VCB01), and then at 20001F00 hex (for VCB02). If there is no response at either location, the console program assumes that alternate console devices are not present and moves to the console terminal determination code (Section 3.2.6.2).

If a VCB01 or VCB02 video subsystem is detected, it is initialized and a short diagnostic is executed. If the initialization and diagnostics succeed, the console uses the VCB01 or VCB02 as the console terminal, skips the next step and moves directly to the console message language check (Section 3.2.7). If either the initialization or the diagnostic fails, the system hangs at this point. 3.2.6.2 Console Terminal Determination -- When VCB01 or VCB02 alternate console devices are not detected, it is assumed that a normal console terminal is connected to the console port, or that no terminal is connected. The console program then attempts to determine the type of terminal connected. This information is used when in console I/O mode to govern how command line editing is performed. The console program sends the console port a device attribute request escape sequence. If the device responds with a recognizable response, the terminal is classified as a video terminal. The terminal must respond in 1 second to the device query. When there is no response or the response is not recognized, the test is repeated twice. If the device still does not respond or the response is not recognized, the terminal is classified as a hard-copy terminal. Terminal response is recognized in either 8- or 7-bit mode.

The information obtained in this procedure is also used to determine if the terminal supports the Digital Multinational Character Set (MCS). The console program assumes that all new terminals (VT200 series and beyond) support MCS. If the terminal does not support MCS, CPMBX <07:04> is set to 2, selecting English as the console display language. The value 9 is output to the LEDs during this test.

#### 3.2.7 Console Message Language Check

The console next outputs the value 8 to the LEDs and then determines the appropriate language to use for all console messages. The console language is stored in CPMBX <07:04>. The algorithm used to determine the language follows.

- If power-up mode (Table 3-1) is 2 or 3, set the console language to English and exit.

- 2. If power-up mode is 1 and the terminal supports MCS, or if the value of CPMBX <07:04> is 0, solicit the language from the user. If the user does not respond within 30 seconds, set the language to English (mode 2) and exit.

Note that when the terminal is queried, if it is not recognized as one that supports MCS, CPMBX <07:04> is set to 2, forcing English as the console language. English messages use the 7-bit subset of MCS. If a loss of power to the TOY clock chip is detected, the contents of the TOY RAM are zeroed. This means that step 2 above causes the user to be prompted for language if the terminal supports the MCS. If the console program determines that a VCBO1 video display system is being used as the console, a step in addition to selecting one of the languages is required. The VCBO1 display system uses the DEC LK2O1 keyboard, which comes in 16 national variants (Table 3-2). The keyboard variant cannot be determined by querying the keyboard itself; it must be determined either from the language selected or by means of an additional menu selection. If French, German or English is selected, the keyboard variant is ambiguous and the additional menu is displayed. The user is prompted to specify which national keyboard variant is in use. If the user does not respond in 30 seconds, the last selection is assumed.

#### 3.3 ENTRY/DISPATCH

Following the determination of the console language on power-up, or directly on entry from any other halt condition, the console dispatches to the appropriate code to service the halt.

To determine what action to take, the console program examines the halt error code (IPR 43 <14:08>), the halt enable bit (BDR 14), and the processor halt action (CPMBX <01:00>). It then acts in accordance with the decision table shown in Table 3-3.

| ROM Language<br>Selected/<br>Additional<br>Selections | French         | German          | English                  |

|-------------------------------------------------------|----------------|-----------------|--------------------------|

| 1                                                     | Canada         | Germany/Austria | United Kingdom           |

| 2                                                     | France/Belgium | Switzerland     | United States/<br>Canada |

| 3                                                     | Switzerland    |                 |                          |

| Table 3-2 Additional Language Selections (VCB01 Only | Table | 3-2 | Additional | Language | Select | ions | (VCB01 | Only | •) |

|------------------------------------------------------|-------|-----|------------|----------|--------|------|--------|------|----|

|------------------------------------------------------|-------|-----|------------|----------|--------|------|--------|------|----|

| Table 3 | -3 | Console | Entry | Decision | Table* |

|---------|----|---------|-------|----------|--------|

|---------|----|---------|-------|----------|--------|

| Halt<br>Enable<br>(BDR 14) | Power-Up<br>Halt | Processor<br>Halt Action<br>(CPMBX <01:00>) | Functions                     |

|----------------------------|------------------|---------------------------------------------|-------------------------------|

| т                          | T                | X                                           | Diagnostics, halt.            |

| т                          | F                | 0                                           | Halt.                         |

| F                          | Т                | х                                           | Diagnostics, bootstrap, halt. |

| F                          | F                | 0                                           | Restart, bootstrap, halt.     |

| x                          | F                | 1                                           | Restart, halt.                |

| X                          | F                | 2                                           | Bootstrap, halt.              |

| Х                          | F                | 3                                           | Halt.                         |

If a power-up halt (second column) is true, it is one in which the halt error code contained in IPR 43 <14:08> equals 3. When the processor halt action is 1, 2 or 3, the condition of BDR bit 14 is ignored. When the processor halt action is 0, the action is determined by the condition of HLT ENB (BDR bit 14). Multiple actions mean that the first action is taken, and if and only if it fails, the next action is taken. Diagnostics are an exception. If diagnostics fail, the console program hangs without attempting to bootstrap the processor. If they succeed, then the next action is taken.

Note that because the KA630-AA does not support battery backup for main memory, it examines the halt code and does not attempt to perform restart operations following power-up.

### 3.4 DIAGNOSTICS

On power-up, the console outputs the message "Performing normal diagnostic tests of system" to the console terminal. The Entry/Dispatch code dispatches the diagnostics to check the processor and memory before proceeding. As each test in the diagnostics is run, it is output to the console terminal, causing a "countdown" to be displayed on the processor LEDs.

The first diagnostic LED code is 8. Executing the diagnostics continues the LED countdown. The diagnostic codes are listed in Chapter 5.

At the conclusion of all tests, the message "Tests successfully completed" is output to the console terminal. If a diagnostic test detects a fatal error, an error message is displayed on the console, along with a summary message indicating that continued operation is not possible. The console program then hangs there, leaving the test code on the LEDs. If halts are disabled, the only way to clear the system is to turn it Off and then On again. If halts are enabled, the system can be cleared by manually halting it, causing it to enter console command mode. Additional information on the diagnostics is located in Chapter 5.

### 3.5 RESTART

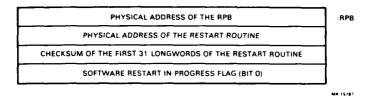

The console can restart a halted operating system. To do so, the console searches system memory for the Restart Parameter Block (RPB, Figure 3-2), a page-aligned control block created for this purpose by the operating system. If a valid RPB is found, the console restarts the operating system at an address specified in the RPB.

Figure 3-2 RPB Format

The console uses the following sequence to find an RPB:

- Searches for a page of memory that contains its address in the first longword. If none is found, the search for an RPB fails.

- 2. Reads the second longword in the page (the physical address of the restart routine). If it is not a valid physical address, or if it is 0, the console program returns to step 1. The check for 0 is necessary to ensure that a page of 0s does not pass the test for a valid RPB.

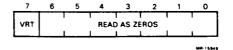

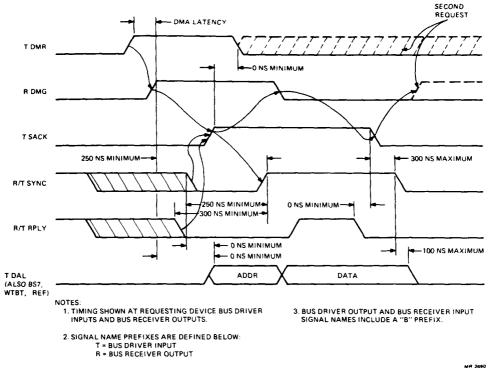

- 3. Calculates the 32-bit 2's complement sum (ignoring overflows) of the first 31 longwords of the restart routine. If the sum does not match the third longword of the RPB, the console program returns to step 1. If the sum does match, a valid RPB exists and has been found.