DZV11 asynchronous multiplexer user's guide

digital equipment corporation • maynard, massachusetts

1st Edition, February 1978 2nd Printing (Rev), August 1978

Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DĘCUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

# CONTENTS

.

## CHAPTER 1 GENERAL DESCRIPTION

| 1.1                                                                                         | INTRODUCTION                                                                                                                                                                                             | 1-1                                           |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1.2                                                                                         | PHYSICAL DESCRIPTION                                                                                                                                                                                     | 1-1                                           |

| 1.2.1                                                                                       | DZV11 Configurations                                                                                                                                                                                     | 1-1                                           |

| 1.2.2                                                                                       | BC11U Interface Cable                                                                                                                                                                                    |                                               |

| 1.2.3                                                                                       | Test Connectors                                                                                                                                                                                          |                                               |

| 1.3                                                                                         | SPECIFICATIONS                                                                                                                                                                                           |                                               |

| 1.3.1                                                                                       | Environmental                                                                                                                                                                                            | 1-5                                           |

| 1.3.2                                                                                       | Electrical                                                                                                                                                                                               | 1-5                                           |

| 1.3.3                                                                                       | Performance                                                                                                                                                                                              | Ì-5                                           |

| 1.3.3.1                                                                                     | Maximum Configurations                                                                                                                                                                                   |                                               |

| 1.3.3.2                                                                                     | Throughput                                                                                                                                                                                               |                                               |

| 1.3.3.3                                                                                     | Receivers                                                                                                                                                                                                | 1-7                                           |

| 1.3.3.4                                                                                     | Transmitters                                                                                                                                                                                             | 1-7                                           |

| 1.3.3.5                                                                                     | Baud Rate Generator                                                                                                                                                                                      | 1-7                                           |

| 1.3.3.6                                                                                     | Performance Summary                                                                                                                                                                                      | 1-7                                           |

| 1.3.4                                                                                       | Interrupts                                                                                                                                                                                               | 1-7                                           |

|                                                                                             |                                                                                                                                                                                                          |                                               |

| CHAPTER 2                                                                                   | INSTALLATION                                                                                                                                                                                             |                                               |

| <b>CHAPTER 2</b> 2.1                                                                        | INSTALLATION SCOPE                                                                                                                                                                                       | 2-1                                           |

|                                                                                             |                                                                                                                                                                                                          |                                               |

| 2.1                                                                                         | SCOPE                                                                                                                                                                                                    | 2-1                                           |

| 2.1<br>2.2                                                                                  | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE                                                                                                                                              | 2-1                                           |

| 2.1<br>2.2<br>2.3                                                                           | SCOPE<br>UNPACKING AND INSPECTION                                                                                                                                                                        | 2-1<br>2-1<br>2-1                             |

| 2.1<br>2.2<br>2.3<br>2.3.1                                                                  | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration                                                                                                                      | 2-1<br>2-1<br>2-1<br>2-1                      |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1                                                       | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration<br>Device Operation                                                                                                  | 2-1<br>2-1<br>2-1<br>2-1<br>2-3               |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2                                            | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration<br>Device Operation<br>Modem Control Jumpers.                                                                        | 2-1<br>2-1<br>2-1<br>2-1<br>2-3               |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.2                                   | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration<br>Device Operation<br>Modem Control Jumpers<br>Module Installation                                                  | 2-1<br>2-1<br>2-1<br>2-3<br>2-3               |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.2<br>CHAPTER 3                      | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration<br>Device Operation<br>Modem Control Jumpers.<br>Module Installation<br>DEVICE REGISTERS                             | 2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-3        |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.2<br><b>CHAPTER 3</b><br>3.1        | SCOPE<br>UNPACKING AND INSPECTION.<br>INSTALLATION PROCEDURE.<br>Jumper Configuration<br>Device Operation<br>Modem Control Jumpers.<br>Module Installation<br>DEVICE REGISTERS<br>SCOPE                  | 2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-3<br>2-3 |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.2<br><b>CHAPTER 3</b><br>3.1<br>3.2 | SCOPE<br>UNPACKING AND INSPECTION<br>INSTALLATION PROCEDURE<br>Jumper Configuration<br>Device Operation<br>Modem Control Jumpers<br>Module Installation<br>DEVICE REGISTERS<br>SCOPE<br>DEVICE REGISTERS |                                               |

| 3.2.3 | Line Parameters Register     |  |

|-------|------------------------------|--|

| 3.2.4 | Transmitter Control Register |  |

| 3.2.5 | Modem Status Register        |  |

| 3.2.6 | Transmit Data Register       |  |

|       | 6                            |  |

## CHAPTER 4 PROGRAMMING

| APPENDIX A | GLOSSARY                             | Δ_1 |

|------------|--------------------------------------|-----|

| 4.4.8      | Data Set Control                     | 4-5 |

| 4.4.7      | Transmitting a Character             |     |

| 4.4.6      | Emptying the Silo                    | 4-4 |

| 4.4.5      | Interrupts                           | 4-3 |

| 4.4.4      | Parity                               | 4-3 |

| 4.4.3      | Stop Bits                            |     |

| 4.4.2      | Character Length                     | 4-2 |

| 4.4.1      | Baud Rate                            | 4-2 |

| 4.4        | PROGRAMMING FEATURES                 |     |

| 4.3        | INTERRUPT VECTOR ADDRESS ASSIGNMENTS |     |

| 4.2        | DEVICE ADDRESS ASSIGNMENTS           | 4-1 |

| 4.1        | SCOPE                                | 4-1 |

## **FIGURES**

Title

.

## Figure No.

| •2<br>•3 |

|----------|

|          |

|          |

| 4        |

| 5        |

| 6        |

| 2        |

| 4        |

| 4        |

| 2        |

| •        |

# **TABLES**

## Table No.

## Title

## Page

Page

| 2-1 | Items Supplied per Configuration      | 2-1 |

|-----|---------------------------------------|-----|

| 2-2 | Jumper Configuration                  |     |

| 2-3 | M7957 Vector Address Switch Selection |     |

| 2-4 | Vector Switch Selection               | 2-5 |

| 3-1 | DZV11 Register Address Assignments    |     |

| 3-2 | CSR Bit Assignments                   |     |

| 3-3 | RBUF Bit Assignments                  |     |

| 3-4 | LPR Bit Assignments                   |     |

| 4-1 | Baud Rate Selection Chart             |     |

## CHAPTER 1 GENERAL DESCRIPTION

#### **1.1 INTRODUCTION**

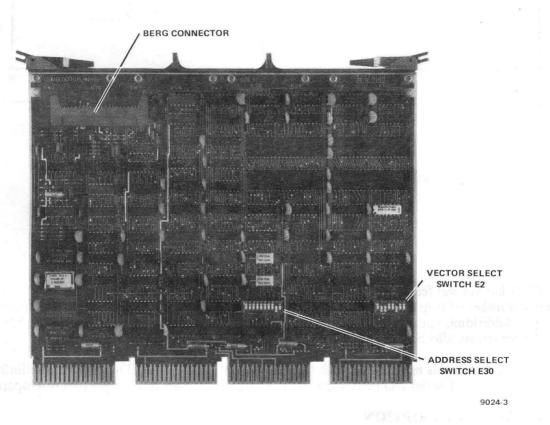

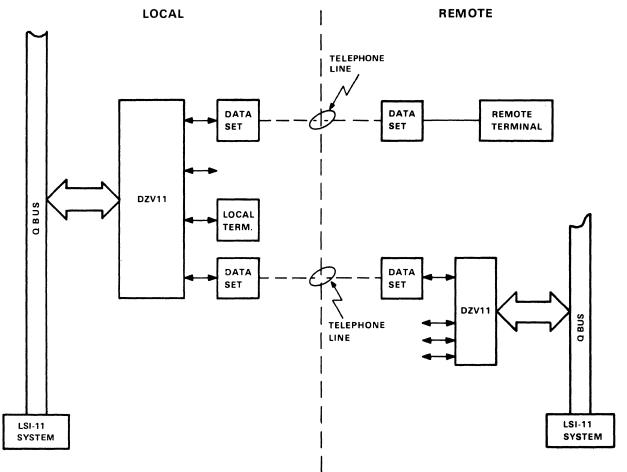

The DZV11, shown in Figure 1-1, is an asynchronous multiplexer that provides an interface between an LSI-11 processor and four asynchronous serial data communication channels. It can be used with the LSI-11 processor in a variety of applications that include data concentration, real time processing and cluster controlling. The DZV11 provides an EIA RS232C interface and enough data set control to permit dial-up (auto answer) operation with modems capable of full-duplex operation\*, such as the Bell models 103, 113, 212, or equivalent. Remote operation over private lines for full-duplex point to point or full-duplex multipoint as a control (master) station is also possible. Figure 1-2 depicts several of the possible applications for the DZV11 in an LSI-11 system.

Figure 1-1 DZV11-A (M7957 Module)

<sup>\*</sup>The DZV11 data set control does not support half-duplex operations or the secondary transmit and receive operations available with some modems such as the Bell 202, etc.

MA-0553

Figure 1-2 DZV11 System Applications

The DZV11 has several features that provide flexible control of parameters such as baud rate, character length, number of stop bits for each line, odd or even parity for each line, and transmitter-receiver interrupts. Additional features include limited data set control, zero receiver baud rate, break generation and detection, silo buffering of received data, and line turnaround.

Program compatibility is maintained with the Unibus option DZ11-A. The only compatibility exception is the number of serial channels supported. The DZV11 does not support 20 mA operation.

#### **1.2 PHYSICAL DESCRIPTION**

The DZV11 comprises a single quad size module,  $21.6 \text{ cm} \times 26.5 \text{ cm} (8.51 \text{ inches} \times 10.44 \text{ inches})$ , and is designated as the M7957 module. All input and output leads are available on a Berg header. The DZV11 connects to the LSI-11 QBUS by the H9270 mounting panel or equivalent. All QBUS input/output signals enter and leave the module via the mounting panel pins.

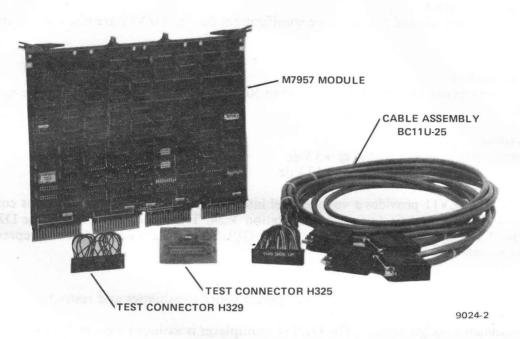

## 1.2.1 DZV11 Configurations

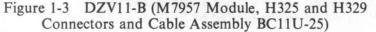

The DZV11 can be supplied in two configurations. The DZV11-A, as shown in Figure 1-1, consists of the M7957 module only. Cabling assemblies for connection to terminals and modem channels are not supplied with the DZV11-A, but are available in the DZV11-B. The DZV11-B consists of an M7957 module, BC11U-25 cable assembly, and two accessory test connectors, H329 and H325. This configuration is shown in Figure 1-3.

#### 1.2.2 BC11U Interface Cable

The interfacing cable for terminal and modem connections to the DZV11-B is provided by the BC11U cable assembly (see Figure 1-3). It consists of four separate cables, 762 cm (25 feet) in length, each terminated by a separate EIA type connector housing and a common Berg housing. Each cable within the assembly provides nine input/output leads. The EIA connector pinning conforms to EIA standard RS232C and CCITT\* recommendation V.24. The leads supported by the DZV11-B are:

| Circuit AA (CCITT 1  | 01) Pin 1 | 1  |

|----------------------|-----------|----|

| Circuit AB (CCITT 1  |           | 7  |

| Circuit BA (CCITT 1) | 03) Pin 2 | 2  |

| Circuit BB (CCITT 10 | 04) Pin 3 | 3  |

| Circuit CD (CCITT 1  |           | 20 |

| Circuit CE (CCITT 1) |           | 22 |

| Circuit CF (CCITT 1  | 09) Pin 8 | 3  |

|                      |           |    |

Protective Ground Signal Ground Transmitted Data Received Data Data Terminal Ready Ring Indicator Carrier

#### NOTE

Signal ground and protective ground are connected together.

<sup>\*</sup>CCITT – the Consultive Committee International Telegraph and Telephone is an advisory committee established under the United Nations to recommend worldwide standards.

## **1.2.3** Test Connectors

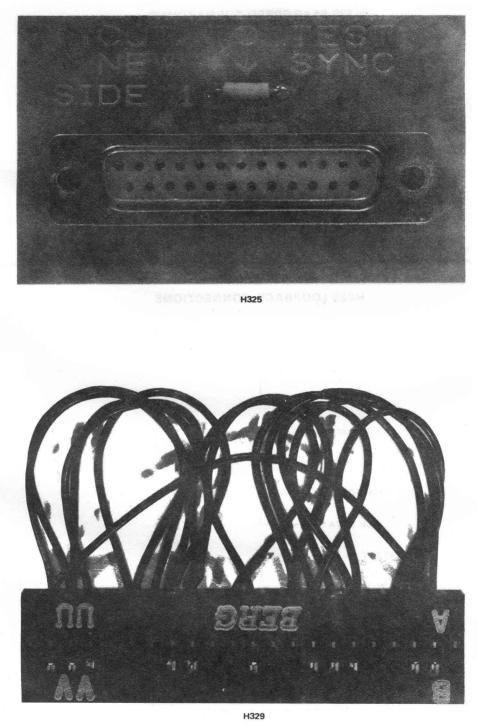

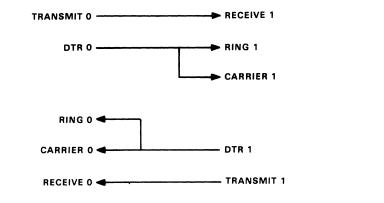

Figure 1-4 shows the two accessory test connectors, H329 and H325, that are provided with each DZV11-B. The H325 plugs into an EIA connector on the BC11U to loopback data and modem signals onto a single line. The H329 plugs into the M7957 module socket housing and provides staggered loopback of the data and modem lines. The loopback connections are shown in Figure 1-5.

## **1.3 SPECIFICATIONS**

Environmental, electrical, and performance specifications for the DZV11 are discussed in the following paragraphs.

## 1.3.1 Environmental

The DZV11 operates in an environment from 5° to 50° C (41° to 122° F) and in a relative humidity of 10% to 95%.

## 1.3.2 Electrical

| Power Consumption | 1.15 A @ +5 Vdc  |

|-------------------|------------------|

| -                 | 0.39 A @ +12 Vdc |

For each line the DZV11 provides a voltage level interface whose levels and connections conform to EIA standard RS232C and CCITT recommendation V.24. The leads supported by the DZV11 are listed in topic 1.2.2. Each DZV11 meets the LSI-11 QBUS Interface specification and represents one unit load as an interface.

## 1.3.3 Performance

The following paragraphs describe the DZV11 performance capabilities and restrictions.

**1.3.3.1** Maximum Configurations – The DZV11 multiplexer is assigned a device address in the floating address space. The floating address space starts at 760010 and extends to 764000. A maximum configuration of DZV11s would not be limited by floating address space, but would be limited by the rules governing an intermediate size system configuration. Therefore, a maximum of seven DZV11 multiplexers may reside in a nine by four backplane.

**1.3.3.2** Throughput – Each DZV11 is capable of a throughput rate of 10,970 characters per second. This rate is calculated as follows:

(Bits/Second  $\times$  No. Lines  $\times$  Direction) divided by Bits/Character. (9600  $\times$  4  $\times$  2) 1/7 equals 10,970 Characters/Second.

For a character service routine of 100  $\mu$ s or less, the device throughput rate can be sustained.

**1.3.3.3** Receivers – The receivers provide serial to parallel conversion of 5, 6, 7, 8 level code with one start space and at least one stop mark. The character length, number of stop bits, parity generation and operating speed are programmable parameters for each line. A receiver and transmitter of a corresponding line share the same operating speed with provisions for enabling/disabling of that receive line.

Each receiver is double-buffered and has an allowable input distortion of 43.75% on any bit. Also, the accumulated character distortion must not exceed 43.75%. Break detection is provided on each receiver.

9024-1

Figure 1-4 Test Connectors H325 and H329

#### H329 STAGGERED TURNAROUND

NOTE: LINES 2&3 ARE STAGGERED IN THE SAME WAY.

H325 LOOPBACK CONNECTIONS

MA-0551

Figure 1-5 Loopback Connections

**1.3.3.4** Transmitters – The transmitters provide parallel to serial conversion of 5, 6, 7, 8 level code with or without parity. The parity sense when selected can be either odd or even. The stop code can be either 1 or 2 units except when 5 level code is selected. When 5 level code is selected, the stop code can be set to 1 or 1.5 units. The character length, number of stop units, parity generation and sense, and operating speed are programmable parameters for each line. The operating speed for the transmitter is common with the receiver. Breaks are capable of being transmitted on any line. The gross start-stop distortion for a transmitter's TTL output will be less than 2.5% for an 8-bit character.

**1.3.3.5** Baud Rate Generator – The baud rate generator is a MOS/LSI device which provides the DZV11 multiplexer with full programmable capability for operating speed selection. Each line has an independent generator capable of producing 1 of 15 selectable baud rates. Speed tolerance for all rates is less than 0.3% with a clock duty of  $50\% \pm 5\%$ . (See below for rates.)

**1.3.3.6 Performance Summary** – The following summarizes the programmable features offered for each line:

| Character length    | 5, 6, 7, or 8 level code                                                              |

|---------------------|---------------------------------------------------------------------------------------|

| Number of stop bits | 1 or 2 for 6, 7, 8 level code<br>1 or 1.5 for 5 level code                            |

| Parity              | odd, even or none                                                                     |

| Baud rates          | 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 3600, 4800, 7200, and 9600 |

| Breaks              | Can be generated and detected on each line.                                           |

## 1.3.4 Interrupts

The following interrupts are available on DZV11.

## **Receiver Done Interrupt**

Occurs every time a character appears at the output of the receiver buffer register and the Silo Alarm is disabled. Can be enabled or disabled from the bus.

#### Silo Alarm Interrupt

Occurs after 16 entries have been made into the receive buffer register by the scanner. This interrupt disables Receiver Done Interrupt and is rearmed when the receive buffer register has been read.

## **Transmit Interrupt**

Occurs every time the scanner finds a UART buffer empty condition, and the transmitter control register bit is set for that line. Can be enabled or disabled from the bus.

# CHAPTER 2 INSTALLATION

### 2.1 SCOPE

This chapter contains the procedures for the unpacking, installation, and initial checkout of the DZV11 Asynchronous Multiplexer.

#### 2.2 UNPACKING AND INSPECTION

The DZV11 is packaged in accordance with commercial packaging practices. First, remove all packing material and check the equipment against the shipping list. (Table 2-1 contains a list of supplied items per configuration.) Report damage or shortages to the shipper immediately and notify the DIGITAL representative. Inspect all parts and carefully inspect the module for cracks, loose components, and separations in the etched paths.

| Quantity | Description                | Α | В |  |

|----------|----------------------------|---|---|--|

| 1        | M7957 module               | X | x |  |

| 1        | BC11U-25 cable assembly    |   | X |  |

| 1        | H329 test connector        |   | X |  |

| 1        | H325 test connector        |   | X |  |

| 1        | Print set (B-TC-DZV11-0-1) | X | X |  |

|          | DZV11-A and -B             |   |   |  |

|          | Order number MP00462       |   |   |  |

| 1        | Software kit ZJ251-RB      | X | X |  |

| 1        | DZV11 User's Guide         | X | X |  |

|          | (EK-DZV11-UG)              |   |   |  |

Table 2-1

Items Supplied per Configuration

#### 2.3 INSTALLATION PROCEDURE

The following paragraphs describe the installation of the DZV11 option in an LSI-11 system.

#### 2.3.1 Jumper Configuration

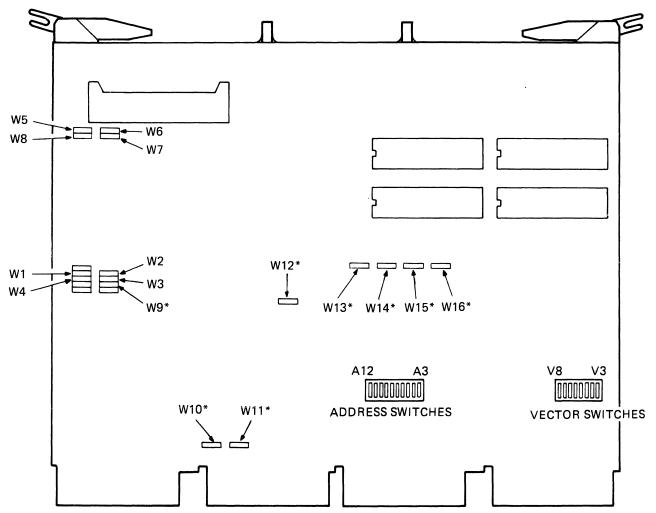

There are 16 machine-insertable jumpers on the M7957 module (Figure 2-1).

**2.3.1.1** Device Operation – Jumpers W10 and W11 must be installed only when the module is used on an H9270 backplane, or one that applies LSI-11 bus signals to the C and D sections of the module.

\*NOTES:

JUMPERS W9, W12, W13, W14, W15, AND W16 ARE REMOVED ONLY FOR MANUFAC-TURING TESTS. THEY SHOULD NOT BE REMOVED IN THE FIELD.

JUMPERS W10 AND W11 MUST REMAIN INSTALLED WHEN THE MODULE IS USED IN A BACKPLANE THAT SUPPLIES LSI-11 BUS SIGNALS TO THE C AND D CONNECTORS OF THE DZV11 (SUCH AS THE H9270). WHEN THE MODULE IS USED IN A BACK-PLANE THAT INTERCONNECTS THE C AND D SECTIONS TO AN ADJACENT MODULE, JUMPERS W10 AND W11 MUST BE REMOVED.

MK-0064

**2.3.1.2** Modem Control Jumpers – There are eight jumpers used for modem control. The jumpers labeled W1 through W4 connect Data Terminal Ready (DTR) to Request To Send (RTS). This allows the DZV11 to assert both DTR and RTS if using a modem that requires control of RTS. These jumpers must be installed to run the cable and external test diagnostic programs. The remaining four jumpers, W5 through W8, connect the Forced Busy (FB) leads to the RTS leads. With these jumpers installed, the assertion of an RTS lead places an ON or BUSY signal on the corresponding Forced Busy lead. The Forced Busy jumpers (W5 through W8) are normally cut out unless the modem requires them (Table 2-2).

| Jumper | oper Connection |    |

|--------|-----------------|----|

| W1     | DTR to RTS      | 03 |

| W2     | DTR to RTS      | 02 |

| W3     | DTR to RTS      | 01 |

| W4     | DTR to RTS      | 00 |

| W5     | RTS to FB       | 03 |

| W6     | RTS to FB       | 02 |

| W7     | RTS to FB       | 01 |

| W8     | RTS to FB       | 00 |

Table 2-2

Jumper Configuration

## 2.3.2 Module Installation

To install the M7957 module, perform the following.

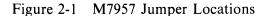

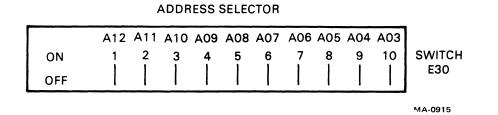

- 1. Refer to Paragraph 4.2 for descriptions of the address assignments. Set the switches at E30 so that the module responds to its assigned address. When a switch is closed (ON), a binary 1 is decoded. When a switch is open (OFF), a binary 0 is decoded. Note that the switch labeled 1 corresponds to address bit 12, 2 corresponds to address bit 11, etc. (Figure 2-2 and Table 2-3).

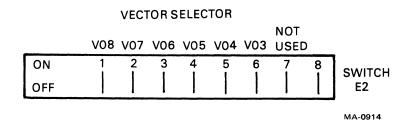

- 2. Vector selection is accomplished by the 8-position switch at E2. Switch positions 7 and 8 are not used. Switch position 6 corresponds to vector bit 3, 5 corresponds to vector bit 4, etc. When a switch is closed (ON), a binary 1 is decoded. When a switch is open (OFF), a binary 0 is decoded (Figure 2-3 and Table 2-4).

- 3. If the module is part of the DZV11-A option, perform step 3. If it is a part of the DZV11-B option, proceed to step 4 for testing.

- a. Insert the module in a quad QBus slot of the backplane.

## CAUTION

#### Insert and remove modules slowly and carefully to avoid snagging module components on the card guides and changing switch settings inadvertently.

- b. Run the DZV11 diagnostics, MAINDECs DVDZA and DVDZB, in internal mode to verify operation. Refer to the listing for assistance. Run at least three passes without error.

- c. Proceed to step 8.

Figure 2-2 M7957 Address Selection

| E30<br>Switch<br>Address | 1<br>A12 | 2<br>A11 | 3<br>A10 | 4<br>A9 | 5<br>A8 | 6<br>A7 | 7<br>A6 | 8<br>A5 | 9<br>A4 | 10<br>A3 |

|--------------------------|----------|----------|----------|---------|---------|---------|---------|---------|---------|----------|

| 160000                   | _        | _        | _        | _       | -       | -       | _       | _       | _       | _        |

| 160010                   |          | -        | _        | -       | -       | -       | -       | -       | _       | X        |

| 160020                   | -        | _        | _        | _       | _       | _       | _       | _       | X       | -        |

| 160030                   | -        | _        | _        | -       | _       | _       | _       | -       | X       | X        |

| 160040                   | -        | -        | _        | _       | _       | _       | _       | X       | _       | _        |

| 160050                   | -        | _        | -        | _       | _       | -       | _       | X       | -       | X        |

| 160060                   | -        | _        | -        | _       | _       | _       | _       | X       | X       | _        |

| 160070                   | _        | _        | -        | -       | _       | -       | _       | X       | X       | X        |

| 160100                   | -        | _        | -        | -       | -       | -       | X       | -       | _       | _        |

|                          |          |          |          |         |         |         |         |         |         |          |

| 163760<br>163770<br>X    |          |          | X<br>-   | X<br>X  | X<br>X  | X<br>X  | X<br>X  | X<br>X  | X<br>X  | -<br>X   |

Table 2-3

Address Switch Selection

NOTE: X = ON- = OFF

Figure 2-3 M7957 Vector Selection

| E2<br>Switch<br>Vector | 1<br>V08                                      | 2<br>V07 | 3<br>V06 | 4<br>V05 | 5<br>V04 | 6<br>V03 |

|------------------------|-----------------------------------------------|----------|----------|----------|----------|----------|

| 300                    | _                                             | x        | X        | _        | _        | _        |

| 310                    | -                                             | X        | X        | -        | -        | X        |

| 320                    | -                                             | X        | X        | -        | X        | -        |

| 330                    | -                                             | X        | X        | -        | X        | X        |

| 340                    | -                                             | X        | X        | X        | -        | -        |

| 350                    | -                                             | X        | X        | X        | -        | X        |

| 360                    | -                                             | X        | X        | X        | X        | -        |

| 370                    | -                                             | X        | X        | X        | X        | X        |

| 400                    |                                               | - 1      | -        | -        | -        | -        |

|                        |                                               |          |          |          |          |          |

| •                      |                                               |          |          |          |          |          |

| •                      |                                               |          |          |          |          |          |

| 760                    | X                                             | X        | X        | X        | X        | -        |

| 770                    | X                                             | X        | X        | X        | X        | X        |

| NOTE:                  | $\begin{array}{c} X = O \\ - = O \end{array}$ |          |          |          |          |          |

Table 2-4 Vector Switch Selection

- 4. Insert the H329 test connector in J1 with the letter side facing up. J1 is the cable connector at the top of the M7957 module.

- 5. Insert the module in a quad QBus slot of the backplane.

### CAUTION

#### Insert and remove modules slowly and carefully to avoid snagging module components on the card guides and changing switch settings inadvertently.

Run the DZV11 diagnostics, MAINDECs DVDZA and DVDZB, in the staggered mode to verify module operation. Refer to the diagnostic listing for the correct procedure. Run at least three passes without error.

- 6. Replace the H329 test connector with the Berg end of the BC11U cable assembly. Observe the "This Side Up" wording on the assembly. Refer to D-UA-DZV11-0-0 for installation help.

- 7. Connect the H325 test connector on the first line and run MAINDEC DVDZC. Select the cable test portion of the diagnostic. Three passes are required without error. Repeat this step for each line.

- 8. Run DEC/X11 system exerciser to verify the absence of QBus interference with other system devices.

9. The DZV11 is now ready for connection to external equipment. If the connection is to a local terminal through the DZV11-B option, a null modem cable assembly must be used. Use the BC03M or BC03P null modem cables for connection between the BC11U and the terminal. The H312-A null modem unit may also be used in place of the null modem cables. If connection is to a Bell 103 or equivalent modem, install the appropriate line of the BC11U connector into the connector on the modem. A BC05D cable may be required between the BC11U and the modem. Refer to Paragraph 2.3.1.2, Modem Control Jumpers, for selection of jumpers for modem options such as RTS and forced busy. All of the cables mentioned, excluding the BC11U, must be ordered separately as they are not components of a standard DZV11 shipment. When possible, run the diagnostic DVDZC in echo test mode to verify the cable connections and the terminal equipment.

۲

## CHAPTER 3 DEVICE REGISTERS

#### 3.1 SCOPE

This chapter provides a description of each DZV11 register, its format, and bit functions.

#### **3.2 DEVICE REGISTERS**

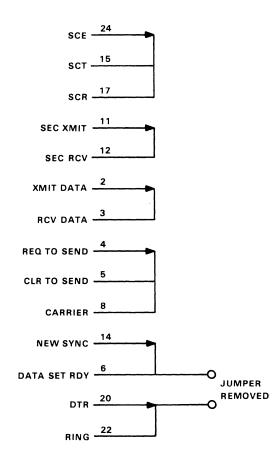

The DZV11 contains six addressable registers. A comprehensive pictorial of these registers' bit assignments is shown in Figure 3-1. Table 3-1 lists the registers and associated DZV11 addresses.

| Register                     | Mnemonic | Address | Program<br>Capability |

|------------------------------|----------|---------|-----------------------|

| Control and Status Register  | CSR      | 76XXX0  | Read/Write            |

| Receiver Buffer              | RBUF     | 76XXX2  | Read Only             |

| Line Parameter Register      | LPR      | 76XXX2  | Write Only            |

| Transmitter Control Register | TCR      | 76XXX4  | Read/Write            |

| Modem Status Register        | MSR      | 76XXX6  | Read Only             |

| Transmit Data Register       | TDR      | 76XXX6  | Write Only            |

Table 3-1 DZV11 Register Address Assignments

XXX = Selected in accordance with floating device address scheme.

#### 3.2.1 Control and Status Register

The control and status register (CSR) is a byte and word addressable register. All bits in the CSR are cleared by an occurrence of BINIT or by setting device Master Clear (CSR 04). The format is shown in Figure 3-1 and the bit assignments are listed in Table 3-2.

#### **3.2.2 Receiver Buffer**

The Receiver Buffer (RBUF) is a 16-bit read only register which contains the received character at the output of the FI/FO buffer. A read of the register causes the character entry to be extracted from the buffer and all other entries to bubble down to the lowest unoccupied location. Only the Valid Data bit (RBUF 15) is cleared by BINIT or by setting device Master Clear (CSR 04). Bits 00–14 are not affected. The bit assignments for the RBUF register are listed in Table 3-3.

|     |                              | MSB<br>15           | 14                | 13                | 12               | 11                       | 10                       | 09                       | BYT<br>HIGH<br>08        |                  | 06                | 05                 | 04                      | 03                      | 02                             | 01                       | LSB<br>00                |

|-----|------------------------------|---------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|--------------------------|--------------------------|------------------|-------------------|--------------------|-------------------------|-------------------------|--------------------------------|--------------------------|--------------------------|

|     | CONTROL<br>& STATUS<br>(CSR) | RO                  | RW<br>TIE         | _ <u>RO</u><br>SA | _RW              | USED VOY                 | USED.                    | RO<br>TLINE<br>B         | <u>RO</u><br>TLINE<br>A  | . <u>RO</u>      | RW<br>RIE         | <u>RW</u><br>MSE   | <u>RW</u><br>CLR        | <u>RW</u>               | USED 1                         | USED T                   | LOW CLUS                 |

| DR2 | RECEIVER<br>BUFFER<br>(RBUF) | RO<br>DATA<br>VALID | RO<br>OVRN<br>ERR | RO<br>FRAM<br>ERR | RO<br>PAR<br>ERR | USED LOT                 | USED .                   | RO<br>RX<br>LINE<br>B    | RO<br>RX<br>LINE<br>A    | RO<br>RBUF<br>D7 | RO<br>RBUF<br>D6  | RO<br>RBUF<br>D5   | RO<br>RBUF<br>D4        | <u>RO</u><br>RBUF<br>D3 | RO<br>RBUF<br>D2               | RBUF<br>D1               | RBUF<br>D0               |

|     | LINE<br>PARAMETER<br>(LPR)   | NOT CIT             | USED              |                   | WO<br>RX<br>ENAB | WO<br>SPEED<br>CODE<br>D | WO<br>SPEED<br>CODE<br>C | WO<br>SPEED<br>CODE<br>B | WO<br>SPEED<br>CODE<br>A | WO<br>ODD<br>PAR | WO<br>PAR<br>ENAB | WO<br>STOP<br>CODE | WO<br>CHAR<br>LGTH<br>B | WO<br>CHAR<br>LGTH<br>A | LON 10350                      | WO<br>LINE<br>B          | WO<br>LINE<br>A          |

| DR4 | TRANSMIT<br>CONTROL<br>(TCR) | USED USED           | USED              | 1.2 KO7           | USE01            | RW<br>DTR<br>3           | RW<br>DTR<br>2           | <u>RW</u><br>DTR<br>1    | <u>RW</u><br>DTR<br>0    | USED             | USED              | USED               | USED                    | _ <u>RW</u>             | <u>RW</u><br>LINE<br>ENAB<br>2 | _RW<br>LINE<br>ENAB<br>1 | _RW<br>LINE<br>ENAB<br>0 |

|     | MODEM<br>STATUS<br>(MSR)     | Lon USED            | USED              | 1040<br>10250     | 1015<br>10250    | RO<br>CO<br>3            | RO<br>CO<br>2            | RO<br>CO<br>1            | RO<br>CO<br>0            | USED             | USED              | USED T             | 101<br>10250            | RO<br>RI 3              | RO<br>RI 2                     | RO<br>RI 1               | RO<br>RI 0               |

|     | TRANSMIT<br>DATA<br>(TDR)    | Used                | USED.             | 104<br>10255      | 101<br>10255     | WO<br>BRK<br>3           | WO<br>BRK<br>2           | WO<br>BRK<br>1           | WO<br>BRK<br>0           | WO<br>TBUF<br>7  | WO<br>TBUF<br>6   | WO<br>TBUF<br>5    | WO<br>TBUF<br>4         | WO<br>TBUF<br>3         | WO<br>TBUF<br>2                | WO<br>TBUF<br>1          | WO<br>TBUF<br>0          |

MA-0552

Figure 3-1 Register Bit Assignments

£

| Bit   | Title                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00–02 | Not used                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 03    | Maintenance                     | This bit, when set, loops all the transmitter's serial output leads<br>to the corresponding receiver's serial input leads on a TTL<br>basis. While operating in maintenance mode, the EIA received<br>data leads are disabled. Normal operating mode is assumed<br>when this bit is cleared. This bit is read/write.                                                                                                                                                                                                                                                           |

| 04    | Master Clear                    | When written to a 1, generates "Initialize" within the DZV11. A read back of the CSR with this bit set, indicates initialize in progress within the device. This bit is self-clearing. All registers, silos, and UARTS are cleared with the following exceptions:                                                                                                                                                                                                                                                                                                              |

|       |                                 | 1. Only bit 15 of the receiver buffer register (VALID DATA); the remaining bits 00-14 are not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                 | 2. The high byte of the transmitter control register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                 | 3. The modem status register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 05    | Master Scan<br>Enable           | This read/write bit must be set to permit the receiver and trans-<br>mitter control sections to begin scanning. When cleared, Trans-<br>mitter Ready (CSR 15) will be inhibited from setting and the<br>received character buffers (silos) will be cleared.                                                                                                                                                                                                                                                                                                                    |

| 06    | Receiver<br>Interrupt<br>Enable | This bit, when set, permits the setting of CSR 07 or CSR 13 to generate a receiver interrupt request. This bit is read/ write.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 07    | Receiver Done                   | This is a read only bit that will set when a character appears at<br>the output of the FI/FO buffer. To operate in interrupt per<br>character mode, CSR 06 must be set and CSR 12 must be<br>cleared. With CSR 06 and CSR 12 cleared, character flag mode<br>would be indicated. Receiver Done will clear when the receiver<br>buffer register (RBUF) is read or when Master Scan Enable<br>(CSR 05) is cleared. If the FI/FO buffer contains an additional<br>character, the Receiver Done flag will stay cleared a minimum<br>of 1 $\mu$ s before presenting that character. |

| 08–09 | Transmitter Line<br>Number      | These read only bits indicate the line number whose transmit<br>buffer requires servicing. These bits are valid only when Trans-<br>mitter Ready (CSR 15) is set and will be cleared when Master<br>Scan Enable is cleared. Bit 08 is the least significant bit.                                                                                                                                                                                                                                                                                                               |

| 10–11 | Not used                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | ~~~ ~  |                |

|-----------|--------|----------------|

| Table 3-2 | CSR Bi | it Assignments |

| Bit | Title                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 12  | Silo Enable<br>Alarm               | This is a read/write bit, when set, enables the silo alarm counter<br>to keep count of the number of characters stored in the FI/FO<br>buffer. The counter will be cleared when the Silo Alarm Enable<br>bit is cleared. Conditioning of this bit must occur prior to any<br>character reception.                                                                                                                                                                                                                                                                   |  |  |  |

| 13  | Silo Alarm                         | This is a read only bit set by the hardware after 16 characters<br>have been entered into the FI/FO buffer. Silo Alarm will be<br>held cleared when Silo Alarm Enable (CSR 12) is cleared. This<br>bit will be reset by a read to the receiver buffer register and will<br>not set until 16 additional characters are entered into the buffer.<br>If Receiver Interrupt Enable (CSR 06) is set, the occurrence of<br>Silo Alarm will generate a receiver interrupt request. Reception<br>with CSR 06 cleared, permits flag mode operation of the Silo<br>Alarm bit. |  |  |  |

| 14  | Transmitter<br>Interrupt<br>Enable | This bit must be set for Transmitter Ready to generate an inter-<br>rupt. It is read/write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 15  | Transmitter<br>Ready               | This bit is read only and is set by the hardware. This bit will set<br>when the transmitter clock stops on a line whose transmit buffer<br>may be loaded with another character and whose associated<br>TCR bit is set. The Transmitter Line Number, specified in CSR<br>08 and CSR 09, is only valid when Transmitter Ready is set.<br>Transmitter Ready will be cleared by any of the following<br>conditions:                                                                                                                                                    |  |  |  |

|     |                                    | 1. Master Scan Enable cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|     |                                    | 2. When the associated TCR bit is cleared for the line number pointed to in CSR 08 and CSR 09.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|     |                                    | 3. At the conclusion of the load instruction of the trans-<br>mit data register (low byte only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|     | ~                                  | If additional transmit lines require service, Transmitter Ready<br>will reappear within 1.4 $\mu$ s from the completion of the transmit<br>data register load instruction. The occurrence of Transmitter<br>Ready with Transmitter Interrupt Enable set, will generate a<br>transmitter interrupt request.                                                                                                                                                                                                                                                          |  |  |  |

| Table 3-2 | CSR | Bit | Assignments  | (Cont) | ) |

|-----------|-----|-----|--------------|--------|---|

|           |     |     | TROOPERTATES | Come,  | , |

Ŧ

| Bit   | Title                                | Function                                                                                                                                                                                                                                                                                                                                     |

|-------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00–07 | Received<br>Character                | These bits contain the received character, right justified. The least significant bit is bit 00. Unused bits are 0. The parity bit is not shown.                                                                                                                                                                                             |

| 08–09 | Received<br>Character<br>Line Number | These bits contain the line number upon which the aforemen-<br>tioned character was received. Bit 08 is the least significant bit.                                                                                                                                                                                                           |

| 10-11 | Not used                             |                                                                                                                                                                                                                                                                                                                                              |

| 12    | Parity Error                         | This bit is set if the sense of the parity of the received character does not agree with that designated for that line.                                                                                                                                                                                                                      |

| 13    | Framing Error                        | This bit is set if the received character did not have a stop bit<br>present at the proper time. This bit is usually interpreted as in-<br>dicating the reception of a break.                                                                                                                                                                |

| 14    | Overrun Error                        | This bit is set if the received character was preceded by a charac-<br>ter that was lost due to the inability of the receiver scanner to<br>service the UART receiver holding buffer on that line.                                                                                                                                           |

| 15    | Valid Data                           | This bit, when set, indicates that the data presented in bits $00-14$ is valid. This bit permits the use of a character handling program that takes characters from the FI/FO buffer until there are no more available. This is done by reading this register and checking bit 15 until the program obtains a word for which bit 15 is zero. |

## Table 3-3 RBUF Bit Assignments

## 3.2.3 Line Parameter Register

The line parameter register (LPR) controls the operating parameters associated with each line in the DZV11. The LPR is a word addressable, write only register. The line parameters for all lines must be reloaded following an occurrence of either BINIT or device Master Clear. Table 3-4 lists bit assignments.

## 3.2.4 Transmitter Control Register

The transmitter control register (TCR) is a byte and word addressable register. The low byte of the TCR register contains the transmitter control bits which must be set to initiate transmission on a line. Each TCR bit position corresponds to a line number. For example, TCR bit 00 corresponds to line 00, bit 01 to line 01, etc. Setting of a TCR bit causes the transmitter scanner clock to stop if the UART for this line has a transmit buffer empty condition. An interrupt will then be generated if Transmitter Interrupt Enable is set. The scanner clock will restart when either the transmit data register is loaded with a character or the TCR bit is cleared for the line on which the clock has stopped. TCR bits must only be cleared when the scanner is not running, (i.e., Transmitter Ready is set or Master Scan Enable is cleared.)

The TCR bits are represented in bits 00–03. These bits are read/write and are cleared by BINIT or device Master Clear. Bits 04–07 are unused and read as zero.

The high byte of the TCR register contains the writable modem control lead, data terminal ready (DTR). Bit designations are as follows:

| Bit   | Name                 |

|-------|----------------------|

| 08    | DTR Line 00          |

| 09    | DTR Line 01          |

| 10    | DTR Line 02          |

| 11    | DTR Line 03          |

| 12-15 | Unused; read as zero |

Assertion of a DTR bit puts an ON condition on the appropriate modem circuit for that line. DTR bits are read/write and are cleared only by BINIT. Jumpers have been provided to allow the Request to Send circuits to be asserted with Data Terminal Ready assertions.

| Bit   | Title                    | Function                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 00–01 | Parameter Line<br>Number | These bits specify the line number for which the parameter in-<br>formation (bits 3-12) is to apply. Bit 00 is the least significant<br>bit.                                                                                                                                                                                                                                           |  |  |  |

| 02    | Not used                 | Must always be written as a zero when specifying the parameter<br>line number. Writing this bit as a one will extend the parameter<br>line number field into nonexistent lines. Parameters for lines<br>00-03 will not be affected.                                                                                                                                                    |  |  |  |

| 03–04 | Character<br>Length      | These bits are set to receive and transmit characters of the length (excluding parity) as shown below.                                                                                                                                                                                                                                                                                 |  |  |  |

|       |                          | 04         03           0         0         5 bit           0         1         6 bit           1         0         7 bit           1         1         8 bit                                                                                                                                                                                                                          |  |  |  |

| 05    | Stop Code                | This bit sets the stop code length $(0 = 1 \text{ unit stop}, 1 = 2 \text{ unit stop or } 1.5 \text{ unit stop if a 5-level code is employed}).$                                                                                                                                                                                                                                       |  |  |  |

| 06    | Parity Enable            | If this bit is set, characters transmitted on the line have an appropriate parity bit affixed, and characters received on the line have their parity checked.                                                                                                                                                                                                                          |  |  |  |

| 07    | Odd Parity               | If this bit is set and bit 06 is set, characters of odd parity are<br>generated on the line and incoming characters are expected to<br>have odd parity. If this bit is not set, but bit 06 is set, characters<br>of even parity are generated on the line and incoming characters<br>are expected to have even parity. If bit 06 is not set, the setting<br>of this bit is immaterial. |  |  |  |

Table 3-4LPR Bit Assignments

| Bit   | Title              | Func | tion                                                                                                         |          |            |                                                                                                |  |  |  |

|-------|--------------------|------|--------------------------------------------------------------------------------------------------------------|----------|------------|------------------------------------------------------------------------------------------------|--|--|--|

| 08-11 | Speed Code         |      | The state of these bits determine the operating speed for the transmitter and receiver of the selected line. |          |            |                                                                                                |  |  |  |

|       |                    | 11   | 10                                                                                                           | 09       | 08         | Baud Rate                                                                                      |  |  |  |

|       |                    | 0    | 0                                                                                                            | 0        | 0          | 50                                                                                             |  |  |  |

|       |                    | 0    | 0                                                                                                            | 0        | 1 ,        | 75                                                                                             |  |  |  |

|       |                    | 0    | 0                                                                                                            | 1        | 0          | 110                                                                                            |  |  |  |

|       |                    | 0    | 0                                                                                                            | 1        | 1          | 134.5                                                                                          |  |  |  |

|       |                    | 0    | 1                                                                                                            | 0        | 0          | 150                                                                                            |  |  |  |

|       |                    | 0    | 1                                                                                                            | 0        | 1          | 300                                                                                            |  |  |  |

|       |                    | 0    | 1                                                                                                            | 1        | 0          | 600                                                                                            |  |  |  |

|       |                    | 0    | 1                                                                                                            | 1        | 1          | 1200                                                                                           |  |  |  |

|       |                    | 1    | 0                                                                                                            | 0        | 0          | 1800                                                                                           |  |  |  |

|       |                    | 1    | 0                                                                                                            | 0        | 1          | 2000                                                                                           |  |  |  |

|       |                    | 1    | 0                                                                                                            | 1        | 0          | 2400                                                                                           |  |  |  |

|       |                    | 1    | 0                                                                                                            | 1        | 1          | 3600                                                                                           |  |  |  |

|       |                    | 1    | 1                                                                                                            | 0        | 0          | 4800                                                                                           |  |  |  |

|       |                    | 1    | 1                                                                                                            | 0        | 1          | 7200                                                                                           |  |  |  |

|       |                    | 1    | 1                                                                                                            | 1        | 0          | 9600                                                                                           |  |  |  |

|       |                    | 1    | 1                                                                                                            | 1        | 1          | Invalid                                                                                        |  |  |  |

| 12    | Receiver<br>Enable | semt | ole char                                                                                                     | acters f | from the s | the UART receiver logic can as-<br>serial input line. This bit will be<br>device Master Clear. |  |  |  |

| 13–15 | Not used           |      |                                                                                                              |          |            |                                                                                                |  |  |  |

## 3.2.5 Modem Status Register

The modem status register (MSR) is a 16-bit read only register. A read to this register results in the status of the readable modem control leads, Ring and Carrier. The ON condition of a modem control lead is interpreted as a logical one. Bits 04–07 and 12–15 are unused and read as a zero. Remaining bit designations are as follows:

.

| Bit   | Name                  |

|-------|-----------------------|

| 00    | Ring Line 00          |

| 01    | Ring Line 01          |

| 02    | Ring Line 02          |

| 03    | Ring Line 03          |

| 04–07 | Unused; read as zero. |

| 08    | Carrier Line 00       |

| 09    | Carrier Line 01       |

| 10    | Carrier Line 02       |

| 11    | Carrier Line 03       |

| 12–15 | Unused; read as zero. |

## 3.2.6 Transmit Data Register

The transmit data register (TDR) is a byte and word addressable, write only register. Characters for transmission are loaded into the low byte. TDR bit 00 is the least significant bit. Loading of a character should occur only when Transmitter Ready (CSR 15) is set. That character which is loaded into this register is directed to the line defined in CSR bits 08 and 09. The high byte of the TDR is designated as the break control register.

Each of the four multiplexer lines has a corresponding break bit for that line. TDR bit 08 represents the break bit for line 00, TDR bit 09 for line 01, etc. TDR bits 12–15 are unused. Setting a break bit will force that line's output to space. This condition will remain until cleared by the program. This register is cleared by BINIT or device Master Clear. The break control register can be utilized regardless of the state of the device Maintenance bit (CSR 03).

## CHAPTER 4 PROGRAMMING

#### 4.1 SCOPE

This chapter contains information for programming the DZV11 in the most efficient manner. To do so, the programming controls must be fully understood. The following paragraphs discuss the DZV11 from the programming point of view and describe recommended programming methods.

#### 4.2 DEVICE ADDRESS ASSIGNMENTS

The device address assigned to the DZV11 resides in the floating address space of the LSI-11. This address space ranges from  $160010_8$  to  $163776_8$ . Each DZV11 requires increments of  $10_8$  address locations and the first option should be configured with an address of  $160010_8$ . The initial configured address assumes that the system consists of only DZV11s in the floating address field. If the DUV11 option is also configured in the floating address field, assign the DZV11 an address which establishes a gap of  $10_8$  address locations between the last DUV11 and the first DZV11. For example: If the system consisted of one DUV11 located at  $160010_8$ , the DZV11 should be configured with an address of  $160030_8$ .

### 4.3 INTERRUPT VECTOR ADDRESS ASSIGNMENTS

The DZV11 device vector address is selected from the floating vector space. This space ranges from address  $300_8$  to address  $776_8$ . Each DZV11 requires increments of  $10_8$  address locations for its two contiguous interrupt vectors. If the DZV11 is the only option in the floating vector area, configure it for a vector of  $300_8$ . If there are options other than the DZV11 residing in the floating vector area, other configuration rules must be applied. When configuring the device vector, only the first vector address must be considered. The first vector, or base vector, must start on a zero boundary.

A zero boundary is one which has the three least significant bits equal to zero. The second vector is controlled by the first vector and data bit 02. Data bit 02 is generated by the M7957 hardware.

Any option ahead of DZV11 in the floating vector space which is not in the configuration should not occupy any vector space gap. For example, if only one DZV11 is in the system the vector for the DZV11 should be 300. The simplest case is as follows:

| Option | Address | Vector | Comment                  |

|--------|---------|--------|--------------------------|

| GAP    | 160010  | -      | No QBUS compatible DJ11  |

| GAP    | 160020  | _      | No QBUS compatible DH11  |

| GAP    | 160030  | -      | No QBUS compatible DQ11  |

| GAP    | 160040  | -      | No DUV11                 |

| GAP    | 160050  | -      | No QBUS compatible DUP11 |

| GAP    | 160060  | -      | No QBUS compatible LK11  |

| GAP    | 160070  | _      | No QBUS compatible DMC11 |

| DZV11  | 160100  | 300    |                          |

| GAP    | 160110  | -      | No more DZV11s           |

Each DZV11 requires two interrupt vectors, one for the transmitter section and one for the receiver section. If simultaneous interrupt requests were generated from each section, the receiver section would have priority in placing its vector onto the LSI bus. A receiver interrupt to address XX0 will be generated from having either a Receiver Done (CSR 07) or Silo Alarm (CSR 13) occurrence. A transmitter interrupt to address XX4 will be generated by Transmitter Ready (CSR 15). Additional prerequisites for generating interrupts are that the individual interrupt enable bits (CSR 06 and CSR 14) be set. The recommended method of clearing interrupt enable bits is to first raise the processor status word to level four, next clear these interrupt enable bits and then lower the processor status word to zero. Using this method prevents false interrupts from being generated.

#### 4.4 **PROGRAMMING FEATURES**

The DZV11 has several programming features that allow control of baud rate, character length, stop bits, parity, and interrupts. This section discusses the application of these controls to achieve the desired operating parameters.

#### 4.4.1 Baud Rate

Selection of the desired transmission and reception speed is controlled by the conditions of bits 08–11 of the LPR. Table 4-1 depicts the required bit configuration for each operating speed. The baud rate for each line is the same for both the transmitter and receiver. The receiver clock is turned on and off by setting and clearing bit 12 in the LPR for the selected line.

|    | Bi |    |    |           |

|----|----|----|----|-----------|

| 11 | 10 | 09 | 08 | Baud Rate |

| 0  | 0  | 0  | 0  | 50        |

| 0  | 0  | 0  | 1  | 75        |

| 0  | 0  | 1  | 0  | 110       |

| 0  | 0  | 1  | 1  | 134.5     |

| 0  | 1  | 0  | 0  | 150       |

| 0  | 1  | 0  | 1  | 300       |

| 0  | 1  | 1  | 0  | 600       |

| 0  | 1  | 1  | 1  | 1200      |

| 1  | 0  | 0  | 0  | 1800      |

| 1  | 0  | 0  | 1  | 2000      |

| 1  | 0  | 1  | 0  | 2400      |

| 1  | 0  | 1  | 1  | 3600      |

| 1  | 1  | 0  | 0  | 4800      |

| 1  | 1  | 0  | 1  | 7200      |

| 1  | 1  | 1  | 0  | 9600      |

| 1  | 1  | 1  | 1  | Not used  |

**Table 4-1 Baud Rate Selection Chart**

#### 4.4.2 Character Length

The selection of one of the four available character lengths is controlled by bits 03 and 04 of the LPR. The bit conditions for bits 04 and 03, respectively, are as follows: 00 (5-level), 01 (6-level), 10 (7-level), and 11 (8-level). For character lengths of 5, 6, and 7, the high-order bits of the received character are forced to zero.

### 4.4.3 Stop Bits

The length of the stop bits in a serial character string is determined by bit 05 of the LPR. If bit 05 is a zero, the stop length is one unit; bit 05 set to a one selects a 2-unit stop unless the 5-level character length (bits 03 and 04 at zero) is selected, in which case the stop bit length is 1.5 units.

## 4.4.4 Parity

The parity option is selected by bit 06 of the LPR. Parity is enabled on transmission and reception by setting bit 06 to a one. Bit 07 of the LPR allows selection of even or odd parity, and bit 06 must be set for bit 07 to be significant. The parity bit is generated and checked by hardware and does not appear in the RBUF or TBUF. The parity error (bit 12, RBUF) flag is set when the received character has a parity error.

### 4.4.5 Interrupts

The receiver interrupt enable (RIE) and silo alarm enable (SAE) bits in the CSR control the circumstances upon which the DZV11 receiver interrupts the LSI-11 processor.

If RIE and SAE are both clear, the DZV11 never interrupts the LSI-11 processor. In this case, the program must periodically check for the availability of data in the silo and empty the silo when data is present. If the program operates off a clock, it should check for characters in the silo at least as often as the time it takes for the silo to fill, allowing a safety factor to cover processor response delays and time to empty the silo. The RDONE bit in the CSR will set when a character is available in the silo. The program can periodically check this bit with a TSTB or BIT instruction. When RDONE is set, the program should empty the silo.