DLV11-E and DLV11-F asynchronous line interface user's manual

### Copyright © 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## **CONTENTS**

|           |                              | Page   |

|-----------|------------------------------|--------|

| CHAPTER 1 | INTRODUCTION                 |        |

| 1.1       | PURPOSE AND SCOPE            | . 1-1  |

| 1.2       | OPERATING FEATURES           |        |

| 1.3       | MODULE SPECIFICATIONS        |        |

| 1.4       | MAINTENANCE                  |        |

| 1.1       | Manufact                     | . 1-5  |

| CHAPTER 2 | GENERAL DESCRIPTION          |        |

| 2.1       | GENERAL                      | . 2-1  |

| 2.2       | MODULE FUNCTIONS             | . 2-1  |

| 2.3       | CIRCUIT FUNCTIONS            |        |

| 2.3.1     | General                      | . 2-3  |

| 2.3.2     | Bus Interface                | . 2-3  |

| 2.3.3     | I/O Control Logic            | . 2-4  |

| 2.3.4     | Control/Status Registers     | . 2-4  |

| 2.3.5     | Data Buffers                 | . 2-7  |

| 2.3.6     | Receiver Active Circuit      | . 2-7  |

| 2.3.7     | Interrupt Logic              | . 2-7  |

| 2.3.8     | Baud Rate Control            |        |

| 2.3.9     | Break Logic                  |        |

| 2.3.10    | Maintenance Mode Logic       |        |

| 2.3.11    | DLV11-E Peripheral Interface |        |

| 2.3.12    | DLV11-F Peripheral Interface |        |

| 2.3.13    | DC-to-DC Power Inverter      |        |

|           |                              |        |

| CHAPTER 3 | INSTALLATION                 |        |

| 3.1       | GENERAL                      | . 3-1  |

| 3.2       | CONFIGURATION                | . 3-1  |

| 3.3       | MODULE INSTALLATION          | . 3-1  |

| 3.4       | MODULE CHECKOUT              | . 3-11 |

| 3.4.1     | DLV11-E Checkout             | . 3-15 |

| 3.4.2     | DLV11-F Checkout             | . 3-15 |

| CHAPTER 4 | PROGRAMMING                  |        |

| 4.1       | INTRODUCTION                 | . 4-1  |

| 4.2       | DEVICE REGISTERS             |        |

| 4.3       | INTERRUPTS                   |        |

| 4.4       | TIMING CONSIDERATIONS        |        |

| 4.4.1     | Receiver                     |        |

| 4.4.2     | Transmitter                  |        |

| 4.4.3     | BREAK Generation Logic       |        |

| 4.4.4     | System Reset Timing          |        |

| 4.5       | PROGRAMMING EXAMPLES         |        |

| 4.6       | PROGRAMMING NOTES            |        |

# CONTENTS (CONT)

|            | Pag                                             | зe |

|------------|-------------------------------------------------|----|

| CHAPTER 5  | DETAILED TECHNICAL DESCRIPTION                  |    |

| 5.1        | GENERAL                                         | -1 |

| 5.2        | BUS INTERFACE                                   | -1 |

| 5.2.1      | Address Decoding                                |    |

| 5.2.2      | Vector Addressing                               |    |

| 5.3        | I/O CONTROL LOGIC                               | -2 |

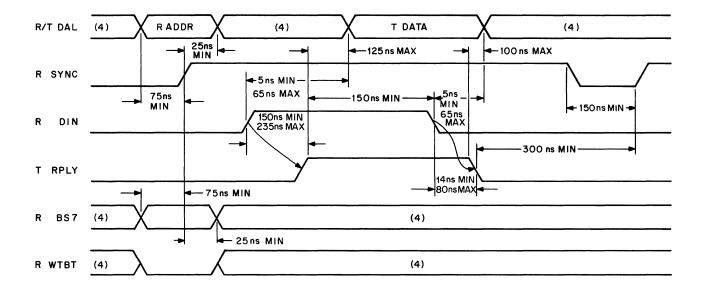

| 5.3.1      | Input Operation                                 | -3 |

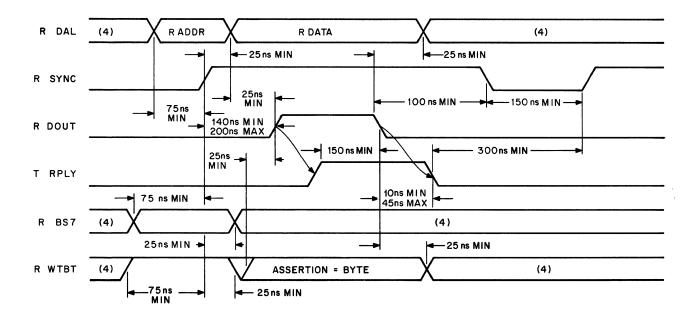

| 5.3.2      | Output Operation                                | -6 |

| 5.3.3      | Vector Operation                                | -7 |

| 5.4        | CONTROL/STATUS REGISTERS                        | -7 |

| 5.4.1      | CSR Data Flow                                   | -8 |

| 5.4.2      | Input Operation                                 | 1  |

| 5.4.3      | Output Operation                                |    |

| 5.5        | DATA BUFFERS                                    |    |

| 5.5.1      | Receiver Operation                              | 3  |

| 5.5.2      | Transmit Operation                              |    |

| 5.6        | RECEIVER ACTIVE CIRCUIT                         |    |

| 5.7        | INTERRUPT LOGIC                                 |    |

| 5.7.1      | DLV11-E Receiver Interrupts                     |    |

| 5.7.2      | DLV11-F Receiver Interrupts                     |    |

| 5.7.3      | Transmitter Interrupts                          |    |

| 5.7.4      | Interrupt Transactions                          |    |

| 5.8        | BAUD RATE CONTROL                               |    |

| 5.8.1      | Program Control                                 |    |

| 5.8.2      | Jumper Control                                  |    |

| 5.8.3      | External Control                                |    |

| 5.8.4      | Clock Selection                                 |    |

| 5.9        | BREAK LOGIC                                     |    |

| 5.9.1      | Receive Operation                               | 4  |

| 5.9.2      | Transmit Operation                              |    |

| 5.10       | MAINTENANCE MODE LOGIC                          | 25 |

| 5.11       | DLV11-E PERIPHERAL INTERFACE                    |    |

| 5.12       | DLV11-F PERIPHERAL INTERFACE                    | 8. |

| 5.12.1     | EIA Data Leads Only Operation                   | 8. |

| 5.12.2     | Current Loop Operation                          | 9  |

| 5.13       | DC-TO-DC POWER INVERTER                         | .9 |

| APPENDIX A | IC DESCRIPTIONS                                 |    |

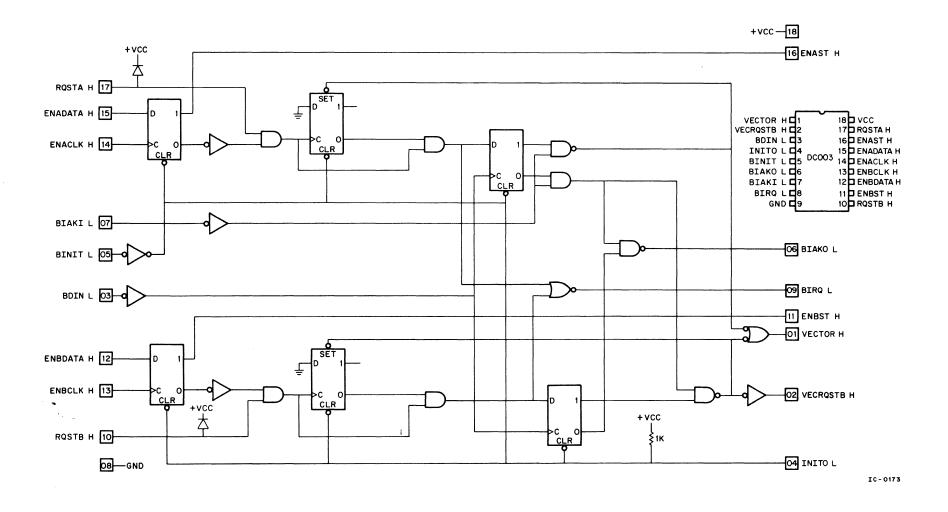

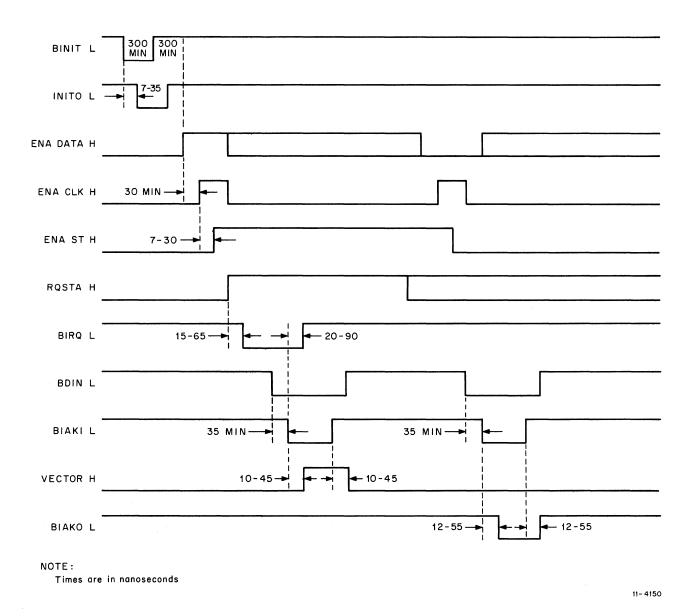

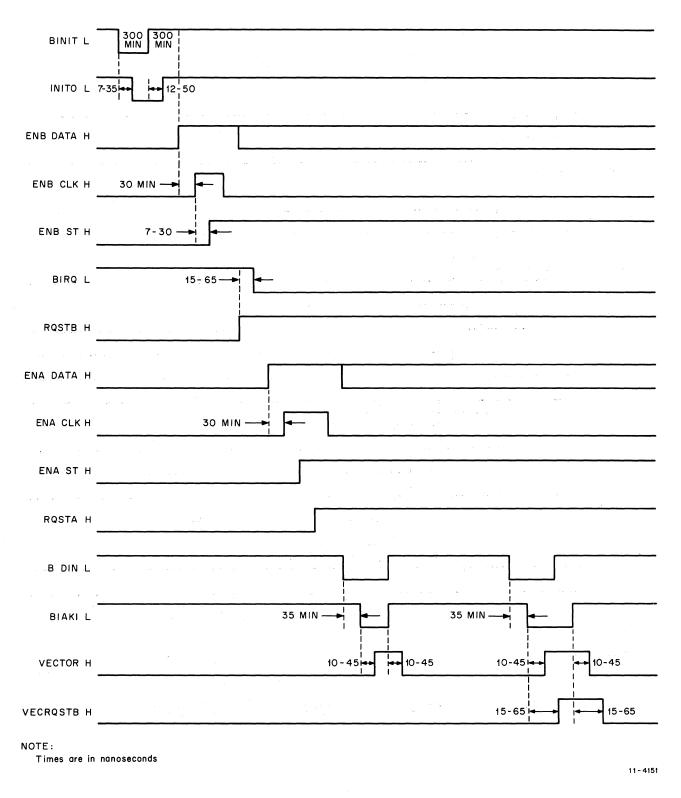

| A.1        | DC003 INTERRUPT LOGIC                           | -1 |

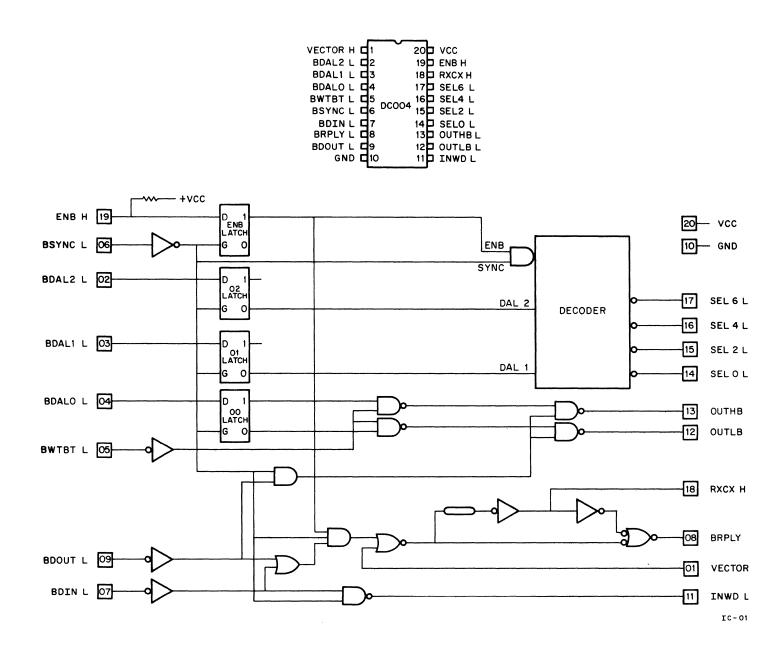

| A.2        | DC004 PROTOCOL LOGIC                            | -1 |

| A.3        | DC005 TRANSCEIVER LOGIC                         | -1 |

| A.4        | UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER A-1 |    |

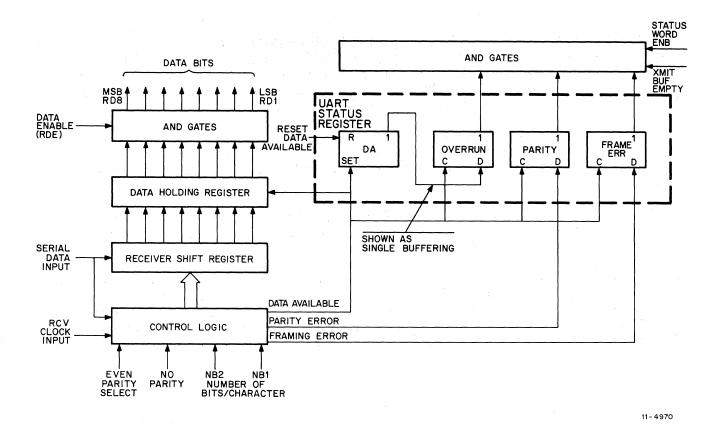

| A.4.1      | Receiver Operation                              |    |

# CONTENTS (CONT)

|                          |                                                         | Page        |

|--------------------------|---------------------------------------------------------|-------------|

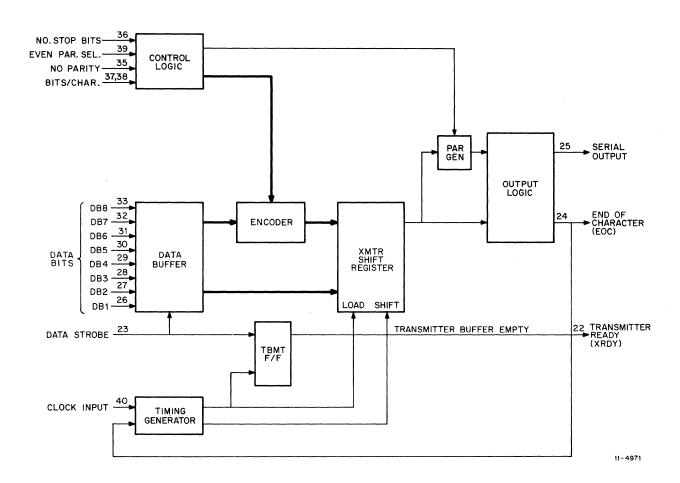

| A.4.2<br>A.5             | Transmitter Operation                                   |             |

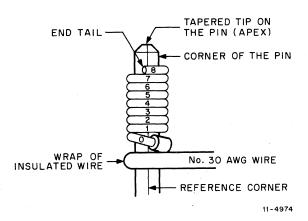

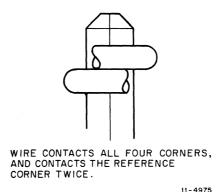

| APPENDIX B               | WIRE WRAP INSTRUCTIONS                                  |             |

| B.1<br>B.2<br>B.3<br>B.4 | PURPOSE DEFINITIONS CONNECTIONS PROCEDURE               | . B-1 . B-2 |

|                          | FIGURES                                                 |             |

| Figure No.               | Title                                                   | Page        |

| 2-1                      | Interfacing Examples                                    | . 2-2       |

| 2-2                      | DLV11-E and DLV11-F Data Flow, Simplified Block Diagram |             |

| 2-3                      | DLV11-E and DLV11-F Functional Block Diagram            |             |

| 3-1                      | DLV11-E Jumper Locations                                |             |

| 3-2                      | DLV11-F Jumper Locations                                |             |

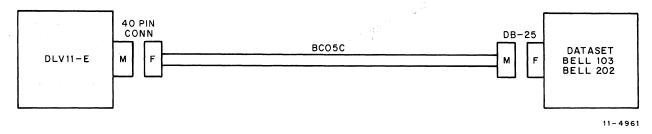

| 3-3                      | DLV11-E Cabling Example                                 |             |

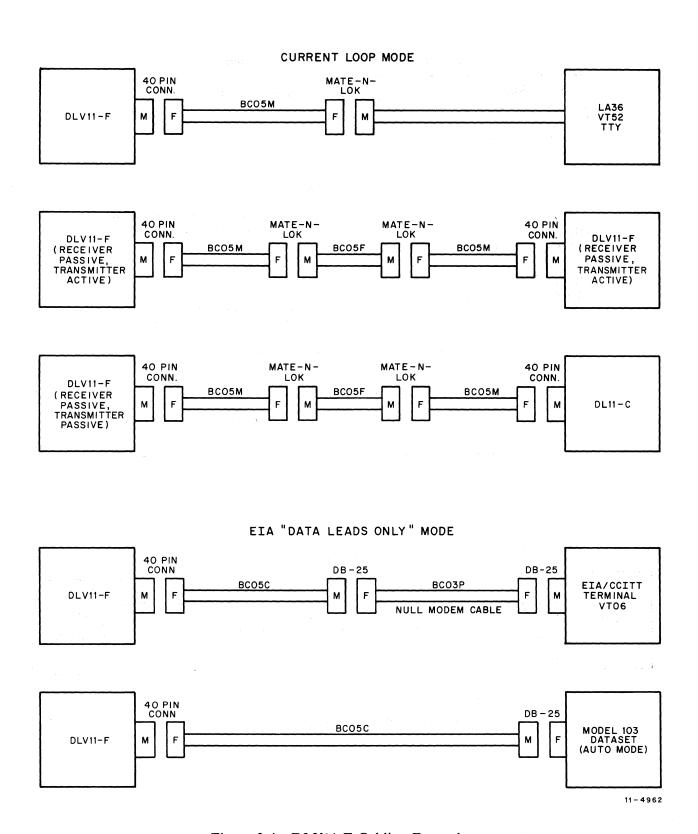

| 3-4                      | DLV11-F Cabling Examples                                |             |

| 3-5                      | Typical Backplane Configuration                         |             |

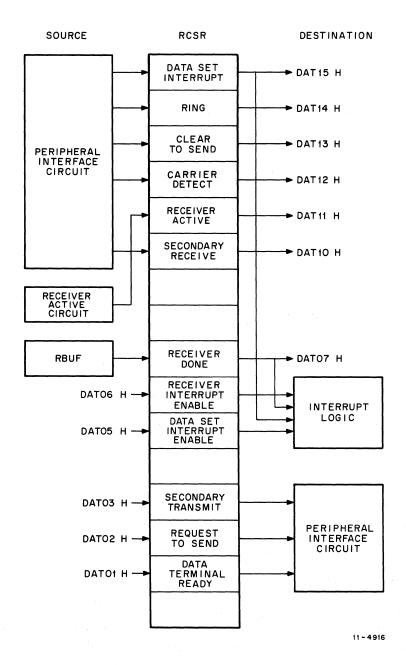

| 4-1                      | DLV11-E RCSR Bit Assignments                            |             |

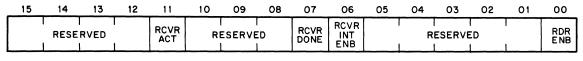

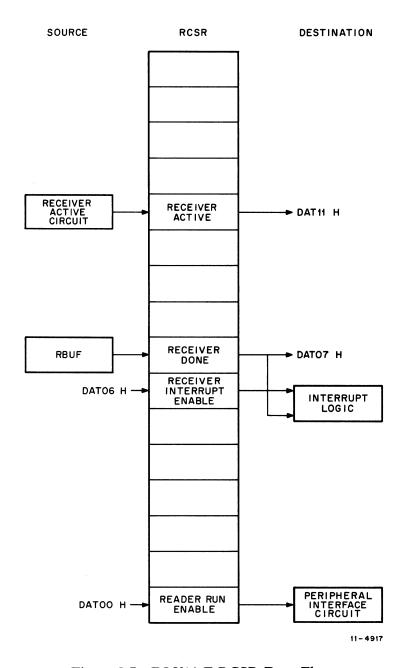

| 4-2                      | DLV11-F RCSR Bit Assignments                            |             |

| 4-3                      | DLV11-E and DLV11-F RBUF Bit Assignments                |             |

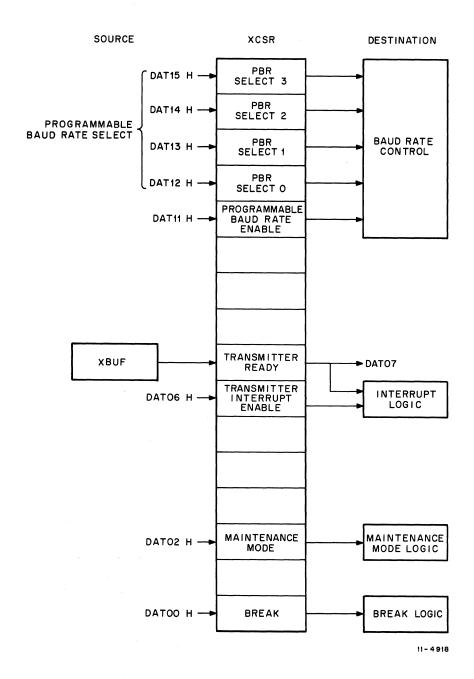

| 4-4                      | DLV11-E and DLV11-F XCSR Bit Assignments                |             |

| 4-5                      | DLV11-E and DLV11-F XBUF Bit Assignments                |             |

| 4-6                      | DLV11-F Programming Example                             |             |

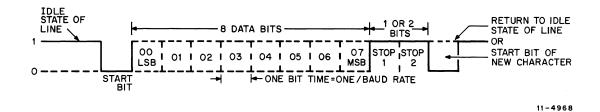

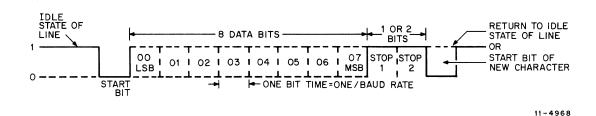

| 4-7                      | Serial Data Format                                      | . 4-18      |

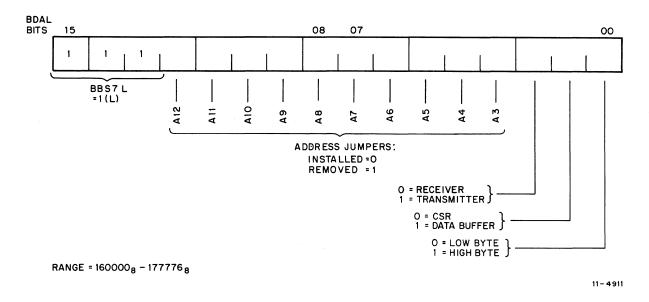

| 5-1                      | DLV11-E and DLV11-F Addresses                           | . 5-2       |

| 5-2                      | DLV11-E and DLV11-F Interrupt Vectors                   | . 5-2       |

| 5-3                      | I/O Control Logic, Block Diagram                        |             |

| 5-4                      | Data Input Timing                                       |             |

| 5-5                      | Data Output Timing                                      |             |

| 5-6                      | DLV11-E RCSR Data Flow                                  | . 5-8       |

| 5-7                      | DLV11-F RCSR Data Flow                                  | . 5-9       |

| 5-8                      | DLV11-E and DLV11-F XCSR Data Flow                      | . 5-10      |

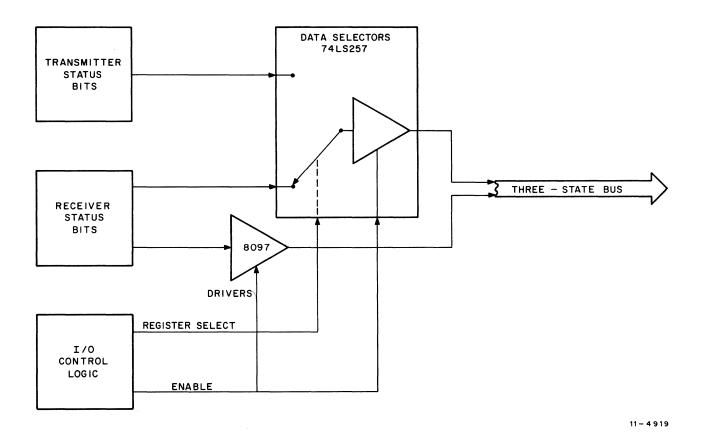

| 5-9                      | Control/Status Registers During DATI                    |             |

| 5-10                     | Control/Status Registers During DATO or DATOB           |             |

| 5-11                     | UART Signal Flow                                        |             |

| 5-12                     | DLV11-E and DLV11-F RBUF Data Flow                      |             |

| 5-13                     | DLV11-E and DLV11-F XBUF Data Flow                      |             |

# FIGURES (CONT)

Title

Page

Figure No.

| 5-14        | Receiver Active Circuit                            |

|-------------|----------------------------------------------------|

| 5-15        | Interrupt Vector Signal Flow                       |

| 5-16        | Interrupt Timing                                   |

| 5-17        | Baud Rate Control Signal Flow                      |

| 5-18        | Break Logic Receive Signal Flow                    |

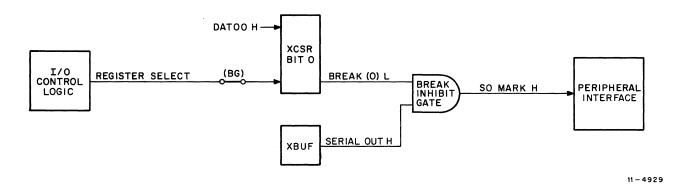

| 5-19        | Break Logic Transmit Signal Flow                   |

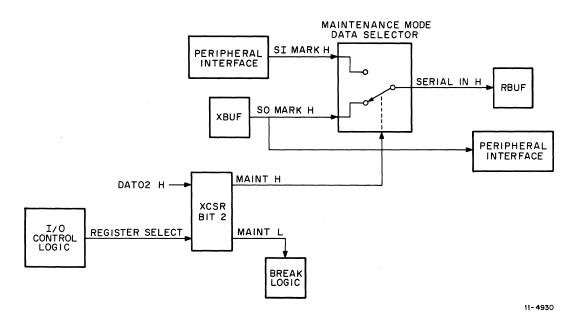

| 5-20        | Maintenance Mode Logic                             |

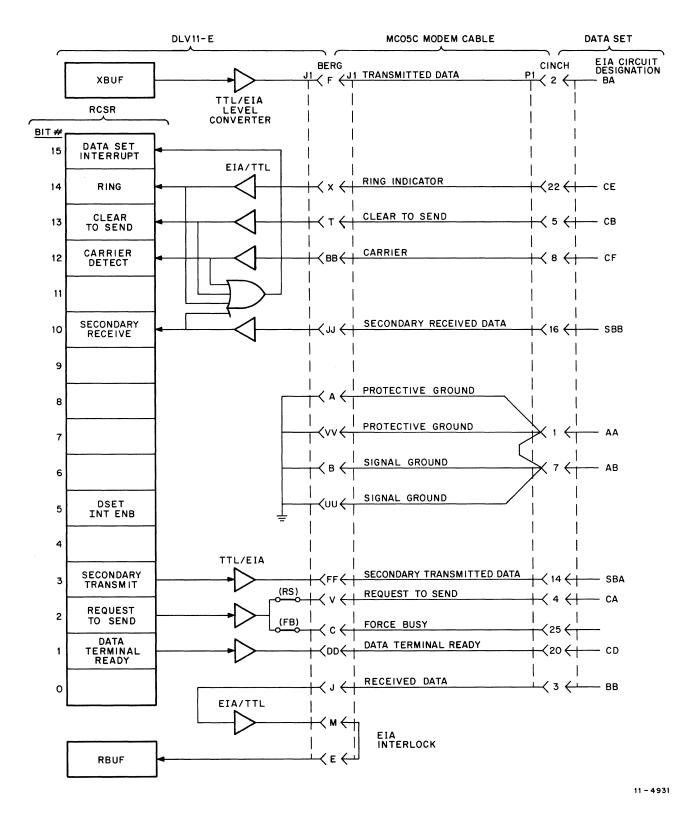

| 5-21        | DLV11-E Peripheral Interface Signal Flow           |

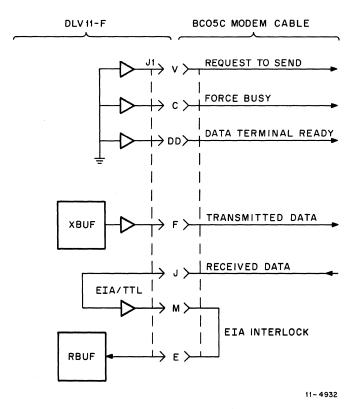

| 5-22        | Data Lead Only Interface                           |

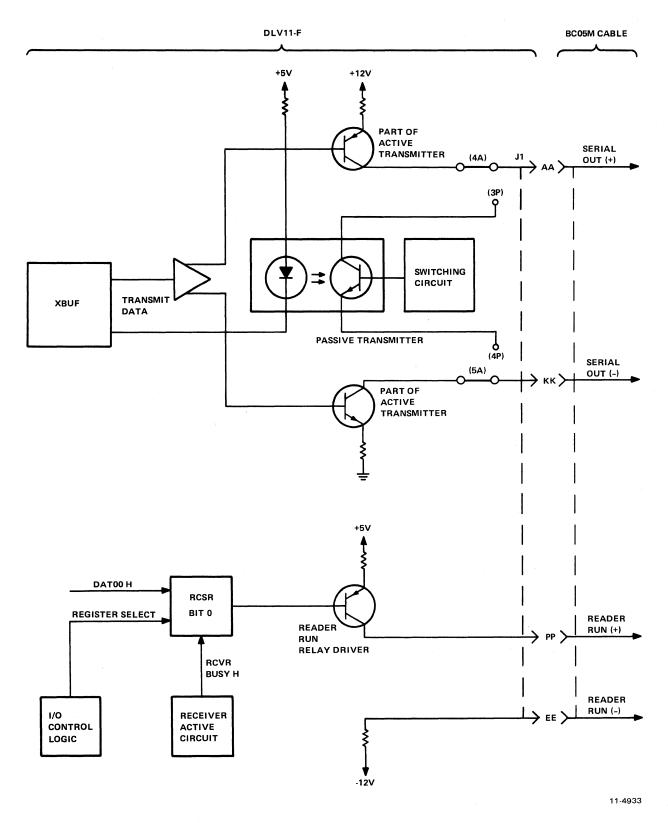

| 5-23        | 20 mA Transmitter and Reader Run Circuit           |

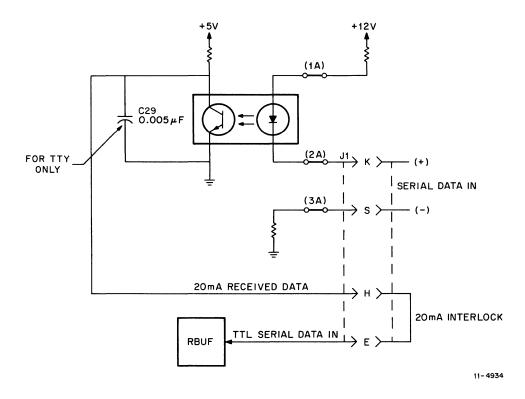

| 5-24        | Active Receive 20 mA Current Loop                  |

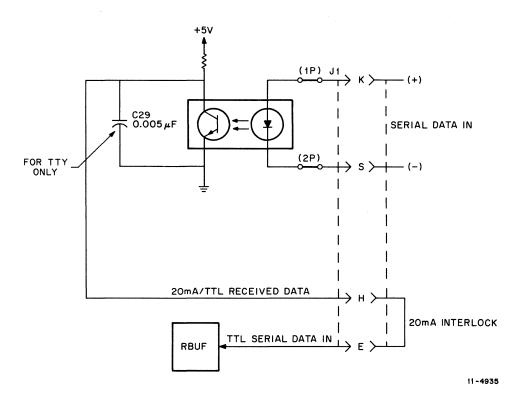

| 5-25        | Passive Receive 20 mA Current Loop                 |

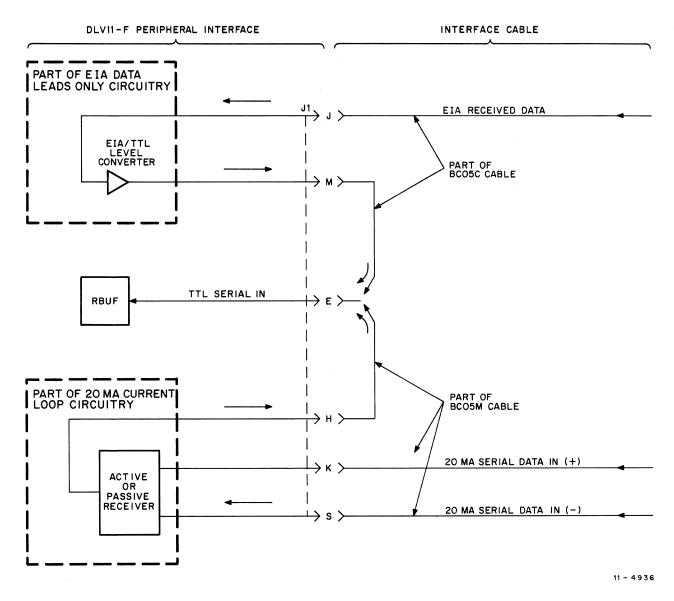

| 5-26        | Interlock Jumper Data Flow                         |

| A-1         | DC003 Simplified Logic Diagram                     |

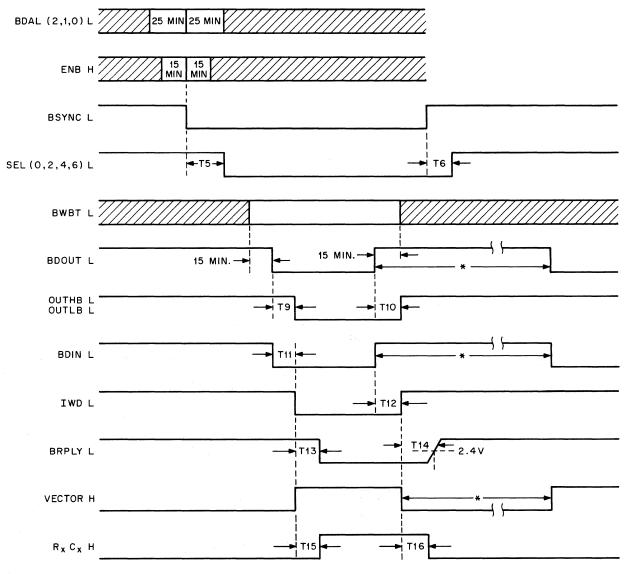

| A-2         | DC003 "A" Interrupt Section Timing Diagram         |

| A-3         | DC003 "A" and "B" Interrupt Section Timing Diagram |

| A-4         | DC004 Simplified Logic Diagram                     |

| A-5         | DC004 Timing Diagram                               |

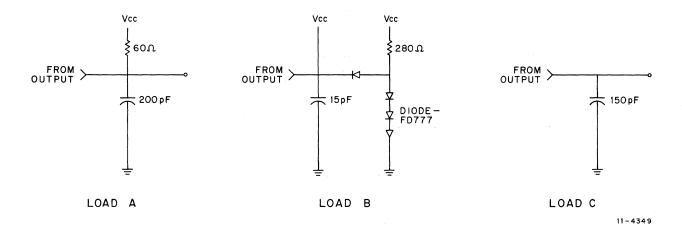

| A-6         | DC004 Loading Configuration for Table A-2          |

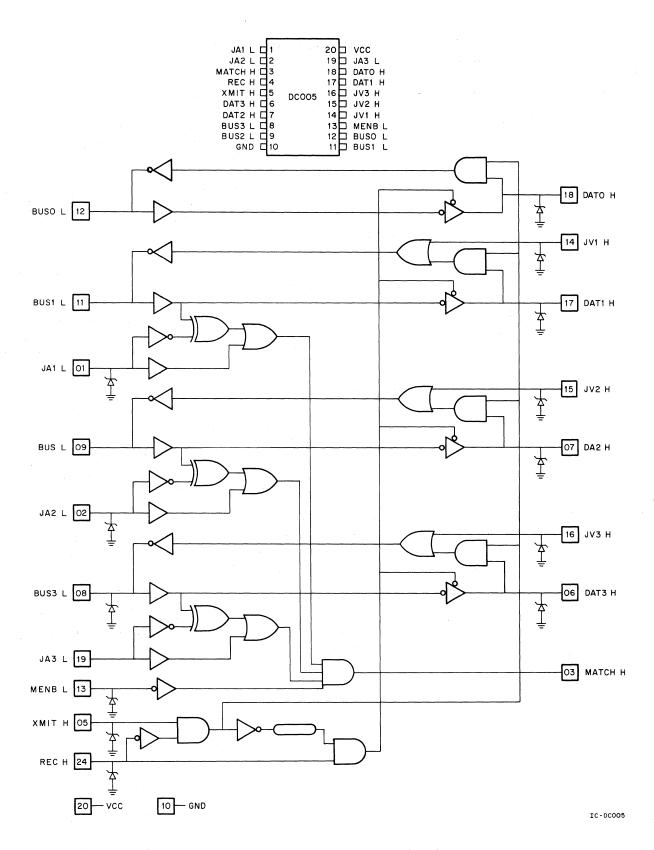

| A-7         | DC005 Simplified Logic Diagram                     |

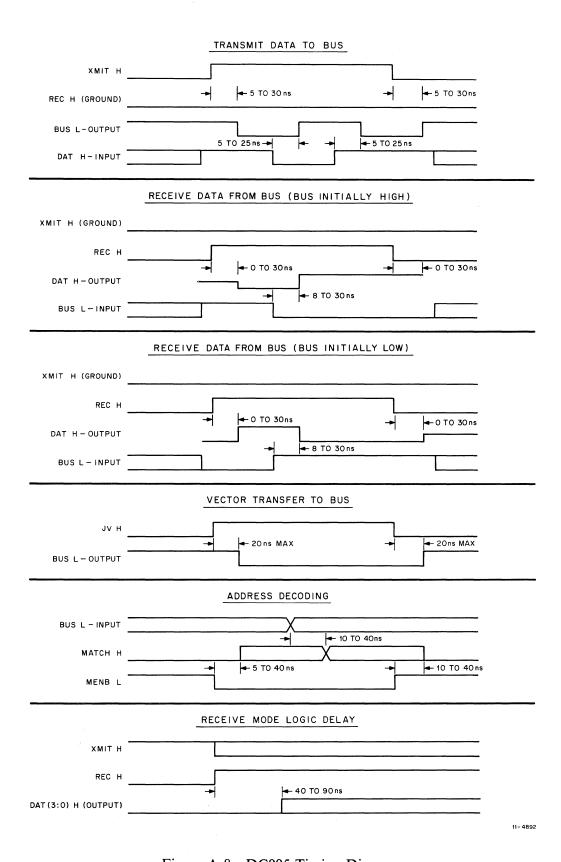

| <b>A-</b> 8 | DC005 Timing Diagram                               |

| <b>A-9</b>  | UART Data Format                                   |

| A-10        | UART Receiver – Block Diagram                      |

| A-11        | UART Transmitter – Block Diagram                   |

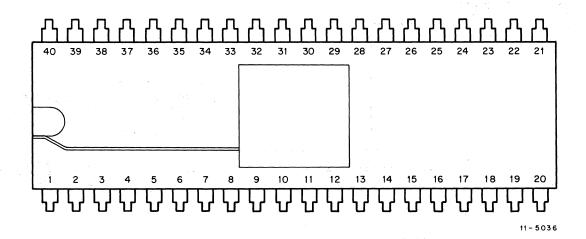

| A-12        | UART Pin Locations                                 |

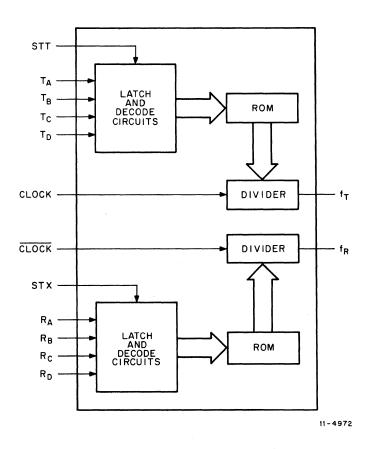

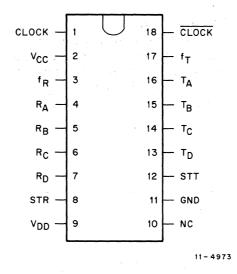

| A-13        | 5016 Block Diagram                                 |

| A-14        | 5016 Pin Locations                                 |

| B-1         | Solderless Wrapped Connection on Wire Wrap Pin     |

| B-2         | Full Turn                                          |

| B-3         | Half Turn                                          |

| B-4         | Two Levels of Wire Wrap                            |

| B-5         | Defective Wire Wraps                               |

| B-6         | Loading the Wire Wrapping Kit                      |

|             |                                                    |

|             | TABLES                                             |

| Table No.   | Title Page                                         |

| 1-1         | Feature Comparison                                 |

| 3-1         | Jumper Definitions                                 |

| 3-2         | Baud Rate Selections                               |

|             |                                                    |

# TABLES (CONT)

| Table No.   | Title                                      | Page   |

|-------------|--------------------------------------------|--------|

| 3-3         | Data Bit Selections                        | . 3-6  |

| 3-4         | Jumper Configuration When Shipped          | . 3-7  |

| 3-5         | Module Application Examples                | . 3-9  |

| 3-6         | DLV11-E 40-Pin Header Connector Pinning    | . 3-12 |

| 3-7         | DLV11-F 40-Pin Header Connector Pinning    | . 3-13 |

| 3-8         | DLV11-E and DLV11-F Edge Connector Pinning | . 3-14 |

| 4-1         | Register Addresses for Console Interfacing |        |

| 4-2         | DLV11-E RCSR Bit Assignments               | . 4-2  |

| 4-3         | DLV11-F RCSR Bit Assignments               |        |

| 4-4         | DLV11-E and DLV11-F RBUF Bit Assignments   | . 4-6  |

| 4-5         | DLV11-E and DLV11-F XCSR Bit Assignments   | . 4-7  |

| 4-6         | DLV11-E and DLV11-F XBUF Bit Assignments   | . 4-8  |

| 4-7         | DLV11-E Programming Example                | . 4-11 |

| 5-1         | Register Selection                         | . 5-3  |

| 5-2         | Byte Selection (Output Operations Only)    | . 5-7  |

| 5-3         | UART Clock Sources                         |        |

| <b>A-1</b>  | DC003 Pin/Signal Descriptions              | . A-7  |

| A-2         | DC004 Signal Timing vs Output Loading      | A-11   |

| A-3         | DC004 Pin/Signal Descriptions              |        |

| A-4         | DC005 Pin/Signal Descriptions              | A-18   |

| A-5         | UART Pin Functions                         | A-23   |

| A-6         | 5016 Selectable Frequencies                | A-30   |

| <b>A-</b> 7 | 5016 Pin Functions                         | A-31   |

## CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE AND SCOPE

The DLV11-E and DLV11-F are asynchronous line interface modules that interface the LSI-11 bus to any of several standard types of serial communications lines. The modules receive serial data from peripheral devices, assemble it into parallel data, and transfer it to the LSI-11 bus. They accept data from the LSI-11 bus, convert it into serial data, and transmit it to the peripheral devices. The two modules differ in that the DLV11-E offers full modem control, whereas the DLV11-F supports either 20 mA current loop or EIA-standard lines, but does not include modem control.

This manual describes these modules to the user. It treats the two modules together for those functions common to both, and separately for those areas in which they differ. It is assumed that the reader has a general familiarity with the operation of the LSI-11 computer and with the requirements of the peripheral equipment. Refer to *Microcomputer Handbook*, EB 06583 76, for detailed information about the LSI-11.

#### 1.2 OPERATING FEATURES

Each asynchronous line interface is constructed on a single 21.6 cm  $\times$  122.7 cm (8.5 in  $\times$  5.0 in) dual-height module. The module mounts in any slot in the LSI-11's backplane. Both the DLV11-E and the DLV11-F have the following features:

- Jumper- or program-selectable crystal-controlled baud rates: 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 3600, 4800, 7200, and 9600.

- Provisions for user-supplied external clock inputs for baud rate control.

- Jumper-selectable parity and data bit formats.

- LSI-11 bus interface and control logic for interrupt processing and vectored addressing of interrupt service routines.

- Control, status, and data buffer registers directly accessible via processor instructions.

- Program and peripheral connector plug compatible with the PDP-11 DL11 series of asynchronous line interface modules.

The DLV11-E is designed to interface data sets (modems with control capability) such as Bell models 103, 202C, and 202D.

The DLV11-F is designed for either 20 mA current loop equipment or EIA-standard "data leads only" (no modem control) operation. Flexibility is achieved by the use of wire wrap jumpers. Table 1-1 compares the features of the DLV11-E and DLV11-F with those of the DLV11 and the DL11 series. Refer to Paragraph 4.4, Timing Considerations, for further information.

Table 1-1 Feature Comparison

(NOTE: X indicates feature available.)

| Features                                               | DL11-A<br>through D | DL11-E | DLV11 | DLV11-F | DLV11-E |

|--------------------------------------------------------|---------------------|--------|-------|---------|---------|

| Programmable Baud Rates (Write Only Bits)              |                     |        |       | x       | X       |

| Modem Control                                          |                     | x      |       |         | X       |

| EIA "Data Leads Only"                                  | X                   |        | X     | X       | X       |

| 20 mA Current Loop                                     | X                   |        | X     | X       | ·       |

| Jumper Selectable Active or Passive 20 mA Current Loop |                     |        | X     | X       |         |

| Error Flags                                            | x                   | x      |       | X       | X       |

| BREAK Generation Bit                                   | x                   | x      | x     | X       | X       |

| Receiver Active Bit                                    | X                   | x      |       | X       | X       |

| Maintenance Bit                                        | X                   | x      |       | X       | X       |

| On-board Clocks for Split Speed Operation              | x                   | x      |       | X       | X       |

| Halt on Framing Error                                  |                     |        | X     | X       | X       |

| Boot on Framing Error                                  |                     |        |       | X       | X       |

| UART Cleared by INIT                                   | X                   | X      |       | X       | X       |

| UART Cleared by DCOK                                   |                     |        | x     | i       | n       |

| No Trap on Write to RBUF                               | X                   | x      |       | X       | X       |

| 1.5 STOP BITS                                          | X                   | x      |       |         |         |

| Modem Status Bit                                       |                     |        | x     |         |         |

#### 1.3 MODULE SPECIFICATIONS

The following specifications and particulars are for informational purposes only and are subject to change without notice.

#### **Physical Characteristics**

Dimensions

Circuit Card Plus Handles

Length:

21.6 cm (8.5 in)

22.8 cm (8.9 in)

Height:

12.7 cm (5.0 in)

13.2 cm (5.2 in)

Width:

1.3 cm (0.5 in)

1.3 cm (0.5 in)

Cable Connection One 40-pin header connector

Mounting Requirements Plugs directly into any dual-height slots on the

LSI-11 backplane or LSI-11 expansion box

backplane.

**Electrical Characteristics**

Module Type

DLV11-E: M8017 DLV11-F: M8028

Power Requirements

1.0 A (nominal) @ +5 V  $\pm 5\%$ , 5.0 W 150 mA (nominal) @ +12 V  $\pm 5$ , 1.8 W

LSI-11 Bus Loading

Presents one bus load.

**Environmental Characteristics**

Temperature

Operating 5° C to 50° C (41° F to 122° F)

Nonoperating -40° C to 66° C (-40° F to 151° F)

Humidity (Operating and Nonoperating)

10% to 95%, maximum wet bulb 32° C

(90° F) and minimum dew point 2° C (35° F)

Altitude

Operating 2.4 km (8,000 ft)

Nonoperating 9.1 km (30,000 ft)

#### 1.4 MAINTENANCE

This manual explains the normal operation of the asynchronous line interface modules. This information and the diagnostic maintenance programs will aid the user when analyzing trouble symptoms to determine necessary corrective action. A set of engineering drawings is available for each of the two modules. Refer to DLV11-E Asynchronous Line Interface, Circuit Schematics (DIGITAL part number D-CS-M8017-0-1) or DLV11-F Asynchronous Line Interface, Circuit Schematics (DIGITAL part number D-CS-M8028-0-1).

Signal names in the DLV11-E and DLV11-F print sets are in the following basic form:

**SOURCE**

#### SIGNAL NAME

**POLARITY**

SOURCE indicates the drawing number of the print set where the signal originates. The drawing number of a print (K-3, K-4, K-5, etc.) is located above the title block.

SIGNAL NAME is the proper name of the signal. The names used in the print set are also used in this manual.

POLARITY is either H or L to indicate the voltage level of the signal:  $H \approx +3 \text{ V}$ ; L  $\approx$  ground.

As an example, the signal:

(K-3) INIT H

originates on sheet K-3 of the drawings and means "when INIT is true, this signal is at approximately +3 V."

LSI-11 bus signal lines do not carry a SOURCE indicator. These names represent a bidirectional wire-ORed bus. As a result, multiple sources for a particular bus signal exist. The LSI-11 bus signal names begin with a "B" for "bussed."

The DLV11-E module is shipped with an H315 modem test connector included. This is plugged into the interface cable in place of a data set when running maintenance programs. The DLV11-F does not use this test connector.

A paper tape diagnostic maintenance program is shipped with the module for checkout and maintenance. The following programs are available:

DLV11-E: MAINDEC-11-DVDVA DLV11-F: MAINDEC-11-DVDVC

# CHAPTER 2 GENERAL DESCRIPTION

#### 2.1 GENERAL

The DLV11-E is designed to interface equipment that transmits and receives data over communications lines and conforms to EIA Standard RS232C and CCITT Recommendation V.24. The DLV11-E is used by the program to control a communications data set through the use of control signals and handshake sequences.

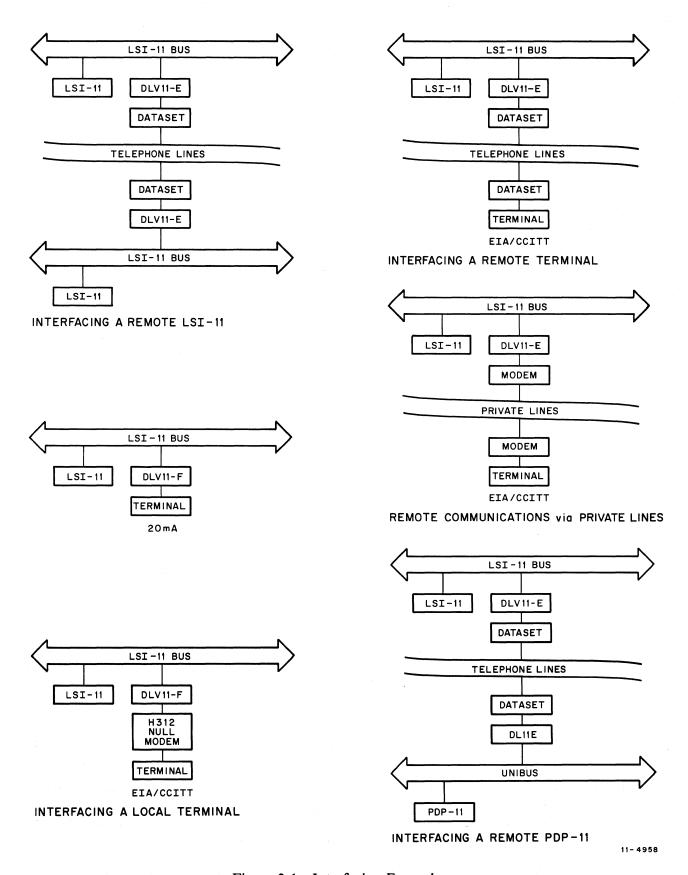

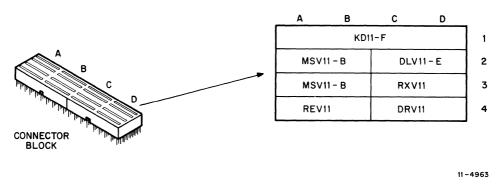

The DLV11-F supports either EIA-compatible data lines or 20 mA current loop data lines. When configured for EIA support, the DLV11-F transmits and receives bipolar levels over the data lines to the device. This operation does not include control lines. When configured for 20 mA current loop operation, the DLV11-F can support either active or passive current loop devices. Figure 2-1 illustrates several applications of the modules.

#### 2.2 MODULE FUNCTIONS

The DLV11-E and DLV11-F asynchronous line interface modules take data from the LSI-11 and convert it to the speed, character format, and signal levels required by the user's peripheral devices. Conversely, they assemble inputs from the peripheral devices into the format required for transfer to the computer. The computer program can address any of four registers in the interface modules to transfer data or status information. It can also enable the interface modules to generate interrupts. When a peripheral device requires service, the interface module will, if enabled, interrupt the program and vector to the necessary service routine.

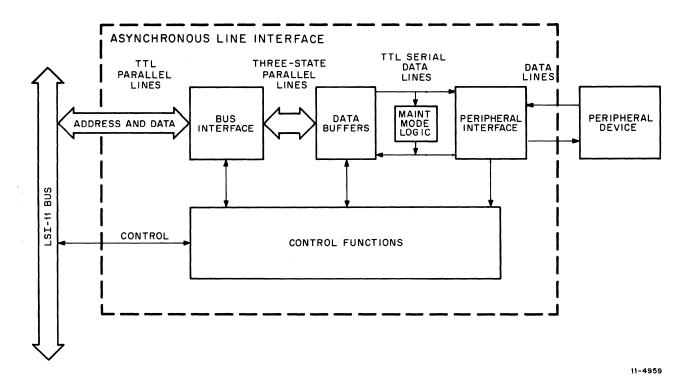

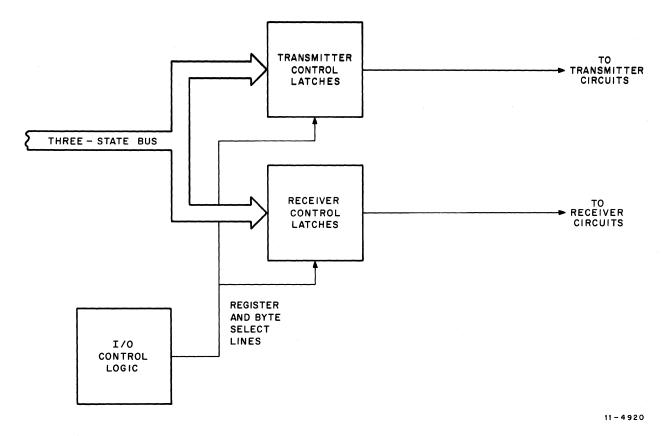

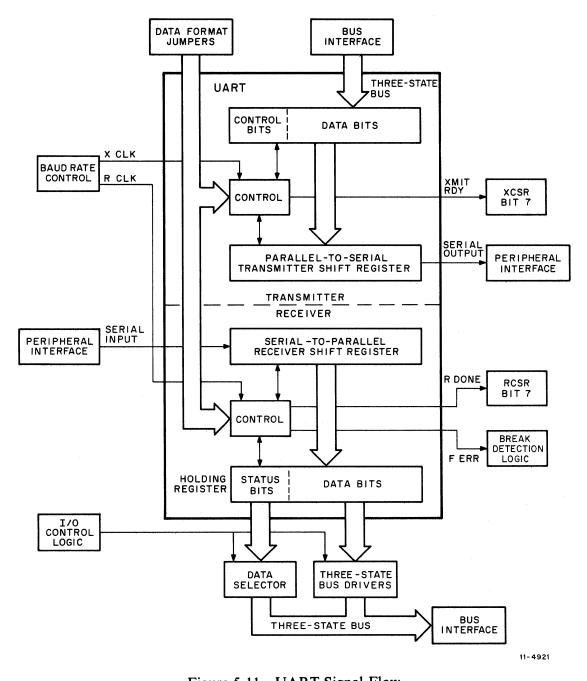

Data passes through three main circuits on its way to and from the peripheral device (Figure 2-2). During computer output operations, parallel data is taken off the LSI-11 bus by a bus interface circuit and placed on the module's internal three-state bus. The data on the three-state bus enters a data buffer, where it is serialized and formatted for the peripheral device. From there it goes to a peripheral interface circuit that changes it from TTL to either EIA-compatible bipolar levels (DLV11-E or DLV11-F) or 20 mA current loop signals (DLV11-F only). The data then leaves the module on an interface cable and goes to the user's peripheral device. Data coming into the computer from the peripheral device goes through this process in reverse order.

The control functions within the interface module are carried out by circuits that handle I/O transfers, interrupt requests, and control and status information. The DLV11-E interfaces control signals as well as data between the LSI-11 and the peripheral. The extent of this interaction is determined by the program and the type of peripheral being supported.

The DLV11-E and DLV11-F also have a self-test function. When the computer program places the module in the maintenance mode, parallel data travels through the bus interface and the data buffer, is serialized, and then loops back through the data buffer, is converted back to parallel, and travels through the bus interface to the computer to be checked for accuracy.

Figure 2-1 Interfacing Examples

Figure 2-2 DLV11-E and DLV11-F Data Flow, Simplified Block Diagram

#### 2.3 CIRCUIT FUNCTIONS

#### 2.3.1 General

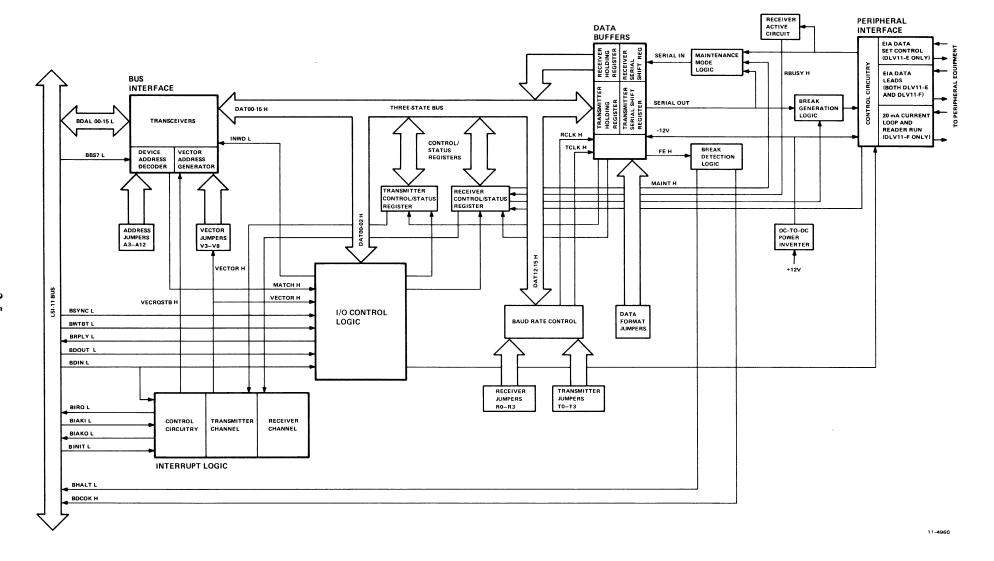

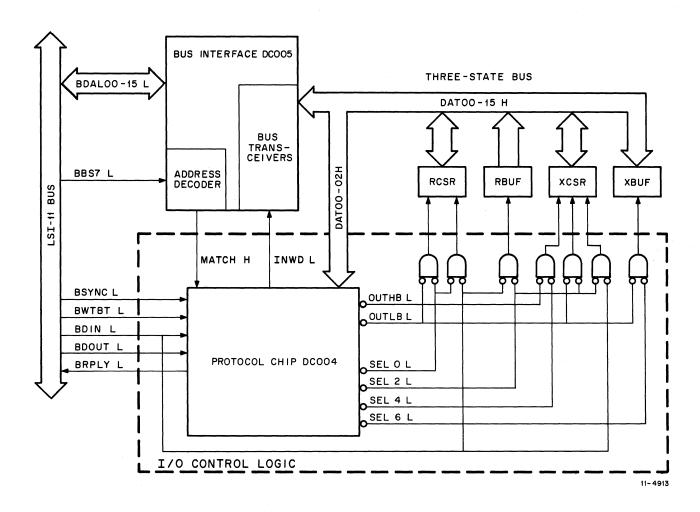

This section discusses the circuits on a functional level and is keyed to Figure 2-3. For a more detailed coverage of circuit operation, refer to Chapter 5.

#### 2.3.2 Bus Interface

The bus interface circuit performs three basic functions:

- 1. It converts signal levels of data moving between the LSI-11 bus and the interface module's internal three-state bus.

- 2. It decodes the device address and produces an address match (MATCH H) signal.

- 3. It generates interrupt vectors and places them on the LSI-11 bus.

The LSI-11 signals are standard TTL levels. The module's internal three-state bus, however, has three signal conditions. It has TTL high and low states, and also a disabled state. When a bus interface transceiver output is disabled, it goes to a high impedance condition that does not affect other devices connected to the same line. This permits the lines to be used in both directions by high speed, low power devices.

The bus interface is normally enabled to receive from the LSI-11 bus. It can be switched to transmit onto the LSI-11 bus by either the I/O control logic or the interrupt logic. The signals received from the LSI-11 bus are ignored unless the address decoding function is enabled.

The bus interface circuit monitors LSI-11 bus lines BDAL00 L through BDAL15 L. It inverts these signals and places them on three-state bus lines DAT00 H through DAT15 H. If the information on the BDAL lines is the address of a location in the upper 4K of addressing space, i.e., in the I/O page, the LSI-11 asserts BBS7 L. This signal enables the device address decoding function in the bus interface.

To decode the address, the circuit compares BDAL03 L through BDAL12 L with address jumpers A3 through A12. If the states of the BDAL lines match the corresponding jumpers the user has installed, the circuit sends MATCH H to the I/O control logic. MATCH H is a prerequisite for data transactions.

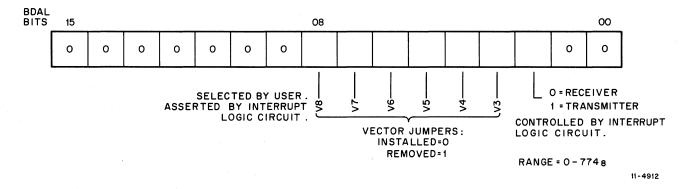

The bus interface logic generates vector addresses under the control of the interrupt logic and the vector address jumpers. The circuit creates two vectors; one for receiver interrupts and one for transmitter interrupts. The combination of VECTOR H and VECRQSTB H from the interrupt logic and the states of vector address jumpers V3 through V8 determines what vector will be placed on the LSI-11 bus lines.

#### 2.3.3 I/O Control Logic

The I/O control logic directs data transactions between the LSI-11 and the interface module. A data transaction can be a word or a byte, a high byte or a low byte, an input or an output, or status information or character information. The I/O control logic monitors the LSI-11 bus lines to recognize what type of transaction is to be accomplished. It uses this information to control four device registers. The registers are named after their functions as follows:

| Receiver Control/Status Register    | (RCSR) |

|-------------------------------------|--------|

| Transmitter Control/Status Register | (XCSR) |

| Receiver Buffer                     | (RBUF) |

| Transmitter Buffer                  | (XBUF) |

These four registers are described in subsequent paragraphs of this chapter.

An I/O operation begins with the LSI-11 addressing the interface module. The bus interface decodes the address, asserts MATCH H to the I/O control logic, and places the address on the three-state bus lines. The I/O control logic decodes the three least significant bits of the three-state bus lines (DAT00 H through DAT02 H) and the LSI-11 bus control signals. The circuit develops register selection and byte selection signals to enable the correct data paths between the computer and the appropriate device register. It also controls INWD L, which determines whether the bus interface transceivers are transmitting or receiving. When data becomes available, the I/O control logic gates it to its destination (from the LSI-11 bus to the three-state bus for an output transfer, or from the three-state bus to the LSI-11 bus for an input transfer).

#### 2.3.4 Control/Status Registers

The DLV11-E and DLV11-F each have two control/status registers: the RCSR and the XCSR. The computer writes control bits out of these registers and reads status bits in from them. The registers consist of a series of latches, data selectors, and gating circuitry. During data transactions involving control and status information, the I/O control logic enables the XCSR or RCSR to either latch in control bits or gate out status bits.

When status information is to be read into the computer, the LSI-11 addresses the device register containing the desired information. The bus interface and I/O control logic decode the address and enable the contents of the selected register to be placed on the bus and transferred into the computer. When control information is to be written out to the interface modules, the computer addresses the device register that is to be loaded. The bus interface and I/O control logic decode the address and enable the register to load the control information when it is placed on the bus.

Figure 2-3 DLV11-E and DLV11-F Functional Block Diagram

Not all control and status bits are both read and write; some are read-only bits and some are write-only bits. A detailed description of each bit is given with the programming information in Chapter 4.

#### 2.3.5 Data Buffers

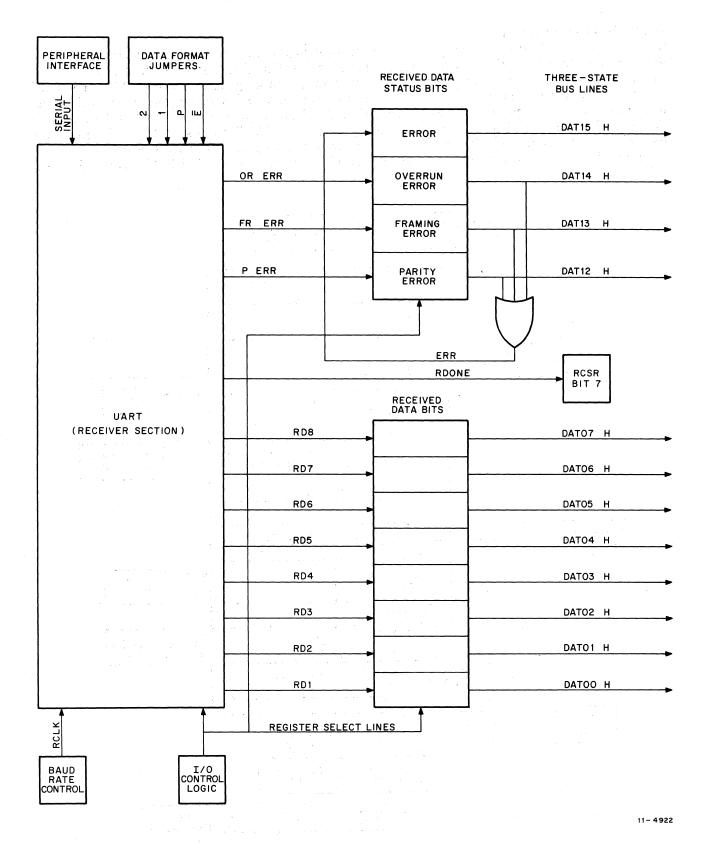

The DLV11-E and the DLV11-F each have two data buffers: one for receive data (RBUF) and one for transmit data (XBUF). Both data buffers handle data by bytes. The RBUF also holds error flag bits pertaining to the status of the received data.

The data received from the peripheral device is transferred serially from the peripheral interface circuit into a receive shift register in the data buffer. From there it is transferred in parallel to a holding register. At the appropriate time, the buffer control circuitry places the parallel data, along with error information, onto the module's internal three-state bus. The bus interface then transfers the data to the computer.

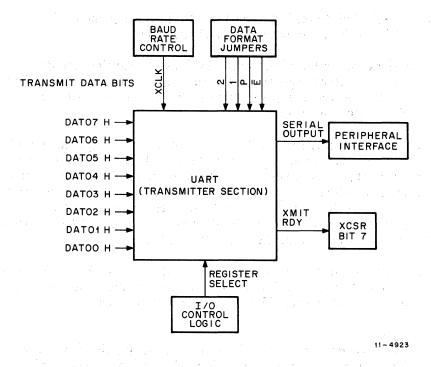

Data to be transmitted to the peripheral device is taken off the three-state bus in parallel by the XBUF and then shifted serially out to the peripheral interface circuit.

Both the RBUF and the XBUF provide "double-buffering" of the data. The buffering is double in that the circuits each have both a serial shift register and a parallel holding register. This allows one character to be held while another is being moved into or out of the buffer.

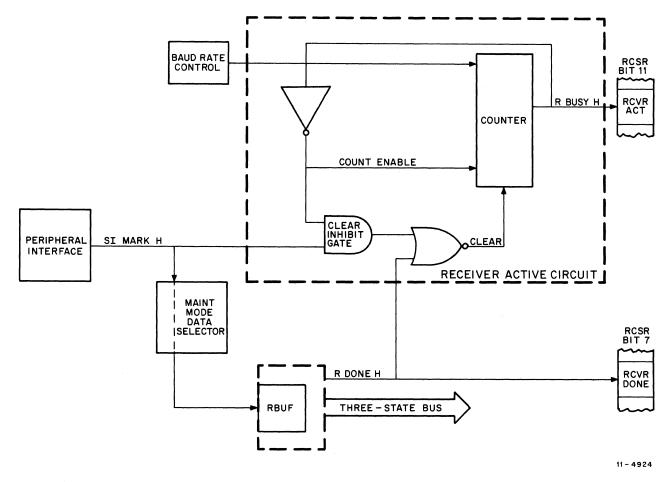

#### 2.3.6 Receiver Active Circuit

The receiver active circuit monitors the serial received data line from the peripheral interface and a receiver done (RDONE H) status bit from the RBUF. The circuit generates a busy signal (RBUSY H) to indicate that the receiver is active. This signal sets the RCVR ACT bit in the RCSR.

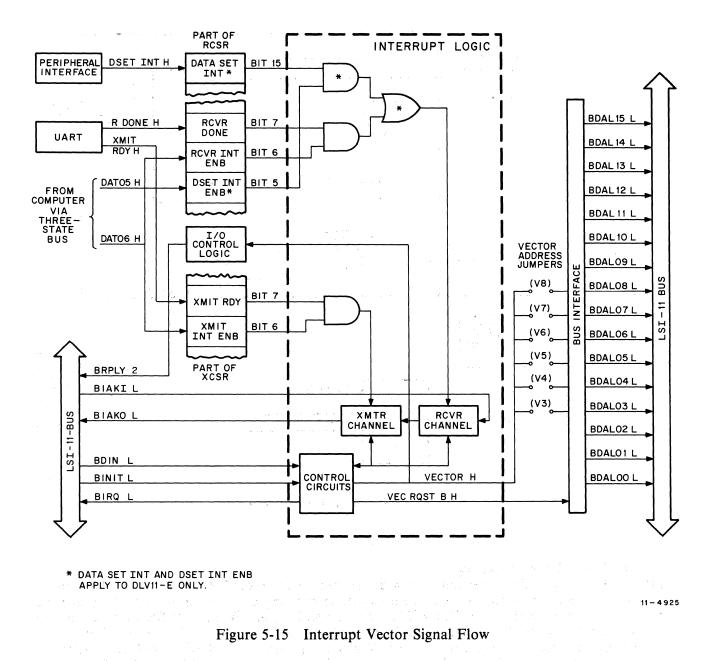

#### 2.3.7 Interrupt Logic

When a peripheral device interfaced by a DLV11-E or DLV11-F needs service, the module can, if enabled, interrupt the computer program and vector to a service routine. The interrupt logic can initiate two types of interrupts: a receiver interrupt and a transmitter interrupt. These interrupts are handled through separate receiver and transmitter channels.

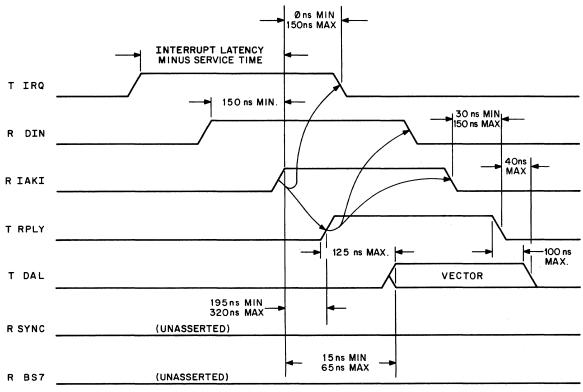

For an interrupt transaction to occur, first the program sets the interrupt enable bit in the control/status register. Next, the interrupt logic recognizes the condition requiring service and asserts the interrupt request line (BIRQ L) to the computer. When the interrupt is acknowledged by the computer, the interrupt logic enables the bus interface to place the vector on the bus lines.

There are two vectors: one for a receiver interrupt and one for a transmitter interrupt. The interrupt logic uses VECRQSTB H to indicate which vector is enabled.

The LSI-11's interrupt acknowledge signal (BIAKI L/BIAKO L) is daisy-chained through the devices on the LSI-11 bus. A device's priority is established by its position in the interrupt acknowledge daisy-chain. The interrupt acknowledge chain goes through both the receiver section and the transmitter section of the module's interrupt logic. It goes through the receiver section first, thereby giving the receiver channel priority over the transmitter channel.

A receiver interrupt is initiated when the RBUF has received and assembled a character of data and is ready to transfer it to the computer. A transmitter interrupt is initiated when the XBUF's holding register is empty and is ready for another data input from the computer.

The DLV11-E differs from the DLV11-F in that it recognizes a second condition requiring a receiver interrupt. The DLV11-E initiates a receiver interrupt when the data set that it is interfacing signals for a handshake. The computer program can read the DLV11-E's RCSR to determine whether the receiver interrupt is for a handshake or for another character of data.

#### 2.3.8 Baud Rate Control

The baud rate control circuit generates clock signals that control the speeds at which the RBUF and XBUF move serial data. The circuit can provide a common clock to both data buffer circuits (common speed operation) or separate transmit and receive clocks (split speed operation).

In common speed operation, both transmit and receive baud rates are either set by wire wrap jumpers R0 through R3 or programmable by three-state bus lines DAT12 H through DAT15 H. In split speed operation, the transmit baud rate is set by jumpers T0 through T3, while the receive baud rate remains under the control of either R0 through R3 or the computer program.

Should it be desired to use a baud rate not available from the baud rate control's crystal-controlled clock generator, the module has provisions for external inputs for both the transmit and receive clocks.

#### 2.3.9 Break Logic

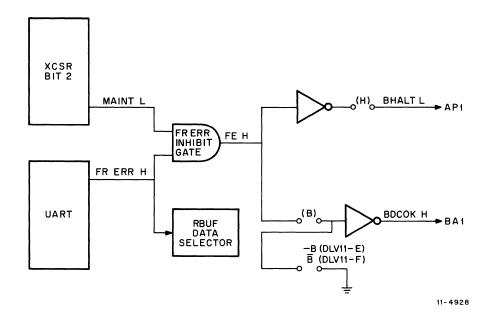

A BREAK signal is a continuous spacing condition on the serial data line. The DLV11-E and DLV11-F can receive BREAK signals from a peripheral device (normally the console device) and can transmit BREAK signals to a peripheral device (normally another processor). Either operation can be enabled or inhibited by wire wrap jumpers.

When the interface module receives a BREAK signal from the serial data line, it interprets the absence of STOP bits as a framing error. It can respond to this apparent error (or to an actual error) in one of three ways:

- 1. It can ignore it the apparent error.

- 2. It can place the LSI-11 in the HALT mode.

- 3. It can cause the LSI-11 to re-boot.

Which action the module takes is controlled by wire wrap jumpers. To place the computer in the HALT mode, the break logic asserts BHALT L. To cause the computer to reload a bootstrap, the break logic negates BDCOK H. Refer to Paragraph 5.9 for further information.

#### 2.3.10 Maintenance Mode Logic

The DLV11-E and DLV11-F have a maintenance mode for verifying the operation of the modules' data paths up to (but not including) the peripheral interface circuitry. This mode is controlled by the computer program, but is used only for checking the interface module, not the computer. In maintenance mode, data from the computer is transferred from the bus interface to the XBUF and serialized, as in normal operation. But then, in addition to going to the peripheral interface circuit, a sample of the XBUF's serial output is also routed back to the RBUF's serial input. There it is converted to parallel, placed on the three-state bus to the bus interface, and transferred back into the computer. The program can then compare the received data with the transmitted data to check for errors.

### 2.3.11 DLV11-E Peripheral Interface

The peripheral interface circuitry converts the DLV11-E's data and modem control signals from TTL levels to EIA-standard bipolar levels for the peripheral device. Likewise, it converts the peripheral's data and control lines from EIA levels to TTL levels for the interface module.

The circuit can receive four modem control signals (RING, CARRIER, CLEAR TO SEND, and SECONDARY RECEIVED DATA) and can transmit four modem control signals (DATA TERMINAL READY, REQUEST TO SEND, FORCE BUSY, and SECONDARY TRANSMITTED DATA). The control signals are routed through the control/status registers. The interrupt logic uses the received control signals to initiate data set interrupts. The program uses the transmitted control signals to perform handshakes with the data set. Refer to Paragraph 5.11 for an example of a handshake sequence.

#### 2.3.12 DLV11-F Peripheral Interface

The DLV11-F peripheral interface operates in one of two possible modes:

- 1. EIA Data Leads Only This type of operation supports terminals that use EIA levels, but do not require control signal interaction.

- 2. 20 mA Current Loop This operation supports terminals that use either active or passive current loops. It also controls the paper tape reader on DIGITAL-modified TTY units that have a reader run relay.

When interfacing EIA-level equipment, the module performs the TTL-to-EIA and EIA-to-TTL level conversion on the transmit and receive data leads only. During data leads only operation, the module does not monitor incoming control signals. Outgoing control signals (REQUEST TO SEND, FORCE BUSY, and DATA TERMINAL READY) are held by driver circuits in a continuous TRUE condition.

When the DLV11-F interfaces a 20 mA current loop peripheral device, it can be jumpered to operate in either active or passive configuration. In the active configuration, the peripheral interface supplies the current for the loop; in the passive configuration, the current is supplied by the peripheral device. In either case, the receive data line from the peripheral is optically isolated from the DLV11-F's internal data path.

The 20 mA current loop transmitter operates in either the active or passive configuration. The transmit data lines are optically isolated from the DLV11-F's internal data path only in the passive configuration.

A Reader Run signal is produced for a peripheral device that has a reader run relay. When enabled by the program, the peripheral interface circuit supplies current to the relay, causing the reader to advance the paper tape.

#### 2.3.13 DC-to-DC Power Inverter

Both the DLV11-E and DLV11-F need -12 V for the data buffers and the peripheral interface. This voltage is produced on the module by a small power inverter. The inverter uses the +12 V power available on the LSI-11 backplane to produce a regulated -12 V for the data buffers and peripheral interface circuits.

# **CHAPTER 3 INSTALLATION**

#### 3.1 GENERAL

This chapter describes the jumper configuration, the installation requirements, and the checkout of the DLV11-E and DLV11-F asynchronous line interface modules. The wire wrap jumper functions are defined and application examples are presented. Wire wrapping instructions are presented in Appendix B.

#### 3.2 CONFIGURATION

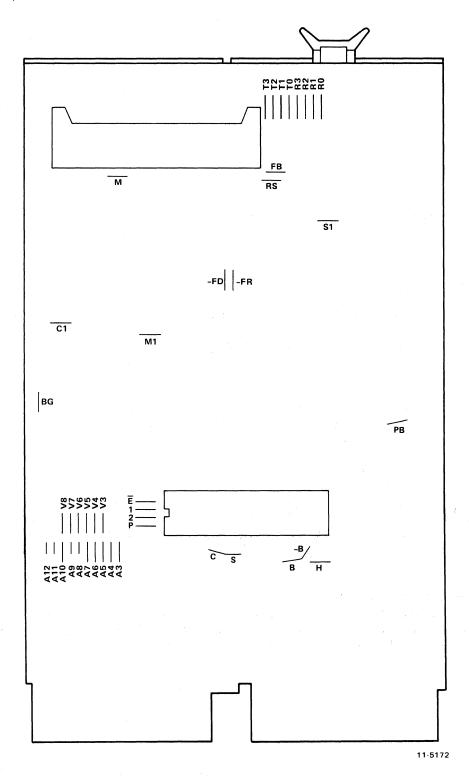

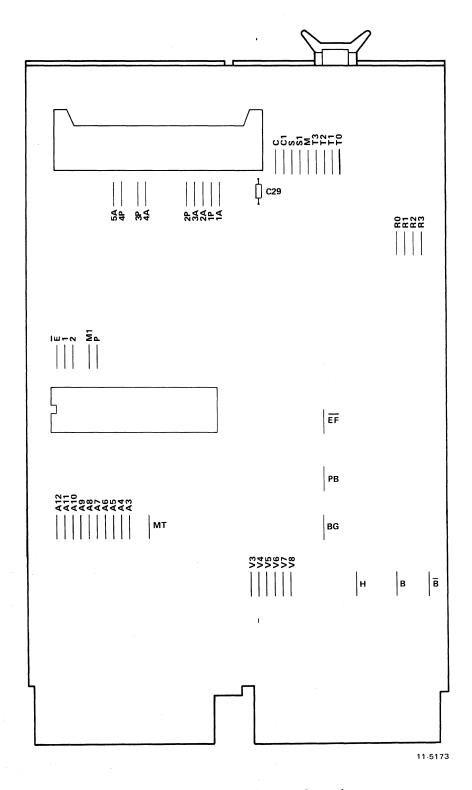

Before installing the module, ensure that it is configured for your application. The jumper locations are depicted in Figures 3-1 and 3-2. Their functions are defined in Tables 3-1, 3-2, and 3-3. Table 3-4 explains the configuration in which the modules are shipped from the factory. Table 3-5 lists common applications of the DLV11-E and DLV11-F; Figures 3-3 and 3-4 illustrate examples of typical cabling requirements.

The DLV11-F is shipped from the factory with capacitor C29 installed (Figure 3-2). This capacitor is provided for applications using Teletype® terminals. For applications using DIGITAL terminals, remove capacitor C29.

#### 3.3 MODULE INSTALLATION

The DLV11-E or DLV11-F module can be installed in any slots in the LSI-11 backplane, except the first four slots (the LSI-11 processor always occupies the first slots). Do not leave any unused option locations between the processor and the DLV11-E or DLV11-F. An open slot would break the interrupt acknowledge daisy chain. The priority of the module is determined by its proximity to the processor on the bus (refer to Figure 3-5). The closer the slot is to the processor module, the higher the interface module's priority.

Determine the appropriate slot for the module. For example, if a DLV11-E is interfacing communications lines from a host computer, it would normally be placed in the slot closest to the processor module, followed by the module interfacing the console terminal. Refer to *Microcomputer Handbook* (DIGITAL part number EB 06583 76) for system considerations.

<sup>®</sup>Teletype is a registered trademark of Teletype Corporation.

Figure 3-1 DLV11-E Jumper Locations

Figure 3-2 DLV11-F Jumper Locations

## Table 3-1 Jumper Definitions

#### **NOTE**

This table pertains to both the DLV11-E and the DLV11-F, except as noted. Jumpers are inserted to enable the function they control except for those jumpers that indicate negation (such as "-B" and "B"). Negated jumpers are removed to enable the functions they control.

| Jumper | Function                                                                                                                                                                    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3-A12 | These jumpers correspond to bits 3-12 of the address word. When inserted, they will cause the bus interface to check for a True condition on the corresponding address bit. |

| V3-V8  | Used to generate the vector during an interrupt transaction. Each inserted jumper will assert the corresponding vector address bit on the LSI-11 bus.                       |

| R0-R3  | Receiver and transmitter baud rate select jumpers, during common speed operation.                                                                                           |

|        | Receiver only baud rate select jumpers during split speed operation (see Table 3-2).                                                                                        |

| T0-T3  | Transmitter baud rate select jumpers during split speed operation.                                                                                                          |

|        | Both receiver and transmitter baud rate if maintenance mode is entered during split speed operation (see Tale 3-2).                                                         |

| BG     | Jumper is inserted to enable Break generation.                                                                                                                              |

| P      | Jumper is inserted for operation with parity.                                                                                                                               |

| Ē      | Removed for even parity; inserted for odd parity. Receiver checks for appropriate parity and transmitter inserts appropriate parity.                                        |

| 1, 2   | These jumpers select the desired number of data bits (see Table 3-3).                                                                                                       |

| РВ     | Jumper is inserted to enable the programmable baud rate capability.                                                                                                         |

| C, C1  | These jumpers are inserted for common speed operation. (Note that S and S1 must be removed when C and C1 are inserted.)                                                     |

| S, S1  | Inserted for split speed operation. (Note that C and C1 must be removed when S and S1 are inserted.)                                                                        |

| Н      | This jumper is inserted to assert BHALT L when a framing error is received, except when the Maintenance bit is set. This places the LSI-11 in the halt mode.                |

|        |                                                                                                                                                                             |

**Table 3-1 Jumper Definitions (Cont)**

| Table 3-1 Jumper Definitions (Cont)     |                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Jumper                                  | Function                                                                                                                                                                                                                              |  |  |  |

| B, -B<br>(DLV11-E)<br>B, B<br>(DLV11-F) | Jumper B is inserted to negate BDCOK H when a BREAK signal or framing error is received, except when the Maintenance bit is set. This causes the LSI-11 to reload the bootstrap. (Jumper -B or B must be removed when B is inserted.) |  |  |  |

| -FD<br>(DLV11-E<br>only)                | Jumper is removed to force DATA TERMINAL READY signal on.                                                                                                                                                                             |  |  |  |

| -FR<br>(DLV11-E<br>only)                | Jumper is removed to force REQUEST TO SEND signal on.                                                                                                                                                                                 |  |  |  |

| RS<br>(DLV11-E<br>only)                 | This jumper is inserted to enable normal transmission of the REQUEST TO SEND signal.                                                                                                                                                  |  |  |  |

| FB<br>(DLV11-E<br>only)                 | Inserted to enable transmission of the FORCE BUSY signal (for Bell model 103E data sets).                                                                                                                                             |  |  |  |

| 1A, 2A,<br>and 3A<br>(DLV11-F<br>only)  | These three jumpers are inserted to make the 20 mA current loop receiver active. (Jumpers 1P and 2P must be removed when 1A, 2A, and 3A are inserted.)                                                                                |  |  |  |

| 1P, 2P<br>(DLV11-F<br>only)             | These jumpers are inserted to make the 20 mA current loop receiver passive. (Jumpers 1A, 2A, and 3A must be removed when 1P and 2P are installed.)                                                                                    |  |  |  |

| 4A, 5A<br>(DLV11-F<br>only)             | Inserted to make the 20 mA current loop transmitter active. (Jumpers 3P and 4P must be removed when 4A and 5A are inserted.)                                                                                                          |  |  |  |

| 3P, 4P<br>(DLV11-F<br>only)             | Inserted to make the 20 mA current loop transmitter passive. (Jumpers 4A and 5A must be removed when 3P and 4P are inserted.)                                                                                                         |  |  |  |

| EF<br>(DLV11-F<br>only)                 | Jumper is removed to enable the error flags to be read in the high byte of the Receiver Buffer.                                                                                                                                       |  |  |  |

| MT<br>(DLV11-F<br>only)                 | When inserted, enables maintenance bit.                                                                                                                                                                                               |  |  |  |

| M, M1                                   | These are test jumpers used during the manufacture of the module.  They are not defined for field use.                                                                                                                                |  |  |  |

Table 3-2 Baud Rate Selections

|                  | Bit | Bit | Bit | Bit | Bit |       |

|------------------|-----|-----|-----|-----|-----|-------|

| Program Control  | 15  | 14  | 13  | 12  | 11* |       |

| Receive Jumpers  | R3  | R2  | R1  | R0  |     | Baud  |

| Transmit Jumpers | T3  | T2  | T1  | T0  |     | Rate  |

| •                | I   | I   | I   | I   |     | 50    |

|                  | I   | I   | I   | R   | ·   | 75    |

|                  | I   | I   | R   | I   |     | 110   |

|                  | I   | I   | R   | R   |     | 134.5 |

|                  | I   | R   | l I | I   |     | 150   |

|                  | I   | R   | I   | R   | İ   | 300   |

|                  | I   | R   | R   | I   | ,   | 600   |

|                  | I   | R   | R   | R   | Ì   | 1200  |

|                  | R   | I   | I   | I   |     | 1800  |

|                  | R   | I   | I   | R   | }   | 2000  |

|                  | R   | l I | R   | I   |     | 2400  |

|                  | R   | I   | R   | R   |     | 3600  |

|                  | R   | R   | I   | I   |     | 4800  |

|                  | R   | R   | I   | R   |     | 7200  |

|                  | R   | R   | R   | I   |     | 9600  |

I = Jumper Inserted = Program Bit Cleared.

Table 3-3 Data Bit Selections

| Jumpers          |                  | Number of Data Bits |

|------------------|------------------|---------------------|

| 2                | 1                |                     |

| I<br>I<br>R<br>R | I<br>R<br>I<br>R | 5<br>6<br>7<br>8    |

R = Jumper Removed = Program Bit Set.

<sup>\*</sup>Bit 11 of the XCSR (Write Only Bit) must be set in order to select a new baud rate under program control. Also, jumper PB must be inserted to enable baud rate selection under program control.

Table 3-4 Jumper Configuration When Shipped

| Jumper<br>Designation                                | Jumper<br>DLV11-E                    | r State                              | Function Implemented                                                                                                                                                                                                                                           |

|------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11 | R<br>I<br>I<br>R<br>R<br>R<br>I<br>R | I<br>R<br>R<br>I<br>R<br>R<br>R<br>R | Jumpers A3 through A12 implement device address 17561X for the DLV11-E and 17756X for the DLV11-F. The least significant octal digit is hardwired on the module to address the four device registers as follows:   X = 0 RCSR X = 2 RBUF X = 4 XCSR X = 6 XBUF |

| V3<br>V4<br>V5<br>V6<br>V7<br>V8                     | I<br>I<br>I<br>R<br>R<br>I           | I<br>R<br>R<br>I<br>I                | This jumper selection implements interrupt vector address $300_8$ for receiver interrupts and $304_8$ for transmitter interrupts on the DLV11-E. On the DLV11-F it selects $60_8$ for receiver interrupts and $64_8$ for transmitter interrupts.               |

| R0<br>R1<br>R2<br>R3                                 | I<br>R<br>I<br>I                     | I<br>R<br>I<br>I                     | The module is configured to receive at 110 baud.                                                                                                                                                                                                               |

| T0<br>T1<br>T2<br>T3                                 | I<br>R<br>R<br>R                     | I<br>R<br>R<br>R                     | The transmitter is configured for 9600 baud if split speed operation is used.                                                                                                                                                                                  |

| BG V                                                 | I<br>R                               | I<br>R                               | Break generation is enabled. Parity bit is disabled.                                                                                                                                                                                                           |

| Ē                                                    | R                                    | R                                    | Parity type is not applicable when P is removed.                                                                                                                                                                                                               |

| 1 2                                                  | R<br>R                               | R<br>R                               | Operation with 8 data bits per character.                                                                                                                                                                                                                      |

| PB                                                   | R                                    | $\mathbf{R}_{\mathbf{q}}$            | Programmable baud rate function disabled.                                                                                                                                                                                                                      |

| C<br>C1                                              | I<br>I                               | I<br>I                               | Common speed operation enabled.                                                                                                                                                                                                                                |

Table 3-4 Jumper Configuration When Shipped (Cont)

| erica de entre de la companya de entre | essa make e 1985a kira ay ar e e e e e e e e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | era e jeune volgjere liti se                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

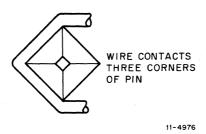

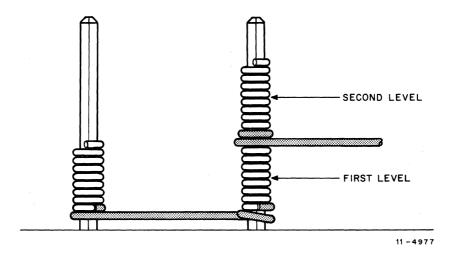

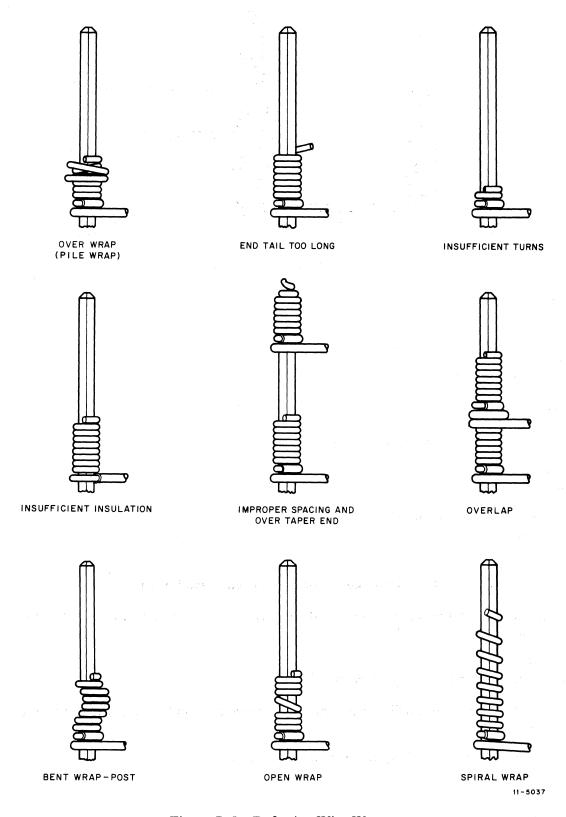

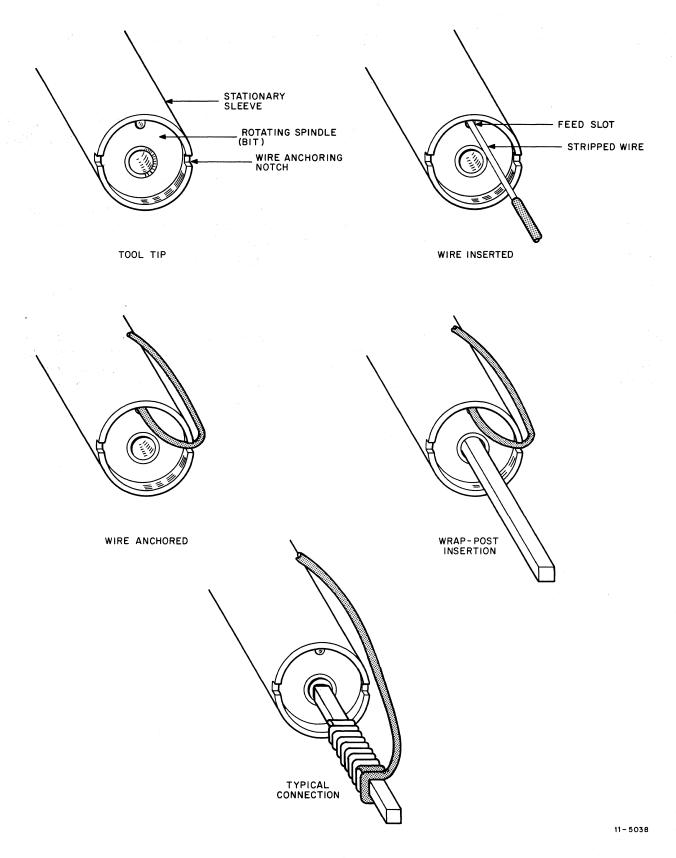

| Jumper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jumpe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | r State                                                                                              | and the state of t |