FP11-A floating-point processor user's guide

FP11-A floating-point processor user's guide

# Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

# CONTENTS

# CHAPTER 1 INTRODUCTION

| 1.1   | GENERAL                                 | 1-1 |

|-------|-----------------------------------------|-----|

| 1.2   | FEATURES                                | 1-1 |

| 1.2.1 | Floating-Point Instruction Set Features | 1-1 |

| 1.2.2 | FP11-A Features                         | 1-2 |

| 1.3   | ARCHITECTURE                            | 1-2 |

| 1.4   | PHYSICAL DESCRIPTION                    | 1-2 |

| 1.5   | RELATED DOCUMENTATION                   | 1-3 |

# CHAPTER 2 INSTALLATION AND CHECKOUT

| 2.1   | SCOPE                                        | 2-1 |

|-------|----------------------------------------------|-----|

| 2.2   | FP11-A FLOATING-POINT PROCESSOR INSTALLATION | 2-1 |

| 2.2.1 | FP11-A Add-On Installation Procedure         | 2-1 |

| 2.2.2 | BA11-L Box                                   | 2-4 |

| 2.3   | FP11-AU UPGRADE KIT                          | 2-7 |

| 2.3.1 | FP11-AU Power Components Installation        | 2-7 |

| 2.3.2 | FP11-AU Logic Installation                   |     |

# CHAPTER 3 REVIEW OF FLOATING-POINT NUMBERS

| 3.1 | INTRODUCTION                               | 3-1 |

|-----|--------------------------------------------|-----|

| 3.2 | INTEGERS                                   | 3-1 |

| 3.3 | FLOATING-POINT NUMBERS                     | 3-1 |

| 3.4 | NORMALIZATION                              | 3-2 |

| 3.5 | FLOATING-POINT ADDITION AND SUBTRACTION    | 3-3 |

| 3.6 | FLOATING-POINT MULTIPLICATION AND DIVISION | 3-4 |

# CHAPTER 4 DATA FORMATS

| 4.1     | INTRODUCTION                            | 4-1 |

|---------|-----------------------------------------|-----|

| 4.2     | FP11-A INTEGER FORMATS                  | 4-1 |

| 4.3     | FP11-A FLOATING-POINT FOR MATS          | 4-1 |

| 4.3.1   | FP11-A Floating-Point Data Word         | 4-1 |

| 4.3.1.1 | Floating-Point Fraction                 | 4-5 |

| 4.3.1.2 | Floating-Point Exponent                 | 4-6 |

| 4.4     | FP11-A PROGRAM STATUS REGISTER          | 4-7 |

| 4.5     | PROCESSING OF FLOATING-POINT EXCEPTIONS | 4-8 |

# **CONTENTS** (Cont)

| 5.1       | FLOATING-POINT ACCUMULATORS                                         | 5-1  |

|-----------|---------------------------------------------------------------------|------|

| 5.2       | INSTRUCTION FORMATS                                                 | 5-1  |

| 5.3       | INSTRUCTION SET                                                     | 5-4  |

| 5.3.1     | Arithmetic Instructions                                             | 5-10 |

| 5.3.2     | Floating-Modulo Instruction                                         | 5-11 |

| 5.3.3     | Load Instruction                                                    | 5-11 |

| 5.3.4     | Store Instruction                                                   | 5-11 |

| 5.3.5     | Load Convert (Double-to-Floating, Floating-to-Double) Instructions  | 5-11 |

| 5.3.6     | Store Convert (Double-to-Floating, Floating-to-Double) Instructions |      |

| 5.3.7     | Clear Instruction                                                   |      |

| 5.3.8     | Test Instruction                                                    | 5-12 |

| 5.3.9     | Absolute Instruction                                                | 5-12 |

| 5.3.10    | Negate Instruction                                                  | 5-13 |

| 5.3.11    | Load Exponent Instruction                                           |      |

| 5.3.12    | Load Convert Integer-to-Floating Instruction                        |      |

| 5.3.13    | Store Exponent Instruction                                          |      |

| 5.3.14    | Store Convert Floating-to-Integer Instruction                       |      |

| 5.3.15    | Load FP11's Program Status                                          |      |

| 5.3.16    | Store FP11's Program Status                                         |      |

| 5.3.17    | Store FP11's Status                                                 |      |

| 5.3.18    | Copy Floating Condition Codes                                       | 5-20 |

| 5.3.19    | Set Floating Mode                                                   |      |

| 5.3.20    | Set Double Mode                                                     | 5-20 |

| 5.3.21    | Set Integer Mode                                                    | 5-20 |

| 5.3.22    | Set Long-Integer Mode                                               | 5-20 |

| 5.4       | FP11-A PROGRAMMING EXAMPLES                                         | 5-21 |

| CHAPTER 6 | PROCESSOR ORGANIZATION                                              |      |

| 6.1       | INTRODUCTION                                                        | 6-1  |

| 6.2       | MICROPROCESSOR DESCRIPTION                                          |      |

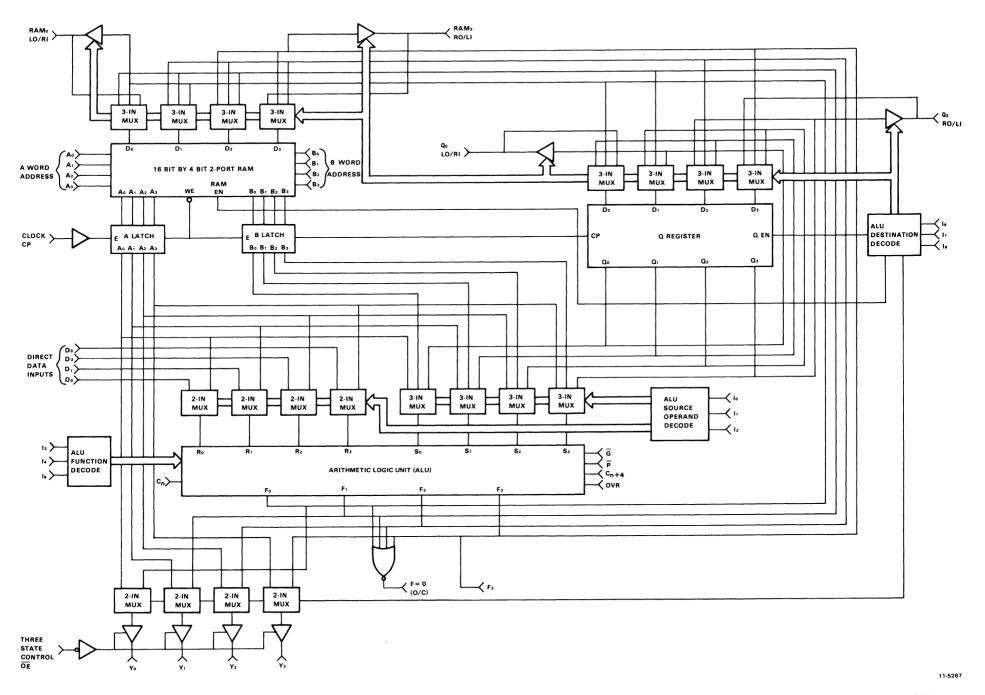

| 6.2.1     | Microprocessor Organization                                         |      |

| 6.2.2     | Arithmetic/Logical Operations                                       |      |

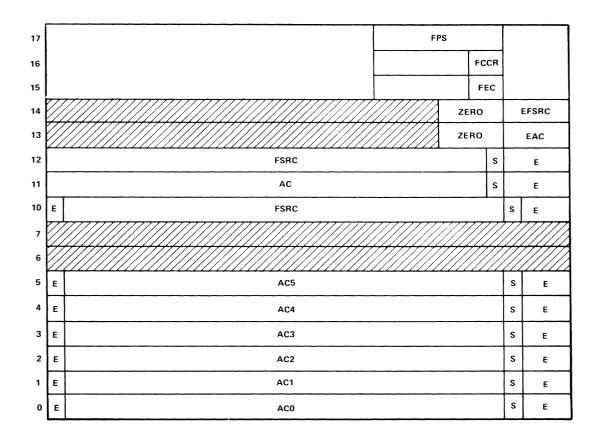

| 6.2.3     | RAM                                                                 |      |

| 6.2.4     | Arithmetic Logic Unit (ALU)                                         |      |

| 6.2.5     | Q-Register                                                          |      |

# CHAPTER 5 FLOATING-POINT INSTRUCTIONS

| PROCESSOR ORGANIZATION                                   |                                             |

|----------------------------------------------------------|---------------------------------------------|

| INTRODUCTION                                             | -1                                          |

| MICROPROCESSOR DESCRIPTION                               | -2                                          |

| Microprocessor Organization6                             | -5                                          |

| Arithmetic/Logical Operations6                           | -5                                          |

|                                                          |                                             |

| Arithmetic Logic Unit (ALU)6                             | -9                                          |

| Q-Register                                               | 10                                          |

| Source Operands and ALU Functions6-                      | 10                                          |

| Logical and Arithmetic Functions6-                       | 10                                          |

| Logical Functions for G, P, C <sub>n+4</sub> , and OVR6- | 10                                          |

|                                                          |                                             |

|                                                          |                                             |

| TRI-STATE TRANSCEIVERS AND BUFFER6-                      | 10                                          |

| BRANCH LOGIC AND TRI-STATE CONTROL6-                     | 10                                          |

| CONSTANTS, BYTE AND SECTOR CONTROL, SHIFT CONTROL6-      | 14                                          |

|                                                          | PROCESSOR ORGANIZATION         INTRODUCTION |

# CONTENTS (Cont)

# CHAPTER 7 MAINTENANCE

| 7.1   | INTRODUCTION                 | 7-1 |

|-------|------------------------------|-----|

| 7.2   | FP11-A DIAGNOSTICS           |     |

| 7.2.1 | MAINDEC DFFPAA               |     |

| 7.2.2 | MAINDEC DFFPBA               |     |

| 7.2.3 | MAINDEC DFFPCA               | 7-2 |

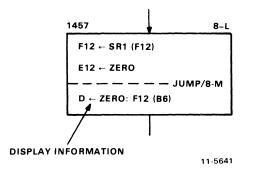

| 7.3   | KY11-LB PROGRAMMER'S CONSOLE | 7-2 |

| 7.4   | FP11-A FLOW DIAGRAMS         |     |

| 7.5   | EXTENDER BOARD               |     |

|       |                              |     |

# APPENDIX A OPTION POWER SPECIFICATIONS

# **FIGURES**

# Figure No.

# Title

# Page

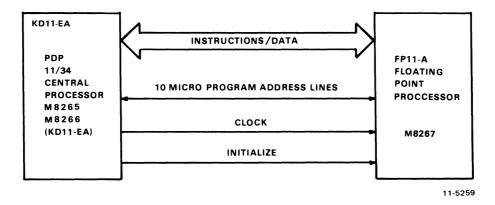

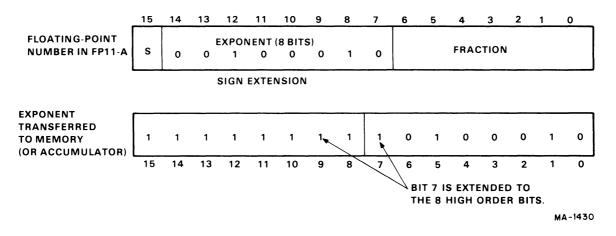

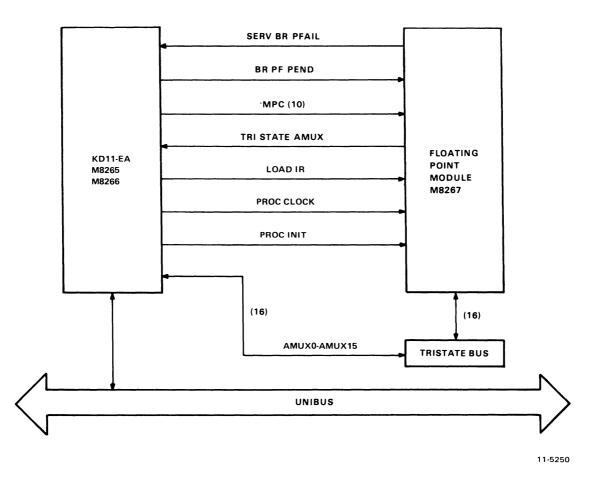

| 1-1 | KD11-EA/FP11-A Signal Interface          | 1-2  |

|-----|------------------------------------------|------|

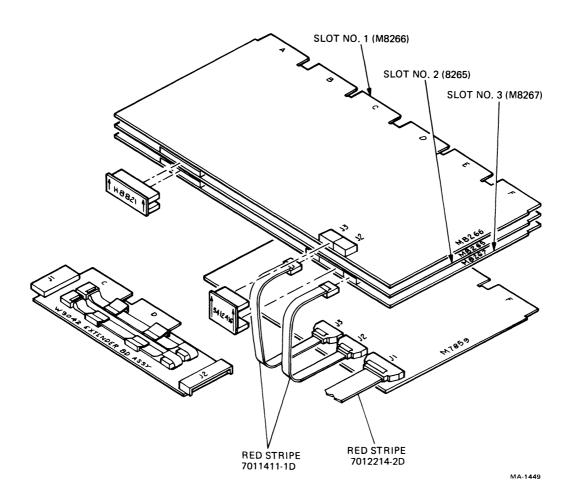

| 2-1 | Maintenance Cable Installation           | 2-5  |

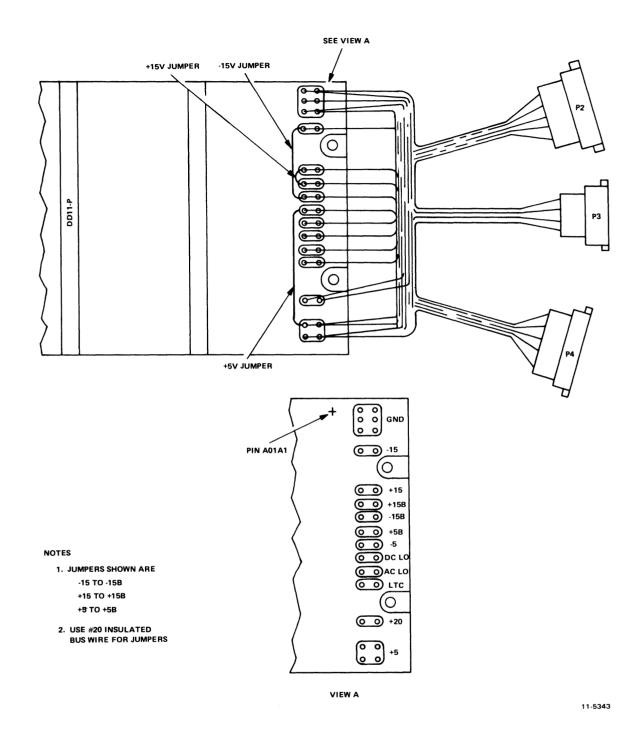

| 2-2 | Backplane Jumpers                        | 2-6  |

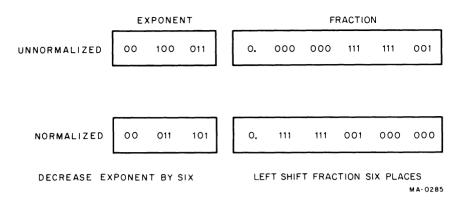

| 3-1 | Normalization                            | 3-3  |

| 4-1 | Integer Formats                          | 4-2  |

| 4-2 | Floating-Point Data Formats              | 4-2  |

| 4-3 | Floating-Point Data Words                |      |

| 4-4 | Interpretation of Floating-Point Numbers | 4-4  |

| 4-5 | Unnormalized Floating-Point Fraction     | 4-5  |

| 4-6 | FP11-A Status Register Format            |      |

| 5-1 | Floating-Point Accumulators              |      |

| 5-2 | Instruction Formats                      |      |

| 5-3 | Double-to-Single Precision Rounding      | 5-11 |

| 5-4 | Single-to-Double Precision Appending     |      |

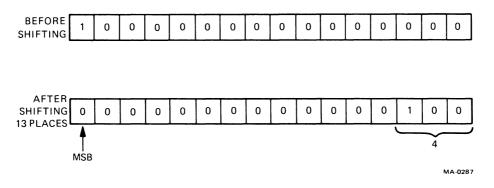

| 5-5 | Integer Left-Shift Example               |      |

| 5-6 | Normalized Integer Example               | 5-15 |

| 5-7 | Store Exponent Example No.1              |      |

| 5-8 | Store Exponent Example No. 2             |      |

| 5-9 | Store Convert Integer Example            | 5-17 |

| 6-1 | KD11-EA/FP11-A Data Flow                 |      |

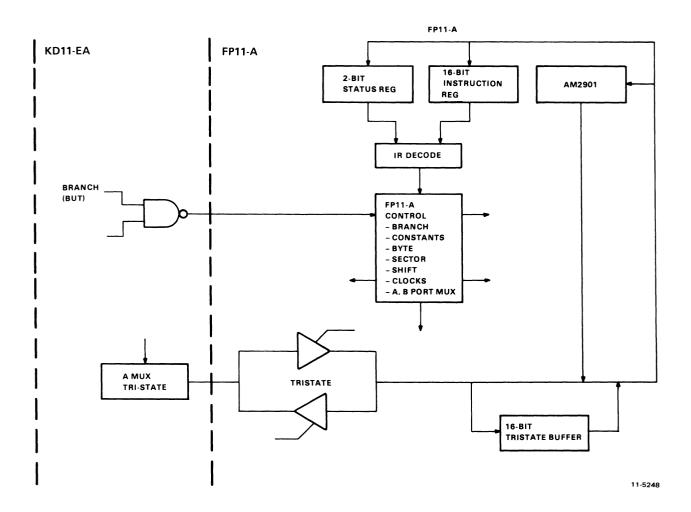

| 6-2 | Simplified FP11-A Block Diagram          |      |

| 6-3 | Microprocessor (AM2901) Block Diagram    |      |

| 6-4 | RAM Register Usage                       |      |

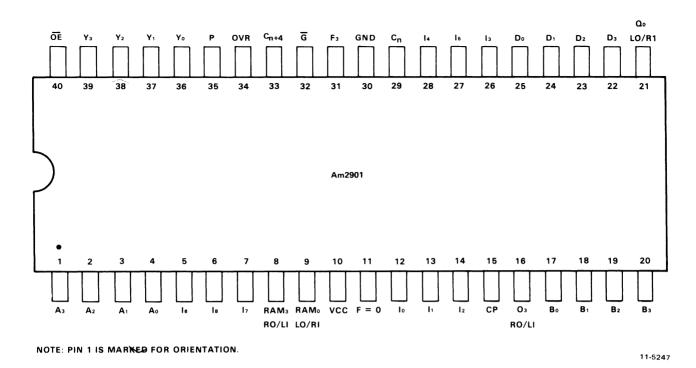

| 6-5 | AM2901 Pin Connections                   |      |

| 7-1 | Display Information                      |      |

# TABLES

# Table No.

# Title

# Page

| 4-1 | FP11-A Status Register                              | 4-7  |

|-----|-----------------------------------------------------|------|

| 4-2 | FP11-A Exception Codes                              |      |

| 5-1 | Format of FP11-A Instructions                       |      |

| 5-2 | FP11-A Instruction Set                              | 5-5  |

| 6-1 | ALU Source Operand Contest                          | 6-5  |

| 6-2 | ALU Function Control                                |      |

| 6-3 | ALU Destination Control                             | 6-7  |

| 6-4 | Source Operand and ALU Function Matrix              | 6-9  |

| 6-5 | ALU Logic Mode Functions                            |      |

| 6-6 | ALU Arithmetic Mode Functions                       |      |

| 6-7 | Logic Equations for ALU Functions                   | 6-12 |

| 6-8 | $P, G, C_{N+4}, OVR$ Functions                      | 6-13 |

| A-1 | PDP-11 Family Models and Options Power Requirements | A-1  |

| A-2 | PDP-11 Family Options Power Requirements            |      |

# CHAPTER 1 INTRODUCTION

# **1.1 GENERAL**

The FP11-A Floating-Point Processor is a hardware option that enables the PDP-11/34A central processor to execute floating-point arithmetic operations. The FP11-A performs all floating-point arithmetic operations and converts data between integer and floating-point formats. Floating-point representation permits a greater range of number values than is possible with the conventional integer mode. Thus, the FP11-A option provides a speedier alternative to the use of software floating-point routines, and system speed is increased without complex arithmetic coding routines that consume valuable CPU time. The FP11-A features both single- and double-precision (32- or 64-bit) capability and floating-point modes.

The FP11-A is an integral part of the central processor. It operates using similar address modes, and the same memory management facilities as the central processor. Floating-point processor instructions can reference the floating-point accumulators, the central processor's general registers, or any location in memory.

# **1.2 FEATURES**

The following paragraphs summarize the features of the PDP-11/34A floating-point instruction set and the FP11-A.

# **1.2.1** Floating-Point Instruction Set Features

- 32-bit (single-precision) and 64-bit (double-precision) data modes

- Addressing modes compatible with existing PDP-11 addressing modes

- Special instructions that can improve input/output routines and mathematical subroutines

- Allows execution of in-line code (i.e., floating-point instructions and other instructions can appear in any sequence desired)

- Multiple accumulators for ease of data handling

- Can convert 32- or 64-bit floating-point numbers to 16- or 32-bit integers during the Store class of instructions

- Can convert 32-bit floating-point numbers to 64-bit floating-point numbers and vice-versa during the Load or Store class of instructions.

# 1.2.2 FP11-A Features

- Performs medium-speed, floating-point operations on single- and double-precision data

- Has 17 (decimal) digit accuracy

- Contains its own microprogrammed control store

- Contains six 64-bit floating-point accumulators

- Contains error recovery aids

# **1.3 ARCHITECTURE**

The FP11-A contains scratchpad registers, a floating exception address pointer (FEA), status and error registers, and six general-purpose accumulators (AC0-AC5).

Each accumulator is interpreted to be 32 or 64 bits long depending on the instruction and the status of the floating-point processor. For 32-bit instructions, only the left-most bits are used. The remaining bits are unaffected.

The six general-purpose accumulators are used in numeric calculations and interaccumulator data transfers. The first four registers (AC0-AC3) are also used for all data transfers between the FP11-A and the central processor's general registers or memory.

# **1.4 PHYSICAL DESCRIPTION**

The FP11-A consists of a single hex board [M8267 for the PDP-11/34A (KD11-EA)] and modifications to the M7265 and M7266 boards used in the PDP-11/34 central processor. (The modified boards are designated M8265 and M8266, and the modified processor is designated as the KD11-EA). Figure 1-1 shows the basic signal paths between the central processor and the FP11-A. The bidirectional data bus transfers instructions and data between the processors. An expanded control store in the KD11-EA accommodates floating-point requirements.

Figure 1-1 KD11-EA/FP11-A Signal Interface

## **1.5 RELATED DOCUMENTATION**

The following documents supplement this user's guide on the FP11-A Floating-Point Processor.

# Manual

#### **Document Number**

| MM11-D/DP Core Memory ManualEMS11-E-J MOS Memory Maintenance ManualEPDP-11 Peripherals HandbookEPDP-11/04, 34, 45, 55 Processors HandbookE | K-MM11B-TM<br>K-MM11D-TM<br>K-MS11E-MM<br>P-PDP11-HB<br>P-PDP11/04-HB |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| PDP-11/34 Processor Handbook E                                                                                                             | P-PDP11/04-HB<br>P-11034-HB<br>K-KD1EA-MM                             |

# CHAPTER 2 INSTALLATION AND CHECKOUT

# 2.1 SCOPE

This chapter provides the information necessary for unpacking, inspection, installation, and checkout of the FP11-A and FP11-AU Floating-Point Processors.

#### 2.2 FP11-A FLOATING-POINT PROCESSOR INSTALLATION

The FP11-A Floating-Point Processor option for the PDP-11/34A CPU consists of the following parts:

- 1. M8267 Floating-point module

- 2. H8821 20-pin over-the-top connector

- 3. 54-12416 10-pin over-the-top connector

- 4. W9042 Bus extender module

Prior to the installation of the FP11-A option, the +5 Vdc current available to the PDP-11/34A CPU backplane must be calculated. The following procedure is designed to help you calculate +5 Vdc current drain and system configuration.

#### 2.2.1 FP11-A Add-On Installation Procedure

1. Verify system integrity by running the following diagnostics in the order given.

| PDP-11/34   | CPU Test                     | DFKAA |

|-------------|------------------------------|-------|

| ,           | Traps Test (at least Rev. C) | DFKAB |

|             | EIS Test                     | FDKAC |

| 0-124K memo | ry exerciser                 | DZQMC |

2. Is CPU a PDP-11/34A? (See serial name tag.)

An FP11-A cannot be installed on a PDP-11/34. To upgrade a PDP-11/34 to use an FP11-A, an FP11-AU kit must be used. Refer to Paragraph 2.3.

3. Is CPU box 26.7cm (10.5 in)?

No

YesNoIRefer to Paragraph 2.2.2, BA11-L Box.

4. Calculate +5 Vdc current drain in the CPU backplane. Calculate +5 Vdc current drain for all other backplanes in box (Figure 2-1).

5. Is the total current drain (all backplanes) greater than 57 A? (Does not include M8267 current.)

No

Yes

Is expander box available with room and current?

Yes

No

Refer to step 17.

Refer to step 6.

6. Is the battery backup (BBU) option present?

No Yes All jumpers must be out of all backplanes in box. Refer to Figure 2-2 and step 9.

7. Do backplane jumpers check as follows?

```

\begin{array}{c} \text{CPU backplane (DD11-PK).} \\ +5 \text{ VB to } +5 \text{ V jumper} & \text{In} \\ +15 \text{ VB to } +15 \text{ V jumper} & \text{In} \\ -15 \text{ VB to } -15 \text{ V jumper} & \text{In} \end{array} \right\} \text{ See Figure 2-2.}

```

Refer to step 8.

8. All other backplanes in box (DD11-DK, CK).

```

\begin{array}{c} +5 \text{ VB to } +5 \text{ V jumper} \\ +15 \text{ VB to } +15 \text{ V jumper} \\ -15 \text{ VB to } -15 \text{ V jumper} \end{array} \begin{array}{c} \text{Out} \\ \text{In} \\ \text{In} \end{array} \right\} \text{ See Figure 2-2.}

```

Refer to step 9.

9. Is slot 3 open in CPU backplane?

Yes

No

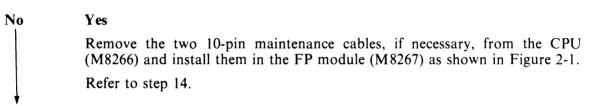

Is cache (M8268) in slot 3?

No

Yes

Cache is placed in slot 3 only if FP is not present. When FP is added, cache is moved to slot 5. Slots 4A and B are reserved for M9301/M9312 (Figure 2-1). Remove the over-the-top (OTT) connectors and move cache module (M8268) to slot 5. H8822 (OTT) is necessary to complete the installation (Figure 2-1). Refer to step 10.

Refer to step 10.

- 10. Is the MOS memory installed in any backplane other than the CPU backplane?

- NoYesAdd 0.5 A at +5 Vdc for each MOS board not installed in the CPU backplane<br/>(CPU box only) to the current drain total for the CPU backplane calculated in<br/>step 4.Refer to step 11.

11. Is the CPU backplane current drain less than 25 A at +5 Vdc?

Yes

No

The devices must be moved from the CPU backplane to some other backplane in the box in order to vacate slot 3 and to reduce the current drain at +5 Vdc to 25 A or less. This must be done without overloading the second +5 Vdc regulator in the box.

Is reconfiguring within the box possible?

Yes No

No

Can the devices be moved to an expander box without overloading the expander box?

Yes Reconfigure the system until the current in the CPU backplane is less than 25 A at +5 Vdc.

Refer to step 17.

Reconfigure within the box until the CPU backplane current drain at +5 Vdc is less than 25 A.

Refer to step 12.

- 12. Install the FP11-A module (M8267) in slot 3 of the CPU backplane.

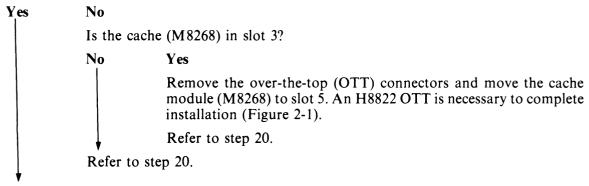

- 13. Is KY11-LB (M7859) present?

- 14. Install the two over-the-top (OTT) connectors as shown in Figure 2-1. Use H8822 if the cache and FP are both present.

- 15. Turn power on and run the following diagnostics in the order given.

| PDP-11/34 | CPU Test        |                 | DFKAA |

|-----------|-----------------|-----------------|-------|

| PDP-11/34 | Traps Test      | At least Rev. C | DFKAB |

| PDP-11/34 | <b>EIS</b> Test |                 | DFKAC |

| PDP-11/34 | FPP Diagnostic  | Part 1          | DFFPA |

| PDP-11/34 | FPP Diagnostic  | Part 2          | DFFPB |

| PDP-11/34 | FPP Diagnostic  | Part 3          | DFFPC |

- 16. End

- 17. When it is impossible to reconfigure the box to accommodate the FP11-A (M8267) without overloading the +5 V regulator, one alternative is to move some devices to an expander box. If an expander box is not present on the system, then there are two ways to proceed.

- a. Remove some number of devices from the box to compensate for the 7 A at +5 Vdc used by the FP11-A, and leave these devices out of the system.

- b. Postpone installation until an expansion box can be added to the system. Refer to step 16.

# 2.2.2 BA11-L Box

- 18. Calculate the current drain at +5 Vdc for the backplane (DD11-PK) (Table 2-1 and Figure 2-1).

- 19. Is slot 3 open in the backplane?

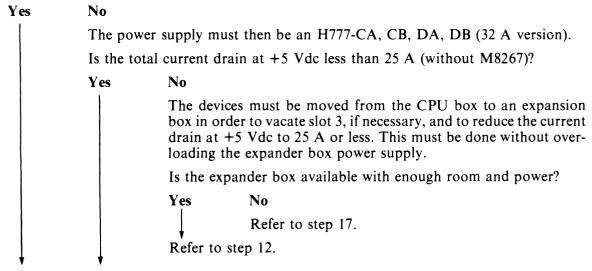

20. Is the power supply an H777-AA, AB, BB (25 A version)?

21. Is the total current drain at +5 Vdc less than 18 A (without M8267)?

Yes No

The devices must be moved from the CPU box to an expansion box in order to vacate slot 3, if necessary, and to reduce the current drain at +5 Vdc to 18 A or less. This must be done without overloading the expander box power supply. Is the expander box available with enough room and power?

Yes No

Refer to step 17.

Reconfigure the system until the CPU box current drain at +5 Vdc is less than 18 A.

Refer to step 12.

2-4

Figure 2-1 Maintenance Cable Installation

Figure 2-2 Backplane Jumpers

# 2.3 FP11-AU UPGRADE KIT

The FP11-AU upgrade kit contains power supply components necessary to increase the +5 Vdc current levels available from the 26.7 cm (10.5 in) mounting box. The purpose of the upgrade kit is to provide a method by which PDP-11/34 CPUs can use the floating-point (FP11-A) option. Since the FP11-A is an option for the PDP-11/34A CPU, additional hardware is required to upgrade the PDP-11/34 models to include the floating-point option. The following parts are required.

- 1. M8265 Data path module

- 2. M8267 FP module

- 3. M8266 Control module

- 4. H7441 Regulator module

- 5. H8821 20-pin over-the-top connector

- 6. 54-12416 10-pin over-the-top connector

- 7. W9042 Bus extender module

- 8. 54-10834YA Power distribution board

The tools required are:

- 1. Phillips screwdriver (medium and large)

- 2. Slot screwdriver (large)

- 3. 90 degree offset Phillips screwdriver.

# 2.3.1 FP11-AU Power Components Installation

# CAUTION

#### Turn off computer system and disconnect it from power source before performing installation procedure.

- 1. Slide BA11-K mounting box out of the cabinet assembly to the limits of the chassis slides.

- 2. Release and remove mounting box top cover to gain access to H765 power supply assembly.

- 3. Loosen and remove cable clamp that secures the cables that are routed across the top of the power supply.

- 4. Loosen and remove power supply cover.

- 5. Rotate the mounting box in such a manner that the bottom of the mounting box faces away from the cabinet (box rotated 90 degrees).

- 6. Loosen and remove mounting box bottom cover to gain access to the power distribution board located between the power supply and the backplane.

# CAUTION

Do not remove the hinge screws (one on each side) located at the junction of the power supply and the module enclosure near the top side of the mounting box.

7. Remove four flat-head screws (no washers) located approximately 10 cm (4 in) from the bottom of the mounting box and at the junction of the power supply and the module enclosure assembly. The power supply can now be swiveled away from the module enclosure.

- 8. Locate the H744 +5 Vdc regulator assembly. This regulator is the second module from the right when viewing the bottom of the mounting box from the wire-wrap side of the back-plane.

- 9. Locate and remove the two mounting screws and washers located just to the left of the H744 Mate-N-Lok connector. There will be a green safety wire secured by one of these screws.

# NOTE A 90 degree offset Phillips-head screwdriver is required to remove these screws and attached hardware.

- 10. Locate and remove the last retaining screw and washer located on the back of the power supply and to the left of the H744 decal.

- 11. Release and remove the H744 Mate-N-Lok connector.

- 12. Remove the H744 regulator by sliding it out through the top of the power supply assembly. (Note that the mounting box may have to be rotated to accomplish removal.)

- 13. Replace the H744 regulator with the H7441 regulator (included in the upgrade kit).

- 14. Replace mounting hardware removed in steps 9 and 10. Do not connect the H7441 Mate-N-Lok connector at this time.

- 15. Release and remove the three Mate-N-Lok connectors connecting the remaining regulators to the power distribution board assembly:

- 16. Locate and remove the black ground wire soldered to the power distribution board (located near J16). Remove this ground wire from the power supply and the module enclosure assembly.

- 17. Remove the +5 V and ground fastons from the power distribution board (located near J14).

- 18. Release and disconnect Mate-N-Lok connector from J8 on the power distribution board.

- 19. Locate and remove four flat-head screws securing the power distribution board to the module enclosure assembly. These screws are located (two on each side) 5 cm (2 in) from the bottom of the mounting box and near the junction of the power supply and the module enclosure.

#### NOTE

#### The removal of these four screws will allow the removal of the power distribution panel which in turn will allow removal of all backplane Mate-N-Lok connectors.

- 20. Release and disconnect all backplane Mate-N-Lok connectors.

- 21. Release and disconnect two Mate-N-Lok connectors connecting the power distribution board to the power supply.

- 22. Remove the power distribution board.

- 23. Replace the power distribution board with the new 5410834-YA power distribution board (included in upgrade kit).

- 24. Reverse procedure (steps 22-14 and steps 7-1) to install the new power distribution board and to return system to normal.

•

**2.3.2 FP11-AU Logic Installation** Refer to Paragraph 2.2.1 and calculate +5 Vdc current drain and system configuration.

# CHAPTER 3 REVIEW OF FLOATING-POINT NUMBERS

#### 3.1 INTRODUCTION

This chapter briefly outlines some fundamentals of floating-point arithmetic. It provides useful background for more advanced topics in later chapters. The reader already familiar with floating-point numbers and arithmetic may skip this chapter and continue to Chapter 4 for a discussion of FP11-A data formats.

## 3.2 INTEGERS

All data within a computer system can be represented in integer form. The numbers that can be represented in a 16-bit machine range in magnitude from  $000000_8$  to  $177777_8$  (or from  $0_{10}$  to  $65,536_{10}$ ). However, this presents problems with integer representation. A number between 1 and 2 (for example) or numbers greater than  $65,536_{10}$  can not be represented. Thus, integer representation imposes an *accuracy* and a *range* limitation.

These limitations are imposed by the stationary position of the *radix point* (e.g., the decimal point in base 10 notation or the binary point in base 2 notation). An integer's radix point is usually omitted in integer representation because it always marks the integer's least significant place. That is, there are never any digits to the right of an integer's radix point. For this reason, an integer is sometimes called a *fixed-point* number.

Integer notation, however, can be modified to overcome the range and accuracy limitations imposed by the fixed radix point. This is accomplished through the use of *floating-point* notation.

#### **3.3 FLOATING-POINT NUMBERS**

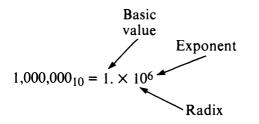

Floating-point numbers, unlike integers, have no position restrictions imposed on their radix points. A popular type of floating-point representation is called scientific notation. With scientific notation, a floating-point number is represented by some basic value multiplied by the radix raised to some power.

#### Example

3-1

There are many ways to represent the same number in scientific notation, as shown in the example below.

$512. = 51200. \times 10^{-2}$ = 5120. × 10^{-1} = 512. × 10^{0} = 51.2 × 10^{1} = 5.12 × 10^{2} = .512 × 10^{3}

The convention chosen for representing floating-point numbers with scientific notation in the FP11-A requires the radix point to always be to the left of the most significant digit in the basic value (e.g., .512  $\times$  10<sup>3</sup> in the above example). This modified basic value is called a fraction.

More examples of scientific notation are shown below.

| Decimal<br>No. | Decimal<br>Scient. No. | Octal<br>Scient. No.   | Binary<br>Scient. No.   |

|----------------|------------------------|------------------------|-------------------------|

| 64             | $0.64 \times 10^{2}$   | $0.1 \times 8^{3}$     | $0.1 \times 2^7$        |

| 33             | $0.33 \times 10^{2}$   | $0.41 \times 8^{2}$    | $0.100001 \times 2^{6}$ |

| 1/2            | $0.5 \times 10^{0}$    | $0.4 \times 8^{\circ}$ | $0.1 \times 2^{0}$      |

| 1/16           | $0.625 \times 10^{-1}$ | $0.4 \times 8^{-1}$    | 0.1 × $2^3$             |

Note that in each of the examples above, only significant digits are retained in the final result and the radix point is always (by convention) to the left of the most significant digit. Establishing the radix point in a number whose basic value is greater than or equal to 1 is accomplished by shifting the number to the right until the most significant digit is to the right of the radix point. Each right shift causes the exponent to be incremented by 1. Similarly, establishing the radix point in a number whose basic value is greater than or equal to 3 shifting the radix point in a number whose basic value is between 1 and 0 (i.e., a fraction) is accomplished by shifting the number to the left until all leading 0s are eliminated. Each left shift causes the exponent to be decremented by 1.

To summarize, the value of the number remains constant if its exponent is incremented for each right shift of the basic value and decremented for each left shift. The representation for floating-point fractions in the FP11-A is one in which all nonsignificant leading 0s have been removed. The process used to obtain this representation is called *normalization*, which is explained in more detail in Paragraph 3.4.

# 3.4 NORMALIZATION

In digital computers, the number of bits in a fraction is limited. Retention of nonsignificant leading 0s decreases accuracy by taking places that could be filled by significant digits. For this reason, a process called normalization is used in the FP11-A. The normalization process consists of testing the fraction for leading 0s and left-shifting it until it is in the form  $0.1 \ldots$ . The exponent is accordingly decremented by the number of left shifts of the fraction. This ensures that the normalized number retains equivalence with the original number. Since digits to the right of the binary point are weighted with inverse powers of 2 (i.e., 1/2, 1/4,  $1/8 \ldots$ ), the smallest normalized fraction is 1/2 ( $0.10000 \ldots$ ). The largest normalized fraction is  $0.11111 \ldots$ . Figure 3-1 shows an unnormalized fraction that must be left-shifted six places to be normalized. The exponent is decremented by six to maintain equivalence with the original number.

Figure 3-1 Normalization

**Problem A** – Represent the number  $75_{10}$  as a binary normalized floating-point number.

- 1. Integer conversion  $75_{10} = 1001011_2$

- 2. Convert to floating-point form  $1001011.0 \times 2^0 = 0.1001011 \times 2^7$

Fraction = 0.1001011Exponent = 111

**Problem B** – Represent the number  $0.25_{10}$  as a binary normalized floating-point number.

- 1. Integer conversion  $0.25_{10} = 0.01_2$

- 2. Convert to floating-point form  $0.01 \times 2^0 = 0.1 \times 2^{-1}$

Fraction = 0.1Exponent = -1

#### 3.5 FLOATING-POINT ADDITION AND SUBTRACTION

In order to perform floating-point addition or subtraction, the exponents of the two floating-point numbers involved must be aligned or equal. If they are not aligned, the fraction with the smaller exponent is shifted right until they are. Each shift to the right is accompanied by an incrementation of the associated exponent. When the exponents are aligned or equal, the fractions can then be added or subtracted. The exponent value indicates the number of places the binary point is to be moved to obtain the integer representation of the number.

In the example below, the number  $7_{10}$  is added to the number  $40_{10}$  using floating-point representation. Note that the exponents are first aligned and then the fractions are added; the exponent value dictates the final location of the binary points.

+0.101 000 000 000 000  $\times 2^6 = 50_8 = 40_{10}$ +0.111 000 000 000 000  $\times 2^6 = 7_8 = 7_{10}$  1. To align exponents, shift the fraction with the smaller exponent three places to the right and increment the exponent by 3, and then add the two fractions.

+0.101 000 000 000  $\times 2^6 = 50_8 = 40_{10}$ +0.000 111 000 000 000  $\times 2^6 = 7_8 = 7_{10}$ +0.101 111 000 000 000  $\times 2^6 = 57_8 = 47_{10}$

2. To find the integer value of the answer, move the binary point six places to the right.

## 3.6 FLOATING-POINT MULTIPLICATION AND DIVISION

In floating-point multiplication, the fractions are multiplied and the exponents are added. For floating-point division, the fractions are divided and the exponents are subtracted.

There is no requirement to align the binary point in floating-point multiplication or division.

#### **Example:**

Multiply  $7_{10}$  by  $40_{10}$ .

.1000110000000 X 2 (Result and aly in normalized to

2. Move the binary point nine places to the right.

$$\underbrace{\overset{4}{100011000},00000}_{100011000} = 430_8 = 280_{10}$$

#### Example:

Divide  $15_{10}$  by  $5_{10}$ .

1.  $.1111000 \times 24$

$.1010000 \times 2^{3}$

1.010000 ).1111000 =

- 2. Exponent: 4 3 = 1

- 3. Result:  $1.100000 \times 2$

Normalized Result: .1100000 × 2<sup>2</sup> Normalized Fraction Normalized Exponent

Move binary point two places to the right.

$.11.00000 = 3_8 = 3_{10}$

1

# CHAPTER 4 DATA FORMATS

## 4.1 INTRODUCTION

The FP11-A requires its input data (operands) to be formatted. Formatting allows the FP11-A to process operands in a meaningful way and produce correct results. There are four different formats for operands input to the FP11-A: short-integer format (I), long-integer format (L), single-precision format (F), and double-precision format (D).

Output data from the FP11-A is also formatted. This output data is in the form of:

- 1. FP11-A status information and FP11-A exception information required by the CPU

- 2. Data sent to memory (via the CPU), which must be in I, L, F, or D format.

This chapter describes the FP11-A data formats. It is assumed that the reader is familiar with 2's complement notation.

#### 4.2 FP11-A INTEGER FORMATS

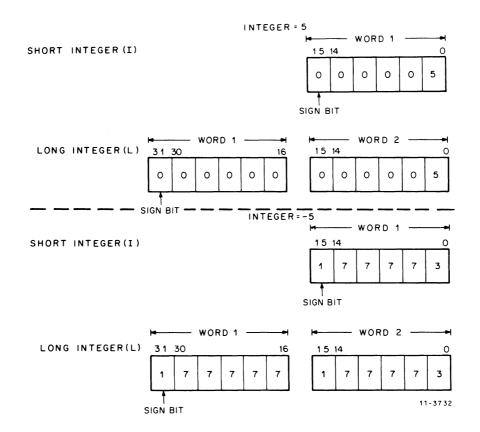

There are two integer formats, short (I) and long (L). The short-integer format is 16 bits long and the long-integer format is 32 bits long. Data words (operands) in integer format are represented in 2's complement notation. In both I and L formats, the most significant bit of the data word is the sign bit. Figure 4-1 shows the integers 5 and -5 in both I and L formats.

Figure 4-2 illustrates the formats in which integers are arranged *in memory*. Integers sent to memory must be in one of these formats. Integers received by the FP11-A are arranged and manipulated according to the type of instruction being executed. Refer to Paragraphs 5.3.11 and 5.3.12 for descriptions of the ways in which incoming integers are manipulated during the load exponent and load convert integer-to-floating instructions, respectively.

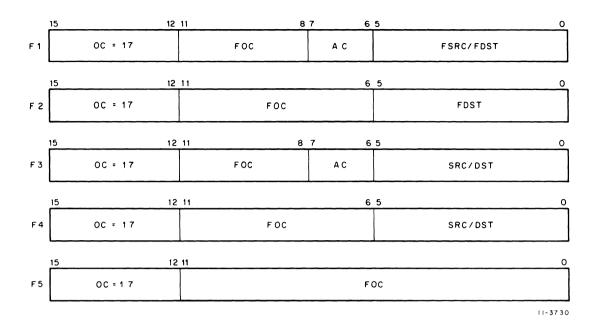

# 4.3 FP11-A FLOATING-POINT FORMATS

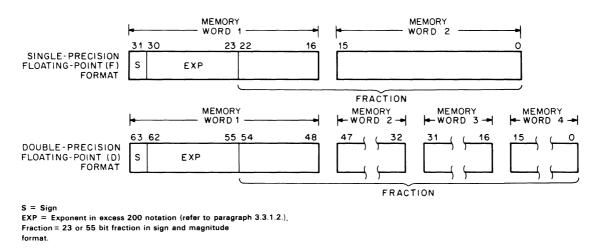

There are two floating-point formats, single-precision (F) and double-precision (D). The single-precision format is 32 bits long and the double-precision format is 64 bits long. Figure 4-2 shows that the most significant bit is the sign of the fraction (and the floating-point number being represented). The next 8 bits contain the value of the exponent, expressed in excess 200 notation (Paragraph 4.3.1.2). The remaining bits (23 for single-precision, 55 for double-precision) contain the fraction. The fraction and its associated sign bit are expressed in sign and magnitude notation (Paragraph 4.3.1.1).

#### 4.3.1 FP11-A Floating-Point Data Word

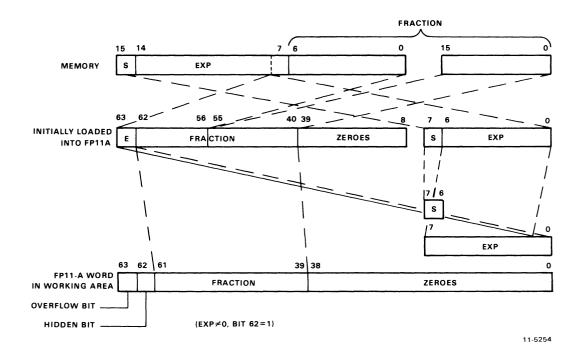

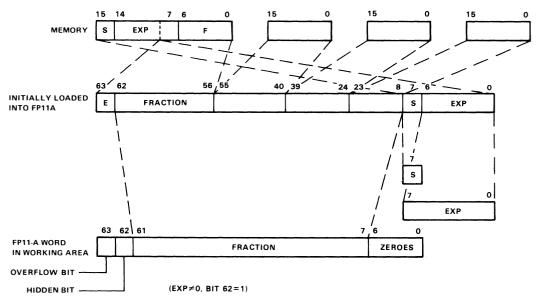

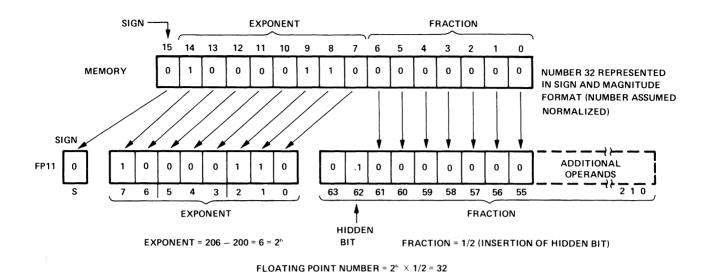

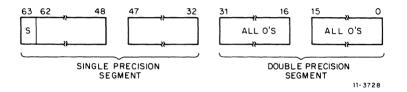

Figure 4-3 illustrates the formats in which floating-point numbers are arranged *in memory*. Floating-point numbers sent to memory must be in one of these formats. Floating-point numbers received by the FP11-A are arranged as illustrated in Figure 4-4.

Figure 4-1 Integer Formats

MA-0280

Figure 4-2 Floating-Point Data Formats

#### a. Single Precision

11-5255

b. Double Precision

Figure 4-3 Floating-Point Data Words

FLOATING POINT NUMBER =  $2^{-1} \times 7/8 = 7/16$

MA-1448

Figure 4-4 Interpretation of Floating-Point Numbers

The sign bit, exponent bits, and fraction bits in the FP11-A data word have the same values as the data word in memory. Note, however, that the FP11-A data word has more bits than its counterpart in memory. This is because the FP11-A has provisions for generating an overflow bit and a "hidden" bit.

For purposes of discussion, the FP11-A data word can be thought of as being divided into two major parts:

- 1. A fraction, with its associated sign bit, hidden bit, and overflow bit.

- 2. An exponent.

**4.3.1.1** Floating-Point Fraction – The fraction is expressed in sign and magnitude notation. The following simple example illustrates the idea behind sign and magnitude notation.

|    | 2's Complement<br>Notation | Sign and Magnitude Notation |

|----|----------------------------|-----------------------------|

| +2 | 000010                     | Sign Magnitude              |

| -2 | 111110                     | Sign Magnitude              |

Only a change of sign bit is required to change the sign of a number in sign and magnitude notation. Note that a positive number is the same in both notations.

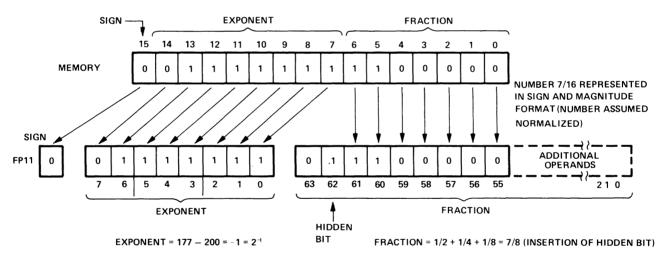

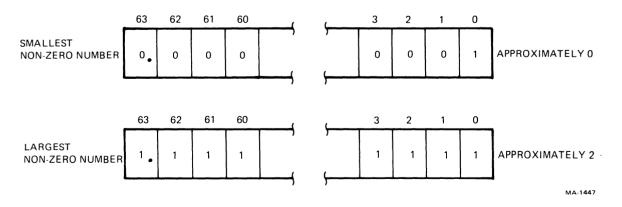

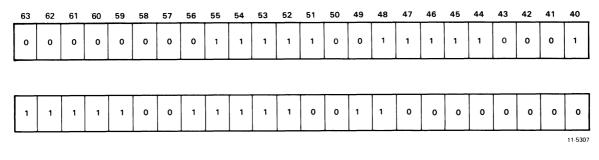

Unnormalized floating-point fractions have a range from approximately 0 through 2 as shown in Figure 4-5. The FP11-A, however, normalizes all unnormalized fractions. That is, the fractions are adjusted such that there is a 0 to the left of the binary point (bit 63) and a 1 to the right of the binary point (bit 62). Thus, normalized fractions range in magnitude from 0.1000... to 0.1111 or from 1/2 to approximately 1.

Figure 4-5 Unnormalized Floating-Point Fraction

The fraction overflow bit (bit 63) is set during certain arithmetic operations. For example, during addition, certain sums will produce an overflow such as  $0.1000 \dots + 0.100 \dots$  which yields  $1.000 \dots$ . This result must be normalized, so the FP11-A right-shifts the fraction one place and increases the exponent by one.

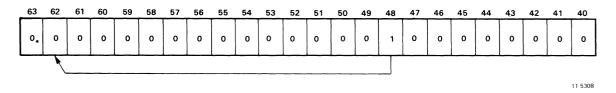

Bit 62 is called the hidden bit. Recall that since fractions are normalized by the FP11-A, the bit immediately to the right of the binary point (bit 62) is always a 1. This bit is dropped when a fraction is sent to memory and appended when a fraction is received from memory. This procedure allows one extra bit of significance in floating-point fraction representation.

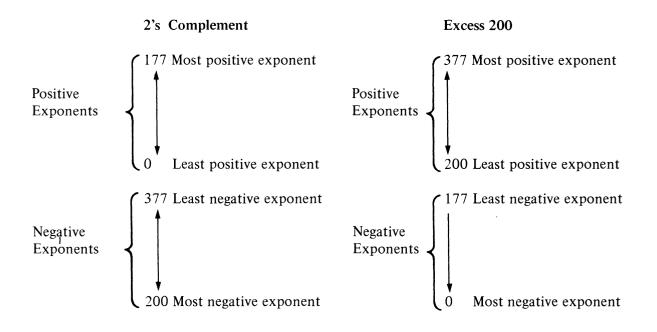

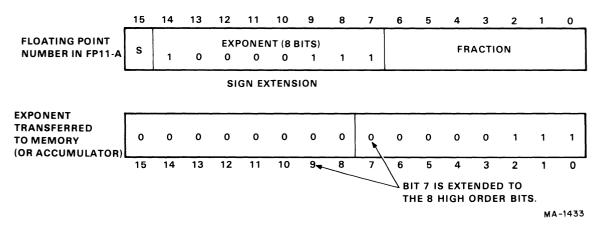

**4.3.1.2** Floating-Point Exponent – The 8-bit floating-point exponent is expressed in excess 200 notation. The chart below illustrates the relationship between exponents in 2's complement notation and exponents in excess 200 notation.

Note that an exponent in excess 200 notation is obtained by simply adding 200 to the exponent in 2's complement notation. Thus, 8-bit exponents in excess 200 notation range from 0 to 377 (or from -200 to +177). A number with an exponent of -200 is treated by the FP11-A as 0.

For example, the number  $0.1_2$  is actually  $0.1 \times 2^0$ , and the exponent is represented as 10 000 000 because  $200_8$  represents an exponent of zero. Figure 3-5 illustrates the range of floating-point numbers that can be handled by the FP11-A. For simplicity, a fraction length of only three bits is shown.

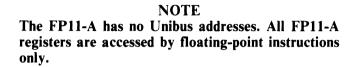

# 4.4 FP11-A PROGRAM STATUS REGISTER

The FP11-A contains a resident program status register that contains the floating-point condition codes (carry, overflow, zero, and negative) that can be copied into the central processor. In other words, FN, FZ, FV, and FC can be copied into the CPU's N, Z, V, and C condition codes, respectively. The program status register also contains 3 mode bits and additional bits to enable various interrupt conditions. Figure 4-6 shows the layout of the program status register. Each bit shown in the figure is described in Table 4-1.

Figure 4-6 FP11-A Status Register Format

| Table 4-1 | FP11-A | Status | Register |

|-----------|--------|--------|----------|

|-----------|--------|--------|----------|

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                     |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | FER      | This bit indicates an error condition of the FP11-A.                                                                                                                                                                                                                                                         |

| 14  | FID      | Floating Interrupt Disable – All interrupts by the FP11-A are disabled when this bit is on. Primarily for maintenance use. Normally clear.                                                                                                                                                                   |

| 13  | Not Used |                                                                                                                                                                                                                                                                                                              |

| 12  | Not Used |                                                                                                                                                                                                                                                                                                              |

| 11  | FIUV     | Floating Interrupt on Undefined Variable – When this bit is set and a $-0$ is obtained from memory, an interrupt occurs. If the bit is not set, $-0$ can be loaded and stored; however, any arithmetic operation treats it as if it were a positive 0.                                                       |

| 10  | FIU      | Floating Interrupt on Underflow – When this bit is set, an underflow condition causes a floating underflow interrupt. The result of the operation causing the interrupt is correct except for the exponent, which is off by $400_8$ . If the FIU is not set and underflow occurs, the result is set to zero. |

| Bit | Name                  | Function                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | FIV                   | Floating Interrupt on Overflow – When this bit is set, floating overflow causes an interrupt. The result of the operation causing the interrupt is correct except for the exponent, which is off by $400_8$ . If the FIV bit is not set, the result of the operation is the same; the only difference is that the interrupt does not occur.                                                                          |

| 8   | FIC                   | Floating Interrupt on Integer Conversion Error – When this bit is set<br>and the store convert floating-to-integer instruction causes FC to be set<br>(indicating a conversion error), an interrupt occurs. When a conversion<br>occurs, the destination register is cleared and the source register is un-<br>touched. When FIC is reset, the result of the operation is the same;<br>however, no interrupt occurs. |

| 7   | FD                    | Double-Precision Mode Bit – This bit, when set, specifies double-precision format and, when reset, specifies single-precision format.                                                                                                                                                                                                                                                                                |

| 6   | FL                    | Long-Precision Integer Mode Bit – This bit is employed during con-<br>version between integer and floating-point format. If set, double-preci-<br>sion 2's complement integer format of 32 bits is specified; if reset,<br>single-precision 2's complement integer format of 16 bits is specified.                                                                                                                   |

| 5   | FT                    | Truncate Bit – This bit, when set, causes the result of any floating-point operation to be truncated rather than rounded.                                                                                                                                                                                                                                                                                            |

| 4   | Not Used              |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3-0 | FN, FZ, FV,<br>and FC | These bits are the four floating-point condition codes, which can be<br>loaded in the CPU's N, Z, V, and C condition codes, respectively. This<br>is accomplished by the copy floating condition codes (CFCC) instruc-<br>tion. To determine how each instruction affects the condition codes,<br>refer to Table 5-1.                                                                                                |

Table 4-1 FP11-A Status Register (Cont)

# 4.5 PROCESSING OF FLOATING-POINT EXCEPTIONS

Location 244 is the interrupt vector used to handle all floating-point interrupts. A total of six possible interrupts can occur. These possible interrupt exceptions are encoded in the FP11-A exception code (FEC) register. The interrupt exception codes represent an offset into a dispatch table, which routes the program to the right error handling routine. The dispatch table is a function of the software. The FEC for each exception is briefly described in Table 4-2.

Refer to the *PDP-11/04*, 34, 45, 45 Processor Handbook for further details concerning FP11-A exceptions.

In addition to the FEC register, the CPU contains a 16-bit floating exception address (FEA) register, which stores the address of the last floating-point instruction that caused a floating-point exception.

| FP11-A<br>Exception<br>Code | Definition                                                                            |

|-----------------------------|---------------------------------------------------------------------------------------|

| 2                           | Floating Op Code Error – The FP11-A causes an interrupt for an erroneous op code      |

| 4                           | Floating Divide by Zero – Division by zero causes an inter-<br>rupt if FID is not set |

| 6                           | Floating (or Double) Integer Conversion Error                                         |

| 10                          | Floating Overflow                                                                     |

| 12                          | Floating Underflow                                                                    |

| 14                          | Floating Undefined Variable                                                           |

# Table 4-2 FP11-A Exception Codes

NOTE

The traps for exception codes 6, 10, 12, and 14, can be enabled in the FP11-A program status register. All traps are disabled if FID is set.

# CHAPTER 5 FLOATING-POINT INSTRUCTIONS

# 5.1 FLOATING-POINT ACCUMULATORS

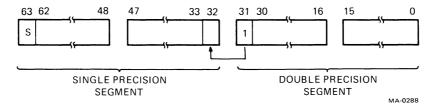

The FP11-A contains six general-purpose accumulators (AC0-AC5). These accumulators are 64-bit read/write scratchpad memories with non-destructive readout.

Each accumulator is interpreted as being either 32 or 64 bits long, depending on the instruction and the FP11-A status (Chapter 4). If an accumulator is interpreted as being 64 bits long, 64 bits of data occupy the entire accumulator. If an accumulator is interpreted as being 32 bits long, 32 bits of data occupy only the left-most 32 bits of an accumulator as shown in Figure 5-1.

The floating-point accumulators are used in numeric calculations and interaccumulator data transfers. AC0-AC3 are used for all data transfers between the FP11-A and the CPU or memory.

Figure 5-1 Floating-Point Accumulators

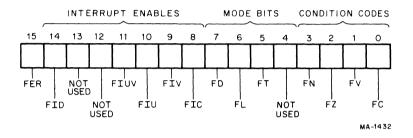

# 5.2 INSTRUCTION FORMATS

An FP11-A instruction must be in one of five formats. These formats are summarized in Figure 5-2.

The 2-bit AC field (bits 6 and 7) allows selection of scratchpad accumulators 0 through 3 only.

If address mode 0 is specified with formats F1 or F2, bits 2–0 are used to select a floating-point accumulator. Only accumulators 5–0 can be specified in mode 0. If 6 or 7 is specified in bits 2–0 in mode 0, the FP11-A traps if floating-point interrupts are enabled (FID = 0). The FEC will indicate an illegal op code error (exception code 2).

Figure 5-2 Instruction Formats

The fields of the various instruction formats (as summarized in Table 5-1) are interpreted as follows.

| Mnemonic | Description                                                                                                                                                                                 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OC       | Operation Code – All floating-point instructions are designated by a 4-bit op code of $17_8$ .                                                                                              |

| FOC      | Floating Operating Code – The number of bits in this field varies with the format; the code is used to specify the actual floating-point operation.                                         |

| SRC      | Source – A 6-bit source field identical to that in the PDP-11 instruction.                                                                                                                  |

| DST      | Destination – A 6-bit destination field identical to that in a PDP-11 instruction.                                                                                                          |

| FSRC     | Floating Source – A 6-bit field used only in format F1. It is identical to SRC, except in mode 0 when it references a floating-point accumulator rather than a CPU general register.        |

| FDST     | Floating Destination – A 6-bit field used in formats F1 and F2. It is identical to DST, except in mode 0 when it references a floating-point accumulator instead of a CPU general register. |

| AC       | Accumulator – A 2-bit field used in formats F1 and F3 to specify FP11-A scratchpad accumulators 0–3.                                                                                        |

| Instruction<br>Format | Instruction                   | Mnemonic      |

|-----------------------|-------------------------------|---------------|

| F2                    | ABSOLUTE                      | ABSF FDST     |

|                       |                               | ABSD FDST     |

| F1                    | ADD                           | ADDF FSRC, AC |

|                       |                               | ADD FSRC, AC  |

| F2                    | CLEAR                         | CLRF FDST     |

| 12                    | CEDAIR                        | CLRD FDST     |

| F4                    | COMPARE                       | CMPF FSRC, AC |

| 1 4                   | COMTARE                       | CMPD FSRC, AC |

| F5                    | COPY FLOATING CONDITION CODES | CFCC          |

| F1                    | DIVIDE                        | DIVF FSRC, AC |

| 1.1                   | DIVIDE                        | DIVD FSRC, AC |

| F1                    | LOAD                          | LDF FSRC, AC  |

| ГІ                    |                               |               |

| F1                    | LOAD CONVERT                  | LDD FSRC, AC  |

| ГІ                    |                               | LDCFD FSRC, A |

| 53                    |                               | FDCDF FSRC, A |

| F3                    | LOAD CONVERT INTEGER          | LDCIF SRC, AC |

|                       |                               | LDCID SRC, AC |

|                       |                               | LDCLF SRC, AC |

|                       |                               | LDCLD SRC, AC |

| F3                    | LOAD EXPONENT                 | LDEXP SRC, AC |

| F4                    | LOAD FP11'S PROGRAM STATUS    | LDFPS SRC     |

| F1                    | MODULO                        | MODF FSRC, AC |

|                       |                               | MODD FSRC, AG |

| F1                    | MULTIPLY                      | MULF FSRC, AC |

|                       |                               | MULD FSRC, AC |

| F2                    | NEGATE                        | NEGF FDST     |

|                       |                               | NEGD FDST     |

| F5                    | SET DOUBLE MODE               | SETD          |

| F5                    | SET FLOATING MODE             | SETF          |

| F5                    | SET INTEGER MODE              | SETI          |

| F5                    | SET LONG INTEGER MODE         | SETL          |

| F1                    | STORE                         | STF AC, FDST  |

|                       |                               | STD AC, FDST  |

| F1                    | STORE CONVERT                 | STCFD AC, FDS |

|                       |                               | STCDF AC, FDS |

| F3                    | STORE CONVERT                 | STCFI AC, DST |

|                       | FLOATING TO INTEGER           | STCFL AC, DST |

|                       |                               | STCDI AC, DST |

|                       |                               | STCDL AC, DST |

| F3                    | STORE EXPONENT                | STEXP AC, DST |

| F4                    | STORE FP11'S PROGRAM STATUS   | STEPS DST     |

| F4                    | STORE FP11'S STATUS           | STST DST      |

| F1                    | SUBTRACT                      | SUBF FSRC, AC |

| * 1                   |                               |               |

| F2                    | TEST                          | SUBD FSRC, AC |

| 1 2                   |                               | TSTF FDST     |

|                       |                               | TSTD FDST     |

Table 5-1

Format of FP11-A Instructions

### 5.3 INSTRUCTION SET

Table 5-2 contains the instruction set of the FP11-A. Some of the symbology may not be familiar. Therefore, a brief description follows.

1. A floating-point flip-flop, designated FD, determines whether single- or double-precision floating-point format is specified. If the flip-flop is cleared, single-precision is specified and is designated by F. If the flip-flop is set, double-precision is specified and is designated by D. Examples are NEGF, NEGD, and SUBD.

#### NOTE

Only the assembler or compiler differentiates between NEGF and NEGD or LDCID or LDCLD instructions. The Floating-point does not differentiate between the instructions but depends upon the value of FD and FL as usually controlled by SETD, SETF, SETC, and SETI instructions (i.e., LDCID  $\rightarrow$  SETI  $\rightarrow$  SETD  $\rightarrow$  LDCLD).

- 2. An integer flip-flop, designated FL, determines whether short-integer or long-integer format is specified. If the flip-flop is cleared, short-integer format is specified and is designated by I. If the flip-flop is set, long-integer format is specified and is designated by L. Examples are SETI and SETL.

- 3. Several convert-type instructions use the symbology defined below.

C<sub>IL,FD</sub> – Convert integer to floating

C<sub>FD,IL</sub> – Convert floating to integer

$C_{F,D}$  or  $C_{D,F}$  – Convert single-floating to double-floating or convert double-floating to single-floating

- 4. UPLIM is defined as the largest possible number that can be represented in floating-point format. This number has an exponent of 377 (excess 200 notation) and a fraction of all 1s. Note the UPLIM is dependent on the format specified. LOLIM is defined as the smallest possible number that is not identically 0. This number has an exponent of 001 and a fraction of all 0s except for the hidden bit.

- 5. The following conventions are used when referring to address locations.

(xxxx) = the contents of the location specified by xxxx ABS (address) = absolute value of (address) EXP (address) = exponent of (address) in excess 200 notation

6. Some of the octal codes listed in Table 5-2 are in the form of mathematical expressions. These octal codes can be calculated as shown in the following examples.

#### **Example 1: LDFPS Instruction**

Mode 3, register 7 specified (F instruction format)

170100 + SRC SRC field is equal to 37 Basic op code is 170100 SRC and basic op code are added to yield 170137.

### **Example 2: LDF Instruction**

AC2, mode 2, and register 6 specified (F1 instruction format).

172400 + C \* 100 + FSRCAC = 2 2 \* 100 = 200 172400 + 200 = 172600FSRC is equal to 26 172600 + 26 + 172626

7. AC v 1 means that the accumulator field (bits 6 and 7 in formats F1 and F3) is logically ORed with 01.

#### Example:

Accumulator field = bits 6 and 7 = AC2 = 10.  $AC \vee 1 = 11$ .

The information in Table 5-2 is expressed in symbolic notation to provide the reader with a quick reference to the function of each instruction. The following paragraphs supplement the information in Table 5-2.

| Mnemonic                       | Instruction Description                                                                                                                                                                                                                                                                                                                                                                                       | Octal Code                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| ABSF FDST<br>Absd Fdst         | Absolute<br>FDST $\leftarrow$ minus (FDST) if FDST $\leq$ 0; other-<br>wise FDST $\leftarrow$ (FDST)<br>FC $\leftarrow$ 0<br>FV $\leftarrow$ 0<br>FZ $\leftarrow$ 1 if exp (FDST) = 0; otherwise FZ $\leftarrow$ 0<br>FN $\leftarrow$ 0                                                                                                                                                                       | 170600+FDST<br>F2 Format        |

| ADDF FSRC, AC<br>ADDD FSRC, AC | Floating Add<br>$AC \leftarrow (AC) + (FSRC) \text{ if }  AC  + (FSRC)$<br>$\leq \text{LOLIM}; \text{ otherwise } AC \leftarrow 0$<br>$FC \leftarrow 0$<br>$FV \leftarrow 1 \text{ if }  AC  \geq \text{UPLIM}; \text{ otherwise } FV \leftarrow 0$<br>$FZ \leftarrow \text{ if } (AC) = 0; \text{ otherwise } FZ \leftarrow 0$<br>$FN \leftarrow 1 \text{ if } (AC) < 0; \text{ otherwise } FN \leftarrow 0$ | 172000+AC*100+FSRC<br>F1 Format |

| CLRF FDST<br>CLRD FDST         | Clear<br>FDST $\leftarrow 0$<br>FC $\leftarrow 0$<br>FV $\leftarrow 0$<br>FZ $\leftarrow 1$<br>FN $\leftarrow 0$                                                                                                                                                                                                                                                                                              | 170400+FDST<br>F2 Format        |

| Table 5-2         FP11-A Instruction Set | Table 5-2 | 2 FP11-4 | <b>A</b> Instruction | Set |

|------------------------------------------|-----------|----------|----------------------|-----|

|------------------------------------------|-----------|----------|----------------------|-----|

| Mnemonic                           | Instruction Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Octal Code                                                                                                                                                                        |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMPF FSRC, AC<br>CMPD FSRC, AC     | Floating Compare<br>FC $\leftarrow 0$<br>FV $\leftarrow 0$<br>FZ $\leftarrow 1$ if (FSRC) - (AC) = 0; otherwise<br>FZ $\leftarrow 0$<br>FN $\leftarrow 1$ if (FSRC) - (AC) < 0; otherwise<br>FN $\leftarrow 0$                                                                                                                                                                                                                                                                | 173400+AC*100+FSRC<br>F1 Format                                                                                                                                                   |

| CFCC                               | Copy Floating Condition Codes<br>C ← FC<br>V ← FV<br>Z ← FZ<br>N ← FN                                                                                                                                                                                                                                                                                                                                                                                                         | 170000<br>F5 Format                                                                                                                                                               |

| DIVF FSRC, AC<br>DIVD FSRC, AC     | Floating Divide<br>$AC \leftarrow (AC)/(FSRC) \text{ if }  (AC)/(FSRC) $<br>$\ge LOLIM; \text{ otherwise } AC \leftarrow 0$<br>$FC \leftarrow 0$<br>$FV \leftarrow 1 \text{ if }  AC  \ge UPLIM; \text{ otherwise } FV \leftarrow 0$<br>$FZ \leftarrow 1 \text{ if } EXP (AC) = 0; \text{ otherwise } FZ \leftarrow 0$<br>$FN \leftarrow 1 \text{ if } (AC) < 0; \text{ otherwise } FN \leftarrow 0$                                                                          | 174400+AC*100+FSRC<br>F1 Format                                                                                                                                                   |

| LDF FSRC, AC<br>or<br>LDD FSRC, AC | Floating Load<br>$AC \leftarrow (FSRC)$<br>$FC \leftarrow 0$<br>$FV \leftarrow 0$<br>$FZ \leftarrow 1$ if $(AC) = 0$ ; otherwise $FZ \leftarrow 0$<br>$FN \leftarrow 1$ if $(AC) < 0$ ; otherwise $FN \leftarrow 0$                                                                                                                                                                                                                                                           | 172400+AC*100+FSRC<br>F1 Format                                                                                                                                                   |

| LDCDF FSRC, AC<br>LDCFD FSRC, AC   | Load Convert Double-to-Floating or<br>Floating-to-Double<br>$AC \leftarrow C_{F,D}$ or $C_{D,F}$ (FSRC)<br>$FC \leftarrow 0$<br>$FV \leftarrow 1$ if $ AC  \ge UPLIM$ ; otherwise<br>$FV \leftarrow 0$<br>$FZ \leftarrow 1$ if $(AC) = 0$ ; otherwise $FZ \leftarrow 0$<br>$FN \leftarrow 1$ if $(AC) < 0$ ; otherwise $FN \leftarrow 0$                                                                                                                                      | <ul> <li>177400+AC*100+FSRC</li> <li>F1 Format</li> <li>F, D-single-precision to double-precision floating</li> <li>D, F-double-precision to single-precision floating</li> </ul> |

|                                    | If the current format is single-precision float-<br>ing-point (FD = 0), the source is assumed to<br>be a double-precision number and is con-<br>verted to single-precision. If the floating-trun-<br>cate bit is set, the number is truncated;<br>otherwise, it is rounded. If the current format<br>is double-precision (FD = 1), the source is as-<br>sumed to be a single-precision number and<br>loaded left-justified in the AC. The lower half<br>of the AC is cleared. |                                                                                                                                                                                   |

| Mnemonic                                                                                                                                                                                                                                         | Instruction Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Octal Code                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| LDCIF SRC, AC<br>LDCID SRC, AC<br>LDCLF SRC, AD<br>LDCLD SRC, AC<br>LDCIF = Single Integer<br>to Single Float<br>LDCID = Single Integer<br>to Double Float<br>LDCLF = Long Integer<br>to Single Float<br>LDCLD = Long Integer<br>to Double Float | Load and Convert from Integer to Floating<br>$AC \leftarrow C_{IL,FD}$ (SRC)<br>$FC \leftarrow 0$<br>$FV \leftarrow 0$<br>$FZ \leftarrow 1$ if (AC) = 0; otherwise $FZ \leftarrow 0$<br>$FN \leftarrow 1$ if (AC) < 0; otherwise $FN \leftarrow 0$<br>$C_{IL,FD}$ specifies conversion from a 2's com-<br>plement integer with precision I or L to a<br>floating-point number of precision F or D. If<br>integer flip-flop IL = 0, a 16-bit integer (I) is<br>double specified, and if IL = 1, a 32-bit in-<br>teger (L) is specified. If floating-point flip-flop<br>FD = 0, a 32-bit floating-point number (F) is<br>specified, and if $FD = 1$ , a 64-bit floating-<br>point number (D) is specified. If a 32-bit in-<br>teger is specified and addressing mode 0 or<br>immediate mode is used, the 16 bits of the<br>source register are left justified, and the re-<br>maining 16 bits are zeroed before the con-<br>version. | 177000+AC*100+SRC<br>F3 Format  |

| LDEXP SRC, AC                                                                                                                                                                                                                                    | Load Exponent<br>AC SIGN $\leftarrow$ (AC SIGN)<br>AC EXP $\leftarrow$ (SRC) + 200 only if ABS (SRC)<br>< 177<br>AC FRACTION $\leftarrow$ (AC FRACTION)<br>FC $\leftarrow 0$<br>FV $\leftarrow 1$ if (SRC) > 177; otherwise FV $\leftarrow 0$<br>FZ $\leftarrow 1$ if EXP (AC) = 0; otherwise FZ $\leftarrow 0$<br>FN $\leftarrow 1$ if (AC) < 0; otherwise FN $\leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 176400+AC*100+SRC<br>F3 Format  |

| LDFPS SRC                                                                                                                                                                                                                                        | Load FP11-A's Program Status Word<br>FPS ← (SRC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170100+SRC<br>F4 Format         |

| MODF FSRC, AC<br>MODD FSRC, AC                                                                                                                                                                                                                   | Floating Modulo<br>AC v 1 $\leftarrow$ integer part of (AC)*(FSRC)<br>AC $\leftarrow$ fractional part of (AC)*(FSRC)<br>- (AC v 1) if $ (AC)*(FSRC) \geq LOLIM or FIU = 1; otherwise AC \leftarrow 0FC \leftarrow 0FV \leftarrow 1 if  AC  \geq UPLIM; otherwise FV \leftarrow 0FZ \leftarrow 1 if (AC) = 0; otherwise FZ \leftarrow 0FN \leftarrow 1 if (AC) < 0; otherwise FN \leftarrow 0The product of AC and FSRC is 48 bits insingle-precision floating-point format or 59bits in double-precision floating-point format.The integer part of the product[(AC)*(FSRC)] is found and stored in AC v 1.$                                                                                                                                                                                                                                                                                                                        | 171400+AC*100+FSRC<br>F1 Format |

|                                                                                                                                                                                                                                                  | The fractional part is then obtained and<br>stored in AC. Note that multiplication by 10<br>can be done with zero error, allowing decimal<br>digits to be stripped off with no loss in preci-<br>sion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

Table 5-2

FP11-A Instruction (Cont)

| Mnemonic                       | Instruction Description                                                                                                                                                                                                                                                                                                                                                                              | Octal Code                      |