# PDP-8/I MAINTENANCE MANUAL VOLUME I

1st Printing October 1968 2nd Printing March 1968 3rd Printing May 1969 4th Printing July 1969 5th Printing March 1970

Copyright © 1968, 1969, 1970 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP PDP FOCAL

DIGITAL

COMPUTER LAB

# CONTENTS

|       | ;                                      | Page         |

|-------|----------------------------------------|--------------|

|       | CHAPTER 1 INTRODUCTION AND DESCRIPTION |              |

|       | INTRODUCTION AND DESCRIPTION           |              |

| 1.1   | Introduction                           | 1-1          |

| 1.2   | Description                            | 1-1          |

| 1.3   | Pertinent Documents                    | 1-2          |

| 1.4   | Abbreviations                          | 1-2          |

|       | CHAPTER 2 INSTALLATION                 |              |

| 2.1   | Space Requirements                     | 2-1          |

| 2.2   | Environmental Requirements             | 2-2          |

| 2.3   | Power Requirements                     | 2-2          |

| 2.4   | Cable Requirements                     | 2-6          |

| 2.5   | Installation Procedure                 | 2-6          |

| 2.6   | Internal Option Installation           | 2-8          |

| 2.7   | System Configurations                  | 2-8          |

| 2.8   | I/O Interface                          | 2-8          |

| 2.8.1 | I/O Bus Signal                         | 2-8          |

| 2.8.2 | I/O Cables                             | 2-8          |

| 2.8.3 | Logic Levels and Level Converters      | 2-8          |

| 2.8.4 | Interface Signal Connections           | 2-9          |

|       | CHAPTER 3 OPERATION                    |              |

| 3.1   | Controls and Indicators                | 3-1          |

| 3.1.1 | Computer                               | 3-1          |

| 3.1.2 | Teletype                               | 3 <b>-</b> 6 |

| 3.2   | Operating Procedures                   | 3-6          |

| 3.2.1 | Common Procedures                      | 3-6          |

| 3.2.2 | Manual Loading Procedures              | 3-6          |

| 3.2.3 | Teletype Loading Procedures            | 3-6          |

| 3.2.4 | Off-Line Teletype Procedures           | 3-8          |

# CONTENTS (Cont)

|         |                               | Page |

|---------|-------------------------------|------|

|         | CHAPTER 4<br>THEORY           |      |

| SECTION | I: BLOCK DIAGRAM DISCUSSION   |      |

| 4.1     | Registers                     | 4-1  |

| 4.1.1   | Accumulator (AC)              | 4-1  |

| 4.1.2   | Link (L)                      | 4-1  |

| 4.1.3   | Program Counter (PC)          | 4-1  |

| 4.1.4   | Memory Address Register (MA)  | 4-1  |

| 4.1.5   | Memory Buffer Register (MB)   | 4-1  |

| 4.1.6   | Sense Register (SENSE or MEM) | 4-1  |

| 4.1.7   | Instruction Register (IR)     | 4-1  |

| 4.1.8   | Switch Register (SR)          | 4-3  |

| 4.2     | Major Register Gating Network | 4-3  |

| 4.3     | Timing and Control Elements   | 4-3  |

| 4.3.1   | Timing Elements               | 4-3  |

| 4.3.2   | Control Elements              | 4-3  |

| 4.4     | Input/Output                  | 4-3  |

| 4.5     | Memory                        | 4-4  |

| 4.5.1   | Core Array                    | 4-4  |

| 4.5.2   | Memory Control                | 4-4  |

| 4.5.3   | Address Selection             | 4-4  |

| 4.5.4   | Inhibit Drivers               | 4-4  |

| 4.5.5   | Sense Amplifiers              | 4-4  |

| SECTION | II: GENERAL THEORY            |      |

| 4.6     | Time States/Time Pulses       | 4-4  |

| 4.7     | Major States                  | 4-5  |

| 4.8     | Internal Data Flow            | 4-5  |

| 4.9     | Instructions                  | 4-5  |

| 4.9.1   | Memory Reference Instructions | 4-5  |

| 4.9.2   | Augmented Instructions        | 4-7  |

| 4.10    | Program Interrupt             | 4-12 |

| 4.10.1  | Instructions                  | 4-13 |

# CONTENTS (Cont)

|              |                                  | Page         |

|--------------|----------------------------------|--------------|

| SECTION III: | DETAILED MEMORY THEORY           |              |

| 4.11         | Overall Memory Theory            | 4-13         |

| 4.12         | Memory Operation                 | 4-13         |

| 4.12.1       | Memory Control                   | 4-13         |

| 4.12.2       | Read/Write                       | 4-15         |

| 4.12.3       | Address Selection                | 4-18         |

| SECTION IV:  | DETAILED PROCESSOR THEORY        |              |

| 4.13         | Flow Diagram Interpretation      | 4-19         |

| 4.14         | Timing                           | 4-21         |

| 4.14.1       | Manual Function Timing Generator | 4-21         |

| 4.14.2       | Manual Operations                | 4-21         |

| 4.14.3       | Time States                      | 4-24         |

| 4.15         | Major States                     | 4-26         |

| 4.16         | Internal Data Flow               | 4-29         |

| 4.16.1       | Source                           | 4-29         |

| 4.16.2       | Route                            | 4-29         |

| 4.16.3       | Destination                      | 4-29         |

| 4.17         | Operating Instructions           | 4-31         |

| 4.17.1       | Instructions                     | 4-31         |

| 4.17.2       | Memory Reference Instructions    | 4-31         |

| 4.17.3       | Direct/Indirect Addressing       | 4-38         |

| 4.17.4       | Augmented Instructions           | 4-39         |

|              | CHAPTER 5<br>MAINTENANCE         |              |

| 5.1          | Equipment                        | 5-1          |

| 5.2          | Programs                         | 5-1          |

| 5.3          | Preventive Maintenance           | 5-3          |

| 5.3.1        | Weekly Checks                    | 5-3          |

| 5.3.2        | Preventive Maintenance Tasks     | 5-3          |

| 5.4          | Corrective Maintenance           | 5 <b>-</b> 4 |

| 5.4.1        | Preliminary Investigation        | 5-4          |

| 5.4.2        | System Troubleshooting           | 5 <b>-</b> 4 |

| 5.4.3        | Logical Troubleshooting          | 5-5          |

# CONTENTS (Cont)

|       |                                              | Page        |

|-------|----------------------------------------------|-------------|

| 5.4.4 | Circuit Troubleshooting                      | 5-5         |

| 5.4.5 | Repairs and Replacement                      | 5-6         |

| 5.4.6 | Validation Tests                             | 5-7         |

| 5.4.7 | Recording                                    | 5 <b>-7</b> |

| 5.5   | Adjustments                                  | 5-8         |

| 5.5.1 | Power-Up Threshold Adjustment                | 5-8         |

| 5.5.2 | Memory Alignment Procedure                   | 5-8         |

| 5.6   | ASR33 Teleprinter and Control Maintenance    | 5-12        |

| 5.6.1 | Equipment                                    | 5-14        |

| 5.6.2 | Programs                                     | 5-14        |

| 5.6.3 | Preventive Maintenance                       | 5-14        |

| 5.6.4 | Corrective Maintenance                       | 5-15        |

| 5.7   | Spare Parts                                  | 5-17        |

| 5.8   | Mechanization Charts                         | 5-19        |

|       | ILLUSTRATIONS                                |             |

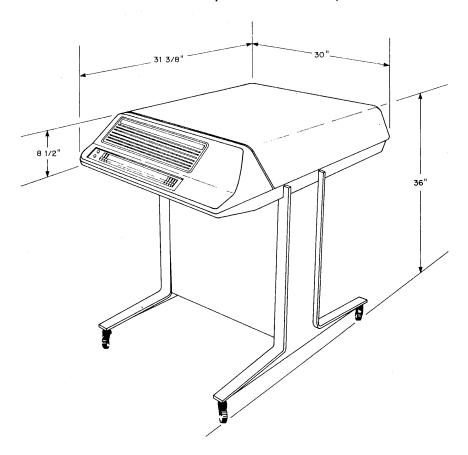

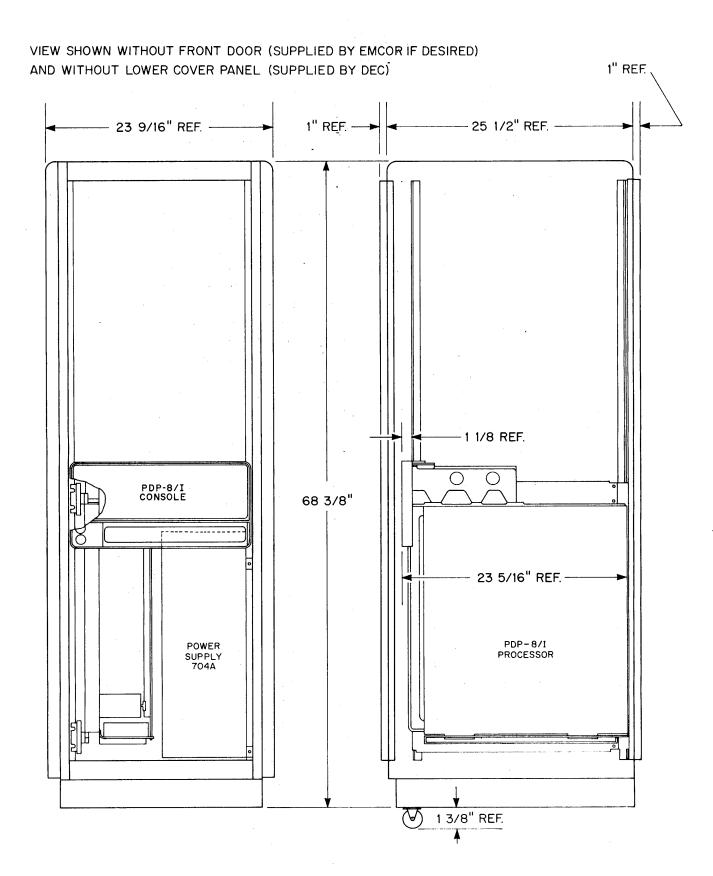

| 2-1   | PDP-8/I Pedestal Dimensions                  | 2-1         |

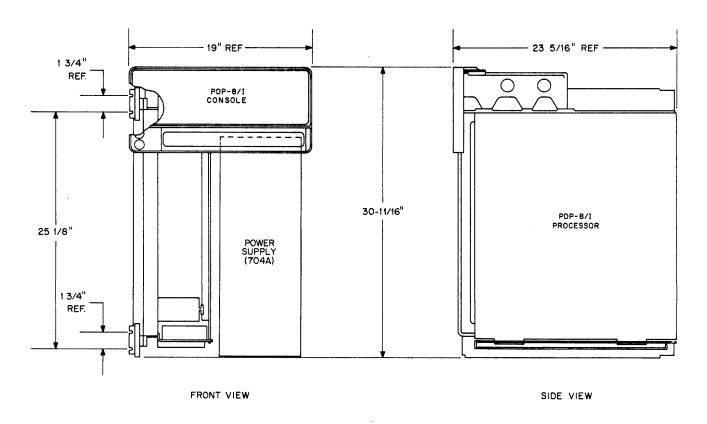

| 2-2   | Rack Mounted PDP-8/I Dimensions              | 2-2         |

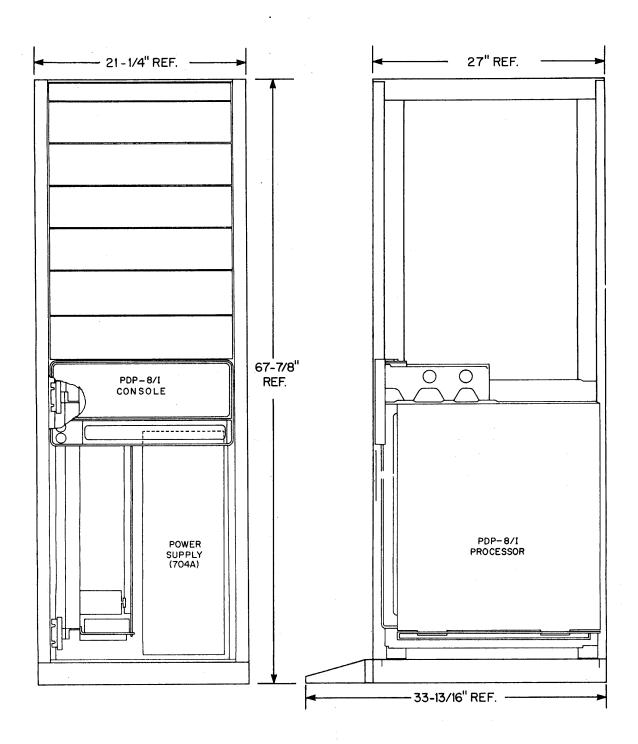

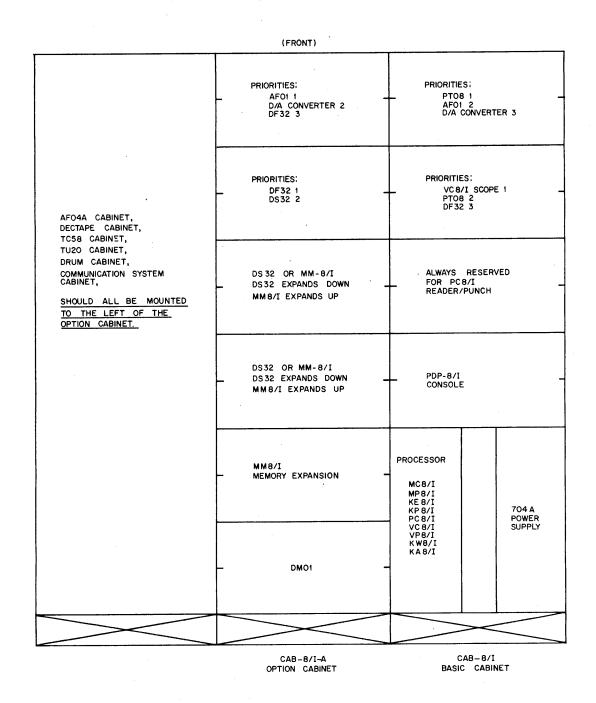

| 2-3   | PDP-8/I Installation in Standard DEC Cabinet | 2-3         |

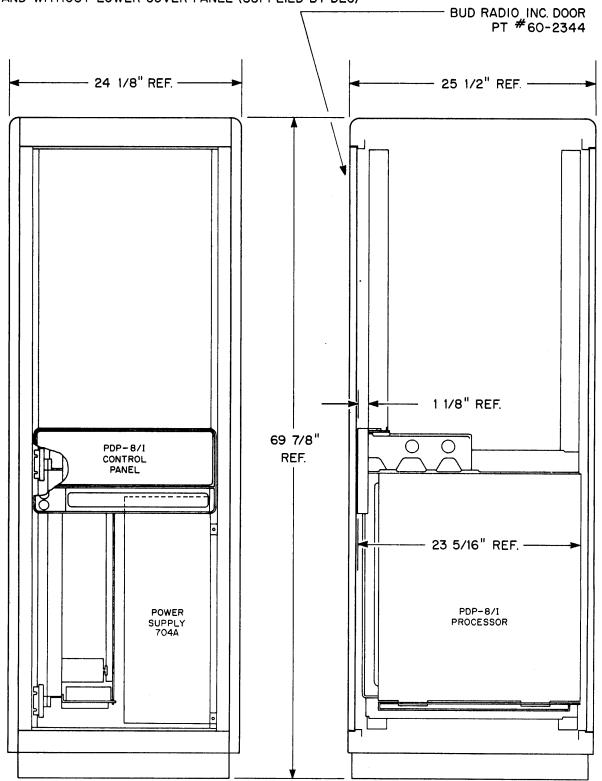

| 2-4   | PDP-8/I Installation in Bud Cabinet          | 2-4         |

| 2-5   | PDP-8/I Installation in Emcor Cabinet        | 2-5         |

| 2-6   | System Configurations                        | 2-7         |

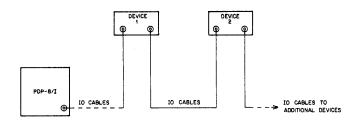

| 2-7   | I/O Bus Configuration                        | 2-8         |

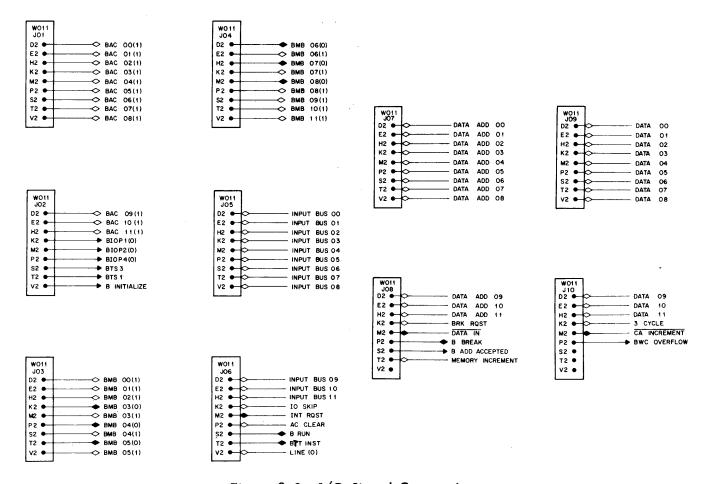

| 2-8   | I/O Signal Connections                       | 2-9         |

| 3-1   | PDP-8/I Front Panel                          | 3-1         |

| 3-2   | Teletype Model ASR33 Console                 | 3-5         |

| 4-1   | System Block Diagram                         | 4-2         |

| 4-2   | Memory Reference Instruction Bit Assignments | 4-6         |

| 4-3   | IOT Instructions Bit Assignments             | 4-8         |

| 4-4   | Group 1 Operate Instruction Bit Assignments  | 4-8         |

| 4-5   | Group 2 Operate Instruction Bit Assignments  | 4-11        |

| 4-6   | Memory System, Block Diagram                 | 4-14        |

| 4-7   | Memory Operations Timing Diagram             | 4-16        |

| 4-8   | Simple Core Memory Plane                     | 4-16        |

# ILLUSTRATIONS (Cont)

|              |                                                                          | Page         |

|--------------|--------------------------------------------------------------------------|--------------|

| 4-9          | Memory Address Selector and Read/Write Current Control                   | 4-18         |

| 4-10         | Manual Function Timing Diagram                                           | 4-22         |

| 4-11         | System Timing Diagram                                                    | 4-25         |

| 4-12         | Data Flow                                                                | 4-30         |

| 4-13         | Direct and Indirect Address Selection, Simplified Flow Chart             | 4-40         |

| 4-14         | IOT Generation                                                           | 4-41         |

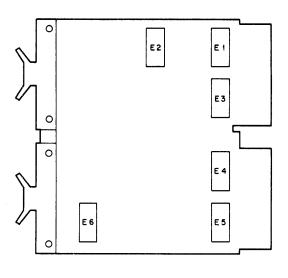

| 5-1          | IC Location                                                              | 5 <b>-</b> 6 |

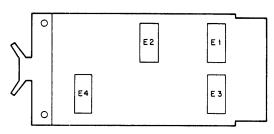

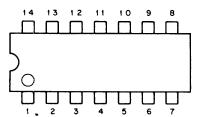

| 5-2          | IC Pin Location                                                          | 5-6          |

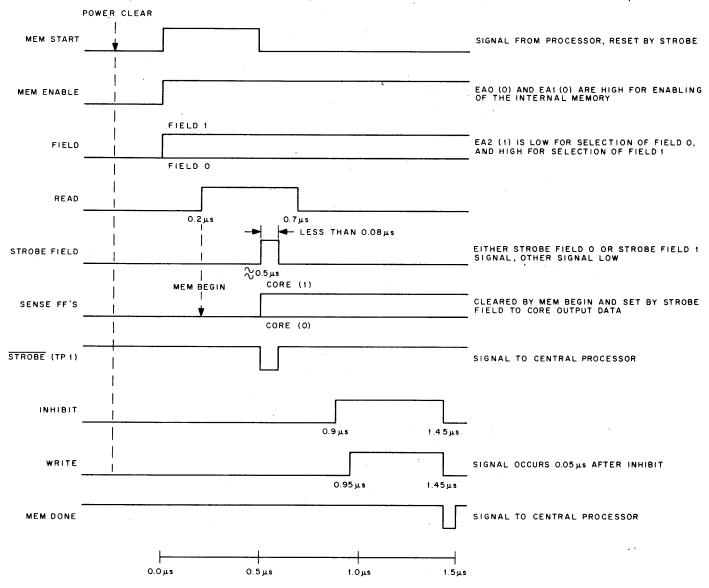

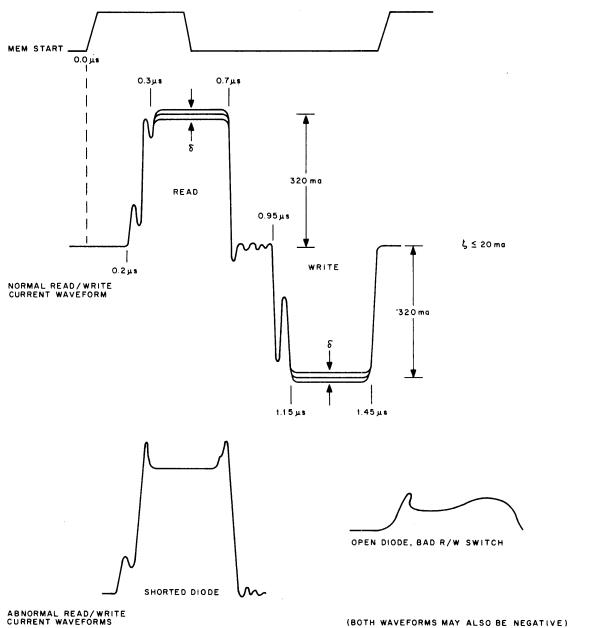

| 5-3          | Memory Control Waveforms                                                 | 5 <b>-</b> 9 |

| 5-4          | Representative Read/Write Current Waveforms                              | 5-10         |

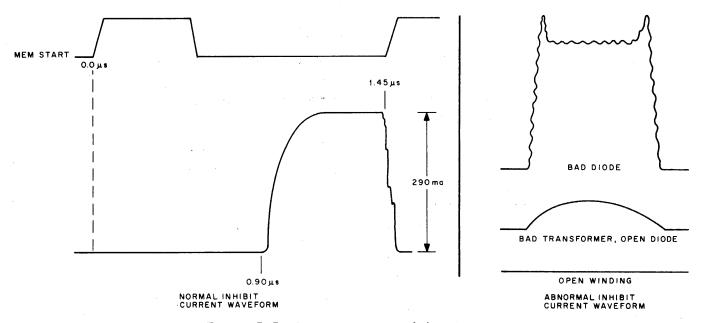

| 5 <b>-</b> 5 | Representative Inhibit Current Waveforms                                 | 5-13         |

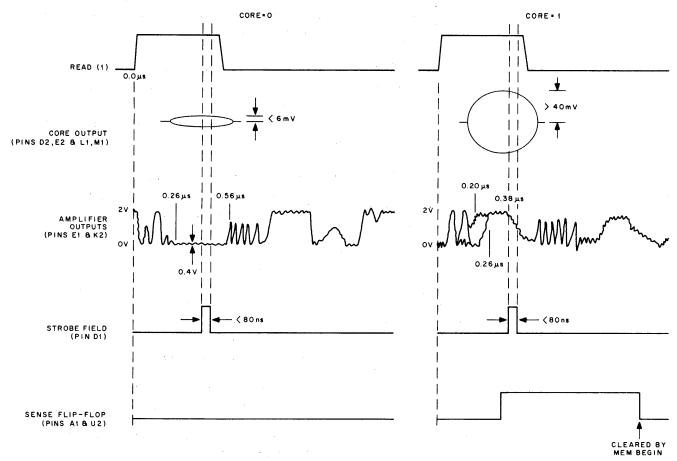

| 5-6          | Representative Sense Amplifier Waveforms                                 | 5-13         |

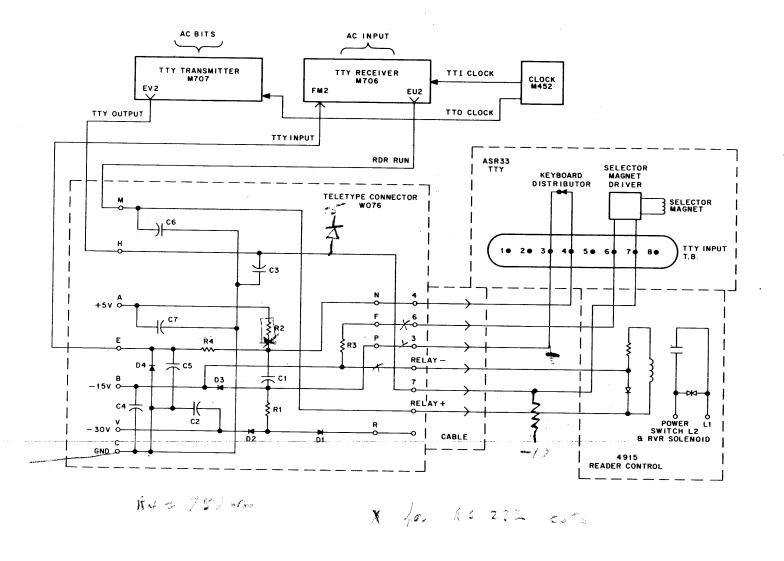

| 5 <b>-</b> 7 | Teletype Connections                                                     | 5-16         |

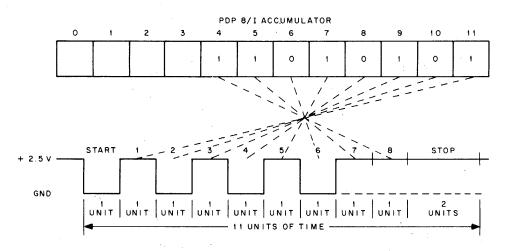

| 5-8          | Teletype Signal Waveform and Bit Relationship for the Character "U"      | 5-17         |

|              | TABLES                                                                   |              |

| 3-1          | Computer Controls and Indicators                                         | 3-2          |

| 3-2          | Teletype Controls and Indicators                                         | 3-7          |

| 3-3          | Readin Mode Loader Program                                               | 3-8          |

| 4-1          | Example of Register Contents During JMS Instruction                      | 4-35         |

| 5-1          | Maintenance Equipment                                                    | 5-1          |

| 5-2          | Maintenance Programs                                                     | 5-2          |

| 5-3          | Type H704 Power Supply Outputs                                           | 5-4          |

| 5-4          | Teletype Maintenance Tools                                               | 5-14         |

| 5-5          | Teleprinter Maintenance Programs                                         | 5-14         |

| 5-6          | Spare Parts for Keyboard-Model ASR33 Teletype                            | 5-18         |

| 5-7          | Spare Module List                                                        | 5-18         |

| 5-8          | Recommended Spare Diodes                                                 | 5-18         |

| 5-9          | Recommended Spare Transistors                                            | 5-18         |

| 5-10         | Recommended Spare Integrated Circuits                                    | 5-19         |

| 5-11         | Spare Miscellaneous Components and Parts                                 | 5-19         |

| 5-12         | Sample Mechanization Chart                                               | 5-20         |

| 5-13         | Fetch Cycle, AND, TAD, ISZ, DCA, and JMS Instruction Mechanization Chart | 5-20         |

# TABLES (Cont)

|               |                                                     | Page |

|---------------|-----------------------------------------------------|------|

| 5-14          | Fetch Cycle, OPR Instruction Mechanization Chart    | 5-22 |

| 5-15          | Fetch Cycle, JMP Instruction, Mechanization Chart   | 5-29 |

| 5-16          | Fetch Cycle, IOT Instructions, Mechanization Chart  | 5-30 |

| 5 <b>-</b> 17 | Execute Cycle, AND Instruction, Mechanization Chart | 5-30 |

| 5-18          | Execute Cycle, TAD Instruction, Mechanization Chart | 5-33 |

| 5-19          | Execute Cycle, ISZ Instruction, Mechanization Chart | 5-34 |

| 5-20          | Execute Cycle, DCA Instruction, Mechanization Chart | 5-35 |

| 5-21          | Execute Cycle, JMS Instruction, Mechanization Chart | 5-36 |

| 5-22          | Defer Cycle, JMP Instruction, Mechanization Chart   | 5-37 |

| 5-23          | Defer Cycle, JMP Instruction, Mechanization Chart   | 5-38 |

| 5-24          | Word Count Cycle, Mechanization Chart               | 5-41 |

| 5-25          | Current Address Cycle, Mechanization Chart          | 5-42 |

| 5-26          | Break Cycle Mechanization Chart                     | 5-43 |

| 5-27          | Signal Origins                                      | 5-45 |

|               |                                                     |      |

PDP-8/I Pedestal and Cabinet Configuration

# CHAPTER 1 INTRODUCTION AND DESCRIPTION

#### 1.1 INTRODUCTION

This manual covers installation, operation, theory, and maintenance of the Programmed Data Processor - 8/I (PDP-8/I). It is the intent of this manual to provide the field service engineer or maintenance technician who is familiar with digital logic circuitry with the information he needs to install and maintain a PDP-8/I system. This manual is largely written under the assumption that the reader is conversant with DIGITAL's system of logic notation. If this is not the case, the reader should refer to applicable sections in the appendix for a description.

The PDP-8/I is a one-address, 12-bit, fixedword-length, parallel computer using two's complement arithmetic. Normal cycle time of the 4096-word (referred to as 4K), randomaccess, magnetic-core memory is 1.5 µs. An additional 4K of memory with extended memory control may also be added to the system by plugging the memory modules directly into the system in spaces provided. As much as 32K of memory is available as well as other options, with their control logic internal to the basic machine. Standard features of the system include indirect addressing, facilities for instruction skipping and program interruption as functions of input/output-device conditions, and high-speed information transfers with massmemory devices via a cycle-stealing data break.

#### 1.2 DESCRIPTION

The integrated-circuit (PDP-8/I) is a smallscale general-purpose computer that functions as an independent information-handling facility in a large computer system, or as the control element in a complex processing system. In terms of operating characteristics, speed, programming and available peripheral devices, the PDP-8/I is completely compatible with the PDP-8.

The PDP-8/I performs one addition in 3.0 µs (with one number in the accumulator), permitting a computation rate of 333,333 additions per second to be achieved. It performs subtraction in 6.0 µs (with the minuend in the accumulator) using two's complement addition. Multiplication takes approximately 360 µs, using a subroutine that operates on two signed 12-bit numbers to produce a 24-bit product, leaving the 12 most significant bits in the accumulator. Division of two signed 12-bit numbers takes approximately 460 µs, using a subroutine that produces a 12-bit quotient in the accumulator, and a 12-bit remainder in core memory. The optional Extended Arithmetic Element (KE8I) performs similar multiplication and division operations in 6.0 and 6.5 µs, respectively.

Flexible, high-capacity, input/output capabilities of the computer allow it to operate a variety of peripheral equipment. In addition to the Teletype keyboard/printer and perforated-tape reader/punch, equipment supplied with a basic PDP-8/I, the system can operate a number of optional devices. These options include highspeed perforated-tape reader and punch, card reader, line printer, analog-to-digital converters, cathode-ray-tube displays, magnetic drum systems, magnetic disk-file systems, and magnetic tape equipment. Instruments or equipment of special design can also be connected into the PDP-8/I system. The computer itself needs no modification for the addition of peripheral devices.

The PDP-8/I is completely self-contained and, under normal conditions, requires neither spec-

ial power sources nor rigidly controlled environmental conditions. A single source of 115 VAC, 60 Hz, single-phase power permits internal power supplies to produce all required operating voltages. M-series modules, using TTL-type integrated circuit packs, ensure reliable operation in ambient temperatures between +32 and +130°F.

#### 1.3 PERTINENT DOCUMENTS

The following documents serve as source material and complement the information in this manual:

- 1. Logic Handbook, C-105 (1970 edition), printed by DIGITAL, which notes the function and specifications of the M-series modules and module accessories for the PDP-8/I.

- 2. Small Computer Handbook, (1970 edition), printed by DIGITAL, which contains programming and operational data and the PDP-8/I Users Handbook.

- Technical Manual, Automatic Send and Receive Sets (ASR), Bulletin 273B (Volumes I and II). This manual covers operation and maintenance of the Teletype unit.

- 4. Parts, Model 33 Page Printer Set, Bulletin 1184B, contains an illustrated parts breakdown to serve as a guide to disassembly, reassembly, and ordering replacement parts for the Teletype unit.

- 5. Instruction List F-816, printed by DIGITAL. This is a shirt-pocket list of all memory reference instructions, all augmented instructions, the most common IOT instructions, and the ASCII code used with many I/O devices.

- 6. Instruction manuals and MAINDEC programs for appropriate input/output devices are prepared by DIGITAL.

- 7. Digital Program Library Documents. Perforated program tapes and descriptive matter

for the Program Assembler Language (PAL III), FORTRAN, FOCAL, utility subroutines, and the maintenance programs (MAINDEC) prepared by Digital are available to PDP-8/Iusers. The list of programs currently in the library and available is provided in Appendix D.

#### 1.4 ABBREVIATIONS

Listed below are the most-commonly used abbreviations of registers, key operations, components, instructions and signal names

| ponents, instructions and signal names. |                                   |  |  |

|-----------------------------------------|-----------------------------------|--|--|

| AC                                      | Accumulator                       |  |  |

| A/D                                     | Analog-to-digital (converter or   |  |  |

|                                         | converted signal)                 |  |  |

| ADD or ADDR                             | Address                           |  |  |

| В                                       | Break state                       |  |  |

| BD                                      | Bus driver                        |  |  |

| BRK RQST                                | Break request                     |  |  |

| CA                                      | Current address state             |  |  |

| CLA                                     | Clear accumulator (instruction or |  |  |

|                                         | signal)                           |  |  |

| CLR                                     | Clear                             |  |  |

| CM or COMP                              | Complement                        |  |  |

| CONT                                    | Continue                          |  |  |

| CP                                      | Central processor                 |  |  |

| D                                       | Defer state                       |  |  |

| DCA                                     | Deposit and clear accumulator     |  |  |

|                                         | (instruction)                     |  |  |

| DEP                                     | Deposit                           |  |  |

| DF                                      | Data Field Register               |  |  |

| DIV                                     | Divide                            |  |  |

| DLI                                     | Data line interface               |  |  |

| DP                                      | Deposit                           |  |  |

| E                                       | Execute state                     |  |  |

| EAE ,                                   | Extended arithmetic element       |  |  |

| EX or EXAM                              | Examine                           |  |  |

| F                                       | Fetch state                       |  |  |

| FLG                                     | Flag                              |  |  |

Halt

Inhibit

Interrupt

Instruction field

Instruction (key)

Instruction field register

Interrupt acknowledge

HLT

IF

**IFR**

INH

INST

INT ACK

INT

| I/O | Input/Output                     | PROG    | Program                             |

|-----|----------------------------------|---------|-------------------------------------|

| ION | Interrupt on                     | PWR CLR | Power clear                         |

| IOP | Input/Output pulse               | RDR     | Reader                              |

| IOT | Input/Output (information)       | SA      | Sense amplifier                     |

|     | transfer                         | SC      | Step counter (EAE)                  |

| IR  | Instruction register             | SD      | Solenoid driver                     |

| ISZ | Increment and skip if zero       | SENSE   | Memory register (also MEM)          |

| JMP | Jump (instruction)               | SF      | Start field                         |

| JMS | Jump to subroutine (instruction) | SING    | Single (key)                        |

| KBD | Keyboard (Teletype)              | SKP     | Skip                                |

| Ĺ   | Link                             | ST      | Start                               |

| MA  | Memory address register          | SR      | Switch register                     |

| MB  | Memory buffer register           | SYNC    | Synchronize                         |

| MEM | Memory register (also SENSE)     | TAD     | Two's complement add (instruction)  |

| MQ  | Multiplier quotient register     | TP      | Time pulse                          |

| MUL | Multiply                         | TS      | Time state                          |

| OP  | Operate                          | TT      | Teletype                            |

| OPR | Operate (class of instruction)   | TTI     | Teletype in (Teletype keyboard/     |

| P   | Parity                           |         | reader buffer)                      |

| PA  | Pulse amplifier                  | TTO     | Teletype out (Teletype teleprinter/ |

| PC  | Program counter                  |         | punch buffer)                       |

| PI  | Program interrupt                | WC      | Word count state                    |

# CHAPTER 2 INSTALLATION

This chapter contains installation information and physical specifications of the PDP-8/I and its options.

#### 2.1 SPACE REQUIREMENTS

Access space must be provided at the installation site to accommodate the PDP-8/I and peripheral equipment, and to allow access to all doors and panels for maintenance.

The PDP-8/I is available in either the pedestal or rack mounted configuration. The rack mounted configuration and peripherals may be purchased completely installed in DEC cabinets or may

be purchased unmounted for installation in a customer cabinet. Figure 2-1 gives dimensions for the pedestal mounted PDP-8/I. Figures 2-2 through 2-5 show detailed mounting information for installing the PDP-8/I into standard DEC, BUD, and EMCOR racks.

Minimum service clearance on all standard DEC computer cabinets is 8-3/4 in. at the front and 14-7/8 in. at the back.

The standard Teletype automatic send receive set requires a floor space of approximately 22-1/4 in, wide by 18-1/2 in, deep. The Teletype signal cable requires the Teletype to be placed near the computer.

Figure 2-1 PDP-8/I Pedestal Dimensions

#### 2.2 ENVIRONMENTAL REQUIREMENTS

Ambient temperature at the installation site can vary between 32° and 130°F (0° and 55°C). To extend the life expectancy of the system, however, it is recommended that the temperature at the installation site be maintained at between 70° and 85°F (between 20° and 30°C).

During shipping or storing of the system, the ambient temperature may vary between 32° and 130°F (between 0° and 55°C). All exposed surfaces of all DEC cabinets and hardware are treated to prevent corrosion, but exposure of systems to extreme humidity for long periods of time should be avoided.

#### 2.3 POWER REQUIREMENTS

A source of 115V (±17V), 60 Hz (±0.5 Hz), single-phase power capable of supplying at least

15A must be provided to operate a standard PDP-8/I. To allow connection of the computer to the power cable, this source should be provided with a Hubbell 3-terminal connector plug. A rack mounted PDP-8/I has a 20A twist-lock plug; systems that draw more than 20A use a 30A twist-lock plug. All free-standing cabinets require independent 115V receptacles. However, these units may be turned on or off, or controlled from the PDP-8/I operator console.

Upon special request, a PDP-8/I can be constructed to operate from a 220V (±33V), 60 Hz (±0.5 Hz), single-phase power source or from a 100V (±15V), 50 Hz (±0.5 Hz), single-phase power source.

Figure 2-2 Rack Mounted PDP-8/I Dimensions

Figure 2-3 PDP-8/I Installation in Standard DEC Cabinet

Figure 2-4 PDP-8/I Installation in Bud Cabinet

Figure 2-5 PDP-8/I Installation in Emcor Cabinet

#### 2.4 CABLE REQUIREMENTS

Signal conductor cables with Type W011 Cable Connectors provide signal connections between the computer and the optional equipment in free-standing cabinets. These cables are connected by plugging the W011 connectors into standard module receptacles. Cables connect to cabinets through a drop panel in the bottom of cabinets. Subflooring is not necessary because casters elevate the cabinets high enough from the floor to provide sufficient cable clearance. Cable details are included in the I/O Interface paragraph.

#### 2.5 INSTALLATION PROCEDURE

Installation of a PDP-8/I system requires no special tools or equipment. A fork-lift truck, or other pallet-handling equipment, and normal hand tools should be available for receiving and installing the equipment. To install the computer observe the following procedure:

- 1. Place the computer package near the final installation location. Pry the top, and side sections of the wooden shipping crate apart with a hammer, and wedge at the staple joints. Unfasten the four bolts holding the computer frame to the pallet. Using a ramp, slide the computer off the pallet to the final location. When a cabinet mounted PDP-8/I is installed, a similar procedure is used. First, remove the shipping straps with cutting shears. Remove the packing material, and the cardboard crate to disassemble the wooden corner supports.

- 2. Remove the plastic cover. Remove the two machine screws in the rear of the computer logic frame that hold it firm. This allows the logic frame to be serviced pulling it out on the tracks.

- 3. Open the Teletype carton, and remove the packing material. Remove the back cover from the stand. Remove and unwrap the copyholder, chad box, and power pack. Remove the stand

from the shipping carton. Remove the Teletype console from the carton, holding it by means of the wooden pallet attached to the bottom. Snap the power pack in place at the top of the rear side of the Teletype stand. Remove the Teletype console from the pallet, and mount it on the stand. Connect the Teletype console to the power pack (a six-lead cable attached at the console is connected to the power pack by means of a white plastic Molex 1375 Female Connector which mates with a male output plug on the power pack). Pass the three-wire power cable, and the seven-conductor signal cable (which is terminated in a type W076 Cable Connector Module) through the opening at the lower left-hand corner of the Teletype stand; then replace the back cover of the stand by means of the two mounting screws.

- 4. Dress the Teletype cable under the PDP-8/I cabinet, through the large opening and into logic frame slot J12. It is necessary that this cable be dressed through the cable clamp at the lower rear corner of the logic frame where the power cables are secured. A second clamp may be desirable at the bottom of the PDP-8/I cabinet to assure that sufficient slack exists irrespective of the Teletype position.

- 5. Connect the three-prong male connector of the Teletype power cable to the connector at the rear of the computer power supply chassis.

- 6. Set the PANEL LOCK switch to the full counterclock wise position (OFF). Set the POWER LOCK switch to the full counterclock-wise position (OFF). Set the main power switch (circuit breaker at rear of computer power supply chassis) to ON.

- 7. Turn the POWER switch on.

- 8. Install a roll of printed paper into the Teletype keyboard/printer, and install a tape in the punch as described in the Teletype technical manual.

- 9. Set the LINE/OFF/LOCAL switch to LINE. Press the punch ON pushbutton. Strike several keys, and note whether or not the printer and punch operate. Check the operation of the printer with the LINE/OFF/LOCAL switch set to LOCAL. After completion of these checks, set the switch to OFF.

- 10. Turn the power OFF.

This completes the installation of a standard PDP-8/I system. Before normal operating use, verify the operating capability of the system. Perform the power supply checks, and run the complete set of diagnostic programs (MAIN-DECs) as described in Chapter 5.

Figure 2-6 System Configurations

#### 2.6 INTERNAL OPTION INSTALLATION

The installation of the internal options involves the addition of the logic modules in the proper locations. Turn off the computer before inserting or removing any modules in the logic frame. Refer to both sheets of the module utilization drawings MU-8I-0-17 for the locations of each module of all internal options. If an option involves an external device, dress connecting cables through the large opening from the logic frame to the option. Proper adequately ventilated mounting facilities are necessary to insure protection and safety of the equipment. Refer to the system configurations drawing (Figure 2-6) for proper location of options.

#### 2.7 SYSTEM CONFIGURATIONS

PDP-8/I systems are mounted in standard DEC cabinets. The basic cabinet contains the processor and the power supply. The other cabinets and spaces in Figure 2-6 show the position priority assignments and the top priority when a choice exists. The priorities are assigned with considerations of ease of control, and cable lengths.

# 2.8 I/O INTERFACE

The following paragraphs describe the PDP-8/I I/O bus, the I/O cables, the logic level converters and their driving capabilities, and the processor location terminals of each I/O bus signal.

#### 2.8.1 I/O Bus Signal

The PDP-8/I employs a series I/O bus system which allows interface connections to be made between all of the external devices without modifying the computer wiring. In a series I/O bus, the computer sends all I/O signals to the first device which makes use of pertinent signals and sends all of the I/O signals to the next de-

vice, as shown in Figure 2-7. Where physical location of equipment makes series connections impractical, or when cable length become excessive, additional interface connectors are usually installed near the computer.

Figure 2-7 I/O Bus Configuration

#### 2.8.2 I/O Cables

The standard PDP-8/I I/O bus uses 18-conductor  $93\Omega$ ribbon cable that terminates into W011 Cable Connectors. Terminals C,F,J,L,N,R, and U of receptacles J01 through J10 are grounded within the computer, and terminals D,E,H,J,M,P,S,T, and V carry signals.

All PDP-8/I I/O cable connections are made at the assigned module receptacle connectors J01 through J10 in the mounting frame, with the exception of the Address Extend 1,2,3 inputs, and Data Field 0,1, and 2 outputs which terminate at location H01.

# 2.8.3 Logic Levels and Level Converters

The PDP-8/I internal logic levels are positive levels of +3V and 0V. The present DEC external peripherals function with negative DEC standard levels or pulses. The standard levels are either ground potential (0.0V to -0.3V) designated by an open diamond (<), or -3V (-3V to -4V) designated by a solid diamond (<). To provide compatibility between the internal PDP-8/I levels and the external negative logic

levels, the computer inputs and outputs are converted by the M506 and M650 Level Converters (Drawing BS-8I-0-10).

Input interface signals to the computer use the M506 Negative Input Converters which shift the DEC standard negative levels of -3V and 0V to PDP-8/I positive levels of 0V and +3V. A -3V input produces an M506 output of 0V, and a 0V input generates a +3V output. In addition, the M506 contains positive-logic internal bus inputgating that allows the outputs from the Teletype logic, extended memory internally generated skip and interrupt, and AC CLEAR from the internal options to input to the major register gating network.

All I/O bus output signals to the external options except the MM8I, are first converted by

the M650 Negative Output Converter and Bus Driver modules which shift the PDP-8/I levels of +3V and 0V to DEC levels of 0V and -3V. An M506 input voltage level of +3V is converted to 0V as an I/O signal, and a 0V input signal converts to -3V. The M650 can drive 20 mA at 0V or sink 20 mA at -3V.

#### 2.8.4 Interface Signal Connections

Figure 2-8 shows the I/O bus interface signals as well as the cable and signal locations. The signal direction is also shown by the logic levels which are shown with the functions in the active states.

Figure 2-8 I/O Signal Connections

# CHAPTER 3 OPERATION

This chapter contains operating information for the PDP-8/I and the ASR33 Teletypewriter. Operating information for the peripheral input/ output devices is contained in their respective manuals.

#### 3.1 CONTROLS AND INDICATORS

The following subparagraphs contain detailed information regarding the controls and indicators of the PDP-8/I and the ASR33 Teletypewriter.

#### 3.1.1 Computer

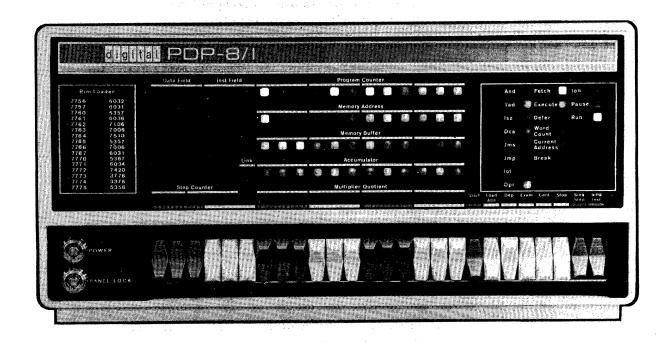

Figure 3-1 shows the location of the PDP-8/I controls and indicators. Although not marked on the front panel, register bits are numbered from left to right starting with zero. Therefore the most significant (leftmost) bit in the program

counter (PC) is identified as PC00, and the least (rightmost) significant bit is identified as PC11. Table 3-1 contains a listing of the PDP-8/I controls and indicators within their functions. The PDP-8/I controls (except the power and panel lock switches) are of two types: butterfly switches, and momentary-contact switches. The butterfly switches are considered to be in their zero or off-state when the top half of the butterfly is fully depressed, and are considered to be in their one or on state when the bottom half of the butterfly is depressed. The momentary-contact switches include the Start, Exam, Load Add, Cont, Dep and Stop switches. These switches (except Dep) are actuated when the bottom half is fully depressed. The Dep switch is the reverse of the above. Indicators are considered to be in their on or one state when they are lit, and in their off or zero state when not lit.

Figure 3-1 PDP-8/I Front Panel

Table 3-1 Computer Controls And Indicators

| Control or Indicator  | Function                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Panel Lock key switch | When turned clockwise, this key-operated switch disables all controls except the Switch Register switches on the operator console. In this condition, inadvertent key operation cannot disturb the program. The program can, however, monitor the content of SR by execution of the OSR instruction.                                                                       |

| Power key switch      | This key-operated switch controls application of primary power to the computer. When this switch is turned clockwise, primary power is applied.                                                                                                                                                                                                                            |

| Start key             | Starts the program by turning off the program interrupt circuits clearing the AC and L, setting the Fetch state, and starts the central processor.                                                                                                                                                                                                                         |

| Load Add key          | This key transfers the content of SR into PC, the content of INST FIELD * switches into IF, the content of the DATA FIELD * switches into DF, and clears the major state flip-flops.                                                                                                                                                                                       |

| Dep key               | This key transfers the content of SR into MB and core memory at the address specified by the current content of PC. The major state flip-flops are cleared. The contents of PC is then incremented by one to allow storing of information in sequential core memory addresses by repeated operation of the Dep key.                                                        |

| Exam key              | This key transfers the content of core memory at the address specified by the content of PC, into the MB. The content of the PC is then incremented by one to allow examination of the contents of sequential core memory addresses by repeated operation of the Exam key. The major state flip-flop register cleared. The MA indicates the address of the data in the MB. |

| Cont key              | This key sets the RUN flip-flop to continue the program in the state and instruction designated by the lighted console indicators, at the address currently specified by the PC if key SS is not on.                                                                                                                                                                       |

| Stop key              | Causes the RUN flip-flop to be cleared at the end of the instruction in progress at the time the key is pressed.                                                                                                                                                                                                                                                           |

| Sing Step key         | This key causes the RUN flip-flop to be cleared to disable the timing circuits at the end of one cycle of operation. Thereafter, repeated operation of the Cont key steps the program one cycle at a time so that the operator can observe the contents of registers in each major state.                                                                                  |

<sup>\*</sup> Activated only on systems containing the MC8/I, Memory Extension Control option.

Table 3–1 Operator Console Controls And Indicators (Cont)

| Control or Indicator                    | Function                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sing Inst key                           | This key allows execution of one instruction. When the computer is started by pressing the Start or Cont key, the Sing Inst key causes the RUN flip-flop to be cleared at the end of the last cycle of the current instruction. Thereafter, repeated operation of the Cont key steps the program one instruction at a time. |  |  |  |

| Switch Register switches                | Provide a means of manually setting a 12-bit word into the machine. Load the content of this register into PC by pressing the Load Add key or load the content into the MB and core memory by the Dep key. Under program control, the OSR and LAS instructions can set the content of SR into AC.                           |  |  |  |

| Data Field indicators and switches *    | The indicators denote the content of the data field register (DF), and the switches serve as an extension of SR to load DF by means of the Load Add key. DF determines the core memory field of data storage and retrieval.                                                                                                 |  |  |  |

| Inst Field indicators<br>and switches * | The indicators denote the content of the instruction field register (IF), and the switches serve as an extension of SR to load the IF by means of the Load Add key. IF determines the core memory field from which instructions are to be taken.                                                                            |  |  |  |

| Register Indicators                     |                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Program Counter indicators              | The PC contains the location of the next instruction to be performed.                                                                                                                                                                                                                                                       |  |  |  |

| Memory Address<br>indicators            | Indicate the content of MA. Usually, the contents of MA denote the core memory address of the word currently or previously read or written. After operation either the Dep or Exam key, the contents of MA indicate the core memory address just examined or deposited into.                                                |  |  |  |

| Memory Buffer indicators                | Indicates the content of MB. Usually, the contents of MB designate the word just written at the core memory address in MA.                                                                                                                                                                                                  |  |  |  |

| Accumulator                             | Indicates the content of AC.                                                                                                                                                                                                                                                                                                |  |  |  |

| Link                                    | Indicates the content of L.                                                                                                                                                                                                                                                                                                 |  |  |  |

| Multiplier Quotient                     | Indicates the content of the multiplier quotient (MQ). MQ holds the multiplier at the beginning of a multiplication and holds the least-significant half of the product at the conclusion. It holds the least-significant half of the dividend at the start of division and holds the quotient at the conclusion.           |  |  |  |

<sup>\*</sup>Activated only on systems containing the MC8/1, Memory Extension Control option.

Table 3-1 Operator Console Controls And Indicators (Cont)

| Control or Indicator          |                                                                                                                                                                                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Function                                                                                                                                                                                                                        |

| <u>Major State Indicators</u> |                                                                                                                                                                                                                                 |

| Fetch                         | Indicates that the processor is currently performing or has performed a Fetch cycle.                                                                                                                                            |

| Execute                       | Indicates that the processor is currently performing or has performed an Execute cycle.                                                                                                                                         |

| Defer                         | Indicates that the processor is currently performing or has performed a Defer cycle.                                                                                                                                            |

| Word Count                    | Indicates that the processor is currently performing or has performed a Word Count cycle.                                                                                                                                       |

| Current Address               | Indicates that the processor is currently performing or has performed a Current Address cycle.                                                                                                                                  |

| Break                         | Indicates that the processor is currently performing or has performed a Break cycle.                                                                                                                                            |

| Miscellaneous Indicators      |                                                                                                                                                                                                                                 |

| Ion                           | Indicates the 1 status of the INT.ENABLE flip-flop. When lit, the interrupt control is enabled for information exchange with an I/O device.                                                                                     |

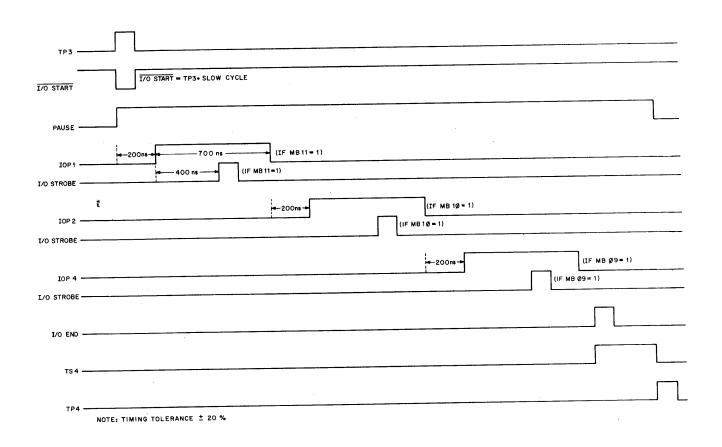

| Pause                         | Indicates the 1 status of the PAUSE flip-flop when lit. The PAUSE flip-flop is set for 2.75 µs by any IOT instruction that requires generation of IOP pulses or by any EAE instruction ** that require shifting of information. |

| Run                           | Indicates the 1 status of the RUN flip-flop. When lit, the internal timing circuits are enabled and the machine performs instructions.                                                                                          |

| Instruction Indicators        |                                                                                                                                                                                                                                 |

| And                           | Indicates that the processor is currently performing or has performed an And instruction.                                                                                                                                       |

| Tad                           | Indicates that the processor is currently performing or has performed a Tad instruction.                                                                                                                                        |

<sup>\*\*</sup> Activated only on systems containing the KE8I, Extended Arithmetic Element option.

Table 3–1 Operator Console Controls And Indicators (Cont)

| Control or Indicator   | Function                                                                                  |  |  |

|------------------------|-------------------------------------------------------------------------------------------|--|--|

| Instruction Indicators |                                                                                           |  |  |

| Isz                    | Indicates that the processor is currently performing or has performed an Isz instruction. |  |  |

| Dca                    | Indicates that the processor is currently performing or has performed a Dca instruction.  |  |  |

| Jms                    | Indicates that the processor is currently performing or has performed a Jms instruction.  |  |  |

| Jmp                    | Indicates that the processor is currently performing or has performed a Jmp instruction.  |  |  |

| Iot                    | Indicates that the processor is currently performing or has performed an Iot instruction. |  |  |

| Opr                    | Indicates that the processor is currently performing or has performed an Opr instruction. |  |  |

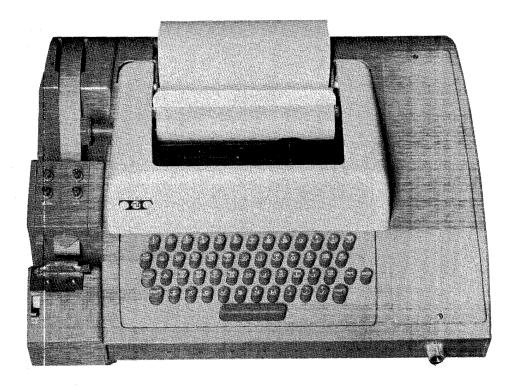

Figure 3-2 Teletype Model ASR33 Console

#### 3.1.2 Teletype

Figure 3-2 shows the location of the ASR33 Teletypewriter controls and indicators. Table 3-2 contains a listing of the ASR33 controls and indicators with a description of their functions.

#### 3.2 OPERATING PROCEDURES

Many means are available for loading and unloading PDP-8/I information. The means used depend upon the form of the information, time limitations, and the peripheral equipment connected to the computer. The following procedures are basic to any use of the PDP-8/I. Although these procedures are used infrequently as the programming and use of the computer become more sophisticated, they are valuable in preparing the initial programs and learning the function of machine input and output transfers.

#### 3.2.1 Common Procedures

All of the following procedures require that the PANEL LOCK switch be rotated fully counter-clockwise (off), and that the Power switch be rotated fully clockwise(on).

#### 3.2.2 Manual Loading Procedures

Programs and data can be stored or modified manually by means of the facilities on the operator console. The chief use of the manual data storage facility is to load the Readin Mode Loader program into the computer core memory. The Readin Mode Loader (RIM) is a program used for loading into the PDP-8/I other programs that have been assembled on perforated tape in RIM format. This program and the RIM tape format are described in the PDP-8/I Users Handbook (see Small Computer Handbook, C-800, 1968 edition) and in Digital Program Library descriptions. The RIM program is also listed in Table 3-3 for rapid reference and can be used as an exercise in manual data storage. To store data manually in the PDP-8/I core memory proceed as follows:

- 1. Set the bit switches of the Switch Register (SR) to correspond with the address bits of the first word to be stored. Press the Load Add key and observe that the address specified by the SR is held in the PC, as designated by lighted Program Counter indicators corresponding to switches in the 1 position and unlighted indicators corresponding to switches in the 0 position.

- 2. Set the SR to correspond with the data or instruction word to be stored at the address just set into the PC. Press the Dep key and observe that the MB, and hence the core memory, hold the word set by the SR.

- 3. Observe that the contents of the PC have been incremented by 1 so that additional data can be stored at sequential addresses by repeated SR setting and Dep key operation.

To check the contents of an address in core memory, set the address into the PC as in step 2; then press the Exam key. The Memory Buffer indicates the contents of the Address. The contents of the PC are incremented by 1 with the operation of the Exam key, so that the contents of consecutive addresses can be examined by repeated operation of the Exam key after the original (or starting) address is loaded. Any address can be modified by repeating steps 2 and 3.

# 3.2.3 Teletype Loading Procedures

Information can be stored or modified in the computer under program control. For example, having the RIM Loader stored in core memory allows RIM format tapes to be loaded as follows.

- 1. Set the Teletype LINE/OFF/LOCAL switch to the LINE POSITION.

- 2. Load the tape in the Teletype reader by setting the START/STOP/FREE switch to the FREE position, releasing the cover guard by means of the latch at the right, loading the tape so that the sprocket wheel teeth engage

the feed holes in the tape, closing the cover guard, and setting the switch to the STOP position. Load the tape in the back of the reader so that it moves toward the front as it is read. Proper positioning of the tape in the reader finds three channels being sensed to the left of the sprocket wheel and five channels being sensed to the right of the sprocket wheel.

- 3. Load the starting address of the RIM Loader program (77568) into the PC using the SR and the Load Add key.

- 4. Press the computer Start key and set the 3-position Teletype reader switch to the START position. The tape is read into memory by program control.

The RIM Loader program loads the Binary Loader (BIN) program as previously described. With

the BIN Loader stored in core memory, program tapes assembled in Program Assembly Language (PAL III) binary format can be stored as described in the previous procedure, except that the starting address of the BIN Loader (7777g) is used in step 4. After storing a program in this manner, the computer stops; the AC should contain all 0's if the program is stored properly. If the computer stops with a number other than 0 in the AC, a checksum error has been detected; therefore, the program has been stored incorrectly, and the storage procedure should be repeated. When the program has been stored correctly, initiate it by loading the program starting address (usually designated on the leader of the tape) into the PC using the SR and Load Add key. Then press the Start key.

Table 3-2 Teletype Controls and Indicators

| Control or Indicator   | Function                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REL. pushbutton        | Disengages the tape in the punch to allow tape removal or tape loading.                                                                                                                                                                                                                                                       |  |  |

| B. SP. pushbutton      | Backspaces the tape in the punch by one space, allowing manual correction or rubout of the character just punched.                                                                                                                                                                                                            |  |  |

| OFF and ON pushbuttons | Control use of the tape punch with operation of the Teletype keyboard/printer.                                                                                                                                                                                                                                                |  |  |

| START/STOP/FREE switch | Controls use of the tape reader with operation of the Teletype. In the lower FREE position, the reader is disengaged and can be loaded or unloaded. In the center STOP position, the reader mechanism is engaged but de-energized. In the upper START position, the reader is engaged and operated under program control.     |  |  |

| Keyboard               | Provides a means of printing on paper in use as a typewriter and punching tape when the operator presses the punch ON pushbutton. The keyboard also supplies input data to the computer when the LINE/OFF/LOCAL switch is in the LINE position.                                                                               |  |  |

| LINE/OFF/LOCAL switch  | Controls application of primary power in the Teletype and controls data connection to the processor. In the LINE position, the Tetype is energized and connected as an I/O device of the computent the OFF position, the Teletype is de-energized. In the LOC position, the Teletype is energized for off-line operation, and |  |  |

|                        | signal connections to the processor are broken. Only line use of<br>the Teletype requires that the computer be energized through the<br>POWER switch if primary power for the Teletype is supplied from<br>a source other than the outlet at the back of the computer.                                                        |  |  |

Table 3–3

Readin Mode Loader Program

| Address       | Octal<br>Content | Tag   | Mnemonic   | Comments                          |

|---------------|------------------|-------|------------|-----------------------------------|

| <i>7</i> 756, | 6032             | BEG,  | KCC        | /CLEAR AC AND FLAG                |

| 7757,         | 6031             | -     | KSF        | /SKIP IF FLAG = 1                 |

| <i>7</i> 760, | 5357             |       | JMP1       | LOOKING FOR CHARACTER             |

| <i>7</i> 761, | 6036             |       | KRB        | /READ BUFFER                      |

| 7762,         | <i>7</i> 106     |       | CLL RTL    | ,                                 |

| <i>7</i> 763, | 7006             |       | RTL        | CHANNEL 8 IN ACO                  |

| 7764,         | <i>7</i> 510     |       | SPA        | CHECKING FOR LEADER               |

| 7765,         | 5357             |       | JMP BEG+1  | FOUND LEADER                      |

| <i>7</i> 766, | 7006             |       | RTL        | OK, CHANNEL 7 IN LINK             |

| 7767 <b>,</b> | 6031             |       | KSF        | , 511, 513 11 11 122 / 11 1 21 11 |

| <i>777</i> 0  | 5367             |       | JMP1       |                                   |

| <i>777</i> 1, | 6034             |       | KRS        | /READ, DO NOT CLEAR               |

| 7772,         | 7420             |       | SNL        | CHECKING FOR ADDRESS              |

| <i>777</i> 3, | 3776             |       | DCA I TEMP | STORE CONTENTS                    |

| <i>7774</i> , | 3376             |       | DCA TEMP   | STORE ADDRESS                     |

| <i>7775</i> , | 5356             |       | JMP BEG    | NEXT WORD                         |

| 7776,         | 0 .              | TEMP, | 0          | /TEMP STORAGE                     |

#### 3.2.4 Off-Line Teletype Procedures

The Teletype can operate separately from the PDP-8/I for typing, punching tape, or duplicating tapes. To use the Teletype in this manner follow the procedure described below.

- 1. Assure that primary Teletype power is ON.

- 2. Set the Teletype LINE/OFF/LOCAL switch to the LOCAL position.

- 3. Load the punch as follows. Raise the cover and manually feed the tape from the top of the roll into the guide at the back of the punch. Advance the tape through the punch by manually turning the friction wheel; then close the cover.

- 4. Energize the punch by pressing the ON pushbutton, and produce about 2 ft of leader. The leader-trailer can be either 200<sub>g</sub> or 377<sub>g</sub> code. To produce the 200<sub>g</sub> code leader, simultaneously press and hold the CTRL and

SHIFT keys with the left hand; press and hold the REPT key; press and release the P key. When the required amount of leader has been punched, release the REPT key, then CTRL and SHIFT keys. To produce the 337g code leader, simultaneously press and hold both the REPT and RUB OUT keys until a sufficient amount of leader has been punched.

If an incorrect key is struck while punching a tape, the tape can be corrected as follows. If the error is noticed after typing and punching N characters, press the punch B.SP. (back-space) pushbutton N+1 times and strike the keyboard RUB OUT key N+1 times. Then continue typing and punching with the character which was in error.

To duplicate and obtain a listing of an existing tape; load the tape to be duplicated in the paper tape reader. Set the LOCAL/LINE switch to LOCAL, turn the punch on, and turn the paper tape reader on.

# CHAPTER 4 THEORY

This chapter is divided into four sections and covers the theory of operation of the PDP-8/I Computer. Section I contains a discussion of the theory at a block diagram level; Section II contains a discussion in terms of general theory of operation; Sections III and IV cover detailed memory theory and detailed processor theory, respectively.

# SECTION I BLOCK DIAGRAM DISCUSSION

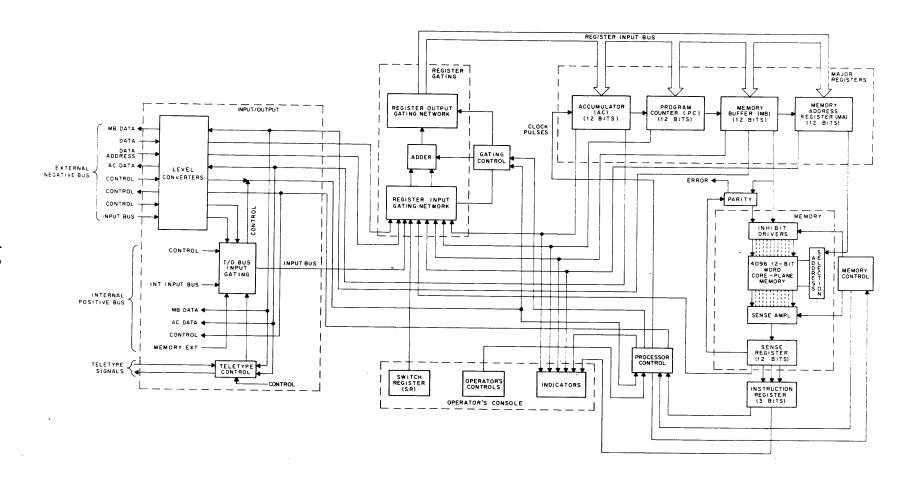

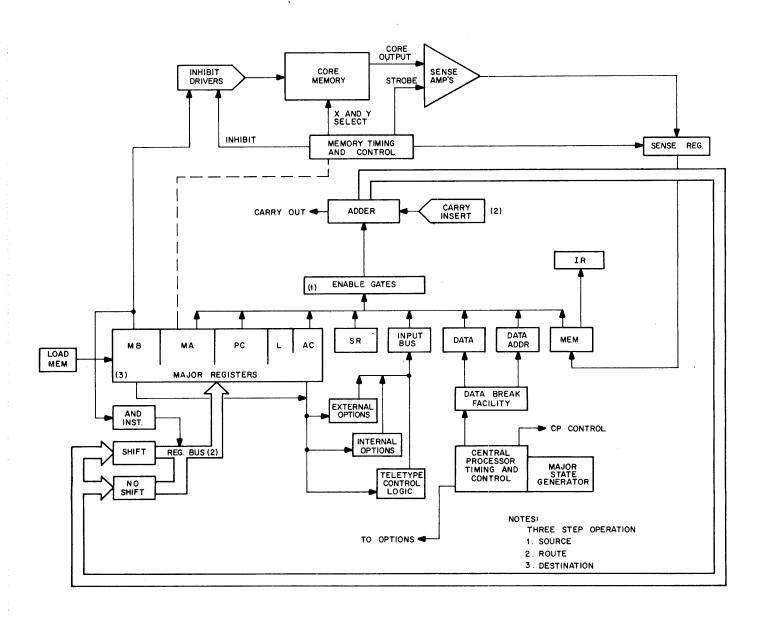

The following paragraphs discuss the major functional elements of the PDP-8/I as shown on the simplified system block diagram (Figure 4-1).

#### 4.1 REGISTERS

# 4.1.1 Accumulator (AC)

This 12-bit AC serves as an input/output register for programmed information transfers between core memory and peripheral equipment, and as a transfer register through which arithmetic and logic operations are performed.

# 4.1.2 Link (L)

This 1-bit register extends the arithmetic facilities of the accumulator and serves as the carry register for two's complement arithmetic.

# 4.1.3 Program Counter (PC)

This 12-bit register contains the address of the core-memory location from which the next instruction will be taken.

#### 4.1.4 Memory Address Register (MA)

This 12-bit register contains the address in core memory that is currently selected for reading or writing. This address is decoded by the memory selection matrix to permit addressing of all 4096 words of core memory.

#### 4.1.5 Memory Buffer Register (MB)

All data to be written into core memory is loaded first into the 12-bit MB. Through the facilities provided by the major-register gating network, the MB accepts data fram any of the major registers in the processor and, during a high-speed data-break transfer, from mass-memory devices. Its only output capability, other than its direct access to core memory, is through the processor interface to optional peripheral equipment.

# 4.1.6 Sense Register (SENSE or MEM)

All data read from core memory is strobed first into this 12-bit register. It accepts data only from the core memory and transfers data directly to the Instruction Register (IR) and, through the major register gating network, to other registers in the processor.

# 4.1.7 Instruction Register (IR)

This 3-bit register contains the operation code of the instruction currently being performed by the computer. The three most-significant bits of the current instruction load into the IR from SENSE during a Fetch cycle. The contents of the IR are decoded to produce logic signals for each of the eight basic instructions.

Figure 4-1 System Block Diagram

#### 4.1.8 Switch Register (SR)

The 12-bit SR performs a dual function in that it permits the manual loading of either a discrete core-memory address into the PC or a 12-bit data or control word into core memory. The SR is loaded by 12 toggle switches located on the operator's console. Actuation of either the Load Address or Deposit keys then causes the stored information to be loaded into the PC or MB, respectively.

### 4.2 MAJOR REGISTER GATING NETWORK

All internal data transfers occuring in the PDP-8/I, except those performed through hardwired facilities, such as MEM → IR and MB → MEMORY, are implemented through the major-register gating network. The network contains a separate gate structure and a common register input bus for the 12 bits. Transfers between registers and into and out of memory, as well as the implementing of logical and two's complement arithmetic functions occur through the network. Data and address information received through the I/O interface also pass through this network.

# 4.3 TIMING AND CONTROL ELEMENTS

# 4.3.1 Timing Elements

The processor and memory control circuits in the standard PDP-8/I used fixed and variable delay lines in place of timing clocks. Interleaving of fixed delay sequences provide asynchronous control between the processor and the memory. The overall cycle time of approximately 1.5 µs is determined by the memory timing. For applications involving real time, the KW8/I Real Time Clock option is added to the system.

# 4.3.2 Control Elements

Circuits in the PDP-8/I control program advance and instruction skipping. These circuits, which

operate in response to conditions established in either the processor or peripheral equipment, control the flow of information between registers. In addition, they initiate program interrupt operations during which subroutines enable the servicing of peripheral equipment.

#### 4.4 INPUT/OUTPUT

The PDP-8/I has two bus systems to input/out-put (I/O) equipment: an internal positive bus; and an external negative bus.

Typical of the available internal bus peripherals are paper-tape reader and punch, punched-card reader, incremental plotter, and CRT display equipment. The control logic elements for these options are located in the PDP-8/I processor logic rack. The control logic interfaces with the internal portion of the I/O bus and does not operate through the I/O level converters.

The data-break peripherals, also optionally available, are représented by mass-memory devices such as magnetic tape, magnetic drum, and disk file systems. These peripherals employ the negative external I/O but to communicate with the PDP-8/I. All of the signals to and from these options pass through the I/O level converters.

A Teletype ASR33 Automatic Send-Receive Set is provided as standard equipment with the PDP-8/I. In addition to a manual keyboard and hard-copy printout facilities, the ASR33 contains an 8-level paper-tape punch and a paper-tape reader, all of which are interfaced with the processor through the Teletype control logic. This logic interfaces with the processor in a similar manner as the internal options.

The PDP-8/I integrated circuits operate on logic levels of 0 and +3V. At the present time, most peripherals contain discrete-component control

elements operating on logic levels of 0 and -3V. To permit proper interfacing with these peripherals, the PDP-8/I contains I/O level converters which produce appropriate changes in the levels of both input and output signals. The output circuits, in addition, provide the necessary linedrive capability to operate over interconnecting cables of reasonable lengths. Refer to the Logic Level and Level Converter discussions in Chapter 2, Section 2.8.3.

#### 4.5 MEMORY

The standard memory supplied with the PDP-8/I is a random access, coincident current, magnetic core memory with a storage capacity of 4096 12-bit words. The core planes and diode matrices that make up the core array are mounted on printed circuit cards. These cards plug directly into the PDP-8/I logic rack receptacles. The Extended Memory Control (MC8I) allows an additional 4K of memory with control for 32K of memory to be installed directly into the logic rack as an option. The additional memory fields above 8K are external as the MM8I option. The major functional elements of the core memory are described in the following paragraphs.

# 4.5.1 Core Array

The ferrite-core array consists of  $12.64 \times 64$  core planes. This provides a total of 4096 12-bit words of data and program storage. A thirteenth core plane is optionally available to permit a parity bit for each word in memory.

# 4.5.2 Memory Control

Memory control circuits determine the sequence of operations of the complete read/write memory cycle, starting and stopping each function as required.

#### 4.5.3 Address Selection

The Memory Address register (MA) contains the 12-bit address of the currently selected core-

memory location. This address is decoded through the selection switches and the diode matrix to enable passage of read/write currents through specific X and Y drive lines of the memory. The coincidence of these currents select the specific 12-bit core-memory location desired.

#### 4.5.4 Inhibit Drivers

The PDP-8/I memory is so configured that, unless prohibited, all bit locations of the addressed memory cell would be switched to a logical I during the write portion of the memory cycle. Inhibit drivers, therefore, are used to ensure that the logic 0 levels stored in the MB will be retained in the corresponding bit locations of the addressed memory cell.

#### 4.5.5 Sense Amplifiers

During the read portion of the memory cycle, sense amplifiers detect analog signals induced in the sense windings of the core array. These signals are amplified and used in conjunction with STROBE to set corresponding bits of the SENSE register.

# SECTION II GENERAL THEORY

The following paragraphs discuss the major functional elements of the PDP-8/I in terms of their operational dynamics. These dynamics will be discussed in greater detail in Sections III and IV.

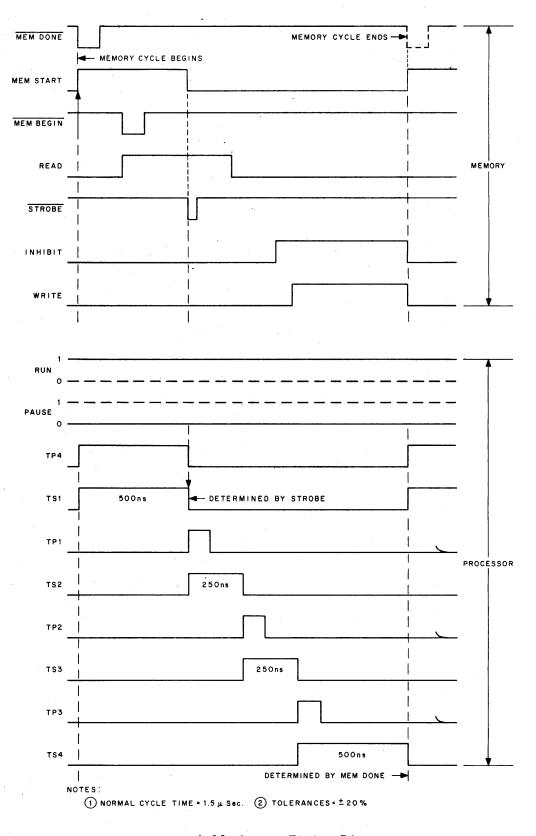

# 4.6 TIME STATES/TIME PULSES

Each computer cycle consists of four basic time divisions, T1, T2, T3, and T4, as denoted on the system flow diagrams. Each time division consists of a time state (TS) and its associated time pulse (TP). The time states each extend

throughout their particular time division (TS1, TS2, TS3, TS4) and end with a time pulse (TP1, TP2, TP3, TP4).

In general, the time states generate enabling levels associated with register outputs. Time pulses are used to strobe data into registers.

#### 4.7 MAJOR STATES

The PDP-8/I contains six major-state flip-flops. These are: Fetch, Defer, Execute, Word Count, Current Address, and Break. The outputs of these flip-flops generate enabling levels used within the control elements of the processor to implement particular machine functions.

The first three major states (Fetch, Defer, and Execute) are sufficient to perform most machine functions in the areas of logical operations, arithmetic functions, memory read/write operations, and data transfers through the processor I/O bus. The last three major states (Word Count, Current Address, and Break) are used only for high-speed data transfers through the Data-Break facility.

The processor determines, near the end of each computer cycle, which major state will be needed for the activities to be performed in the next computer cycle. At the very end of the cycle (TP4) the new major-state will be entered by the setting of that particular flip-flop.

## 4.8 INTERNAL DATA FLOW

The simplified system block diagram shown in Figure 4–1 depicts the flow of data through the major elements of the PDP-8/I. Note that all data transfers into the four major registers (AC, PC, MB, and MA) occur through a register gating network and a common register bus. The outputs of these four registers, plus the SENSE and SR, and the data input from the interface are all connected to the input gates of the major-register gating network.

This permits incoming data to be strobed into any desired major register, or the contents of any register to be complemented, incremented, or transferred into any other major register. The complementing function is implemented by transferring the 0 output of the desired register through the gating network and back into the same register. The incrementing function is performed by transferring the 1 output of the register through the gating network while inserting a carry into the low-order bit of the word. The data is then transferred back into the desired register.

#### 4.9 INSTRUCTIONS

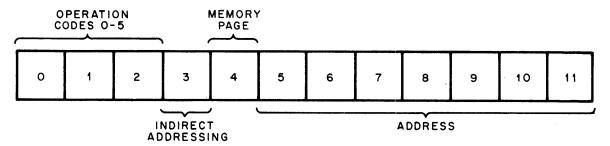

Instruction words are of two types: memory reference and augmented. Memory reference instructions store or retrieve data from core memory, while augmented instructions do not. All instructions utilize bits 0 through 2 to specify the operation code. Operation codes of 0g through 5g specify memory reference instructions, and codes of 6g and 7g specify augmented instructions. Memory reference instruction execution times are multiples of the 1.5 µs memory cycle. Indirect addressing increases the execution time of a memory reference instruction by 1.5 µs. The augmented instructions, input-output transfer, and operate, are performed in 4.25 and 1.5 µs respectively. (All computer times are ±20%.)

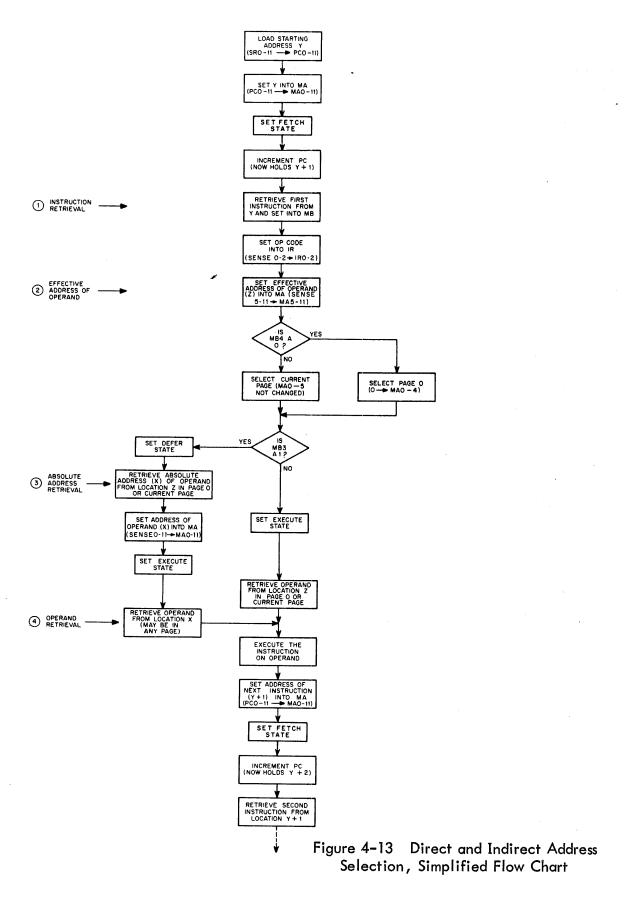

## 4.9.1 Memory Reference Instructions

Since the PDP-8/I system contains a 4096-word core memory, 12 bits are required to address all locations. To simplify addressing, the core memory is divided into blocks, or pages, of 128 words (200<sub>8</sub> addresses). Pages are numbered 0<sub>8</sub> through 37<sub>8</sub>; each field of 4096-words of core memory uses 32 pages. The seven address bits (bits 5 through 11) of a memory reference instruction can address any location in the page on which the current instruction is located by placing a 1 in bit 4 of the instruction. By placing a 0 in bit 4 of the instruction, any location in page 0 can be

addressed directly from any page of core memory. All other core memory locations can be addressed indirectly by placing a 1 in bit 3 and placing a 7-bit effective address in bits 5 through 11 of the instruction to specify the location in the current page or page 0 which contains the full 12-bit absolute address of the operand.

Word format of memory reference instructions is shown in Figure 4.2 and the instructions perform as follows:

## Logical AND (AND Y)

Octal Code: 0

Indicators: AND, FETCH, EXECUTE

Execution Time: 3.0 µs with direct addressing,

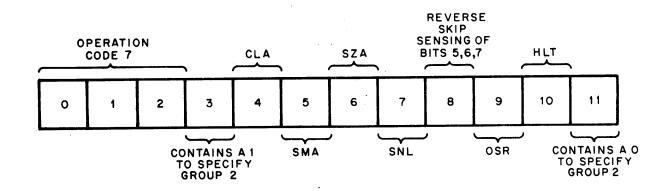

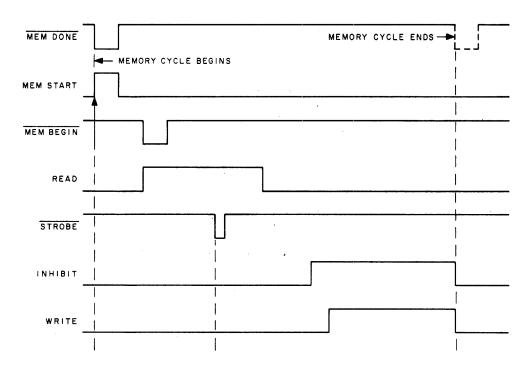

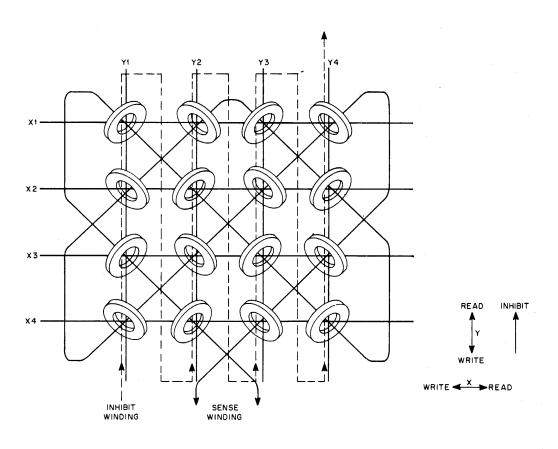

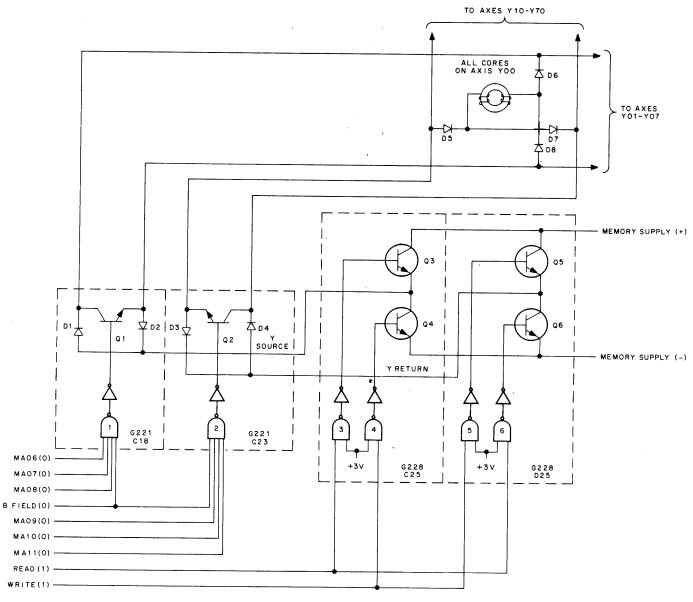

4.5 µs with indirect addressing.