DEC-8E-HR3B-D-VT8-E

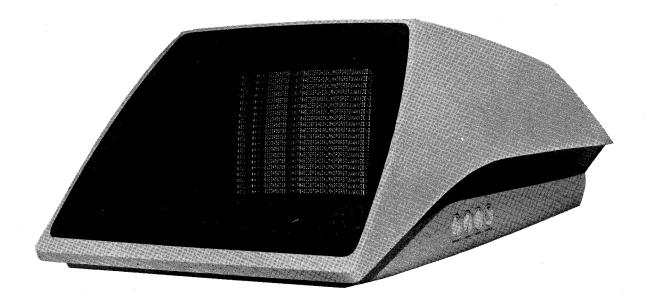

# VT8-E HIGH SPEED VIDEO DISPLAY TERMINAL AND CONTROL OPTION

The information in this preliminary manual will become, in its final form, a part of the PDP-8/E/F/M Maintenance Manual, Volume 3.

## **PRELIMINARY**

Copyright © 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

**DIGITAL**

**COMPUTER LAB**

#### CONTENTS

| CHAPTER 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                                      | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------|------|

| 12.1   SYSTEM OPERATING SPECIFICATIONS   12-2     12.1.1   CRT Operating Specifications (Motorola Raster Display)   12-2     12.1.2   Visible Display Specifications   12-3     12.1.2.1   Alphanumeric Mode   12-3     12.1.2.2   Graphic Mode   12-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CHAPTER 12 | VT8-E HIGH SPEED VIDEO DISPLAY TERMINAL AND CONTROLS |      |

| 12.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | Section 1 — Introduction                             |      |

| 12.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12.1       | SYSTEM OPERATING SPECIFICATIONS                      | 12-2 |

| 12.1.2       Visible Display Specifications       12.3         12.1.2.1       Alphanumeric Mode       12.3         12.1.2.2       Graphic Mode       12.3         Section 2 — Installation and Acceptance Test         12.2       UNPACKING       12.4         12.2.1       Primary Power       12.4         12.2.2       VT8-E Installation       12.5         Section 3 — Operation and Programming         12.3         FUNCTIONAL DESCRIPTION       12.8         2.3.1       VT8-E Printer/Keyboard Control Module (M8335)       12.8         12.3.1.1       MD Bus Gating       12.8         12.3.1.2       IOT Decoders       12.9         12.3.1.3       Data Bus Gating       12.9         12.3.1.4       Keyboard Buffer       12.10         12.3.1.5       I/O Transfer Control       12.10         12.3.1.6       Interrupt and Skip Logic       12.10         12.3.1.7       Interrupt Logic       12.10         12.3.1.8       Starting Address Register and Counter (SAR)       12.10         12.3.1.1       Printer Buffer       12.10         12.3.1.1       Printer Buffer       12.10         12.3.1.1 </td <td>12.1.1</td> <td></td> <td></td>                                                  | 12.1.1     |                                                      |      |

| 12.1.2.1   Alphanumeric Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12.1.2     |                                                      |      |

| Section 2 - Installation and Acceptance Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12.1.2.1   |                                                      |      |

| 12.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.1.2.2   |                                                      |      |

| 12.2.1       Primary Power       12.4         12.2.2       VT8-E Installation       12.5         12.2.3       Acceptance Test       12.8         Section 3 – Operation and Programming         Interval of Experiment (Neyboard Control Module (M8335)         12.3.1       VT8-E Printer/Keyboard Control Module (M8335)       12-8         12.3.1.1       MD Bus Gating       12-8         12.3.1.2       IOT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt and Skip Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.2.1       Higher Priority Detection       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4                                  |            | Section 2 — Installation and Acceptance Test         |      |

| 12.2.1       Primary Power       12.4         12.2.2       VT8-E Installation       12-5         12.2.3       Acceptance Test       12-8         Section 3 – Operation and Programming         Interval of Exemption of Exemption of Exemption Section 3 – Operation and Programming         12.3.1         VT8-E Printer/Keyboard Control Module (M8335)       12-8         12.3.1.1       MD Bus Gating       12-8         12.3.1.2       IOT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt and Skip Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.2.1       Higher Priority Detection       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer<                              |            |                                                      |      |

| 12.2.2   VT8-E Installation   12.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                      |      |

| Section 3 - Operation and Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                      |      |

| Section 3 - Operation and Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                      |      |

| 12.3       FUNCTIONAL DESCRIPTION       12-8         12.3.1       VT8-E Printer/Keyboard Control Module (M8335)       12-8         12.3.1.1       MD Bus Gating       12-8         12.3.1.2       IOT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.1       PRINT DONE Flag       12-10         12.3.1.1       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffer Module (M8337)       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic                 | 12.2.3     | Acceptance Test                                      | 12-8 |

| 12.3.1       VT8-E Printer/Keyboard Control Module (M8335)       12.8         12.3.1.1       MD Bus Gating       12-8         12.3.1.2       IOT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.2.1       Higher Priority Detection       12-10         12.3.2.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Con |            | Section 3 — Operation and Programming                |      |

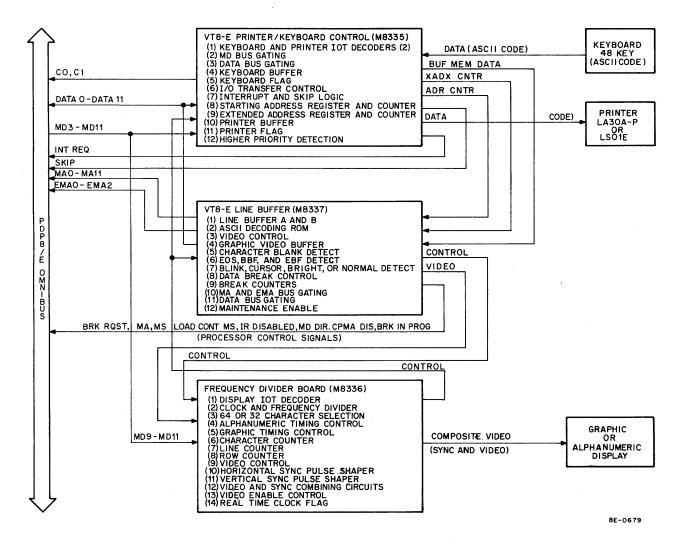

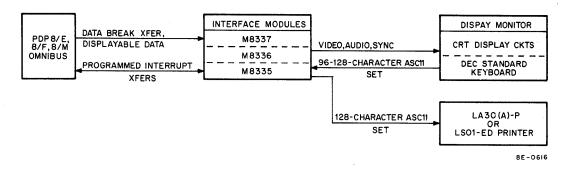

| 12.3.1       VT8-E Printer/Keyboard Control Module (M8335)       12.8         12.3.1.1       MD Bus Gating       12.8         12.3.1.2       IOT Decoders       12.9         12.3.1.3       Data Bus Gating       12.9         12.3.1.4       Keyboard Buffer       12.10         12.3.1.5       I/O Transfer Control       12.10         12.3.1.6       Interrupt and Skip Logic       12.10         12.3.1.7       Interrupt Logic       12.10         12.3.1.8       Starting Address Register and Counter (SAR)       12.10         12.3.1.9       Extended Starting Address Register       12.10         12.3.1.10       Printer Buffer       12.10         12.3.1.11       PRINT DONE Flag       12.10         12.3.2.1       Higher Priority Detection       12.10         12.3.2.2       VT8-E Line Buffer Module (M8337)       12.11         12.3.2.1       Line Buffers A and B       12.11         12.3.2.2       ASCII Decoding ROMs       12.11         12.3.2.3       Graphic Video Buffer       12.11         12.3.2.4       Character Display Mode Detection Logic       12.11         12.3.2.5       Visible Field Detection Logic       12.11         12.3.2.6       Single Cycle Data Break Con | 12.3       | FUNCTIONAL DESCRIPTION                               | 12-8 |

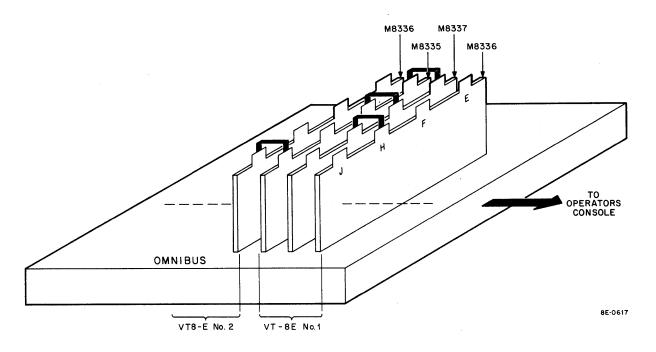

| 12.3.1.1       MD Bus Gating       12-8         12.3.1.2       1OT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.2       Higher Priority Detection       12-10         12.3.2.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.8       Break Counters       12-          | 12.3.1     | VT8-E Printer/Keyboard Control Module (M8335)        | 12-8 |

| 12.3.1.2       IOT Decoders       12-9         12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.2.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable           |            |                                                      |      |

| 12.3.1.3       Data Bus Gating       12-9         12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.2.1       Higher Priority Detection       12-10         12.3.2.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-11         12.3.2.7       Processor Control Signals       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance En |            |                                                      |      |

| 12.3.1.4       Keyboard Buffer       12-10         12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus G |            |                                                      |      |

| 12.3.1.5       I/O Transfer Control       12-10         12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Exteended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2.1       Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffer Module (M8337)       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Da |            |                                                      |      |

| 12.3.1.6       Interrupt and Skip Logic       12-10         12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency D |            |                                                      |      |

| 12.3.1.7       Interrupt Logic       12-10         12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                             |            |                                                      |      |

| 12.3.1.8       Starting Address Register and Counter (SAR)       12-10         12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                |            |                                                      |      |

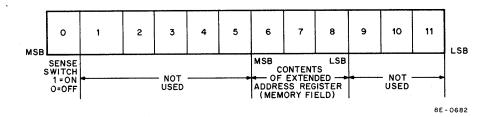

| 12.3.1.9       Extended Starting Address Register       12-10         12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                               |            |                                                      |      |

| 12.3.1.10       Printer Buffer       12-10         12.3.1.11       PRINT DONE Flag       12-10         12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                     |            |                                                      |      |

| 12.3,1.11       PRINT DONE Flag       12-10         12.3,1.12       Higher Priority Detection       12-10         12.3,2       VT8-E Line Buffer Module (M8337)       12-11         12.3,2.1       Line Buffers A and B       12-11         12.3,2.2       ASCII Decoding ROMs       12-11         12.3,2.3       Graphic Video Buffer       12-11         12.3,2.4       Character Display Mode Detection Logic       12-11         12.3,2.5       Visible Field Detection Logic       12-11         12.3,2.6       Single Cycle Data Break Control Logic       12-12         12.3,2.7       Processor Control Signals       12-12         12.3,2.8       Break Counters       12-12         12.3,2.9       MA and EMA Bus Gates       12-12         12.3,2.10       Data Bus Gates       12-12         12.3,2.11       Maintenance Enable       12-12         12.3,2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                        |            |                                                      |      |

| 12.3.1.12       Higher Priority Detection       12-10         12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                            |            |                                                      |      |

| 12.3.2       VT8-E Line Buffer Module (M8337)       12-11         12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                      |      |

| 12.3.2.1       Line Buffers A and B       12-11         12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                      |      |

| 12.3.2.2       ASCII Decoding ROMs       12-11         12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                      |      |

| 12.3.2.3       Graphic Video Buffer       12-11         12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                      |      |

| 12.3.2.4       Character Display Mode Detection Logic       12-11         12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | ·                                                    |      |

| 12.3.2.5       Visible Field Detection Logic       12-11         12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                                                      |      |

| 12.3.2.6       Single Cycle Data Break Control Logic       12-12         12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                      |      |

| 12.3.2.7       Processor Control Signals       12-12         12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                      |      |

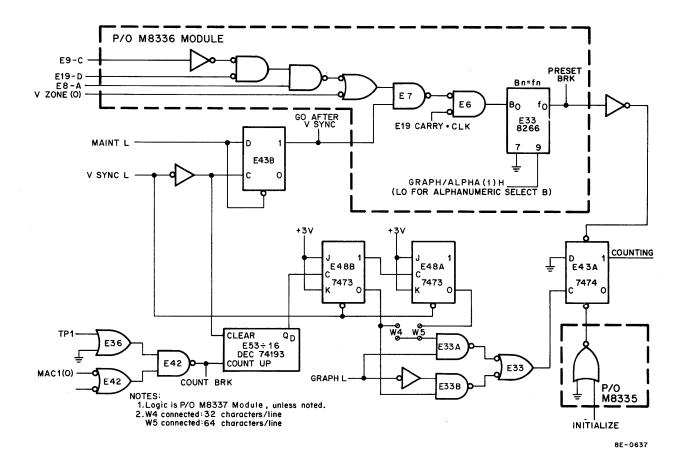

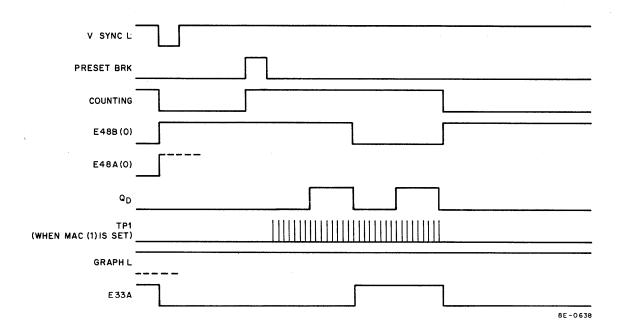

| 12.3.2.8       Break Counters       12-12         12.3.2.9       MA and EMA Bus Gates       12-12         12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                      |      |

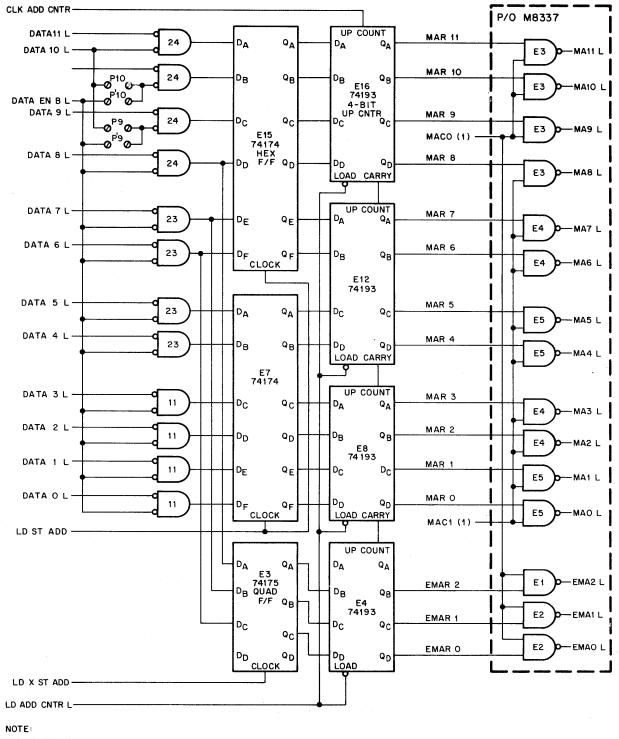

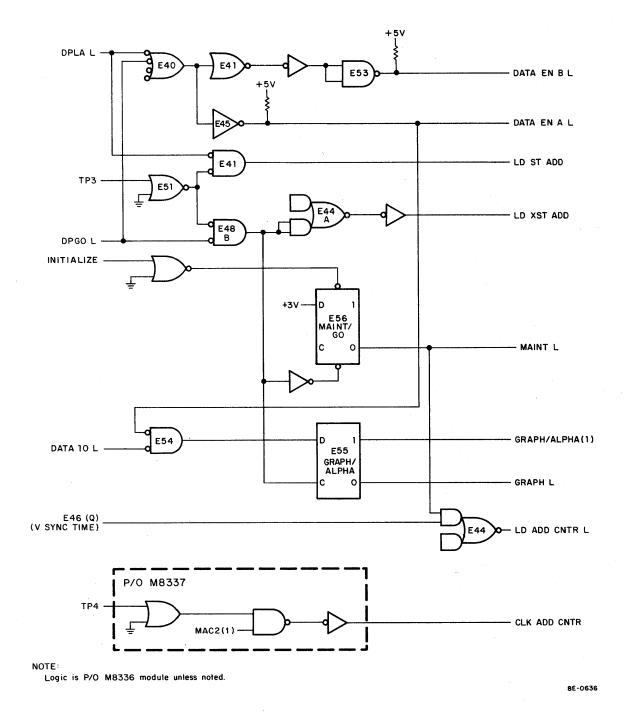

| 12.3.2.9       MA and EMA Bus Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | <del>-</del>                                         |      |

| 12.3.2.10       Data Bus Gates       12-12         12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                      |      |

| 12.3.2.11       Maintenance Enable       12-12         12.3.2.12       Frequency Divider Board (M8336)       12-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                      |      |

| 12.3.2.12 Frequency Divider Board (M8336)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                      |      |

#### **CONTENTS (Cont)**

|           |                                                                                 | Page  |

|-----------|---------------------------------------------------------------------------------|-------|

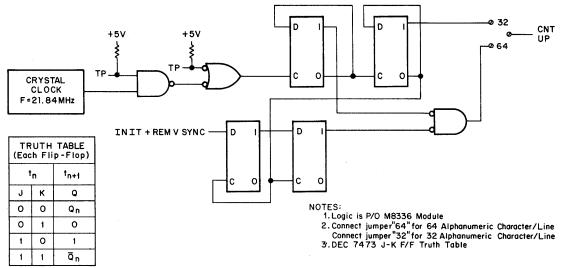

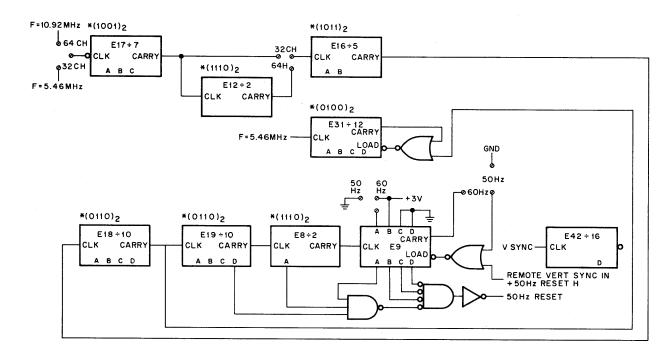

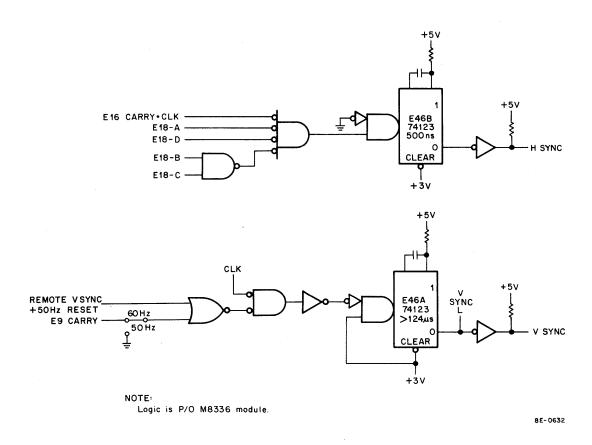

| 12.3.3    | VT8-E Clock and Frequency Divider (M8336)                                       | 12-12 |

| 12.3.3.1  | Real Time Clock Flag                                                            | 12-12 |

| 12.3.3.2  | Video and Sync Combining Circuits                                               | 12-13 |

| 12.3.4    | IOT Instructions                                                                | 12-13 |

| 12.3.4.1  | Display Instructions                                                            | 12-13 |

| 12.3.4.2  | Keyboard Instructions                                                           | 12-14 |

| 12.3.4.3  | Printer Instructions                                                            | 12-16 |

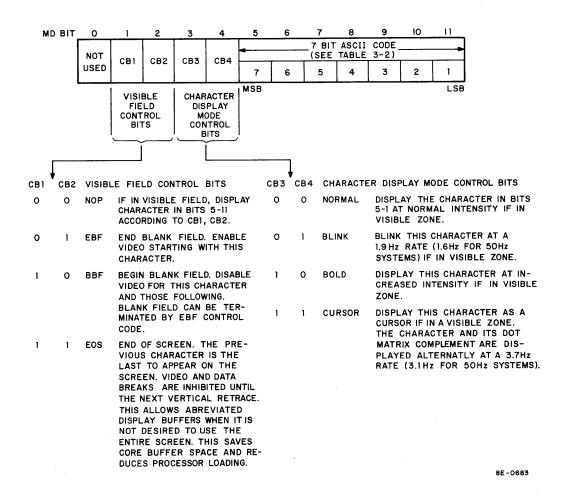

| 12.3.5    | Display Data Format                                                             | 12-17 |

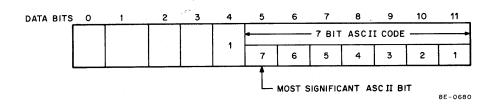

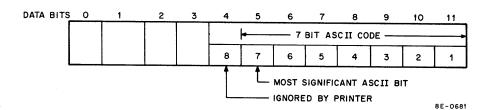

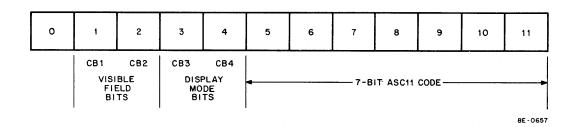

| 12.3.5.1  | Alphanumeric Data Format                                                        | 12-17 |

| 12.3.5.2  | Graphic Data Format                                                             | 12-18 |

| 12.3.6    | Display Monitor and Keyboard Switches and Controls                              | 12-18 |

| 12.3.6.1  | Display Monitor Switches and Controls                                           | 12-18 |

| 12.3.6.2  | Keyboard Controls                                                               | 12-18 |

| 12.3.7    | Programming Examples                                                            |       |

| 12.3.7.1  | Graphic Display Program Example                                                 |       |

| 12.3.7.2  | Alphanumeric Display Program Example                                            |       |

| 12,0.7.2  | , aprilation of opinity in egitain Example 111111111111111111111111111111111111 |       |

|           | Section 4 — Detailed Logic Description                                          |       |

|           |                                                                                 |       |

| 12.4      | INTRODUCTION                                                                    |       |

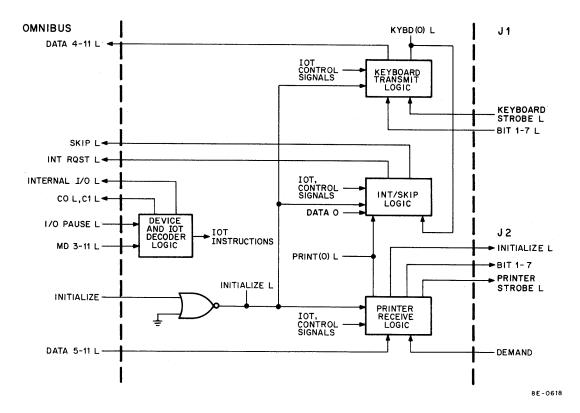

| 12.4.1    | Keyboard/Printer Logic                                                          |       |

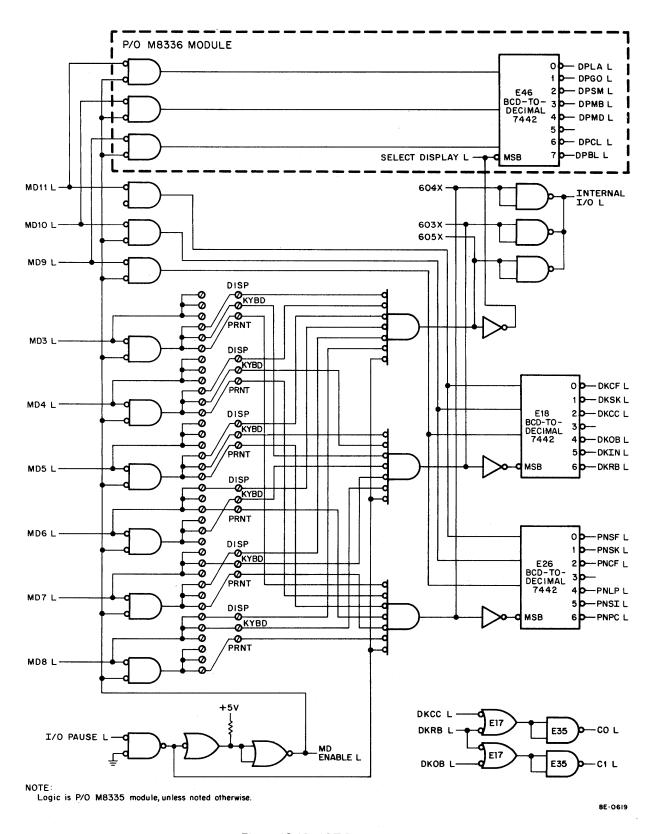

| 12.4.1.1  | IOT Decoder Logic                                                               |       |

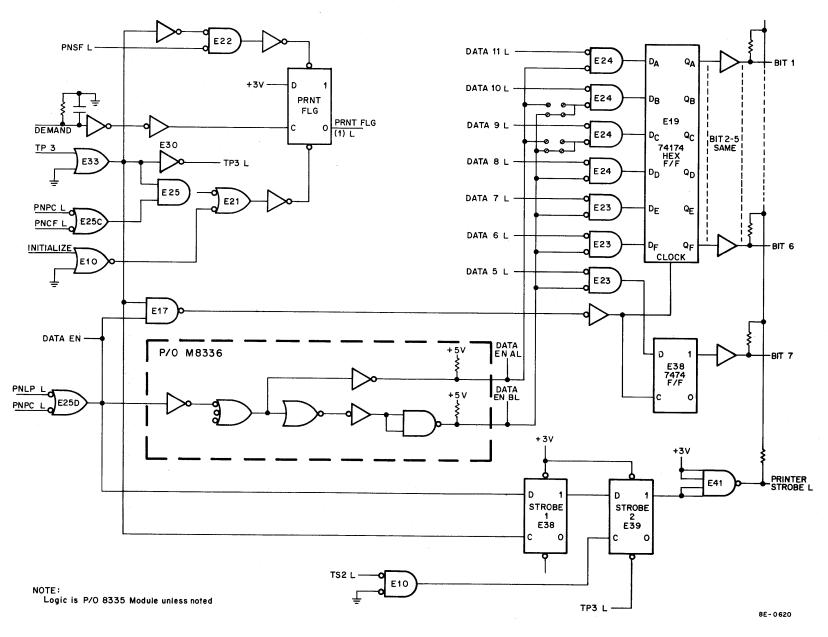

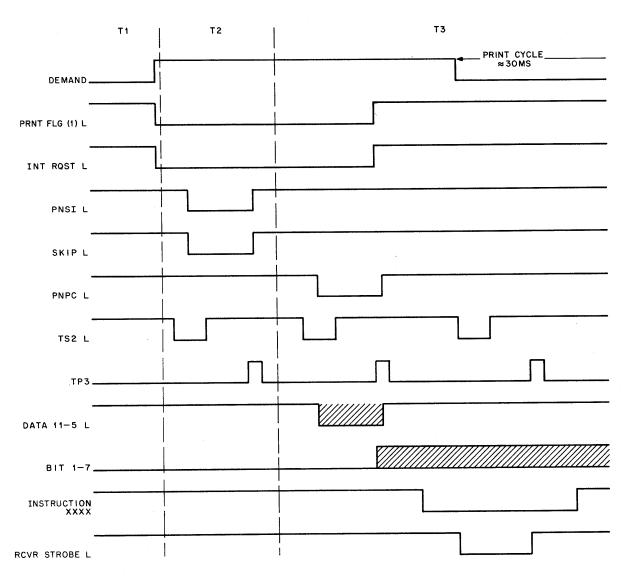

| 12.4.1.2  | Printer Receive Logic                                                           |       |

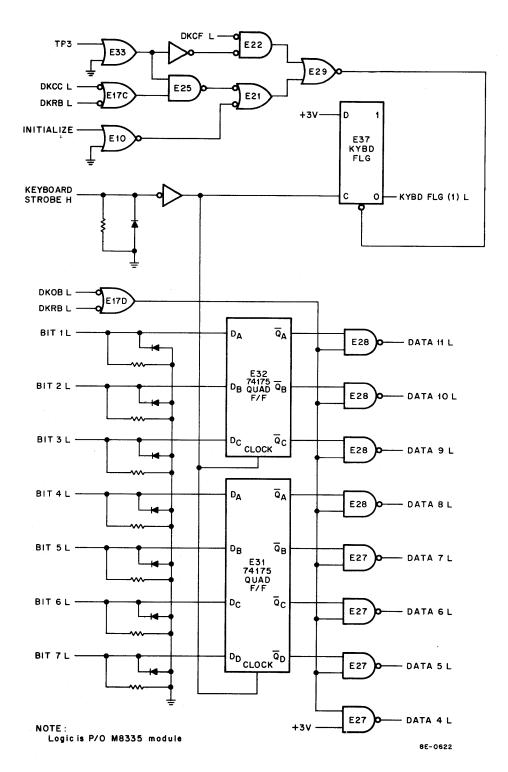

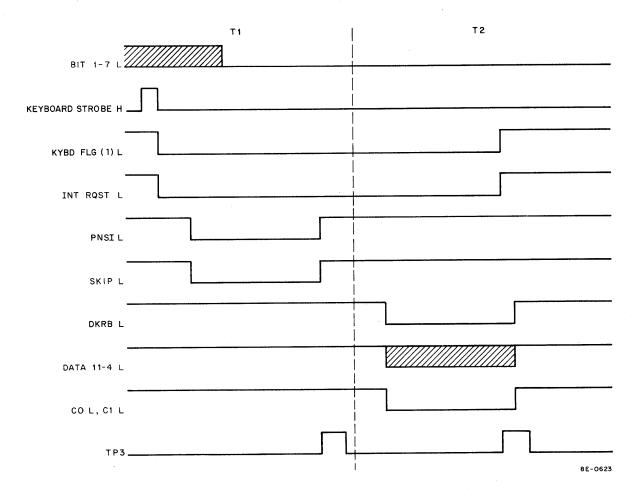

| 12.4.1.3  | Keyboard Transmit Logic                                                         |       |

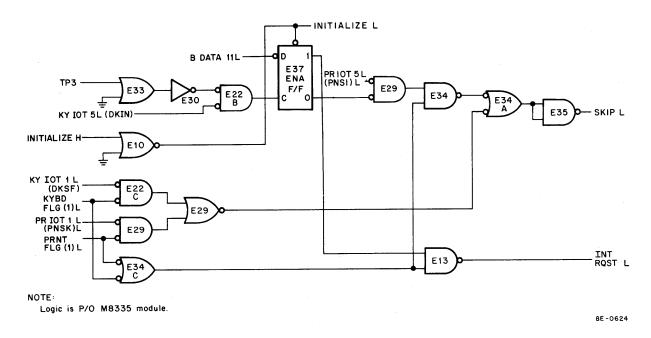

| 12.4.1.4  | INT/SKIP Logic                                                                  |       |

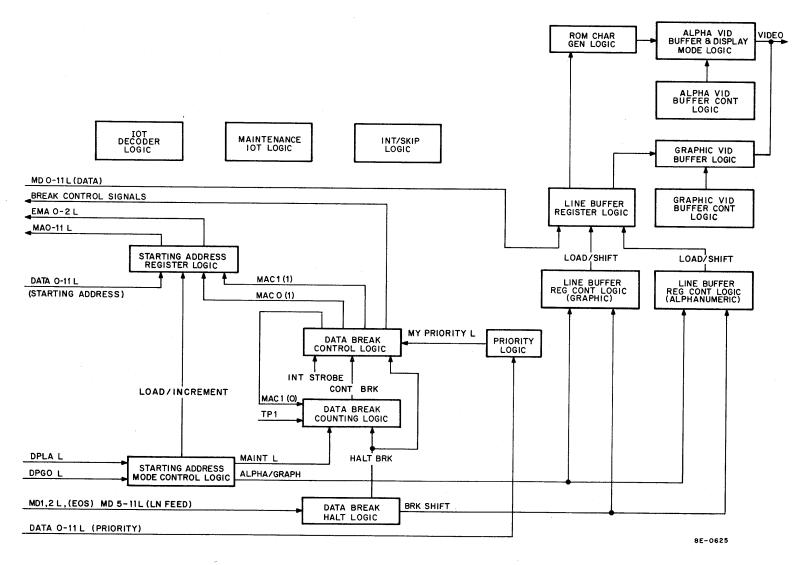

| 12.4.2    | Display Logic                                                                   |       |

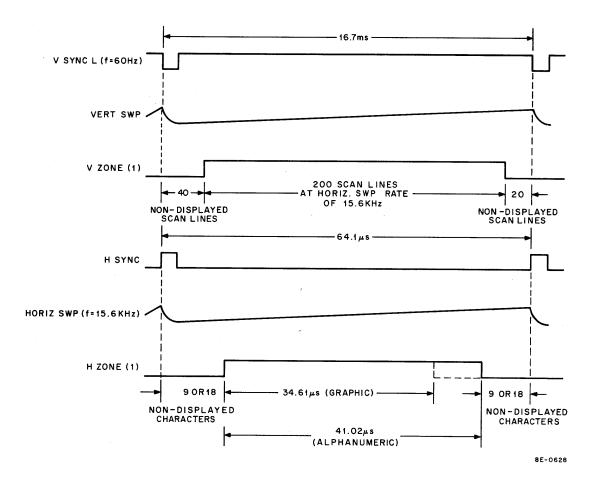

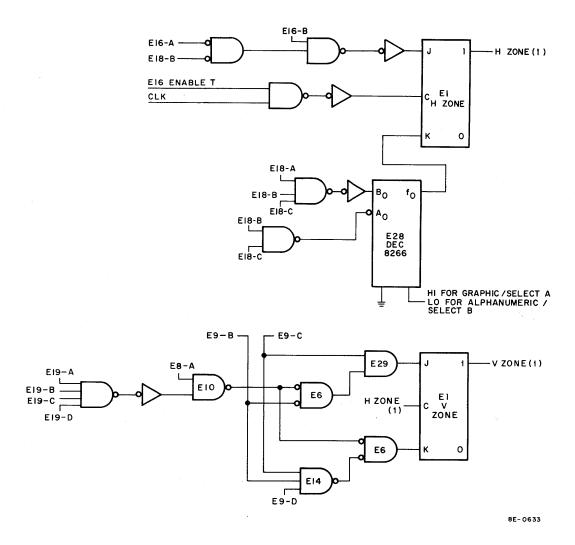

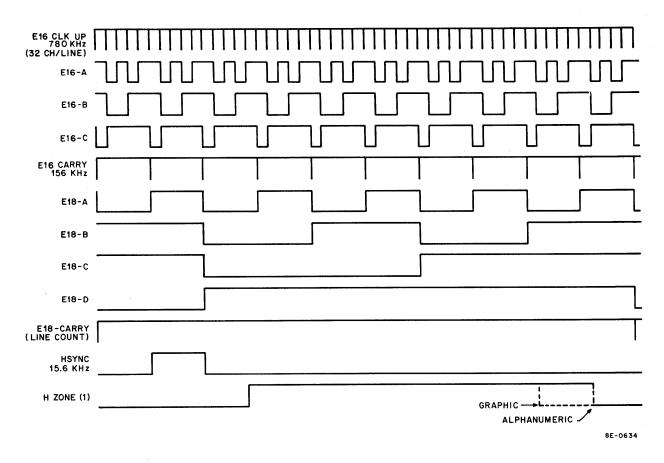

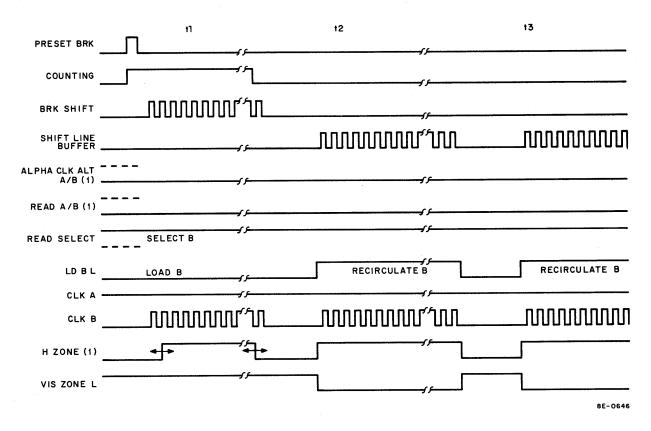

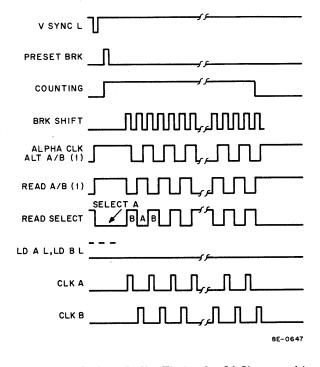

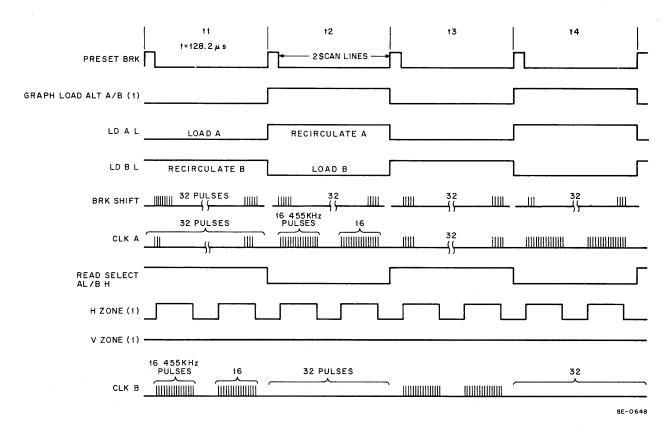

| 12.4.2.1  | VT8-E Timing                                                                    |       |

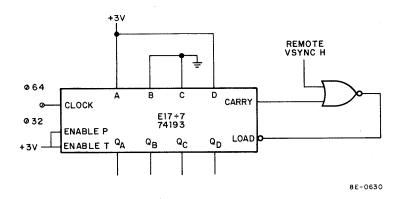

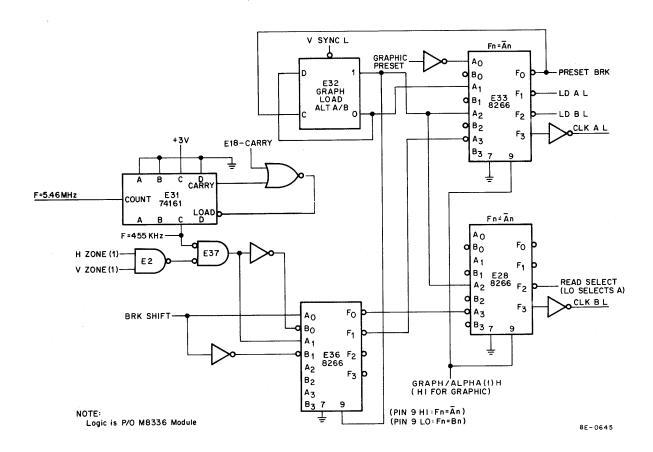

| 12.4.2.2  | VT8-E Timing Logic                                                              |       |

| 12.4.2.3  | Starting Address Register Logic                                                 |       |

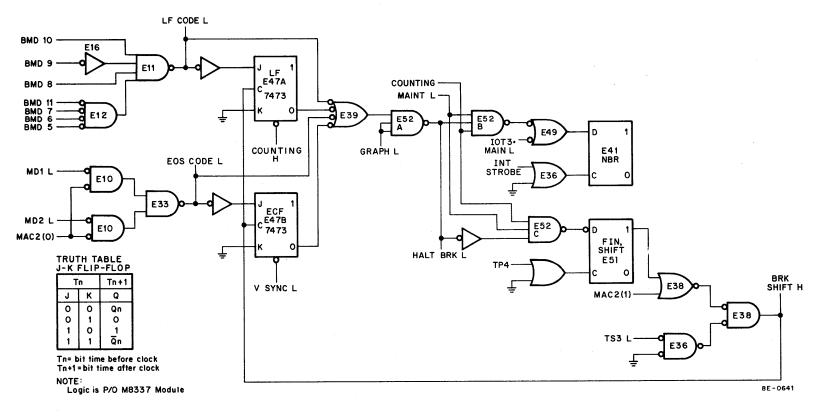

| 12.4.2.4  | Data Break Counting Logic                                                       |       |

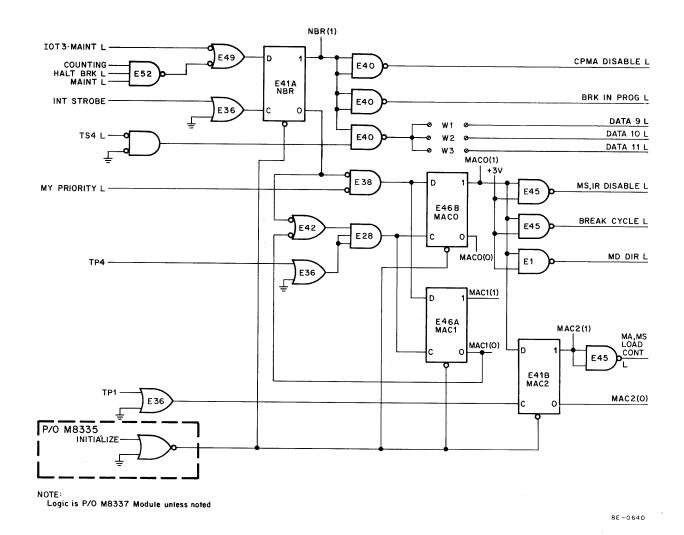

| 12.4.2.5  | Data Break Control Logic                                                        |       |

| 12.4.2.6  | Data Break Halt, Line Feed, and End-of-Screen Logic                             |       |

| 12.4.2.7  | Priority Logic                                                                  |       |

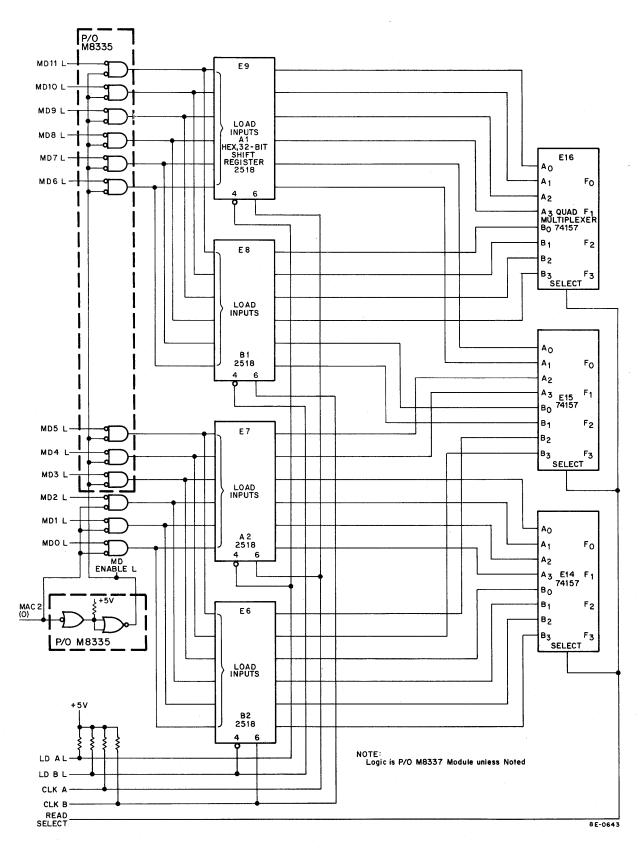

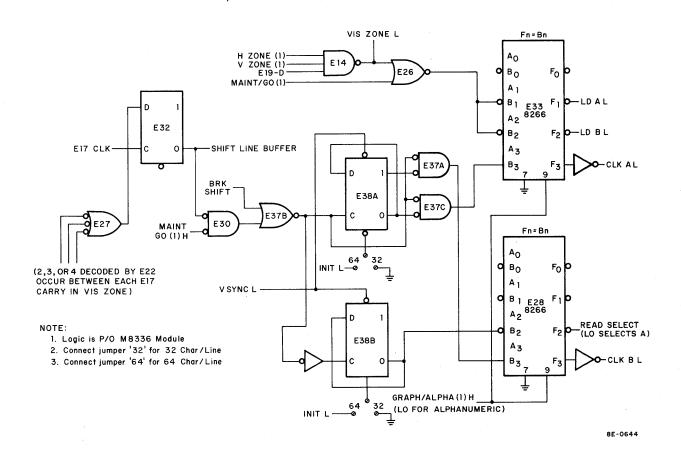

| 12.4.2.8  | Line Buffer Register and Control Signal Logic                                   |       |

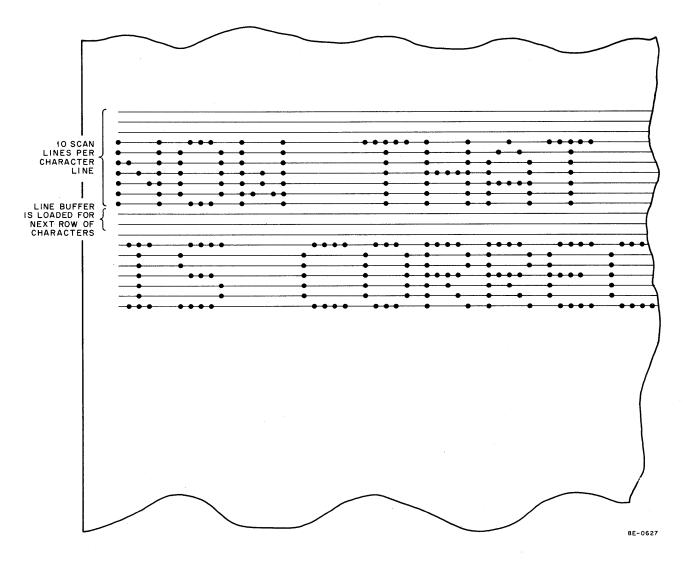

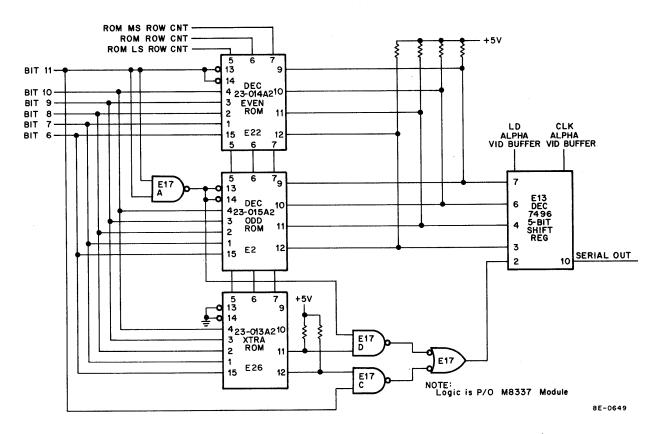

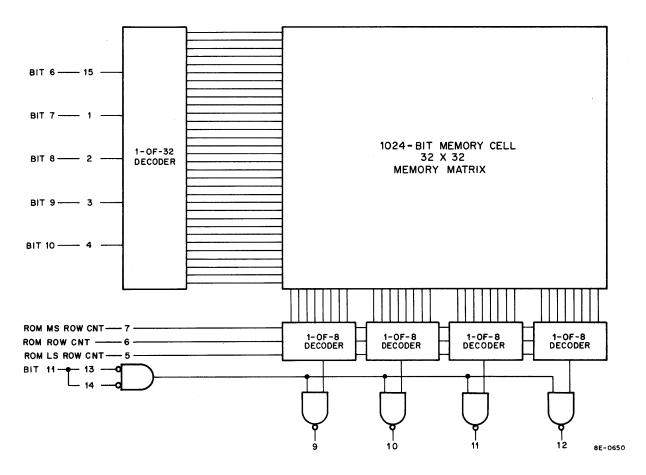

| 12.4.2.9  | ROM Character Generator Logic                                                   | 12-53 |

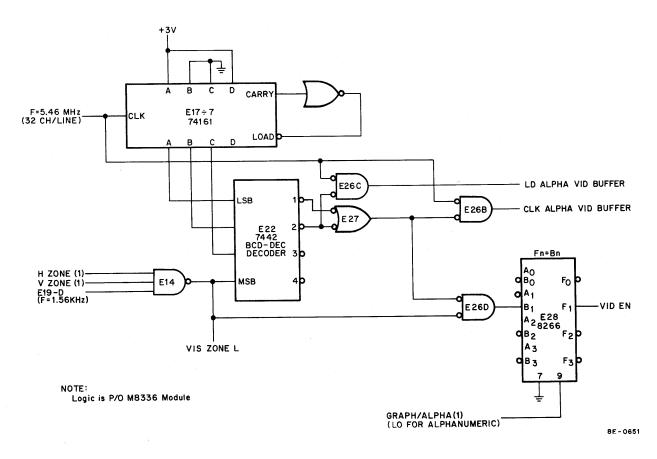

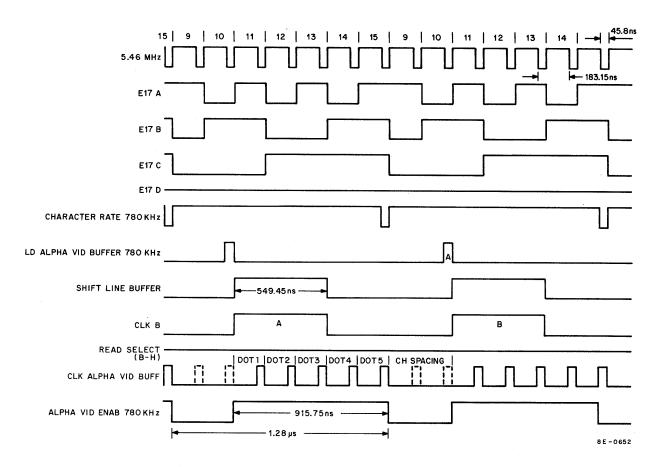

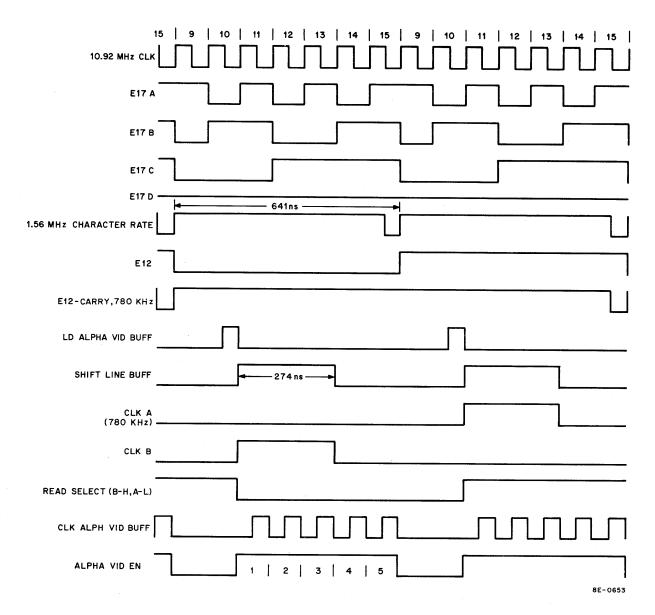

| 12.4.2.10 | Alphanumeric Video Buffer Control Logic                                         | 12-56 |

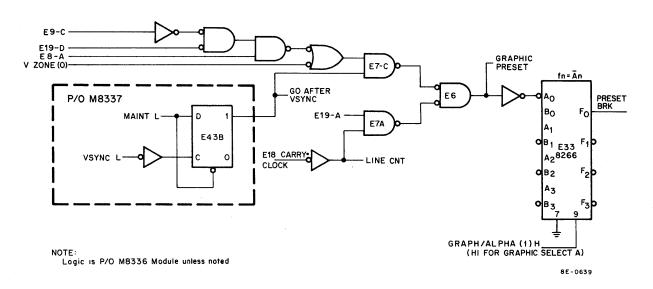

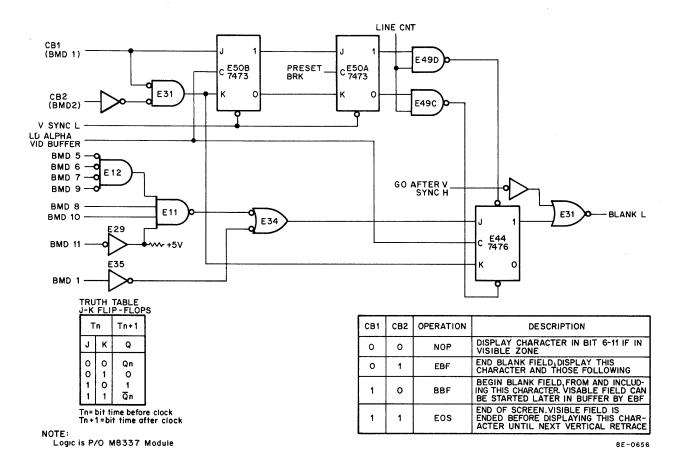

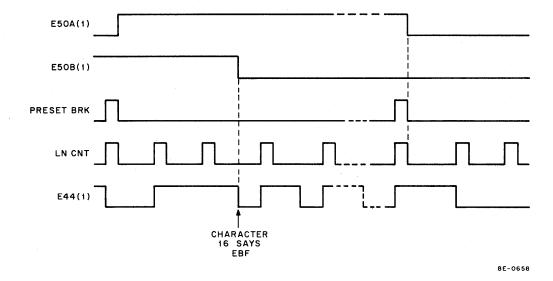

| 12.4.2.12 | Visible Field Logic                                                             | 12-59 |

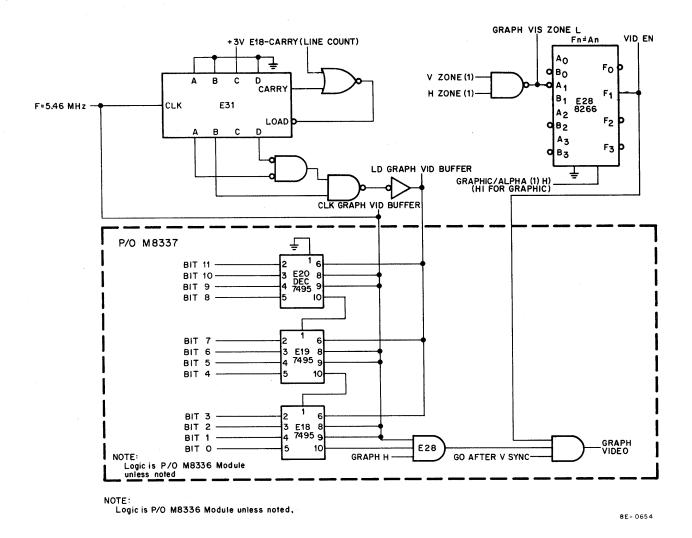

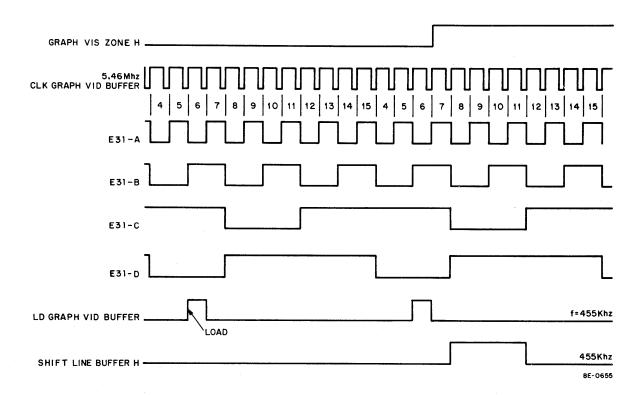

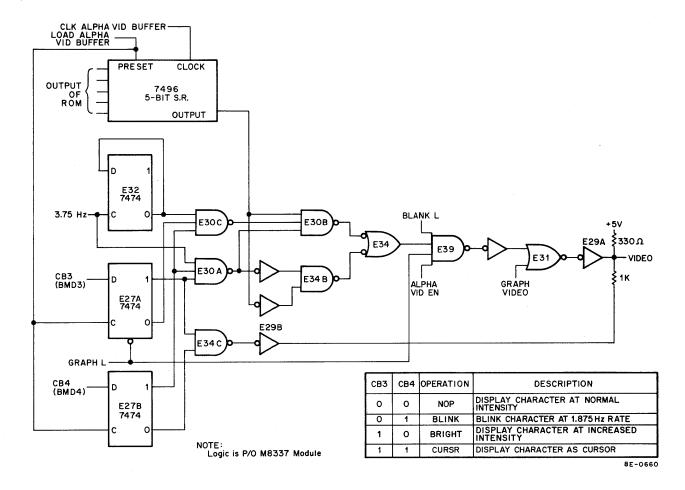

| 12.4.2.13 | Display Mode Logic                                                              | 12-61 |

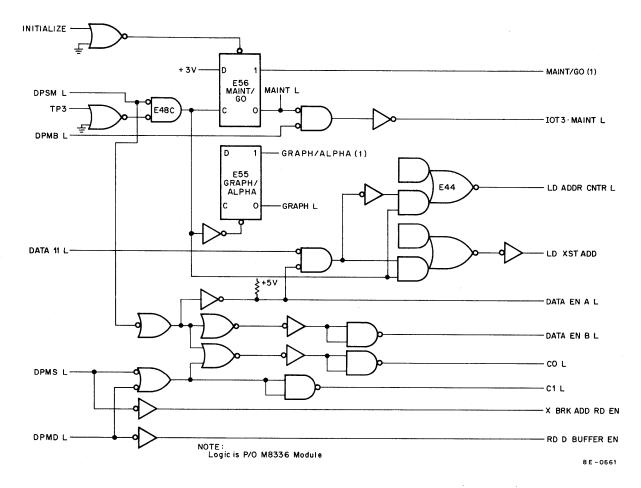

| 12.4.2.14 | Maintenance IOT Logic                                                           | 12-63 |

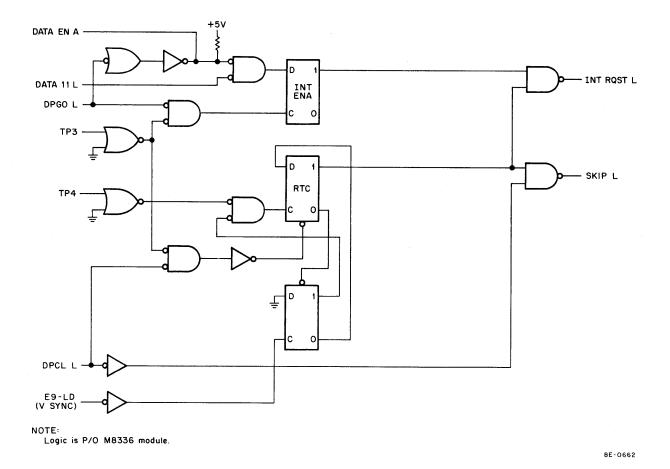

| 12.4.2.15 | Display Interrupt and Skip Logic                                                | 12-63 |

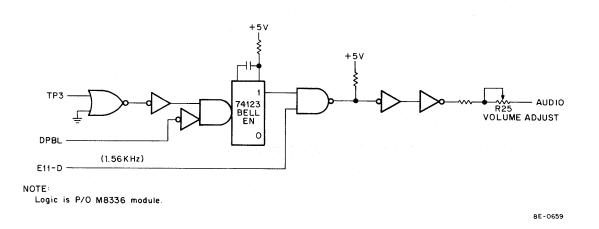

| 12.4.2.16 | Bell Logic                                                                      | 12-64 |

| 12.5      | DISPLAY MONITOR CIRCUITS                                                        | 12-64 |

| 12.5.1    | Keyboard Logic                                                                  | 12-64 |

| 12.5.2    | Motorola CRT Display                                                            | 12-66 |

| 12.5.2.1  | Video Amplifier                                                                 | 12-66 |

| 12.5.2.2  | Sync Separator                                                                  | 12-66 |

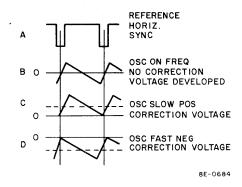

| 12.5.2.3  | Phase Detector                                                                  | 12-66 |

#### **CONTENTS (Cont)**

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 12.5.2.4                                                                                                                            | Horizontal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-67                                                                                                   |

| 12.5.2.5                                                                                                                            | Pulse Shaper and Horizontal Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| 12.5.2.6                                                                                                                            | Horizontal Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| 12.5.2.7                                                                                                                            | Vertical Oscillator Driver and Output                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        |

| 12.5.2.7                                                                                                                            | Retrace Blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |

| 12.5.2.9                                                                                                                            | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12-00                                                                                                  |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |

|                                                                                                                                     | Section 5 — Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                        |

| 12.6                                                                                                                                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12-68                                                                                                  |

| 12.6.1                                                                                                                              | Equipment Required                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |

| 12.6.2                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-69<br>12-69                                                                                         |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-69<br>12-69                                                                                         |

| 12.6.3                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-09<br>12-70                                                                                         |

| 12.6.3.1                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |

| 12.6.4                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-70                                                                                                  |

| 12.6.4.1                                                                                                                            | -/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12-70                                                                                                  |

| 12.6.4.2                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-70                                                                                                  |

| 12.6.4.3                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-70                                                                                                  |

| 12.6.4.3.1                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-70                                                                                                  |

| 12.6.4.3.2                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-70                                                                                                  |

| 12.6.4.3.3                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-71                                                                                                  |

| 12.6.4.3.4                                                                                                                          | CRT Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12-71                                                                                                  |

| APPENDIX A                                                                                                                          | ROM PATTERN TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |