## DWMVA VME Adapter Technical Manual

Order Number: EK-DWMVA-TM-001

This manual is for software developers who write drivers and application programs for the DWMVA adapter in VAX 6000 systems.

**Digital Equipment Corporation**

#### First Printing, August 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1991 by Digital Equipment Corporation

All Rights Reserved. Printed in U.S.A.

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

DEC DEC LANcontroller DECnet DECUS DWMVA PDP ULTRIX UNIBUS VAX VAXBI VAXcluster VAXELN VMS XMI digitaI

This document was prepared using VAX DOCUMENT, Version 1.2

## Contents

| PREF      | ACE                                                                                                                         | ix  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| CHAPTER 1 | OVERVIEW                                                                                                                    | 1–1 |

| 1.1       | MAJOR COMPONENTS                                                                                                            | 1–1 |

| 1.2       | MAJOR BUSES<br>1.2.1 XMI Bus<br>1.2.2 VMEbus                                                                                |     |

|           | 1.2.2 VMEBUS                                                                                                                |     |

| 1.3       | TRANSACTIONS                                                                                                                | 1–3 |

| 1.4       | INTERRUPTS                                                                                                                  | 1–4 |

| CHAPTER 2 | ADDRESS MAPPING                                                                                                             | 2–1 |

| 2.1       | XMI MEMORY SPACE                                                                                                            | 2–2 |

| 2.2       | XMI I/O SPACE         2.2.1       Private Space         2.2.2       Nodespace         2.2.3       I/O Adapter Address Space | 2–3 |

| 2.3       | VME ADDRESS SPACE                                                                                                           | 2–4 |

| 2.4       | ADDRESS TRANSLATION IN CPU TRANSACTIONS                                                                                     | 2–6 |

| 2.5       | ADDRESS TRANSLATION IN DMA TRANSACTIONS<br>2.5.1 No Address Translation<br>2.5.2 34-Bit VAX Address Translation             | -   |

#### Contents

| 2.5.3 | 40-Bit VAX | Address Translation       | 2–12 |

|-------|------------|---------------------------|------|

|       | 2.5.3.1    | 512-Byte Page Size • 2–12 |      |

|       | 2.5.3.2    | 4-Kbyte Page Size • 2–14  |      |

|       | 2.5.3.3    | 8-Kbyte Page Size • 2–16  |      |

#### CHAPTER 3 VME SYSTEM CONTROL 3–1 3.1 **BUS TIMER** 3–2 ARBITRATION 3.2 3–3 3.2.1 Arbitration Subsystem Input/Output 3–3 Arbitration Algorithms 3.2.2 3–4 3.2.3 Bus Request Level Assignment 3–5 3.2.4 Arbitration Timeout Counter 3–6 3.2.5 Data Transfer Bus Requesters 3–6 3.3 IACK DAISY-CHAIN DRIVER 3–8 3.4 SYSTEM CLOCK DRIVER 3–9 3.5 SERIAL CLOCK DRIVER 3–9 3–10 3.6 POWER MONITOR

# CHAPTER 4 TRANSACTIONS 4.1 COMMAND TRANSLATION

| COMM  | AND TRANSLATION        | 4–2     |

|-------|------------------------|---------|

| 4.1.1 | XMI-to-VME Translation | <br>4–2 |

| 4.1.2 | VME-to-XMI Translation | <br>4–3 |

4–1

| 4.2 | CPU TRANSACTION PROCESS |          | 4–3                               |     |

|-----|-------------------------|----------|-----------------------------------|-----|

|     | 4.2.1                   | DWMVA    | Register Transactions             | 4–4 |

|     |                         | 4.2.1.1  | T2018 Register Read/Write • 4–4   |     |

|     |                         | 4.2.1.2  | C3200 Register Read/Write • 4-4   |     |

|     | 4.2.2                   | CPU-to-\ | /ME Device Transactions           | 4–5 |

|     |                         | 4.2.2.1  | VME Device Write • 4–5            |     |

|     |                         | 4.2.2.2  | VME Device Read • 4–5             |     |

|     |                         | 4.2.2.3  | CPU Reads and Masked Writes • 4–6 |     |

|     |                         | 4.2.2.4  | CPU Interlocks • 4–7              |     |

| 4.3     | DMA TRANSACTION PROCESS              | 4-7 |

|---------|--------------------------------------|-----|

| 110     | 4.3.1 VME-to-XMI Memory Write        |     |

|         | 4.3.2 VME-to-XMI Memory Read         |     |

|         | 4.3.3 DMA Interlocks                 |     |

|         |                                      |     |

| CHAPTER | 5 VMEBUS INTERFACE                   | 5–1 |

| 5.1     | DATA TRANSFER BUS                    | 5–1 |

|         | 5.1.1 Address Lines                  | 5–2 |

|         | 5.1.2 Data Lines                     | 5–3 |

|         | 5.1.3 Control Lines                  | 5–4 |

| 5.2     | ARBITRATION BUS                      | 5–4 |

| 5.3     | PRIORITY INTERRUPT BUS               | 5–5 |

| 5.4     | UTILITY BUS                          | 5–5 |

| 5.5     | VMEBUS SIGNAL DESCRIPTIONS           | 5–5 |

|         | 5.5.1 Data Transfer Bus Signals      | 5–5 |

|         | 5.5.2 Arbitration Bus Signals        | 5–6 |

|         | 5.5.3 Priority Interrupt Bus Signals | 5–7 |

|         | 5.5.4 Utility Bus Signals            | 5–8 |

| CHAPTER | 6 INTERRUPTS                         | 6–1 |

| 6.1     | ERROR INTERRUPTS                     | 6–1 |

| 6.2     | INTERRUPT SEQUENCE                   | 6–1 |

| 6.3     | VME-TO-XMI INTERRUPT PROTOCOL        | 6–2 |

| 6.4     | INTERRUPT REQUEST LEVELS             | 6–4 |

6.5 C3200 INTERRUPTER/INTERRUPT HANDLER SELECTION

6–5

6.6 VME INTERRUPTER TYPES

#### CHAPTER 7 REGISTERS

6–5

| 7.1 | T2018 REGISTERS                                                                                                                                                                                                                                                                                                                                           |                                                                                      | 7–2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|

|     | DEVICE REGISTER (XDEV)                                                                                                                                                                                                                                                                                                                                    | 7–4                                                                                  |      |

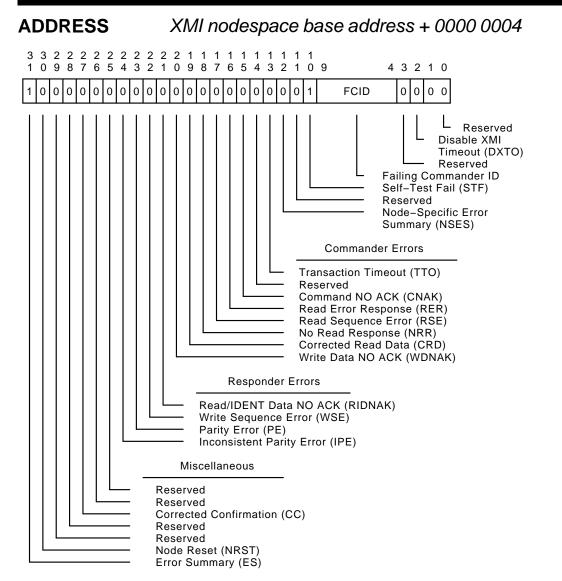

|     | BUS ERROR REGISTER (XBER)                                                                                                                                                                                                                                                                                                                                 | 7–6                                                                                  |      |

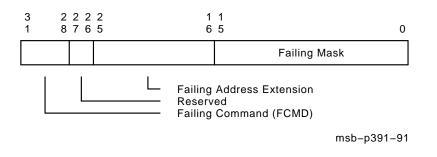

|     | FAILING ADDRESS REGISTER (XFADR)                                                                                                                                                                                                                                                                                                                          | 7–14                                                                                 |      |

|     | RESPONDER ERROR ADDRESS REGISTER (AREAR)                                                                                                                                                                                                                                                                                                                  | 7–16                                                                                 |      |

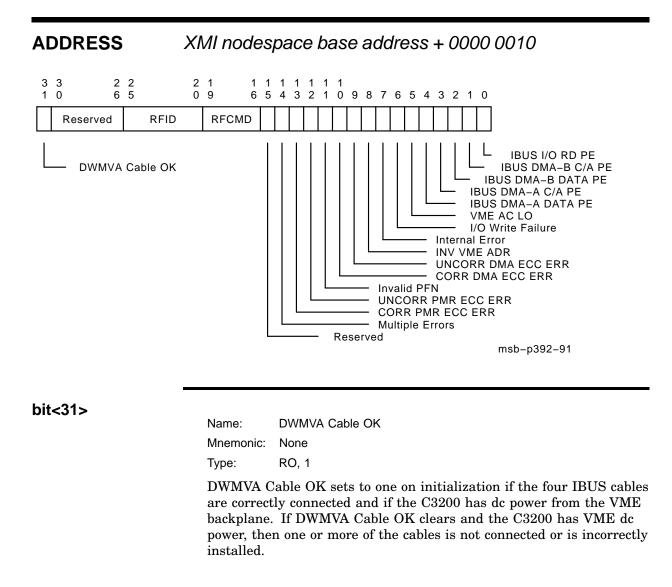

|     | ERROR SUMMARY REGISTER (AESR)                                                                                                                                                                                                                                                                                                                             | 7–18                                                                                 |      |

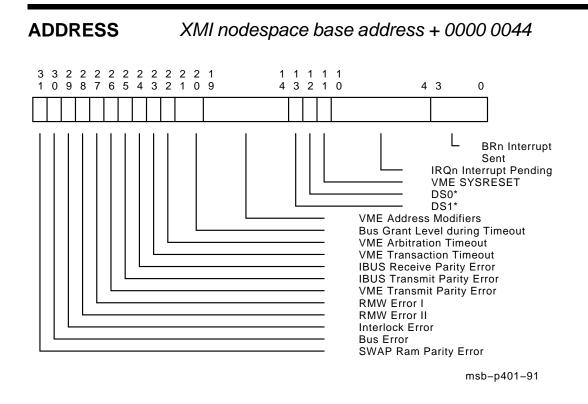

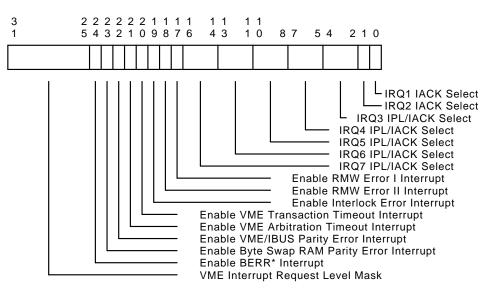

|     | INTERRUPT MASK REGISTER (AIMR)                                                                                                                                                                                                                                                                                                                            | 7–26                                                                                 |      |

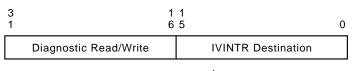

|     | IMPLIED VECTOR INTERRUPT                                                                                                                                                                                                                                                                                                                                  |                                                                                      |      |

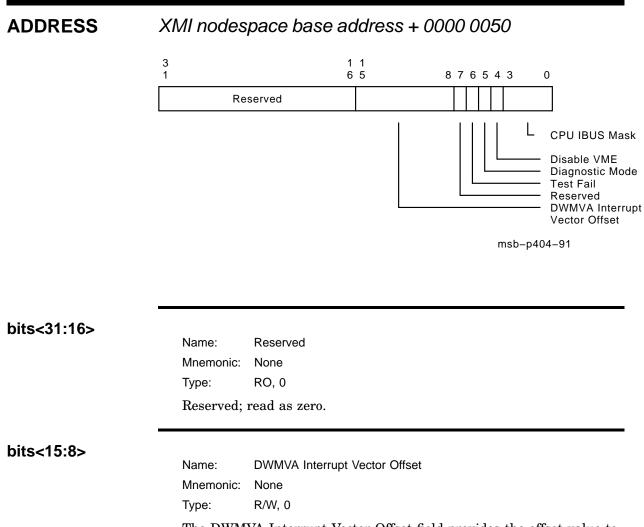

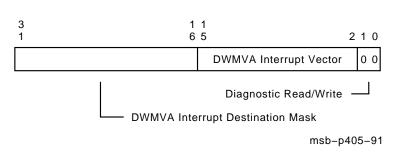

|     | DESTINATION/DIAGNOSTIC REGISTER (AIVINTR)                                                                                                                                                                                                                                                                                                                 | 7–33                                                                                 |      |

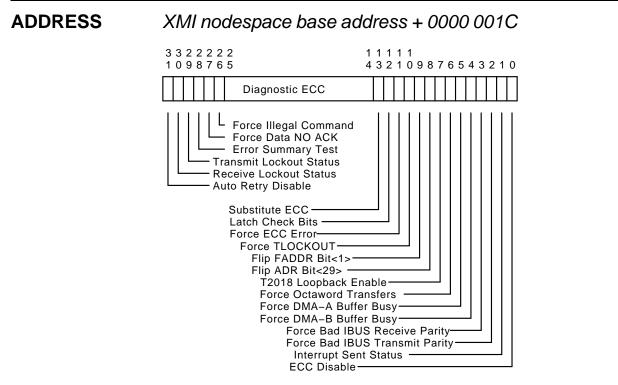

|     | DIAGNOSTIC 1 REGISTER (ADG1)                                                                                                                                                                                                                                                                                                                              | 7–34                                                                                 |      |

|     | UTILITY REGISTER (AUTLR)                                                                                                                                                                                                                                                                                                                                  | 7–35                                                                                 |      |

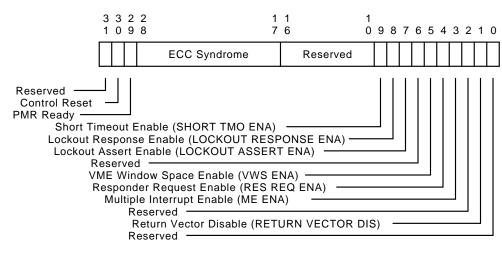

|     | CONTROL AND STATUS REGISTER (ACSR)                                                                                                                                                                                                                                                                                                                        | 7–39                                                                                 |      |

|     | RETURN VECTOR REGISTER (ARVR)                                                                                                                                                                                                                                                                                                                             | 7–44                                                                                 |      |

|     | FAILING ADDRESS EXTENSION REGISTER (XFAER)                                                                                                                                                                                                                                                                                                                | 7–45                                                                                 |      |

|     | VME EDDOD ADDRESS DECISTED (ADEAD)                                                                                                                                                                                                                                                                                                                        | 7–47                                                                                 |      |

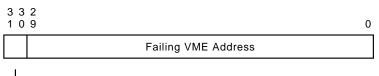

|     | VME ERROR ADDRESS REGISTER (ABEAR)                                                                                                                                                                                                                                                                                                                        | /-4/                                                                                 |      |

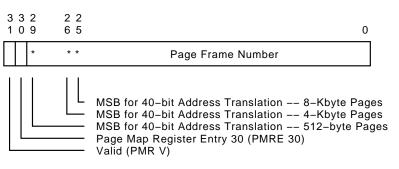

|     | PAGE MAP REGISTERS (PMRS)                                                                                                                                                                                                                                                                                                                                 | 7–47<br>7–49                                                                         |      |

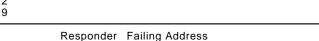

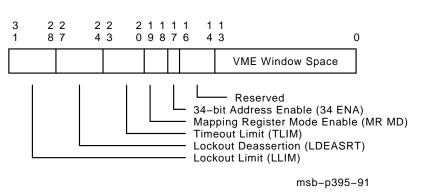

| 7.2 | , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                     |                                                                                      | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)                                                                                                                                                                                                                                                                                                                                 |                                                                                      | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)                                                                                                                                                                                                                                                                                                                                 | 7–49                                                                                 | 7–51 |

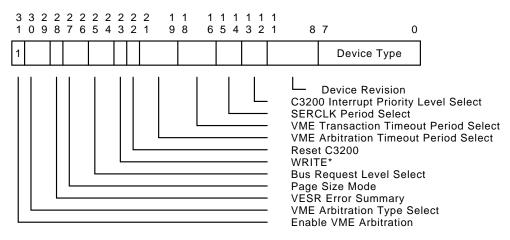

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)                                                                                                                                                                                                                                                                      | 7-49                                                                                 | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)                                                                                                                                                                                                                                 | 7–49<br>7–53<br>7–59                                                                 | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VFADR)                                                                                                                                                                                         | 7–49<br>7–53<br>7–59<br>7–65                                                         | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)                                                                                                                                               | 7–49<br>7–53<br>7–59<br>7–65<br>7–66                                                 | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)<br>VECTOR OFFSET REGISTER (VVOR)                                                                                                              | 7–49<br>7–53<br>7–59<br>7–65<br>7–66<br>7–73                                         | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)<br>VECTOR OFFSET REGISTER (VVOR)<br>VECTOR REGISTER (VVR)                                                                                     | 7–49<br>7–53<br>7–59<br>7–65<br>7–66<br>7–73<br>7–75                                 | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)<br>VECTOR OFFSET REGISTER (VVOR)<br>VECTOR REGISTER (VVR)<br>BYTE SWAP RAM ACCESS REGISTER (RAR)                                              | 7–49<br>7–53<br>7–59<br>7–65<br>7–66<br>7–73<br>7–75<br>7–77                         | 7–51 |

| 7.2 | PAGE MAP REGISTERS (PMRS)<br>C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)<br>VECTOR OFFSET REGISTER (VVOR)<br>VECTOR REGISTER (VVR)<br>BYTE SWAP RAM ACCESS REGISTER (RAR)<br>CSR ACCESS REGISTER (VCAR)                | 7–49<br>7–53<br>7–59<br>7–65<br>7–66<br>7–73<br>7–75<br>7–77<br>7–80                 | 7–51 |

| 7.2 | C3200 REGISTERS<br>DEVICE/CONFIGURATION REGISTER (VDCR)<br>VME ERROR SUMMARY REGISTER (VESR)<br>VME FAILING ADDRESS REGISTER (VESR)<br>INTERRUPT CONFIGURATION REGISTER (VICR)<br>VECTOR OFFSET REGISTER (VVOR)<br>VECTOR REGISTER (VVR)<br>BYTE SWAP RAM ACCESS REGISTER (RAR)<br>CSR ACCESS REGISTER (VCAR)<br>VME ADDRESS RANGE ENABLE REGISTER (VAER) | 7–49<br>7–53<br>7–59<br>7–65<br>7–66<br>7–73<br>7–75<br>7–77<br>7–80<br>7–80<br>7–83 | 7–51 |

#### CHAPTER 8 INITIALIZATION

APPENDIX A VME INTERFACE SIGNAL LIST

A–1

8–1

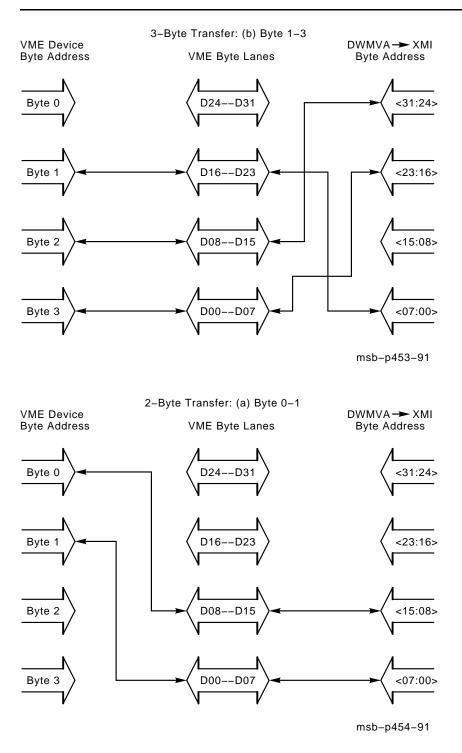

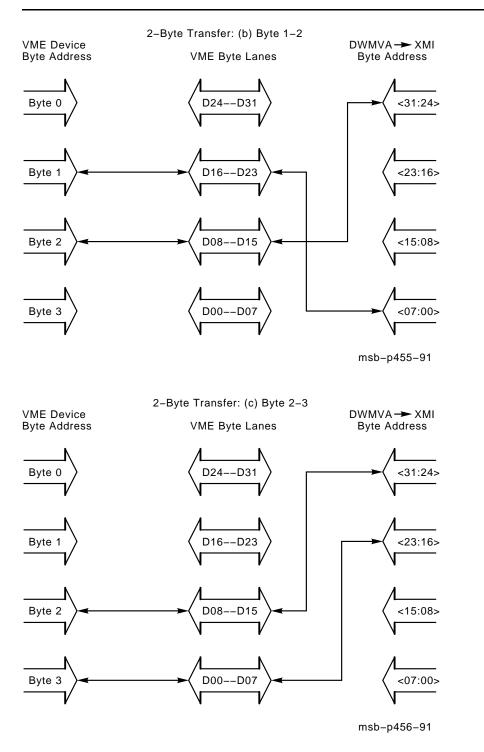

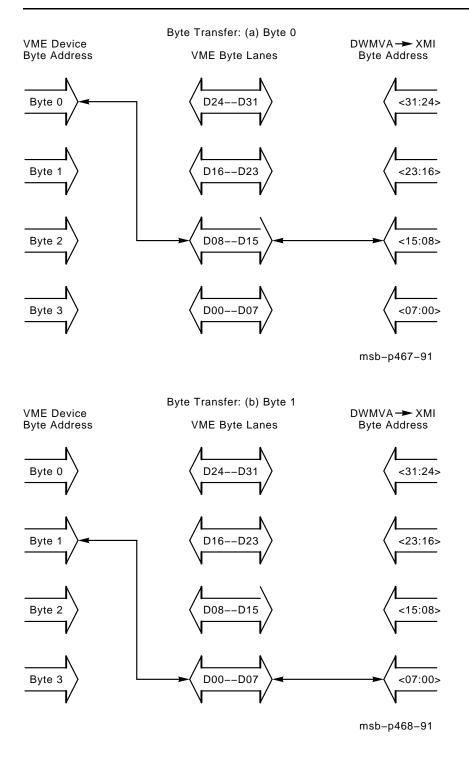

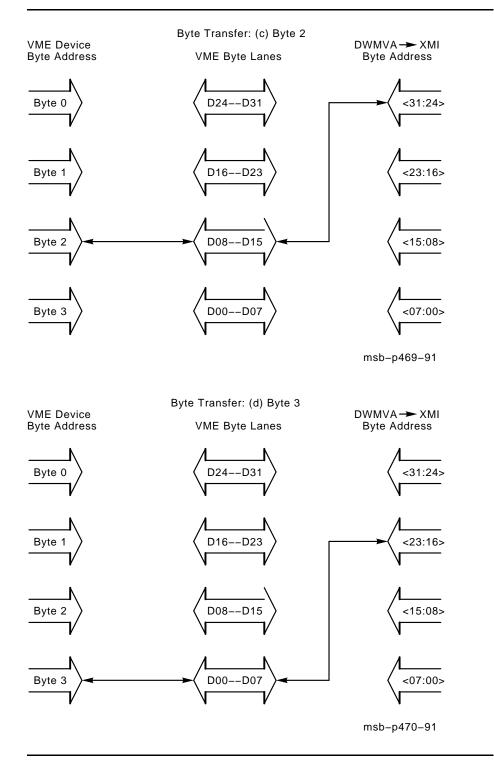

| APPENDIX B | VME-TO-XMI BYTE SWAPPING         | B–1  |

|------------|----------------------------------|------|

| B.1        | DEFINITION OF TERMS              | B–1  |

| B.2        | BYTE SWAPPING IN DATA STORAGE    | B-3  |

| B.3        | DWMVA BYTE SWAPPING REQUIREMENTS | B–5  |

|            | B.3.1 Mode 0—No Swap             | B–6  |

|            | B.3.2 Mode 1—Byte Swap           | B–12 |

|            | B.3.3 Mode 2—Word Swap           | B–18 |

|            | B.3.4 Mode 3—Longword Swap       | B-24 |

GLOSSARY

Glossary-1

## INDEX

| FIGURES |                                                         |

|---------|---------------------------------------------------------|

| 1–1     | DWMVA Adapter on the XMI Bus                            |

| 1–2     | DWMVA Block Diagram                                     |

| 2–1     | XMI Memory and I/O Address Space                        |

| 2–2     | XMI I/O Space Address Allocation                        |

| 2–3     | VME Address Map                                         |

| 2–4     | CPU Transaction Command Format                          |

| 2–5     | Building VME Addresses                                  |

| 2–6     | No Translation Mode VAX Address                         |

| 2–7     | 34-Bit VAX Address Translation                          |

| 2–8     | 40-Bit VAX Address Translation Using 512-Byte Page Size |

| 2–9     | 40-Bit VAX Address Translation Using 4-Kbyte Page Size  |

| 2–10    | 40-Bit VAX Address Translation Using 8-Kbyte Page Size  |

| 3–1     | VME System Controller Block Diagram                     |

| 3–2     | Bus Timer Block Diagram                                 |

| 3–3     | VME Arbitration Bus                                     |

| 3–4     | VMEbus Requester Block Diagram                          |

| 3–5     | IACK Daisy-Chain Driver                                 |

| 3–6     | Power Supply Block Diagram                              |

| 4–1     | C3200 Block Diagram                                     |

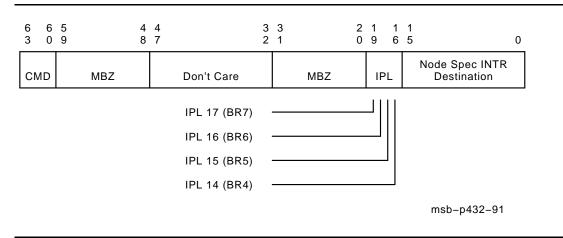

| 6–1     | XMI INTR Command Format                                 |

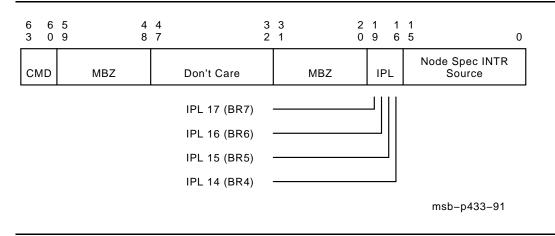

| 6–2     | XMI IDENT Command Format                                |

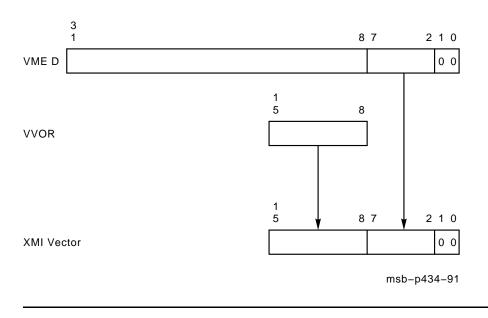

| 6–3 | Generating the XMI IDENT Response Vector | 6–4  |

|-----|------------------------------------------|------|

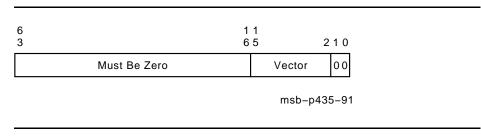

| 6–4 | XMI IDENT Response Format                | 6–4  |

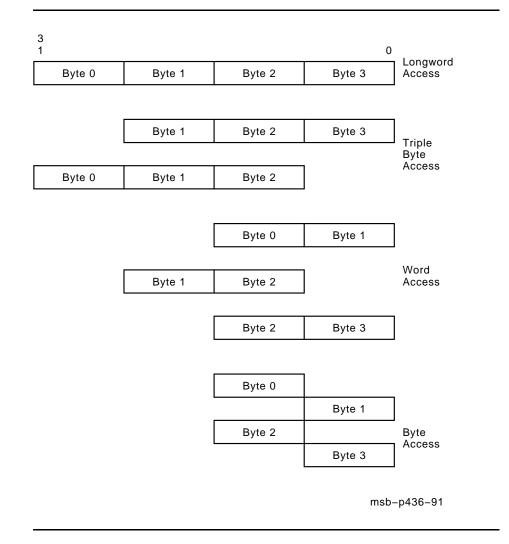

| B–1 | Big Endian VME Byte Lane Formats         | B–2  |

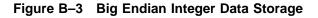

| B–2 | Little Endian Integer Data Storage       |      |

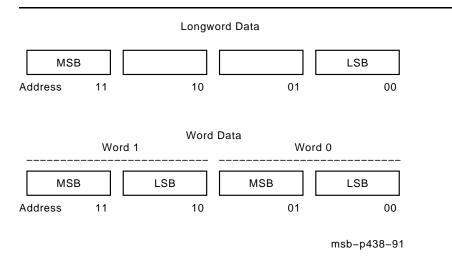

| B–3 | Big Endian Integer Data Storage          | B–4  |

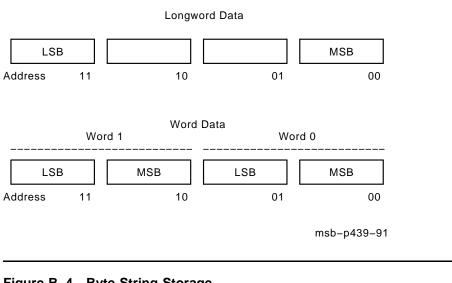

| B–4 | Byte String Storage                      | B–4  |

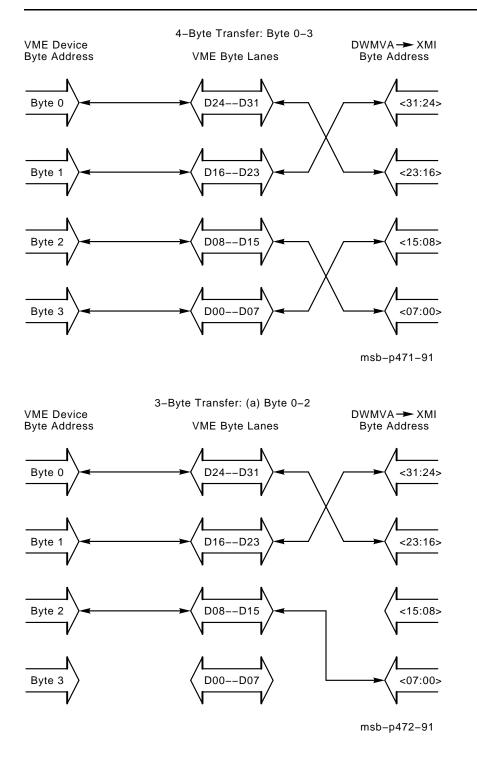

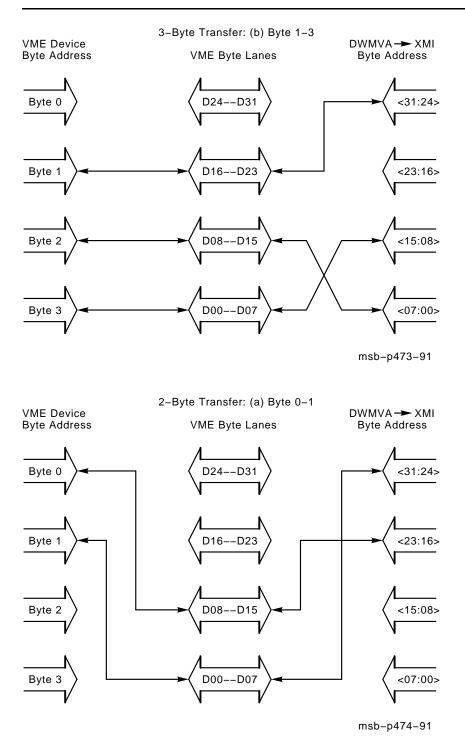

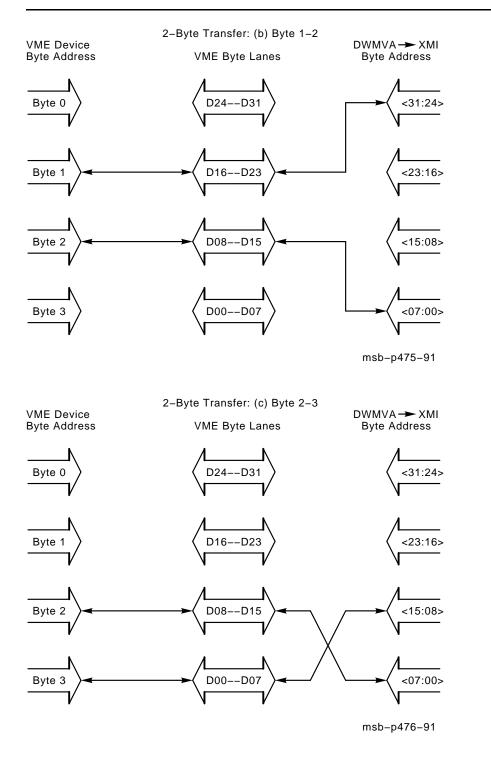

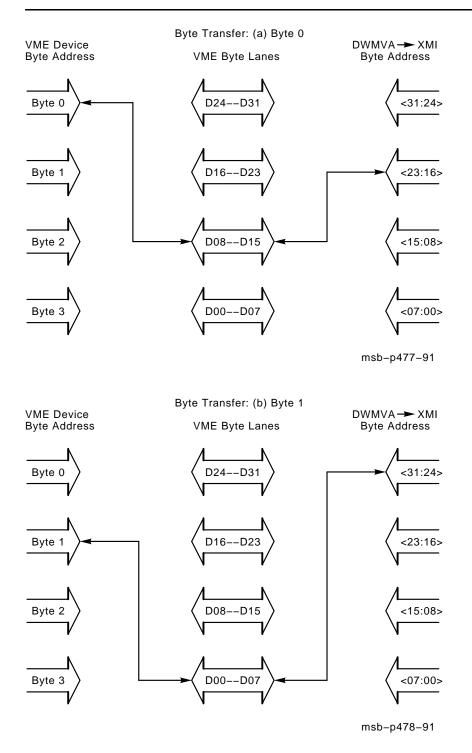

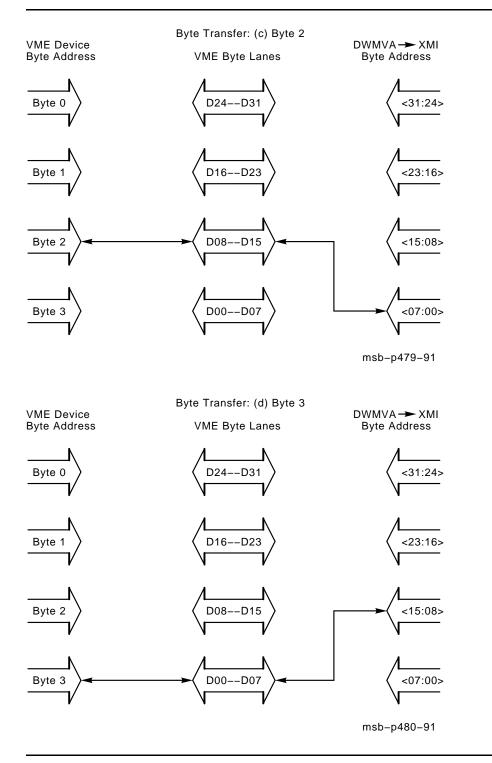

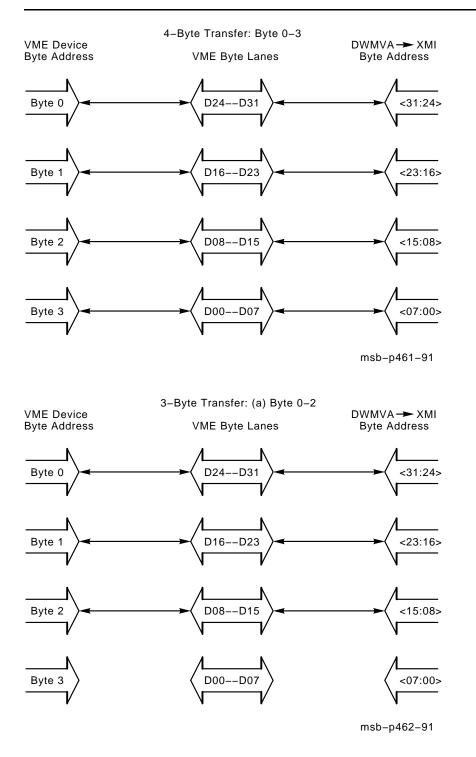

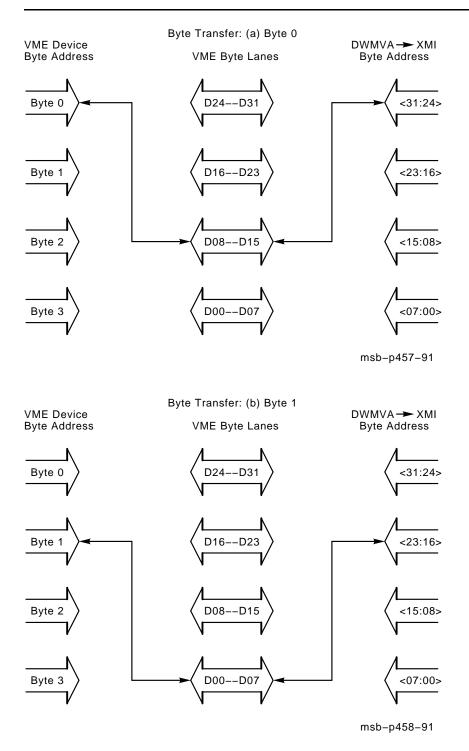

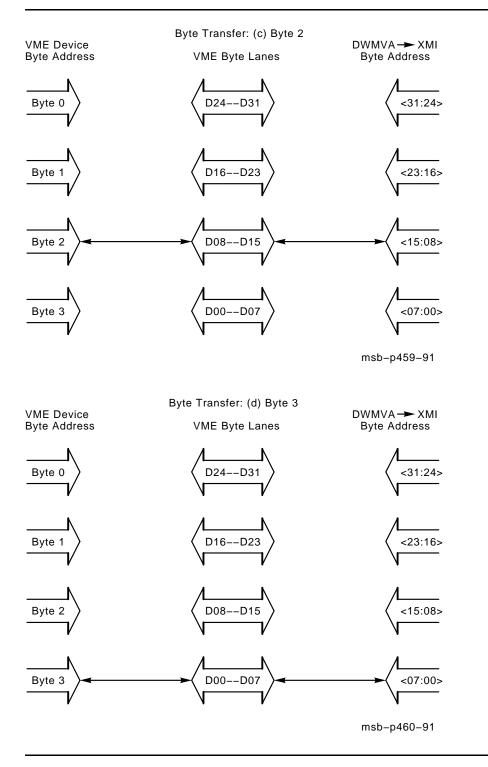

| B–5 | Mode 0 (No Swap) Transfers               | B–7  |

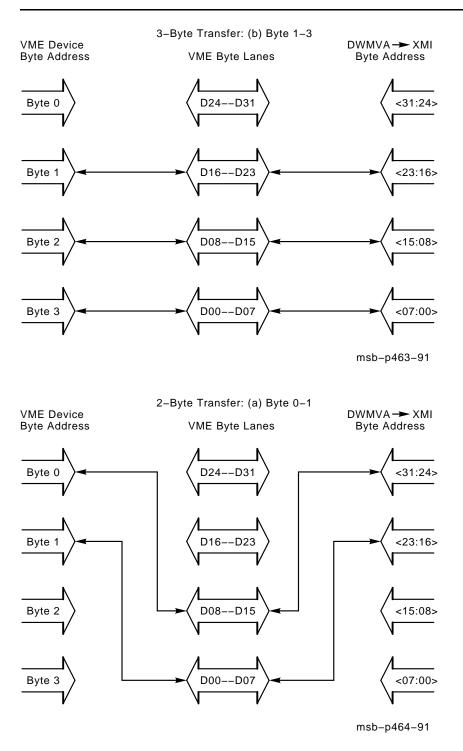

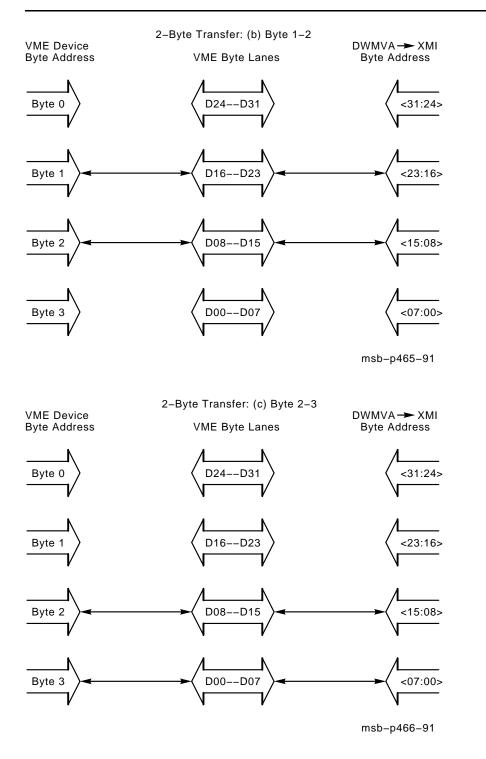

| B–6 | Mode 1 (Byte Swap) Transfers             |      |

| B–7 | Mode 2 (Word Swap) Transfers             |      |

| B–8 | Mode 3 (Longword Swap) Transfers         | D 05 |

|     |                                          |      |

## TABLES

| 2–1 | XMI Nodespace Addresses                         |  |

|-----|-------------------------------------------------|--|

| 2–2 | VME Address Modes                               |  |

| 2–3 | CPU Transaction Command                         |  |

| 3–1 | VME Transaction Timeout Selection               |  |

| 3–2 | VME Arbitration Algorithms                      |  |

| 3–3 | VME Bus Request Level Codes                     |  |

| 3–4 | VME Arbitration Timeout Selection               |  |

| 4–1 | XMI-to-VME Command Translations                 |  |

| 4–2 | VME-to-XMI Command Translations                 |  |

| 4–3 | Address Modifier Codes for CPU Transactions     |  |

| 4–4 | CPU Masked Writes to VME Space                  |  |

| 4–5 | CPU Reads of DWMVA                              |  |

| 5–1 | Data Transfer Bus Signals                       |  |

| 5–2 | Categories of Byte Locations                    |  |

| 5–3 | Selecting Byte Locations Within Longwords       |  |

| 5–4 | Address Modifier Codes                          |  |

| 5–5 | Use of Data Lines to Access Byte Locations      |  |

| 5–6 | Control Line Signals                            |  |

| 6–1 | VME-to-XMI Interrupt Progression                |  |

| 6–2 | VME Interrupt Request Levels and XMI Defaults   |  |

| 7–1 | Types of Registers and Bits                     |  |

| 7–2 | T2018 Registers                                 |  |

| 7–3 | Initialization Values of the T2018 Registers    |  |

| 7–4 | C3200 Registers                                 |  |

| 7–5 | Initialization Values of the C3200 Registers    |  |

| A–1 | DWMVA-to-VME Interface (J1 Connector)           |  |

| A–2 | DWMVA-to-VME Interface (J2 Connector)           |  |

| B–1 | Byte Lanes for Different Sizes of VME Transfers |  |

| B–2 | Byte Swapping Modes                             |  |

|     |                                                 |  |

## Preface

This manual presents a detailed technical description of the DWMVA I/O adapter that connects a VMEbus to the XMI bus of a VAX 6000 computer system. It provides complete discussions of the hardware operations of the component modules and bit-level functional descriptions of all adapter registers.

#### Audience

This manual is for software developers who write driver and application programs for the DWMVA I/O adapter.

#### **Document Structure**

The manual consists of eight chapters and two appendixes.

- **Chapter 1, Overview**, describes the major components of the DWMVA adapter, provides a summary of the buses, and introduces the types of DWMVA transactions.

- **Chapter 2, Address Mapping**, discusses mapping of VME addresses to XMI address space. The chapter explains how an XMI address is translated to a VME address in a CPU transaction, and how a VME address is translated to an XMI address in a DMA transaction.

- **Chapter 3, VME System Control**, describes the components and functions of the VME system controller, including the VME arbitration subsystem.

- **Chapter 4, Transactions**, discusses the two types of transactions, CPU and DMA, processed by the DWMVA. CPU transactions are initiated by the CPU and perform reads and writes on VME devices, while DMA transactions are initiated by a VME device and perform reads and writes to XMI memory. This chapter also discusses the translation of commands over the XMI to the VMEbus and from the VMEbus to the XMI data paths.

- **Chapter 5, VMEbus Interface**, discusses the substructures of the VMEbus and describes the VMEbus signals.

- **Chapter 6, Interrupts**, discusses the VME-to-XMI interrupt protocol, the interrupt request levels, and interrupt handler selection.

- **Chapter 7, Registers**, provides bit-level descriptions of functions performed by the register sets on the two modules of the DWMVA adapter.

- **Chapter 8, Initialization**, discusses the various methods used to initialize the DWMVA adapter.

- Appendix A, VME Interface Signal List, gives the pin assignments on the two connectors of the VME interface.

- Appendix B, VME-to-XMI Byte Swapping, discusses how the DWMVA implements byte swapping to allow VME data to appear correctly on the XMI bus and XMI data to appear correctly on the VMEbus.

- A Glossary provides additional reference support.

#### **Associated Documents**

Other documents related to the DWMVA adapter include:

• DWMVA VME Adapter Installation Guide, EK–DWMVA–IN

Describes the installation of the DWMVA I/O adapter in a VAX 6000 computer system.

• BA62 VME Enclosure, EK-VME01-IN

Describes the BA62 enclosure that is used as an expansion cabinet to provide a VMEbus backplane and to house the C3200 module.

• *IEEE Standard for a Versatile Backplane Bus: VMEbus*, IEEE Std 1014, 1987.

Provides complete specifications for the VMEbus.

• VMS Version 5.4-3 Release Notes, AA–PHUFA–TE

Includes a chapter (Open Bus Driver Support Features) that discusses VMS support for VMEbus devices.

• VMS Device Support Manual, AA-PBPWA-TE

Describes the components of a VMS device driver and the basic rules that device drivers must observe.

• VMS Device Support Reference Manual, AA-PBPXA-TE

Describes driver data structures, routines, and entry points.

# Overview

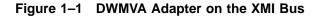

The DWMVA adapter connects to the I/O segment of the VAX 6000 XMI bus and interfaces the synchronous XMI bus to the VMEbus, an asynchronous industry-standard bus. The DWMVA implements the handshaking protocol and acts as a channel for data flow between the two buses. Figure 1–1 is a block diagram showing the DWMVA adapter on the XMI bus.

## 1.1 Major Components

The DWMVA subsystem consists of two modules:

- T2018 (DWMVA/A)

- C3200 (DWMVA/B)

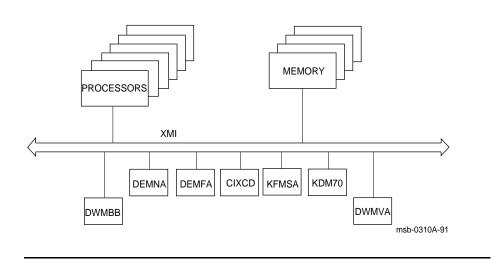

The T2018 module is on the XMI bus and the C3200 module is on the VMEbus. The two modules are connected through the IBUS, which is a physical path between the system XMI bus and the VMEbus. Figure 1-2 shows a block diagram of the DWMVA adapter.

The T2018 module contains the XMI and IBUS interfaces, registers, a data buffer, and state machines for transmitting and receiving data. The XMI Corner is a circuit area on all XMI nodes that provides the interface to the XMI bus. This corner handles the distribution of the XMI clock, control, and data lines to the T2018 module. The T2018 allows access to XMI addresses from VME through on-board 64K page map registers.

The C3200 module contains the following functional blocks: VME and IBUS interfaces, control logic, registers, data buffers, the VME interrupt handler, and the VME system controller (VSC).

### 1.2 Major Buses

Three major buses are used to exchange information between the host computer system and an I/O device connected to the VMEbus:

- XMI bus

- VMEbus

- IBUS

The T2018 uses the XMI bus to communicate with the processor. The C3200 communicates with a VME device through the VMEbus. The IBUS provides communication between the T2018 module and the C3200 module.

#### 1.2.1 XMI Bus

The XMI is a 64-bit wide, pended, synchronous bus that can process multiple read requests at any given time. It has a cycle time of 64 ns, allowing an effective bandwidth on the bus of 100 Mbytes/second. The XMI protocol supports quadword, octaword, and hexword reads and writes to XMI memory space. The DWMVA, however, allows only quadword and octaword transactions to XMI memory. The DWMVA accepts only longword transactions to its address space.

#### 1.2.2 VMEbus

The VMEbus is an asynchronous, interlocked bus that processes one transaction at a time. The VME protocol, defined by IEEE 1014, consists of four subbuses: the data transfer bus, the arbitration bus, the priority interrupt bus, and the utility bus. The VME supports 1-, 2-, 3-, and 4-byte transfers as well as block transactions consisting of multiple 1-, 2-, or 4-byte transfers over the data transfer bus, a nonmultiplexed data/address path. The VME has an effective bandwidth of 40 Mbytes/second.

Chapter 5 provides an overview of the VMEbus. For a more complete treatment of the VMEbus, refer to the IEEE VMEbus specification. (See, for example, *VMEbus*, A standard specification for a versatile backplane bus, IEEE Computer Society Publication P1014, March 1987.)

### 1.2.3 IBUS

The IBUS is the communications path between the two modules of the DWMVA. The IBUS data path consists of a 4-bit function field, IB I<3:0>, and a 32-bit, multiplexed address/data field, IB D<31:0>. The IBUS can transfer address or data every 200 ns, yielding an effective bandwidth of 16 Mbytes/second.

In addition to the bidirectional lines (address and data), the IBUS includes many lines to carry control signals. The signals driven from the T2018 to the C3200 are used to indicate the status of the T2018's buffers, while the signals from the C3200 to the T2018 are used to control the operation of the IBUS.

#### 1.3 Transactions

The DWMVA conducts two types of transactions:

- CPU transactions

- DMA transactions

A CPU transaction is initiated by a processor on the XMI bus. The processor is the commander. The DWMVA becomes the responder. A DMA transaction begins on the VMEbus and targets XMI memory through the DWMVA adapter. Transactions are discussed in Chapter 4.

## 1.4 Interrupts

The DWMVA accepts longword-aligned VME interrupts and generates XMI INTR transactions in response to them. The DWMVA (or any other XMI device) does not issue interrupts to the VMEbus. Interrupts are discussed in Chapter 6.

# 2 Address Mapping

This chapter discusses the XMI I/O address space and explains how the VME address space is mapped to the XMI I/O adapter space.

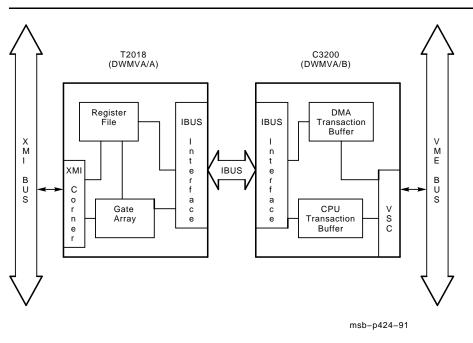

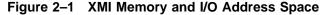

The XMI supports one terabyte  $(2^{40})$  of address space, accessible with 40-bit addresses. Since a VAX 6000 series system supports 30- or 32-bit addresses, the maximum space available to a single system on the XMI is  $(2^{32})$  bytes, which is 4 gigabytes.

The VAX 6000 series systems use one of three addressing modes depending on the model and the environment.

- 30-bit addressing (Models 200 through 500)

- 32-bit addressing (Model 500 and above)

- 30-bit addressing in a 32-bit environment (Model 500 and above)

Figure 2–1 shows how memory and I/O space are divided in the 30-bit and the 32-bit addressing modes.

## 2.1 XMI Memory Space

Memory address space is the lower part of the address space no matter which address mode, 30-bit or 32-bit, is used. A VAX 6000 system using 30-bit addressing cannot access the 3 Gbytes of memory space between address 2000 0000 (hex) and DFFF FFFF.

## 2.2 XMI I/O Space

The maximum amount of I/O space available for a VAX 6000 is 512 Mbytes regardless of the addressing mode. The I/O space is divided into three sections:

- Private space

- Nodespace

- I/O adapter space

The I/O space is allocated as shown in Figure 2-2.

| 32-Bit<br>Byte Address | 30-Bit<br>Byte Address |                             | Size            |

|------------------------|------------------------|-----------------------------|-----------------|

| E000 0000              | 2000 0000              | XMI Private Space           | 24 Mbytes       |

| E180 0000              | 2180 0000              | XMI Nodespace               | 16 x 512 Kbytes |

| E200 0000              | 2200 0000              | ·                           |                 |

| E400 0000              | 2400 0000              | I/O Adapter 1 Address Space | 32 Mbytes       |

|                        |                        | I/O Adapter 2 Address Space | 32 Mbytes       |

| E600 0000              | 2600 0000              | I/O Adapter 3 Address Space | 32 Mbytes       |

| E800 0000              | 2800 0000              | I/O Adapter 4 Address Space | 32 Mbytes       |

| EA00 0000              | 2A00 0000              | I/O Adapter 5 Address Space | 32 Mbytes       |

| EC000000               | 2C00 0000              | Non-I/O Space               | 128 Mbytes      |

| F400 0000              | 3400 0000              | ·                           | ,               |

| F600 0000              | 3600 0000              | I/O Adapter A Address Space | 32 Mbytes       |

|                        |                        | I/O Adapter B Address Space | 32 Mbytes       |

| F800 0000              | 3800 0000              | I/O Adapter C Address Space | 32 Mbytes       |

| FA00 0000              | 3A00 0000              | I/O Adapter D Address Space | 32 Mbytes       |

| FC00 0000              | 3C00 0000              | · ·                         |                 |

| FE00 0000              | 3E00 0000              | I/O Adapter E Address Space | 32 Mbytes       |

|                        | 0200 0000              |                             |                 |

#### Figure 2–2 XMI I/O Space Address Allocation

msb-p373A-90

#### 2.2.1 Private Space

The XMI private space is a 24-Mbyte address region located from E000 0000 to E17F FFFF (32-bit address) or from 2000 0000 to 217F FFFF (30-bit address). References to XMI private space are serviced by resources local to a node, such as local device CSRs and boot ROM. The references are not broadcast on the XMI.

#### 2.2.2 Nodespace

The VAX 6000 platform XMI nodespace is a collection of sixteen 512-Kbyte regions located from E180 0000 to E1FF FFFF (32-bit address) or from 2180 0000 to 21FF FFFF (30-bit address). Each XMI node is allocated one of the fourteen 512-Kbyte regions for its control and status registers (nodes 0 and F are not implemented). The starting address of the 512-Kbyte region associated with a given node (BB) is computed as follows:

BB = E180 0000 + Node ID \* 8 0000 (32-bit address)

BB = 2180 0000 + Node ID \* 8 0000 (30-bit address)

Table 2–1 gives the address ranges of the 14 XMI nodespace regions implemented on the VAX 6000 series.

| Slot            | Node | Nodespace                          | I/O Window Space (DWMVA) |

|-----------------|------|------------------------------------|--------------------------|

| 1               | 1    | E188 0000 - E18F FFFF <sup>1</sup> | E200 0000 - E3FF FFFF    |

| 2               | 2    | E190 0000 - E197 FFFF              | E400 0000 – E5FF FFFF    |

| 3               | 3    | E198 0000 - E19F FFFF              | E600 0000 – E7FF FFFF    |

| 4               | 4    | E1A0 0000 - E1A7 FFFF              | E800 0000 – E9FF FFFF    |

| 5 <sup>2</sup>  | 5    | E1A8 0000 - E1AF FFFF              | EA00 0000 – EBFF FFFF    |

| 6               | 6    | E1B0 0000 - E1B7 FFFF              | N/A <sup>3</sup>         |

| 7               | 7    | E1B8 0000 - E1BF FFFF              | N/A <sup>3</sup>         |

| 8               | 8    | E1C0 0000 - E1C7 FFFF              | N/A <sup>3</sup>         |

| 9               | 9    | E1C8 0000 - E1CF FFFF              | N/A <sup>3</sup>         |

| 10 <sup>2</sup> | А    | E1D0 0000 - E1D7 FFFF              | F400 0000 – F5FF FFFF    |

| 11              | В    | E1D8 0000 - E1DF FFFF              | F600 0000 – F7FF FFFF    |

| 12              | С    | E1E0 0000 - E1E7 FFFF              | F800 0000 – F9FF FFFF    |

| 13              | D    | E1E8 0000 - E1EF FFFF              | FA00 0000 – FBFF FFFF    |

| 14              | Е    | E1F0 0000 - E1F7 FFFF              | FC00 0000 - FDFF FFFF    |

Table 2–1 XMI Nodespace Addresses

<sup>1</sup>32-bit addresses are converted to 30-bit addresses by changing the most significant byte from E to 2 and from F to 3.

<sup>2</sup>These slots cannot be used on VAX 6000 Models 200, 300, and 400 due to processor restrictions.

<sup>3</sup>Slots in the center of the XMI card cage have no I/O connectors because of the daughter card's presence.

## 2.2.3 I/O Adapter Address Space

The XMI I/O adapter address space consists of ten 32-Mbyte address regions (windows) used to access I/O devices. The I/O adapter address space accessed by the DWMVA is determined by the XMI slot in which it is installed. Table 2–1 also shows the I/O window space for each XMI adapter. All 4 gigabytes of the VME address space are accessible from a 32-Mbyte I/O window space.

The DWMVA accepts only longword-length references to its XMI adapter address space. These references are then translated to their corresponding VME transactions or, internally, as DWMVA register transactions.

#### 2.3 VME Address Space

The VMEbus supports 4 gigabytes  $(2^{32})$  of address space. Unlike the XMI, the VME address space is not divided into memory and I/O spaces. To address a byte in this space, VME data transfer bus lines DS0\*, DS1\*, and LWORD\* are used in conjunction with the VME address lines A01–A31.

The VMEbus allows devices of different address widths to coexist on the bus at any given time. The address width can be 16 bits, 24 bits, or 32 bits. The master indicates the nature of the current address by asserting an appropriate value on the VME address modifier lines (see Section 5.1.1). Table 2–2 shows the address space accessible with each address mode.

Table 2–2 VME Address Modes

| Address Mode | Address Width | Accessible VME Space |

|--------------|---------------|----------------------|

| Extended     | 32 bits       | 4 Gbytes             |

| Standard     | 24 bits       | 16 Mbytes            |

| Short        | 16 bits       | 64 Kbytes            |

Figure 2–3 shows the VME address map.

NOTE: In VME-initiated (DMA) transactions, the DWMVA makes a distinction between addresses it will accept and addresses it will not by using the VME Address Range Enable Register (see VESR in Chapter 7). If enabled, the DWMVA accepts any extended VME address with VME address bits A29-A31 = 000. The DWMVA can also be configured to accept standard VME addresses with VME address bit A23 = 0. The DWMVA does not support short address DMA transactions.

Since the VMEbus and the XMI use different addressing schemes, address translation is required to move data from one bus to the other. The DWMVA translates XMI addresses to VME addresses in CPU transactions, when data is moved from the XMI bus to the VMEbus. Conversely, the DWMVA translates VME addresses to XMI addresses in DMA transactions, when data is moved from the VMEbus to the XMI.

Figure 2–3 VME Address Map

## 2.4 Address Translation in CPU Transactions

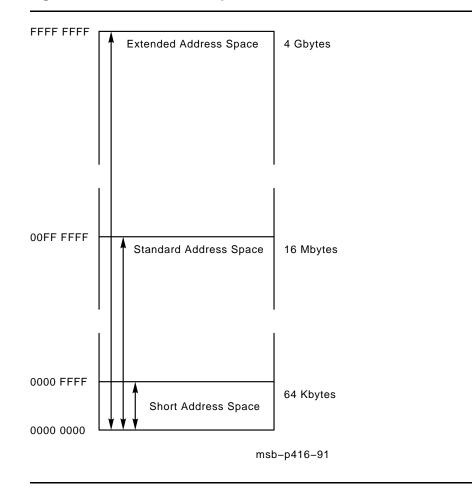

In a CPU transaction, the 4-Gbyte VME address space is mapped to the 32-Mbyte XMI adapter space by decoding the 32-bit CPU transaction command as shown in Figure 2–4 and Figure 2–5.

| 3<br>1   |                | 1<br>9 0    |

|----------|----------------|-------------|

| XMI Node | VAOR<br>Select | VME Address |

msb-p417-91

The fields of the CPU transaction command are described in Table 2–3.

| Bit Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <31:25>   | XMI Node—This field is used to access a 32-Mbyte region of DWMVA adapter space on the XMI. Each XMI node responds to a unique value in this field.                                                                                                                                                                                                                                                                                                                     |  |

| <24:20>   | VAOR Select—The VAOR Select field selects one of the 32 CPU<br>Address Offset Registers that is used to supply the upper 12<br>address bits, address length, and data length information for the<br>CPU transaction. This field selects the offset value that is appended<br>to the VME address field (bits <19:0>) of the CPU transaction address<br>to generate the corresponding VME address. See Chapter 7 for<br>information on the CPU Address Offset Registers. |  |

| <19:0>    | VME Address—This field contains the lower 20 bits of the VME address for the CPU transaction.                                                                                                                                                                                                                                                                                                                                                                          |  |

Table 2–3 CPU Transaction Command

Figure 2–5 shows how VME addresses are generated from XMI addresses. The XMI address (CPU transaction address, shown at the top) provides the lower 20 bits of the VME address. The other bits of the VME address as well as the address length and data length information for the transaction are provided by the appropriate fields of the CPU Transaction Address Offset Register (see Chapter 7) determined by the VAOR Select field. This address generation scheme allows access to any 32-Mbyte VME address region through the 32-Mbyte XMI window. Each VME address region consists of 32 1-Mbyte sections and is selected by one of the 32 values provided by the VAOR Select field.

Figure 2–5 Building VME Addresses

## 2.5 Address Translation in DMA Transactions

This section discusses translation of VME addresses into XMI physical (VAX) addresses in DMA read/write transactions. The DWMVA implements five modes of VAX address translation:

- No address translation

- 34-bit VAX address translation

- 40-bit VAX address translation

- 40-bit VAX address translation using 4-Kbyte page size

- 40-bit VAX address translation using 8-Kbyte page size

The DWMVA defaults to no address translation mode at power-up or node reset. The address translation mode is selected at system initialization by loading the Mapping Register Mode Enable field (bits<19:17> of the T2018 Utility Register) with the appropriate configuration.

# NOTE: Normally, the VMS operating system uses the 34-bit address translation mode.

## 2.5.1 No Address Translation

In no address translation mode the XMI physical address is identical to the VME address. The upper address bits of the extended XMI address format, XMI A<39:29>, are forced to zero. The steps used to generate a VAX address from a VME address using no translation mode are as follows:

1 Check Upper Address Bit

VME A29–A31 must be zero.

2 Generate XMI Address

Load zeros into XMI A<39:29>. Load VME A0-A28 into XMI A<28:0>.

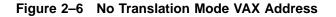

Figure 2–6 shows the 29-bit VAX address generation in no translation mode.

## 2.5.2 34-Bit VAX Address Translation

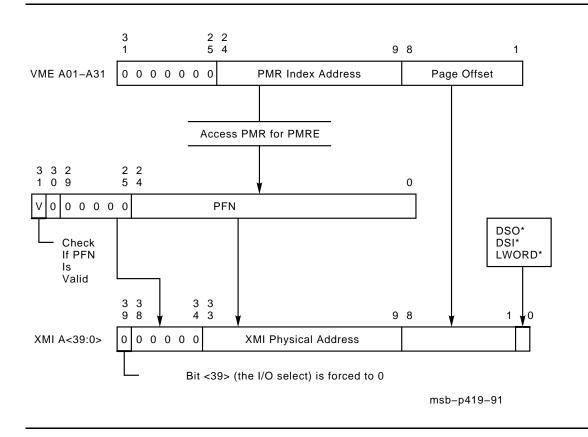

In 34-bit VAX address translation mode (see Figure 2–7), the DWMVA can map only the first 32 Mbytes of VME memory address space to XMI memory address space. Since the page size is 512 bytes, this is the maximum range that can be mapped with 64K page map register (PMR) entries.

Figure 2–7 34-Bit VAX Address Translation

The translation of a VME DMA address to a 34-bit XMI address uses VME address bits VME A09–A24 as an index into the PMRs. These bits select the page map register entry (PMRE) that contains the required VAX page frame number (PFN). Because in this mode the DWMVA only maps the first 32 Mbytes of VME memory address space, the upper bits of the VME address, VME A25–A31, must be zero. The validity of the PFN is checked and if good the PFN is used to complete the DMA address translation. The 34-bit physical address is obtained by combining the PFN field of the PMRE (PMRE<24:0>) with VME address bits VME A0–A08. The unused upper address bits (XMI A<39:34>) are forced to zero. The steps used for 34-bit address translation are as follows:

1 Check Upper Address Bits

VME A25-A31 must all be zero.

**2** Access PMR for PMRE

VME address VME A09–A24 used as an index into the PMR to fetch the PMRE.

**3** Check PMRE Valid Bit

If PMRE<31> = 1, then PFN is valid. If PMRE<31> = 0, then PFN is invalid and transaction is aborted.

4 ECC Check

If no error or correctable error, then PFN is good. If uncorrectable error, then PFN is bad and the transaction is aborted.

**5** Generate XMI Address

Load zeros into XMI A<39:34>. Load PMRE<24:0> into XMI A<33:9>. Load VME A0–A08 into XMI A<8:0>.

## 2.5.3 40-Bit VAX Address Translation

The 40-bit VAX address translation mode uses three different page sizes: 512 bytes, 4 Kbytes, and 8 Kbytes. The mapped address range depends on the selected page size.

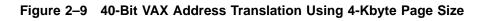

#### 2.5.3.1 512-Byte Page Size When using a 512-byte page size in the 40-bit VAX address translation mode, the DWMVA maps only the first 32 Mbytes of VME memory address space to XMI memory address space (see Figure 2–8). This is the maximum range that can be mapped with 64K PMR entries.

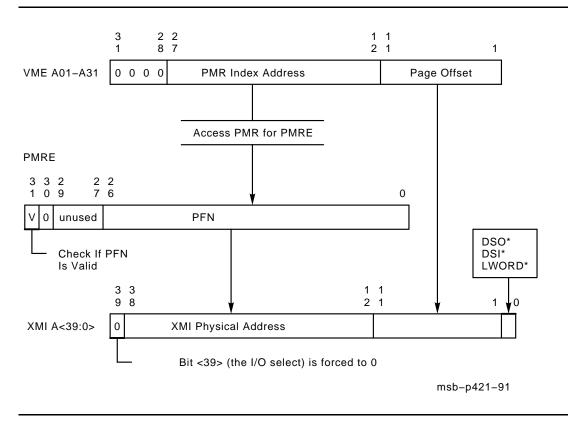

#### Figure 2–8 40-Bit VAX Address Translation Using 512-Byte Page Size

The translation of a VME DMA address to a 40-bit XMI address uses VME address bits VME A09–A24 as an index into the PMRs. These bits select the PMRE that contains the required PFN. Because in this mode the DWMVA only maps the first 32 Mbytes of VME memory address space, the upper address bits of the VME address, VME A25–A31, must be zero. The validity of the PFN is checked and if good the PFN is used to complete the DMA address translation. The 40-bit physical address is obtained by combining the PFN field of the PMRE (PMRE<29:0>) with VME address bits VME A0–A08. The steps used for 40-bit address translation are as follows:

1 Check Upper Address Bits

VME A25-A31 must all be zero.

**2** Access PMR for PMRE

VME address VME A09–A24 used as an index into the PMR to fetch the PMRE.

3 Check PMRE Valid Bit

If PMRE<31> = 1, then PFN is valid. If PMRE<31> = 0, then PFN is invalid and transaction is aborted.

4 ECC Check

If no error or correctable error, then PFN is good. If uncorrectable error, then PFN is bad and the transaction is aborted.

**5** Generate XMI Address

Load zero into XMI A<39>. Load PMRE<29:0> into XMI A<38:9>. Load VME A0–A08 into XMI A<8:0>.

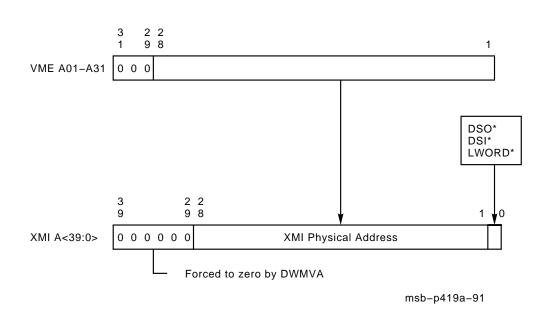

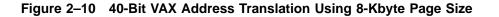

#### 2.5.3.2 4-Kbyte Page Size When using a 4-Kbyte page size in 40-bit VAX address translation mode, the DWMVA maps only the first 256 Mbytes of VME memory address space to XMI memory address space (see Figure 2–9). This is the maximum range that can be mapped with 64K PMR entries.

The 40-bit translation of a VME DMA address using 4-Kbyte page sizes uses VME address bits VME A12–A27 as an index into the PMRs. These bits select the PMRE that contains the required PFN. Because in this mode the DWMVA only maps the first 256 Mbytes of VME memory address space, the upper address bits of the VME address, VME A28– A31, must be zero. The validity of the PFN is checked and if good the PFN is used to complete the DMA address translation. The 40-bit physical address is obtained by combining the PFN field of the PMRE (PMRE<26:0>) with VME address bits VME A0–A11. The steps used for 40-bit address translation using 4-Kbyte page sizes are as follows:

1 Check Upper Address Bits

VME A28-A31 must all be zero.

**2** Access PMR for PMRE

VME address VME A12–A27 used as an index into the PMR to fetch the PMRE.

3 Check PMRE Valid Bit

If PMRE<31> = 1, then PFN is valid. If PMRE<31> = 0, then PFN is invalid and transaction is aborted.

4 ECC Check

If no error or correctable error, then PFN is good. If uncorrectable error, then PFN is bad and the transaction is aborted.

**5** Generate XMI Address

Load zeros into XMI A<39>. Load PMRE<26:0> into XMI A<38:12>. Load VME A0-A11 into XMI A<11:0>.

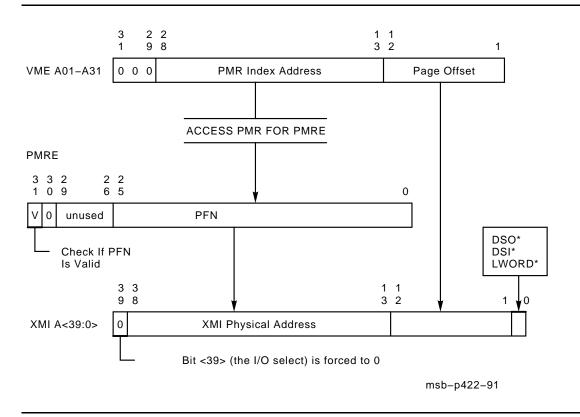

#### 2.5.3.3 8-Kbyte Page Size

When using an 8-Kbyte page size in 40-bit VAX address translation mode, the DWMVA can map 512 Mbytes of VME memory address space to XMI memory address space (see Figure 2–10). This is the maximum range that can be mapped with 64K PMR entries.

The 40-bit translation of a VME DMA address using 8-Kbyte page sizes uses VME address bits VME A13–A28 as an index into the PMRs. The validity of the PFN is checked and, if good, the PFN is used to complete the DMA address translation. The 40-bit physical address is obtained by combining the PFN field of the PMRE (PMRE<25:0>) with VME address bits VME A0–A12. The steps used for 40-bit address translation using 8-Kbyte page sizes are as follows:

1 Check Upper Address Bits

VME A29–A31 must be zero.

**2** Access PMR for PMRE

VME address VME A13–A28 used as an index into the PMR to fetch the PMRE.

**3** Check PMRE Valid Bit

If PMRE<31> = 1, then PFN is valid. If PMRE<31> = 0, then PFN is invalid and transaction is aborted.

4 ECC Check

If no error or correctable error, then PFN is good. If uncorrectable error, then PFN is bad and the transaction is aborted.

**5** Generate XMI Address

Load zeros into XMI A<39>. Load PMRE<24:0> into XMI A<38:13>. Load VME A0-A12 into XMI A<12:0>.

# VME System Control

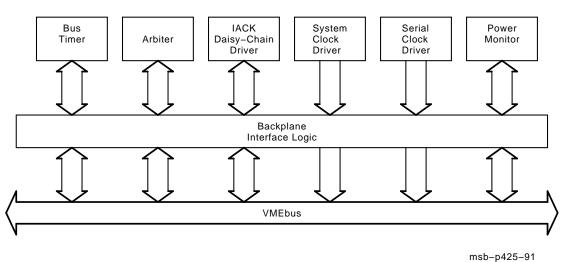

The C3200 module contains the VME system controller (VSC) that includes all the hardware necessary to provide timing and control to the VME system. The VSC consists of the following elements:

- Bus timer

- VME arbitration

- IACK daisy-chain driver

- System clock driver

- Serial clock driver

In addition, the DWMVA requires an external power monitor provided by the system integrator.

Figure 3–1 shows a block diagram of the VME system controller, including the power monitor.

#### Figure 3–1 VME System Controller Block Diagram

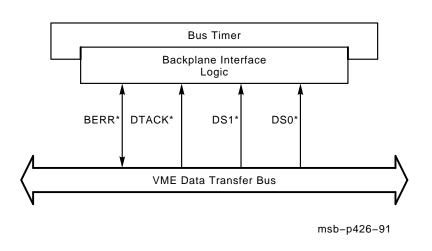

### 3.1 Bus Timer

The bus timer asserts BERR<sup>\*1</sup>, the bus error line, to indicate to the master that the data transfer was not completed. BERR<sup>\*</sup> is asserted when the first data strobe (DS0<sup>\*</sup> or DS1<sup>\*</sup>) stays asserted for longer than the bus timeout period, and DTACK<sup>\*</sup> and BERR<sup>\*</sup> are deasserted. Figure 3–2 shows a block diagram of the bus timer.

Figure 3–2 Bus Timer Block Diagram

The timeout value is set by software. The timeout period is programmed in bits <18:16> of the DWMVA Device/Configuration Register, as shown in Table 3–1.

Table 3–1 VME Transaction Timeout Selection

| VDCR<18:16> | Timeout Value     |

|-------------|-------------------|

| 111         | Timeouts disabled |

| 110         | 3.28 ms           |

| 101         | 819 μs            |

| 100         | 128 μs            |

| 011         | 64.0 <i>µ</i> s   |

| 010         | 32.0 µs           |

| 001         | 12.8 <i>µ</i> s   |

| 000         | 800 ns            |

The transaction timeout period causes an interrupt if the Enable VME Transaction Timeout Interrupt bit (VICR<21>) is set.

<sup>&</sup>lt;sup>1</sup> An asterisk (\*) appended to a VME signal name indicates a low true signal.

### 3.2 Arbitration

The VME system controller contains an arbitration subsystem that supports arbitration algorithms and timeouts. The type of arbitration is selected by software.

The arbiter is responsible for allocating the data transfer bus to optimize bus usage and prevent two or more masters from using the bus simultaneously.

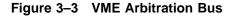

#### 3.2.1 Arbitration Subsystem Input/Output

The arbitration subsystem of the VME system controller uses the following signals:

Bused signals

- BR0\* through BR3\*

- BBSY\*

- BCLR\*

Daisy-chained signals

- BG0IN\* through BG3IN\*

- BG0OUT\* through BG3OUT\*

The bus request lines, BR0\* through BR3\*, are asserted by a requester of the data transfer bus. These lines are monitored by the arbiter, which in turn asserts the appropriate bus grant line BG0OUT\* through BG3OUT\*. The bus grant signals are propagated down the backplane in a daisy-chained manner. The bus grant line, BGxOUT\*, asserted by the arbiter, is monitored by the option in slot 2 on the BGxIN\* line of the option. If this device is not currently requesting the bus, it passes the bus grant to the next device on the backplane by asserting its BGxOUT\* line, which is received on the next module via the BGxIN\* signal, and so on. If the device receiving BGxIN\* has a request pending at that particular level, BBSY\* is asserted by the device and all other devices are prevented from using the bus. The logical connections of the arbitration bus are shown in Figure 3–3.

#### VME System Control

Other arbitration signals are BBSY\*, the bus busy line, and BCLR\*, the bus clear line. After receiving a bus grant, a requester asserts BBSY\* to inform the arbiter that it has received the bus grant and is using the bus. See Chapter 5 for a complete description of VMEbus signals.

### 3.2.2 Arbitration Algorithms

The arbiter logic on the C3200 module supports four arbitration algorithms. The first three of these are defined in the VME specification; the fourth is DWMVA specific. The type of arbitration is determined by bits <30:29> of the DWMVA Device/Configuration Register. The default arbitration set at power-up and at node reset is round robin. The algorithms are described in Table 3–2.

| VDCR    | Algorithm                         | Description                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <30:29> | Algorithm                         | Description                                                                                                                                                                                                                                                                                                                                                  |

| 00      | Round<br>robin                    | Grants the bus on a rotating basis. When the bus is granted to requester $BR(n)^*$ , the highest priority requester for the next bus cycle becomes $BR(n-1)^*$ . $BR(n)^*$ now becomes the lowest priority device. $BR(n)^*$ is only allowed access to the bus after all devices currently requesting the bus have received bus grants, in descending order. |

| 01      | Prioritized                       | Assigns the bus on a fixed priority basis, with BR3* having<br>the highest priority and BR0* the lowest. If a higher priority<br>device requests the bus while a lower priority device is<br>using it, the arbiter asserts BCLR*, requesting that the<br>low-priority device relinquish the bus to the higher priority<br>device.                            |

| 10      | Prioritized<br>and<br>round robin | Combines the prioritized and round robin arbitration algorithms. The BR3* line has the highest priority, while BR2*–BR0* are granted in a round robin fashion.                                                                                                                                                                                               |

| 11      | Single                            | Accepts only requests on BR3* and relies on the BG3OUT*/BG3IN* daisy-chain to arbitrate as well as grant the requests.                                                                                                                                                                                                                                       |

Table 3–2

VME Arbitration Algorithms

The VMEbus implements an additional level of arbitration that is based on placement of VME devices in the backplane. For example, if two devices are configured to request the bus at BR3, the device in the lower numbered slot (physically closer to the arbiter) has priority, because any device receiving the BG3IN signal can choose to not propagate the signal to the next slot through BG3OUT, if it is currently requesting the bus (both devices are asserting BR3).

Bus request conflicts can be minimized by judicious assignment of BR levels and backplane slots to the VME devices. In addition, the selection of appropriate requester types enables the VME system integrator to eliminate any lockout possibilities that the conflict condition may cause. Refer to Section 3.2.5 for additional discussion on requester types.

#### 3.2.3 Bus Request Level Assignment

The bus request levels for the C3200 module are determined by bits <25:24> of the DWMVA Device/Configuration Register (see Table 3–3). The bus request level for other VME devices is typically configured using jumpers on the module.

| VDCR<25:24> | Selected Bus Request Level |  |

|-------------|----------------------------|--|

| 00          | Bus Request Level 0 (BR0)  |  |

| 01          | Bus Request Level 1 (BR1)  |  |

| 10          | Bus Request Level 2 (BR2)  |  |

| 11          | Bus Request Level 3 (BR3)  |  |

Table 3–3 VME Bus Request Level Codes

## 3.2.4 Arbitration Timeout Counter

The arbitration timeout counter prevents the VME from hanging in the event of a failure by the DWMVA adapter. The timer causes the arbitrer to stop driving BGxOUT\* if, after a period of time, the requester has not asserted BBSY\*. The arbitration timeout period is determined by bits <21:19> in the DWMVA Device/Configuration Register (see Table 3–4). The arbitration timeout causes an interrupt if the Enable VME Arbitration Timeout Interrupt bit (VICR<21>) is set.

Table 3–4 VME Arbitration Timeout Selection

| VDCR<21:19> | Timeout Value     |  |

|-------------|-------------------|--|

| 111         | Timeouts disabled |  |

| 110         | 3.28 ms           |  |

| 101         | 819 μs            |  |

| 100         | 128 μs            |  |

| 011         | 64.0 µs           |  |

| 010         | 32.0 µs           |  |

| 001         | 12.8 <i>µ</i> s   |  |

| 000         | 800 ns            |  |

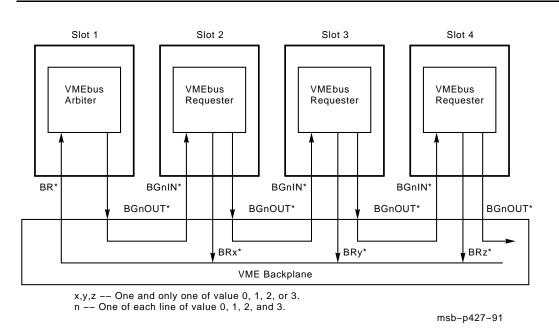

## 3.2.5 Data Transfer Bus Requesters

A requester is a functional block on the C3200 module that is responsible for requesting the VME bus for CPU writes and reads to VME slaves. The requester does not physically form part of the VSC. However, it is functionally related to the VME arbitration, and is described here to complete the arbitration discussion. Figure 3–4 shows a block diagram of a VMEbus requester.

The requester is notified by on-board logic that the VMEbus will be required to complete the current transaction. As a result, the requester asserts BRx\* on the VMEbus. The pending transaction halts until the arbiter grants permission to use the VMEbus. The requester then monitors the BGxIN\* signals. When it detects an asserted BGxIN\* signal at the same level as the BRx it sent, it does not pass on that BGxIN\*

Figure 3–4 VMEbus Requester Block Diagram

along the arbitration daisy-chain, but uses the bus grant to drive the bus and complete its pending transaction.

The VME specification defines three types of requesters:

- Release when done (RWD)

- Release on request (ROR)

- FAIR

An RWD requester releases the bus by deasserting BBSY\* when its master no longer needs the bus for its current data transfer. An RWD requester need not monitor BR3\*–BR0\*, since it will release the bus upon completion of its transaction regardless of the values of the bus request lines.

An ROR requester does not deassert BBSY\* when its master no longer needs the bus, but instead holds the bus until it detects another requester asserting a BRx\* signal. This type of requester, therefore, monitors  $BR3^{*}-BR0^{*}$  continuously once it has ownership of the bus. The release of the bus upon detection of  $BRx^{*}$  by another requester reduces the amount of arbitration on the bus when the master of the ROR requester is generating a large percentage of the bus traffic.

A FAIR requester is used in the case of more than one master sharing the same bus request level. After it has been granted the bus, a FAIR requester will not request the bus again as long as there are any active bus requests pending at its bus request level. To implement a FAIR requester, the bus requester logic must be able to monitor at least its own bus request level line.

NOTE: The RWD and ROR capabilities describe the conditions under which a requester relinquishes control of the data transfer bus. The FAIR capability describes under what condition a requester

# will request control of the data transfer bus. Therefore, RWD and ROR requesters can include the FAIR capability as well.

All three types of requesters are supported by the DWMVA. However, the preferred type is an ROR FAIR requester. The DWMVA requester type is RWD FAIR.

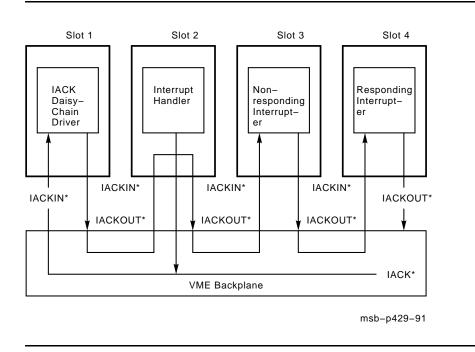

## 3.3 IACK Daisy-Chain Driver

The DWMVA provides an IACK daisy-chain driver as required by all slot 1 VME devices. The IACK daisy-chain driver generates the signal IACKOUT\* each time an interrupt handler initiates an interrupt acknowledge cycle by asserting IACK\*. The IACKOUT\* signal propagates to the module in slot 2 of the VME backplane as IACKIN\*. This module propagates the interrupt acknowledge on its IACKOUT\* line if it does not have an interrupt pending at the level present on A01–A03. This IACKOUT\* enters the module at VME slot 3 as IACKIN\*, and so on down the backplane.

When the IACKIN<sup>\*</sup> reaches the module with the current interrupt pending at the correct level, that module does not propagate IACKOUT<sup>\*</sup>. Instead, the interrupting device returns its vector to the interrupt handler in response to the interrupt acknowledge cycle.

The IACK daisy-chain driver is illustrated in Figure 3–5.

# 3.4 System Clock Driver

The system clock is an independent, nongated, fixed-frequency, 16 MHz, 50% (nominal) duty cycle signal (SYSCLK). The system clock driver is located on the system controller module. SYSCLK is always driven by the C3200 module, which must be installed in slot 1 of the VMEbus backplane.

# 3.5 Serial Clock Driver

The serial clock driver provides a programmable, special waveform signal used by serial modules that reside on VME-compatible boards. SERCLK in conjunction with SERDAT\* provides a serial communication link between boards. The C3200 module does not drive the SERDAT\* line, but it does provide the serial clock for any module on the VME backplane that needs it. The clock source is software programmable to 32, 16, 8, and 4 MHz (see description of VDCR in Chapter 7).

# 3.6 **Power Monitor**

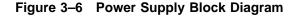

The power monitor detects power failures and signals the system by issuing an IVINTR (see descriptions of AREAR and AESR in Chapter 7). When power is then reapplied to the system, the power monitor ensures that all other modules are initialized. Whenever any board asserts SYSRESET\*, the power monitor holds the signal asserted for a minimum of 200 ms. Figure 3–6 shows a block diagram of the VME power supply.

NOTE: The power monitor is provided by the system integrator through an external module.

# Transactions

The DWMVA performs two types of transactions:

- CPU transactions

- DMA transactions

A CPU transaction is initiated by a processor on the XMI bus. The processor is the commander. The DWMVA becomes the responder. A DMA transaction begins on the VMEbus and targets XMI memory through the DWMVA adapter.

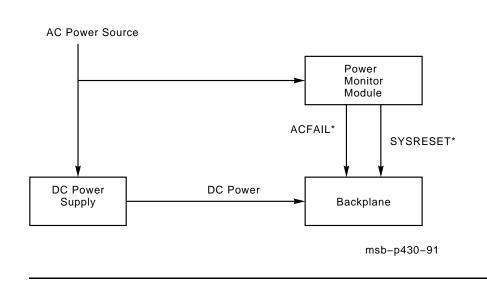

This chapter explains how the two types of transactions are processed through the C3200 module, between the IBUS and the VMEbus. Figure 4–1 shows the data paths and the major logic sections on the C3200 module.

Figure 4–1 C3200 Block Diagram

### 4.1 Command Translation

The XMI and the VMEbus use different commands. A translation of commands must take place over the XMI-to-VME data path for commands initiated on the XMI to be executed on the VME, and vice versa.

### 4.1.1 XMI-to-VME Translation

The DWMVA generates VME commands when it is acting as the responder to an XMI-initiated transaction. The DWMVA accepts only longword CPU transactions. Hexword, octaword, and quadword Write Mask transactions are illegal when targeted at I/O space.

Interlock Read/Unlock Write pairs on the XMI are translated into Read Modify Write (RMW) commands on the VME. Due to differences in protocol between the XMI and VME, some problems may occur and the Interlock Read/Unlock Write may get separated into distinct read and write transactions on the VMEbus, as explained in Section 4.2.2.4. If this condition occurs, the C3200 sets an error bit and generates an interrupt, if enabled to do so. The C3200 does not generate interrupts to the VME. Table 4–1 shows the XMI-to-VME command translations.

| ХМІ                          | VME                                        |

|------------------------------|--------------------------------------------|

| Longword Read                | Byte/Word/Longword Read                    |

| Quadword Read                | Illegal                                    |

| Octaword Read                | Illegal                                    |

| Hexword Read                 | Illegal                                    |

| Longword Masked Write        | Byte/Word/Longword Write                   |

| Quadword Masked Write        | Illegal                                    |

| Octaword Masked Write        | Illegal                                    |

| Hexword Masked Write         | Illegal                                    |

| Longword Interlock Read      | Byte/Word/Longword Read - Start of VME RMW |

| Quadword Interlock Read      | Illegal                                    |

| Octaword Interlock Read      | Illegal                                    |

| Hexword Interlock Read       | Illegal                                    |

| Longword Unlock Masked Write | Byte/Word/Longword Write - End of VME RMW  |

| Quadword Unlock Masked Write | Illegal                                    |

| Octaword Unlock Masked Write | Illegal                                    |

| Hexword Unlock Masked Write  | Illegal                                    |

| IDENT                        | Interrupt Acknowledge                      |

Table 4–1 XMI-to-VME Command Translations

# 4.1.2 VME-to-XMI Translation

When the DWMVA processes a DMA transaction, it generates the corresponding XMI command.

A VME read or write can be 1, 2, 3, or 4 bytes of data. The smallest unit of data that can be addressed in XMI memory space is a quadword. Therefore, VME reads translate into XMI quadword reads, and VME writes into quadword masked writes.

Because VME block transfers are assumed to be quite long, the C3200 always issues octaword transactions when it decodes a VME block transfer.

Table 4-2 shows the VME-to-XMI command translations.

| VME               | ХМІ                                                |  |  |

|-------------------|----------------------------------------------------|--|--|

| Read              | Quadword Read                                      |  |  |

| Write             | Quadword Write Mask                                |  |  |

| Block Read        | Octaword Read                                      |  |  |

| Block Write       | Octaword Write Mask                                |  |  |

| Read Modify Write | A VME RMW translates to the following XM sequence: |  |  |

|                   | 1 Quadword Interlock Read                          |  |  |

|                   | 2 Quadword Unlock Write                            |  |  |

| Address Only      | No-op                                              |  |  |

| Interrupt         | INTR                                               |  |  |

Table 4–2 VME-to-XMI Command Translations

## 4.2 CPU Transaction Process

The CPU initiates the following transactions:

- DWMVA register transactions

- VME device transactions

When a CPU targets the VMEbus as the destination of a transaction, the T2018 accepts the command and stores it in its internal data buffer. The T2018 then informs the C3200 module that it has a CPU transaction in its buffer that is ready to be transmitted to the VMEbus.

The C3200 checks the status of the IBUS. If the IBUS is available, the C3200 loads the CPU transaction into its internal CPU data buffer. Once the buffer is loaded, the C3200 begins requesting the VMEbus. When the C3200 receives the bus grant indicating that it is the VMEbus master, it drives the CPU transaction onto the VME. The targeted VME slave

responds with an acknowledgment. The CPU transaction is complete at this point if it is a CPU write.

If the transaction is a CPU read, the C3200 latches read return data from the VME slave into its internal buffer. The C3200 checks the status of the IBUS. When the IBUS is available, the C3200 causes the read return data to be loaded over the IBUS into the T2018's CPU buffer. When the T2018 receives the data, it arbitrates for the XMI and returns the data to the processor.

### 4.2.1 DWMVA Register Transactions

DWMVA registers can be read or written by an XMI processor. They are not accessible by VME devices.

#### 4.2.1.1 T2018 Register Read/Write

If the CPU transaction is a write to a T2018 register, the T2018 receive state machine writes the data into the addressed control/status register (CSR).

In a read transaction, the T2018 receive state machine sets its Busy flag after the T2018 acknowledges a read command from an XMI commander. The T2018 then arbitrates for the XMI as a responder. When granted use of the bus, the T2018 sends the data from its addressed register to the XMI commander. The T2018 receive state machine then clears its Busy flag and returns to its idle state.

#### 4.2.1.2 C3200 Register Read/Write

When the T2018 decodes a valid C3200 register address, it encodes the CSR to be accessed on the address lines, loads the CPU buffer, and signals the C3200 that a valid transaction is in the buffer. When the C3200 fetches the command and address over the IBUS, it determines if the transaction being sent across the IBUS is destined for a device on the VMEbus or is an access to one of the C3200's internal CSRs.

In a write transaction to a C3200 register, handshaking takes place between the T2018 and C3200 across the IBUS. First the T2018 receive state machine loads command, address, and data into the T2018 CPU buffer. Following this operation, the T2018 receive state machine sets the CPU Busy flag. The C3200 reads the data and checks parity. If the parity is good, the data is written into the addressed C3200 register. The C3200 then signals the processor the termination of the transaction. This clears the Busy flag in the T2018's CSR. If the C3200 detects bad parity, it asserts an error signal and does not write the data into the addressed register.

In a read transaction, the command and address are received by the C3200 in the same way as for a C3200 register write. The data is fetched from the addressed register on the C3200 and sent to the T2018 CPU buffer. The C3200 notifies the T2018 transmit state machine that the T2018 CPU buffer contains new data. The T2018 arbitrates for the XMI bus as a responder, sends the data to the XMI commander, and clears its Busy flag. The DWMVA has now completed the transaction and is ready to process

another. If the C3200 detects bad parity during the IBUS transfer, it does not return read data to the T2018 and asserts an error signal.

# NOTE: Certain DWMVA register transactions cause address-only cycles on the VME.

## 4.2.2 CPU-to-VME Device Transactions

The processor targets a VME device for a read or write transaction. There are three modes of CPU transactions. The transaction mode is specified by the address modifier code attached to the VME address. The address modifier codes used by the C3200 during CPU (XMI-to-VME) transactions are listed in Table 4–3.

| Code | Access Type                         |

|------|-------------------------------------|

| 2D   | Short supervisory access            |

| 3E   | Standard supervisory program access |

| 0E   | Extended supervisory program access |

#### 4.2.2.1 VME Device Write

When a CPU transaction targets a node on the VMEbus, the data is written into the C3200 internal buffer the same way as for a C3200 register write. Once the data is stored in the CPU buffer, the C3200 requests the VMEbus. After being granted use of the VMEbus, the C3200 broadcasts the address, address modifier, and data to be written over the VMEbus. The C3200 waits for DTACK\*, which indicates that the slave successfully received the data over the VMEbus. When the transaction is complete, the C3200 notifies the T2018 transmit state machine, which in turn clears the Busy flag. The transaction is now complete, and the DWMVA is ready to process a new transaction.

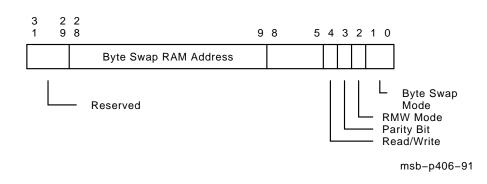

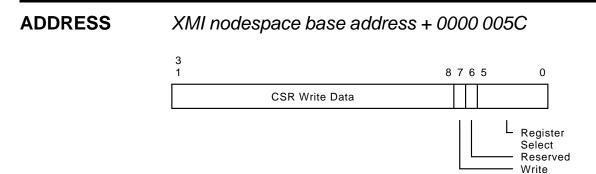

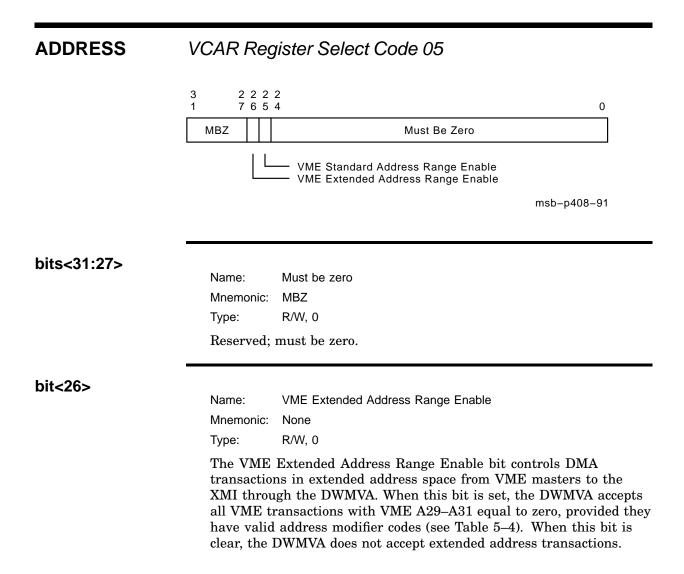

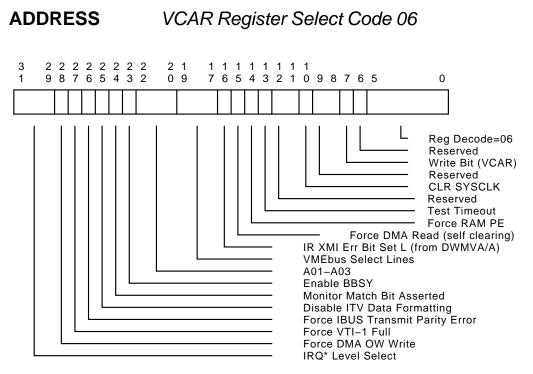

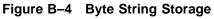

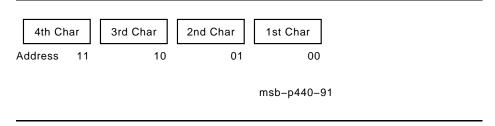

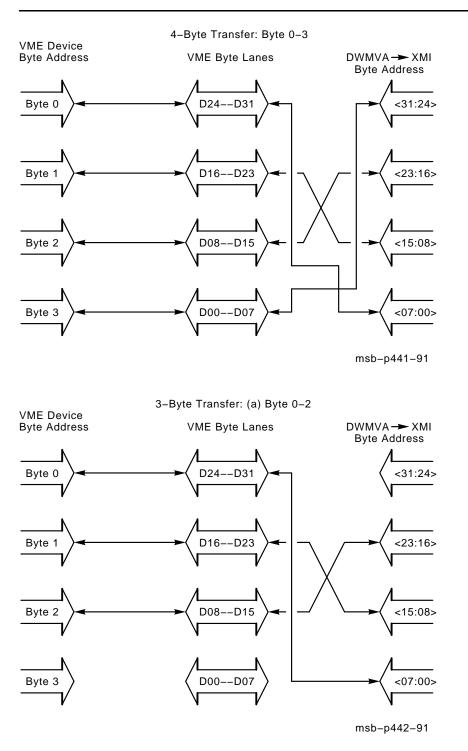

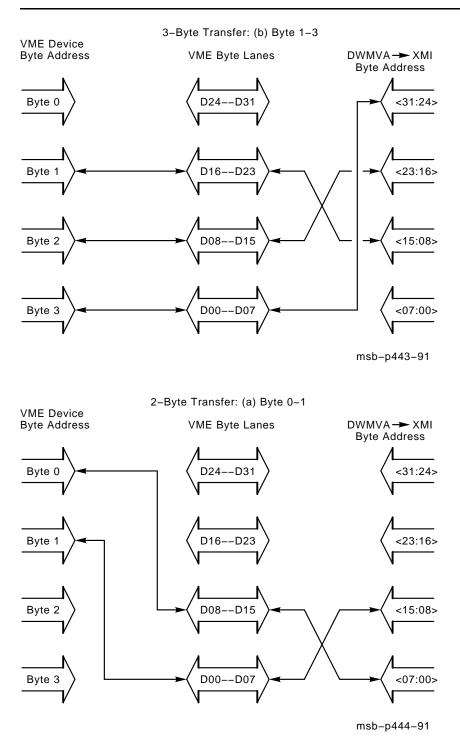

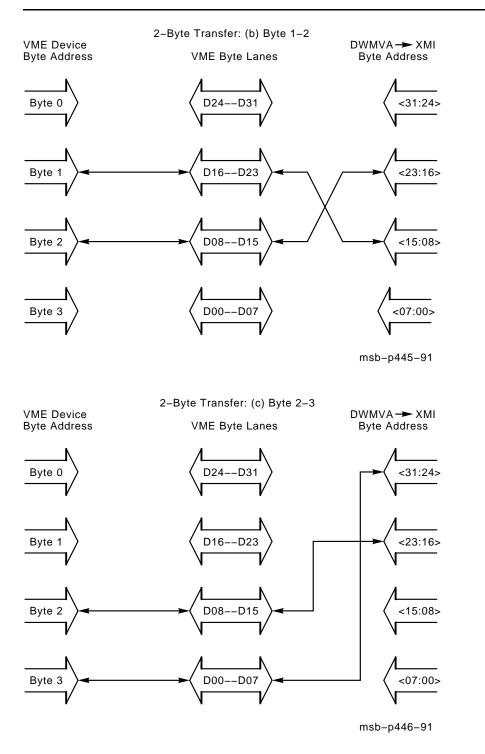

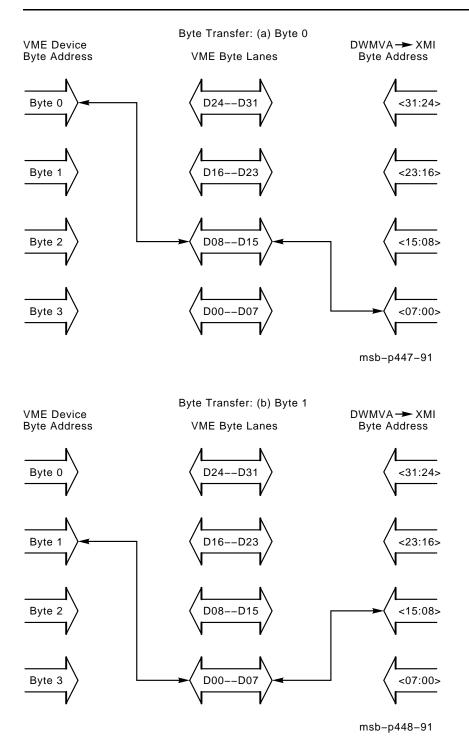

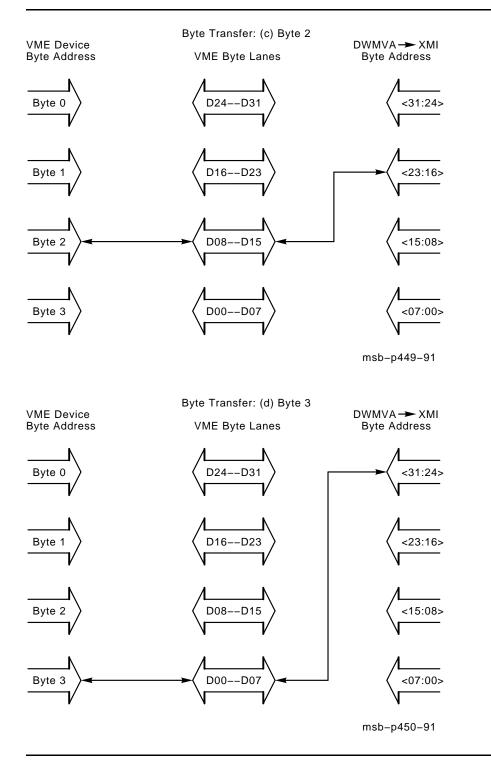

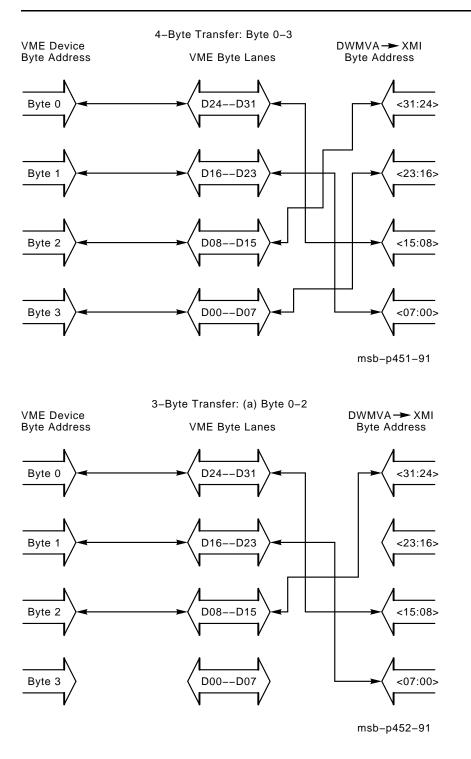

#### 4.2.2.2 VME Device Read