# DWBUA UNIBUS Adapter Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

#### Digital Equipment Corporation 1986 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Printed in U.S.A.

This document was set on a DIGITAL DECset Integrated Publishing System.

The following are trademarks of Digital Equipment Corporation:

DEC DECmate DECset DECsystem-10 DECSYSTEM-20 DECUS DECwriter DIBOL MASSBUS PDP P/OS Professional Rainbow RSTS RSX Scholar ULTRIX UNIBUS VAX VAXBI VMS VT Work Processor

### CONTENTS

#### Page

#### PREFACE

| n |   | D  | T  |   |  | INST  | ۸ | II. | A | TI | O        | N | l |

|---|---|----|----|---|--|-------|---|-----|---|----|----------|---|---|

| r | А | 1. | 91 | I |  | 11401 | n |     | • |    | <u> </u> | • |   |

### CHAPTER 1 INTRODUCTION

|       | PRODUCT DESCRIPTION      |     |

|-------|--------------------------|-----|

| 1.1   | PRODUCT DESCRIPTION      | 1-2 |

| 1.2   | SPECIFICATIONS           |     |

| 1.2.1 | Bus Loading              |     |

| 1.2.2 |                          |     |

| 1.2.3 | C D                      |     |

| 1.3   | SUPPORTED UNIBUS DEVICES | 1-2 |

### CHAPTER 2 INSTALLATION AND TEST

|       | OPTION COMPONENTS                 |                  |

|-------|-----------------------------------|------------------|

| 2.1   | OPTION COMPONENTS                 | 2.3              |

| 2.2   | INSTALLATION                      | 2-8              |

| 2.3   | TEST                              | 2-8              |

| 2.3.1 | Self-Test Microdiagnostic Program | 2.8              |

| 2.3.2 | Macrodiagnostic Program           |                  |

| 2.4   | TO ALLOL CCHOOTING                | *****            |

| 2.4.1 | Tools and Test Equipment          | ····· 2-γ<br>γ_0 |

| 2.4.2 |                                   |                  |

| 2.4.3 | Procedure<br>Helpful Hints        |                  |

### PART II TECHNICAL DESCRIPTION

### CHAPTER 3 PROGRAMMING

| n fan een een stel aan de stel stel een een een een stel stel stel stel stel stel stel stel | SYSTEM ADDRESS SPACE                                                  |       |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------|

| 3.1                                                                                         |                                                                       |       |

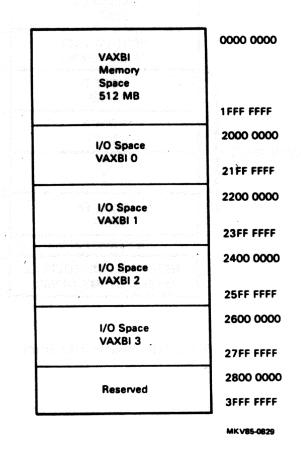

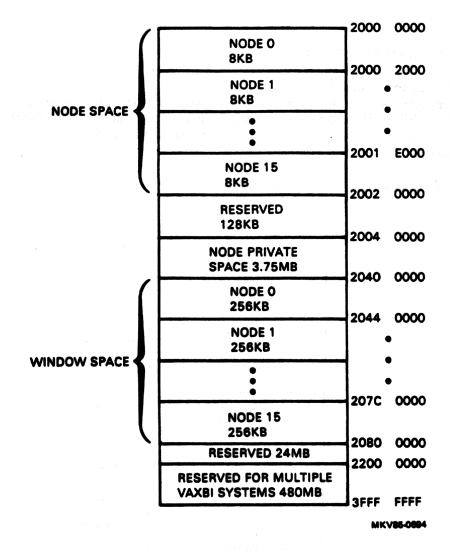

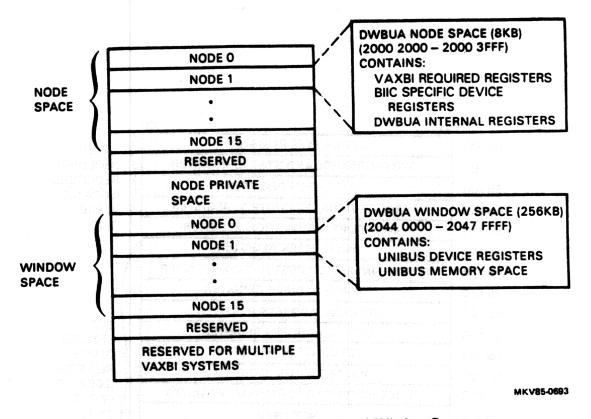

| 3.1.1                                                                                       | Address Space Distribution                                            | 3.7   |

| 3.1.2                                                                                       | Address Space Distribution<br>System I/O Space<br>DWBUA ADDRESS SPACE | 3-3   |

| 3.2                                                                                         | DWBUA ADDRESS SPACE                                                   |       |

| 3.2.1                                                                                       | Register Bit Characteristics                                          |       |

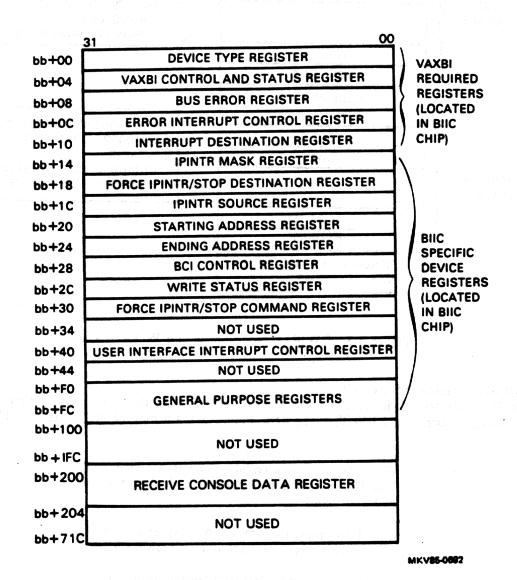

|                                                                                             | VAVDI Decuired Decisters                                              |       |

| 3.2.2                                                                                       | Error Interrupt Control Register                                      |       |

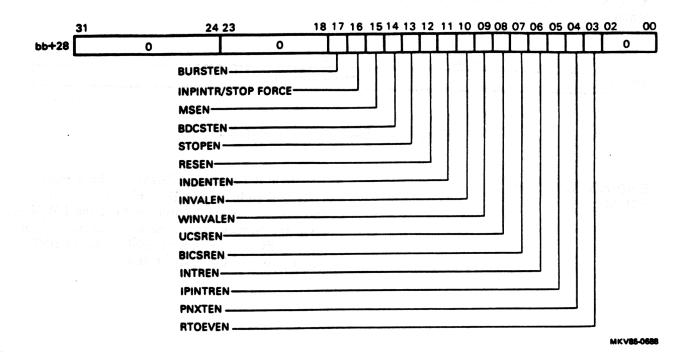

| 3.2.2.1                                                                                     | Error Interrupt Control Register                                      | 3-8   |

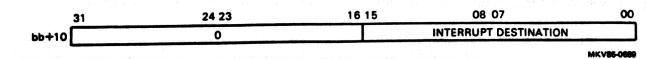

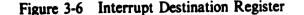

| 3.2.2.2                                                                                     | Interrupt Destination Register                                        | 3_0   |

| 3.2.3                                                                                       | DUC Casalic Device Peristers                                          | ····· |

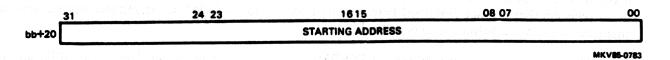

| 3.2.3.1                                                                                     | Starting Address Register                                             | 2 11  |

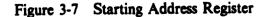

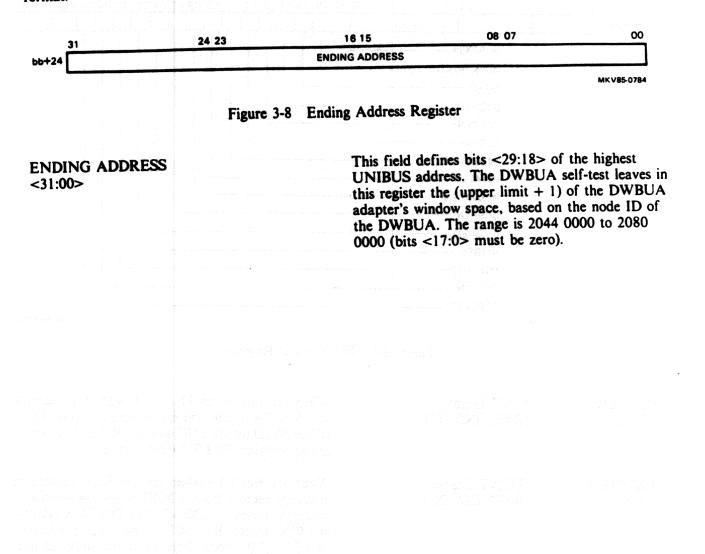

| 3.2.3.2                                                                                     | E-dias Address Degister                                               | J-11  |

| -                                                                                           |                                                                       |       |

| 3.2.3.3                                                                                     | BCI Control Register                                                  | 3-13  |

| 3.2.3.4                                                                                     | User Interface Interrupt Control Register                             | 3-14  |

| 3.2.3.5                                                                                     | General Purpose Registers                                             |       |

## **CONTENTS (Cont)**

e net

| P | 8   | ø | e |

|---|-----|---|---|

|   | 65. | 5 | • |

| 3.2.4   | DWBUA Internal Registers                     |

|---------|----------------------------------------------|

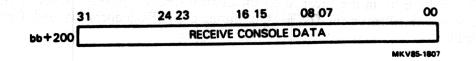

| 3.2.4.1 | Receive Console Data Register                |

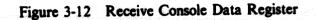

| 3.2.4.2 | DWBUA Control and Status Register            |

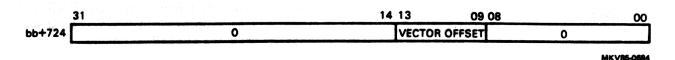

| 3.2.4.3 | Vector Offset Register                       |

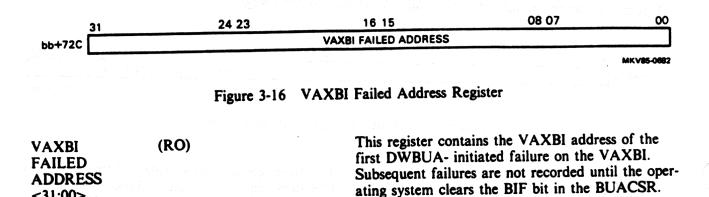

| 3.2.4.4 | Failed UNIBUS Address Register               |

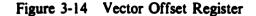

| 3.2.4.5 | VAXBI Failed Address Register                |

| 3.2.4.6 | Microdiagnostic Registers                    |

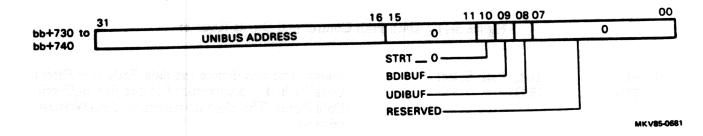

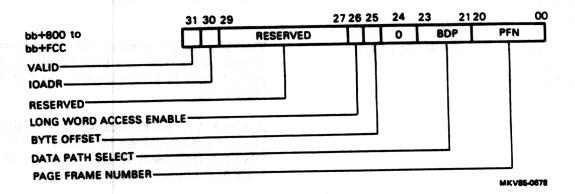

| 3.2.4.7 | Data Path Control and Status Registers       |

| 3.2.4.8 | Buffered Data Path Space                     |

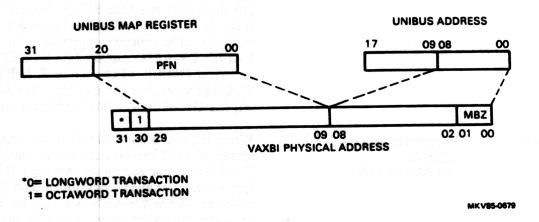

| 3.2.4.9 | UNIBUS Map Registers                         |

| 3.3     | INITIALIZATION                               |

| 3.3.1   | DWBUA Hardware Initialization                |

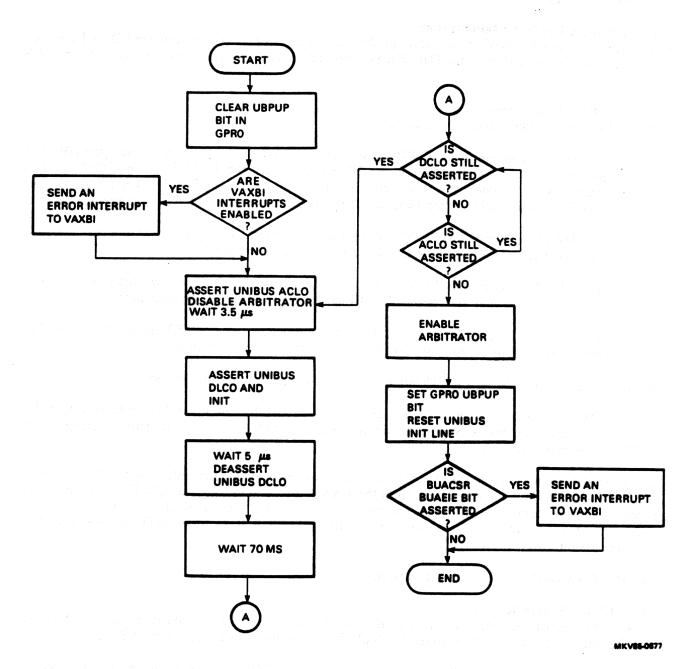

| 3.3.2   | UNIBUS Initialization                        |

| 3.4     | PROGRAMMING CONSIDERATIONS                   |

| 3.4.1   | UNIBUS Map Registers                         |

| 3.4.1.1 | Contiguous Allocation                        |

| 3.4.1.2 | Mapping to VAXBI I/O Space                   |

| 3.4.1.3 | BYTE OFFSET Bit                              |

| 3.4.2   | UNIBUS Power Down                            |

| 3.4.3   | Use of Buffered Data Paths                   |

| 3.4.4   | VAXBI Access to the DWBUA Internal Registers |

| 3.4.5   | Data Length                                  |

| 3.4.6   | IRCI/UWMCI Commands                          |

| 3.4.7   | UNIBUS DATIP                                 |

| 3.4.8   | Hung UNIBUS                                  |

| 3.4.9   | VAXBI Bus Error                              |

| 3.4.10  | UNIBUS Devices                               |

| 3.4.11  | Access to Nonexistent Registers              |

### CHAPTER 4 FUNCTIONAL DESCRIPTION

| 4.1     | INTRODUCTION                                               |

|---------|------------------------------------------------------------|

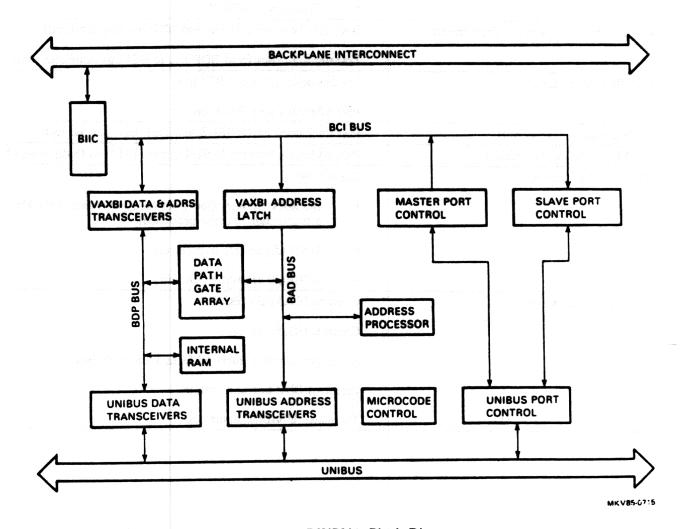

| 4.2     | BLOCK DIAGRAM                                              |

| 4.3     | TRANSACTIONS                                               |

| 4.3.1   | VAXBI-to-DWBUA Transactions                                |

| 4.3.1.1 | DWBUA Responses to VAXBI-to-DWBUA Transactions             |

| 4.3.1.2 | VAXBI-to-DWBUA Commands 4-5                                |

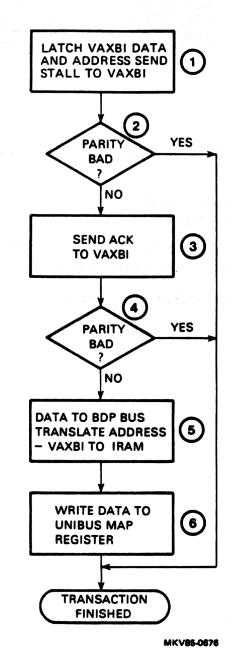

| 4.3.1.3 | Example: VAXBI WRITE to a UNIBUS Map Register              |

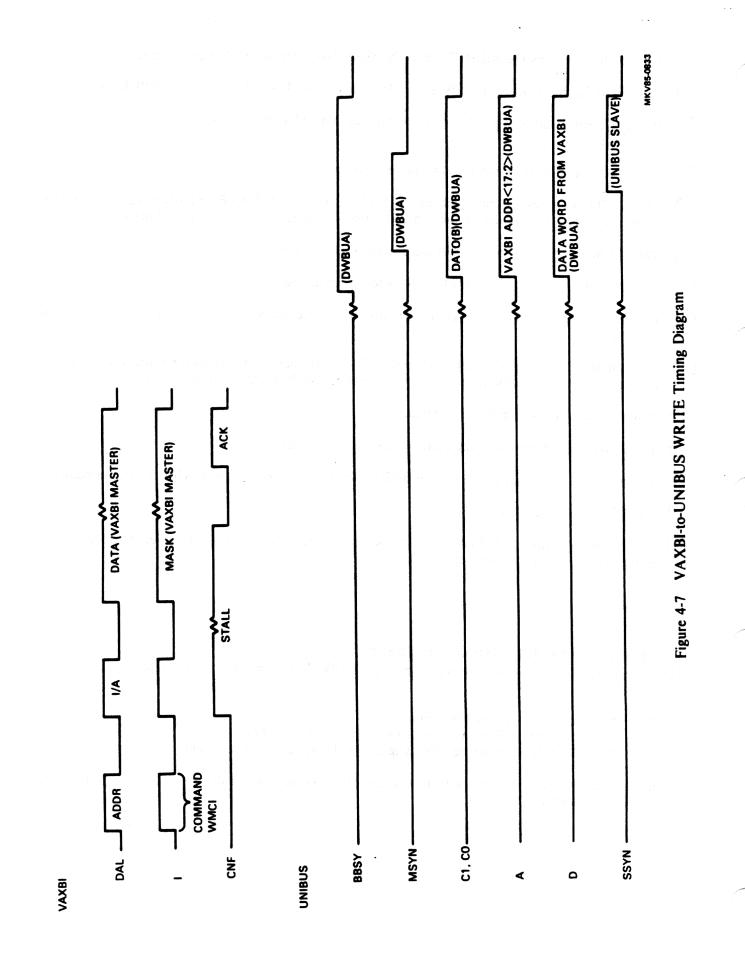

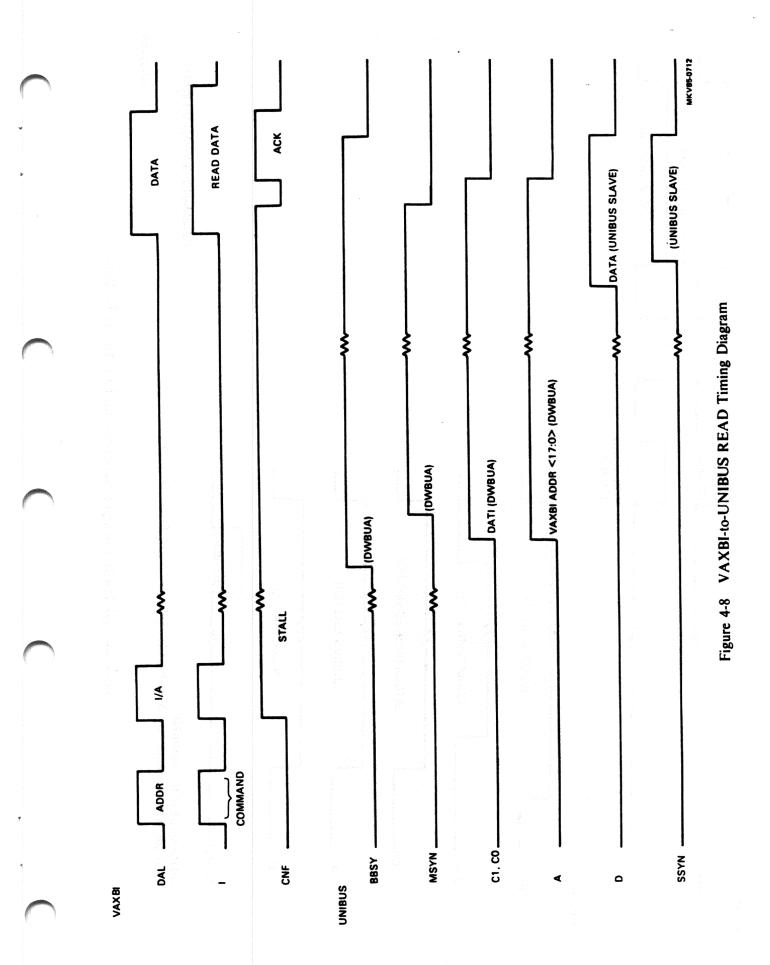

| 4.3.2   | VAXBI-to-UNIBUS Transactions                               |

| 4.3.2.1 | DWBUA Responses to VAXBI-to-UNIBUS Transactions            |

| 4.3.2.2 | VAXBI-to-UNIBUS Commands                                   |

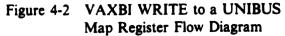

| 4.3.2.3 | Example: VAXBI READ of UNIBUS Data                         |

| 4.3.3   | UNIBUS-to-VAXBI Transactions                               |

| 4.3.3.1 | DWBUA Responses to UNIBUS-to-VAXBI Transactions            |

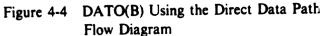

| 4.3.3.2 | UNIBUS-to-VAXBI Commands Through the Direct Data Path      |

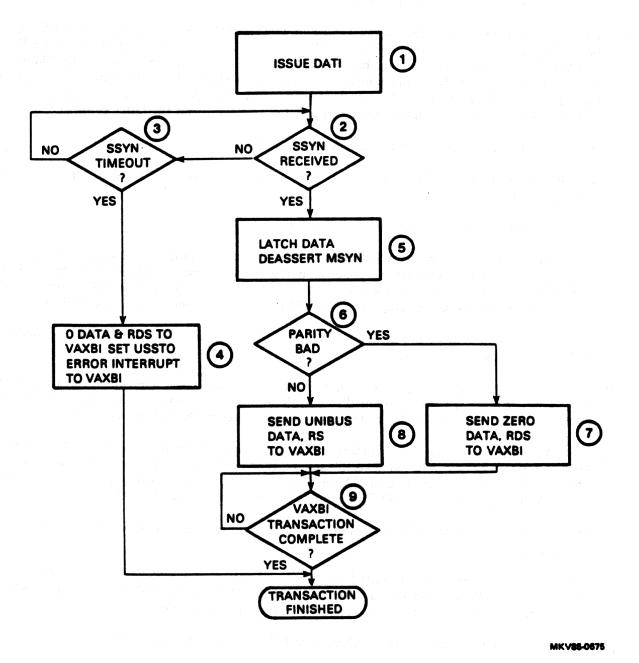

| 4.3.3.3 | Example: DATO(B) Using the Direct Data Path                |

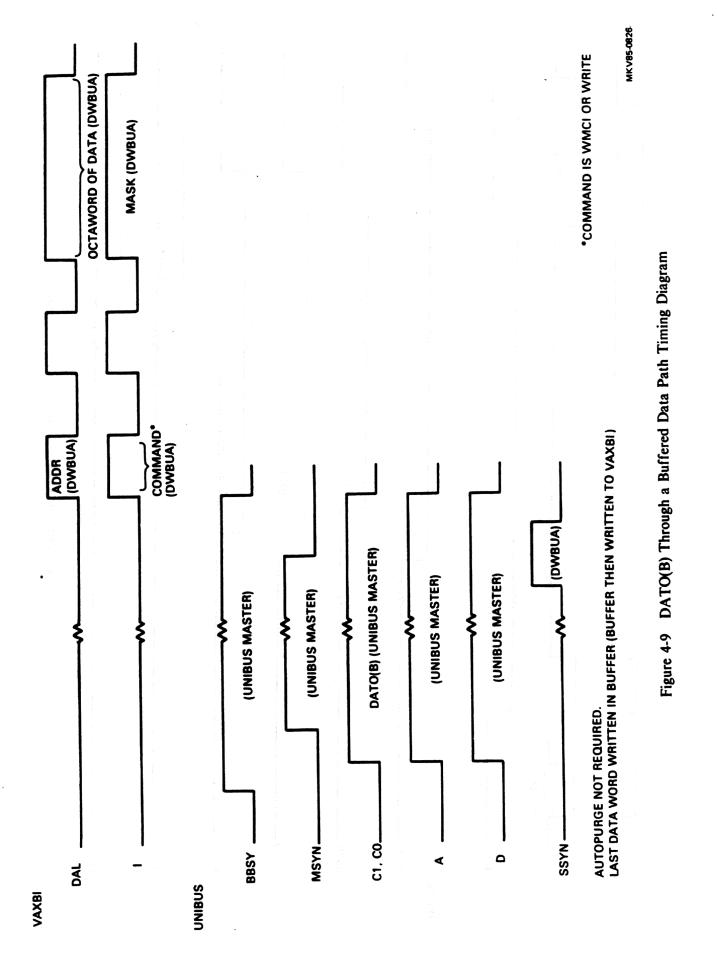

| 4.3.3.4 | UNIBUS-to-VAXBI Commands Through a Buffered Data Path 4-20 |

## **CONTENTS (Cont)**

#### Page

|            | Example: DATO Using a Buffered Data Path                    |                                        |

|------------|-------------------------------------------------------------|----------------------------------------|

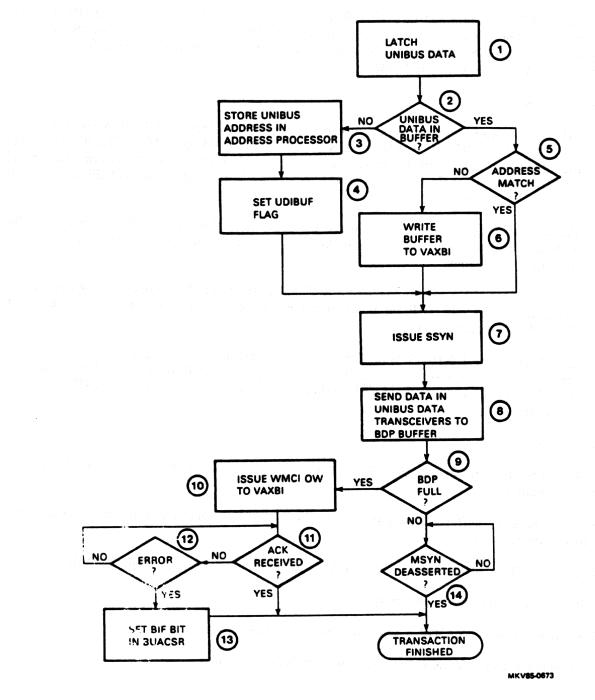

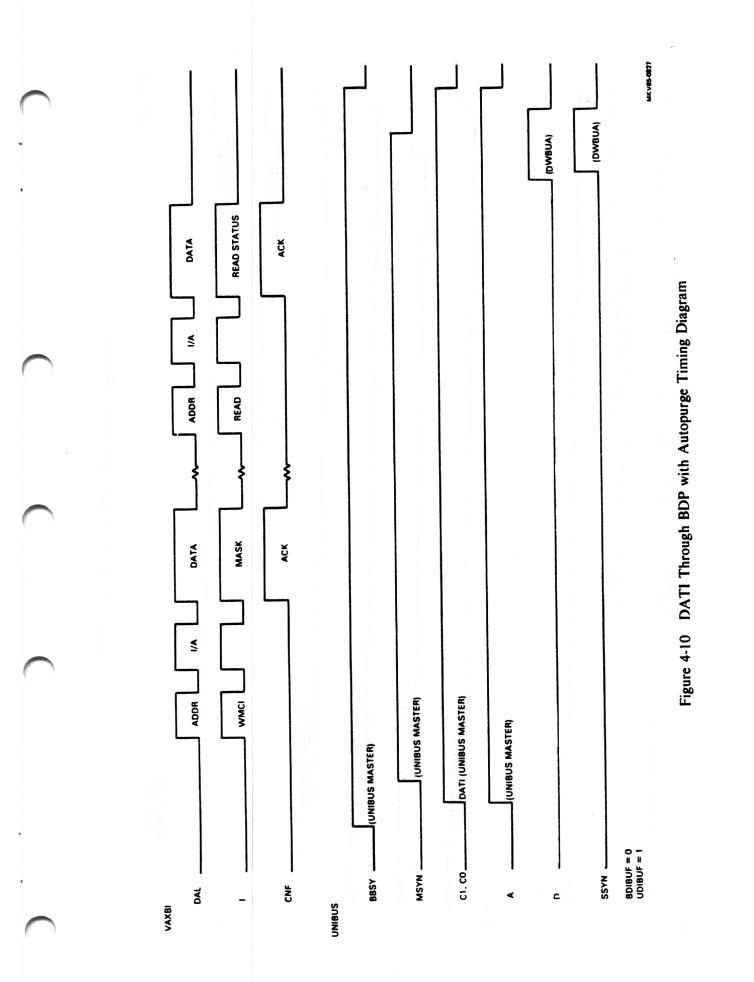

| 4.3.3.5    | Engender DATI Liging a Buffered Data Path                   |                                        |

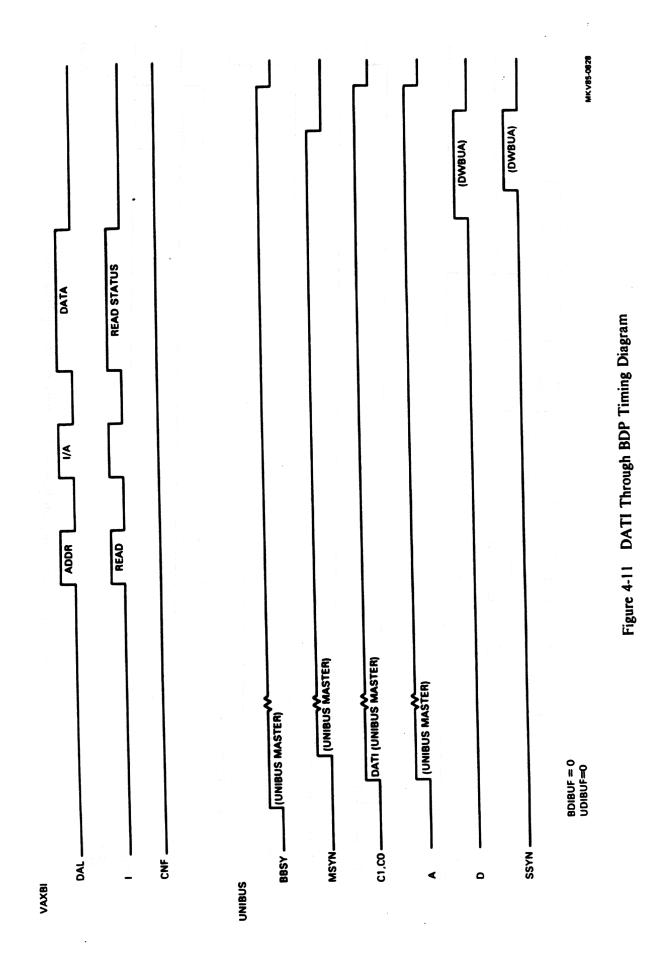

| 4.3.3.6    | REPRESENTATIVE TIMING DIAGRAMS                              |                                        |

| 4.4        | REPRESENTATIVE TIMINO DIAGRAMO                              |                                        |

|            |                                                             |                                        |

|            | THE PROPERTY INTOLIC DEVICES                                |                                        |

| APPENDIX A | DWBUA-SUPPORTED UNIBUS DEVICES                              |                                        |

|            |                                                             |                                        |

|            |                                                             |                                        |

| APPENDIX B | GLOSSARY                                                    |                                        |

|            | 1.1.2.1.1.2.1.1.2.1.1.1.1.1.1.1.1.1.1.1                     |                                        |

| APPENDIX C | SELF-TEST MICRODIAGNOSTIC TESTS                             |                                        |

| AFFEINDIA  |                                                             |                                        |

|            |                                                             |                                        |

|            | MACRODIAGNOSTIC TESTS                                       |                                        |

| APPENDIX D | MACKUDIAGNOSTIC ILSIO                                       |                                        |

|            |                                                             |                                        |

|            |                                                             |                                        |

| APPENDIX E | ERROR CONDITIONS                                            |                                        |

| E.1        | VAXBI-TO-UNIBUS TRANSACTIONS                                | E-1                                    |

| E.1.1      | Quadword and Octaword Transfers                             | ······································ |

|            | DUC E EVENT Codes                                           | E-I                                    |

| E.1.2      | Maak Valuer                                                 | E-I                                    |

| E.1.3      | Nonexistent UNIBUS Address                                  | E-2                                    |

| E.1.4      | Invalid VAXBI Command                                       |                                        |

| E.1.5      | Improper Use of a DWBUA Register                            |                                        |

| E.1.6      | Improper Use of a DWBOA Register                            | E-2                                    |

| E.2        | UNIBUS-TO-VAXBI TRANSACTIONS                                | F-7                                    |

| E.2.1      | VAXBI Error in UNIBUS-Initiated Transfer                    | E-3                                    |

| E.2.2      | Illegal Map Entries                                         | E-J                                    |

| E.2.3      | Illegal UNIBUS Transaction                                  | E-:                                    |

|            | A. C. S. W. S. C. A. S. |                                        |

| APPENDIX F | UNIBUS EXERCISER TERMINATOR                                 |                                        |

|            | UNIBUS EXERCISER TERMINATOR DESCRIPTION                     | <b>F-</b> 1                            |

| F.1        | TINIDUC EVEDCISED TERMINATOR REGINIERS                      |                                        |

| F.2        | Cantal Desister Format                                      | Γ-                                     |

| F.2.1      | Contral Desister Bit Descriptions                           |                                        |

| F.2.2      | NPR DATA TRANSFERS                                          |                                        |

| F.3        | UET WRITE                                                   | F-                                     |

| F.3.1      | UET WRITE                                                   | F-                                     |

| F.3.2      | UET READ                                                    | F.                                     |

| F.4        | BR INTERRUPTS                                               |                                        |

#### NODE SPACE AND WINDOW SPACE ADDRESSES **APPENDIX G**

v

APPENDIX H REGISTER INITIAL STATES

### **CONTENTS (Cont)**

Page

g a C

#### APPENDIX I DATA PATH OPERATION

| n is 1990 and an | DIRECT DATA PATH      |     |

|------------------------------------------------------|-----------------------|-----|

| I.2                                                  | BUFFERED DATA PATH    | I-2 |

| I.2.1                                                | Definitions           | I-3 |

| 1.2.2                                                | BYTE OFFSET Bit Clear | I-4 |

| 1.2.3                                                | BYTE OFFSET Bit Set   |     |

| 1.2.4                                                | Examples              | I-6 |

### APPENDIX J PORT LOCK, RETRY, AND INTERRUPT MECHANISMS

| J.1   | PORT LOCK MECHANISM      | I |

|-------|--------------------------|---|

| J.2   | RETRY MECHANISM          | I |

| J.3   | UNIBUS INTERRUPTS        | 2 |

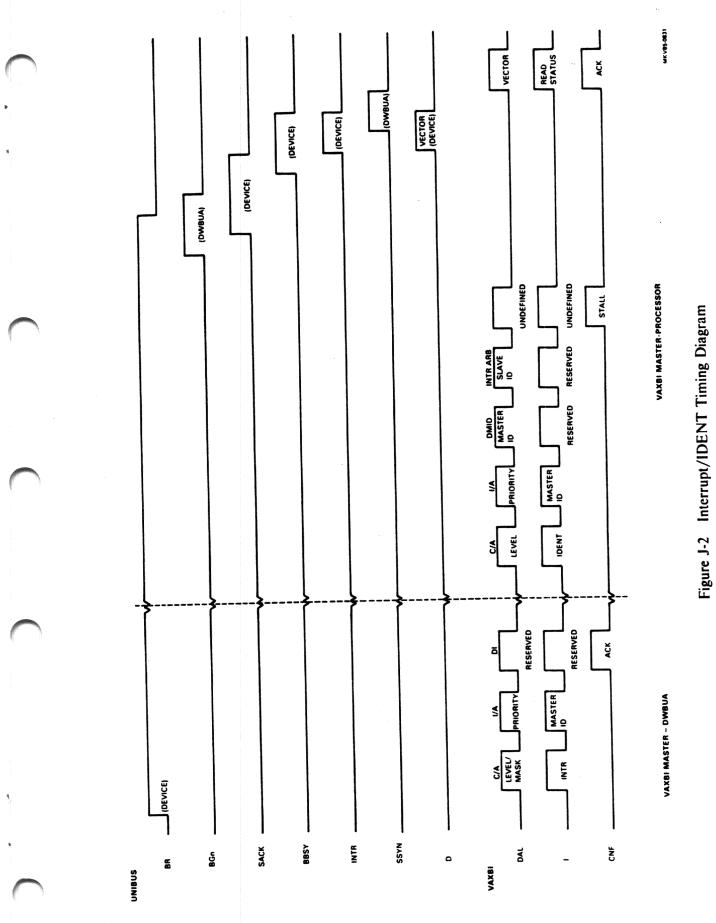

| J.3.1 | Interrupt/IDENT Sequence | 2 |

| J.3.2 | Passive Release          |   |

|       |                          | - |

#### APPENDIX K MSYN-SSYN TIME INTERVALS

#### APPENDIX L DWBUA PARITY CHECKING

| - JL. I | PARITY CHECKING                           | L-1 |

|---------|-------------------------------------------|-----|

| L.2     | INTERNAL RAM                              | L-1 |

| L.3     | PARITY ERRORS                             | L-1 |

| L.3.1   | Parity Errors on UNIBUS Map Registers     | L-1 |

| L.3.2   | Parity Errors on BDP Buffers              |     |

| L.3.3   | Parity Errors on Vector Registers         |     |

| L.3.4   | Parity Errors on DWBUA Internal Registers |     |

| L.4     | PARITY LOGIC TESTING                      |     |

#### INDEX

PPERMIX G - NORS SPACE AND WENTOW SPACE ADDRESSES

· 大学的科学者,我们的学校,在这些学校的情绪。

等的的非常的方面的,如何的情绪就能很感到**了了。**他说的话语警察

### FIGURES

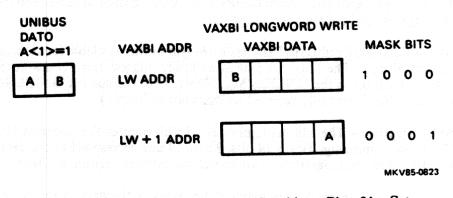

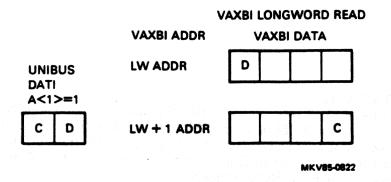

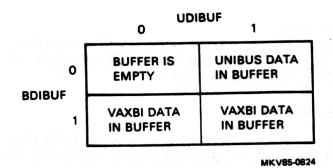

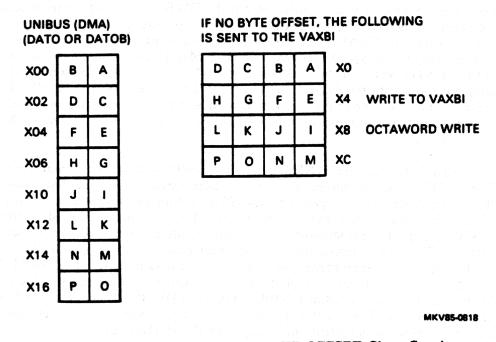

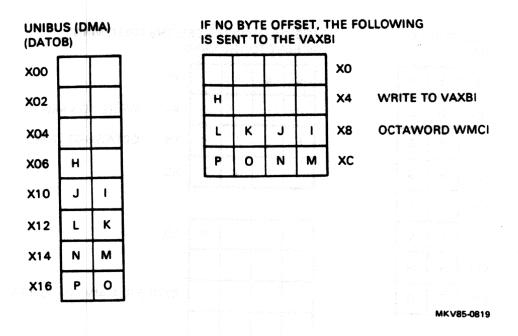

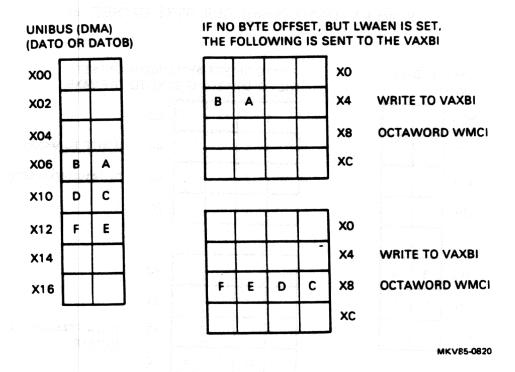

#### Page Title Figure No. Typical DWBUA Configuration ......1-1 1-1 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9 3-10 3-11 3-12 3-13 3-14 3-15 3-16 3-17 3-18 3-19 3-20 3-21 4-1 4-2 4-3 4-4 4-5 4-6 4-7 4-8 4-9 4-10 4-11 UET Control Register Format ......F-1 F-1 I-1 1-2 BDIBUF and UDIBUF Flags......I-3 1-3 DATO(B) Through BDP, BYTE OFFSET Clear, Starting at Octaword 1-4 Boundary.....1-6 DATOB Through BDP, BYTE OFFSET Clear, Starting at Byte 8......I-7 1-5

### **FIGURES (Cont)**

#### Figure No.

Table No.

#### Title

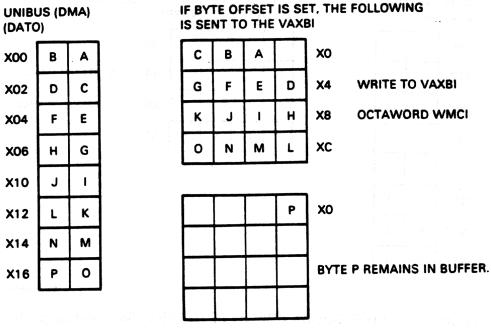

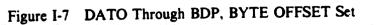

| I-6                            | DATO(B) Through BDP, BYTE OFFSET Clear, LWAEN Set                                 | I-7 |

|--------------------------------|-----------------------------------------------------------------------------------|-----|

| I-7                            | DATO Through BDP, BYTE OFFSET Set                                                 |     |

| I-8                            | DATO Through BDP, BYTE OFFSET and LWAEN Set                                       | I-8 |

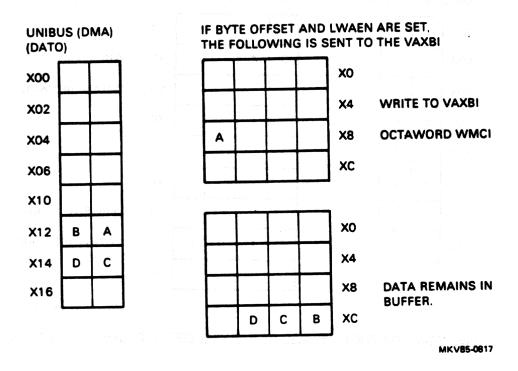

| J-1                            | IDENT Flow Diagram                                                                | J-3 |

| J-2                            | Interrupt/IDENT Timing Diagram                                                    | J-5 |

| a 🖉 a 🚝 a statut sa sur sa sur | Here Here Here Here The The The The The The Here Here Here Here Here Here Here He |     |

### TABLES

Title

stabilities from the first states of the second s

### Page

Page

|                               | 이 이 것 같아요. 이 가지 않는 것 않는 것 같아요. 이 가지 않는 것 않는 것 같아요. 이 가지 않는 것 같아요. 이 가지 않는 것 않는 |             |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1-1                           | DWBUA Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-2         |

| 1-2                           | DWBUA Current Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 2-1                           | DWBUA Components - UNIBUS Installed in BA32-AC/AD Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-2         |

| 2-2                           | DWBUA Components - UNIBUS Installed in BA11 Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 2-3                           | Macrodiagnostic Program Sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| 2-4                           | Tools and Test Equipment for Maintenance Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| 2-5                           | Symptoms and Possible Causes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| 2-6                           | Multiple VAXBI Base Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| 2-7                           | UNIBUS Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| 2-8                           | UNIBUS Quiescent Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| 3-1                           | Register Bit Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| 3-2                           | Microdiagnostic Register Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 3-3                           | Data Path Control and Status Register Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 4-1                           | DWBUA Block Diagram Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| 4-2                           | DWBUA Responses to VAXBI-to-DWBUA Transactions<br>VAXBI-to-DWBUA Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| 4-3                           | VAXBI-to-DWBUA Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-5         |

| 4-4                           | Bus Masters and Slaves for VAXBI-to-UNIBUS Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-7         |

| 4-5                           | DWBUA Responses to VAXBI-to-UNIBUS Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-8         |

| 4-6                           | VAXBI-to-UNIBUS Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| 4-7                           | Bus Masters and Slaves for UNIBUS-to-VAXBI Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| 4-8                           | DWBUA Responses to UNIBUS-to-VAXBI Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 4-9                           | UNIBUS-to-VAXBI Commands Through the Direct Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| 4-10                          | UNIBUS-to-VAXBI Commands Through a Buffered Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| C-1                           | Self-Test Microdiagnostic Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C-1         |

| D-1                           | Macrodiagnostic Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>D-</b> 1 |

| E-1                           | DWBI A Responses to BIIC EVENT Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E-1         |

| F-1                           | UNIBUS Exerciser Terminator Registers<br>Transfer Command Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F-1         |

| F-2                           | Transfer Command Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F-2         |

| G-1                           | Node Space and Window Space Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| H-1                           | Register Initial States<br>MSYN - SSYN Time Intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H-1         |

| K-1                           | MSYN - SSYN Time Intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | K-2         |

| Second Contraction and an and |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

RDBUCT and UDBERT TARS

### PREFACE

#### MANUAL STRUCTURE AND AUDIENCE

This manual is divided into two parts:

#### Part I - Installation

Part I includes an introduction to the DWBUA, product specifications, and instructions for installing and testing a DWBUA option. It is intended for DIGITAL personnel or customers who install this adapter. A knowledge of VAX hardware is assumed.

#### Part II - Technical Description

This part of the manual provides the technical information needed by the system programmer and the support engineer, as well as by customer engineers and programmers who incorporate this adapter into their own product or system. A knowledge of VAX architecture, the VAX Bus Interconnect (VAXBI), and the UNIBUS is assumed.

#### **RELATED DOCUMENTATION**

The DWBUA is one of a family of processors, memories, and adapters that use the 32-bit VAXBI bus. For a technical summary of the VAXBI bus and a description of VAXBI options, see the VAXBI Options Handbook - EB-27271-46.

**NOTE:** For ease of use and for reader comprehension, the DWBUA adapter (VAXBI to UNIBUS Adapter) will be referred to as DWBUA throughout this document. The VAXBI bus will be referred to as VAXBI, and UNIBUS bus will be referred to as UNIBUS.

### PREPACE

#### MANUAL STRUCTURE AND ALIDIEVCE The minute is divided into two parts

#### antitation in it is all

then I includes an introduction in the DWEUA, product receiversizes, and instructions for installing and recting a DWBUA optime. It is introduct for DWEUTAL point read or classophers who install this adapter. A knowledge of VAX hardwate is astructed.

#### water to the state of the second s

This part of the mention provides the featurest characters needed by the system programmer and no subject engineer, as well as by automate sequences that programmers who incorporate this adapter into that own product or system. A knowledge of VAX and Courts, the VAX Bus Interconnect (VAXB), and the UNIRUS is assumed.

#### MONTATION CONCINCTION

The DWRLA Films of a family of processors, are adapted into the the table of VAXBI optimized state of the VAXBI Optimized a technical statementy of the VAXBI but and a definition of VAXBI optimum, see the VAXBI Optimized factors of VAXBI optimum and set of VAXBI optimum

NUTEL For ease of unit and for reader controportion, the DIVELS another (VAXB) in DIVERSO (deputy) will be referred to as DIVELS) thereighted the statistical Tev VAXBI but will be referred to the VAXBL and DIVERSS but will be referred in as UNIGES. Part I Installation

(1010) (pip)

### CHAPTER 1 INTRODUCTION

20131/11 with managers a sheet of the second second

CONTRACTOR AND A DEVICE

### **1.1 PRODUCT DESCRIPTION**

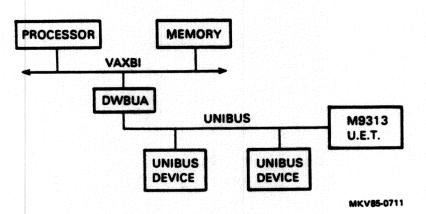

The VAXBI to UNIBUS Adapter (DWBUA), enables transfers between the high-speed synchronous VAXBI and the asynchronous UNIBUS. Through the DWBUA, the VAXBI has access to any UNIBUS address space, and the UNIBUS has access to any VAXBI address space.

Antonio intel A TRACE Second States

The DWBUA transfers data between the buses in two ways:

- 1. Through the Direct Data Path (DDP); the data is transferred immediately.

- 2. Through a Buffered Data Path (BDP); the DWBUA internally buffers as much as one octaword (16 bytes) of data per transfer to maximize the VAXBI bandwidth.

All VAXBI-initiated transactions transfer data through the Direct Data Path. UNIBUS-initiated transactions can transfer data through either the Direct Data Path or a Buffered Data Path.

Other features of the DWBUA are:

- UNIBUS arbitrator

- UNIBUS devices can interrupt on the VAXBI

- Data transfer rate up to 1.0M b/s better

- Self-test to verify data paths and control logic, and to report failures to the VAXBI

Figure 1-1 Typical DWBUA Configuration

#### **1.2 SPECIFICATIONS**

#### 1.2.1 Bus Loading

The DWBUA is 0.5 dc unit load on the UNIBUS.

The DWBUA is 3.5 ac unit load on the UNIBUS.

1.2.2 Power Requirements

#### Table 1-1 DWBUA Power Requirements

| some contra            | 56.20<br>0.6 | 40.50<br>0.54 | 36.50<br>0.036   | 31.35<br><0.012 | 5.00    |

|------------------------|--------------|---------------|------------------|-----------------|---------|

| ie XAX di<br>XBL and C | Maximum      | Standard      | POWER<br>Typical | Minimum         | VOLTAGE |

viertubinimi bertetenast et ante ede (UDP), dan Paris terreterende interneterende interneterende interneterende

#### 1.2.3 Current Requirements

Through a Bulfored Date Parb (BDP): the DWBLA internally outlens i (16 syres) of data for transfer to maximize the VAXBI bandwidth)

| Table | 1-2 | DWBU | <b>A</b> Current | Requi | rements |  |

|-------|-----|------|------------------|-------|---------|--|

|       |     |      |                  |       |         |  |

| - Public Device Indiated transfor- | <mark>19 Honithain</mark><br>1987 an 1984 | CURRENT      |              | All VAXBHinitrated transaction<br>ions can transfer data thirrugh |

|------------------------------------|-------------------------------------------|--------------|--------------|-------------------------------------------------------------------|

| VOLTAGE                            | Minimum                                   | Typical      | Standard     | Maximum                                                           |

| 5.00<br>-12.00                     | 6.6<br><0.001                             | 7.3<br>0.003 | 8.1<br>0.045 | 10.71 SH 10 2010191 155K                                          |

#### **1.3 SUPPORTED UNIBUS DEVICES**

A subset of the available UNIBUS devices is supported in a configuration with a DWBUA. See Appendix A for details.

Billet in with data parts and control logic and to report follows to the VAXIII

noneurganes AURING lesingT 1-1 sugR

## CHAPTER 2 INSTALLATION AND TEST

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  | 6.88 |  |  |  |  |      |      |     |

|--|--|--|--|-----|--|--|-----|--|------|--|------------------|--|--------|--|--|--|------|--|--|--|--|------|------|-----|

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  | 14 <sup>11</sup> |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  | 1.4 |  |  |     |  |      |  |                  |  | 34 T - |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  | 303 |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  | £ 3. |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  | 6.12 |  |                  |  |        |  |  |  |      |  |  |  |  | 20   | - 92 |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  | 1.16 |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      | 67. |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  | - 37 |      |     |

|  |  |  |  |     |  |  |     |  |      |  |                  |  |        |  |  |  |      |  |  |  |  |      |      |     |

is and in the second second

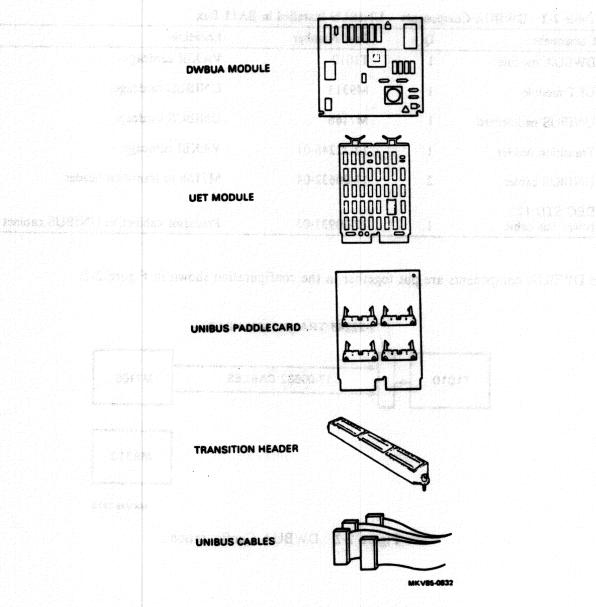

#### **2.1 OPTION COMPONENTS**

and E.A. Short A.B. of balancial EURAND + mesopological sciences (

| Component         | Qty              | Part Number | Location                   |

|-------------------|------------------|-------------|----------------------------|

| DWBUA module      | 1                | T1010       | VAXBI cardcage             |

| UET module        | 8 8 <b>1</b> - 1 | M9313       | UNIBUS cardcage            |

|                   | L                | M7166       | UNIBUS cardcage            |

| Transition header | 1                | 12-22246-01 | VAXBI cardcage             |

| UNIBUS cables     | 1                | 17-00631-01 | M7166 to transition header |

|                   |                  |             | ALANO MONENTS              |

Table 2-1 DWBUA Components - UNIBUS Installed in BA32-AC/AD Box

Table 2-2 DWBUA Components - UNIBUS Installed in BA11 Box

| Component                      | Qty | Part Number | Location                            |

|--------------------------------|-----|-------------|-------------------------------------|

| DWBUA module                   | 1   | T1010       | VAXBI cardcage                      |

| UET module                     | 1   | M9313       | UNIBUS cardcage                     |

| UNIBUS paddlecard              | 1   | M7166       | UNIBUS cardcage                     |

| Transition header              | 1   | 12-22246-01 | VAXBI cardcage                      |

| UNIBUS cables                  | 2   | 17-00632-04 | M7166 to transition header          |

| DEC STD 123<br>power bus cable |     | 17-00931-03 | Processor cabinet to UNIBUS cabinet |

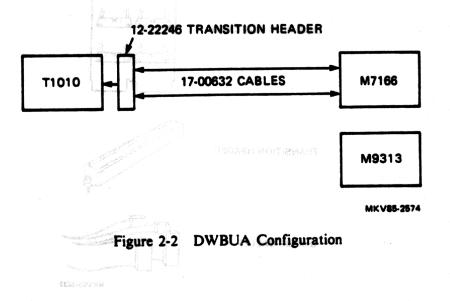

The DWBUA components are put together in the configuration shown in Figure 2-2.

2.2 INSTALLATION & Bir Justin of the Astronuce Inde an breadbles of the second

#### sudgised 2091/2011 in the Advant CAUTION

CAUTION An antistatic wrist strap connected to an active ground must be worn when installing the DWBUA.

WARNING Shut off system power before proceeding.

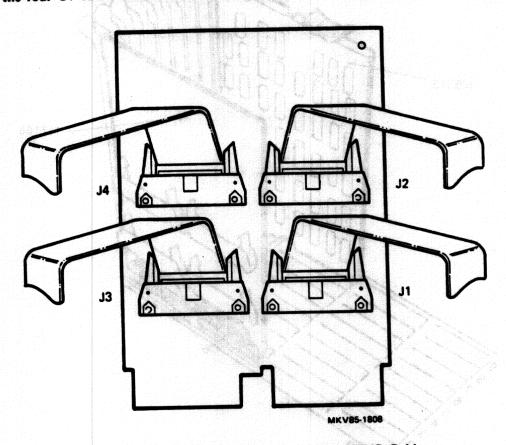

Attach the four UNIBUS cables to the M7166 paddlecard (Figure 2-3). The connectors are keyed. 1.

2-3

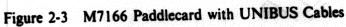

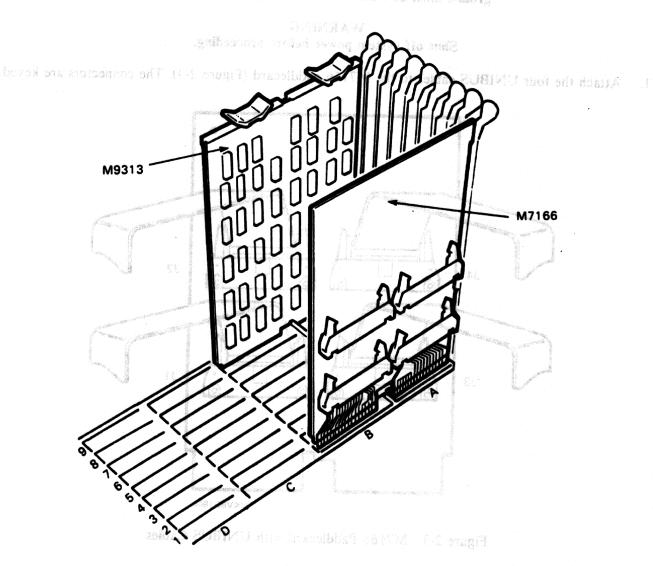

- 2. Insert the M7166 paddlecard into slot 1, segments A and B, of the UNIBUS backplane (Figure 2-4),

- 3. Insert the M9313 UET module into the last slot, segments A and B, of the UNIBUS backplane (Figure 2-4).

MKV85-0763

Figure 2-4 UNIBUS Backplane

4. Insert grant continuity cards in all unused UNIBUS slots.

NOTE

For field installations only, the T1010 module may be installed in any empty VAXBI slot (except slot 1). Installation in the next empty slot (after slot 1) is suggested.

5. Install the transition header on the backplane of the slot that will hold the T1010 module (Figure 2-5).

NOTE When installing the transition header, use only the torque screwdriver (P/N 29-17381-00) provided in the Field Service kit.

Figure 2-5 VAXBI Transition Header Installation

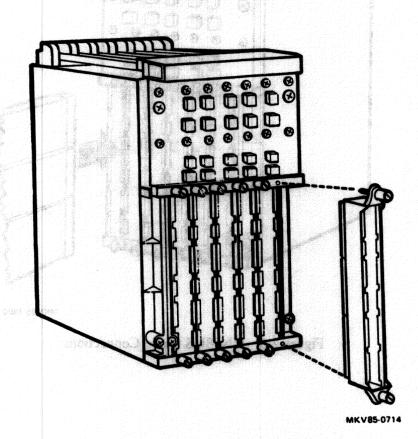

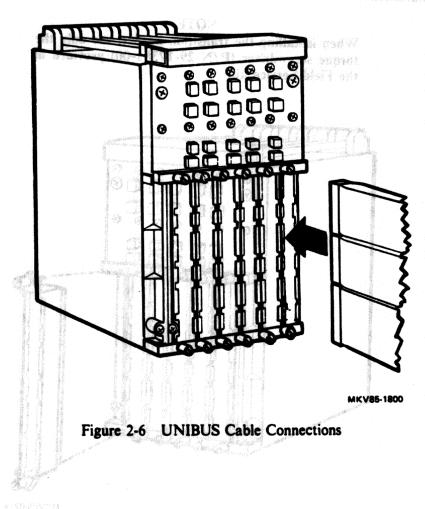

- Refer to Figure 2-6 and connect the four UNIBUS cables to the transition header assembly. 6.

- least great continuity cards in all unused UNIBES slow

- J1 segment E (left) J2 - segment E (right) J3 - segment D (left), tole tipoto) tol. 1826 A C (tipot you wi bolisteri ad J4 - segment D (right) 1012 1012 (16/10 1/20 and al antibilities)

#### The connectors are keyed.

- 7. Insert the T1010 module into the appropriate slot of the VAXBI cardcage.

- 8. If the UNIBUS backplane is in an expansion cabinet, the power bus cable (P/N 17-00931-03) may be installed from the processor cabinet to the expansion cabinet.

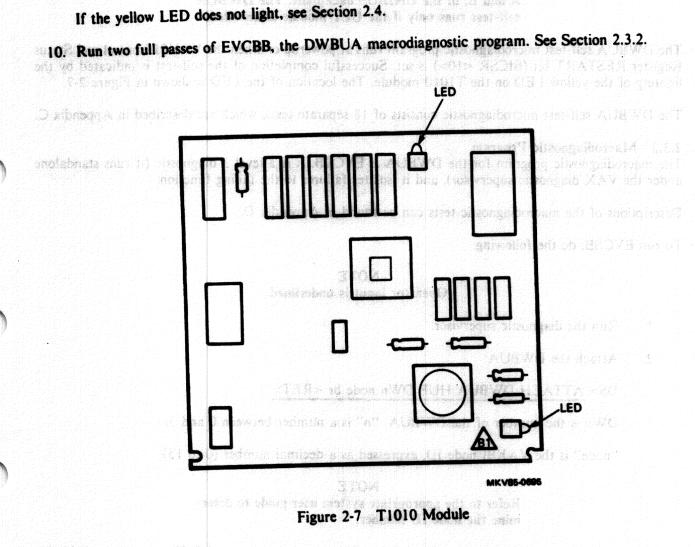

- Power up the system. The DWBUA self-test runs upon powerup. Check that the yellow LED on the T1010 module lights. See Figure 2-7.

A and R. M. the UMBRED as

while between provided and a restrict restrict a restrict and a line of restriction of restriction of restriction of the

allong the rate of the fill

CERTER NUTLES NUTLES NO. 1 MUSE AND

receiver of the SECTION maps ("geal" in the above community) is or thenal, it to SECTION normally an indexity the DEFAULT section is run. The SECTION moment and the tests they normally are instead in Table 2-st.

#### 2.3 TEST

that the vallow LEO on the

### 2.3.1 Self-Test Microdiagnostic Program

If the UNIBUS backplane is in an expansion cabiner be installed from the processor celuter to

NOTE

A UNIBUS Exerciser Terminator (UET) module and a start of the second (M9313) must be installed in the last slot, segments the laboration of the A and B, of the UNIBUS backplane. The DWBUA self-test runs only if the UET module is installed.

lasen the T1010 module into the appropriate dot of the VAXBI cardence

The DWBUA self-test microdiagnostic program runs at powerup or when the VAXBI Control and Status Register RESTART bit (BICSR <10>) is set. Successful completion of the self-test is indicated by the lighting of the yellow LED on the T1010 module. The location of the LED is shown in Figure 2-7.

The DWBUA self-test microdiagnostic consists of 18 separate tests, which are described in Appendix C.

#### 2.3.2 Macrodiagnostic Program

The macrodiagnostic program for the DWBUA is EVCBB. It is a level 3 diagnostic (it runs standalone under the VAX diagnostic supervisor), and it isolates failures to the failing function.

Descriptions of the macrodiagnostic tests can be found in Appendix D.

To run EVCBB, do the following.

NOTE

**Operator input is underlined.**

- Run the diagnostic supervisor. 1.

- 2. Attach the DWBUA:

DS> ATTACH DWBUA HUB DWn node br <RET>

DWn is the number of the DWBUA. "n" is a number between 0 and 3.

"node" is the VAXBI node ID, expressed as a decimal number (0 to 15).

NOTE

Refer to the appropriate system user guide to determine the node ID number.

"br" is the UNIBUS BR interrupt level, a number between 4 and 7. The recommended value is 7.

3. Run the macrodiagnostic:

DS> RUN EVCBB[/SECTION:xxx]<RET>

Inclusion of the SECTION name ("xxx" in the above command) is optional. If no SECTION name is included, the DEFAULT section is run. The SECTION names and the tests they include are listed in Table 2-3.

### Tests 31 and 32 can be run only if a UNIBUS Exerciser (UBE) is attached.

| Table 2-3 | Macrodiag     | nostic Pi    | rograi                                                                                      | m Sec    | tions     |        |  |

|-----------|---------------|--------------|---------------------------------------------------------------------------------------------|----------|-----------|--------|--|

| Section   |               | <b>Fests</b> | Ú.                                                                                          | THE WALL | 2.345     |        |  |

| DEFAULT   | <b>1</b>      | l – 30       |                                                                                             |          |           |        |  |

| ALL       | 1101131       | l – 32       | iyati x                                                                                     | n sj     |           |        |  |

| ALL       |               | in a second  | -<br>51 A                                                                                   | 69.25    | Ny Sta    |        |  |

| UBE       |               | 31, 32       |                                                                                             |          |           |        |  |

|           | enser heren e | At inte      | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Acres    | ner de ce | a s de |  |

anaouppullar ......

and billion to many the second

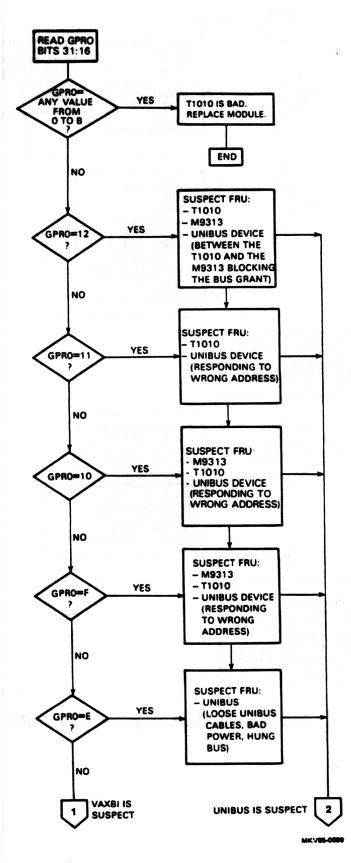

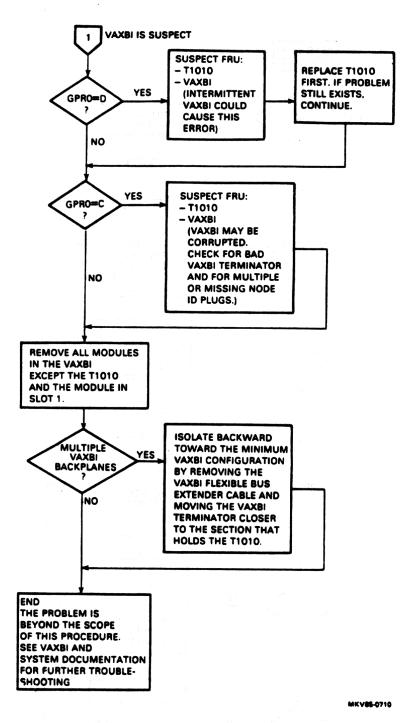

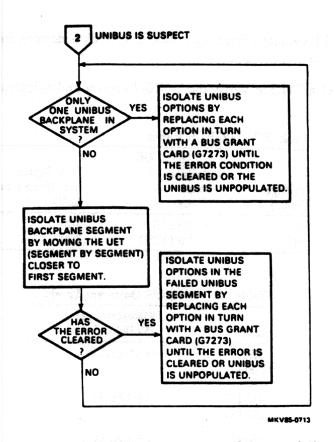

#### 2.4 TROUBLESHOOTING

shelinaba AURVA a salaha

This procedure provides the information needed to isolate a DWBUA failure to one of its assemblies: T1010 module, I/O cable, M7166 paddlecard, UNIBUS, or M9313 UET module. Corrective maintenance of the DWBUA consists of faulty subassembly replacement.

This procedure does not attempt to isolate problems caused by devices attached to the UNIBUS. It does, however, identify the UNIBUS node that is causing a DWBUA malfunction.

The assumption is made in this procedure that system troubleshooting procedures have indicated a problem in the DWBUA. No system-specific troubleshooting procedures are included here.

A. D. R. G. adt artes 2 ST

#### 2.4.1 Tools and Test Equipment

The tools and test equipment listed in Table 2-4 are needed to perform the maintenance procedures described in this section. he are the marked (FPA his released show some a FPA)

| seinn or sea<br>as mann | Table 2-4 Tools and |                  |                     | DIGITAL     |

|-------------------------|---------------------|------------------|---------------------|-------------|

| ann wardenar            | Equipment           | Manufacturer (U) | Designation         | Part Number |

| i nevalikteere ook      | Gold Wipes          | Texwipe          | TX809               | 49-01603-01 |

| i kitat kan             | Torque Screwdriver  | Utica            | ni ci celi stilo si | 29-17381-00 |

|                         | Bus Grant Card      |                  |                     | G7273       |

#### 2.4.2 Procedure

This section is a step-by-step procedure for isolating faults to the field replaceable unit (FRU). It uses only the tools and test equipment listed in Table 2-4 and the DWBUA adapter's self-test. By using this procedure, faults in the DWBUA can be isolated when the system is not capable of running diagnostics. (Such a situation can occur if the DWBUA is in the load path for the operating system and diagnostics.)

See Section 2.3.1 and Appendix C for information on the DWBUA adapter's self-test.

#### NOTE

Follow the steps in the order listed.

START - Is the DWBUA malfunctioning? 1.

The DWBUA may be suspect if:

- The system cannot be booted from a UNIBUS device. a.

- No UNIBUS devices can be used. b.

- C. The system console indicates that the node number corresponding to DWBUA adapter's node ID is malfunctioning.

offdonseen**d**, N Excessive errors occur when using any UNIBUS device.

TTOTS mandals 140 cable 142136 paddecard, CNURUS, or MORES USE mode

The system crashes. Internation videoziedus viduel lo strikton AUR VC ach in second e.

2. **POWER DOWN THE SYSTEM -** Wait 30 seconds for the stored power to drain off. and allocation and and OPEN THE CABINET - Open the system cabinet so that the yellow lights on the modules can 3. The assumption is made in this procedure that system mublishooting procedure, as a problem in the DWBUA. No system-specific troubleshooting procedures are included here.

4. **POWER UP THE SYSTEM -** This starts the DWBUA self-test.

- inanging his I the stort CHECK THE LIGHT ON THE T1010 MODULE - If the yellow light on the T1010 module 5. is lit, the DWBUA has passed self-test. The problem is most likely not in the T1010 module, the UNIBUS cabling, or the terminator card (UET). If the light is OFF, go to Step 7.

- 6. RUN EVCBB - If the system is operational, run the system level diagnostic, EVCBB, to further verify that the problem is not in the DWBUA. Refer to the macrodiagnostic printout and documentation to isolate the failing FRU if this diagnostic should fail.

If one of the symptoms listed in Step 1 exists, but the DWBUA self-test passes, the problem is probably somewhere other than in the DWBUA. Refer to Table 2-5 for suggested areas to troubleshoot.

| Symptom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Possible Cause                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Cannot boot from a UNIBUS device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TO Dear dealer contained backs and and same shart |

| shie 1-4 and the DWBUA adapter's soll-test by using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I m bottell internations test bins cloot set      |

| Unable to use devices on the UNIBUS Para and and a basis of a second basis of the UNIBUS para and the second basis of the seco | Bad device of software and in the software        |

| Excessive errors when using any devices on the UNIBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Devices on the bus or system-wide problems        |